# 1.0GSPS、12/14/16ビットの デュアルD/Aコンバータ

# AD9776/AD9778/AD9779

### 特長

DAC出力サンプル・レート:1GSPS

单電源動作: 1.8V/3.3V

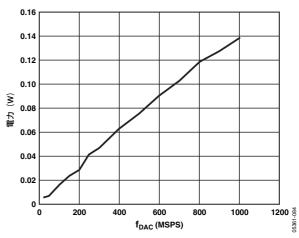

低消費電力:1.0W@1GSPS、600mW@500MSPS、フル動作

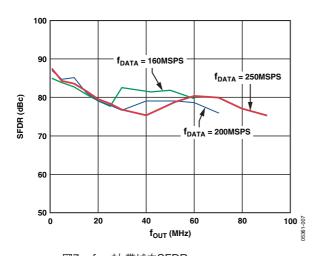

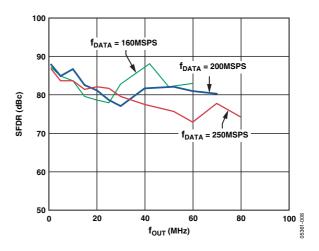

SFDR=78dBc(f<sub>our</sub>=100MHzまで)

シングル・キャリアWCDMA ACLR=79dBc@80MHz IF

調整可能なセットアップ/ホールドを備えたCMOSデータ入力

インターフェース

アナログ出力: 8.7~31.7mAで調節可能、RL=25~50Ω

新しい2/4/8×インターポレータ/複素変調器により、DAC帯

域幅のどこにでもキャリアを配置可能

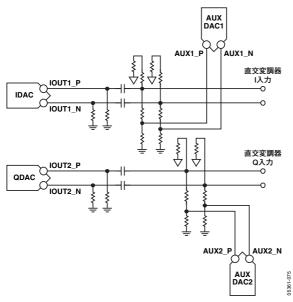

補助DACにより外付けVGAの制御とオフセット制御が可能

マルチチップ同期インターフェース

高性能、低ノイズのPLLクロック逓倍器

デジタル反転sincフィルタ

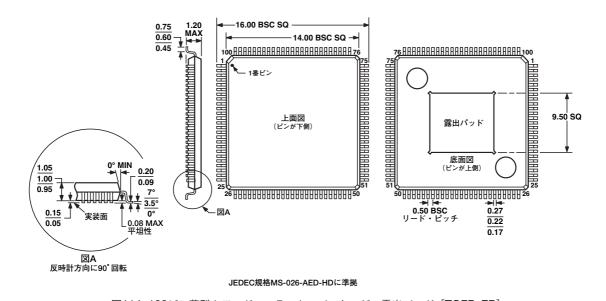

100ピン、露出パドル型TQFPパッケージ

### アプリケーション

無線インフラストラクチャ デジタル高/低IF合成 内部デジタル・アップコンバージョン機能 送信ダイバーシティ ワイドバンド通信システム ポイントtoポイント無線、LMDS マルチキャリアWCDMA マルチキャリアGSM

#### 概要

AD9776 (12ビット) /AD9778 (14ビット) /AD9779 (16 ビット)は、1GSPSのサンプル・レートを提供する、高ダイナ ミック・レンジのデュアルD/Aコンバータ (DAC) で、ナイキ スト周波数までのマルチキャリアの生成が可能です。これらの デバイスは、複雑なデジタル変調やゲイン/オフセット補償な ど、ダイレクト・コンバージョン方式の送信アプリケーション に最適な機能を備えています。DAC出力は、AD8349などのア ナログ直交変調器とのシームレスなインターフェースを実現で きるように最適化されています。シリアル・ペリフェラル・イ ンターフェース (SPI) によって、多くの内部パラメータの設 定/読出しが可能です。出力フルスケール電流は、10~30mA の範囲で設定できます。高度な0.18µm CMOSプロセスで製造 され、1.8V電源と3.3V電源で動作し、総消費電力は1.0Wです。 100ピンTQFPパッケージで提供しています。

### 製品のハイライト

- 1. 超低ノイズと優れた相互変調歪み (IMD) 性能により、 ベースバンドから中間周波数までのワイドバンド信号の高 品質合成が可能です。

- 2. 独自のDAC出力スイッチング技術により、動的性能を高め

- 3. 電流出力は、さまざまなシングルエンド回路または差動回 路トポロジ用に簡単に設定できます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の 利用に関して、あるいは利用によって生じる論とされています。 せん。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもので もありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有 に属します。 ※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2005 Analog Devices, Inc. All rights reserved.

REV. 0

社/〒105-6891

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 電話03(5402)8200

## 目次

| 機能ブロック図3                   | DACCLK入力の駆動              | 33 |

|----------------------------|--------------------------|----|

| 仕様                         | フルスケール電流の生成              | 36 |

| 絶対最大定格                     | 消費電力                     | 37 |

| ESDに関する注意5                 | パワーダウン・モードとスリープ・モード      | 38 |

| ピン配置と機能の説明8                | インターリーブ・データ・モード          | 39 |

| 代表的な性能特性14                 | タイミング情報                  | 39 |

| 用語の説明22                    | 評価用ボードの動作                | 45 |

| 動作原理23                     | 実装された直交変調器AD8349を使用するための |    |

| シリアル・ペリフェラル・インターフェース23     | 評価用ボードの変更                | 47 |

| MSB/LSB転送                  | 評価用ボードの回路図               | 48 |

| SPIレジスタのマップ25              | 外形寸法                     | 55 |

| インターポレーション・フィルタのアーキテクチャ29  | オーダー・ガイド                 | 55 |

| インターポレーション・フィルタの最小/最大幅仕様33 |                          |    |

## 改訂履歴

7/05—Revision 0: Initial Version

\_2\_ REV. 0

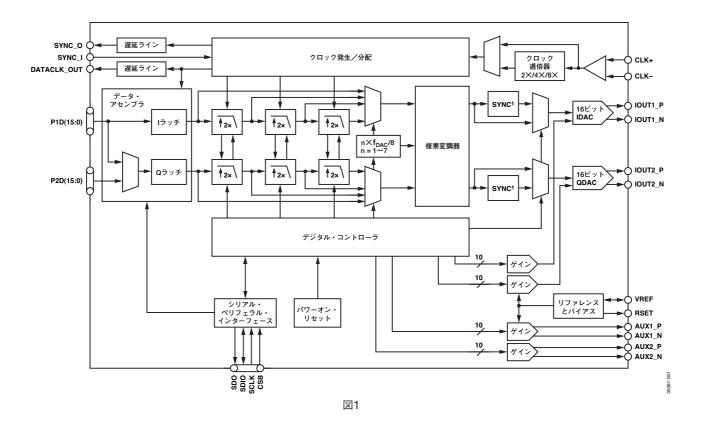

# 機能ブロック図

REV. 0 — 3 —

# 仕様

特に指定のない限り、 $T_{\text{min}} \sim T_{\text{max}}$ 、AVDD33=3.3V、DVDD33=3.3V、DVDD18=1.8V、CVDD18=1.8V、 $I_{\text{outffs}}$ =20mA、最大サンプル・レート。

表1. AD9776/AD9778/AD9779のDC仕様

|                                                           |        | AD977     | 6      |        | AD977      | 8      |        | AD977     | 9      |        |

|-----------------------------------------------------------|--------|-----------|--------|--------|------------|--------|--------|-----------|--------|--------|

| パラメータ                                                     | Min    | Тур       | Max    | Min    | Тур        | Max    | Min    | Тур       | Max    | 単位     |

| 分解能                                                       |        | 12        |        |        | 14         |        |        | 16        |        | ビット    |

| 精度                                                        |        |           |        |        |            |        |        |           |        |        |

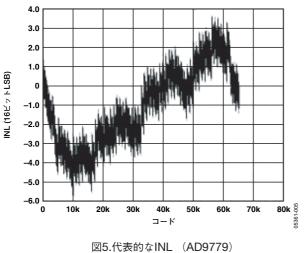

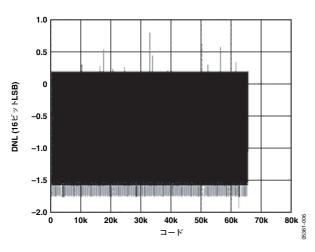

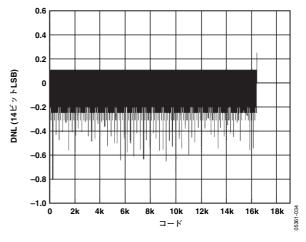

| 微分非直線性 (DNL)                                              |        | $\pm 0.1$ |        |        | $\pm 0.65$ |        |        | $\pm 2.1$ |        | LSB    |

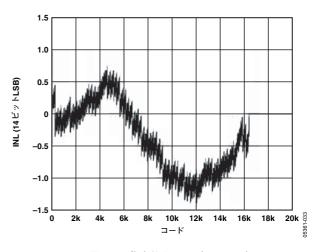

| 積分非直線性 (INL)                                              |        | $\pm 0.6$ |        |        | $\pm 1$    |        |        | $\pm 3.7$ |        | LSB    |

| メインDAC出力                                                  |        |           |        |        |            |        |        |           |        |        |

| オフセット誤差                                                   | -0.001 | 0         | +0.001 | -0.001 | 0          | +0.001 | -0.001 | 0         | +0.001 | % FSR  |

| ゲイン誤差<br>(内部リファレンス使用時)                                    |        | $\pm 2$   |        |        | $\pm 2$    |        |        | $\pm 2$   |        | % FSR  |

| フルスケール出力電流「                                               | 8.66   | 20.2      | 31.66  | 8.66   | 20.2       | 31.66  | 8.66   | 20.2      | 31.66  | mA     |

| 出力コンプライアンス電圧範囲                                            | -1.0   |           | +1.0   | -1.0   |            | +1.0   | -1.0   |           | +1.0   | V      |

| 出力抵抗                                                      |        | 10        |        |        | 10         |        |        | 10        |        | ΜΩ     |

| ゲインDACの単調性保証                                              |        |           |        |        |            |        |        |           |        |        |

| メインDAC温度ドリフト                                              |        |           |        |        |            |        |        |           |        |        |

| オフセット                                                     |        | 0.04      |        |        | 0.04       |        |        | 0.04      |        | ppm/°C |

| ゲイン                                                       |        | 100       |        |        | 100        |        |        | 100       |        | ppm/°C |

| リファレンス電圧                                                  |        | 30        |        |        | 30         |        |        | 30        |        | ppm/°C |

| 補助DAC出力                                                   |        |           |        |        |            |        |        |           |        |        |

| 分解能                                                       |        | 10        |        |        | 10         |        |        | 10        |        | ビット    |

| フルスケール出力電流」                                               | -1.998 |           | +1.998 | -1.998 |            | +1.998 | -1.998 |           | +1.998 | mA     |

| 出力コンプライアンス電圧範囲<br>(ソース)                                   | 0      |           | 1.6    | 0      |            | 1.6    | 0      |           | 1.6    | V      |

| 出力コンプライアンス電圧範囲<br>(シンク)                                   | 0.8    |           | 1.6    | 0.8    |            | 1.6    | 0.8    |           | 1.6    | V      |

| 出力抵抗                                                      |        | 1         |        |        | 1          |        |        | 1         |        | ΜΩ     |

| 補助DACの単調性保証                                               |        |           |        |        |            |        |        |           |        |        |

| リファレンス                                                    |        |           |        |        |            |        |        |           |        |        |

| 内部リファレンス電圧                                                |        | 1.2       |        |        | 1.2        |        |        | 1.2       |        | V      |

| 出力抵抗                                                      |        | 5         |        |        | 5          |        |        | 5         |        | kΩ     |

| アナログ電源電圧                                                  |        |           |        |        |            |        |        |           |        |        |

| AVDD33                                                    | 3.13   | 3.3       | 3.47   | 3.13   | 3.3        | 3.47   | 3.13   | 3.3       | 3.47   | V      |

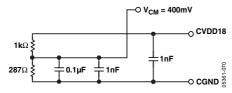

| CVDD18                                                    | 1.70   | 1.8       | 1.90   | 1.70   | 1.8        | 1.90   | 1.70   | 1.8       | 1.90   | V      |

| デジタル電源電圧                                                  |        |           |        |        |            |        |        |           |        |        |

| DVDD33                                                    | 3.13   | 3.3       | 3.47   | 3.13   | 3.3        | 3.47   | 3.13   | 3.3       | 3.47   | V      |

| DVDD18                                                    | 1.70   | 1.8       | 1.90   | 1.70   | 1.8        | 1.90   | 1.70   | 1.8       | 1.90   | V      |

| 消費電力                                                      |        |           |        |        |            |        |        |           |        |        |

| $1 \times \text{F-F}$ ( $f_{DAC} = 100 \text{MSPS}$ ,     |        | 250       | 300    |        | 250        | 300    |        | 250       | 300    | mW     |

| IF = 1MHz                                                 |        |           |        |        |            |        |        |           |        |        |

| $2\times$ モード $(f_{DAC}=320MSPS$ 、 $IF=16MHz$ 、 $PLL$ オフ) |        | 498       |        |        | 498        |        |        | 498       |        | mW     |

| $2\times$ モード $(f_{DAC} = 320MSPS$ 、                      |        | 588       |        |        | 588        |        |        | 588       |        | mW     |

| IF=16MHz、PLLオン)                                           |        |           |        |        |            |        |        |           |        |        |

| $4 \times \xi - F$ ( $f_{DAC}/4$ Mod,                     |        | 572       |        |        | 572        |        |        | 572       |        | mW     |

| $f_{DAC} = 500MSPS$                                       |        |           |        |        |            |        |        |           |        |        |

| IF=137.5MHz、Q DACオフ)                                      |        |           |        |        |            |        |        |           |        |        |

|                                               |      | AD977 | '6   |      | AD977 | 78   |      | AD977 | '9   |            |

|-----------------------------------------------|------|-------|------|------|-------|------|------|-------|------|------------|

| パラメータ                                         | Min  | Тур   | Max  | Min  | Тур   | Max  | Min  | Тур   | Max  | 単位         |

| $8 \times \text{E-F} (f_{DAC}/4 \text{ Mod},$ |      | 980   |      |      | 980   |      |      | 980   |      | mW         |

| $f_{DAC} = 1GSPS$ , $IF = 262.5MHz$ )         |      |       |      |      |       |      |      |       |      |            |

| パワーダウン・モード                                    |      | 2     | 3.7  |      | 2     | 3.7  |      | 2     | 3.7  | mW         |

| 電源電圧変動除去比—AVDD33                              | -0.3 |       | +0.3 | -0.3 |       | +0.3 | -0.3 |       | +0.3 | %FSR/V     |

| 動作範囲                                          | -40  | +25   | +85  | -40  | +25   | +85  | -40  | +25   | +85  | $^{\circ}$ |

<sup>10</sup>kΩの外付け抵抗に基づく。

特に指定のない限り、 $T_{\text{min}} \sim T_{\text{max}}$ 、AVDD33=3.3V、DVDD33=3.3V、DVDD18=1.8V、CVDD18=1.8V、 $I_{\text{outes}}$ =20mA、最大サンプル・レート。特に指定のない限り、LVDSドライバとレシーバは、IEEE-1596 reduced range link(縮小範囲リンク)に準拠して います。

### 表2. AD9776/AD9778/AD9779のデジタル仕様

| パラメータ                                                                                      | Min   | Тур | Max  | 単位   |

|--------------------------------------------------------------------------------------------|-------|-----|------|------|

| LVDSレシーバの入力                                                                                |       |     |      |      |

| $(SYNC_I + SYNC_I -)$ , $SYNC_I + V_{IA}$ , $SYNC_I - V_{IR}$                              |       |     |      |      |

| 入力電圧範囲( $V_{\scriptscriptstyle \rm IA}$ または $V_{\scriptscriptstyle  m IR}$ )               | 825   |     | 1575 | mV   |

| 入力差動スレッショールド( $old V_{ m norm}$ )                                                          | -100  |     | +100 | mV   |

| 入力差動ヒステリシス(V <sub>IDTHI</sub> – V <sub>IDTHI</sub> )                                       |       | 20  |      | mV   |

| レシーバの差動入力インピーダンス( $\mathbf{R_{_{\mathbf{N}}}}^{_{\mathbf{I}}}$ )                           | 80    |     | 120  | Ω    |

| LVDS入力レート                                                                                  |       |     | 125  | MSPS |

| セットアップ時間 (DACクロックへのSYNC_I)                                                                 | -0.2  |     |      | ns   |

| ホールド時間 (DACクロックへのSYNC_I)                                                                   | 1     |     |      | ns   |

| LVDSドライバ出力                                                                                 |       |     |      |      |

| $(SYNC_O+, SYNC_O-), SYNC_O+=V_{OA}, SYNC_O-=V_{OB}, 1000$ 終端                              |       |     |      |      |

| 出力ハイレベル電圧( $V_{\scriptscriptstyle \mathrm{OA}}$ または $V_{\scriptscriptstyle \mathrm{OB}}$ ) | 825   |     | 1575 | mV   |

| 出力ローレベル電圧( $V_{oA}$ または $V_{oB}$ )                                                         | 1025  |     |      | mV   |

| 出力差動電圧(IV <sub>op</sub> I)                                                                 | 150   | 200 | 250  | mV   |

| 出力オフセット電圧( $\mathbf{V}_{\mathrm{os}}$ )                                                    | 1150  |     | 1250 | mV   |

| 出力インピーダンス、シングルエンド( $\mathbf{R}_{\mathrm{o}}$ )                                             | 80    | 100 | 120  | Ω    |

| 最大クロック・レート                                                                                 | 1     |     |      | GHz  |

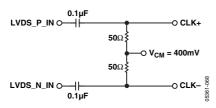

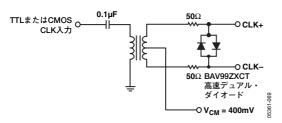

| DACクロック入力(CLK+、CLK-)                                                                       |       |     |      |      |

| ピークtoピーク電圧@ $CLK$ +および $CLK$ $-2$                                                          | 400   | 800 | 1600 | mV   |

| コモンモード電圧                                                                                   | 300   | 400 | 500  | mV   |

| 最大クロック・レート3                                                                                |       | 1   |      | GSPS |

| シリアル・ペリフェラル・インターフェース                                                                       |       |     |      |      |

| 最大クロック・レート (SCLK)                                                                          |       |     | 40   | MHz  |

| 最小パルス幅ハイレベル                                                                                |       |     | 12.5 | ns   |

| 最小パルス幅ローレベル                                                                                |       |     | 12.5 | ns   |

| 入力データ                                                                                      |       |     |      |      |

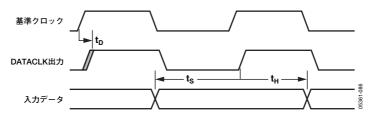

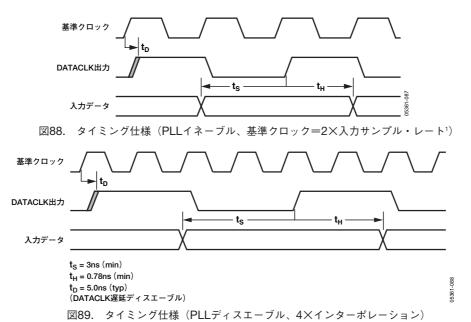

| セットアップ時間 (DATACLKへの入力データ (全モード))                                                           | 3.0   |     |      | ns   |

| ホールド時間(DATACLKへの入力データ(全モード))                                                               | -0.78 |     |      | ns   |

<sup>- 25℃</sup>での保証。25℃を超える温度では、120Qを超えるドリフトが生じることもあります。 <sup>2</sup> PLLを使用するときは、最小IVの振幅を推奨します。 <sup>3</sup> DVDD18=CVDD18=1.9Vのときの最大クロック・レート (typ)。

REV. 0 -5-

特に指定のない限り、 $T_{\text{min}} \sim T_{\text{max}}$ 、AVDD33=3.3V、DVDD33=3.3V、DVDD18=1.8V、CVDD18=1.8V、 $I_{\text{outffs}}$ =20mA、最大サンプル・レート。

表3. AD9776/AD9778/AD9779のAC仕様

|                                                                                   | AD9776 |        | AD9778 |     |      | AD9779 |     |      |     |        |

|-----------------------------------------------------------------------------------|--------|--------|--------|-----|------|--------|-----|------|-----|--------|

| パラメータ                                                                             | Min    | Тур    | Max    | Min | Тур  | Max    | Min | Тур  | Max | 単位     |

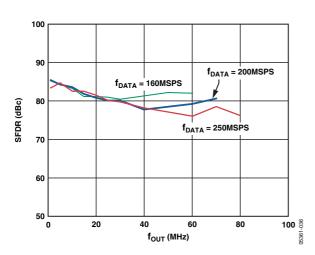

| スプリアス・フリー・ダイナミック・                                                                 |        |        |        |     |      |        |     |      |     |        |

| レンジ (SFDR)                                                                        |        |        |        |     |      |        |     |      |     |        |

| $f_{DAC} = 100MSPS$ , $f_{OUT} = 20MHz$                                           |        | 82     |        |     | 82   |        |     | 82   |     | dBc    |

| $f_{DAC} = 200MSPS$ , $f_{OUT} = 50MHz$                                           |        | 81     |        |     | 81   |        |     | 82   |     | dBc    |

| $f_{DAC} = 400MSPS$ , $f_{OUT} = 70MHz$                                           |        | 80     |        |     | 80   |        |     | 80   |     | dBc    |

| $f_{DAC} = 800MSPS$ , $f_{OUT} = 70MHz$                                           |        | 85     |        |     | 85   |        |     | 87   |     | dBc    |

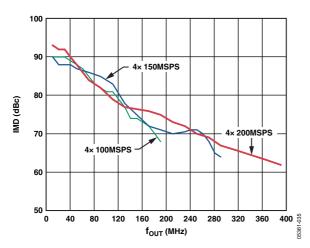

| ツートーン相互変調歪み(IMD)                                                                  |        |        |        |     |      |        |     |      |     |        |

| $f_{DAC} = 200MSPS$ , $f_{OUT} = 50MHz$                                           |        | 87     |        |     | 87   |        |     | 91   |     | dBc    |

| $f_{DAC} = 400MSPS$ , $f_{OUT} = 60MHz$                                           |        | 80     |        |     | 85   |        |     | 85   |     | dBc    |

| $f_{DAC} = 400MSPS$ , $f_{OUT} = 80MHz$                                           |        | 75     |        |     | 81   |        |     | 81   |     | dBc    |

| $f_{DAC} = 800MSPS$ , $f_{OUT} = 100MH$                                           |        | 75     |        |     | 80   |        |     | 81   |     | dBc    |

| ノイズ・スペクトル密度(NSD)                                                                  |        |        |        |     |      |        |     |      |     |        |

| (8トーン、500kHzトーン間隔)                                                                |        |        |        |     |      |        |     |      |     |        |

| $f_{DAC} = 200MSPS$ , $f_{OUT} = 80MHz$                                           |        | -152   |        |     | -155 |        |     | -158 |     | dBm/Hz |

| $f_{DAC} = 400MSPS$ , $f_{OUT} = 80MHz$                                           |        | -155   |        |     | -159 |        |     | -160 |     | dBm/Hz |

| $f_{\text{\tiny DAC}} = 800 \text{MSPS}$ , $f_{\text{\tiny OUT}} = 80 \text{MHz}$ |        | -157.5 | 5      |     | -160 |        |     | -161 |     | dBm/Hz |

| WCDMA隣接チャンネル漏れ率                                                                   |        |        |        |     |      |        |     |      |     |        |

| (ACLR)(シングル・キャリア)                                                                 |        |        |        |     |      |        |     |      |     |        |

| $f_{DAC} = 491.52 MSPS, f_{OUT} = 100 MHz$                                        |        | 76     |        |     | 78   |        |     | 79   |     | dBc    |

| $f_{DAC} = 491.52 MSPS, f_{OUT} = 200 MHz$                                        |        | 69     |        |     | 73   |        |     | 74   |     | dBc    |

| WCDMA第2隣接チャンネル漏れ率                                                                 |        |        |        |     |      |        |     |      |     |        |

| (ACLR) (シングル・キャリア)                                                                |        |        |        |     |      |        |     |      |     |        |

| $f_{DAC} = 491.52 MSPS$ , $f_{OUT} = 100 MHz$                                     |        | 77.5   |        |     | 80   |        |     | 81   |     | dBc    |

| $f_{DAC} = 491.52 MSPS, f_{OUT} = 200 MHz$                                        |        | 76     |        |     | 78   |        |     | 78   |     | dBc    |

## 絶対最大定格

#### 表4

| パラメータ                                                                                                                                                                                | 基準                   | 定格值                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------|

| AVDD33                                                                                                                                                                               | AGND<br>DGND<br>CGND | -0.3~+3.6 V                |

| DVDD33、DVDD18、<br>CVDD18                                                                                                                                                             | AGND<br>DGND<br>CGND | −0.3~+1.98 V               |

| AGND                                                                                                                                                                                 | DGND<br>CGND         | $-0.3 \sim +0.3 \text{ V}$ |

| DGND                                                                                                                                                                                 | AGND<br>CGND         | $-0.3 \sim +0.3 \text{ V}$ |

| CGND                                                                                                                                                                                 | AGND<br>DGND         | $-0.3 \sim +0.3 \text{ V}$ |

| I120, VREF, IPTAT                                                                                                                                                                    | AGND                 | $-0.3V\sim AVDD33+0.3V$    |

| $\begin{array}{cccc} I_{\text{out1-P}}, & I_{\text{out1-N}}, & I_{\text{out2-P}}, \\ I_{\text{out2-N}}, & Aux_{_{1-P}}, & Aux_{_{1-N}}, \\ Aux_{_{2-P}}, & Aux_{_{2-N}} \end{array}$ | AGND                 | -1.0V~AVDD33+0.3V          |

| P1D15~P1D0,<br>P2D15~P2D0                                                                                                                                                            | DGND                 | -0.3V~DVDD33+0.3V          |

| DATACLK, TXENABLE                                                                                                                                                                    | DGND                 | $-0.3V \sim DVDD33 + 0.3V$ |

| CLK+, CLK-, RESET, IRQ, PLL_LOCK, SYNC_O+, SYNC_O-, SYNC_I-                                                                                                                          | CGND                 | -0.3V~CVDD18+0.3V          |

| RESET, IRQ, PLL_LOCK, SYNC_O+, SYNC_O-, SYNC_I+, SYNC_I-, CSB, SCLK, SDIO, SDO                                                                                                       | DGND                 | -0.3V~DVDD33+0.3V          |

| ジャンクション温度                                                                                                                                                                            |                      | +125°C                     |

| 保存温度                                                                                                                                                                                 |                      | $-65 \sim +150$ °C         |

#### 熱抵抗

100ピン、熱特性強化型TQFPパッケージ:θ<sub>JA</sub>=27.4℃/W(自然空冷)

左記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

#### 注音

ESD (静電放電)の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

REV. 0 —7—

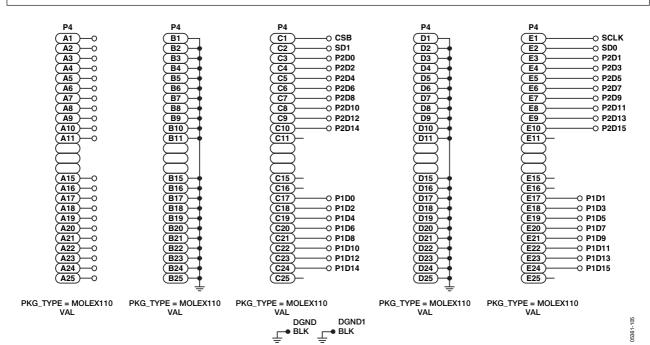

## ピン配置と機能の説明

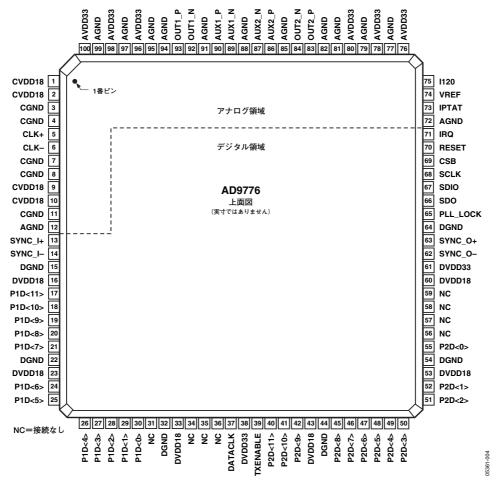

図2. AD9776のピン配置

表5. AD9776のピン機能の説明

| ピン番号 | 記号       | 記号                  | ピン番号 | 記号      | 記号                    |

|------|----------|---------------------|------|---------|-----------------------|

| 1    | CVDD18   | 1.8Vクロック電源          | 19   | P1D <9> | ポート1、データ入力 <b>D</b> 9 |

| 2    | CVDD18   | 1.8Vクロック電源          | 20   | P1D <8> | ポート1、データ入力D8          |

| 3    | CGND     | クロック・コモン            | 21   | P1D <7> | ポート1、データ入力D7          |

| 4    | CGND     | クロック・コモン            | 22   | DGND    | デジタル・コモン              |

| 5    | CLK+1    | 差動クロック入力            | 23   | DVDD18  | 1.8Vデジタル電源            |

| 6    | CLK-1    | 差動クロック入力            | 24   | P1D <6> | ポート1、データ入力D6          |

| 7    | CGND     | クロック・コモン            | 25   | P1D <5> | ポート1、データ入力D5          |

| 8    | CGND     | クロック・コモン            | 26   | P1D <4> | ポート1、データ入力D4          |

| 9    | CVDD18   | 1.8Vクロック電源          | 27   | P1D <3> | ポート1、データ入力D3          |

| 10   | CVDD18   | 1.8Vクロック電源          | 28   | P1D <2> | ポート1、データ入力D2          |

| 11   | CGND     | クロック・コモン            | 29   | P1D <1> | ポート1、データ入力D1          |

| 12   | AGND     | アナログ・コモン            | 30   | P1D <0> | ポート1、データ入力D0          |

| 13   | SYNC_I+  | 差動同期入力              | 31   | NC      | 接続なし                  |

| 14   | SYNC_I-  | 差動同期入力              | 32   | DGND    | デジタル・コモン              |

| 15   | DGND     | デジタル・コモン            | 33   | DVDD18  | 1.8Vデジタル電源            |

| 16   | DVDD18   | 1.8Vデジタル電源          | 34   | NC      | 接続なし                  |

| 17   | P1D <11> | ポート1、データ入力D11 (MSB) | 35   | NC      | 接続なし                  |

| 18   | P1D <10> | ポート1、データ入力D10       | 36   | NC      | 接続なし                  |

─8 ─ REV. 0

| <br>ピン番号 | 記号       | 記号                     |

|----------|----------|------------------------|

| 37       | DATACLK  | データ・クロック出力             |

| 38       | DVDD33   | 3.3Vデジタル電源             |

| 39       | TXENABLE | 送信イネーブル                |

| 40       | P2D <11> | ポート2、データ入力D11<br>(MSB) |

| 41       | P2D <10> | ポート2、データ入力D10          |

| 42       | P2D <9>  | ポート2、データ入力D9           |

| 43       | DVDD18   | 1.8Vデジタル電源             |

| 44       | DGND     | デジタル・コモン               |

| 45       | P2D <8>  | ポート2、データ入力D8           |

| 46       | P2D <7>  | ポート2、データ入力D7           |

| 47       | P2D <6>  | ポート2、データ入力D6           |

| 48       | P2D <5>  | ポート2、データ入力D5           |

| 49       | P2D <4>  | ポート2、データ入力D4           |

| 50       | P2D <3>  | ポート2、データ入力D3           |

| 51       | P2D <2>  | ポート2、データ入力D2           |

| 52       | P2D <1>  | ポート2、データ入力D1           |

| 53       | DVDD18   | 1.8Vデジタル電源             |

| 54       | DGND     | デジタル・コモン               |

| 55       | P2D <0>  | ポート2、データ入力D0           |

| 56       | NC       | 接続なし                   |

| 57       | NC       | 接続なし                   |

| 58       | NC       | 接続なし                   |

| 59       | NC       | 接続なし                   |

| 60       | DVDD18   | 1.8Vデジタル電源             |

| 61       | DVDD33   | 3.3Vデジタル電源             |

| 62       | SYNC_O-  | 差動同期出力                 |

| 63       | SYNC_O+  | 差動同期出力                 |

| 64       | DGND     | デジタル・コモン               |

| 65       | PLL_LOCK | PLLロック・インジケータ          |

| 66       | SDO      | SPIポート・データ出力           |

| 67       | SDIO     | SPIポート・データ入出力          |

| 68       | SCLK     | SPIポート・クロック            |

| 69       | CSB      | SPIポート・チップ・セレクト・<br>バー |

| 70       | RESET    | リセット、アクティブ・ハイ          |

| 71       | IRQ      | 割込み要求                  |

| 72       | AGND     | アナログ・コモン               |

| 73       | IPTAT    | リファレンス電流               |

| <br>ピン番号 | 記号     | 記号               |

|----------|--------|------------------|

| 74       | VREF   | 電圧リファレンス出力       |

| 75       | I120   | 120µAリファレンス電流    |

| 76       | AVDD33 | 3.3Vアナログ電源       |

| 77       | AGND   | アナログ・コモン         |

| 78       | AVDD33 | 3.3Vアナログ電源       |

| 79       | AGND   | アナログ・コモン         |

| 80       | AVDD33 | 3.3Vアナログ電源       |

| 81       | AGND   | アナログ・コモン         |

| 82       | AGND   | アナログ・コモン         |

| 83       | OUT2_P | 差動DAC電流出力、チャンネル2 |

| 84       | OUT2_N | 差動DAC電流出力、チャンネル2 |

| 85       | AGND   | アナログ・コモン         |

| 86       | AUX2_P | 補助DAC電圧出力、チャンネル2 |

| 87       | AUX2_N | 補助DAC電圧出力、チャンネル2 |

| 88       | AGND   | アナログ・コモン         |

| 89       | AUX1_N | 補助DAC電圧出力、チャンネル1 |

| 90       | AUX1_P | 補助DAC電圧出力、チャンネル1 |

| 91       | AGND   | アナログ・コモン         |

| 92       | OUT1_N | 差動DAC電流出力、チャンネル1 |

| 93       | OUT1_P | 差動DAC電流出力、チャンネル1 |

| 94       | AGND   | アナログ・コモン         |

| 95       | AGND   | アナログ・コモン         |

| 96       | AVDD33 | 3.3Vアナログ電源       |

| 97       | AGND   | アナログ・コモン         |

| 98       | AVDD33 | 3.3Vアナログ電源       |

| 99       | AGND   | アナログ・コモン         |

| 100      | AVDD33 | 3.3Vアナログ電源       |

<sup>-</sup> CLK+ピンとCLKーピンにおける結合差動クロック入力は、DACCLKと呼ばれます。

REV. 0 — 9 —

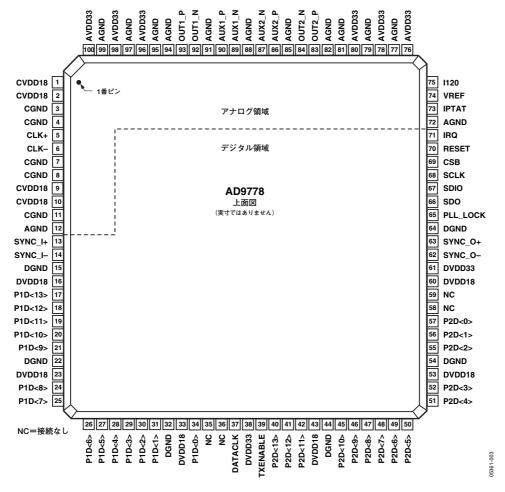

図3. AD9778のピン配置

表6. AD9778のピン機能の説明

| ピン番号 | 記号       | 記号                  | ピン番号 | 記号       | 記号                    |

|------|----------|---------------------|------|----------|-----------------------|

| 1    | CVDD18   | 1.8Vクロック電源          | 21   | P1D <9>  | ポート1、データ入力 <b>D</b> 9 |

| 2    | CVDD18   | 1.8Vクロック電源          | 22   | DGND     | デジタル・コモン              |

| 3    | CGND     | クロック・コモン            | 23   | DVDD18   | 1.8Vデジタル電源            |

| 4    | CGND     | クロック・コモン            | 24   | P1D <8>  | ポート1、データ入力 <b>D</b> 8 |

| 5    | CLK+1    | 差動クロック入力            | 25   | P1D <7>  | ポート1、データ入力D7          |

| 6    | CLK-1    | 差動クロック入力            | 26   | P1D <6>  | ポート1、データ入力 <b>D</b> 6 |

| 7    | CGND     | クロック・コモン            | 27   | P1D <5>  | ポート1、データ入力 <b>D</b> 5 |

| 8    | CGND     | クロック・コモン            | 28   | P1D <4>  | ポート1、データ入力D4          |

| 9    | CVDD18   | 1.8Vクロック電源          | 29   | P1D <3>  | ポート1、データ入力D3          |

| 10   | CVDD18   | 1.8Vクロック電源          | 30   | P1D <2>  | ポート1、データ入力 <b>D</b> 2 |

| 11   | CGND     | クロック・コモン            | 31   | P1D <1>  | ポート1、データ入力D1          |

| 12   | AGND     | アナログ・コモン            | 32   | DGND     | デジタル・コモン              |

| 13   | SYNC_I+  | 差動同期入力              | 33   | DVDD18   | 1.8Vデジタル電源            |

| 14   | SYNC_I-  | 差動同期入力              | 34   | P1D <0>  | ポート1、データ入力 <b>D</b> 0 |

| 15   | DGND     | デジタル・コモン            | 35   | NC       | 接続なし                  |

| 16   | DVDD18   | 1.8Vデジタル電源          | 36   | NC       | 接続なし                  |

| 17   | P1D <13> | ポート1、データ入力D13 (MSB) | 37   | DATACLK  | データ・クロック出力            |

| 18   | P1D <12> | ポート1、データ入力D12       | 38   | DVDD33   | 3.3Vデジタル電源            |

| 19   | P1D <11> | ポート1、データ入力D11       | 39   | TXENABLE | 送信イネーブル               |

| 20   | P1D <10> | ポート1、データ入力D10       | 40   | P2D <13> | ポート2、データ入力D13 (MSB)   |

| <br>ピン番号 | 記号       | 記号                     |

|----------|----------|------------------------|

| 41       | P2D <12> | ポート2、データ入力D12          |

| 42       | P2D <11> | ポート2、データ入力D11          |

| 43       | DVDD18   | <br>  1.8Vデジタル電源       |

| 44       | DGND     | デジタル・コモン               |

| 45       | P2D <10> | ポート2、データ入力D10          |

| 46       | P2D <9>  | ポート2、データ入力 <b>D</b> 9  |

| 47       | P2D <8>  | ポート2、データ入力D8           |

| 48       | P2D <7>  | ポート2、データ入力D7           |

| 49       | P2D <6>  | ポート2、データ入力D6           |

| 50       | P2D <5>  | ポート2、データ入力D5           |

| 51       | P2D <4>  | ポート2、データ入力D4           |

| 52       | P2D <3>  | ポート2、データ入力D3           |

| 53       | DVDD18   | 1.8Vデジタル電源             |

| 54       | DGND     | デジタル・コモン               |

| 55       | P2D <2>  | ポート2、データ入力D2           |

| 56       | P2D <1>  | ポート2、データ入力D1           |

| 57       | P2D <0>  | ポート2、データ入力D0           |

| 58       | NC       | 接続なし                   |

| 59       | NC       | 接続なし                   |

| 60       | DVDD18   | 1.8Vデジタル電源             |

| 61       | DVDD33   | 3.3Vデジタル電源             |

| 62       | SYNC_O-  | 差動同期出力                 |

| 63       | SYNC_O+  | 差動同期出力                 |

| 64       | DGND     | デジタル・コモン               |

| 65       | PLL_LOCK | PLLロック・インジケータ          |

| 66       | SDO      | SPIポート・データ出力           |

| 67       | SDIO     | SPIポート・データ入出力          |

| 68       | SCLK     | SPIポート・クロック            |

| 69       | CSB      | SPIポート・チップ・セレクト・<br>バー |

| 70       | RESET    | リセット、アクティブ・ハイ          |

| 71       | IRQ      | 割込み要求                  |

| 72       | AGND     | アナログ・コモン               |

| 73       | IPTAT    | リファレンス電流               |

| 74       | VREF     | 電圧リファレンス出力             |

| 75       | I120     | 120μAリファレンス電流          |

|             | T      | T                |

|-------------|--------|------------------|

| ピン番号<br>——— | 記号     | 記号               |

| 76          | AVDD33 | 3.3Vアナログ電源       |

| 77          | AGND   | アナログ・コモン         |

| 78          | AVDD33 | 3.3Vアナログ電源       |

| 79          | AGND   | アナログ・コモン         |

| 80          | AVDD33 | 3.3Vアナログ電源       |

| 81          | AGND   | アナログ・コモン         |

| 82          | AGND   | アナログ・コモン         |

| 83          | OUT2_P | 差動DAC電流出力、チャンネル2 |

| 84          | OUT2_N | 差動DAC電流出力、チャンネル2 |

| 85          | AGND   | アナログ・コモン         |

| 86          | AUX2_P | 補助DAC電圧出力、チャンネル2 |

| 87          | AUX2_N | 補助DAC電圧出力、チャンネル2 |

| 88          | AGND   | アナログ・コモン         |

| 89          | AUX1_N | 補助DAC電圧出力、チャンネル1 |

| 90          | AUX1_P | 補助DAC電圧出力、チャンネル1 |

| 91          | AGND   | アナログ・コモン         |

| 92          | OUT1_N | 差動DAC電流出力、チャンネル1 |

| 93          | OUT1_P | 差動DAC電流出力、チャンネル1 |

| 94          | AGND   | アナログ・コモン         |

| 95          | AGND   | アナログ・コモン         |

| 96          | AVDD33 | 3.3Vアナログ電源       |

| 97          | AGND   | アナログ・コモン         |

| 98          | AVDD33 | 3.3Vアナログ電源       |

| 99          | AGND   | アナログ・コモン         |

| 100         | AVDD33 | 3.3Vアナログ電源       |

<sup>「</sup>CLK+ピンとCLK-ピンにおける結合差動クロック入力は、DACCLKと呼ばれます。

REV. 0 — 11 —

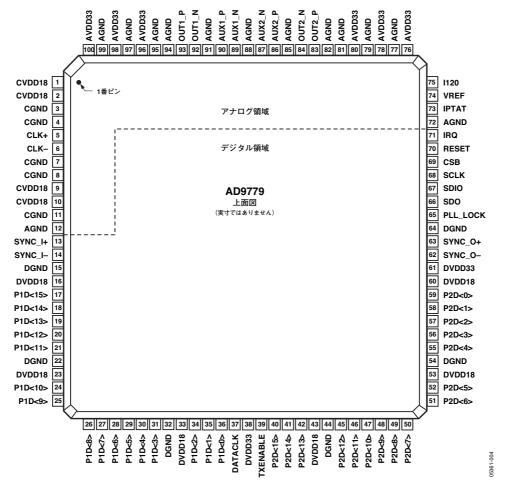

図4. AD9779のピン配置

表7. AD9779のピン機能の説明

| ピン番号 | 記号       | 記号                  | ピン番号 | 記号       | 記号                    |

|------|----------|---------------------|------|----------|-----------------------|

| 1    | CVDD18   | 1.8Vクロック電源          | 20   | P1D <12> | ポート1、データ入力D12         |

| 2    | CVDD18   | 1.8Vクロック電源          | 21   | P1D <11> | ポート1、データ入力D11         |

| 3    | CGND     | クロック・コモン            | 22   | DGND     | デジタル・コモン              |

| 4    | CGND     | クロック・コモン            | 23   | DVDD18   | 1.8Vデジタル電源            |

| 5    | CLK+1    | 差動クロック入力            | 24   | P1D <10> | ポート1、データ入力D10         |

| 6    | CLK-1    | 差動クロック入力            | 25   | P1D <9>  | ポート1、データ入力 <b>D</b> 9 |

| 7    | CGND     | クロック・コモン            | 26   | P1D <8>  | ポート1、データ入力 <b>D</b> 8 |

| 8    | CGND     | クロック・コモン            | 27   | P1D <7>  | ポート1、データ入力 <b>D7</b>  |

| 9    | CVDD18   | 1.8Vクロック電源          | 28   | P1D <6>  | ポート1、データ入力 <b>D</b> 6 |

| 10   | CVDD18   | 1.8Vクロック電源          | 29   | P1D <5>  | ポート1、データ入力 <b>D</b> 5 |

| 11   | CGND     | クロック・コモン            | 30   | P1D <4>  | ポート1、データ入力D4          |

| 12   | AGND     | アナログ・コモン            | 31   | P1D <3>  | ポート1、データ入力D3          |

| 13   | SYNC_I+  | 差動同期入力              | 32   | DGND     | デジタル・コモン              |

| 14   | SYNC_I-  | 差動同期入力              | 33   | DVDD18   | 1.8Vデジタル電源            |

| 15   | DGND     | デジタル・コモン            | 34   | P1D <2>  | ポート1、データ入力D2          |

| 16   | DVDD18   | 1.8Vデジタル電源          | 35   | P1D <1>  | ポート1、データ入力D1          |

| 17   | P1D <15> | ポート1、データ入力D15 (MSB) | 36   | P1D <0>  | ポート1、データ入力D0 (LSB)    |

| 18   | P1D <14> | ポート1、データ入力D14       | 37   | DATACLK  | データ・クロック出力            |

| 19   | P1D <13> | ポート1、データ入力D13       | 38   | DVDD33   | 3.3Vデジタル電源            |

| <br>ピン番号 | 記号       | 記号                     |

|----------|----------|------------------------|

| 39       | TXENABLE | 送信イネーブル                |

| 40       | P2D <15> | ポート2、データ入力D15 (MSB)    |

| 41       | P2D <14> | ポート2、データ入力D14          |

| 42       | P2D <13> | ポート2、データ入力D13          |

| 43       | DVDD18   | 1.8Vデジタル電源             |

| 44       | DGND     | デジタル・コモン               |

| 45       | P2D <12> | ポート2、データ入力D12          |

| 46       | P2D <11> | ポート2、データ入力D11          |

| 47       | P2D <10> | ポート2、データ入力D10          |

| 48       | P2D <9>  | ポート2、データ入力D9           |

| 49       | P2D <8>  | ポート2、データ入力D8           |

| 50       | P2D <7>  | ポート2、データ入力D7           |

| 51       | P2D <6>  | ポート2、データ入力D6           |

| 52       | P2D <5>  | ポート2、データ入力D5           |

| 53       | DVDD18   | 1.8Vデジタル電源             |

| 54       | DGND     | デジタル・コモン               |

| 55       | P2D <4>  | ポート2、データ入力D4           |

| 56       | P2D <3>  | ポート2、データ入力D3           |

| 57       | P2D <2>  | ポート2、データ入力D2           |

| 58       | P2D <1>  | ポート2、データ入力D1           |

| 59       | P2D <0>  | ポート2、データ入力D0 (LSB)     |

| 60       | DVDD18   | 1.8Vデジタル電源             |

| 61       | DVDD33   | 3.3Vデジタル電源             |

| 62       | SYNC_O-  | 差動同期出力                 |

| 63       | SYNC_O+  | 差動同期出力                 |

| 64       | DGND     | デジタル・コモン               |

| 65       | PLL_LOCK | PLLロック・インジケータ          |

| 66       | SPI_SDO  | SPIポート・データ出力           |

| 67       | SPI_SDIO | SPIポート・データ入出力          |

| 68       | SCLK     | SPIポート・クロック            |

| 69       | SPI_CSB  | SPIポート・チップ・セレクト・<br>バー |

| 70       | RESET    | リセット、アクティブ・ハイ          |

| 71       | IRQ      | 割込み要求                  |

| 72       | AGND     | アナログ・コモン               |

| 73       | IPTAT    | リファレンス電流               |

| 74       | VREF     | 電圧リファレンス出力             |

| <br>ピン番号 | 記号     | 記号               |

|----------|--------|------------------|

| 75       | I120   |                  |

| 76       | AVDD33 | 120μAリファレンス電流    |

| , -      |        | 3.3Vアナログ電源       |

| 77       | AGND   | アナログ・コモン         |

| 78       | AVDD33 | 3.3Vアナログ電源       |

| 79       | AGND   | アナログ・コモン         |

| 80       | AVDD33 | 3.3Vアナログ電源       |

| 81       | AGND   | アナログ・コモン         |

| 82       | AGND   | アナログ・コモン         |

| 83       | OUT2_P | 差動DAC電流出力、チャンネル2 |

| 84       | OUT2_N | 差動DAC電流出力、チャンネル2 |

| 85       | AGND   | アナログ・コモン         |

| 86       | AUX2_P | 補助DAC電圧出力、チャンネル2 |

| 87       | AUX2_N | 補助DAC電圧出力、チャンネル2 |

| 88       | AGND   | アナログ・コモン         |

| 89       | AUX1_N | 補助DAC電圧出力、チャンネル1 |

| 90       | AUX1_P | 補助DAC電圧出力、チャンネル1 |

| 91       | AGND   | アナログ・コモン         |

| 92       | OUT1_N | 差動DAC電流出力、チャンネル1 |

| 93       | OUT1_P | 差動DAC電流出力、チャンネル1 |

| 94       | AGND   | アナログ・コモン         |

| 95       | AGND   | アナログ・コモン         |

| 96       | AVDD33 | 3.3Vアナログ電源       |

| 97       | AGND   | アナログ・コモン         |

| 98       | AVDD33 | 3.3Vアナログ電源       |

| 99       | AGND   | アナログ・コモン         |

| 100      | AVDD33 | 3.3Vアナログ電源       |

<sup>-</sup> CLK+ピンとCLK-ピンにおける結合差動クロック入力は、DACCLKと呼ばれます。

REV. 0 — 13 —

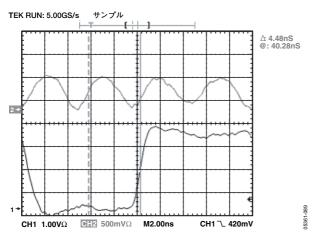

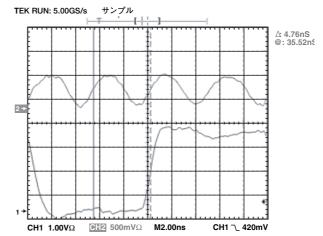

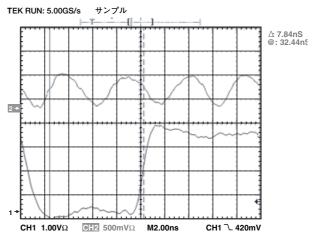

# 代表的な性能特性

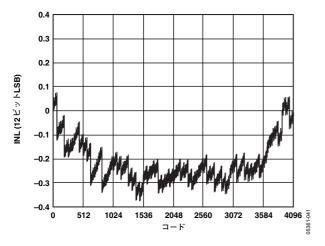

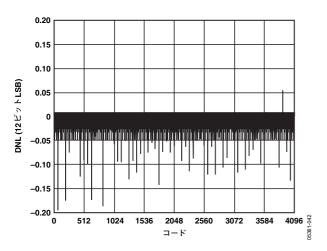

図6.代表的なDNL (AD9779)

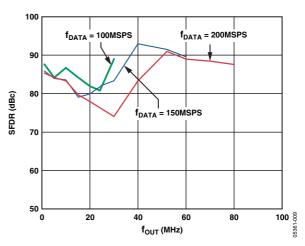

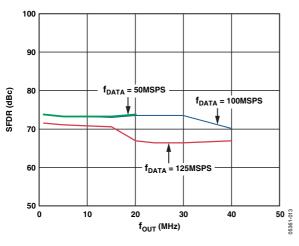

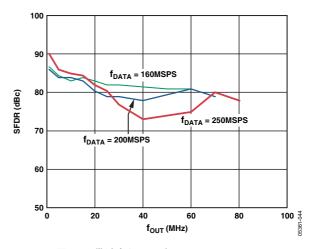

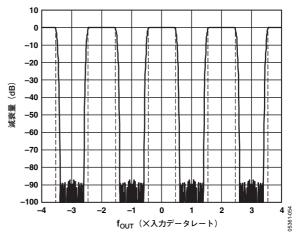

図7. f<sub>out</sub> 対 帯域内SFDR (AD9779、1×インターポレーション)

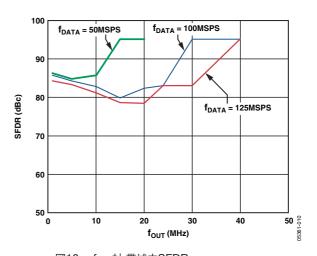

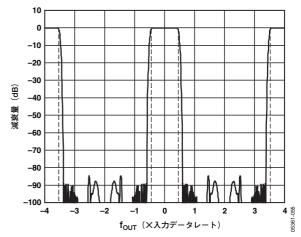

図8. f<sub>out</sub> 対 帯域内SFDR (AD9779、2×インターポレーション)

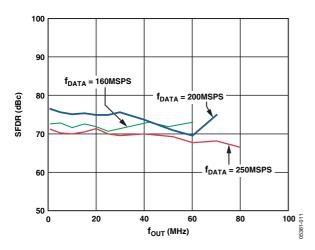

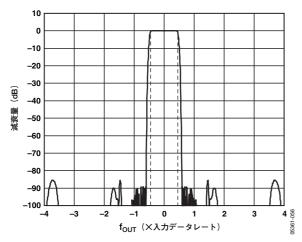

図9. f<sub>out</sub> 対 帯域内SFDR (AD9779、4×インターポレーション)

-14-REV. 0

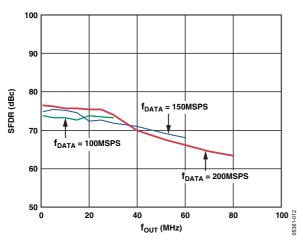

図11. f<sub>out</sub> 対 帯域外SFDR (AD9779、2×インターポレーション)

図12. f<sub>out</sub> 対 帯域外SFDR (AD9779、4×インターポレーション)

図13. f<sub>out</sub> 対 帯域外SFDR (AD9779、8×インターポレーション)

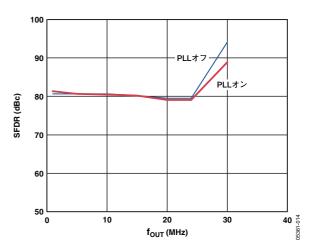

図14. 帯域内SFDR (AD9779、4×インターポレーション、 f<sub>DATA</sub>=100MSPS、PLLオン/オフ)

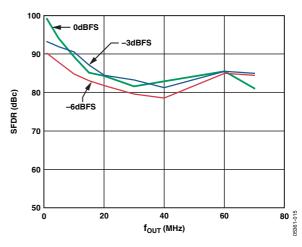

図15. デジタル・フルスケール入力 対 帯域内 SFDR (AD9779)

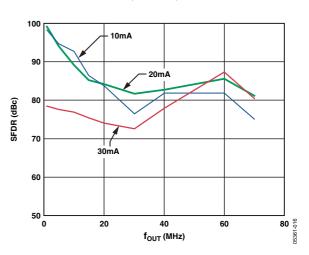

図16. 出力フルスケール電流 対 帯域内SFDR (AD9779)

REV. 0 — 15 —

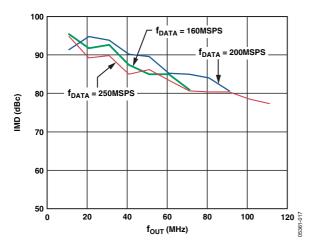

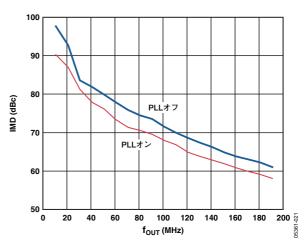

図17. f<sub>out</sub> 対 3次IMD (AD9779、1×インターポレーション)

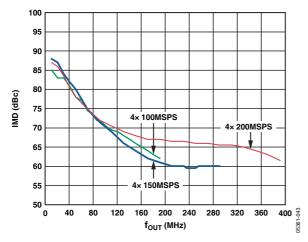

図18. f<sub>out</sub> 対 3次IMD (AD9779、2×インターポレーション)

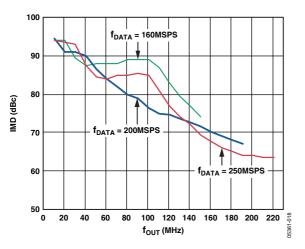

図19. f<sub>out</sub> 対 3次IMD (AD9779、4×インターポレーション)

図20. f<sub>out</sub> 対 3次IMD (AD9779、8×インターポレーション)

図21. f<sub>OUT</sub> 対 3次IMD (AD9779、4×インターポレーション、 f<sub>DATA</sub>=100MSPS、PLLオン 対 PLLオフ)

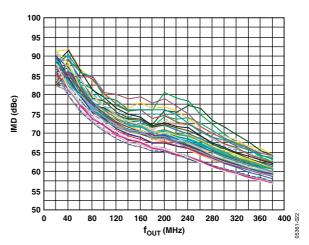

図22. f<sub>OUT</sub> 対 3次IMD (AD9779、50超のデバイス、4×イン ターポレーション、f<sub>DATA</sub>=200MSPS)

— 16 — REV. 0

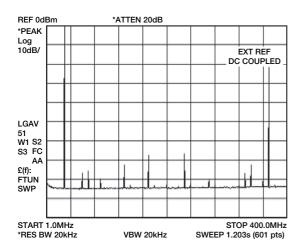

図23. シングル・トーン(AD9779、4× インターポレーション、 $f_{\text{DATA}}$ =100MSPS、 $f_{\text{OUT}}$ =30MHz)

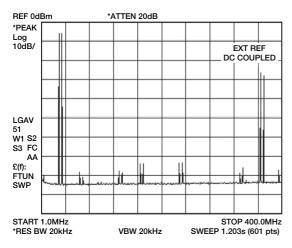

図24. ツートーン・スペクトル(AD9779、4× インターポレーション、 $f_{DATA}$ =100MSPS、 $f_{OUT}$ =30、35MHz)

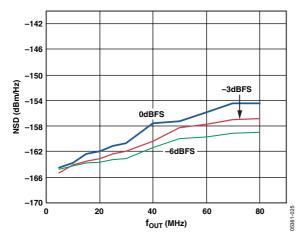

図25. シングル・トーン入力のデジタル・ フルスケール 対 ノイズ・スペクトル密度 (AD9779、 $f_{DATA}$ =200MSPS、  $2\times$ インターポレーション)

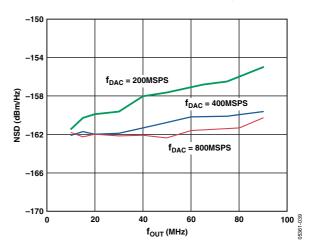

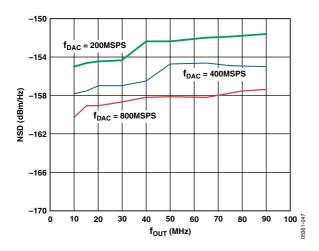

図26. f<sub>DAC</sub> 対 ノイズ・スペクトル密度 (AD9779、500kHz間隔による 8トーン入力、f<sub>DATA</sub>=200MSPS)

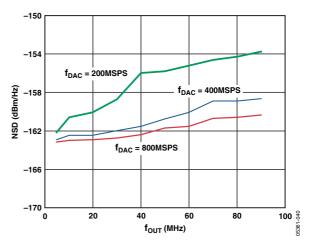

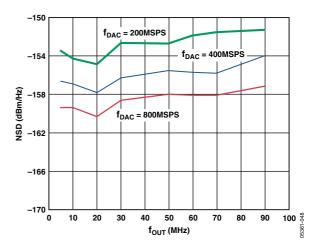

図27. f<sub>DAC</sub> 対 ノイズ・スペクトル密度 (AD9779、-6dBFSでのシングル・ トーン入力)

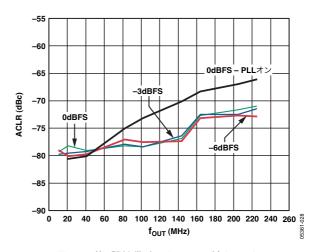

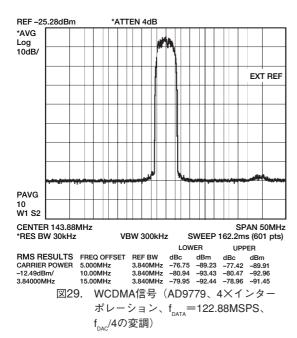

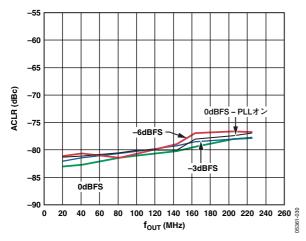

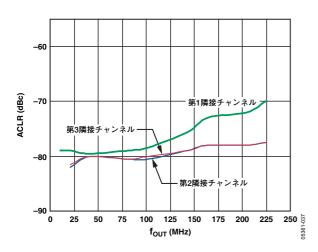

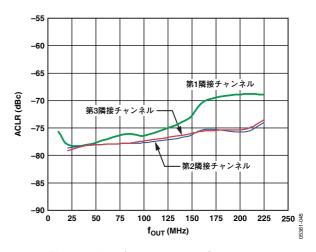

図28. 第1隣接帯域WCDMAに対するACLR (AD9779、4×インターポレーション、 f<sub>DATA</sub>=122.88MSPS、内部変調で ベースバンド信号をIFに変換)

REV. 0 — 17 —

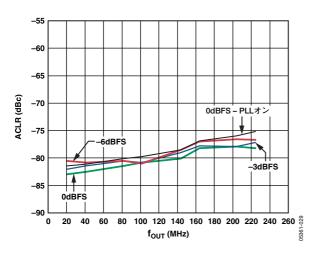

図30. 第3隣接帯域WCDMAに対するACLR (AD9779、4×インターポレーション、 f<sub>DATA</sub>=122.88MSPS、内部変調でベース バンド信号をIFに変換)

図31. 第2隣接帯域WCDMAに対するACLR (AD9779、4×インターポレーション、 f<sub>DATA</sub>=122.88MSPS、内部変調でベース バンド信号をIFに変換)

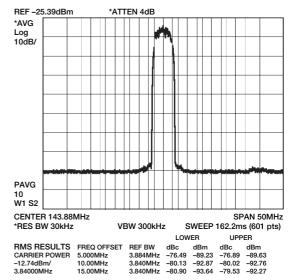

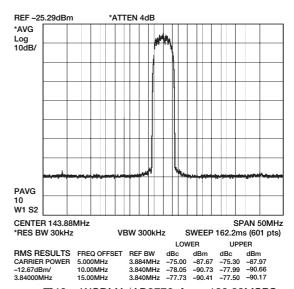

FREQ OFFSET INTEG BW dBc dBm dBc dBm 1-17.87dBm 5.000MHz 3.840MHz -67.70 -85.57 -67.70 -85.57 2-20.65dBm 10.00MHz 3.840MHz -70.00 -97.87 -69.32 -87.19 3-18.26dBm 15.00MHz 3.840MHz 71.65 -99.52 -71.00 -88.88 4-18.23dBm

図33. 代表的なINL (AD9778)

図34. 代表的なDNL (AD9778)

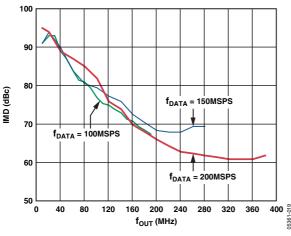

図35. IMD (AD9778、4×インターポレーション)

図36. 帯域内SFDR (AD9778、2×インター ポレーション)

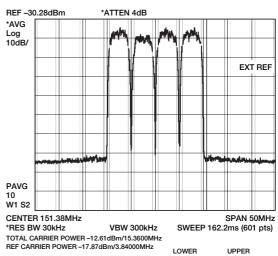

図38. WCDMA (AD9778、 $f_{DATA}$ =122.88MSPS、4×インターポレーション、 $f_{DAC}/4$ の変調)

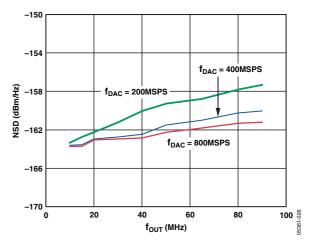

図39. f<sub>DAC</sub> 対 ノイズ・スペクトル密度 (AD9778、500kHz間隔による8トーン 入力、f<sub>DATA</sub>=200MSPS)

図40.  $f_{DAC}$  対 ノイズ・スペクトル密度 (AD9778、-6dBFSでのシングル・トーン入力、 $f_{DATA}$ =200MSPS)

図41. 代表的なINL (AD9776)

図42. 代表的なDNL (AD9776)

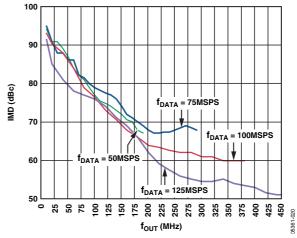

図43. IMD (AD9776、4×インターポレーション)

図44. 帯域内SFDR (AD9776、2×インター ポレーション)

図45. ACLR (AD9776、シングル・キャリア WCDMA、 $4\times$ 1ンターポレーション、 $f_{DATA}$ =122.88MSPS、振幅=-3dBFS)

図46. WCDMA (AD9776、 $f_{DATA}$ =122.88MSPS、 4 imes 4 imes 9ン、 $f_{DAC}/4$ の変調)

05361-04

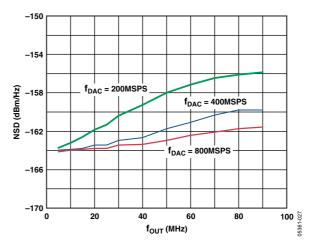

図47. f<sub>DAC</sub> 対 ノイズ・スペクトル密度 (AD9776、500kHz間隔による8トーン 入力、f<sub>DATA</sub>=200MSPS)

図48.  $f_{DAC}$  対 ノイズ・スペクトル密度 (AD9776、-6dBFSでのシングル・トーン入力、 $f_{DATA}$ =200MSPS)

REV. 0 — 21 —

## 用語の説明

#### 直線性誤差(積分非直線性またはINL)

実際のアナログ出力と、ゼロスケールとフルスケールを結ぶ直 線で示される理想的な出力との最大偏差です。

#### 微分非直線性 (DNL)

デジタル入力コードの1LSBの変化に伴って発生するアナログ値(フルスケールに対して正規化)の変動を測定したものです。

#### 単調増加性

デジタル入力が増加したとき、出力が増加するか一定の値に維持される場合に、D/Aコンバータは単調増加性を備えていることになります。

#### オフセット誤差

理想値ゼロからの出力電流の偏差をオフセット誤差と呼びます。 $I_{\text{outh}}$ の場合、入力がオール0のときに0mAの出力が予想されます。 $I_{\text{outh}}$ の場合は、入力がオール1に設定されるときに0mAの出力が予想されます。

#### ゲイン誤差

出力スパンの実際の値と理想値との差です。実際のスパンは、入力をオール1に設定したときの出力と、入力をオール0に設定したときの出力の差によって求められます。

#### 出力コンプライアンス電圧範囲

電流出力DACの出力において許容可能な電圧範囲です。最大コンプライアンス制限値を超えた動作は、出力段の飽和またはブレークダウンを引き起こし、直線性性能が劣化します。

### 温度ドリフト

周囲温度(25°C)時の値から $T_{MIN}$ または $T_{MAX}$ 時の値までの最大変化量として規定されます。オフセットおよびゲイン・ドリフトは、フルスケール範囲(FSR)のppm/°Cの単位で表します。リファレンスのドリフトはppm/°Cの単位で表します。

#### 電源電圧変動除去比

電源が最小から最大の規定電圧に変化するときのフルスケール 出力の最大変動です。

#### セトリング時間

出力がその最終値について規定された誤差帯域に到達し、その 帯域範囲内に収まるまでの所要時間のことであり、出力遷移の 開始時点から測定します。

### 帯域内スプリアス・フリー・ダイナミック・レンジ (SEDR)

入力データレートの半分の周波数とDCとの間のピーク・スプリアス信号と、出力信号のピーク振幅との差であり、dBの単位で表します。

# 帯域外スプリアス・フリー・ダイナミック・レンジ (SFDR)

入力データレートの周波数で始まりDAC出力サンプル・レートのナイキスト周波数で終わる帯域内のピーク・スプリアス信号と、出力信号のピーク振幅との差であり、dBの単位で表します。通常、この帯域内のエネルギーは、インターポレーション・フィルタによって除去されます。したがってこの仕様は、インターポレーション・フィルタの効果と、他の寄生カップリング・パスがDAC出力に与える影響を規定します。

#### 全高調波歪み(THD)

最初の6つの高調波成分のrms値の総和と、測定された基本波のrms値との比で、%またはdBの単位で表します。

#### S/N比 (SNR)

測定された出力信号のrms値と、ナイキスト周波数より下の全スペクトル成分のrms値総和から最初の6つの高調波成分とDC成分を除いた値との比です。S/N比はdBの単位で表します。

#### インターポレーション・フィルタ

$\mathrm{DAC}$ へのデジタル入力が $\mathbf{f}_{\mathrm{DATA}}$ (インターポレーション・レート)の複数レートでサンプリングされる場合、 $\mathbf{f}_{\mathrm{DATA}}/2$ の近くに急峻な遷移帯域を持つデジタル・フィルタを構築できます。一般的に $\mathbf{f}_{\mathrm{DAC}}$ (出力データ・レート)の周囲に現われるイメージを大幅に抑制できます。

#### 隣接チャンネル漏れ率(ACLR)

隣接チャンネルを基準にして、チャンネル内で測定したパワーの比(単位はdBc)。

### 複素のイメージ除去

従来の2部アップコンバージョンでは、第2IF周波数の周りに2 つのイメージが作成されます。これらのイメージには、送信パワーとシステム帯域幅を浪費する作用があります。第1複素変調器と直列に第2複素変調器の実数部を配置することによって、第2IFの近くの高/低周波数イメージを除去できます。

## 動作原理

AD9776/AD9778/AD9779は、多くの機能を兼ね備えており、有線/無線通信システムにとって非常に魅力的なDACとなっています。シングル・サイドバンド・トランスミッタの設計に際しては、デュアル・デジタル信号経路とデュアルDAC構造により、一般的な直交変調器とのインターフェースが容易になります。これらのデバイスの速度と性能により、これまでのDACに比べて広い帯域幅と多くのキャリアを合成できます。デジタル・エンジンでは、インターポレーションとデジタル直交変調器を組み合わせた、画期的なフィルタ・アーキテクチャを採用しています。したがって、これらのデバイスでは、直交周波数のデジタル・アップコンバージョンが可能になります。また、着信データとの同期や複数のデバイス間の同期を簡単にする機能も備えています。

シリアル・ポートの設定は、レジスタ0x00のビット<6:7>によって制御されます。なお、この設定変更は、バイトの最終ビットへの書込みの直後に行われます。マルチバイト転送の場合、このレジスタへの書込みが通信サイクルの途中で発生することがあります。現在の通信サイクルの残りのバイトに対しては、この新しい設定の補償を行ってください。

ソフトウェア・リセットであるRESET (レジスタ0x00、ビット5) の設定や、RESETピン(70番ピン)をハイレベルにする際にも、同じ注意が必要です。すべてのレジスタはデフォルト値に設定されます(ただし、レジスタ0x00と0x04は変化しません)。

シリアル・ポート設定の変更やソフトウェア・リセットの開始 に際しては、予期しないデバイス動作を防止するために、シン グルバイト転送のみを使用するようにしてください。

ここで説明するように、デバイス間でのシリアル・ポート・データ転送は、すべてSCLKピンに同期して行われます。同期が失われた場合、デバイスはI/O動作を非同期に終了させて、シリアル・ポート・コントローラを既知の状態にすることで、同期を取り戻す機能を持っています。

### シリアル・ペリフェラル・インターフェース

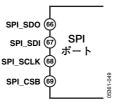

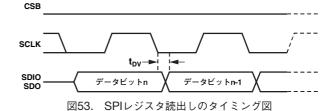

図49. SPIポート

シリアル・ポートは、フレキシブルで同期式のシリアル通信ポートであるため、業界標準の多くのマイクロコントローラやマイクロプロセッサとのインターフェースが容易です。シリアルI/Oは、Motorola SPI®プロトコルやIntel® SSRプロトコルなど、多くの同期転送フォーマットと互換性があります。このインターフェースを使用すると、AD9776/AD9778/AD9779を設定する全レジスタとの間で読出し/書込みが可能になります。MSBファーストやLSBファーストの転送フォーマットのみでなく、シングルバイト転送やマルチバイト転送にも対応しています。シリアル・インターフェース・ポートは、シングルのI/Oピン(SDIO)または入出力用の2本の単方向ピン(SDIO/SDO)として設定できます。

#### シリアル・インターフェースの一般的な動作

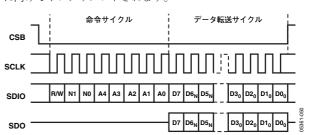

AD977xの通信サイクルには2つのフェーズがあります。フェーズ1は命令サイクルで、先頭の8個のSCLK立上がりエッジでデバイスに命令バイトを書き込みます。命令バイトは、シリアル・ポート・コントローラにデータ転送サイクルに関する情報を提供します。このデータ転送サイクルが、通信サイクルのフェーズ2になります。フェーズ1の命令バイトでは、次のデータ転送が読出しであるか書込みであるか、データ転送のバイト数、データ転送の最初のバイトの開始レジスタ・アドレスを規定します。各通信サイクルの先頭の8個のSCLK立上がりエッジを使って、デバイスに命令バイトを書き込みます。

CSBピンがロジック・ハイに続いてロジック・ローになると、SPIポートのタイミングは、命令サイクルの初期状態にリセットされます。この状態からは、内部レジスタの状態やSPIポートに入力される他の信号レベルとは無関係に、次の8個のSCLK立上がりエッジは、現在のI/O動作の命令ビットを表します。SPIポートが命令サイクルやデータ転送サイクルの途中にある場合は、現在のデータは書き込まれません。

残りのSCLKエッジは、通信サイクルのフェーズ2で使います。フェーズ2では、デバイスとシステム・コントローラの間で実際のデータ転送が行われます。通信サイクルのフェーズ2では、命令バイトによって決定されるデータバイト1、2、3または4の転送を行います。1回でのマルチバイト転送を推奨します。レジスタ・アクセスが1つのバイトのみを必要とするときは、CPUオーバーヘッドの削減のためにシングルバイトのデータ転送を使用します。レジスタの変更は、各転送バイトの最終ビットへの書込みの直後に行われます。

#### 命令バイト

命令バイトには、表8に示す情報が含まれます。

#### 表8. SPIの命令バイト

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| 17  | 16 | 15 | 14 | 13 | 12 | 11 | 10  |

| R/W | N1 | N0 | A4 | A3 | A2 | A1 | A0  |

R/W (命令バイトのビット7) では、命令バイトの書込みの後で行われるデータ転送が読出しであるか書込みであるかを決定します。ロジック・ハイは読出し動作を示します。ロジック0 は書込み動作を示します。

N1とN0 (命令バイトのビット6と5) では、データ転送サイクル中に転送されるバイト数を決定します。ビットの意味を表9に示します。

REV. 0 — 23 —

A4、A3、A2、A1、A0(それぞれ、命令バイトのビット4、3、2、1、0)は、通信サイクルのデータ転送部分でアクセスするレジスタを決定します。マルチバイト転送では、このアドレスは開始バイト・アドレスです。残りのレジスタ・アドレスは、LSBファースト・ビット(レジスタ0x00、ビット6)に基づいて、デバイスによって生成されます。

表9. バイト転送数

| N0 | N1 | 説明      |

|----|----|---------|

| 0  | 0  | 1バイトを転送 |

| 0  | 1  | 2バイトを転送 |

| 1  | 0  | 3バイトを転送 |

| 1  | 1  | 4バイトを転送 |

#### シリアル・インターフェース・ポートのピンの説明

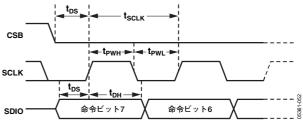

#### シリアル・クロック (SCLK)

シリアル・クロック・ピンは、デバイスとの間のデータ転送の 同期と、内部ステート・マシンの動作に使われます。SCLKの 最大周波数は40MHzです。すべてのデータ入力は、SCLKの立 上がりエッジでレジスタに格納されます。すべてのデータは、 SCLKの立下がりエッジで出力されます。

#### チップ・セレクト (CSB)

アクティブ・ローの入力によって、通信サイクルが開始および ゲーティングされます。これにより、同じシリアル通信ラインで複数のデバイスを使用できます。この入力がハイレベルになると、SDOピンとSDIOピンは高インピーダンス状態になります。チップ・セレクトは、通信サイクルの全体にわたってローレベルのままにしておきます。

#### シリアル・データI/O (SDIO)

このピン上のデータは、常にデバイスに書き込まれます。ただし、このピンは双方向データ・ラインとして使用できます。このピンの設定は、レジスタ0x00のビット7によって制御されます。デフォルトはロジック0で、SDIOピンは単方向として設定されます。

#### シリアル・データ出力 (SDO)

データの送信と受信に別のラインを使用するプロトコルでは、データはこのピンから読み込まれます。デバイスがシングル双方向I/Oモードで動作する場合、このピンはデータを出力せずに、高インピーダンス状態に設定されます。

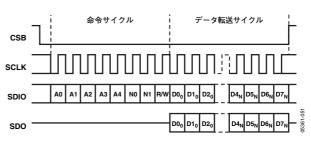

### MSB/LSB転送

シリアル・ポートは、MSBファーストとLSBファーストの両方のデータ・フォーマットに対応できます。この機能は、レジスタ・ビットLSBファースト(レジスタ0x00、ビット6)によって制御されます。デフォルトはMSBファースト(LSBファースト=0)です。

LSBファースト=0 (MSBファースト) のとき、命令とデータビットは、MSBからLSBに向けて書き込んでください。MSBファースト・フォーマットでのマルチバイト・データ転送は、最上位データバイトのレジスタ・アドレスを含む命令バイトから始まります。それ以降のデータバイトは、高位アドレスから低位アドレスの順に続けてください。MSBファースト・モードでは、シリアル・ポートの内部バイト・アドレス・ジェネレータは、マルチバイト通信サイクルのデータバイトごとにデクリメントします。

LSBファースト=1 (LSBファースト) のとき、命令とデータ ビットは、LSBからMSBに向けて書き込んでください。LSB ファースト・フォーマットでのマルチバイト・データ転送は、 最下位データバイトのレジスタ・アドレスを含む命令バイトで 始まり、その後に複数のデータバイトが続きます。シリアル・ ポートの内部バイト・アドレス・ジェネレータは、マルチバイト通信サイクルのバイトごとにインクリメントします。

MSBファースト・モードがアクティブの場合、マルチバイト I/O動作では、シリアル・ポート・コントローラのデータ・アドレスは、書き込まれたデータ・アドレスから0x00に向けてデクリメントされます。LSBファースト・モードがアクティブの場合、マルチバイトI/O動作では、シリアル・ポート・コントローラのアドレスは、書き込まれたデータ・アドレスから0x1Fに向けてインクリメントされます。

図50. シリアル・レジスタ・インターフェースのタイミング (MSBファースト)

図51. シリアル・レジスタ・インターフェースのタイミング (LSBファースト)

図52. SPIレジスタ書込みのタイミング図

— 24 — REV. 0

# SPIレジスタのマップ

### 表10

| レジスタ名           | アドロ  | ノス        | ビット7                                    | ビット6                               | ビット5                | ビット4                        | ビット3                   | ビット2                 | ビット1                         | ビット0               | デフォル     |

|-----------------|------|-----------|-----------------------------------------|------------------------------------|---------------------|-----------------------------|------------------------|----------------------|------------------------------|--------------------|----------|

| 通信              | 0x00 | 00a       | SDIO双方向                                 | LSB/MSB<br>ファースト                   | ソフト<br>ウェア・<br>リセット | パワー<br>ダウン・<br>モード          | 自動パワー<br>ダウン・<br>イネーブル |                      | PLLロック・<br>インジケータ<br>(読出し専用) |                    | 0x00     |

| デジタル<br>制御      | 0x01 | 01        | フィルタ補                                   | 間係数<1:0>                           |                     | フィルタ変調                      | <b>モード&lt;3:0&gt;</b>  |                      |                              | ゼロ充填<br>イネーブル      | 0x00     |

|                 | 0x02 | 02        | データ・<br>フォーマット                          | デュアル/<br>インターリーブ<br>データ・バス・<br>モード | リアル・<br>・モード        | データ・<br>クロック<br>遅延<br>イネーブル | 反転sinc<br>イネーブル        | DATACLK<br>反転        | TxEnable<br>反転               | Q77-X              | 0x00     |

| 可期制御            | 0x03 | 03        | データ・クロッ<br><1:0>                        | ク遅延モード                             | データ・クロ<br><1:0>     | ック分周比                       |                        | 予                    | 備                            |                    | 0x00     |

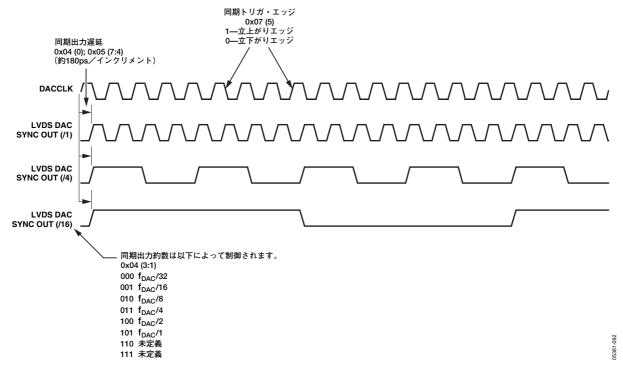

|                 | 0x04 | 04        |                                         | データ・クロ                             | ック遅延<3:0>           |                             | 出力                     | 同期パルス分周              | <2:0>                        | 同期出力遅延<br><4>      | 0x00     |

|                 | 0x05 | 05        |                                         | 同期出力                               | 遅延<3:0>             |                             | 入力同                    | 期パルス周波数              | 比<2:0>                       | 同期入力遅延<br><4>      | 0x00     |

|                 | 0x06 | 06        |                                         | 同期入力                               | 遅延<3:0>             |                             | 入力同期                   | 別パルスのタイ              | ミング誤差許容                      | 值<3:0>             | 0x00     |

|                 | 0x07 | 07        | 同期レシーバ・<br>イネーブル                        | 同期ドライバ・<br>イネーブル                   | 同期トリガ・<br>エッジ       |                             | DACクロ                  | ック・オフセッ              | ット<4:0>                      |                    | 0x00     |

| PLL制御           | 0x08 | 08        |                                         |                                    | PLL带域選択             | <5:0>                       |                        |                      | PLL VCO AGCゲイン<br><1:0>      |                    | 0xCF     |

|                 | 0x09 | 09        | PLLイネーブル                                | PLL VCO                            | 分周比<1:0>            | PLLルーフ                      | 分周比<1:0>               | F                    | LLバイアス設                      | 定<2:0>             | 0x37     |

| その他の制御          | 0x0A | 10        | PLL制御電圧範囲<2:0> (読出し専用) PLLループ帯域幅調整<4:0> |                                    |                     | 0x38                        |                        |                      |                              |                    |          |

| DAC             | 0x0B | 11        | IDACゲイン調整<7:0>                          |                                    |                     | 0xF9                        |                        |                      |                              |                    |          |

| コントロール・<br>レジスタ | 0x0C | 12        | I DAC<br>スリープ                           | I DACパワー<br>ダウン                    |                     |                             |                        |                      | IDACゲイ                       | ン調整<9:8>           | 0x01     |

| 辅助DAC1          | 0x0D | 13        |                                         | T                                  |                     | 補助DAC1                      | データ<7:0>               | T                    | T                            |                    | 0x00     |

| コントロール・<br>レジスタ | 0x0E | 14        | 補助DAC1<br>符号                            | 補助DAC1<br>電流方向                     | 補助DAC1<br>パワーダウン    |                             |                        |                      | 補助DAC1 <sup>-</sup>          | データ<9:8>           | 0x00     |

| Q DAC           | 0x0F | 15        |                                         |                                    |                     | Q DACゲイ                     | ン調整<7;0>               |                      |                              |                    | 0xF9     |

| コントロール・<br>ンジスタ | 0x10 | 16        | Q DAC<br>スリープ                           | Q DAC<br>パワーダウン                    |                     |                             |                        |                      | Q DACゲイ                      | ン調整<9:8>           | 0x01     |

| 前助DAC2          | 0x11 | 17        |                                         |                                    |                     | 補助DAC2                      | データ<7:0>               |                      |                              |                    | 0x00     |

| コントロール・<br>ンジスタ | 0x12 | 18        | 補助DAC2<br>符号                            | 補助DAC2<br>電流方向                     | 補助DAC2<br>パワーダウン    |                             |                        |                      | 補助DAC2 <sup>-</sup>          | データ<9:8>           | 0x00     |

|                 | 0x13 | 19~<br>24 |                                         |                                    |                     | Ţ                           | 備                      |                      |                              |                    |          |

|                 | 0x18 |           |                                         |                                    | T                   | I                           | T                      | I                    | I                            | l                  |          |

| 削込み<br>ノジスタ     | 0x19 | 25        |                                         | 同期遅延IRQ                            |                     |                             |                        | 同期遅延<br>IRQ<br>イネーブル |                              | 内部同期<br>ループ<br>バック | 0x00     |

|                 | 0x1A | 26~       |                                         |                                    | 1                   | <u>1</u>                    | <br>:-備                | 1                    | l                            |                    | <u> </u> |

|                 | ~    | 31        |                                         |                                    |                     | ·                           |                        |                      |                              |                    |          |

|                 | 0x1F |           |                                         |                                    |                     |                             |                        |                      |                              |                    |          |

REV. 0 — 25 —

表11. SPIレジスタの説明

|                          |       | <b>・レス</b> |                                        | LIK OF                                                                           |       |

|--------------------------|-------|------------|----------------------------------------|----------------------------------------------------------------------------------|-------|

| レジスタ名<br>                | 16進   | 10進        | 名前                                     | 機能                                                                               | デフォル  |

| 通信レジスタ                   | 00    | 7          | SDIO双方向                                | 0:SDIOピンを入力データとしてのみ使用<br>1:SDIOを入出力データとして使用                                      | 0     |

|                          | 00    | 6          | LSB/MSBファースト                           | 0:シリアル・データの先頭ビットはデータバイトの<br>MSB                                                  | 0     |

|                          |       |            |                                        | 1:シリアル・データの先頭ビットはデータバイトの<br>LSB                                                  |       |

|                          | 00    | 5          | ソフトウェア・リセット                            | SPIレジスタ・マップをソフト・リセットするには、ビットに1を書き込んでから0を書き込む                                     | 0     |

|                          | 00    | 4          | パワーダウン・モード                             | 0:すべての回路がアクティブ<br>1:すべてのデジタル/アナログ回路をディスエーブル、<br>SPIポートのみがアクティブ                   |       |

|                          | 00    | 3          | 自動パワーダウン・<br>イネーブル                     | 自動パワーダウン・モードの制御、「パワーダウン・<br>モードとスリープ・モード」を参照                                     | 0     |

|                          | 00    | 1          | PLLロック (読出し専用)                         | 0:PLLはロックされません<br>1:PLLはロックされます                                                  | 0     |

| デジタル・<br>コントロール・<br>レジスタ | 01    | 7:6        | フィルタ補間係数                               | 00:1×インターポレーション<br>01:2×インターポレーション<br>10:4×インターポレーション<br>11:8×インターポレーション         | 00    |

|                          | 01    | 5:2        | フィルタ変調モード                              | フィルタ・モードについては表19を参照                                                              | 0000  |

|                          | 01    | 0          | ゼロ充填                                   | 0:ゼロ充填オフ<br>1:ゼロ充填オン                                                             | 0     |

|                          | 02    | 7          | データ・フォーマット                             | 0: 符号付き2進数<br>1: 符号なし2進数                                                         | 0     |

|                          | 02    | 6          | デュアル/インターリーブ・<br>データ・バス・モード            | 0:両方の入力データ・ポートがデータを受信<br>1:データ・ポート1のみがデータを受信                                     | 0     |

|                          | 02    | 5          | リアル・モード                                | 0:Qパスで信号処理をイネーブルにする<br>1:Qパス・データをディスエーブル(内部Qチャンネル・クロックをディスエーブル、IおよびQ変調器をディスエーブル) | 0     |

|                          | 02    | 3          | 反転sincイネーブル                            | 0:反転sincフィルタをディスエーブル<br>1:反転sincフィルタをイネーブル                                       | 0     |

|                          | 02    | 2          | DATACLK反転                              | 0:出力DATACLKは内部キャプチャ・クロックと同じ<br>位相                                                | 0     |

|                          |       |            |                                        | 1:出力DATACLKは内部キャプチャ・クロックと逆の<br>位相                                                |       |

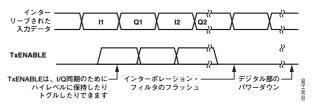

|                          | 02    | 1          | TxEnable反転                             | TxEnableピン(39番ピン)の機能を反転、「インターリーブ・データ・モード」を参照                                     | 0     |

|                          | 02    | 0          | Qファースト                                 | 0:送信開始時のデータの先頭バイトは常にIデータ<br>1:送信開始時のデータの先頭バイトは常にQデータ                             |       |

| 同期<br>コントロール・<br>レジスタ    | 03 03 | 7:6<br>5:4 | データ・クロック遅延モード<br>エクストラ・データ・<br>クロック分周比 | 00:手動、誤差補正なし<br>データ・クロック出力デバイダ (分周比については表22<br>を参照)                              | 00 00 |

|                          | 03    | 3:0        | 予備                                     |                                                                                  | 000   |

|                          | 04    | 7:4        | データ・クロック遅延                             | DACCLK入力からDATACLK出力までの遅延を設定                                                      | 0000  |

|                          | 04    | 3:1        | 出力同期パルス分周                              | SYNC_Oパルスの周波数を設定                                                                 | 000   |

|                          | 04    | 0          | 同期出力遅延                                 | 同期出力遅延、ビット4                                                                      |       |

|                          | 05    | 7:4        | 同期出力遅延                                 | 同期出力遅延、ビット<3:0>                                                                  | 0     |

|                          | 05    | 3:1        | 入力同期パルス周波数                             | 入力同期パルス周波数デバイダ、「同期パルス・レシー<br>バ (スレーブ・デバイス)」を参照                                   | 000   |

|                          | 05    | 0          | 同期入力遅延                                 | 同期入力遅延、ビット4                                                                      | 0     |

— 26 — REV. 0

|                   | アト             | ベレス             |                                        |                                                                                                                                                                  |                   |

|-------------------|----------------|-----------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| レジスタ名             | 16進            | 10進             | 名前                                     | 機能                                                                                                                                                               | デフォルト             |

| 同期<br>コントロール・     | 06             | 7:4             | 同期入力遅延                                 | これらのレジスタを使って複数のDACの同期をとる方法については「マルチDAC同期」を参照。                                                                                                                    | 0                 |

| レジスタ              | 06             | 3:0             | 入力同期パルスの<br>タイミング誤差許容値                 |                                                                                                                                                                  | 0                 |

|                   | 07             | 7               | 同期レシーバ・イネーブル                           |                                                                                                                                                                  | 0                 |

|                   | 07             | 6               | 同期ドライバ・イネーブル                           |                                                                                                                                                                  | 0                 |

|                   | 07             | 5               | 同期トリガ・エッジ                              |                                                                                                                                                                  | 0                 |

|                   | 07             | 4:0             | 入力データへのSYNC_I<br>サンプリング・クロック・<br>オフセット |                                                                                                                                                                  | 0                 |

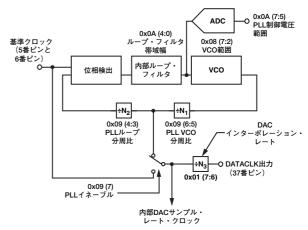

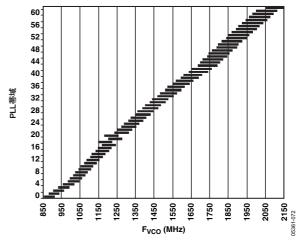

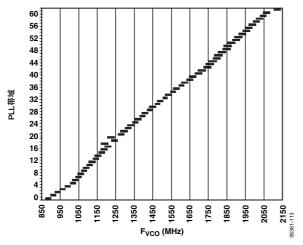

| PLL制御             | 08<br>08<br>09 | 7:2<br>1:0<br>7 | PLL帯域選択<br>VCO AGCゲイン制御<br>PLLイネーブル    | VCO周波数範囲 対 PLL帯域選択値(表17を参照)<br>一般に低い数値(低ゲイン)の方が性能が向上します。<br>0:PLLオフ、DACレート・クロックは外部ソースから<br>供給<br>1:PLLオン、DACレート・クロックはPLLクロック逓<br>倍器を介して外部リファレンス・クロックから内部的に<br>合成 | 110011<br>11<br>0 |

|                   | 09             | 6:5             | PLL VCO分周比                             | FVCO/f <sub>DAC</sub><br>00 × 1<br>01 × 2<br>10 × 4<br>11 × 8                                                                                                    |                   |

|                   | 09             | 4:3             | PLLループ分周比                              | $ \begin{array}{l} f_{\text{DAC}}/f_{\text{REF}} \\ 00 \times 2 \\ 01 \times 4 \\ 10 \times 8 \\ 11 \times 16 \end{array} $                                      |                   |

|                   | 09             | 2:0             | PLLバイアス設定                              | 常に111に設定                                                                                                                                                         | 111               |

| その他の制御            | 0A             | 7:5             | PLL制御電圧範囲                              | 000~111、PLLループ・フィルタ出力での電圧に比例、<br>リードバックのみ                                                                                                                        |                   |

|                   | 0A             | 4:0             | PLLループ帯域幅調整                            | 詳細については「PLLのループ・フィルタ帯域幅」を参照                                                                                                                                      |                   |

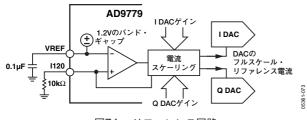

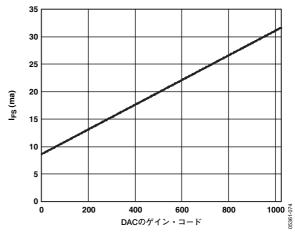

| I DAC<br>コントロール・  | 0B             | 7:0             | I DACゲイン調整                             | I DAC用10ビット・ゲイン設定ワードの(7:0)LSBスライス                                                                                                                                | 11111001          |

| レジスタ              | 0C             | 7               | I DACスリープ                              | 0:IDACオン<br>0:IDACオン                                                                                                                                             | 0                 |

|                   | 0C             | 6               | I DACパワーダウン                            | 0:IDACオン<br>1:IDACオフ                                                                                                                                             | 0                 |

|                   | 0C             | 1:0             | I DACゲイン調整                             | I DAC用の10ビット・ゲイン設定ワードの(9:8)MSB<br>スライス                                                                                                                           | 01                |

| 補助DAC1<br>コントロール・ | 0D             | 7:0             | 補助DAC1ゲイン調整                            | 補助DAC1用の10ビット・ゲイン設定ワードの(7:0)<br>LSBスライス                                                                                                                          | 00000000          |

| レジスタ              | 0E             | 7               | 補助DAC1符号                               | 0:正<br>1:負                                                                                                                                                       |                   |

|                   | 0E             | 6               | 補助DAC1電流方向                             | 0:ソース<br>1:シンク                                                                                                                                                   | 0                 |

|                   | 0E             | 5               | 補助DAC1パワーダウン                           | 0:補助DAC1オン<br>1:補助DAC1オフ                                                                                                                                         | 0                 |

|                   | 0E             | 1:0             | 補助DAC1ゲイン調整                            | 補助DAC1用の10ビット・ゲイン設定ワードの(9:8)<br>  MSBスライス                                                                                                                        | 00                |

REV. 0 — 27 —

|                   | アト  | ドレス |              |                                         |          |

|-------------------|-----|-----|--------------|-----------------------------------------|----------|

| レジスタ名             | 16進 | 10進 | 名前           | 機能                                      | デフォルト    |

| Q DAC<br>コントロール・  | 0F  | 7:0 | Q DACゲイン調整   | Q DAC用の10ビット・ゲイン設定ワードの(7:0)<br>LSBスライス  | 11111001 |

| レジスタ              | 10  | 7   | Q DACスリープ    | 0:QDACオン<br>1:QDACオフ                    | 0        |

|                   | 10  | 6   | Q DACパワーダウン  | 0:QDACオン<br>1:QDACオフ                    | 0        |

|                   | 10  | 1:0 | Q DACゲイン調整   | Q DAC用の10ビット・ゲイン設定ワードの(9:8)<br>MSBスライス  |          |

| 補助DAC2<br>コントロール・ | 11  | 7:0 | 補助DAC2ゲイン調整  | 補助DAC2用の10ビット・ゲイン設定ワードの(7:0)<br>LSBスライス | 00000000 |

| レジスタ              | 12  | 7   | 補助DAC2符号     | 0:正1:負                                  |          |

|                   | 12  | 6   | 補助DAC2電流方向   | 0:ソース<br>1:シンク                          | 0        |

|                   | 12  | 5   | 補助DAC2パワーダウン | 0:補助DAC 2オン<br>1:補助DAC 2オフ              | 0        |

|                   | 12  | 1:0 | 補助DAC2ゲイン調整  | 補助DAC2用の10ビット・ゲイン設定ワードの(9:8)<br>MSBスライス | 00       |

| 割込みレジスタ           | 19  | 7   |              |                                         | 0        |

|                   | 19  | 6   | 同期遅延IRQ      | リードバック、クリアするには0を書き込む                    | 0        |

|                   | 19  | 5   |              |                                         | 0        |

|                   | 19  | 3   |              |                                         | 0        |

|                   | 19  | 2   | 同期遅延IRQイネーブル |                                         | 0        |

|                   | 19  | 1   |              |                                         | 0        |

|                   | 19  | 0   | 内部同期ループバック   |                                         | 0        |

— 28 — REV. 0

## インターポレーション・フィルタの アーキテクチャ

AD9776/AD9778/AD9779では、最高8×のインターポレーションを提供したり、インターポレーション・フィルタを完全にディスエーブルにしたりできます。インターポレーション・フィルタのオーバーフローを回避するには、入力信号をフルスケールから約0.01dB小さくしてください。表12、表13、表14、表15に、ローパス・フィルタと反転sincフィルタの係数を示します。図54、図55、図56は、フィルタ応答のスペクトル・プロットを示します。

表12. ハーフバンド・フィルタ1

| 下位係数   | 上位係数   | 整数值   |

|--------|--------|-------|

| H (1)  | H (55) | -4    |

| H (2)  | H (54) | 0     |

| H (3)  | H (53) | 13    |

| H (4)  | H (52) | 0     |

| H (5)  | H (51) | -34   |

| H (6)  | H (50) | 0     |

| H (7)  | H (49) | 72    |

| H (8)  | H (48) | 0     |

| H (9)  | H (47) | -138  |

| H (10) | H (46) | 0     |

| H (11) | H (45) | 245   |

| H (12) | H (44) | 0     |

| H (13) | H (43) | -408  |

| H (14) | H (42) | 0     |

| H (15) | H (41) | 650   |

| H (16) | H (40) | 0     |

| H (17) | H (39) | -1003 |

| H (18) | H (38) | 0     |

| H (19) | H (37) | 1521  |

| H (20) | H (36) | 0     |

| H (21) | H (35) | -2315 |

| H (22) | H (34) | 0     |

| H (23) | H (33) | 3671  |

| H (24) | H (32) | 0     |

| H (25) | H (31) | -6642 |

| H (26) | H (30) | 0     |

| H (27) | H (29) | 20755 |

| H (28) |        | 32768 |

表13. ハーフバンド・フィルタ2

| 下位係数   | 上位係数   | 整数值  |

|--------|--------|------|

| H (1)  | Н (23) | -2   |

| H (2)  | H (22) | 0    |

| H (3)  | H (21) | 17   |

| H (4)  | H (20) | 0    |

| H (5)  | H (19) | -75  |

| H (6)  | H (18) | 0    |

| H (7)  | H (17) | 238  |

| H (8)  | H (16) | 0    |

| H (9)  | H (15) | -660 |

| H (10) | H (14) | 0    |

| H (11) | H (13) | 2530 |

| H (12) |        | 4096 |

表14. ハーフバンド・フィルタ3

| 下位係数  | 上位係数   | 整数值   |

|-------|--------|-------|

| H (1) | H (15) | -39   |

| H (2) | H (14) | 0     |

| H (3) | H (13) | 273   |

| H (4) | H (12) | 0     |

| H (5) | H (11) | -1102 |

| H (6) | H (10) | 0     |

| H (7) | H (9)  | 4964  |

| H (8) |        | 8192  |

表15. 反転sincフィルタ

| 下位係数  | 上位係数  | 整数值 |

|-------|-------|-----|

| H (1) | H (9) | 2   |

| H (2) | H (8) | -4  |

| H (3) | H (7) | 10  |

| H (4) | H (6) | -35 |

| H (5) |       | 401 |

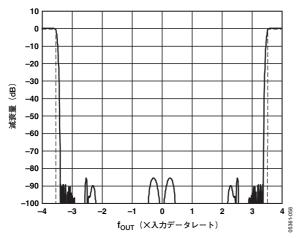

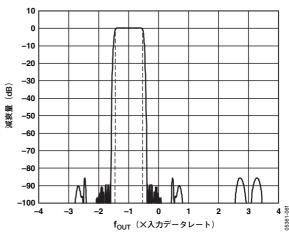

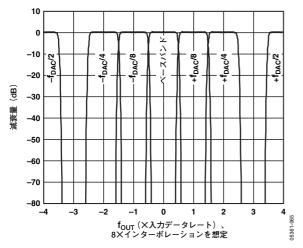

図54. 2×インターポレーション、±4×入力データレートへのローパス応答(点線は1dBのロールオフを示す)

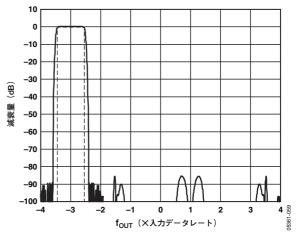

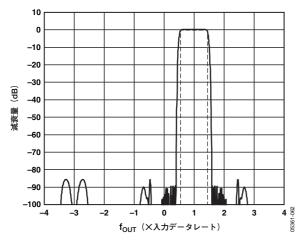

図55. 4×インターポレーション、±4×入力データレートへのローパス応答(点線は1dBのロールオフを示す)

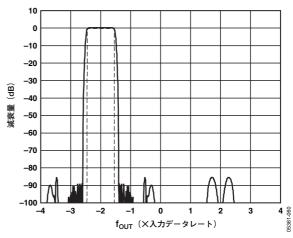

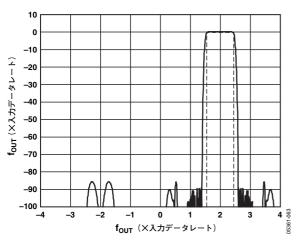

図56. 8×インターポレーション、±4×入力データレートへのローパス応答(点線は1dBのロールオフを示す)

インターポレーション・フィルタと変調器を組み合わせることにより、着信信号はDAC出力サンプル・レートのナイキスト領域内のどこにでも配置できます。入力信号が複素数である場合、このアーキテクチャにより、入力信号を正または負のナイキスト領域に変調できます(表16を参照)。

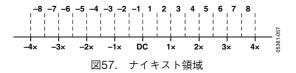

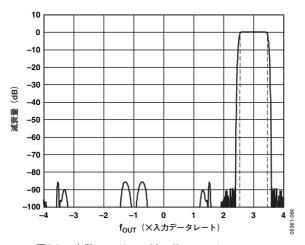

図57は、入力データレートの4倍までのナイキスト領域を示します。

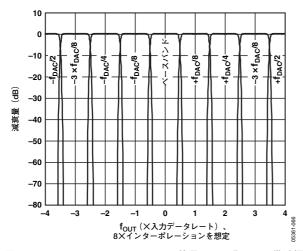

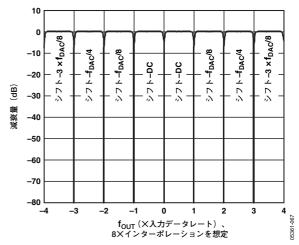

図54、図55、図56は、変調を使用しないデジタル・フィルタのローパス応答を示します。変調機能をオンにすることにより、デジタル・フィルタの応答は、DAC帯域幅内のどこにでも調整できます。一例として、図58~64に非シフト・モードのフィルタ応答を示します(シフト/非シフト・モードのフィルタ応答については表16を参照)。

図58. 4f<sub>DAC</sub>/8フィルタのインターポレーション/ 変調組合わせ

図59.  $-3f_{DAC}/8$ フィルタのインターポレーション/変調組合わせ

図60.  $-2f_{DAC}/8$ フィルタのインターポレーション/変調組合わせ

図61.  $-1f_{DAC}/8$ フィルタのインターポレーション/ 変調組合わせ

図62.  $f_{DAC}/8$ フィルタのインターポレーション/ 変調組合わせ

図63. 奇数モードでの $2f_{DAC}/8$ フィルタの インターポレーション/変調組合わせ

図64. 奇数モードでの $3f_{DAC}/8$ フィルタの インターポレーション/変調組合わせ

シフト・モードのフィルタ応答により、通過帯域の中心を生0.5、 $\pm 1.5$ 、 $\pm 2.5$ 、 $\pm 3.5 f_{DATA}$ とすることができます。シフト・モードの応答に切り替えると、信号は変調されず、代わりに通過帯域がそのままシフトされます。たとえば、図64に示す応答で、信号帯域内が $3.2\sim3.3 f_{DATA}$ の帯域幅にわたって複素数信号であると想定します。ここで偶数モードのフィルタ応答が選択された場合、通過帯域の中心は $3.5 f_{DATA}$ になります。しかし、信号はスペクトル内の同じ場所にとどまります。シフト・モードの機能により、フィルタの通過帯域は、DACナイキスト帯域幅内のどこにでも置くことができます。

AD9776/AD9778/AD9779は、内部複素変調器をインターポレーション・フィルタ応答に組み込んだデュアルDACです。デュアル・チャンネル・モードでは、デバイスは、デジタル入力ポート1とデジタル入力ポート2(それぞれIとQ)において複素数信号の実数成分と虚数成分を期待します。これにより、DAC出力は、複素キャリア $f_{DAC}/2$ 、 $f_{DAC}/4$ 、または $f_{DAC}/8$ によって変調された入力信号の実数成分と虚数成分を表すことになります。

レジスタ2のビット6をセットすると、デバイスはI、Q、I、Q... の順序でポート1からインターリーブされたデータを受け付けます。なおインターリーブ・モードでは、インターリーブが行われるため、IとQのデータ・パスの最初のチャンネル・データレートは、入力データレートの半分になります。最大入力データレートは、デバイスの最大仕様に左右されます。このため、インターリーブ・モードでは入力における合成帯域幅が制限されます。

レジスタ0x02のビット5(実数モード)をセットすると、Qチャンネルに加えて、内部のIとQのデジタル変調もオフになります。これにより、I DACでの出力スペクトルは、 $1\times$ 、 $2\times$ 、 $4\times$ 、 $8\times$ のいずれかに補間された、デジタル入力ポート1での信号を表します。

一般に、所望の信号が $\pm 0.4 \times f_{DATA}$ の範囲内である場合は奇数 フィルタ・モードを、この範囲外なら偶数フィルタ・モードを 使用することを推奨します。いずれの場合も、信号の合計帯域 幅は、 $0.8 \times f_{DATA}$ 未満にしてください。

REV. 0 — 31 —

表16. インターポレーション・フィルタのモード、(レジスタ0x01、ビット<5:2>)

| 補間係数<7:6> | フィルタ・<br>モード<br><5:2> | 変調       | ナイキスト・<br>ゾーン<br>通過帯域 | F_Low¹  | センター1   | F_High <sup>1</sup> | 備考                                                                         |

|-----------|-----------------------|----------|-----------------------|---------|---------|---------------------|----------------------------------------------------------------------------|

| 8         | 0x00                  | DC       | 1                     | -0.05   | 0       | +0.05               | $8\times$ インターポレーション; BW (min) =0.0375× $f_{DAC}$ BW (max) =0.1× $f_{DAC}$ |

| 8         | 0x01                  | DCシフト    | 2                     | 0.0125  | 0.0625  | 0.1125              |                                                                            |

| 8         | 0x02                  | F/8      | 3                     | 0.075   | 0.125   | 0.175               |                                                                            |

| 8         | 0x03                  | F/8シフト   | 4                     | 0.1375  | 0.1875  | 0.2375              |                                                                            |

| 8         | 0x04                  | F/4      | 5                     | 0.2     | 0.25    | 0.3                 |                                                                            |

| 8         | 0x05                  | F/4シフト   | 6                     | 0.2625  | 0.3125  | 0.3625              |                                                                            |

| 8         | 0x06                  | 3F/8     | 7                     | 0.325   | 0.375   | 0.425               |                                                                            |

| 8         | 0x07                  | 3F/8シフト  | 8                     | 0.3875  | 0.4375  | 0.4875              |                                                                            |

| 8         | 0x08                  | F/2      | -8                    | -0.55   | -0.5    | -0.45               |                                                                            |

| 8         | 0x09                  | F/2シフト   | -7                    | -0.4875 | -0.4375 | -0.3875             |                                                                            |

| 8         | 0x0A                  | -3F/8    | -6                    | -0.425  | -0.375  | -0.343              |                                                                            |

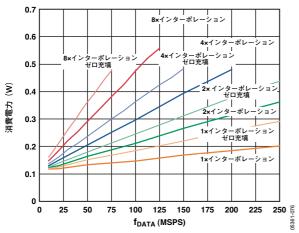

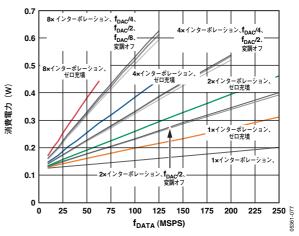

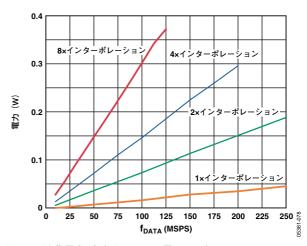

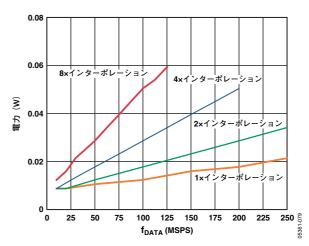

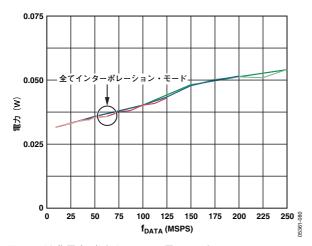

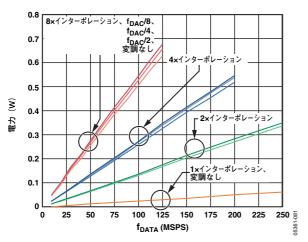

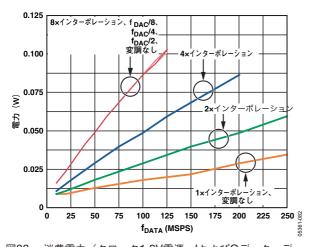

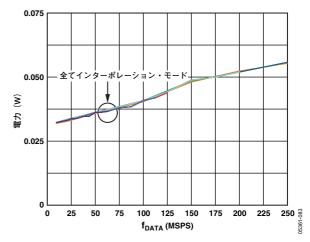

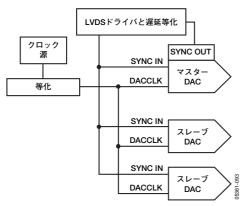

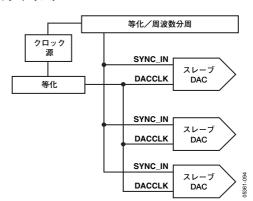

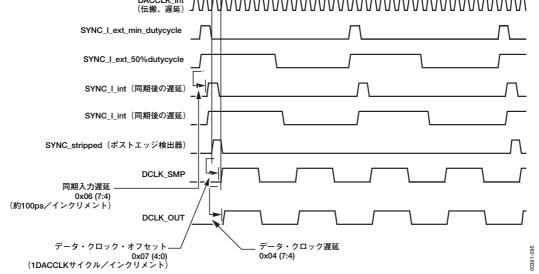

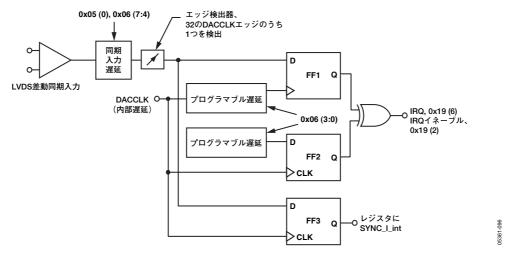

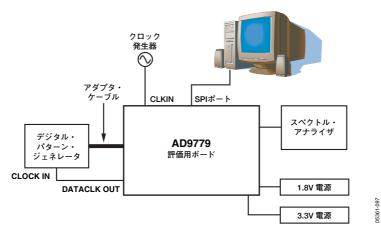

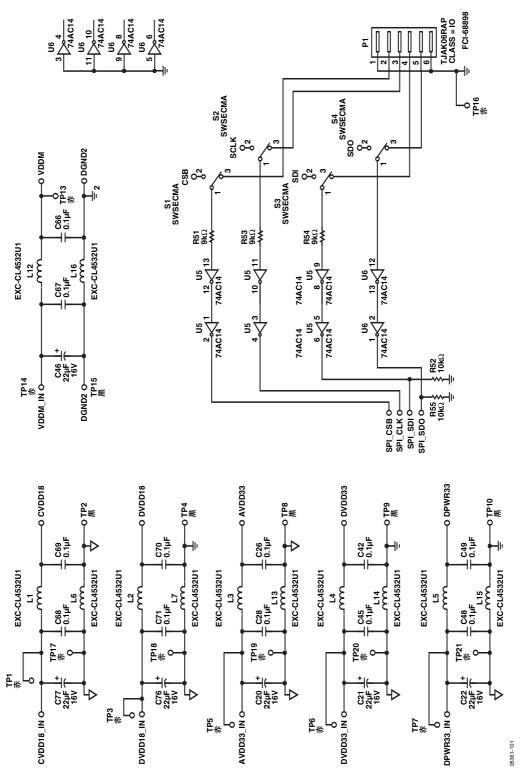

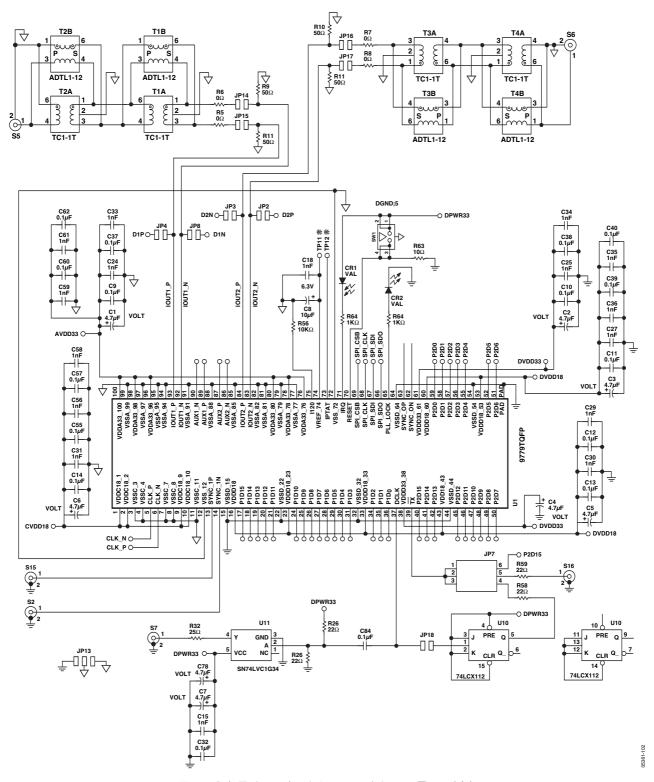

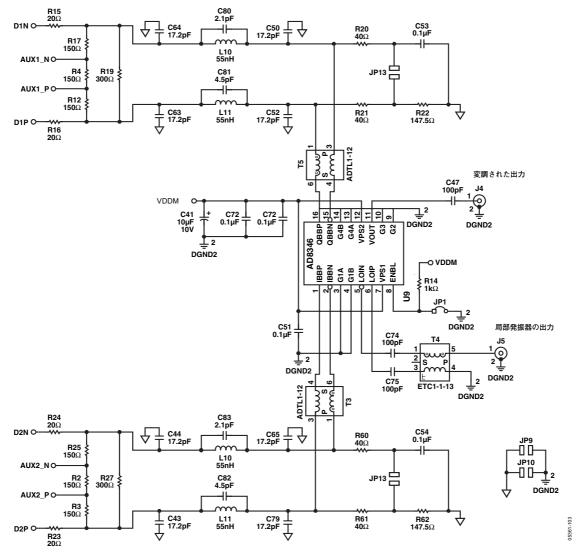

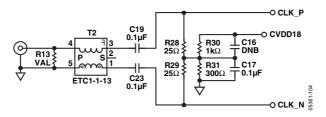

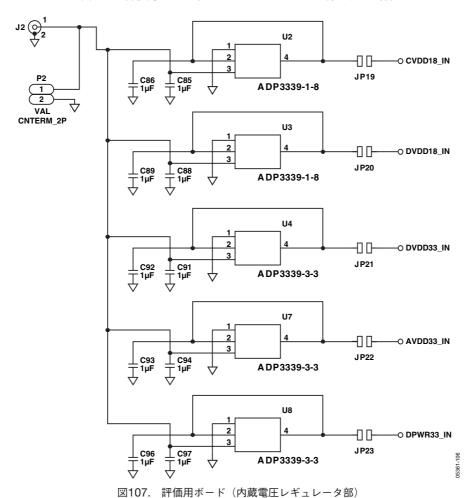

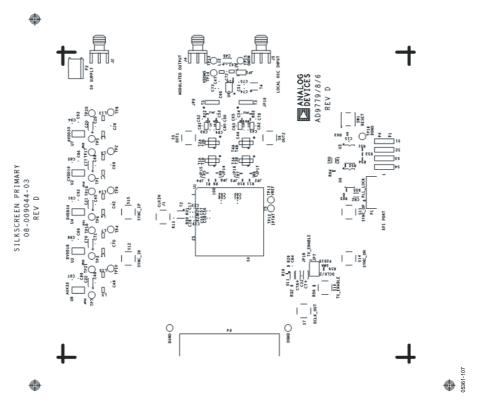

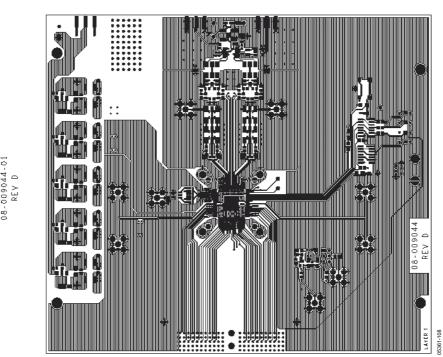

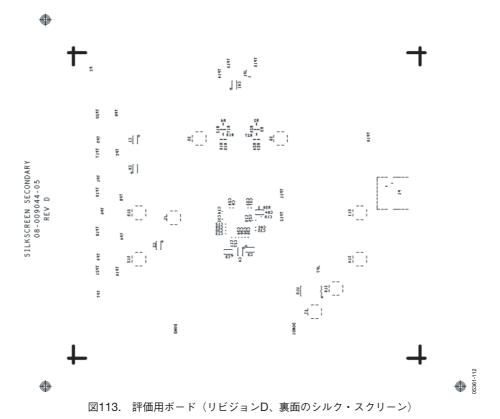

| 8         | 0x0B                  | -3F/8シフト | -5                    | -0.3625 | -0.3125 | -0.2625             |                                                                            |