# 4 x 補間フィルタ付き 14ビット 32 MSPS TxDAC+™

AD9774

### 特長

3 V**または**5 V**の単電源**

14ビットのDAC分解能と入力データ幅

5 Vで32 MSPSの入力データ・レート

13.5 MHz**の再生帯域幅**

1 MHz**で**12 ENOBS

5 MHz 77 dBc SFDR

4×補間フィルタ

69 dB**のイメージ除去**

ナイキスト比に対して84%の通過帯域

0.002 dB の通過帯域リプル

23 3/4サイクルの待ち時間

内蔵4×クロック乗算回路

1.20 Vのオンチップ・リファレンス

44ピンMQFPパッケージ

# アプリケーション

通信送信チャンネル

ワイヤレス基地局

ADSL/HFCモデム ダイレクト・ディジタル合成(DDS)

#### 概要

AD9774は、単電源、オーバーサンプリングの14ピット、ディジタル・アナログ・コンバータ(DAC)で、非常に大きなダイナミック・レンジを必要とする波形再生アプリケーション用に最適化されています。その製造には最新のCMOSプロセスが使用され、完全な低歪みの14ピットDACに、4×ディジタル補間フィルタとクロック乗算回路が組み込まれています。2段の4×ディジタル補間フィルタは、アナログ再生フィルタの複雑性を6分の1以下に抑えます。これは、入力データ・レートを4倍にする一方で、同時にオリジナルの帯域内イメージに対して69 dBを超える抑圧を行っているからです。オンチップのクロック乗算回路は、必要なすべてのクロックを提供します。AD9774は、32 MSPSの入力データ・レート、128 MSPSのDAC出力レートで動作しているとき、最高で13.5 MHzまでの帯域幅を持ったフルスケールの波形を再生することができます。

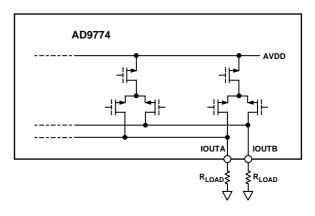

14ピットのDACは、差動電流出力を提供して差動アプリケーションやシングル・エンド・アプリケーションをサポートします。セグメント化された電流ソース構成には、スプリアス成分を抑え、動的性能を高める当社独自のスイッチング技術が使用されています。2つの電流出力の間を整合させることによって、差動出力構成では強力な動的性能が保証されます。差動電流出力を、トランスを介して、あるいは直接出力抵抗に印加すれば相補関係を持った2つのシングル・エンド電圧出力が得られます。また、差動オペアンプ・トポロジーを使用して、1つのシングル・エンド電圧出力を得ることもできます。なお出力電圧のコンプライアンス・レンジは、定格1.25 Vです。

TxDAC+は、アナログ・デバイセズ社の登録商標です。 REV.0

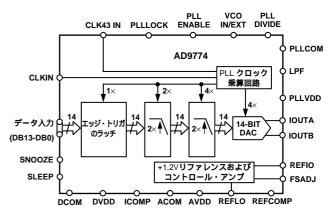

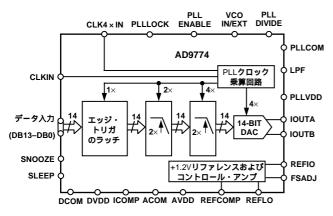

#### 機能ブロック図

さらにエッジ・トリガの入力ラッチ、4×クロック乗算回路、そして温度補償パンドギャップ・リファレンスも組み込まれて、完全なモノリシックDAC製品になっています。電源の選択にも柔軟性があり、+3 Vと+5 VのCMOSロジック・ファミリをサポートします。なお、AD9774のディジタル電源を制限すれば、TTLロジック・レベルも扱うことができます。

オンチップ・リファレンスとコントロール・アンプの構成からは、最高の精度と柔軟性が得られます。AD9774は、オンチップ・リファレンスを用いても、また各種の外部リファレンス電圧を用いても動作させることができます。AD9774のフルスケール電流は、2 mAから20 mAの範囲で調整できるので、さらに広い範囲でゲインの選択が得られます。

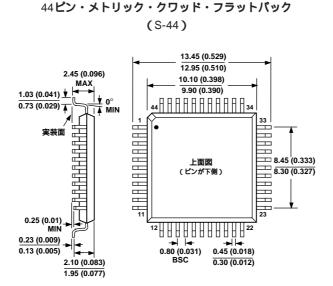

AD9774は、44ピンのMQFPパッケージに実装されています。またその動作は、産業温度範囲にわたって保証されています。

### 製品の主な特長

- 1. 最初の3イメージに69 dBの抑圧を行うことによって、オンチップ4 x 補間フィルタがアナログ再生フィルタの必要条件を軽減します。

- 2. 低いグリッチと短いセトリング時間で、通信を含めた波形再生や ディジタル合成に必要な卓越した動的性能が得られます。

- 3. オンチップのエッジ・トリガ入力CMOSラッチで、CMOSやTTL レベルのロジック・ファミリと簡単にインターフェースすることができます。AD9774では、最大で32 MSPSまでの入力データ・レートがサポートされます。

- 4. 温度補償付き1.20 Vのバンドギャップ・リファレンスがオンチップで組み込まれた完全なDAC製品です。もちろん、外部リファレンスも使用できます。

- 5. AD9774は、各種のシングル・エンドあるいは差動回路トポロ ジー用の電流出力が簡単に構成できます。

- 6. オンチップ・クロック乗算回路が、内蔵補間フィルタに必要なあらゆる高速クロックを生成します。2×クロックと4×クロックは、ともにユーザから供給されたそれより低いレートのデータ・クロックから生成されます。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、 当社はその情報の利用、また利用したことにより引き起こされる第3者の特許または権 利の侵害に関して一切の責任を負いません。さらにアナログ・デバイセズ社の特許また は特許の権利の使用を許諾するものでもありません。

DC仕様(特に指定のない限り、T<sub>MIN</sub>からT<sub>MAX</sub>、AVDD = +5 V、PLLVDD = +5 V、DVDD = +5 V、I<sub>OUTES</sub> = 20 mA)

| パラメータ                                          | Min     | Тур    | Max          | 単位                |

|------------------------------------------------|---------|--------|--------------|-------------------|

| 分解能                                            | 14      |        |              | ピット               |

| DC <b>精度</b> <sup>1</sup>                      |         |        |              |                   |

| 積分線形性誤差(INL)                                   |         |        |              |                   |

| $T_A = +25$                                    |         | ± 4    |              | LSB               |

| $T_{MIN} \sim T_{MAX}$                         |         |        |              |                   |

| <b>微分非線形性(</b> DNL <b>)</b>                    |         |        |              |                   |

| $T_A = +25$                                    |         | ±3     |              | LSB               |

| $T_{MIN} \sim T_{MAX}$                         |         |        |              |                   |

| 単調性(12ビット)                                     | 定格仕     | 様温度範囲に | わたって保証       | ı                 |

| アナログ出力                                         |         |        |              |                   |

| オフセット誤差                                        | - 0.025 |        | + 0.025      | FSR <b>0%</b>     |

| ゲイン誤差(内蔵リファレンスなし)                              | - 7     | ± 1    | +7           | FSR <b>0%</b>     |

| ゲイン誤差(内蔵リファレンスあり)                              | - 7.5   | ± 1    | <b>+</b> 7.5 | FSR <b>0%</b>     |

| フルスケール出力 <b>電流</b> 2                           |         | 20     |              | mA                |

| 出力コンプライアンス・レンジ                                 |         | 1.25   |              | V                 |

| 出力抵抗                                           |         | 100    |              | k                 |

| 出力容量                                           |         | 5      |              | pF                |

| リファレンス出力                                       |         |        |              |                   |

| リファレンス電圧                                       | 1.14    | 1.20   | 1.26         | V                 |

| リファレンス出力電流。                                    |         | 1      |              | μА                |

| リファレンス入力                                       |         |        |              |                   |

| 入力コンプライアンス・レンジ                                 | 0.1     |        | 1.25         | V                 |

| リファレンス入力抵抗                                     |         | 1      |              | М                 |

| 温度係数                                           |         |        |              |                   |

| ユニポーラ・オフセット・ドリフト                               |         | 0      |              | FSR <b>Ø</b> ppm/ |

| ゲイン・ドリフト(内蔵リファレンス不使用)                          |         | ± 50   |              | FSR <b>Ø</b> ppm/ |

| ゲイン・ドリフト(内蔵リファレンス使用)                           |         | ± 100  |              | FSR <b>Ø</b> ppm/ |

| リファレンス電圧ドリフト                                   |         | ± 100  |              | FSR <b>O</b> ppm/ |

| 電源                                             |         |        |              |                   |

| AVDD                                           |         |        |              |                   |

| <b>電圧レンジ</b> 4                                 | 2.7     | 5.0    | 5.5          | V                 |

| アナロ <b>グ電源電流(I<sub>AVDD</sub>)</b>             |         | 26.5   | 32           | mA                |

| スリープ・モードのアナログ電源電流(I <sub>AVDD</sub> )          |         | 3.2    | 5            | mA                |

| PLLVDD                                         |         |        |              |                   |

| 電圧レンジ                                          | 2.7     | 5.0    | 5.5          | V                 |

| クロック乗算回路の電源電流(I <sub>PLLVDD</sub> )            |         | 13     | 17           | mA                |

| DVDD                                           |         |        |              |                   |

| 電圧レンジ                                          | 2.7     | 5.0    | 5.5          | V                 |

| 5 ∨ <b>におけるディジタル電源電流( I<sub>DVDD</sub> )⁵</b>  |         | 123.0  | 140.0        | mA                |

| スヌーズ・モードの5 ∨におけるディジタル電源電流(I <sub>DVDD</sub> )  |         | 42.0   | 50.0         | mA                |

| 3 ∨ <b>におけるディジタル電源電流(</b> I <sub>DVDD</sub> )⁵ |         | 62.0   |              | mA                |

| 定格消費電力                                         |         |        |              |                   |

| 3 V <b>における</b> AVDDとDVDD6                     |         | 415    |              | mW                |

| 5 V <b>における</b> AVDDとDVDD <sup>6</sup>         |         | 1125   |              | mW                |

| 電源除去比(PSRR) - AVDD <sup>7</sup>                | - 0.2   |        | + 0.2        | FSR <b>の%</b> /V  |

| 電源除去比(PSRR) - PLLVDD <sup>7</sup>              | - 0.025 |        | + 0.025      | FSR <b>の%</b> /V  |

| 電源除去比(PSRR) - DVDD <sup>7</sup>                | - 0.025 |        | + 0.025      | FSR <b>の%</b> /∨  |

|                                                | 0.0=0   |        |              |                   |

注

仕様は、予告なしに変更されることがあります。

- 2 -REV.0

E 仮想グラウンドをドライブするIOUTAで測定。 定格フルスケール電流IOUTFSは32×1<sub>REF</sub>電流。 外部負荷をドライブするときは外付けのアンブを使用。 最適性能を維持するために3 V未満で動作させるときは出力電流を12 mA以下に抑えてください。 f<sub>CLOCK</sub> = 25 MSPSとf<sub>OUT</sub> = 1.01 MHzで測定。 IOUTAおよびIOUTBにおいて、f<sub>CLOCK</sub> = 32 MSPS、f<sub>OUT</sub> = 12.8 MHzでパッファなしの電圧出力を測定。 + 564の電源変動

<sup>±5</sup>**%の電源変動**

# 動的仕様(特に指定のない限り、T<sub>MIN</sub>からT<sub>MAX</sub>、AVDD = +5 V、PLLVDD = +5 V、DVDD = +5 V、I<sub>OUTES</sub> = 20 mA、差動トランス結合出力、50 両端終端)

| パラメータ                                                                     | Min    | Тур         | Max | 単位      |

|---------------------------------------------------------------------------|--------|-------------|-----|---------|

| 動的性能                                                                      |        |             |     |         |

| 最大出力更新レート DVDD = 5 V <b>のとき</b>                                           | 128    |             |     | MSPS    |

| DVDD = 3 V <b>のとき</b>                                                     | 100    | 128         |     | MSPS    |

| 出力セトリング時間(t <sub>ST</sub> )(0.025%まで)                                     |        | 35          |     | ns      |

| 出力伝播遅延(t <sub>PD</sub> )                                                  |        | 55          |     | クロック1   |

| グリッチ・インパルス                                                                |        | 5           |     | pV-s    |

| 出力立上り時間(10%~90%) <sup>2</sup>                                             |        | 2.5         |     | ns      |

| 出力立下り時間(10%~90%) <sup>2</sup>                                             |        | 2.5         |     | ns      |

| 出力ノイズ(I <sub>OUTFS</sub> = 20 mA)                                         |        | 50          |     | pA/√Hz² |

| ナイキストに対するAC線形性                                                            |        |             |     |         |

| ナイキストに対するスプリアスのないダイナミック・レンジ(                                              | (SFDR) |             |     |         |

| $f_{CLOCK} = 25 \text{ MSPS}; f_{OUT} = 1.01 \text{ MHz}$                 |        |             |     |         |

| 0 dBFS <b>出力</b>                                                          |        | 79          |     | dB      |

| - 6 dBFS <b>出力</b>                                                        |        | 86          |     | dB      |

| - 12 dBFS <b>出力</b>                                                       |        | 75          |     | dB      |

| - 18 dBFS <b>出力</b>                                                       |        | 75          |     | dB      |

| $f_{CLOCK} = 32 \text{ MSPS}; f_{OUT} = 1.01 \text{ MHz}$                 |        | 78          |     | dB      |

| $f_{CLOCK} = 32 \text{ MSPS}; f_{OUT} = 5.01 \text{ MHz}$                 |        | 77          |     | dB      |

| $f_{CLOCK} = 32 \text{ MSPS}; f_{OUT} = 10.01 \text{ MHz}$                |        | 79          |     | dB      |

| $f_{CLOCK} = 32 \text{ MSPS}; f_{OUT} = 13.01 \text{ MHz}$                |        | 78          |     | dB      |

| 全高調波歪み(THD)                                                               |        |             |     |         |

| $f_{CLOCK} = 25 \text{ MSPS}; f_{OUT} = 1.01 \text{ MHz}; 0 \text{ dBFS}$ |        | <b>-</b> 75 |     | dB      |

| 信号対雑音比(SNR)                                                               |        |             |     |         |

| $f_{CLOCK} = 25 \text{ MSPS}; f_{OUT} = 1.01 \text{ MHz}; 0 \text{ dBFS}$ |        | 76          |     | dB      |

# ディジタル仕様(特に指定のない限り、T<sub>MIN</sub>からT<sub>MAX</sub>、AVDD=+5 V、PLLVDD=+5 V、DVDD=+5 V、I<sub>OUTES</sub>=20 mA)

| The state of the s |      |     | - 1  1001F3 |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------------|----|

| パラメータ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Min  | Тур | Max         | 単位 |

| ディジタル入力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |     |             |    |

| DVDD <b>= +</b> 5 V <b>のときのロジック</b> " 1 " <b>の電圧</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.5  | 5   |             | V  |

| DVDD <b>= +</b> 3 V <b>のときのロジック</b> " 1 " <b>の電圧</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.1  | 3   |             | V  |

| DVDD = +5 V <b>のときのロジック</b> " 0 " <b>の電圧</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 0   | 1.3         | V  |

| DVDD <b>= +</b> 3 V <b>のときのロジック</b> " 0 " <b>の電圧</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 0   | 0.9         | V  |

| ロジック" 1 " <b>の電流</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 10 |     | <b>+</b> 10 | μA |

| ロジック" 0 " <b>の電流</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 10 |     | <b>+</b> 10 | μΑ |

| 入力容量                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | 5   |             | pF |

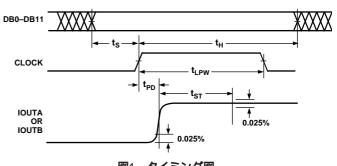

| 入力セットアップ時間( $t_{ m s}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 2.5 |             | ns |

| 入力ホールド時間( t <sub>н</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 1.5 |             | ns |

| ラッチ・パルス幅( t <sub>LPW</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 4   |             | ns |

図1.タイミング図

REV.0 - 3 -

伝播遅延は、データ入力からDAC更新までの遅れ時間。 2 50 の負荷に対するシングルエンドで測定。 仕様は、予告なしに変更されることがあります。

ディジタル・フィルタ仕様(特に指定のない限り、T<sub>MIN</sub>からT<sub>MAX</sub>、AVDD = +2.7 V ~ +5.5 V、DVDD = +2.7 V ~ +5.5 V、I<sub>OUTFS</sub> = 20 mA)

| Min    | _      |                                                                              |                                                                              |

|--------|--------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| IVIIII | Тур    | Max                                                                          | 単位                                                                           |

|        |        |                                                                              |                                                                              |

| 32     |        |                                                                              | MSPS                                                                         |

| 25     | 32     |                                                                              | MSPS                                                                         |

|        |        |                                                                              |                                                                              |

|        | 0.410  |                                                                              | f <sub>OUT</sub> /f <sub>CLOCK</sub>                                         |

|        | 0.414  |                                                                              | f <sub>OUT</sub> /f <sub>CLOCK</sub>                                         |

|        | 0.420  |                                                                              | f <sub>OUT</sub> /f <sub>CLOCK</sub>                                         |

|        | 0.482  |                                                                              | f <sub>OUT</sub> /f <sub>CLOCK</sub>                                         |

|        |        |                                                                              |                                                                              |

|        |        |                                                                              |                                                                              |

|        | - 69.5 |                                                                              | dB                                                                           |

|        | - 79.5 |                                                                              | dB                                                                           |

|        | 38     |                                                                              | 入力クロック                                                                       |

|        |        |                                                                              |                                                                              |

|        | 53     |                                                                              | 入力クロック                                                                       |

|        | 62     |                                                                              | 入力クロック                                                                       |

|        | 32     | 32<br>25<br>32<br>0.410<br>0.414<br>0.420<br>0.482<br>- 69.5<br>- 79.5<br>38 | 32<br>25<br>32<br>0.410<br>0.414<br>0.420<br>0.482<br>- 69.5<br>- 79.5<br>38 |

注

# 絶対最大定格\*

| パラメータ              | 対象     | Min   | Max          | 単位 |

|--------------------|--------|-------|--------------|----|

| AVDD               | ACOM   | - 0.3 | + 6.5        | V  |

| DVDD               | DCOM   | - 0.3 | + 6.5        | V  |

| PLLVDD             | PLLCOM | - 0.3 | + 6.5        | V  |

| ACOM               | DCOM   | - 0.3 | + 0.3        | V  |

| PLLCOM             | ACOM   | - 0.3 | + 0.3        | V  |

| PLLCOM             | DCOM   | - 0.3 | + 0.3        | V  |

| AVDD               | DVDD   | - 6.5 | + 6.5        | V  |

| PLLVDD             | DVDD   | - 0.3 | + 6.5        | V  |

| PLLVDD             | AVDD   | - 0.3 | + 6.5        | V  |

| CLKIN, CLK4 × IN   | DVDD   | - 0.3 | + 6.5        | V  |

| SLEEP, SNOOZE      | DCOM   | - 0.3 | DVDD + 0.3   | V  |

| ディジタル入力            | DCOM   | - 0.3 | DVDD + 0.3   | V  |

| PLL DIVIDE, LPF    | ACOM   | - 0.3 | PLLVDD + 0.3 | V  |

| PLLLOCK            | ACOM   | - 0.3 | PLLVDD + 0.3 | V  |

| VCO IN/EXT         | ACOM   | - 0.3 | PLLVDD + 0.3 | V  |

| IOUTA/IOUTB        | ACOM   | - 0.3 | AVDD + 0.3   | V  |

| PEFIO, FSADJ       | ACOM   | - 0.3 | AVDD + 0.3   | V  |

| FSADJ              | ACOM   | - 0.3 | AVDD + 0.3   | V  |

| ICOMP              | ACOM   | - 0.3 | AVDD + 0.3   | V  |

| REFCOM             | ACOM   | - 0.3 | + 0.3        | V  |

| 接合温度               |        |       | + 150        |    |

| 保管温度               |        | - 65  | + 150        |    |

| リード温度(10 <b>秒)</b> |        |       | + 300        |    |

<sup>\*</sup> 上記の絶対最大定格を超えるストレスは、デバイスに永久的なダメージを与えることがあ ります。このリストはストレス定格を示すことだけを目的とし、これらの条件もしくは本 仕様書の動作に関するセクションに示した以外の条件におけるこのデバイスの機能的な 動作を意味するものではありません。長時間にわたって絶対最大定格条件で使用すると、 デバイスの信頼性に影響が現れることがあります。

# オーダー・ガイド

|          |                           |                   | パッケージ・ |

|----------|---------------------------|-------------------|--------|

| モデル      | 温度範囲                      | パッケージ区分           | オプション* |

| AD9774AS | <b>-</b> 40 ~ <b>+</b> 85 | 44 <b>ピン</b> MQFP | S-44   |

| AD9774EB | 評価ボード                     |                   |        |

<sup>\*</sup>S=メトリック・クワッド・フラットパック

# 温度特性 温度抵抗

44ピンMQFP

$_{JA} = 53.2$  /W <sub>JC</sub> = 19 /W

REV.0 - 4 -

<sup>-</sup>DACのSINX/X特性を除きます。 インパルス入力と出力応答のピークの間のデータ・クロック・サイクル数として定義されます。

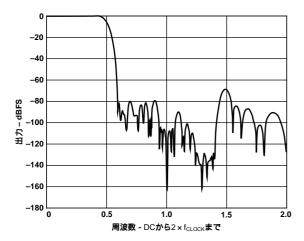

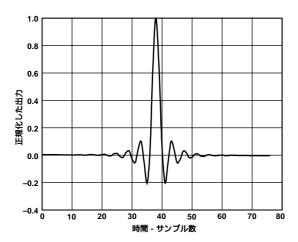

図2a.FIRフィルタの周波数特性

図2b . FIRフィルタのインパルス応答

# 表 . 初段補間フィルタの整数フィルタ係数 (55タップ・ハーフパンドFIRフィルタ)

|        |        | (21707)     |

|--------|--------|-------------|

| 下位係数   | 上位係数   | 整数值         |

| H (1)  | H (55) | - 1         |

| H (2)  | H (54) | 0           |

| H (3)  | H (53) | 3           |

| H (4)  | H (52) | 0           |

| H (5)  | H (51) | 7           |

| H (6)  | H (50) | 0           |

| H (7)  | H (49) | 15          |

| H (8)  | H (48) | 0           |

| H (9)  | H (47) | <b>-</b> 28 |

| H (10) | H (46) | 0           |

| H (11) | H (45) | 49          |

| H (12) | H (44) | 0           |

| H (13) | H (43) | - 81        |

| H (14) | H (42) | 0           |

| H (15) | H (41) | 128         |

| H (16) | H (40) | 0           |

| H (17) | H (39) | - 196       |

| H (18) | H (38) | 0           |

| H (19) | H (37) | 295         |

| H (20) | H (36) | 0           |

| H (21) | H (35) | - 447       |

| H (22) | H (34) | 0           |

| H (23) | H (33) | 706         |

| H (24) | H (32) | 0           |

| H (25) | H (31) | - 1274      |

| H (26) | H (30) | 0           |

| H (27) | H (29) | 3976        |

| H (28) |        | 6276        |

# 表 . 第2段補間フィルタの整数フィルタ係数 (23タップ・ハーフバンドFIRフィルタ)

| (20) ) / ) / ) / ) |        |       |  |

|--------------------|--------|-------|--|

| 下位係数               | 上位係数   | 整数值   |  |

| H (1)              | H (23) | - 6   |  |

| H (2)              | H (22) | 0     |  |

| H (3)              | H (21) | 37    |  |

| H (4)              | H (20) | 0     |  |

| H (5)              | H (19) | - 125 |  |

| H (6)              | H (18) | 0     |  |

| H (7)              | H (17) | 316   |  |

| H (8)              | H (16) | 0     |  |

| H (9)              | H (15) | - 736 |  |

| H (10)             | H (14) | 0     |  |

| H (11)             | H (13) | 2562  |  |

| H (12)             |        | 4096  |  |

注意 -

ESD(静電放電)の影響を受けやすいデバイスです。  $4000 \lor$ もの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることもあります。このAD9774には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電にさらされたデバイスには回復不能な損傷が残ることもあります。 したがって、性能低下や機能喪失を避けるために、適切なESD予防措置をとるようお奨めします。

REV.0 - 5 -

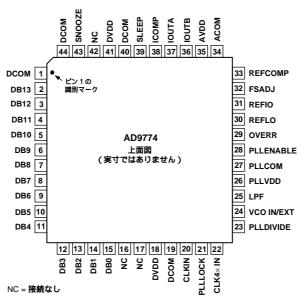

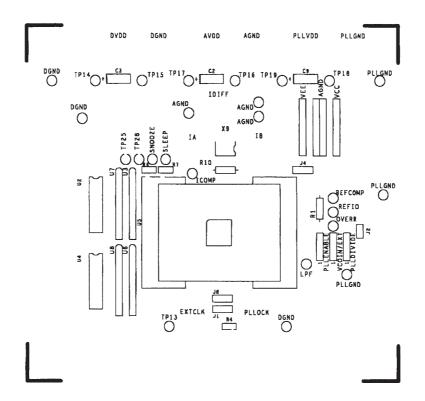

# ピン機能の説明

| ピン番号       | 名称         | 説明                                                                                   |

|------------|------------|--------------------------------------------------------------------------------------|

| 1,19,40,44 | DCOM       | ディジタル共通ペース。                                                                          |

| 2          | DB13       | 最上位データ・ビット(MSB)。                                                                     |

| 3~14       | DB12~DB1   | データ・ピット1~12。                                                                         |

| 15         | DB0        | 最下位データ・ビット(LSB)。                                                                     |

| 16, 17, 42 | NC         | 内部接続なし。                                                                              |

| 18,41      | DVDD       | <b>ディジタル電源(+2.7 V~+5.5 V)</b>                                                        |

| 20         | CLKIN      | クロック入力。クロックの正側のエッジでラッチされるデータ。                                                        |

| 21         | PLLLOCK    | フェーズ・ロック・ループのロック信号。アクティブ・ハイでPLLが入力クロックにロックされたことを示します。                                |

| 22         | CLK4×IN    | PLLがディセーブルのときの外部4×クロック入力。内蔵PLLがアクティブのときは、無接続です。                                      |

| 23         | PLLDIVIDE  | PLLレンジ・コントロール・ピン。CLKINが10 MSPS以下のときは、PLLCOMに接続します。CLKINが10 MSPSを超                    |

|            |            | えるときはPLLVDDに接続します。                                                                   |

| 24         | VCO IN/EXT | 内蔵の電圧制御発振回路(VCO)のイネーブル/ディセーブル・ピン。VCOをイネーブルにするときは、PLLVDDに                             |

|            |            | 接続します。VCOをディセーブルして外付けVCO出力でCLK4×INを駆動するときはPLLCOMに接続します。                              |

| 25         | LPF        | PLLループ・フィルタのノード。内蔵VCOがディセーブルのときは、外付けVCOコントロール入力に接続しま                                 |

|            |            | <b>ं इ</b> .                                                                         |

| 26         | PLLVDD     | フェーズ・ロック・ループ(PLL)電源(+2.7 V~+5.5 V)。                                                  |

| 27         | PLLCOM     | フェーズ・ロック・ループ共通ベース。                                                                   |

| 28         | PLLENABLE  | フェーズ・ロック・ループ・イネーブル。イネーブルするときはPLLVDDに接続します。ディセーブルするときは                                |

|            |            | PLLCOM <b>に接続します。</b>                                                                |

| 29         | OVERR      | ディジタル・フィルタ・オーバーレンジ出力。アクティブ・ハイでディジタル・フィルタがオーバーフローしたこ                                  |

|            |            | とを示します。                                                                              |

| 30         | REFLO      | 内蔵1.2 Vリファレンス使用時のリファレンス・グラウンド。内蔵リファレンスをディセーブルするときは、AVDD                              |

|            |            | に接続します。                                                                              |

| 31         | REFIO      | リファレンス入力/出力。内蔵リファレンスがディセーブルのとき(つまりREFLOがAVDDに接続されているとき)                              |

|            |            | はリファレンス入力となります。内蔵リファレンスがアクティブのとき(つまりREFLOがACOMに接続されている                               |

|            |            | とき)は1.2 Vのリファレンス出力になります。内蔵リファレンスをアクティブにするときは、ACOMに0.1 µ Fの                           |

| 00         | FOARI      | キャパシタが必要になります。                                                                       |

| 32         | FSADJ      | フルスケール電流出力調整。                                                                        |

| 33         | REFCOMP    | ノイズ除去ノード。AVDDに0.1μFを追加してください。                                                        |

| 34         | ACOM       | アナログ共通ペース。                                                                           |

| 35         | AVDD       | アナログ電源(+2.7 V~+5.5 V)。                                                               |

| 36         | IOUTB      | 相補DAC電流出力。すべてのデータ・ビットが0のときはフルスケール電流になります。                                            |

| 37         | IOUTA      | DAC電流出力。すべてのデータ・ピットが1のときはフルスケール電流になります。                                              |

| 38         | ICOMP      | スイッチ・ドライバ回路用の内部バイアス・ノード。0.1μFのキャパシタを用いてACOMと減結合します。                                  |

| 39         | SLEEP      | パワーダウン・コントロール・入力。アクティブ・ハイ。使用しないときはDCOMに接続します。                                        |

| 43         | SNOOZE     | スヌーズ・コントロール入力。4×補間フィルタを非アクティブにしてディジタルの消費電力だけに抑えます。アク<br>  ティブ・ハイ。使用しないときはDCOMに接続します。 |

# ピン構成

- 6 - REV.0

# 仕様の定義

#### 線形性誤差(積分非線形性あるいはINLともいいます)

線形性誤差は、ゼロからフルスケールまでを結んだ直線、つまり 理想的な出力に対する実際のアナログ出力のずれの最大値として定 義されます。

# 微分非線形性(またはDNL)

DNLは、ディジタル入力コードが1LSB変化したときのアナログ値における変化の測定値で、フルスケールに対して正規化されます。

# 単調性モノトニック

D/Aコンパータが単調であれば、ディジタル入力が増加するとき、D/Aコンパータの出力が増加するか一定になります。

### オフセット誤差

理想的なゼロからの出力電流のずれをオフセット誤差といいます。IOUTAの場合は、入力がすべて0のとき、出力が0 mAになることが期待されています。またIOUTBの場合は、入力がすべて1にセットされたとき、出力が0 mAになることが期待されています。

#### ゲイン誤差

理想的な出力スパンと実際のずれをいいます。実際のスパンは、 すべての入力を1にセットしたときの出力から、すべての入力を0に セットしたときの出力を引いた値になります。

#### 出力コンプライアンス・レンジ

電流出力DACの出力における許容電圧範囲をいいます。最大コンプライアンス限界を超えて動作させると、出力段の飽和やブレークダウンを招いて線形性が失われるおそれがあります。

# 温度ドリフト

温度ドリフトは、室温(+25 )から $T_{MIN}$ または $T_{MAX}$ に変化したときの値の変化分として定義されます。オフセットとゲイン・ドリフトについては、1 当たりのドリフトがフルスケール範囲(FSR)に対するppmで表されます。リファレンス・ドリフトについては、1 当たりのドリフトがppmで表されます。

#### 電源除去

電源が定格値から最小または最大の所定電圧に変化したときのフルスケール出力における最大変化をいいます。

#### セトリング時間

出力が最終値から所定許容範囲内の値に達してそこにとどまる までの時間で、出力の遷移の開始から測定されます。

#### グリッチ・インパルス

DACにおける非対称切換え時間は、好ましくない出力の過渡状態をもたらし、グリッチ・インパルスとして定量化されます。pV-sを単位として、グリッチの正味の面積で測定されます。

#### スプリアスのないダイナミック・レンジ

所定の帯域にわたるスプリアス信号のピーク値と、出力信号の振幅の実効値の差をdBで表した値をいいます。

# 全高調波歪み

THDは、入力信号の測定値の実効値と、第1~第6高調波成分のrms和の比をいいます。パーセントまたはデシベル(dB)で表します。

#### 信号対ノイズ比(SNR)

S/Nは、第1~第6高調波成分および直流成分を除いたナイキスト 周波数以下の信号以外のスペクトル成分のrms和に対する出力信号 の測定値の実効値の比をいいます。SNRの値はデシベルで表されま す

#### 诵過帯域

印加された入力が減衰されずにDAC出力となる周波数帯域をいいます。

# 阻止带域除去

DACに印加された通過帯域外の周波数の減衰率で、通過帯域内で DAC入力に印加されたフルスケールの信号に対する相対値で表さ れます。

# 群遅延

デバイス入力にインパルスを印加してからDAC出力電流にピークが現れるまでの入力クロック数をいいます。

#### インパルス応答

入力に印加されたインパルスに対するデバイスの応答をいいます。

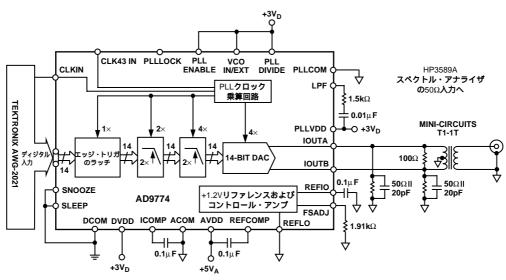

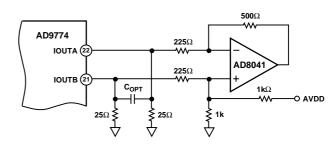

図3.基本AC特性テストのセットアップ

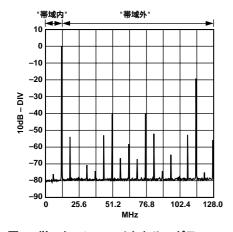

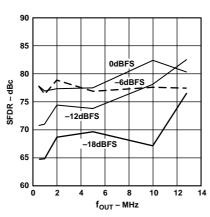

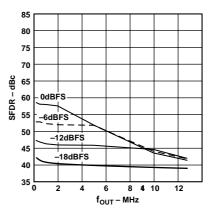

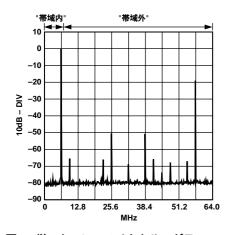

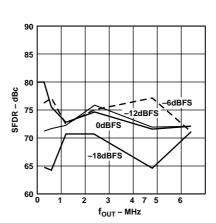

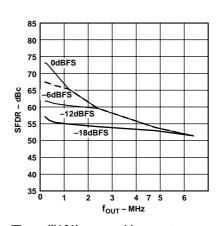

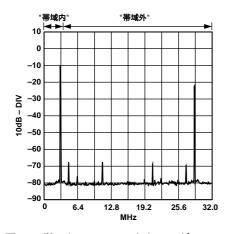

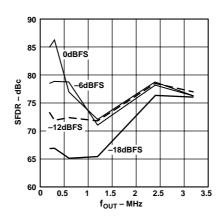

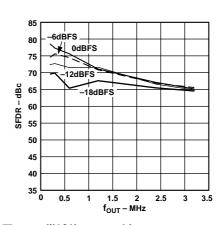

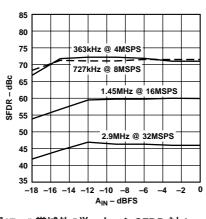

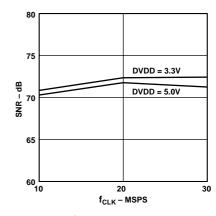

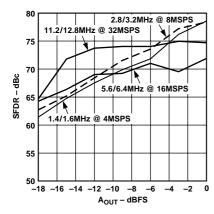

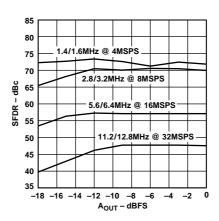

代表的なAC特性曲線(特に指定のない限りAVDD = +5 V、PLLVDD = +3 V、DVDD = +3 V、I<sub>OUTFS</sub> = 20 mA、50 両端終端負荷、 差動出力、T<sub>A</sub> = +25 。図4、5、6についてはPLLVDD = +5 V、DVDD = +5 Vとなっている点に注意)

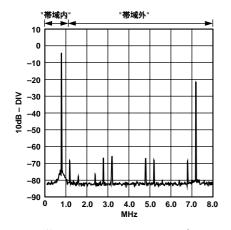

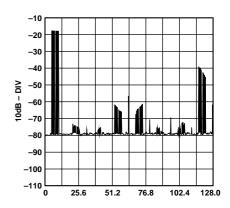

図4.単一トーン・スペクトルのグラフ @32 MSPS、f<sub>OUT</sub> = 12.8 MHz (DC**か**ら4×CLKIN**まで**)

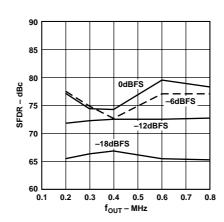

図5. " 帯域内 "SFDR 対 f<sub>out</sub> @32 MSPS (DCからCLKIN/2まで)

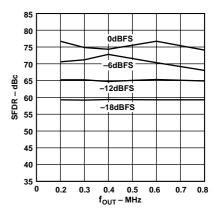

図6. " 帯域外 "SFDR 対 f<sub>out</sub> @32 MSPS (CLKIN/2から3 1/2 CLKINまで)

図7 . 単一トーン・スペクトルのグラフ @16 MSPS、f<sub>OUT</sub> = 6.4 MHz (DC**から**4×CLKINまで)

図8." 帯域内 "SFDR 対 f<sub>OUT</sub> @16 MSPS (DCからCLKIN/2まで)

図9. "帯域外" SFDR 対 f<sub>out</sub> @16 MSPS (CLKIN/2から3 1/2 CLKINまで)

図10 . 単一トーン・スペクトルのグラフ @8 MSPS、f<sub>out</sub> = 3.2 MHz (DC**から**4×CLKINまで)

図11." 帯域内"SFDR 対 f<sub>OUT</sub> @8 MSPS (DC**から**CLKIN/2まで)

- 8 - REV.0

図13 . 単一トーン・スペクトルのグラフ @2 MSPS、f<sub>out</sub> = 800 kHz (DC**から**4×CLKINまで)

図14. "帯域内"SFDR 対 f<sub>OUT</sub> @2 MSPS (DC**から**CLKIN/2まで)

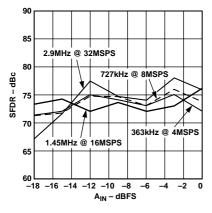

図16. " 帯域内 "単一トーンSFDR 対 A<sub>IN</sub> @f<sub>OUT</sub> = f<sub>CLOCK</sub>/7 (DC**から**CLKIN/2まで)

図17. " 帯域外 "単一トーンSFDR 対 A<sub>IN</sub> @f<sub>OUT</sub> = f<sub>CLOCK</sub>/7 (DC**から**3 1/2 CLKINまで)

図18. SNR 対  $f_{CLKIN}$  @ $f_{OUT} = 2$  MHz (DCからCLKIN/2まで)

図19. " 帯域内 "2トーンSFDR 対 A<sub>OUT</sub> @f<sub>OUT</sub> = f<sub>CLOCK</sub>/2.7 (DC**から**CLKIN/2まで)

図20. " 帯域外 "2トーンSFDR 対 A<sub>OUT</sub> @f<sub>OUT</sub> = f<sub>CLOCK</sub>/2.7 (DC**から**3 1/2 CLKINまで)

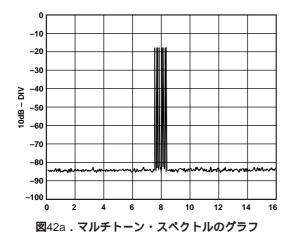

図21 . マルチトーン・スペクトルのグラフ @32 MSPS (DCから4×CLKINまで)

REV.0 - 9 -

## 機能説明

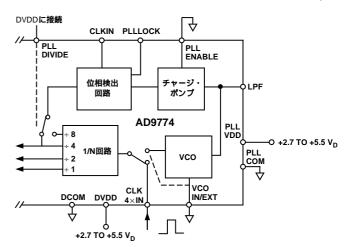

図22に、AD9774の簡略化したブロック図を示します。AD9774は、完全な4×オーバーサンプリングの14ピットDACで、カスケード接続された2つの2×補間フィルタ、フェーズ・ロック・ループ(PLL)クロック乗算回路、および1.20ボルトのバンド・ギャップ電圧リファレンスを備えています。14ピットのDACは、フルスケール電流が外付けの抵抗で決定される2つの相補電流を出力します。エッジ・トリガの入力ラッチにラッチされた入力データは、14ピットのDACを更新する前に、補間フィルタでまず「4倍」に補間されます。PLLクロック乗算回路は、外部リファレンスから必要なクロックを内部的に生成します。生成されるクロックは、互いに同期がとられた1×、2×および4×のクロックです。AD9774は、最高で32MSPSの入力データ・レートをサポートしますが、これは128 MSPSのDAC更新レートに相当します。

AD9774のアナログ・セクションとディジタル・セクションは、2.7 Vから5.5 Vの範囲にわたって動作する個別の電源入力(つまり AVDDとDVDD)を備えています。PLLクロック乗算回路には、同様な動作レンジを持った、これとは別の電源入力(つまりPLLVDD)が備わっています。ノイズと歪みについて最適な性能を維持するためには、PLLVDDをDVDDと同じ電圧レベルに保ちます。

図22.機能ブロック図

14ビットのDACの手前にあるのは、55タップおよび23タップの ハーフバンド対称FIRトポロジーに基づく、カスケード接続された 2つの2×ディジタル補間フィルタ段です。エッジ・トリガのラッチ は、CLKINの立上りエッジで入力をラッチするために使用されています。これらのフィルタの複合周波数応答とインパルス応答については、図2aと図2bに示しました。表 と表 は、それぞれのフィルタ段に関する理想的なフィルタ係数のリストです。この補間フィルタは、基本的に、DACに対する入力データ・レートをオリジナルの入力データ・レートの4倍に上げ、それと同時にオリジナルの入力データ・レートに関連するイメージの大きさを縮小します。

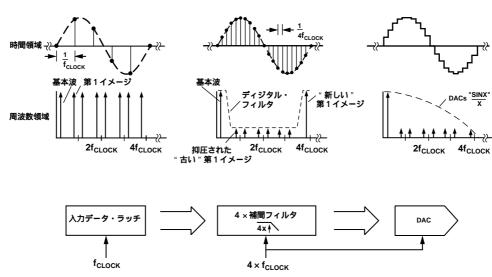

図23は、ディジタル補間フィルタに印加される前後での離散時間正弦波信号の周波数および時間領域を一例で表していますが、これを見れば補間フィルタを用いる利点は明らかでしょう。DACの入力データ・レートの倍数の近傍には、サンプリングの理論からも予想されるように、正弦波信号のイメージが現れます。こういった好ましくないイメージは、DACのsin(x)/(x)ロール・オフ応答によって修正されるものの、再生DACの出力にも現れます。

多くの帯域制限アプリケーションにおいては、DACの出力側にアナログ・フィルタを使用してこれらのイメージを抑圧する必要があります。このアナログ・フィルタは、通常、希望する基本波と第1イメージの近接度および必要とするイメージの抑圧度に応じて複雑なものとなります。このアナログ・フィルタの複雑性に加わえて、DACのsin(x)/x応答を補償する必要もあります。

図23を参照すると、補間後の高くなったDACデータ・レートに関連する"新しい"第1イメージは、入力信号から離れる方に"追い込まれて"いるのがわかります。補間前の低いDACデータ・レートに関連する"古い"第1イメージは、ディジタル・フィルタによって抑圧されています。この結果、アナログ再生フィルタの遷移帯域が広がり、それによってアナログ・フィルタの複雑性が抑えられます。さらに、有効通過帯域(つまりDCからf<sub>cLock</sub>/2まで)にわたってのsin(x)/xロール・オフも飛躍的に抑えられます。

AD9774には、必要なクロック、つまりエッジ・トリガのラッチ、補間フィルタおよびDACが用いる、互いに同期された $1 \times .2 \times$  および $4 \times 0$ クロックを内部的に生成するPLLクロック乗算回路が備わっています。PLLクロック乗算回路は、通常、リファレンス・ソースとして入力データ・クロックCLKINを受入れます。 これに代えて、CLK4  $\times$  IN経由で外部の $4 \times$  クロックを使用するように構成することも可能です。 PLLDIVIDE、 VCO IN/EXT、 PLLENABLE、 およびPLLLOCKは、PLLクロック発生器で使用されるコントロール入力または出力です。動作の詳細については、「PLLクロック乗算回路の動作」のセクションを参照してください。

図23. ディジタル補間フィルタの時間および周波数領域の例

AD9774のディジタル・セクションにも、これらとは別のコントロール入力および出力が備わっています。SLEEP入力とSNOOZE入力は、それぞれ異なる省電力モードを提供しますが、これについては、「スリープとスヌーズ」のセクションで説明します。またOVERR出力は、ディジタル補間フィルタのオーバーフローを示します。

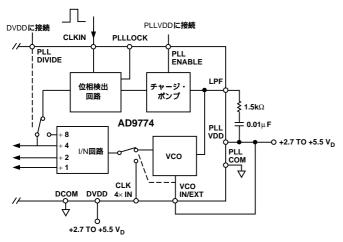

# PLLクロック乗算回路の動作

クロック、つまりエッジ・トリガのラッチ、補間フィルタおよび DACが必要とする、互いに同期された1×、2×および4×のクロックを内部的に生成するフェーズ・ロック・ループ(PLL)クロック 乗算回路は、AD9774の動作固有の回路です。図24は、PLLクロック 乗算回路の機能ブロック図を示し、これを参照すると、この回路には、位相検出回路、チャージ・ポンプ、電圧制御発振回路(VCO)、1/N回路およびいくつかのコントロール入出力が備わっています。この回路は、外部からCLKINまたはCLK4×INに印加可能な2つのリファレンス・クロックのいずれか一方を使用して、AD9774に必要な内部クロックを生成します。PLLENABLEとVCO IN/EXTは、アクティブ・ローのコントロール・入力で、それぞれチャージ・ポンプとVCOをイネーブルにするために使用します。

ノイズと歪みについて最適な性能を維持するためには、PLLVDDとDVDDを類似の電圧レベルに保ちます。PLLVDDに個別の電源を用意できないときは、図41に示したようなLCフィルタ回路を使用して、PLLVDDをDVDDに接続します。

多くのアプリケーションでは、図24に示したようなデータ入力レートで動作するリファレンス・クロックを選択することになります。この場合、外付けのクロック・ソースをCLKINに接続し、PLLENABLEとVCO IN/EXTをPLLVDDに接続すれば、PLLクロック乗算回路を完全に動作させることができます。ただしCLKINは、図1に示したタイミング条件を厳守していなければなりません。LPFからPLLVDDに向って直列に介挿された1.5 k の抵抗と0.01 μ Fのセラミック・キャパシタは、PLLの位相ノイズ対セトリング/アクィジション時間特性を最適化するために必要です。PLLLOCKは、アクティブ・ハイのコントロール出力で、システムのパワー・アップ時にこれをモニタすれば、PLLがCLKINに確実に"ロック"されたことを知ることができます。PLLDIVIDEは、PLLの「ロック・イン"レンジをプリセットするために使用します。CLKINが10MHzを超えるときはDVDDに接続し、10MHz以下のときはDCOMに接続します。

図24. CLKINを使用するPLLクロック乗算回路

入力データ・レートの4倍(つまり4×)で動作するシステム・クロックをすでに備えているアプリケーションの場合、それをPLLクロック乗算回路のリファレンス・ソースとして使用することも考えられます。ただし、複数のAD9774デバイスを正確に同時に更新する必要のあるアプリケーションでは、マスタの4×クロックの生成を考慮するとよいかもしれません。その場合、図25に示したように、クロック・ソースをCLK4×INに印加するとともに、PLLENABLEとVCOIN/EXTをPLLCOMに接続してPLLを部分的にディセーブルします。1/N回路はイネーブルの状態に残されるので、1×および2×の内部クロックが生成されます。LPFは、この部分のPLLがディセーブルになっているので開放しておきます。

図25. CLK4×INを使用するPLLクロック乗算回路

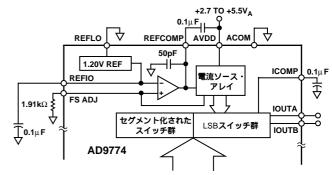

#### DAC**の動作**

14ビットのDACを、1.2 Vのリファレンスおよびリファレンス・コントロール・アンプとともに図26に示しました。このDACは、最大20 mAのフルスケール電流I<sub>OUTFS</sub>を供給する能力があるラージPMOS電流ソース・アレイを備えています。このアレイは、31の等しい電流に等分されて、上位5ビット(5 MSB)に割当てられます。続く4ビット、つまり中間ビット群は、それぞれがMSBのビット電流の1/16の値を持った15の等しい電流ソースを構成します。残る下位ビット群は、中間ビット群の電流ソースの2値重み付け関数になります。これらの電流ソースは、すべてPMOS差動電流スイッチを通じて2つの出力ノードの一方もしくは他方(つまりIOUTAまたはIOUTB)に切換え接続されます。R-2Rはしご型回路に代えて、中間ビット群と下位ビット群に電流ソースを割り当てることで、マルチトーンあるいは低振幅信号に対する動的性能が強化されるとともに、DACの出力インピーダンスを高く(つまり、100 k )維持しておくことが容易になります。

図26. 内蔵DAC、1.2 Vのリファレンスおよび リファレンス・コントロール回路のプロック図

フルスケール出力電流は、リファレンス・コントロール・アンプによって調整され、外付けの抵抗R<sub>SET</sub>を用いて2 mAから20 mAの範囲でセットすることができます。この外付けの抵抗は、リファレンス・コントロール・アンプおよび電圧リファレンスREFIOの両方との組み合わせで、リファレンス電流I<sub>REF</sub>を設定し、このリファレンス電流I<sub>REF</sub>は、所定の倍数にミラーリングされてセグメント化された電流ソースに与えられます。フルスケール電流I<sub>OUTFS</sub>は、I<sub>REF</sub>の値のちょうど32倍になります。

# DAC**の伝達関数**

AD9774は、相補関係にある電流IOUTAおよびIOUTBを出力します。すべてのビットがハイのとき(つまりDAC CODE = 16383)、IOUTAはほぼフルスケールの電流出力I<sub>OUTFS</sub>になり、その相補電流IOUTBはゼロになります。IOUTAとIOUTBに現れる電流出力は、入力コードとI<sub>OUTES</sub>の関数になり、次式で表すことができます。

$$IOUTA = (DAC\ CODE/16384) \times I_{OUTFS}$$

(1)

IOUTB = (16383 - DAC CODE ) 16384

$$\times I_{OUTFS}$$

(2)

ここで、DAC CODEは0から16383(10進数表現)までの値です。 すでに説明したように $I_{OUTFS}$ は、電圧 $V_{REFIO}$ と外付けの抵抗 $R_{SET}$ によって定格値に設定されるリファレンス電流 $I_{REF}$ の関数となります。 この関係は、次の式で表すことができます。

$$I_{OUTFS} = 32 \times I_{REF} \tag{3}$$

$$zz\overline{c}, I_{REF} = VR_{EFIO}/R_{SET}$$

(4)

2つの電流出力は、一般に直接またはトランスを経由した抵抗負荷のドライブに使用されます。DC結合が必要な場合は、IOUTAとIOUTBにアナログ共通ベースACOMに接続された整合抵抗負荷R<sub>LOAD</sub>を直接接続します。ただしこのR<sub>LOAD</sub>は、IOUTAまたはIOUTBから見た、50 または75 で両端が終端されたケーブルに等価な負荷抵抗を表しています。IOUTAとIOUTBに現れるシングルエンド電圧出力は、単純に次式で表されます。

$$V_{OUTA} = IOUTA \times R_{LOAD}$$

(5)

$$V_{OUTB} = IOUTB \times R_{LOAD} \tag{6}$$

ここで、歪みおよび線形性に関して所定の性能を維持するために、 $V_{OUTA}$ と $V_{OUTB}$ のフルスケール値が指定の出力コンプライアンス・レンジ内に収まるように注意します。

IOUTAとIOUTBの間の差動電圧V<sub>DIFF</sub>は、次のようになります。

$V_{DIFF}$  = (IOUTA - IOUTB)  $\times R_{LOAD}$  (7)

この式に前式を代入し、IOUTA、IOUTBおよびI<sub>REF</sub>を消去すると、 V<sub>DIFF</sub>の式が次のようになります。

$$V_{DIFF}$$

={(2 DAC CODE - 16383 )/16384 )/

(32  $R_{LOAD}/R_{SET}$  )×  $V_{REFIO}$  (8)

最後に示した2つの式から、AD9774を差動的に動作させることの利点が浮かび上がります。第1は、差動的な動作によって、ノイズ、歪みおよびDCオフセットといったIOUTAとIOUTBに関連する同相誤差ソースが相殺されることです。第2は、差動コード依存の電流およびそれによって得られる電圧 $V_{DIFF}$ が、シングルエンド電圧出力(つまり $V_{OUTA}$ または $V_{OUTB}$ )の2倍の値になり、負荷に対する信号電力が2倍になることです。

なお、AD9774のシングルエンド(VOUTAおよびVOUTB)または 差動出力( $V_{DIFF}$ )に関するゲイン・ドリフト温度特性は、式8に示した比率で表される関係に応じて $R_{SET}$ と $R_{LOAD}$ に温度追従抵抗を選択することによって向上させることができます。

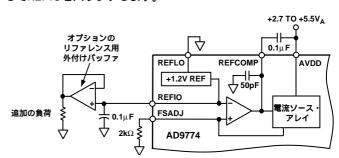

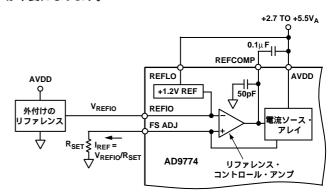

# リファレンスの動作

AD9774には、1.20 Vのパンドギャップ・リファレンスが内蔵されていますが、それをディセーブルして外部リファレンスを使用することも容易です。REFIOは、内蔵リファレンスが選択されているか外部リファレンスが選択されているか外部リファレンスが選択されているかによって「入力」または「出力」として機能します。 図27に示すようにREFLOがACOMに接続されているときは、内蔵リファレンスがアクティブになり、REFIOから1.20 Vが出力されます。この場合、REFIOとREFLOの間に容量が0.1 μ F以上のセラミック・チップ・キャパシタを接続して、内蔵リファレンスの補償を行う必要があります。負荷を追加しなければならないときは、入力パイアス電流が100 nA未満のアンプを外付けしてREFIOをバッファします。

図27.内蔵リファレンスを使用する構成

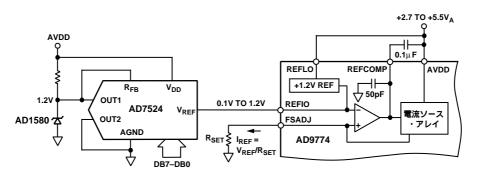

内蔵リファレンスは、REFLOをAVDDに接続すればディセーブルすることができます。その場合、図28に示すように、外部リファレンスをREFIOに印加します。外部リファレンスとしては、固定電圧を用いて精度とドリフト性能を向上することもできれば、可変リファレンス電圧によりゲインをコントロールすることもできます。外部リファレンスを用いた場合は、内蔵リファレンスがディセーブルされ、REFIOの高い入力インピーダンス(つまり1 M )が外付けのリファレンスの負荷を最小化するので、0.1 μ Fの補償キャパシタが不要になります。

図28.外部リファレンスを使用する構成

# リファレンス・コントロール・アンプ

AD9774は、DACのフルスケール出力電流 $I_{OUTFS}$ の調整に使用される内蔵コントロール・アンプも備えています。このコントロール・アンプは、図28に示したようにV-Iコンパータで、電流出力 $I_{REF}$ は、式4で表される $V_{REFIO}$ と外付けの抵抗 $R_{SET}$ の比によって決定されます。 $I_{REF}$ は、式3で示されるように、所定の倍数にコピーされてセグメント化された電流ソース全体に与えられます。

コントロール・アンプでは、IREFを62.5 μ Aから625 μ Aの範囲で設定することにより、2 mAから20 mAにわたる広い範囲(10:1)で IOUTESを調整することができます。IOUTESの調整間隔が広いと、各種の適用上の利点が生まれます。第1の利点は、IOUTESと比例関係にあるAD9774の消費電力に直接に関係します(「消費電力」のセクションを参照してください)。第2の利点は、20 dB調整に関係し、システム・ゲインをコントロールする上で役立ちます。

R<sub>SET</sub>を固定にしてI<sub>REF</sub>を変化させる方法は2とおりあります。第1 の方法は、内蔵リファレンスをディセーブルして、1.25 Vから0.10 VのREFIOのコンプライアンス・レンジにわたってその同相電圧を変化させる方法で、単一電源システムに適しています。REFIOが単一電源アンプまたはDACによってドライブできるので、R<sub>SET</sub>が固定であってもI<sub>REF</sub>を変化させることができます。REFIOの入力インピーダンスが約1 M であることから、電圧モード・トポロジーで構成された簡単な低価格R-2Rはしご型DACを使用してゲインをコントロールすることが可能になります。AD7524および外付けの1.2 VリファレンスAD1580を使用したこの回路の例を図30に示します。

第2の方法は、REFIOの同相電圧を固定し、アンプを経由して $R_{\rm SET}$ に印加する外部電圧 $V_{\rm GC}$ により $I_{\rm REF}$ を変化させる方法で、2電源システムで使用されています。この方法の一例を図29に示しましたが、ここでは内蔵リファレンスを用いてコントロール・アンプの同相電圧を1.20 Vにセットしています。外部電圧 $V_{\rm GC}$ は、ACOMを基準にして1.2 Vを超えないようにします。 $R_{\rm SET}$ の値は $I_{\rm REFMAX}$ と $I_{\rm REFMIN}$ がそれぞれ62.5  $\mu$  Aから625  $\mu$  Aの範囲を出ないように設定します。この $R_{\rm SET}$ の値は、図29に示した関係式を使用して決定することができます。

図29.2電源ゲイン・コントロール回路

### アナログ出力

AD9774が生成する2つの相補電流出力IOUTAとIOUTBは、シングルエンドまたは差動動作用に構成することができます。このIOUTAとIOUTBは、「DACの伝達関数」で説明した式5から式8までの式で示されるように、負荷抵抗R<sub>LOAD</sub>を介して相補関係のあるシングルエンド電圧出力V<sub>OUTA</sub>とV<sub>OUTB</sub>に変換できます。また、トランスまたは差動アンプ構成を使用してV<sub>OUTA</sub>とV<sub>OUTB</sub>の間の差動電圧V<sub>DIFF</sub>をシングルエンド電圧に変換することも可能です。

図31は、セグメント化された電流ソースのそれぞれに関係づけられたPMOS差動電流スイッチをパラレルに組み合わせた構成を持つAD9774の等価アナログ出力回路を示しています。IOUTAとIOUTBの出力インピーダンスは、PMOSスイッチの等価なパラレルの組み合わせによって決定され、通常は100 k で、パラレルに5 pFの容量を有します。PMOSデバイスの特性から、出力インピーダンスは出力電圧(つまりVoutaおよびVouta)にもわずかに依存し、さらに限られますが、アナログ電源電圧AVDDとフルスケール電流Ioutesにも依存します。出力インピーダンスの信号依存性は、DC非線形性とAC線形性(つまり歪み)の原因となる可能性がありますが、所定の注意を怠らなければこの影響を制限することができます。

図31.等価アナログ出力回路

またIOUTAとIOUTBには、負と正の電圧コンプライアンス・レンジがあります。負出力のコンプライアンス・レンジ、-1.0 Vは、CMOSプロセスのブレークダウン限界によって設定されます。この最大限界を超えて動作させると、出力段のブレークダウンを招き、AD9774の信頼性に影響が現れることがあります。

図30.単一電源ゲイン・コントロール回路

REV.0 - 13 -

正出力のコンプライアンス・レンジは、フルスケール出力電流 I<sub>OUTES</sub>にわずかに依存します。これによって、I<sub>OUTES</sub> = 20 mAに対応する定格の1.25 VからI<sub>OUTES</sub> = 2 mAに対応する1.00 Vにわずかな劣化が現れます。正のコンプライアンス・レンジを超えて動作させると、出力信号のクリッピングを招き、線形性と歪みに関するAD9774の性能が著しく損なわれます。

最適なDC線形性を必要とするアプリケーションの場合、I-Vオペアンプ構成を介してIOUTAおよび/またはIOUTBを仮想グラウンドに維持します。IOUTAおよび/またはIOUTBを仮想グラウンドに維持することによって、AD9774の出力インピーダンスが固定され、線形性に対するその影響が格段に小さくなります。しかしながら、I-Vオペアンプの制限によって必ずしも最適な歪み性能が得られるとは限りません。AD9774のINL/DNLスペックが、この方法でIOUTAを使用して測定される点に注意してください。さらに、これらのDC線形性のスペックは、2.7 Vから5.5 Vの指定電源電圧範囲にわたって実質的な影響を受けません。

差動出力またはシングルエンド出力の構成でIOUTAとIOUTBの電圧出力のスイングを小さくしてAD9774を動作させると、出力インピーダンスの信号依存度が小さくなるので、歪み性能を向上することができます。IOUTAとIOUTBの電圧コンプライアンス・レンジは - 1.0 Vから + 1.25 Vに及びますが、最適歪み性能は、IOUTAとIOUTBの最大のフルスケール信号が約0.5 Vを超えないときに得られます。センター・タップを接地させた適切なトランスを使用すれば、IOUTAとIOUTBの電圧スイングを抑えたまま、各種の負荷に必要な電力と電圧のレベルをAD9774から取り出すことができます。差動出力またはシングルエンド出力の構成を必要とするDC結合のアプリケーションでは、これに応じてR<sub>LOAD</sub>を調整します。各種出力構成の例については、「AD9774の適用」のセクションを参照してください。

歪みとノイズに関するAD9774の性能の改善がもっともよく現れるのは、差動出力構成を使用するときです。IOUTAとIOUTBの同相誤差ソースは、トランスまたは差動アンプの同相電圧除去によって実質的に低減されます。これらの同相誤差ソースは、偶数倍(同相)の歪み成分とノイズからなります。歪み性能の向上は、再生波形の周波数成分が増加し、または振幅が減少するとき、あるいはその両方があるとき、さらに顕著になります。

歪みとノイズに関するAD9774の性能は、フルスケールの電圧セッティングI<sub>OUTFS</sub>だけでなくアナログとディジタルの電源にもわずかに依存します。5.0 Vのアナログ電源で動作させた場合は、PMOS電流ソースと差動スイッチのためのヘッドルームが最大に確保され、歪み性能が向上します。I<sub>OUTFS</sub>は、2 mAと20 mAの間で設定可能ですが、I<sub>OUTFS</sub>として20 mAを選択すれば、歪みとノイズの性能が最高になります。 AD9774のノイズ性能は、ディジタル電源(DVDD) 出力周波数に影響され、クロック・レートが高くなると増加します。AD9774を3 Vと3.3 Vの間の低いロジック・レベルで動作させれば、オンチップ・ディジタル・ノイズの量がわずかながら低下します。

以上をまとめると、歪みとノイズに関するAD9774の性能は、以下の条件で最適化されます。

- (1)差動動作。

- (2) IOUTAとIOUTBの正の電圧スイングを+0.5 Vに制限。

- (3) IOUTFSを20 mAに設定。

- (4) アナログ電源(AVDD)を5.0 Vにセット。

- (5) ディジタル電源(DVDD)とフェーズ・ロック・ループ電源 (PLLVDD)を適切なロジック・レベルで3.0 Vから3.3 Vまでに

#### 铅定

なお、上記の動作条件の下でAD9774のAC性能が特性決定される 点に注意してください。

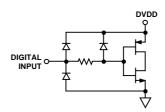

# ディジタル入力

AD9774のディジタル入力は、14本のデータ入力ピンと1本のクロック入力ピンからなります。14ビット・パラレルのデータ入力は、標準の正の2値コード化方式に従い、DB13が最上位ビット(MSB)、DB0が最下位ビット(LSB)になります。すべてのデータ・ビットが論理値1のとき、IOUTAにフルスケール出力電流が現れます。IOUTBには、入力コードに対する補数の関係でフルスケール電流を分割した電流が現れます。

ディジタル・インターフェースは、エッジ・トリガのマスタ・スレープ・ラッチを使用して具体化され、最高32 MSPSまでのクロックと入力データのレートをサポートする設計になっています。このクロックは、図1に示した所定のラッチ・パルス幅を満足していれば、どのようなデューティ・サイクルでも使用可能です。セットアップ時間およびホールド時間もまた、所定の最小時間の条件に適合している限り、クロック・サイクル内で変化させることができます。

ディジタル入力はCMOS互換で、論理値のスレッショルド $V_{THRESHOLD}$ は、正のディジタル電源電圧(DVDD)の約1/2の値に設定されます。これを式で表すと次のようになります。

$$V_{THRESHOLD} = DVDD/2(\pm 20\%)$$

AD9774に内蔵されているディジタル回路は、ディジタル電源の全域、つまり2.7 Vから5.5 Vまでの範囲にわたって動作することができます。この結果、TTLドライバの最高ハイ・レベル電圧V<sub>OH(MAX)</sub>が扱えるようにDVDDがセットされているときは、ディジタル入力でTTLレベルを扱うことも可能になります。通常は3 Vから3.3 Vの間のDVDDで、ほとんどのTTLロジック・ファミリとの適正な互換性が確保されます。図32に、データとクロックが入力されるディジタル入力回路の等価回路を示します。

図32.等価ディジタル入力

AD9774は、最高32 MSPSで更新できることから、最適性能を得るためにはクロックとデータの入力信号の質が重要になります。ロジック・スイングと対応するディジタル電源(DVDD)を小さくしてAD9774を動作させれば、データのフィードスルーとオンチップのディジタル・ノイズを最小に抑えることができます。ディジタル・データ・インターフェース回路のドライバは、AD9774の最小セットアップおよびホールド時間の条件を満たすとともに、最低/最高入力ロジック・レベルのスレッショルドの条件を満たす必要があります。

伝播遅延の不整合を避けるため、ディジタル信号パスを短くし、ランレングスを整合させます。AD9774のディジタル入力とドライバ出力の間に値の小さい抵抗回路(20 から100 )を介揮すると、データのフィードスルーに影響するディジタル入力のオーバーシュートとリンギングの低減に効果があります。

外付けのクロック・ドライバ回路からAD9774に供給するクロック入力は、鋭いエッジを備えるとともに、最低/最高ロジック・レベルの条件に適合するジターの少ないものとします。鋭いクロック・エッジは、明らかな位相ノイズとして再生波形上に現れるジターを最小化するのに役立ちます。したがって、アプリケーションに適した最高速ロジック・ファミリからクロック入力をドライブするとよいでしょう。

# スリープ・モードとスヌーズ・モードの動作

AD9774には、出力電流をオフにして、2.7 Vから5.5 Vの定格電源 範囲と温度範囲にわたって電源電流を5 mA未満に抑えるスリープ 機能が備わっています。このモードは、SLEEPピンにロジック・レ ベルの"1"を印加することによりアクティブになります。AD9774 は、0.1 µ s以内にパワーダウンし、約6.4 µ sで復帰します。

スヌーズ・モードは、スリープ・モードのパワーアップ特性の使用が好ましくないときの代替省電力モードと考えてください。このモードは、SNOOZEピンにロジック・レベルの"1"を印加することによってアクティブになり、AD9774のディジタル・フィルタをディセーブルするだけですが、大きな省電力効果が得られます。なお、省電力効果の必要がない場合は、SLEEPピンとSNOOZEピンをともにDCOMに接続しておきます。

# 消費電力

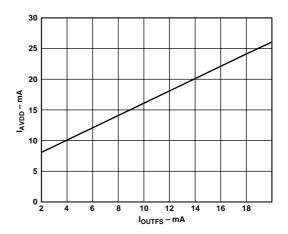

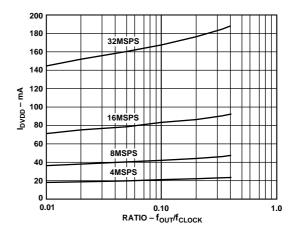

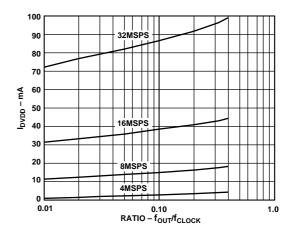

AD9774の消費電力P<sub>D</sub>は、いくつかの要素に依存し、これには(1)電源電圧AVDD、PLLVDD、およびDVDD、(2)フルスケール電流出力I<sub>OUTFS</sub>、(3)更新レートf<sub>CLOCK</sub>、および(4)再生済みのディジタル入力波形が含まれます。消費電力は、アナログ電源電流I<sub>AVDD</sub>およびディジタル電源電流I<sub>DVDD</sub>と直接的な比例関係があります。I<sub>AVDD</sub>は、図33に示すように、I<sub>OUTFS</sub>に正比例し、f<sub>CLOCK</sub>の影響は受けません。

これに対し、 $I_{DVDD}$ は、ディジタル入力波形、 $f_{CLOCK}$ 、およびディジタル電源DVDDの関数となります。図34と図35は、それぞれDVDD = 5 V、DVDD = 3 Vとした場合の各種の更新レートに関するフルスケール正弦波出力の比( $f_{OUT}/f_{CLOCK}$ )として $I_{DVDD}$ を示したグラフです。ここで、DVDDを5 Vから3 Vにすることによって、 $I_{DVDD}$ が1/2以下になることに注目してください。

(1)AVDD、PLLVDD、およびDVDD = +5 V、(2) $f_{CLOCK} > 25$  MSPS、かつ(3)周囲温度 > 70 という条件でAD9774を動作させなければならないアプリケーションの場合、ヒートシンクまたはサーマル・エポキシによる適切な温度管理が推奨されます。

# AD9774**の適用**

# 出力構成

以下、AD9774用の一般的な出力構成について説明します。ここでは、特に示さない限り、I<sub>OUTES</sub>が定格の20 mAに設定されているものとします。最適な動的性能を必要とするアプリケーションについては、差動出力構成が推奨されます。差動出力構成は、RFトランスまたは差動オペアンプのいずれかを用いて構成することができます。トランス構成は、最適高周波性能を提供し、AC結合を考慮したアプリケーションに奨められます。差動オペアンプ構成は、DC結合、バイポーラ出力、信号ゲインおよび/またはレベルのシフトを必要とするアプリケーションに適しています。

シングルエンド出力は、ユニポーラ電圧出力を必要とするアプリケーションに適しています。IOUTAおよび/またはIOUTBに概略

で整合された負荷抵抗R<sub>LOAD</sub>が接続されているとき、その結果として ACOMを基準にした正のユニポーラ出力電圧が得られます。これ は、DC結合、グラウンド基準の出力電圧を必要とする単一電源システムにより適した構成です。これに代えて、I-Vコンパータとしてアンプを構成すれば、それによりIOUTAまたはIOUTBを負のユニポーラ電圧に変換することができます。この構成では、IOUTAまたはIOUTBが仮想グラウンドに維持されることから、最良のDC線形性が得られます。

図33. I<sub>AVDD</sub>とI<sub>OUTES</sub>の関係

図34.I<sub>DVDD</sub>と比の関係 DVDD=5V

図35. I<sub>DVDD</sub>と比の関係 DVDD=3 V

REV.0 - 15 -

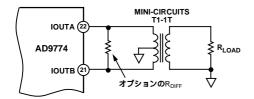

### トランスを使用した差動結合

図36に示すように、RFトランスを使用して差動信号からシングルエンド信号へ変換することができます。差動的に結合されたトランスの出力は、出力信号のスペクトル成分がトランスの通過帯域内に収まる場合に最適な歪み性能をもたらします。Mini-CircuitsのT1-1T等のRFトランスは、同相歪み(つまり偶数倍の高調波)と広い周波数帯域にわたるノイズの除去に優れた効果を発揮します。さらにこれによって電気的な絶縁が得られるだけでなく、負荷を2倍の電力で駆動することができます。異なるインピーダンス比を有するトランスを使用してインピーダンス整合をさせることも可能です。なおトランスが、AC結合のみに使用可能である点に注意してください。

図36.トランスを使用した差動結合

IOUTAとIOUTBに必要なDC電流パスを設けるために、トランスの1次側巻線のセンター・タップをACOMに接続しなければなりません。IOUTAとIOUTBに現れる相補電圧(つまり $V_{\rm OUTA}$ と $V_{\rm OUTB}$ )をACOMを中心にして対称にスイングさせ、AD9774の定格出力コンプライアンス・レンジ内に維持します。トランス出力が負荷 $R_{\rm LOAD}$ に接続されるアプリケーションでは、受動再生フィルタまたはケーブルを経由して差動抵抗 $R_{\rm DIFF}$ を挿入することができます。この $R_{\rm DIFF}$ は、トランスのインピーダンス比によって決定され、適正なソース終端を提供するので、VSWRが低くなります。ただし、信号電力の約1/2が $R_{\rm DIFF}$ で消費されます。

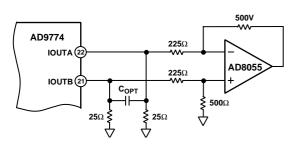

# オペアンプを使用した差動構成

図37に示すように、オペアンプを使用して差動信号からシングルエンド信号へ変換することもできます。AD9774には、25 の等しい2つの負荷抵抗R<sub>LOAD</sub>を接続します。IOUTAとIOUTBに現れる差動電圧は、差動オペアンプ構成を経由してシングルエンド信号に変換されます。IOUTAとIOUTBの間にキャパシタを追加すれば、ロー・パス・フィルタが構成され、それぞれは実際の極となります。このキャパシタの追加によって、DACの高いスルー出力によるオペアンプ入力の過負荷が防止されるので、オペアンプの歪み性能が向上するという効果も得られます。

図37.オペアンプを使用したDC差動結合

この構成の同相電圧除去は、通常、抵抗整合によって決定されます。この回路では、AD8047を使用した差動オペアンプ回路が構成されて、ある種の追加の信号ゲインがもたらされます。このオペアンプは、出力が約±1.0 Vとなることから、2電源で動作させる必要があります。オペアンプには、AD9774の差動性能の保持が可能で、かつ他のシステム・レベルの目的(コスト、消費電力等)に合致した高速のものを選択します。この回路を最適化する場合には、オペアンプの差動ゲイン、ゲイン・セッティング抵抗の値、およびフルスケール出力スイング能力を考慮する必要があります。

図38に示した差動回路は、単一電源システムに必要なレベル・シフトを提供します。この場合、AD9774とオペアンプの両方の正のアナログ電源となるAVDDが、AD9774の差動出力を中間の電源電圧(つまりAVDD/2)にレベル・シフトするためにも使用されます。AD8041は、このようなアプリケーションに適したオペアンプです。

図38. 単一電源のDC差動結合回路

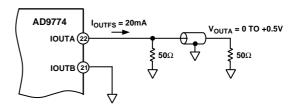

#### シングルエンドのバッファのない電圧出力

図39は、25 の等価負荷R<sub>LOAD</sub>を通って20 mAの定格フルスケール電流I<sub>OUTFS</sub>が流れることによって50 で両端が終端されるケーブルに、約0 Vから + 0.5 Vの範囲でユニポーラ出力を供給するときのAD9774の構成を示しています。この場合のR<sub>LOAD</sub>は、IOUTAから見た等価負荷抵抗を表します。未使用の出力(IOUTB)は、直接ACOMに接続しておくことができます。正のコンプライアンス・レンジが守られている限り、これとは異なる値のI<sub>OUTFS</sub>とR<sub>LOAD</sub>を選定することも可能です。このモードで憂慮される事項は、このデータ・シートの「アナログ出力」のセクションで説明した積分非線形性(INL)です。最適なINL性能を得るためには、シングルエンドのバッファ付き出力構成が推奨されます。

図39.0 V~ +0.5 Vのバッファのない電圧出力

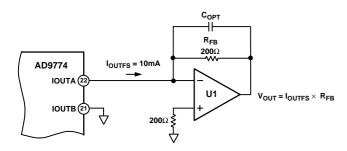

## シングルエンドのバッファ付き出力構成

図40に、バッファ付きのシングルエンド出力構成を示します。ここでは、オペアンプU1がAD9774の出力電流をI-V変換します。U1はIOUTA(またはIOUTB)を仮想グラウンドに維持するので、「アナログ出力」のセクションで説明したようにDACのINL性能に対する非線形出力インピーダンスの影響が最小になります。このシングルエンド構成からは、最良のDC線形性能が得られますが、U1のスルー性能によってDACの更新レートが高くなると、AC歪み性能が制限されることがあります。U1は、負のユニボーラ電圧を出力し、フルスケール出力電圧は、RFBとIOUTFSの単純な積になります。フルスケール出力は、IOUTFSおよび/またはRFBを調整してU1の電圧出力スイング能力内にセットします。IOUTFSを小さくするとシンクに必要なU1の信号電流が下ることから、これによってAC歪み性能の改善が得られることがあります。

図40.バッファ付きユニポーラ出力構成

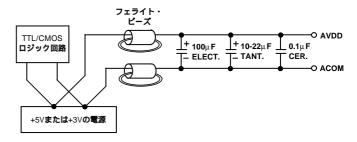

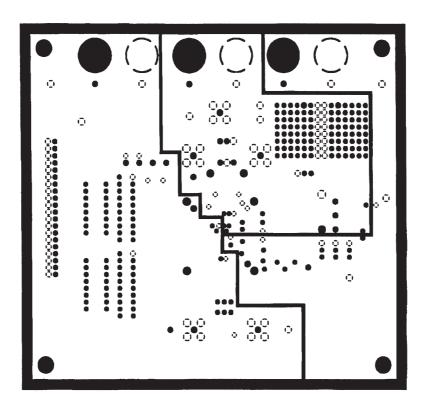

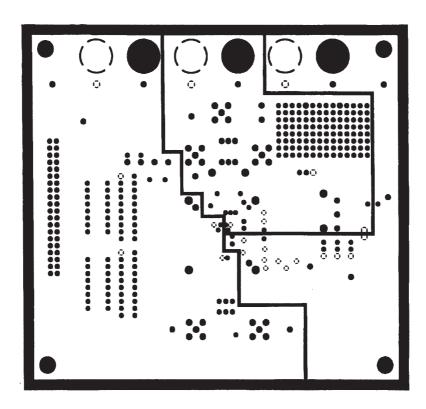

### 電源と接地に関する考察

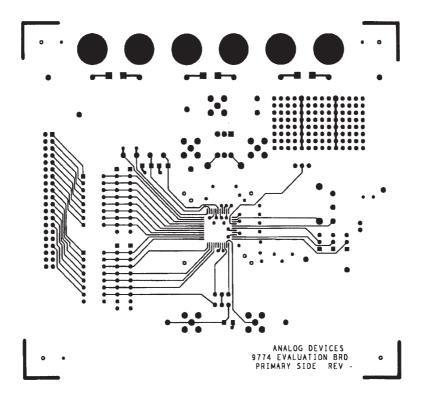

高速と高性能を同時に達成することが要求されるシステムでは、プリント回路基板設計の具体化と構成が回路設計と同程度に重要視されることが少なくありません。デバイス・セクション、配置およびルーティング、そして電源のバイパスと接地には適切なRFテクニックを使用する必要があります。図44~図49は、AD9774の評価ボード上に実装された推奨されるプリント回路基板の接地、電源および信号面のレイアウトを示しています。

適切な接地と減結合は、高速高分解能のシステムでは主要な考慮事項となります。AD9774は、システム内のアナログとディジタルの接地電流を最適に管理するためにアナログとディジタルに個別の電源ピンとグラウンド・ピンを備えることを特長とします。一般に、アナログ電源AVDDは、アナログ共通ベースACOMと切り離し、物理的に可能な限りチップに近付けます。同様に、ディジタル電源DVDDをDCOMと切り離し、フェーズ・ロック・ループ電源PLLVDDをPLLCOMと切り離します。

+5 Vまたは+3 Vの単一電源をアナログ、ディジタル電源およびフェーズ・ロック・ループ電源に使用する必要があるアプリケーションの場合、図41に示した回路を使用してクリーンなAVDDおよび/またはPLLVDDを生成することができます。この回路は、個別

の電源とリターン・ラインを備えた差動LCフィルタで構成されています。より低いノイズについては、低いESRタイプの電解コンデンサとタンタル・コンデンサを使用して達成することができます。

図41 . +5 Vまたは+3 Vの単一電源を用いるアプリケーション のための差動LCフィルタ

電源とグラウンドのノイズを低く維持することは、AD9774から 最適な結果を引き出す上で欠くことができません。適切に実装され た場合、グラウンド面が高速回路基板のホストとして機能し、電流 の伝達等のパイパス、シールドをもたらします。ミックスド・シグ ナル設計においては、ボードのアナログ部分とディジタル部分を互 いに離し、アナログ・グラウンド面はアナログ信号トレースをカ パーするエリアに限定し、ディジタル・グラウンド面はディジタル の相互接続をカパーするエリアに限定します。

DAC、リファレンスおよびその他のアナログ・コンポーネントのアナログ・グラウンド・ピンは、すべてアナログ・グラウンド面に直接接続します。最適性能を維持するため、2つのグラウンド面をDACの下側あるいはそれから1/2インチ以内の個所で、1/8インチから1/4インチの幅のパスを使って接続して下さい。グラウンド面は、重要な信号のパスの影響を受けないように、充分な注意を払う必要があります。ディジタル側のこの種の信号ラインとしては、DACに接続されるディジタル入力ラインを始め、すべてのクロック信号が挙げられます。アナログ側では、DAC出力信号ライン、リファレンス信号ラインおよび電源ラインがあります。

電源ラインのルーティングに広幅のパスや面を使用することも 推奨されています。これにより、部品に対する電源の直列インピー ダンスが低くなるだけでなく、適切なグラウンド面に対してある種 の"フリー"容量減結合が得られます。信号グラウンド・パスに外 来性の電圧降下を招かないように、電圧信号と電源のグラウンドの 相互接続は、慎重にレイアウトすることが非常に重要です。異なる 電流間の伝導パスの共有を最小限に抑えるため、すべての接続を短 くし、物理的に可能な限りパッケージに近い位置で直接行うことが 推奨されています。パスの長さが1インチを超える場合は、適切な 終端抵抗を備えたストリップ・ラインのテクニックを考慮する必要 があります。ただし、この抵抗の必要性と抵抗値は、使用するロ ジック・ファミリに依存します。

高速ミックスド・シグナル・プリント回路基板の実装と構成の さらに詳しい情報については、アナログ・デバイセズ社のアプリ ケーション・ノートAN-280およびAN-333を参照してください。

### マルチトーン性能の考察と特性決定

高速DACの周波数領域の性能は、伝統的に特定の出力周波数と更新レートで再生されたフルスケール(つまり0 dBFS)のシングル・トーン正弦波のスペクトル出力を解析することによって特性決定されています。この特性データは有用ですが、再生されたマルチトーンまたは拡散スペクトル波形に関するDACの性能を反映させるためには不充分なことが少なくありません。実際、帯域制限波形の最大定格周波数(つまりf<sub>H</sub>)でフルスケールのシングル・トーンを使用したDACスペクトル性能の評価では、一般にその波形についてのDACの"最悪ケースの"性能が示されます。時間領域においては、このフルスケール正弦波が、この帯域制限信号で可能な最低のピーク対実効値の比、つまり波高率(V<sub>PFAK</sub>/Vrms)を表します。

1.0000 0.8000 0.4000 0.2000 -0.2000 -0.2000 -0.4000 -0.6000 -0.8000 -1.0000

図42b.マルチトーン波形の時間領域の"スナップショット"

しかしながら、マルチトーンには、指定の帯域にわたって波形のスペクトル・エネルギが拡散する拡散スペクトルあるいはQAM波形と呼ばれる固有の性質があり、単純な正弦波の場合に比較すると、ピーク対実効値の比が高くなります。再生波形のピーク対平均値の比が増加すると、信号エネルギの増加量がDACの中央スケール値近傍に集中します。図42aは、帯域制限マルチトーン・ベクトル(8トーン)の一例ですが、ナイキスト帯域(つまりfclock/4)の1/2近

傍に集中しています。正弦波のピーク対実効値の比は3 dBですが、この特定のマルチトーン・ベクトルのピーク対実効値の比は13.5 dBになります。図43bに示したこの再生マルチトーン・ベクトルの時間領域の"スナップショット"では、中央スケール値の周囲ほど信号成分が多くなっていることがわかります。つまり所定の変調スキームに関して、相互変調歪みを低く抑え、満足のゆくキャリア対ノイズの比を維持する上で"小スケール"でのDACの動的線形性と静的線形性は極めてきわどいものになります。

DACの小規模な線形性能は、ゲイン・コントロールのため、あるいは"逆歪み"信号調整のためにさらにダイナミック・レンジを必要とするアプリケーションでも重要な考慮事項となります。たとえば、充分なダイナミック・レンジを有するDACを使用すれば、再生信号のゲイン・コントロールを余分に得ることができます。このゲインは、DACのディジタル入力ワードを左または右にシフトするだけで、6dBステップでコントロールすることができます。別のアプリケーションとしては、DACのディジタル入力信号を意図的に歪ませて信号チェーン内の続くアナログ・コンポーネントに関係する非線形性を補償するものがあります。たとえば、電力アンプに関連する信号圧縮は、DACのディジタル入力に対してその電力アンプの逆非線形伝達関数を用いた逆歪みを適用することによって補償することができます。いずれのケースでも、より低い信号レベルにおけるDACの性能を慎重に評価する必要があります。

フルスケールのシングル・トーンは、DACが有する歪みに関連したすべての動的および静的非線形性、つまりSFDR性能を導きます。この再生されたフルスケールのシングル・トーン波形の周波数が増加すると、どのDAC(たとえばAD9774)でも動的非線形性が支配的になり、それがSFDR性能におけるロール・オフをもたらします。しかしながらAD9774(および他のTxDAC)では、下位のビット電流のセグメント化にR-2Rはしご型を採用するほとんどのDACと違って、シングル・トーンの振幅がフルスケール・レベルから下ったときに歪み性能が改善されています。信号レベルが低下したときの歪み性能におけるこの改善は、図4~図15に示したように、異なる振幅(たとえば0dBFS、-6dBFS、-12dBFS)の周波数とサンプリング・レートについてSFDR性能を比較すると明らかになります。この整然とした"小スケール"線形性をDACの伝達関数の全域にわたって維持することは、卓越したマルチトーン性能を維持する上でも重要です。

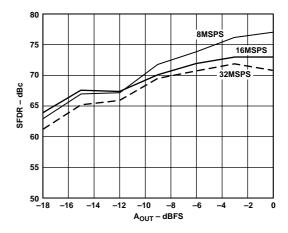

DACのマルチトーン性能の特性決定はアプリケーション固有に傾く傾向にありますが、シングル・トーン、デュアル・トーンおよびマルチトーンのテスト・ベクトルについてDACがスイープする電力(つまり振幅)の性能を各種のクロック・レートとキャリア周波数で評価することによって、DACの潜在的な性能をより深く知ることができます。フルスケール(つまり0dBFS)から3dB間隔で振幅が減衰する特定の波形を再生すれば、各種のクロック・レートでDACを評価できます。それぞれの特定波形について、テストのクロック・レートを変えて得られたSFDR(ナイキスト帯域外)性能と振幅の関係を示すグラフを図19と図20に示します。ここで、いずれのグラフでもキャリア対クロックの比が一定に保たれていることに注意してください。

マルチトーンのテスト・ベクトルは、図42aに示したように、それぞれが定義済み帯域内のチャンネルを表す等振幅、等間隔の複数のキャリアで構成されます。多くの場合、1ないし複数のトーンが除去されることから、DACの相互変調歪み性能を評価することができます。DACに関連する非線形性はスプリアス・トーンを生成し、その一部が"空の"チャンネルに落ちることがあるため、チャンネルのキャリア対ノイズの比が制限されます。注目帯域外に落ちるそのほかのスプリアス成分も、システムのスペクトル・マスクとフィルタリングの必要条件に応じて重要になることがあります。

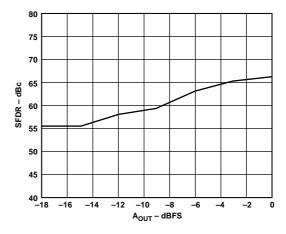

この特定のテスト・ベクトルは、fcLOCK/16の通過帯域でナイキスト帯域の1/2(つまりfcLOCK/4)近傍に集中しています。さらに低い領域(たとえばfcLOCK/10)にトーンを集中させると性能が向上し、より高い領域(たとえばfcLOCK/2.5)に集中させると性能が低下します。図43aは、32 MSPSにおけるSFDR対振幅の関係をナイキスト周波数まで示したグラフで、図43bはテスト・ベクトルの通過帯域内のSFDR対振幅の関係を示したグラフです。DACのマルチトーン性能を評価する場合、性能のばらつきを判定するため、まったく同じ条件で複数のユニットをテストすることも推奨されます。

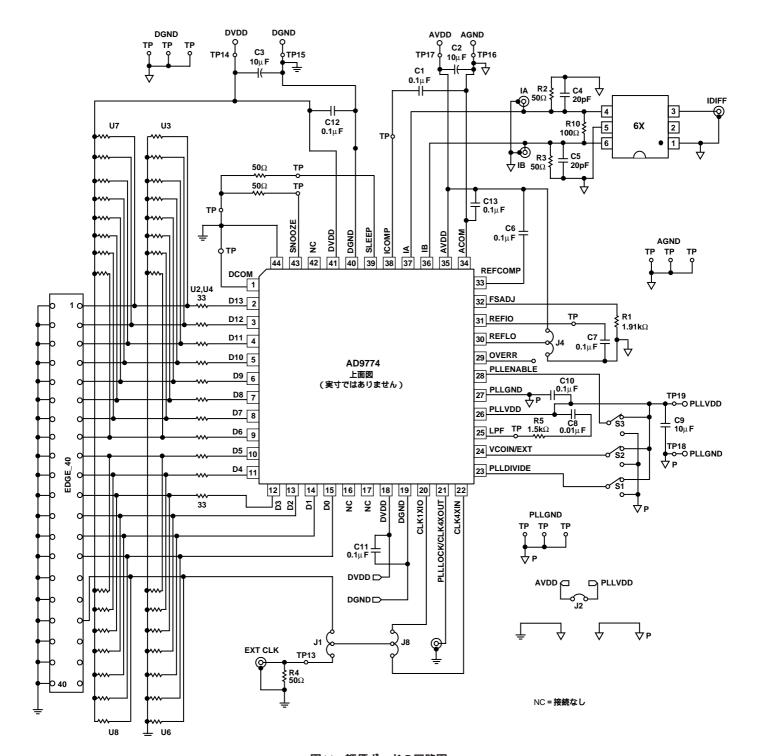

#### AD9774**評価ボード**

# 全般説明

AD9774-EBは、AD9774 14ピットDAコンパータ用の評価ボードです。慎重なレイアウトと回路設計は、試作エリアとともに、高分解能、高速変換を必要とする信号再生アプリケーションにおいてAD9774を効果的に評価する容易な手段をユーザに提供します。

ユーザは、このボードを用いて各種の構成でAD9774を動作させられる柔軟性が得られます。ディジタル入力は、適切な負荷終端のための抵抗回路を追加するオンボードのオプションとともに、各種のワード発生器から直接ドライブできる設計になっています。 AD9774で内蔵リファレンスまたは外部リファレンスを用いた動作、スリープまたはスヌーズ・モードの省電力機能の試験にも対応しています。

**図**43a . マルチトーンのSFDR 対 A<sub>OUT</sub>の関係 @32 MSPS(ナイキスト周波数まで)

**図**43b . マルチトーンのSFDR 対 A<sub>OUT</sub>の関係 @32 MSPS(マルチトーンの通過帯域内)

REV.0 - 19 -

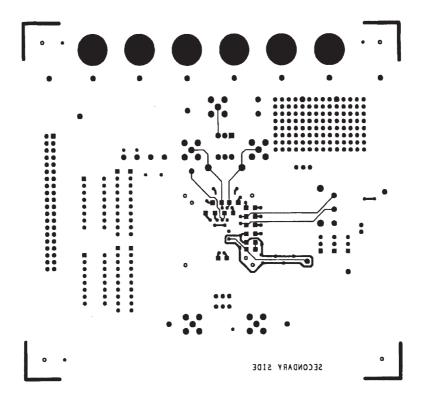

図44.評価ボードの回路図

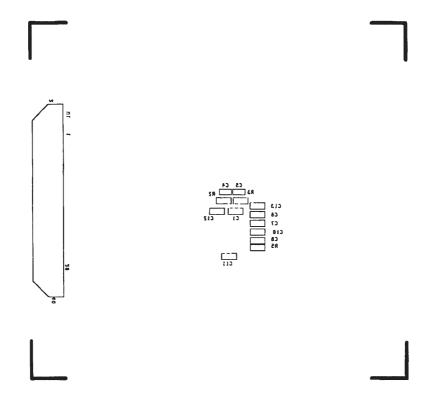

図45.シルクスクリーン・レイヤ 上面

図46.コンポーネント側のPCBレイアウト(レイヤ1)

REV.0 - 21 -

図47. グラウンド面のPCBレイアウト(レイヤ2)

図48.電源面のPCBレイアウト(レイヤ3)

- 22 - REV.0

図49. ハンダ付け側のPCBレイアウト(レイヤ4)

図50.シルクスクリーン・レイヤ 底面

REV.0 - 23 -

外形寸法 サイズはインチと(mm)で示します。 44ピン・メトリック・クワッド・フラットパック (S-44)