# 8ビット、500 MSPS、1.8 V A/Dコンバータ

AD9286

## 特長

1.8 V 単電源動作

200 MHz 入力、500 MSPS で SNR = 49.3 dBFS 200 MHz 入力、500 MSPS で SFDR = 65 dBc

低消費電力: 500 MSPS で 315 mW

インターリーブ・クロック機能を内蔵

リファレンス電圧とトラック・アンド・ホールドを内蔵

各チャンネル 1.2 V p-p のアナログ入力範囲

帯域幅 500 MHz の差動入力

LVDS 準拠デジタル出力

リファレンス電圧とサンプル・アンド・ホールド回路を内蔵

DNL: ±0.2 LSB

シリアル・ポート制御オプション

インターリーブ・クロック・タイミング調整

オフセット・バイナリ、グレイ・コード、または2の補数デー

タ・フォーマット

オプションのクロック・デューティ・サイクル・スタビライザ 選択可能なデジタル・テスト・パターン発生機能を内蔵

ピン設定可能なパワーダウン機能

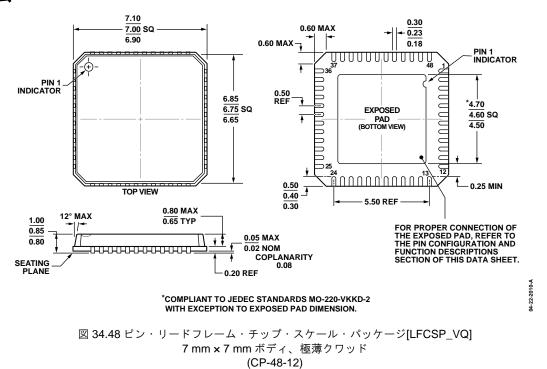

48 ピン LFCSP を採用

## アプリケーション

バッテリ駆動の計装機器 ハンドヘルド型スコープ・メータ 低価格デジタル・オシロスコープ OTS: ビデオ・オーバー・ファイバ

### 概要

AD9286 は、低価格、低消費電力、使い安さについて最適化され た 8 ビットのモノリシック・サンプリング A/D コンバータ (ADC) で、インターリーブ動作をサポートしています。各 ADC は、最 大 250 MSPS の変換レートで動作し、優れたダイナミック性能を 持っています。

AD9286 は 1 つのサンプル・クロックを入力して、内蔵クロック 分周器を使って、2つの ADC コアをタイム・インターリーブして (各々はクロック周波数の 1/2 で動作)定格の 500 MSPS を実現して います。SPI を使用して、各 ADC のサンプリング・エッジのタイ ミングを正確に調整できるため、イメージ・スプリアス・エネル ギーを小さくすることができます。

この ADC は、フル性能動作のために 1.8 V の単電源とエンコー ド・クロックを必要とします。多くのアプリケーションで外付け リファレンス部品が不要です。デジタル出力はLVDS 互換です。

AD9286 は Pb フリーの 48 ピン LFCSP を採用し、-40℃~+85℃の 工業温度範囲で仕様が規定されています。

#### 製品のハイライト

- 1. 8ビット 500 MSPS の ADC を内蔵。

- 1.8 V 単電源動作で、LVDS 出力。 2.

- ピン設定によるパワーダウン・オプション。

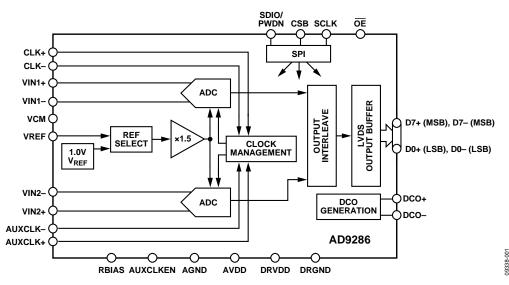

### 機能ブロック図

図 1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明元的またけ除元的に発されて、 ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 -トは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ※日本語デ ©2011 Analog Devices, Inc. All rights reserved.

Rev. A

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

# 目次

| 特長             | ]   |

|----------------|-----|

| アプリケーション       | 1   |

| 概要             | . 1 |

| 製品のハイライト       | . 1 |

| 機能ブロック図        | . 1 |

| 改訂履壓           | 2   |

| 仕様             | 3   |

| DC 仕様          | 3   |

| AC 仕様          |     |

| デジタル仕様         | 5   |

| スイッチング仕様       | .6  |

| SPI タイミング仕様    |     |

| 絶対最大定格         | ç   |

| 熱抵抗            | 9   |

| ESD の注意        | ç   |

| ピン配置およびピン機能説明1 | C   |

| 代表的な性能特性1      | 2   |

| 等価回路1          | _   |

| 動作原理1          | 5   |

| ADC のアーキテクチャ1  | 5   |

| アナログ入力に対する考慮1  | 5   |

|                |     |

| リファレンス電圧                                                                                   | 15                         |

|--------------------------------------------------------------------------------------------|----------------------------|

| RBIAS                                                                                      | 15                         |

| クロック入力の考慮事項                                                                                | 16                         |

| デジタル出力                                                                                     | 18                         |

| ビルトイン・セルフテスト(BIST)と出力テスト                                                                   | 19                         |

| ビルトイン・セルフテスト(BIST)                                                                         | 19                         |

| 出力テスト・モード                                                                                  | 19                         |

| シリアル・ポート・インターフェース(SPI)                                                                     | 20                         |

| SPI を使う設定                                                                                  | 20                         |

| ハードウェア・インターフェース                                                                            | 21                         |

| SPI を使わない設定                                                                                | 21                         |

|                                                                                            |                            |

| SPI からアクセス可能な機能                                                                            |                            |

|                                                                                            | 21                         |

| SPI からアクセス可能な機能                                                                            | 21                         |

| SPI からアクセス可能な機能メモリ・マップ                                                                     | 21<br>22<br>22             |

| SPI からアクセス可能な機能メモリ・マップメモリ・マップ・レジスタ・テーブルの読出し                                                | 21<br>22<br>22<br>23       |

| SPI からアクセス可能な機能メモリ・マップメモリ・マップ・レジスタ・テーブルの読出しメモリ・マップ・レジスタ・テーブル                               | 21<br>22<br>22<br>23       |

| SPI からアクセス可能な機能メモリ・マップメモリ・マップ・レジスタ・テーブルの読出しメモリ・マップ・レジスタ・テーブルメモリ・マップ・レジスタの説明                | 21<br>22<br>23<br>25<br>26 |

| SPI からアクセス可能な機能メモリ・マップメモリ・マップ・レジスタ・テーブルの読出しメモリ・マップ・レジスタ・テーブルメモリ・マップ・レジスタの説明メモリ・マップ・レジスタの説明 | 21<br>22<br>23<br>25<br>26 |

# 改訂履歴

3/11—Rev. 0 to Rev. A

Changes to General Description, ADC Conversion Rate......1

1/11—Revision 0: Initial Version

# 仕様

# DC 仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、1.0 V 内蔵 ADC リファレンス電圧を使用。

表 1.

| Parameter <sup>1</sup>           | Temperature | Min  | Тур        | Max  | Unit   |

|----------------------------------|-------------|------|------------|------|--------|

| RESOLUTION                       | Full        | 8    |            |      | Bits   |

| DC ACCURACY                      |             |      |            |      |        |

| Differential Nonlinearity        | Full        |      | ±0.2       | ±0.4 | LSB    |

| Integral Nonlinearity            | Full        |      | ±0.1       | ±0.3 | LSB    |

| No Missing Codes                 | Full        |      | Guaranteed |      |        |

| Offset Error                     | Full        | 0    | ±0.4       | ±2.1 | % FS   |

| Gain Error                       | Full        | 0    | ±2         | ±2.8 | % FS   |

| MATCHING CHARACTERISTICS         |             |      |            |      |        |

| Offset Error <sup>2</sup>        | Full        | 0    | ±0.4       | ±2.1 | % FS   |

| Gain Error                       | Full        | 0    | ±0.05      | ±0.2 | % FS   |

| TEMPERATURE DRIFT                |             |      |            |      |        |

| Offset Error                     | Full        |      | ±2         |      | ppm/°C |

| Gain Error                       | Full        |      | ±20        |      | ppm/°C |

| ANALOG INPUT                     |             |      |            |      |        |

| Input Span                       | Full        |      | 1.2        |      | V p-p  |

| Input Common-Mode Voltage        | Full        |      | 1.4        |      | V      |

| Input Resistance (Differential)  | Full        |      | 16         |      | kΩ     |

| Input Capacitance (Differential) | Full        |      | 250        |      | fF     |

| Full Power Bandwidth             | Full        |      | 700        |      | MHz    |

| VOLTAGE REFERENCE                |             |      |            |      |        |

| Internal Reference               | Full        | 0.97 | 1          | 1.03 | V      |

| Input Resistance                 | Full        |      | 3          |      | kΩ     |

| POWER SUPPLIES                   |             |      |            |      |        |

| Supply Voltage                   |             |      |            |      |        |

| AVDD                             | Full        | 1.7  | 1.8        | 1.9  | V      |

| DRVDD                            | Full        | 1.7  | 1.8        | 1.9  | V      |

| Supply Current                   |             |      |            |      |        |

| $I_{AVDD}$                       | Full        |      | 125        | 130  | mA     |

| $I_{DRVDD}$                      | Full        |      | 51         | 54   | mA     |

| POWER CONSUMPTION                |             |      |            |      |        |

| Sine Wave Input <sup>3</sup>     | Full        |      | 315        | 330  | mW     |

| Power-Down Power                 | Full        |      | 0.3        | 1.7  | mW     |

<sup>&</sup>lt;sup>1</sup> 完全な定義セットとこれらのテストの実施方法についてはアプリケーション・ノート AN-835「Understanding High Speed ADC Testing and Evaluation」を参照してくだ

さい。

<sup>2</sup>インターリーブ性能のセクションを参照してください。

<sup>3</sup>低周波数、フル・スケール正弦波、各出力ビットに約5pFの負荷を接続して測定。

# AC 仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、1.0 V 内蔵 ADC リファレンス電圧を使用、VIN = -1.0 dBFS 差動入力、最適タイミング値を設定。

表 2.

| Parameter                                       | Temperature | Min  | Тур  | Max | Unit |

|-------------------------------------------------|-------------|------|------|-----|------|

| SIGNAL-TO-NOISE RATIO (SNR)                     |             |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                     | 25°C        |      | 49.3 |     | dBFS |

| $f_{IN} = 70 \text{ MHz}$                       | 25°C        |      | 49.3 |     | dBFS |

| $f_{IN} = 96.6 \text{ MHz}$                     | Full        | 48.8 | 49.3 |     | dBFS |

| $f_{IN} = 220 \text{ MHz}$                      | 25°C        |      | 49.3 |     | dBFS |

| SIGNAL-TO-NOISE-AND-DISTORTION (SINAD)          |             |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                     | 25°C        |      | 49.2 |     | dBFS |

| $f_{IN} = 70 \text{ MHz}$                       | 25°C        |      | 49.2 |     | dBFS |

| $f_{IN} = 96.6 \text{ MHz}$                     | Full        | 48.7 | 49.2 |     | dBFS |

| $f_{IN} = 220 \text{ MHz}$                      | 25°C        |      | 49.2 |     | dBFS |

| EFFECTIVE NUMBER OF BITS (ENOB)                 |             |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                     | 25°C        |      | 7.9  |     | Bits |

| $f_{\rm IN} = 70~{\rm MHz}$                     | 25°C        |      | 7.9  |     | Bits |

| $f_{IN} = 96.6 \text{ MHz}$                     | Full        | 7.8  | 7.9  |     | Bits |

| $f_{IN} = 220 \text{ MHz}$                      | 25°C        |      | 7.9  |     | Bits |

| WORST SECOND OR THIRD HARMONIC                  |             |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                     | 25°C        |      | -70  |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                       | 25°C        |      | -70  |     | dBc  |

| $f_{IN} = 96.6 \text{ MHz}$                     | Full        |      | -69  | -61 | dBc  |

| $f_{\rm IN} = 220~{\rm MHz}$                    | 25°C        |      | -65  |     | dBc  |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR) <sup>1</sup> |             |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                     | 25°C        |      | 70   |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                       | 25°C        |      | 70   |     | dBc  |

| $f_{\rm IN} = 96.6~\rm MHz$                     | Full        | 61   | 68   |     | dBc  |

| $f_{\rm IN} = 220~{ m MHz}$                     | 25°C        |      | 65   |     | dBc  |

| WORST OTHER HARMONIC OR SPUR                    |             |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                     | 25°C        |      | -71  |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                       | 25°C        |      | -71  |     | dBc  |

| $f_{\rm IN} = 96.6 \text{ MHz}$                 | Full        |      | -71  | -64 | dBc  |

| $f_{\rm IN} = 220~{\rm MHz}$                    | 25°C        |      | -67  |     | dBc  |

| CROSSTALK                                       | Full        |      | -80  |     | dBc  |

<sup>「</sup>オフセットと折り返しスプリアスは含みません(インターリーブ性能のセクションを参照してください)。

# デジタル仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、1.0 V 内蔵 ADC リファレンスを使用、AIN = 5 MHz、フル温度範囲。

表 3.

| Parameter <sup>1</sup>                         | Temperature | Min        | Тур           | Max         | Unit  |

|------------------------------------------------|-------------|------------|---------------|-------------|-------|

| CLOCK INPUTS (CLK+, CLK-, AUXCLK+, AUXCLK-)    |             |            |               |             |       |

| Logic Compliance                               |             |            | LVDS/PECL     |             |       |

| Internal Common-Mode Bias                      | Full        |            | 1.2           |             | V     |

| Differential Input Voltage <sup>2</sup>        | Full        | 0.2        |               | 6           | V p-p |

| Input Voltage Range                            | Full        | AVDD - 0.3 |               | AVDD + 1.6  | V     |

| High Level Input Voltage                       | Full        | 1.2        |               | 3.6         | V     |

| Low Level Input Voltage                        | Full        | 0          |               | 0.8         | V     |

| High Level Input Current                       | Full        | -10        |               | +10         | μΑ    |

| Low Level Input Current                        | Full        | -10        |               | +10         | μΑ    |

| Input Resistance (Differential)                | 25°C        |            | 20            |             | kΩ    |

| Input Capacitance                              | 25°C        |            | 4             |             | pF    |

| LOGIC INPUTS                                   |             |            |               |             |       |

| CSB                                            |             |            |               |             |       |

| High Level Input Voltage                       | Full        | 1.2        |               | DRVDD + 0.3 | V     |

| Low Level Input Voltage                        | Full        | 0          |               | 0.8         | V     |

| High Level Input Current                       | Full        | -5         | -0.4          | +5          | μΑ    |

| Low Level Input Current                        | Full        | -80        | -63           | -50         | μΑ    |

| Input Resistance                               | 25°C        |            | 30            |             | kΩ    |

| Input Capacitance                              | 25°C        |            | 2             |             | pF    |

| SCLK, SDIO/PWDN, AUXCLKEN, OE                  |             |            |               |             |       |

| High Level Input Voltage                       | Full        | 1.2        |               | DRVDD + 0.3 | V     |

| Low Level Input Voltage                        | Full        | 0          |               | 0.8         | V     |

| High Level Input Current                       | Full        | 50         | 57            | 70          | μА    |

| Low Level Input Current                        | Full        | -5         | -0.4          | +5          | μA    |

| Input Resistance                               | 25°C        |            | 30            |             | kΩ    |

| Input Capacitance                              | 25°C        |            | 2             |             | pF    |

| DIGITAL OUTPUTS (D7+, D7- to D0+, D0-), LVDS   |             |            |               |             |       |

| DRVDD = 1.8 V                                  |             |            |               |             |       |

| Differential Output Voltage (V <sub>OD</sub> ) | Full        | 290        | 345           | 400         | mV    |

| Output Offset Voltage (Vos)                    | Full        | 1.15       | 1.25          | 1.35        | V     |

| Output Coding (Default)                        |             |            | Offset binary |             |       |

<sup>&</sup>lt;sup>1</sup>完全な定義セットとこれらのテストの実施方法についてはアプリケーション・ノート AN-835「高速 A/D コンバータ (ADC) のテストと評価について」を参照してく ださい。 <sup>2</sup> LVDS と LVPECL に対してのみ規定。

# スイッチング仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、最大サンプル・レート、 $-1.0~\mathrm{dBFS}$  差動入力、 $1.0~\mathrm{V}$  内蔵リファレンスを使用。

# 表 4.

| Parameter                                      | Temperature | Min  | Тур | Max | Unit   |

|------------------------------------------------|-------------|------|-----|-----|--------|

| CLOCK INPUT PARAMETERS                         |             |      |     |     |        |

| Input Clock Rate                               | Full        | 60   |     | 500 | MHz    |

| CLK Period (t <sub>CLK</sub> )                 | Full        | 4    |     |     | ns     |

| CLK Pulse Width High (t <sub>CH</sub> )        | Full        |      | 2   |     | ns     |

| DATA OUTPUT PARAMETERS                         |             |      |     |     |        |

| Data Propagation Delay (tPD)                   |             |      | 3.7 |     | ns     |

| DCO Propagation Delay (t <sub>DCO</sub> )      | Full        |      | 3.7 |     | ns     |

| DCO to Data Skew (t <sub>SKEW</sub> )          | Full        | -280 | -60 | 100 | ps     |

| Pipeline Delay (Latency)                       | Full        |      | 11  |     | Cycles |

| Aperture Delay (t <sub>A</sub> )               | Full        |      | 1.0 |     | ns     |

| Aperture Uncertainty (Jitter, t <sub>J</sub> ) | Full        |      | 0.1 |     | ps rms |

| Wake-Up Time <sup>1</sup>                      | Full        |      | 500 |     | μs     |

| OUT-OF-RANGE RECOVERY TIME                     | Full        |      | 4   |     | Cycles |

<sup>「</sup>ウェイクアップ時間はデカップリング・コデンサの値に依存します。

# SPI タイミング仕様

#### 表 5.

| Parameter               | Description                                                                                           | Min | Тур | Max | Unit |

|-------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SPI TIMING REQUIREMENTS |                                                                                                       |     |     |     |      |

| $t_{ m DS}$             | Setup time between the data and the rising edge of SCLK                                               | 2   |     |     | ns   |

| $t_{ m DH}$             | Hold time between the data and the rising edge of SCLK                                                | 2   |     |     | ns   |

| $t_{CLK}$               | Period of the SCLK                                                                                    | 40  |     |     | ns   |

| $t_{S}$                 | Setup time between CSB and SCLK                                                                       | 2   |     |     | ns   |

| $t_{ m H}$              | Hold time between CSB and SCLK                                                                        | 2   |     |     | ns   |

| $t_{ m HIGH}$           | SCLK pulse width high                                                                                 | 10  |     |     | ns   |

| $t_{LOW}$               | SCLK pulse width low                                                                                  | 10  |     |     | ns   |

| $t_{\rm EN\_SDIO}$      | Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge | 10  |     |     | ns   |

| $t_{ m DIS\_SDIO}$      | Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge  | 10  |     |     | ns   |

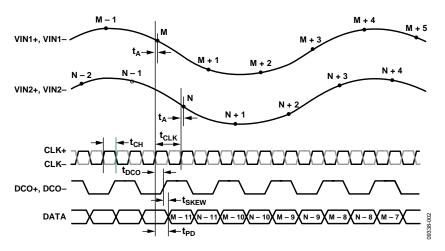

## タイミング図

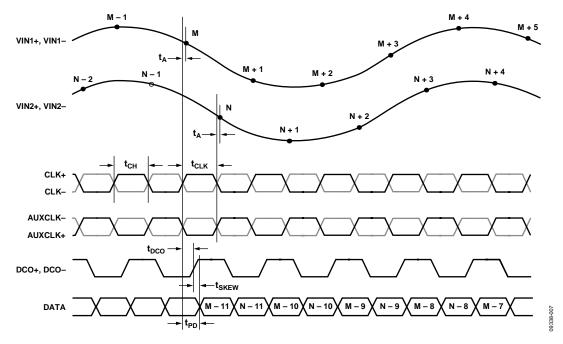

図 2.出力タイミング図、サンプル・モード = インターリーブ (デフォルト)

- 6/27 -

Rev. A

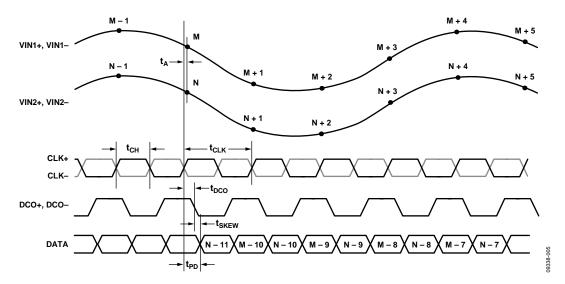

図 3.出力タイミング図、サンプル・モード = 同時、AUXCLKEN = 0

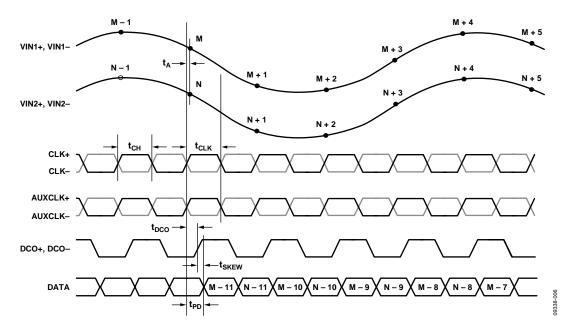

図 4.出力タイミング図、サンプル・モード = 同時、AUXCLKEN = 1、CLK と AUXCLK は同相

Rev. A - 7/27 -

図 5.出力タイミング図、サンプル・モード = 同時、AUXCLKEN = 1、CLK と AUXCLK は逆相

Rev. A - 8/27 -

# 絶対最大定格

表 6.

| Parameter                               | Rating                  |

|-----------------------------------------|-------------------------|

| Electrical                              |                         |

| AVDD to AGND                            | -0.3 V to +2.0 V        |

| DRVDD to DRGND                          | -0.3 V to +2.0 V        |

| AGND to DRGND                           | -0.3 V to +0.3 V        |

| AVDD to DRVDD                           | -2.0 V to +2.0 V        |

| D0+/D0- through D7+/D7-<br>to DRGND     | -0.3 V to DRVDD + 0.3 V |

| DCO+, DCO- to DRGND                     | -0.3 V to DRVDD + 0.3 V |

| CLK+, CLK- to AGND                      | -0.3 V to AVDD + 0.2 V  |

| AUXCLK+, AUXCLK- to AGND                | -0.3 V to AVDD + 0.2 V  |

| VIN1±, VIN2± to AGND                    | -0.3 V to AVDD + 0.2 V  |

| SDIO/PWDN to DRGND                      | -0.3 V to DRVDD + 0.3 V |

| CSB to AGND                             | -0.3 V to DRVDD + 0.3 V |

| SCLK to AGND                            | -0.3 V to DRVDD + 0.3 V |

| Environmental                           |                         |

| Storage Temperature Range               | −65°C to +125°C         |

| Operating Temperature Range             | −40°C to +85°C          |

| Lead Temperature<br>(Soldering, 10 sec) | 300°C                   |

| Junction Temperature                    | 150°C                   |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久 的な損傷を与えることがあります。この規定はストレス定格の規 定のみを目的とするものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼 性に影響を与えます。

# 熱抵抗

θ<sub>JA</sub> はワーストケース条件で規定。すなわち表面実装パッケージの 場合、デバイスを回路ボードにハンダ付けした状態で規定。

#### 表 7.熱抵抗

| Package Type             | $\theta_{\mathrm{JA}}$ | $\theta_{ m JC}$ | Unit |

|--------------------------|------------------------|------------------|------|

| 48-Lead LFCSP (CP-48-12) | 30.4                   | 2.9              | °C/W |

## ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

# ピン配置およびピン機能説明

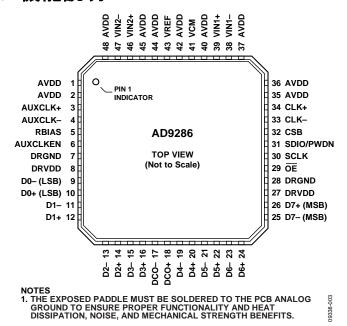

図 6.ピン配置

表 8.ピン機能の説明

| ピン番号                                 | 記 <del>号</del> | タイプ   | 説明                                                                                                                    |

|--------------------------------------|----------------|-------|-----------------------------------------------------------------------------------------------------------------------|

| ADC 電源ピン                             |                |       | •                                                                                                                     |

| 1, 2, 35, 36, 37, 40, 42, 44, 45, 48 | AVDD           | 電源    | アナログ電源 (1.8 V 公称)。                                                                                                    |

| 8, 27                                | DRVDD          | 電源    | デジタル出力ドライバ電源 (1.8 V 公称)。                                                                                              |

| 7、28                                 | DRGND          | グラウンド | デジタル出力グラウンド。                                                                                                          |

| 0                                    | AGND           | グラウンド | アナログ・グラウンド。ピン 0 はパッケージ底面のエクスポーズド・サーマル・パッド。これが唯一のグラウンド接続であるため、PCB アナログ・グラウンドへハンダ付けして、正しい機能と熱放散、ノイズ、機械的強度を確実にする必要があります。 |

| ADC アナログ・ピン                          |                |       |                                                                                                                       |

| 39                                   | VIN1+          | 入力    | 差動アナログ入力ピン (+)、チャンネル 1。                                                                                               |

| 38                                   | VIN1-          | 入力    | 差動アナログ入力ピン (-)、チャンネル 1。                                                                                               |

| 46                                   | VIN2+          | 入力    | 差動アナログ入力ピン (+)、チャンネル 2。                                                                                               |

| 47                                   | VIN2-          | 入力    | 差動アナログ入力ピン (-)、チャンネル 2。                                                                                               |

| 43                                   | VREF           | 入力/出力 | リファレンス電圧入力/出力。                                                                                                        |

| 5                                    | RBIAS          | 入力/出力 | 外付けリファレンス電圧のバイアス抵抗。 RBIAS と AGND の間に $10 \text{ k}\Omega$ を接続します。                                                     |

| 41                                   | VCM            | 出力    | アナログ入力の同相モード・レベル・バイアス出力。                                                                                              |

| 34                                   | CLK+           | 入力    | ADC クロック入力一真。                                                                                                         |

| 33                                   | CLK-           | 入力    | ADC クロック入力—相補。                                                                                                        |

| 3                                    | AUXCLK+        | 入力    | 補助 ADC クロック入力—真。                                                                                                      |

| 4                                    | AUXCLK-        | 入力    | 補助 ADC クロック入力—相補。                                                                                                     |

| デジタル入力                               |                |       |                                                                                                                       |

| 6                                    | AUXCLKEN       | 入力    | 補助クロック入力イネーブル。                                                                                                        |

| 29                                   | ŌE             | 入力    | 出力データ・ピンをスリーステートにするデジタル・イネーブル (アクティブ・ロー)。                                                                             |

| デジタル出力                               | •              | ·     | •                                                                                                                     |

| 26                                   | D7+ (MSB)      | 出力    | 出力データ <b>7</b> —真。                                                                                                    |

| 25                                   | D7- (MSB)      | 出力    | 出力データ <b>7</b> —相補。                                                                                                   |

| 24                                   | D6+            | 出力    | 出力データ 6—真。                                                                                                            |

Rev. A - 10/27 -

# AD9286

| ピン番号        | 記号        | タイプ   | 説明                                              |

|-------------|-----------|-------|-------------------------------------------------|

| 23          | D6-       | 出力    | 出力データ 6—相補。                                     |

| 22          | D5+       | 出力    | 出力データ 5—真。                                      |

| 21          | D5-       | 出力    | 出力データ 5—相補。                                     |

| 20          | D4+       | 出力    | 出力データ <b>4</b> —真。                              |

| 19          | D4-       | 出力    | 出力データ 4―相補。                                     |

| 16          | D3+       | 出力    | 出力データ 3―真。                                      |

| 15          | D3-       | 出力    | 出力データ 3—相補。                                     |

| 14          | D2+       | 出力    | 出力データ 2—真。                                      |

| 13          | D2-       | 出力    | 出力データ 2—相補。                                     |

| 12          | D1+       | 出力    | 出力データ 1一真。                                      |

| 11          | D1-       | 出力    | 出力データ 1—相補。                                     |

| 10          | D0+ (LSB) | 出力    | 出力データ 0―真。                                      |

| 9           | D0- (LSB) | 出力    | 出力データ 0—相補。                                     |

| 18          | DCO+      | 出力    | データ・クロック出力—真。                                   |

| 17          | DCO-      | 出力    | データ・クロック出力—相補。                                  |

| SPI コントロール・ | ピン        |       | ·                                               |

| 30          | SCLK      | 入力    | SPI シリアル・クロック。                                  |

| 31          | SDIO/PWDN | 入力/出力 | 外部モードでの SPI シリアル・データ I/O (SDIO)/パワーダウン入力(PWDN)。 |

| 32          | CSB       | 入力    | SPI チップ・セレクト (アクティブ・ロー)。                        |

Rev. A - 11/27 -

# 代表的な性能特性

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、サンプル・レート = 500 MSPS、DCS をイネーブル、1.2 V p-p 差動入力、VIN = -1.0 dBFS、64k サンプル、 $T_A$  = 25°C。

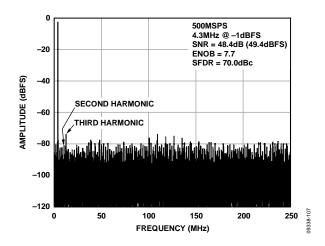

図 7. シングル・トーン FFT、f<sub>IN</sub> = 4.3 MHz

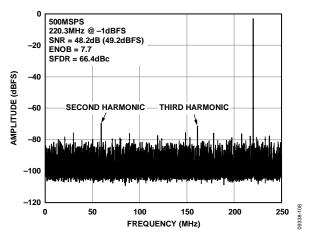

図 8.シングル・トーン FFT、f<sub>IN</sub> = 220.3 MHz

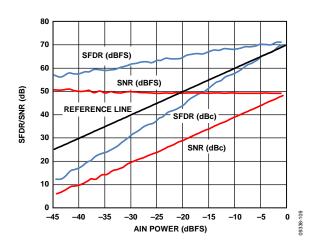

図 9.入力振幅 (AIN)対 SFDR/SNR、f<sub>IN</sub> = 2.2 MHz

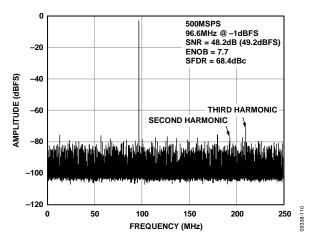

図 10.シングル・トーン FFT、f<sub>IN</sub> = 96.6 MHz

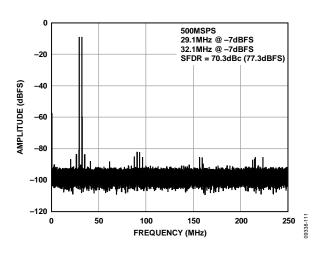

図 11.2 トーン FFT、 $f_{\text{IN1}}$  = 29.1 MHz、 $f_{\text{IN2}}$  = 32.1 MHz

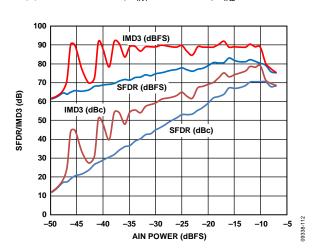

図 12.入力振幅 (AIN)対 2 トーン SFDR/IMD3、 $f_{\text{IN1}}$  = 29.1 MHz、 $f_{\text{IN2}}$  = 32.1 MHz

Rev. A — 12/27 —

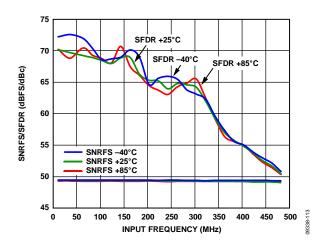

図 13.様々な温度での入力周波数 (f<sub>IN</sub>)対 SNRFS/SFDR

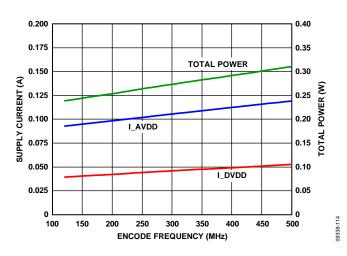

図 14.エンコード対電源電流と消費電力

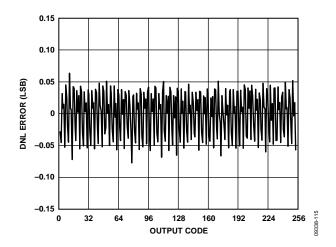

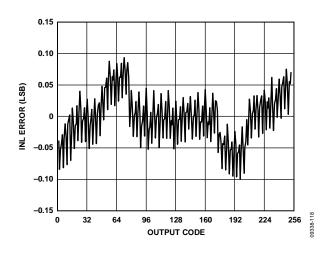

図 15.DNL 誤差、f<sub>IN</sub> = 4.3 MHz

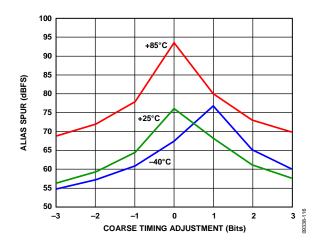

図 16.様々な温度でのタイミング粗調整対折り返しスプリアス

図 17.INL 誤差、f<sub>IN</sub> = 4.3 MHz

Rev. A — 13/27 —

# 等価回路

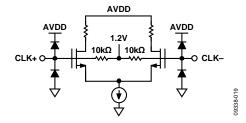

図 18.クロック入力

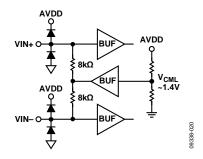

図 19.アナログ入力 (V<sub>CML</sub> = ~1.4 V)

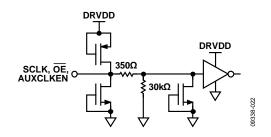

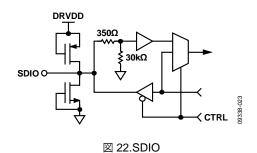

図 21.SCLK、 OE、 AUXCLKEN

図 23.LVDS 出力ドライバ

Rev. A - 14/27 -

# 動作原理

AD9286 はパイプライン型のコンバータです。入力バッファは差動で、両入力セットは内部でバイアスされています。このため、AC 入力モードまたは DC 入力モードを使用することができます。サンプル・アンド・ホールド・アンプが、マルチステージ・パイプライン・コンバータ・コアの最初のステージに組込まれています。 出力ステージのブロックで、データの整列、パイプライン・ステージの誤差補正、インターリーブ・ブロックへのデータ供給、出力バッファへのデータの出力が行われます。すべてのユーザ設定オプションは、専用デジタル入力ピンまたはシリアル・ポート・インターフェース (SPI)を使って設定されます。

## ADC のアーキテクチャ

AD9286 の各インターリーブ・チャンネルは、差動入力バッファとそれに続くサンプル・アンド・ホールド・アンプ (SHA)から構成されています。この SHA の後ろにはパイプライン化されたスイッチド・キャパシタ ADC があります。各ステージからの量子化された出力は、デジタル補正ロジックで結合されて最終的に 8 ビットになります。パイプライン化されたアーキテクチャにより、新しい入力サンプルに対して最初のステージが動作すると同時に、残りのステージは先行しているサンプルに対して動作することができます。

最終ステージ以外のパイプラインの各ステージは、スイッチド・キャパシタDACに接続された低分解能のフラッシュADCとステージ間残留アンプ(MDAC)により構成されています。この残留アンプは、再生されたDAC出力とパイプライン内の次のステージに対するフラッシュ入力の差を増幅します。各ステージ内で冗長な1ビットを使って、フラッシュ誤差のデジタル補正を可能にしています。最終ステージはフラッシュADCで構成されています。

入力ステージには差動 SHA が含まれており、差動モードまたはシングルエンド・モードで AC 結合または DC 結合することができます。出力ステージのブロックで、データの整列、誤差補正、出力バッファへのデータの出力が行われます。出力バッファの電源は分離されているため、出力電圧振幅を調整することができます。パワーダウン時には、出力バッファはハイ・インピーダンス状態にかります

両インターリーブ・チャンネルの出力をタイム・インターリーブして実効 500 MSPS を実現しています。

#### アナログ入力に対する考慮

AD9286 のアナログ入力には差動バッファがついています。最適なダイナミック性能を得るためには、同相モードのセトリング誤差が対称になるように、VIN1+、VIN1-、VIN2+、VIN2-を駆動するソース・インピーダンスが一致している必要があります。AD9286 では 2 つの ADC コアをインターリーブするため、特にボード・レイアウト時に注意して、2 つのアナログ・パスの対称性を維持する必要があります。不一致があると、歪みが発生します。アナログ入力は、優れた広帯域性能を得るように最適化されており、アナログ入力を差動で駆動することが必要です。 アナログ入力をシングルエンド信号で駆動すると、SNR 性能と SINAD 性能は大幅に低下します。

シングルエンドから差動への変換を必要とするアプリケーションに対しては、Mini-Circuits®社の ADT1-IWT のような広帯域トランスを使って差動アナログ入力を用意することができます。両アナログ入力は、内蔵抵抗分圧器により公称 1.4~V にセルフ・バイアスされています。

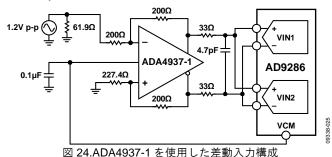

#### 差動入力構成

最適性能は、AD9286 を差動入力構成で駆動したときに得られます。ベースバンド・アプリケーションに対しては、ADA4937-1 差動ドライバが優れた性能と ADC に対する柔軟なインターフェースを提供します(図 24 参照)。AD9286 の出力同相モード電圧は容易に 1.4~V に設定できるため、ドライバは入力信号の帯域制限用 Sallen-Key フィルタ回路内で構成することができます。

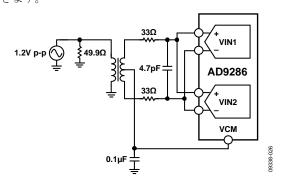

AD9286 は、差動トランス結合入力で受動的に駆動することができます (図 25 参照)。アナログ入力にバイアスを加えるため、 VCM 電圧をトランス二次巻線のセンタータップに接続することができます。

図 25.差動トランス結合構成

トランスを選択するときは、信号特性を考慮する必要があります。 大部分の RF トランスは、数 MHz より低い周波数で飽和します。 大きな信号電力もコア・サチレーションの原因になり、歪みを発 生させます。

### リファレンス電圧

内蔵差動リファレンス電圧が正と負のリファレンス電圧を発生し、これらの電圧が ADC コアの 1.2 V p-p 固定スパンを決定します。この内蔵リファレンス電圧は、SPI 制御を介して調整することができます。安定な外付けリファレンス電圧を使って外部から駆動することもできます。詳細については、メモリ・マップ・レジスタの説明のセクションを参照してください。

#### **RBIAS**

AD9286 では、RBIAS ピンとグラウンドとの間に  $10 \text{ k}\Omega$  の抵抗を接続する必要があります。この抵抗は ADC コアのマスター・リファレンス電流を設定するため、偏差 1%のものを使う必要があります。

### クロック入力の考慮事項

最適性能を得るためには、AD9286 のサンプル・クロック入力 CLK+と CLK- (さらにオプションとして AUXCLK+と AUXCLK-) を差動信号で駆動する必要があります。信号は、一般にトランス またはコンデンサを介して CLK+ピンと CLK-ピンに AC 結合されます。

#### クロック入力オプション

AD9286は非常に柔軟なクロック入力構造を持っています。クロック入力としては、LVDS、LVPECL、または正弦波信号が可能です。このセクションで説明する各構成は、CLK+とCLK-および必要に応じてAUXCLK+とAUXCLK-に適用することができます。

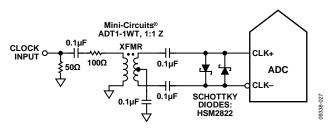

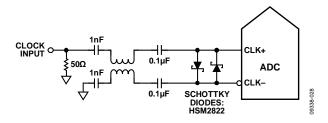

図 26 と図 27に、AD9286をクロック駆動する2つの望ましい方法を示します。ジッタの少ないクロック・ソースは、RFバランまたはRFトランスを使ってシングルエンド信号から差動信号に変換されます。トランス/バランの2次側に互いに逆向きに接続されたショットキ・ダイオードが、AD9286に入力されるクロックを約0.8 Vp-p差動に制限します。

この機能は、クロックの大きな電圧振幅が AD9286 の別の部分に 混入することを防止すると同時に、低ジッタ性能にとって重要な、 信号の高速な立上がり時間と立下がり時間を維持します。

図 26.トランス結合差動クロック

図 27.バラン結合差動クロック

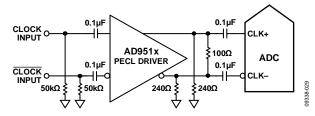

低ジッタ・クロック・ソースがない場合、もう1つのオプション は差動 PECL 信号をサンプル・クロック入力ピンへ AC 結合することです(図 28 参照)。AD9510/ AD9511/ AD9512/ AD9513/ AD9514/ AD9515/ AD9516/ AD9517 クロック・ドライバは、優れたジッタ性能を提供します。

図 28.差動 PECL サンプル・クロック

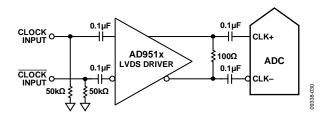

3 つ目のオプションは、差動 LVDS 信号をサンプル・クロック入 力ピンへ AC 結合する方法です(図 29 参照)。AD9510/ AD9511/ AD9512/ AD9513/ AD9514/ AD9515/ AD9516/ AD9517 クロック・ ドライバは、優れたジッタ性能を提供します。

図 29.差動 LVDS サンプル・クロック

#### クロック・モード

AD9286 は、インターリーブをイネーブルした 1 チャンネル・コンバータとしてパワーアップします。このモードでは、CLK+とCLK-を駆動する 1 つの高速クロックが 1/2 分周されて、互いに  $180^\circ$ の位相差で各 ADC コアを駆動します。2 つのアナログ入力を外部で接続すると、AD9286 は 1 つの 500 MSPS ADC として動作します。

高いサンプル・レートは 2 つの ADC コアをインターリーブする ことにより実現されているため、コア間、ボード・レイアウト、クロック・タイミングの不一致があると歪みが発生します。 AD9286 は、2 つの一致した ADC コアを使って不一致を小さくするようにデザインされています。 AD9286 では、タイミング誤差の除去に役立てるため、SPI を使いチャンネルごとのタイミングの微調整と粗調整を提供しています。これらの機能は、レジスタ 0x37 (微調整) とレジスタ 0x38 (粗調整)を介して使うことができます。

AD9286 では、速度を 1/2 にしたクロックを 2 本提供するモードをサポートしています。このモードでは、内部クロック・タイミング回路をバイパスして、各インターリーブ・チャンネル間のクロック・タイミング関係を外部から制御することができます。サンプル・モードを"同時(simultaneous)"に設定し (アドレス 0x09、ビット 3=0)、かつ AUXCLKEN ピンを DRVDD に接続すると、AD9286 はセカンド・クロックが補助クロック入力 (AUXCLK+、AUXCLK-)から入力されるものと見なします。

このモードでは、AD9286 は 2 系統の 8 ビット 250 MSPS コンバータとして動作することもできます。この機能は、1 系統の 8 ビット500 MSPS と 2 系統の 8 ビット250 MSPS コンバータを必要とするアプリケーションで便利です。クロック・マネジメント・ブロックでは、CLK± と AUXCLK± の位相が互いに $0^\circ$  または $180^\circ$ であることが必要です。この条件が満たされると、各 $10^\circ$  ADC コアから出力されるデータが正しく整列されます。

AD9286 を 2 系統の 8 ビット 250 MSPS コンバータとして動作させるため 1 つのクロックだけを入力させるときは、AUXCLKEN ピンを AGND に接続してサンプル・モードを"同時"に設定します。このモードでは、2 つの ADC コアが同時にサンプルします。サポートされるすべてのクロック・モードを、表 9 に示します。

AD9286 は、別々のクロックによる各内部 ADC のクロック駆動をサポートしています。AUXCLKEN を DRVDD に設定すると、AUXCLK+と AUXCLK-に差動補助クロックを入力することができます。このモードでは、各内部 ADC コアの最大サンプル・レートが 250 MSPS になります。このモードでは、内部タイミング調整ブロックがバイパスされます。

#### インターリーブ性能

AD9286では、2つの250 MSPS ADCチャンネルをタイム・インターリーブすることにより500 MSPSの変換を実現しています。この技術は8ビット性能を実現するためには十分ですが、定量化可能な誤差が発生します。これらの誤差は、ゲイン不一致、不完全な逆相サンプリング、2チャンネル間のオフセット不一致の3つの原因から発生します。歪みは、スペクトル的に2つの形態で現れます。すなわち、ゲインとタイミング不一致は折り返しスプリアス(式1)として、オフセット不一致はコンバータのナイキスト・レートの位置のスプリアスとして(式2)、それぞれ現れます。

$$f_{ALIAS\_SPUR} = f_S/2 - f_{IN} \tag{1}$$

ここで、

$f_S$  はインターリーブ・サンプル・レート。  $f_N$  はアナログ入力周波数。

$$f_{OFFSET\_SPUR} = f_S/2 \tag{2}$$

-- -

$f_s$  はインターリーブ・サンプル・レート。

折り返しスプリアス (AS)の振幅は、式3に示すゲイン誤差がその成分になっています。

$$AS_{GAIN} (dBc) = 20 \times \log(AS_{GAIN}) = 20 \times \log(G_E/2)$$

(3)

ここで、

$G_E = Gain\_Error\_Ratio = 1 - V_{FS1}/V_{FS2\circ}$

$V_{ESn}$  はコア n のフルスケール電圧。

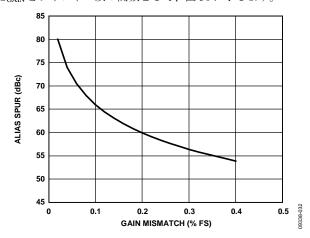

AS<sub>GAIN</sub>をゲイン不一致の関数として、図 30 に示します。

図 30.ゲイン不一致の関数としての ASGAIN

折り返しスプリアス (AS)の振幅は、式 4 に示すタイミング誤差が その成分になっています。

$$AS_{TIMING} (dBc) = 20 \times \log(AS_{TIMING}) = 20 \times \log(\theta_{EP}/2)$$

$$(4)$$

$\theta_{EP} = \omega_A \times \Delta t_E (ラジアン)$ 、 $\omega_A はアナログ入力周波数、 \Delta t_E はクロック・スキュー誤差。$

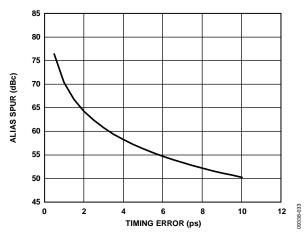

AS<sub>TIMING</sub>をタイミング誤差の関数として図31に示します。

図 31.タイミング誤差の関数としての ASTIMING

折り返しスプリアス (AS) の総合振幅は式5で表されます。

$$AS_{TOTAL} (dB) = 20 \times \log \sqrt{((AS_{GAIN})^2 + (AS_{TIMING})^2)}$$

(5)

表 9.サポートされているクロック・モード

| Effective Number of Channels | Maximum CLK<br>Frequency | AUXCLK<br>Frequency | AUXCLK Phase<br>Relative to CLK | AUXCLKEN | SPI Register,<br>Address 0x09, Bit 3 | Clock Timing Adjust |

|------------------------------|--------------------------|---------------------|---------------------------------|----------|--------------------------------------|---------------------|

| One                          | 500 MSPS                 | N/A                 | N/A                             | Low      | 1                                    | Internal            |

| Two                          | 250 MSPS                 | N/A                 | N/A                             | Low      | 0                                    | N/A                 |

| Two                          | 250 MSPS                 | CLK                 | 0°                              | High     | 0                                    | N/A                 |

| One                          | 250 MSPS                 | CLK                 | 180°                            | High     | 0                                    | External            |

Rev. A - 17/27 -

オフセット・スプリアス (OS)の振幅は式6で表されます。

$OS_{OFFSET}$  (dBFS) =  $20 \times \log(OFFSET \times 2/2^{RESOLUTION})$  $\subset \subset \mathcal{T}$ ,

OFFSET はコードで表したチャンネル間オフセット。 RESOLUTION は、コンバータの分解能 (8 ビット)。

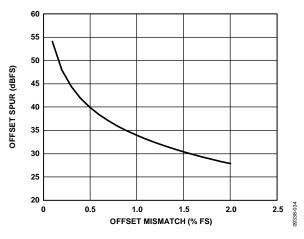

OSoffset をオフセット不一致の関数として図32に示します。

図 32.オフセット・不一致の関数としての OSoffset

ゲイン誤差とタイミング誤差の間に直交性があるため、一方で他方を補正することはできません。AD9286 は、チャンネル間ゲイン誤差を小さくするため、2 つのチャンネル間でゲインが一致するようにデザインされています。SPI のアドレス 0x37 とアドレス 0x38 は、クロック・スキュー誤差を最小にするため、いずれかのクロック・パスに遅延を加える機能を提供しています。また SPI のアドレス 0x10 を介して、チャンネル間オフセット誤差を最小にする機能も提供しています。

# デジタル出力

(6)

## デジタル出カイネーブル機能 (OE)

AD9286 は、デジタル出力ピンに対して柔軟なスリー・ステート機能を持っています。スリー・ステート・モードは、 $\overline{OE}$ ピンを使ってイネーブルします。 $\overline{OE}$ をハイ・レベルにすると、両データ・バスの出力ドライバはハイ・インピーダンス状態になります。

# ビルトイン・セルフテスト(BIST)と出力テスト

AD9286は、ビルトイン・テスト機能を内蔵しています。この機能を使うと、各チャンネルの正常性の確認とボード・レベルのデバッグを行うことができます。AD9286のデジタル・データ・パスの正常性を確認するビルトイン・セルフテスト (BIST)機能も内蔵されています。AD9286の出力に予測可能な値を出力させるための様々な出力テスト・オプションも用意されています。

# ビルトイン・セルフテスト(BIST)

BISTはAD9286の選択した信号パスのデジタル部分をテストします。デバイスが既知の状態にあることを確認するため、リセット後にBIST テストを実行してください。BIST時、内部疑似ランダム・ノイズ (PN) ソースからのデータが、ADC ブロック出力からスタートして両チャンネルのデジタル・データ・パスを通って駆動されます。 データパス出力では、CRC ロジックがデータからのシグネチャを計算します。BISTシーケンスは512サイクル間動作して停止します。テストが完了すると、BIST はシグネチャ結果を規定値と比較します。 シグネチャが一致すると、BISTはレジスタ 0x0Eのビット 0をセットして、テストがパスしたことを通知します。BIST テストに失敗すると、レジスタ 0x0E のビット 0がクリアされます。このテストの間出力が接続されているため、PNシーケンスを動作中に観測することができます。

値0x05をレジスタ 0x0Eに書込むと BISTが開始されます。これにより、レジスタ 0x0Eのビット 0 (BIST イネーブル)がイネーブルされ、

PN シーケンス・ジェネレータ(レジスタ 0x0E)のビット 2 (BIST init)がリセットされます。BISTが完了すると、レジスタ 0x0E のビット 0は自動的にクリアされます。レジスタ 0x0Eのビット 2に0を書込むと、最後の値からPN シーケンスを続けることができますが、PN シーケンスをリセットしない場合、テストの終わりにシグネチャ計算が規定値と一致しません。この時は、出力データの検証を信ずるほかにありません。

# 出力テスト・モード

出力テスト・オプションを表 13 のアドレス 0x0D に示します。出力テスト・モードをイネーブルすると、ADC のアナログ・セクションがデジタル・バックエンド・ブロックから切り離され、テスト・パターンが出力フォーマッティング・ブロックを通して実行されます。テスト・パターンは出力フォーマッティングが行われる場合も、行われない場合もあります。レジスタ 0x0D のビット 4 またはビット 5 をセットすることにより、PN シーケンス・テストの PN ジェネレータをリセットすることができます。これらのテストはアナログ信号の有無によらず(有りの場合、アナログ信号は無視されます)実行することができますが、エンコード・クロックは必要です。詳細については、アプリケーション・ノート AN-877、「SPI を使った高速 ADC へのインターフェース」を参照してください。

# シリアル・ポート・インターフェース(SPI)

AD9286 シリアル・ポート・インターフェース(SPI)を使うと、ADC 内部に用意されている構造化されたレジスタ・スペースを介してコンバータの特定の機能または動作を設定することができます。SPI は、アプリケーションに応じて、柔軟性とカスタマイゼーションを強化します。シリアル・ポートを介してアドレスがアクセスされ、ポートを介して読み書きすることができます。メモリは、バイトで構成されており、さらにフィールドに分割できます。これについてはメモリ・マップのセクションに記載してあります。詳細については、アプリケーション・ノート AN-877、「SPI を使った高速 ADC へのインターフェース」を参照してください。

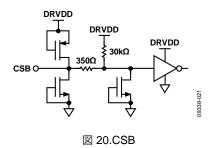

# SPI を使う設定

SCLK、SDIO、CSB の 3 本のピンによりこの ADC の SPI が定義されています (表 10 参照)。SCLK (シリアル・クロック)ピンは、ADC に対する読出し/書込みデータの同期に使用されます。SDIO (シリアル・データ入力/出力)ピンは 2 つの機能で共用されるピンであり、内部 ADC メモリ・マップ・レジスタに対するデータの送受信に使われます。CSB (チップ・セレクト・バー)はアクティブ・ローのコントロール信号であり、読出しサイクルと書込みサイクルをイネーブル/ディスエーブルします。

表 10.シリアル・ポート・インターフェース・ピン

| Pin  | Function                                                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK | Serial clock. A serial shift clock input that is used to synchronize serial interface reads and writes.                                                                             |

| SDIO | Serial data input/output. A dual-purpose pin that typically serves as an input or an output, depending on the instruction being sent and the relative position in the timing frame. |

| CSB  | Chip select bar. An active low control that gates the read and write cycles.                                                                                                        |

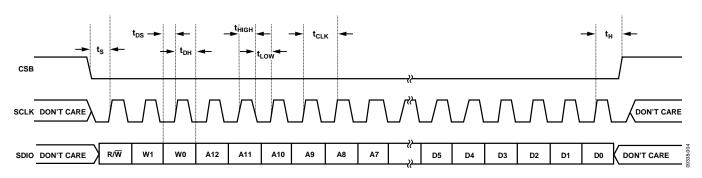

CSB の立下がりエッジと SCLK の立上がりエッジの組み合わせにより、フレームの開始が指定されます。シリアル・タイミングの例とその定義を図 33 に示します。

CSB を使用するその他のモードもあります。CSB はロー・レベルに固定することができ、これによりデバイスが常時イネーブルされます。これはストリーミングと呼ばれます。CSB をバイト間でハイ・レベルに維持して外部タイミングを延ばすことができます。CSB ピンをハイ・レベルに固定すると、SPI 機能はハイ・インピーダンス・モードになります。このモードではすべての SPI ピンは2つ目の機能になります。

命令フェーズでは、16 ビット命令が送信されます。命令フェーズ の後ろにはデータが続き、長さは W0 ビットと W1 ビットにより 指定されます(図 33 参照)。

すべてのデータは 8 ビット・ワードで構成されます。マルチバイト・シリアル・データの先頭バイトの先頭ビットは、発行されているのが読出しコマンドまたは書込みコマンドのいずれであるかを表示します。これにより、シリアル・データ入力/出力(SDIO)ピンがシリアル・フレームの該当する位置で入力と出力との間で方向を変えることができます。

命令フェーズでは、ワード長の他に、シリアル・フレームが読出し動作または書込み動作のいずれであるかを指定します。これにより、シリアル・ポートをチップへの書込みまたは内蔵メモリ値の読出しに使うことができます。命令がリードバック動作の場合、シリアル・データ入力/出力(SDIO)ピンの方向がシリアル・フレーム内の該当するポイントで入力から出力へ変わります。

データは、MSB ファースト・モードまたは LSB ファースト・モードで送信することができます。MSB ファーストはパワーアップ 時のデフォルトであり、SPI ポート設定レジスタを使って変えることができます。この機能およびその他の詳細については、アプリケーション・ノート AN-877、「SPI を使った高速 ADC へのインターフェース」を参照してください。

図 33.シリアル・ポート・インターフェースのタイミング図

#### ハードウェア・インターフェース

表 10 に示すピンにより、ユーザの書込みデバイスと AD9286 のシリアル・ポートとの間の物理インターフェースが構成されています。 SCLK ピンと CSB ピンは、SPI インターフェースを使用するとき入力として機能します。 SDIO ピンは双方向で、書込みフェーズでは入力として、リードバック時は出力として、それぞれ機能します。

SPI インターフェースは、FPGA またはマイクロコントローラから制御できるように十分な柔軟性を持っています。SPI 設定の一方法は、アプリケーション・ノート AN-812「Microcontroller-Based Serial Port Interface (SPI) Boot Circuit」に記載してあります。

コンバータのフル・ダイナミック性能が必要な区間では、SPI ポートをアクティブにしないようにしておく必要があります。 SCLK 信号、CSB 信号、SDIO 信号は一般に ADC クロックに同期しているため、これらの信号からのノイズがコンバータ性能を低下させることがあります。内蔵 SPI バスを他のデバイスに対して使うことが便利な場合には、このバスと AD9286 との間にバッファを設けて、クリティカルなサンプリング区間にコンバータ入力でこれらの信号が変化することを防止することが必要になります。

SPIインターフェースを使用しない場合には、SDIO/PWDNピンは他の機能に使用されます。デバイス・パワーオン時にこのピンをAVDDまたはグラウンドに接続すると、このピンは特定の機能として使われます。モード選択表(表 11 参照)に、AD9286でサポートしているピン接続による機能を示します。

表 11.モードの選択

| Pin           | External       | C                         |

|---------------|----------------|---------------------------|

| rın           | Voltage        | Configuration             |

| SDIO/PWDN     | AVDD (default) | Chip in full power-down   |

|               | AGND           | Normal operation          |

| <del>OE</del> | AVDD           | Outputs in high impedance |

|               | AGND (default) | Outputs enabled           |

#### SPI を使わない設定

SPI コントロール・レジスタにインターフェースしないアプリケーションでは、SDIO/PWDN ピンは、独立した CMOS 互換のコントロール・ピンとして使用することができます。デバイスがパワーアップすると、SDIO ピン、SCLK ピン、CSB ピンは、出力イネーブルとパワーダウンの機能制御用スタティック・コントロール・ラインとして使用されるものと見なされます。このモードで、CSB チップ・セレクトを AVDD に接続すると、シリアル・ポート・インターフェースがディスエーブルされます。

### SPI からアクセス可能な機能

表 12 に、SPI からアクセスできる一般的な機能の簡単な説明を示します。これらの機能は、アプリケーション・ノート AN-877、 「SPI を使った高速 ADC へのインターフェース」で詳しく説明しています。AD9286 デバイスに固有な機能は表 13 のセクションで説明します。

表 12.SPI を使ってアクセスできる機能

| Feature              | Description                                                         |

|----------------------|---------------------------------------------------------------------|

| Mode                 | Allows the user to set either power-down mode or standby mode       |

| Clock                | Allows the user to access the DCS via the SPI                       |

| Offset               | Allows the user to digitally adjust the converter offset            |

| Test I/O             | Allows the user to set test modes to have known data on output bits |

| Output Mode          | Allows the user to set up outputs                                   |

| Output Phase         | Allows the user to set the output clock polarity                    |

| Output Delay         | Allows the user to vary the DCO delay                               |

| Voltage<br>Reference | Allows the user to set the voltage reference                        |

# メモリ・マップ

# メモリ・マップ・レジスタ・テーブルの読出し

メモリ・マップ・レジスタ・テーブル(表 13)内の各行には 8 個の ビット・ロケーションがあります。メモリ・マップは大まかに、 チップ設定レジスタ(アドレス 0x00~アドレス 0x02)、デバイス・イ ンデックス・レジスタと転送レジスタ(アドレス 0x05 とアドレス 0xFF)、プログラム・レジスタ(アドレス 0x08~アドレス 0x38)の 3 つのセクションに分かれています。

表 13 には、各 16 進アドレスに対するデフォルトの 16 進値が記載してあります。先頭ビット 7 (MSB)の列は、デフォルト 16 進値の開始になります。この機能およびその他の詳細については、アプリケーション・ノート AN-877、「SPI を使った高速 ADC へのインターフェース」を参照してください。このドキュメントでは、レジスタ  $0x00\sim$ レジスタ 0xFF により制御される機能を詳しく説明しています。

#### 未使用ロケーション

SPI マップに記載されていないすべてのアドレスとビット・ロケーションは、このデバイスでは現在サポートされていません。有効アドレス・ロケーションの未使用ビットには0を書込む必要があります。アドレス・ロケーションの一部が未使用の場合にのみ、これらのロケーションへの書込みが必要です。アドレス・ロケーション全体が未使用の場合、SPI マップから削除されており(例えばアドレス 0x13)、このアドレス・ロケーションに対しては書込みを行わないでください。

#### デフォルト値

AD9286 のリセット後、クリティカルなレジスタにはデフォルト値がロードされます。レジスタのデフォルト値は、メモリ・マップ・レジスタ・テーブル(表 13)に記載してあります。

#### ロジック・レベル

ロジック・レベルは次のように定義します。

- 「ビットをセットする」は、「ビットをロジック 1 に設定する」または「ビットにロジック 1 を書込む」と同じ意味です。

- 「ビットをクリアする」は、「ビットをロジック 0 に設定する」または「ビットにロジック 0 を書込む」と同じ意味です。

#### 転送レジスタ・マップ

アドレス 0x08~アドレス 0x38 はシャドウされます。これらのアドレスに書込みを行っても、アドレス 0xFF に 0x01 を書込んで転送コマンドが発行されて、転送ビットがセットされるまで、デバイスの動作に反映されません。転送ビットをセットすると、これらのレジスタは内部で同時に更新されます。内部更新は転送ビットがセットされたときに実行され、ビットは自動的にクリアされます。

#### チャンネル固有のレジスタ

幾つかのチャンネル・セットアップ機能は、各チャンネルごとに 異なる設定が可能です。これらの場合、チャンネル・アドレス・ ロケーションは、内部で各チャンネルにコピーされます。これら のレジスタとビットは、メモリ・マップ・レジスタ・テーブルで ローカルと表示してあります。これらのローカル・レジスタとビ ットをアクセスするときは、レジスタ 0x05 内の該当するチャンネ ル1(ビットの)またはチャンネル 2(ビット1)をセットします。

両ビットがセットされている場合は、後続の書込みは両チャンネルのレジスタに対して行われます。読出しサイクルでは、チャンネル1またはチャンネル2の一方のみをセットして、2つのレジスタの内の1つを読出す必要があります。SPI読出しサイクルで両ビットがセットされていると、デバイスはチャンネル1の値を返します。メモリ・マップ・レジスタ・テーブルでグローバルと表示されているレジスタとビットは、デバイス全体またはチャンネル間に独立な設定が許容されていないチャンネル機能に対して有効です。レジスタ0x05内の設定は、グローバルなレジスタとビットに影響を与えません。

# メモリ・マップ・レジスタ・テーブル

表 13 に記載されていないすべてのアドレスとビット・ロケーションは、このデバイスでは現在サポートされていません。

表 13.メモリ・マップ・レジスタ

| Addr<br>(Hex) | Register<br>Name                | Bit 7<br>(MSB)                                                                                                                                                                                                                                                            | Bit 6                              | Bit 5      | Bit 4 | Bit 3 | Bit 2      | Bit 1                                                                                                      | Bit 0<br>(LSB)           | Default<br>Value<br>(Hex)                                                                                                                      | Default<br>Notes/<br>Comments                                                                                                    |

|---------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------|-------|-------|------------|------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Chip C        | Configuration Re                | gisters                                                                                                                                                                                                                                                                   |                                    | •          | •     | •     | •          | •                                                                                                          | •                        | •                                                                                                                                              | •                                                                                                                                |

| 0x00          | SPI port<br>configuration       | 0                                                                                                                                                                                                                                                                         | LSB first                          | Soft reset | 1     | 1     | Soft reset | LSB first                                                                                                  | 0                        | 0x18                                                                                                                                           | Nibbles are<br>mirrored so<br>that LSB-<br>first or MSB-<br>first mode<br>registers<br>correctly,<br>regardless of<br>shift mode |

| 0x01          | Chip ID<br>(global)             |                                                                                                                                                                                                                                                                           | 8-bit chip ID                      |            |       |       |            |                                                                                                            |                          | 0x0A                                                                                                                                           | Unique chip<br>ID used to<br>differentiate<br>devices; read<br>only                                                              |

| 0x02          | Chip grade<br>(global)          | Open                                                                                                                                                                                                                                                                      | Open Speed grade ID 100 = 500 MSPS |            |       |       |            |                                                                                                            |                          | 0x40                                                                                                                                           | Unique<br>speed grade<br>ID used to<br>differentiate<br>devices; read<br>only                                                    |

|               | Index and Tran                  | sfer Registers                                                                                                                                                                                                                                                            |                                    |            |       |       |            |                                                                                                            | T.==:                    | T                                                                                                                                              | Τ                                                                                                                                |

| 0x05          | Device<br>Index A               | Open ADC 2 default default                                                                                                                                                                                                                                                |                                    |            |       |       |            |                                                                                                            | 0xFF                     | Bits are set to<br>determine<br>which on-<br>chip device<br>receives the<br>next write<br>command;<br>default is all<br>devices on<br>the chip |                                                                                                                                  |

| 0xFF          | Transfer                        |                                                                                                                                                                                                                                                                           | Open Transfer                      |            |       |       |            |                                                                                                            |                          | 0xFF                                                                                                                                           | Synchronous<br>transfer of<br>data from<br>the master<br>shift register<br>to the slave                                          |

|               | m Registers (Ma                 | ay or may not                                                                                                                                                                                                                                                             | be indexed by d                    |            |       |       |            |                                                                                                            |                          | 1                                                                                                                                              | Τ                                                                                                                                |

| 0x08          | Modes<br>(global)               | Open                                                                                                                                                                                                                                                                      |                                    |            |       |       |            | nal power-dow<br>00: chip run<br>01: full power-<br>0: reserved<br>1: reserved                             |                          | 0x00                                                                                                                                           | Determines<br>various<br>generic<br>modes<br>of chip<br>operation                                                                |

| 0x09          | Clock<br>(global)               | Open Sample mode 0: simultaneous 1: interleaved                                                                                                                                                                                                                           |                                    |            |       |       | Open       | Clock<br>boost                                                                                             | Duty cycle<br>stabilizer | 0x09                                                                                                                                           |                                                                                                                                  |

| 0x0D          | Test mode (local)  BIST (local) | Open         Reset<br>PN23 gen         Reset<br>PN9 gen         Open         Output test mode<br>000: off<br>001: midscale short<br>010: +FS short<br>011: -FS short<br>100: checkerboard output<br>101: PN23 sequence<br>110: PN9 sequence<br>111: one-/zero-word toggle |                                    |            |       |       | 0x00       | When test<br>mode is set,<br>test data is<br>placed on<br>the output<br>pins in place<br>of normal<br>data |                          |                                                                                                                                                |                                                                                                                                  |

| UXUE          | BIST (local)                    |                                                                                                                                                                                                                                                                           |                                    | Open       |       |       | BIST init  | Open                                                                                                       | BIST enable              | UXUU                                                                                                                                           | B121 mod                                                                                                                         |

Rev. A — 23/27 —

| Addr<br>(Hex) | Register<br>Name                 | Bit 7<br>(MSB) | Bit 6                                                                | Bit 5 | Bit 4            | Bit 3 | Bit 2                           | Bit 1                                                     | Bit 0<br>(LSB)               | Default<br>Value<br>(Hex) | Default<br>Notes/<br>Comments                                                          |

|---------------|----------------------------------|----------------|----------------------------------------------------------------------|-------|------------------|-------|---------------------------------|-----------------------------------------------------------|------------------------------|---------------------------|----------------------------------------------------------------------------------------|

| 0x0F          | ADC input<br>(global/local)      |                |                                                                      | Open  |                  |       | Analog<br>disconnect<br>(local) | Common-<br>mode<br>input<br>enable<br>(global)            | Open                         | 0x00                      | comig                                                                                  |

| 0x10          | Offset (local)                   |                | O <sub>l</sub>                                                       | pen   |                  | 0     | 011<br>000<br>000<br>111        | complement f 1: +7 0: +6 01: +1 00: 0 1: -1 01: -7 00: -8 | ormat)                       | 0x00                      | Device<br>offset trim                                                                  |

| 0x14          | Output mode (local)              |                | Open                                                                 |       | Output<br>enable | Open  | Output<br>invert                | Data form                                                 | binary<br>complement<br>code | 0x00                      | Configures<br>the outputs<br>and the<br>format of the<br>data                          |

| 0x16          | Output phase (global)            | DCO invert     |                                                                      |       |                  | Open  |                                 |                                                           |                              | 0x00                      |                                                                                        |

| 0x18          | Voltage<br>reference<br>(global) |                | Open Voltage reference and input full-scale adjustment (see Table14) |       |                  |       |                                 |                                                           |                              | 0x00                      | Selects/<br>adjusts V <sub>REF</sub>                                                   |

| 0x24          | MISR LSB<br>(local)              |                | LSBs of multiple input shift register (MISR)                         |       |                  |       |                                 |                                                           |                              | 0x00                      | MISR least<br>significant<br>byte; read<br>only                                        |

| 0x25          | MISR MSB<br>(local)              |                | MSBs of multiple input shift register (MISR)                         |       |                  |       |                                 |                                                           |                              | 0x00                      | MISR most<br>significant<br>byte; read<br>only                                         |

| 0x37          | Timing<br>adjust (local)         |                | 0                                                                    | pen   |                  |       | 0000<br>0001                    | ning skew<br>0: 0.0 ps<br>1: 0.075 ps<br><br>1.125 ps     |                              | 0x00                      | Determines<br>the clock<br>delay that is<br>introduced<br>into the<br>sampling<br>path |

| 0x38          |                                  |                | 0                                                                    | pen   |                  |       | 0000<br>0001                    | iming skew<br>b: 0.0 ps<br>l: 1.2 ps<br><br>l: 18 ps      |                              | 0x00                      | Determines<br>the clock<br>delay that is<br>introduced<br>into the<br>sampling<br>path |

Rev. A — 24/27 —

# メモリ・マップ・レジスタの説明

レジスタ 0x00~レジスタ 0xFF で制御される機能の詳細については、アプリケーション・ノート AN-877「Interfacing to High Speed ADCs via SPI」を参照してください。

## リファレンス電圧 (レジスタ 0x18)

## ビット[7:5]—予約済み

## ビット[4:0]—リファレンス電圧

ビット[4:0] は、内部発生のリファレンス電圧を(したがってアナログ入力のフルスケールを)スケールします。容量負荷を小さくして外部から容易に駆動できるようにこのレジスタ内でリファレンス・ドライバを設定することができます。

$\mathbf{V}_{\text{REF}}$ 電圧と入力フルスケールとの関係は、式 7 で表されます。すべてのレジスタ設定値の一覧については、表 14 を参照してください。

$$Input\_Full\_Scale = V_{REF} \times 1.2 \tag{7}$$

表 14.V<sub>REF</sub> と入力フルスケール (レジスタ 0x18)

| Value | V <sub>REF</sub> (V) | Full Scale (V) |

|-------|----------------------|----------------|

| 0x14  | 0.844                | 1.013          |

| 0x15  | 0.857                | 1.028          |

| 0x16  | 0.87                 | 1.044          |

| 0x17  | 0.883                | 1.060          |

| 0x18  | 0.896                | 1.075          |

| 0x19  | 0.909                | 1.091          |

| 0x1A  | 0.922                | 1.106          |

| 0x1B  | 0.935                | 1.122          |

| 0x1C  | 0.948                | 1.138          |

| 0x1D  | 0.961                | 1.153          |

| 0x1E  | 0.974                | 1.169          |

| 0x1F  | 0.987                | 1.184          |

| 0x00  | 1                    | 1.200          |

| 0x01  | 1.013                | 1.216          |

| 0x02  | 1.026                | 1.231          |

| 0x03  | 1.039                | 1.247          |

| 0x04  | 1.052                | 1.262          |

| 0x05  | 1.065                | 1.278          |

| 0x06  | 1.078                | 1.294          |

| 0x07  | 1.091                | 1.309          |

| 0x08  | 1.104                | 1.325          |

| 0x09  | 1.117                | 1.340          |

| 0x0A  | 1.13                 | 1.356          |

| 0x0B  | 1.143                | 1.372          |

| 0x0C  | 1.156                | 1.387          |

| 0x0D  | 1.169                | 1.403          |

| 0x0E  | 1.182                | 1.418          |

| 0x0F  | 1.195                | 1.434          |

| 0x10  | 1.208                | 1.450          |

| 0x11  | 1.221                | 1.465          |

| 0x12  | 1.234                | 1.481          |

| 0x13  | External             | External × 1.2 |

# アプリケーション情報

#### デザイン・ガイドライン

1 つのシステムとして、AD9286 のデザインとレイアウトを開始する前に、特定のピンに必要とされる特別な回路接続とレイアウト条件を説明する次のガイドラインをお読みください。

#### 電源とグラウンドの推奨事項

電源を AD9286 に接続する際、別々の 2 電源を使うことが推奨されます。1つはアナログ用 1.8 V 電源 (AVDD)、もう1つはデジタル出力用 1.8 V 電源 (DRVDD)です。AVDD 電源と DVDD 電源に1つの 1.8 V を共通に使用しなければならない場合には、フェライト・ビードやフィルタ・チョークと個別のデカップリング・コンデンサを使用して、AVDDドメインと DRVDDドメインを分離する必要があります。高周波と低周波のデカップリングをカバーするために、種類の異なる複数のデカップリング・コンデンサを使うことができます。これらのコンデンサは、プリント回路ボード(PCB) レベルの入力ポイント近くに配置し、かつ短いパターンを使ってデバイス・ピンに接続します。

AD9286 をつかうときは、1 枚の PC ボード・グラウンド・プレーンで十分です。適切なデカップリングと PCB のアナログ、デジタル、クロックの各セクションの適切な分割により、最適性能を容易に実現することができます。

### エクスポーズド・パッド・サーマル・ヒート・シンクの推奨 事項

エクスポーズド・パッド (ピン 0) は AD9286 の唯一のグラウンド 接続であるため、PCB のアナログ・グラウンド (AGND)に接続する必要があります。最適な電気的および熱的性能を得るため、PCB 上のハンダ・マスクのない連続銅プレーンと AD9286 エクスポーズド・パッド(ピン 0)を接続してください。

銅プレーンには最小の熱抵抗になるように複数のビアを使用して、PCBの裏面へ放熱するようにします。これらのビアには非伝導性のエポキシを詰める必要があります。

ADC と PCB との接触面積と接着を最大にするため、シルクスクリーンで覆い、PCB の連続プレーンを複数の均一なセクションに分割してください。これにより、リフロー・プロセス時に ADC と PCB の間で複数の接続点を形成することができます。パーティションのない 1 枚の連続プレーンを使うと、ADC と PCB との間の接続点が確実に 1 個だけになります。チップ・スケール・パッケージのパッケージと PCB レイアウトの詳細については、http://www.analog.com/jp/index.html のアプリケーション・ノートAN-772「リード・フレーム・チップ・スケール・パッケージ (LFCSP) の設計および製造ガイド」を参照してください。

#### VCN

VCM ピンは、 $0.1 \mu$ F のコンデンサでグラウンドへデカップリング する必要があります。

#### **RBIAS**

AD9286 では、RBIAS ピンとグラウンドとの間に  $10 \text{ k}\Omega$  の抵抗を接続する必要があります。この抵抗は ADC コアのマスター電流リファレンスを設定するため、偏差 1%以下のものを使う必要があります。

#### リファレンス電圧のデカップリング

VREF ピンは、ESR の小さい  $1.0~\mu$ F のコンデンサと ESR の小さい 0.1口 $\mu$ F のセラミック・コンデンサとの並列接続により外部でグラウンドにデカップリングする必要があります。

#### SPI ポート

コンバータのフル・ダイナミック性能が必要な区間では、SPI ポートをアクティブにしないようにしておく必要があります。 SCLK 信号、CSB 信号、SDIO 信号は一般に ADC クロックに同期しているため、これらの信号からのノイズがコンバータ性能を低下させることがあります。内蔵 SPI バスを他のデバイスに対して使うことが便利な場合には、このバスと AD9286 との間にバッファを設けて、クリティカルなサンプリング区間にコンバータ入力でこれらの信号が変化することを防止することが必要になります。

# 外形寸法

# オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package<br>Option |

|--------------------|-------------------|--------------------------------------------------|-------------------|

| AD9286BCPZ-500     | −40°C to +85°C    | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ] | CP-48-12          |

| AD9286BCPZRL7-500  | −40°C to +85°C    | 48-Lead Lead Frame Chip Scale Package [LFCSP_VQ] | CP-48-12          |

| AD9286-500EBZ      |                   | Evaluation Board                                 |                   |

寸法: mm

Rev. A -27/27 –

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品