# 12ビット、80/105/125MSPS、 1.8V動作のA/Dコンバータ

AD9233

## 特長

1.8Vのアナログ電源動作

1.8~3.3V出力用電源

S/N比=69.5dBc (70.5dBFS) (70MHz入力まで)

SFDR=85dBc(70MHz入力まで) 低消費電力:125MSPS時で395mW

帯域幅650MHzの差動入力

電圧リファレンスおよびサンプル&ホールドアンプを内蔵

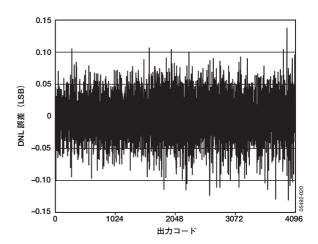

$DNL=\pm0.15LSB$

フレキシブルなアナログ入力:1~2Vp-p

データ形式:オフセット・バイナリ、2の補数、グレーコード クロックのデューティ・サイクル・スタビライザ

データ出力クロック

シリアル・ポート制御

デジタル・テスト・パターン(選択可能)生成機能内蔵

プログラマブルなクロック/データ配置

## アプリケーション

超音波装置

通信用レシーバのIFサンプリング IS-95、CDMA-One、IMT-2000 バッテリ駆動の計測器

ハンドヘルド・スコープメータ 低価格のデジタル・オシロスコープ

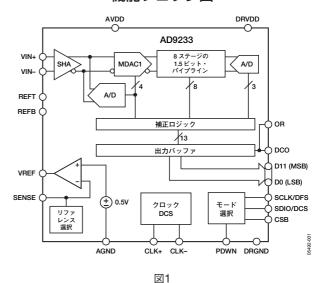

#### 概要

AD9233は1.8Vの単電源で動作するモノリシック、12ビット、80/105/125MSPSのA/Dコンバータ(ADC)で、高性能サンプル&ホールド・アンプ(SHA)と電圧リファレンスを内蔵しています。出力誤差補正ロジック付きのマルチステージ差動パイプライン・アーキテクチャに基づいて、125MSPSのデータ・レートで12ビット精度を提供し、全動作温度範囲でノー・ミスコードを保証します。

広帯域幅で真の差動入力を備えたSHAにより、ユーザはシングルエンド・アプリケーションを含めて各種の入力範囲とオフセットを選択できます。このSHAは、連続的なチャンネルでフルスケール電圧レベルの切替えを行う多重化システムや、ナイキスト・レートをはるかに超える周波数でのシングル・チャンネル入力のサンプリングに適しています。従来のADCに比べて省電力化と低価格化を実現したAD9233は、通信、画像処理、医療用超音波装置などのアプリケーションに最適です。

差動クロック入力を使用して、内部変換サイクルのすべてを制御します。デューティ・サイクル・スタビライザ(DCS)はクロック・デューティ・サイクルの幅広い変動を補償し、ADC全体にわたって優れた性能を維持します。

#### 機能ブロック図

デジタル出力データは、オフセット・バイナリ、グレーコード、2の補数の出力フォーマットのいずれかで提供されます。データ・クロック出力(DCO)は、受信ロジックの適正なラッチ・タイミングを保証します。

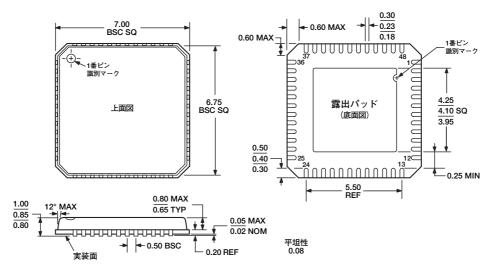

AD9233は48ピンLFCSPを採用しており、工業用温度範囲  $(-40\sim+85\%)$  で仕様を規定しています。

### 製品のハイライト

- 1. 最低1.8Vの単電源で動作します。1.8~3.3Vのロジック・ファミリーに対応した個別のデジタル出力ドライバ電源を提供します。

- 2. 特許取得済みのSHA入力は、225MHzまでの入力周波数に 対して優れた性能を維持します。

- 3. クロックDCSは、広範なクロック・パルス幅でADC全体に わたって優れた性能を維持します。

- 4. 標準シリアル・ポート・インターフェースは、データ形式の設定(オフセット・バイナリ、2の補数、グレーコード)、クロックDCS、パワーダウン、および電圧リファレンス・モードの有効化など、製品のさまざまな特性や機能に対応します。

- 5. AD9246とピン互換性があり、12ビット・システムから14 ビット・システムへの移行が容易です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

に属します。 ※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。 © 2006 Analog Devices, Inc. All rights reserved.

REV. A

本 社/〒105-6891

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル

電話03(5402)8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号 電話06(6350)6868

# **目次**

| 特長               | タイミング                   | 22 |

|------------------|-------------------------|----|

| アプリケーション1        | シリアル・ポート・インターフェース (SPI) | 23 |

| 概要1              | SPIによる設定                | 23 |

| 機能ブロック図1         | ハードウェア・インターフェース         | 23 |

| 製品のハイライト1        | SPIなしの設定                | 23 |

| 改訂履歴3            | メモリマップ                  | 24 |

| 仕様4              | メモリマップ・テーブルの読出し         | 24 |

| DC仕様4            | レイアウトのポイント              | 27 |

| AC仕様5            | 電源とグラウンドに関する推奨事項        | 27 |

| デジタル仕様6          | CML                     | 27 |

| スイッチング仕様7        | RBIAS                   |    |

| タイミング図7          | リファレンス・デカップリング          | 27 |

| 絶対最大定格8          | 評価用ボード                  | 28 |

| 熱抵抗8             | 電源                      | 28 |

| ESDに関する注意8       | 入力信号                    | 28 |

| ピン配置と機能の説明9      | 出力信号                    | 28 |

| 等価回路             | デフォルトの動作とジャンパ選択の設定      | 29 |

| 代表的な性能特性11       | その他のクロック設定              | 29 |

| 動作原理15           | その他のアナログ入力駆動設定          | 30 |

| アナログ入力に関する考慮事項15 | 回路図                     | 31 |

| 電圧リファレンス17       | 評価用ボードのレイアウト            | 36 |

| クロック入力の考慮事項18    | 部品表 (BOM)               | 39 |

| ジッタに関する考慮事項19    | 外形寸法                    |    |

| 消費電力とスタンバイ・モード20 | オーダー・ガイド                | 42 |

| デジタル出力21         |                         |    |

# 改訂履歴

| 8/06—Rev. 0 to Rev. A                                       |

|-------------------------------------------------------------|

| Updated Format                                              |

| Added 80 MSPS                                               |

| Deleted Figure 19, Figure 20, Figure 22, and Figure 23;     |

| Renumbered Sequentially                                     |

| Deleted Figure 24, Figure 25, and Figure 27 to Figure 29;   |

| Renumbered Sequentially                                     |

| Deleted Figure 31 and Figure 34; Renumbered Sequentially 13 |

| Deleted Figure 37, Figure 38, Figure 40, and Figure 41;     |

| Renumbered Sequentially                                     |

| Deleted Figure 46; Renumbered Sequentially                  |

| Deleted Figure 52; Renumbered Sequentially 16               |

| Changes to Figure 40                                        |

| Changes to Figure 46                                        |

| Inserted Figure 54; Renumbered Sequentially20               |

| Changes to Digital Outputs Section                          |

| Changes to Timing Section                                   |

| Added Data Clock Output (DCO) Section                       |

| Changes to Configuration Using the SPI Section and          |

| Configuration Without the SPI Section                       |

| Changes to Table 15                                         |

| Changes to Table 16                                         |

| Changes to Ordering Guide                                   |

4/06—Revision 0: Initial Version

REV. A -3-

# 仕様

## DC仕様

特に指定のない限り、AVDD=1.8V、DRVDD=2.5V、最大サンプル・レート、2Vp-p差動入力、1.0V内部リファレンス、AIN= -1.0dBFS、DCSイネーブル。

#### 表1

|                                                     |     | AD9 | 233BCF    | PZ-80     | AD92 | 233BCF    | Z-105     | AD92 | 233BCP    | Z-125     |         |

|-----------------------------------------------------|-----|-----|-----------|-----------|------|-----------|-----------|------|-----------|-----------|---------|

| パラメータ                                               | 温度  | Min | Тур       | Max       | Min  | Тур       | Max       | Min  | Тур       | Max       | 単位      |

| 分解能                                                 | 全範囲 | 12  |           |           | 12   |           |           | 12   |           |           | ビット     |

| 精度                                                  |     |     |           |           |      |           |           |      |           |           |         |

| ノー・ミスコード                                            | 全範囲 |     | 保証        |           |      | 保証        |           |      | 保証        |           |         |

| オフセット誤差                                             | 全範囲 |     | $\pm 0.3$ | $\pm 0.5$ |      | $\pm 0.3$ | $\pm 0.8$ |      | $\pm 0.3$ | $\pm 0.8$ | % FSR   |

| ゲイン誤差                                               | 全範囲 |     | $\pm 0.2$ | $\pm 4.7$ |      | $\pm 0.2$ | $\pm 4.9$ |      | $\pm 0.2$ | $\pm 3.9$ | % FSR   |

| 微分非直線性 (DNL)                                        | 全範囲 |     |           | $\pm 0.3$ |      |           | $\pm 0.5$ |      |           | $\pm 0.5$ | LSB     |

|                                                     | 25℃ |     | $\pm 0.2$ |           |      | $\pm 0.2$ |           |      | $\pm 0.2$ |           | LSB     |

| 積分非直線性 (INL)                                        | 全範囲 |     |           | $\pm 1.2$ |      |           | $\pm 1.2$ |      |           | $\pm 1.2$ | LSB     |

|                                                     | 25℃ |     | $\pm 0.5$ |           |      | $\pm 0.5$ |           |      | $\pm 0.5$ |           | LSB     |

| 温度ドリフト                                              |     |     |           |           |      |           |           |      |           |           |         |

| オフセット誤差                                             | 全範囲 |     | $\pm 15$  |           |      | $\pm 15$  |           |      | $\pm 15$  |           | ppm/℃   |

| ゲイン誤差                                               | 全範囲 |     | $\pm 95$  |           |      | $\pm 95$  |           |      | $\pm 95$  |           | ppm/℃   |

| 内部電圧リファレンス                                          |     |     |           |           |      |           |           |      |           |           |         |

| 出力電圧誤差(1Vモード)                                       | 全範囲 |     | $\pm 5$   | $\pm 20$  |      | $\pm 5$   | $\pm 35$  |      | $\pm 5$   | $\pm 35$  | mV      |

| 負荷レギュレーション(1.0mA時)                                  | 全範囲 |     | 7         |           |      | 7         |           |      | 7         |           | mV      |

| 入力換算ノイズ                                             |     |     |           |           |      |           |           |      |           |           |         |

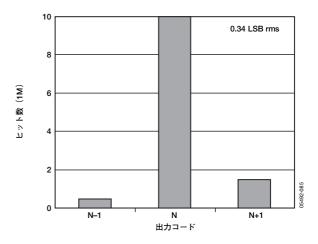

| VREF=1.0V                                           | 25℃ |     | 0.34      |           |      | 0.34      |           |      | 0.34      |           | LSB rms |

| アナログ入力                                              |     |     |           |           |      |           |           |      |           |           |         |

| 入力スパン、VREF=1.0V                                     | 全範囲 |     | 2         |           |      | 2         |           |      | 2         |           | V p-p   |

| 入力容量 <sup>2</sup>                                   | 全範囲 |     | 8         |           |      | 8         |           |      | 8         |           | pF      |

| リファレンス入力抵抗                                          | 全範囲 |     | 6         |           |      | 6         |           |      | 6         |           | kΩ      |

| 電源                                                  |     |     |           |           |      |           |           |      |           |           |         |

| 電源電圧                                                |     |     |           |           |      |           |           |      |           |           |         |

| AVDD                                                | 全範囲 | 1.7 | 1.8       | 1.9       | 1.7  | 1.8       | 1.9       | 1.7  | 1.8       | 1.9       | V       |

| DRVDD                                               | 全範囲 | 1.7 | 3.3       | 3.6       | 1.7  | 3.3       | 3.6       | 1.7  | 3.3       | 3.6       | V       |

| 電源電流                                                |     |     |           |           |      |           |           |      |           |           |         |

| $IAVDD^{\iota}$                                     | 全範囲 |     | 138       | 155       |      | 178       | 194       |      | 220       | 236       | mA      |

| $IDRVDD^{_1}$ (DRVDD=1.8V)                          | 全範囲 |     | 7         |           |      | 8         |           |      | 10        |           | mA      |

| $IDRVDD^{\scriptscriptstyle \perp}\ (DRVDD{=}3.3V)$ | 全範囲 |     | 12        |           |      | 14        |           |      | 17        |           | mA      |

| 消費電力                                                |     |     |           |           |      |           |           |      |           |           |         |

| DC入力                                                | 全範囲 |     | 248       | 279       |      | 320       | 350       |      | 395       | 425       | mW      |

| サイン波入力 <sup>1</sup> (DRVDD=1.8V)                    | 全範囲 |     | 261       |           |      | 335       |           |      | 415       |           | mW      |

| サイン波入力 <sup>1</sup> (DRVDD=3.3V)                    | 全範囲 |     | 288       |           |      | 365       |           |      | 452       |           | mW      |

| スタンバイ3                                              | 全範囲 |     | 40        |           |      | 40        |           |      | 40        |           | mW      |

| パワーダウン                                              | 全範囲 |     | 1.8       |           |      | 1.8       |           |      | 1.8       |           | mW      |

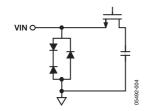

<sup>「</sup>低入力周波数、フルスケールのサイン波で、各出力ビットに約5pFの負荷を接続して測定。 <sup>2</sup> 入力容量とは、1本の差動入力ピンとAGNDとの間の実効容量です。アナログ入力の等価回路については、図4を参照してください。 <sup>3</sup> スタンバイ消費電力は、DC入力で、クロック(CLK)ピンを非アクティブ(AVDDまたはAGNDに接続)にして測定。

# AC仕様

特に指定のない限り、AVDD=1.8V、DRVDD=2.5V、最大サンプル・レート、2Vp-p差動入力、1.0V内部リファレンス、AIN= -1.0dBFS、DCSイネーブル。

表2

|                                                      | \   |      | 9233BC |       |      | 233BCF |       | 1    | 233BCP |       | W / ! |

|------------------------------------------------------|-----|------|--------|-------|------|--------|-------|------|--------|-------|-------|

| パラメータ」                                               | 温度  | Min  | Тур    | Max   | Min  | Тур    | Max   | Min  | Тур    | Max   | 単位    |

| S/N比                                                 |     |      |        |       |      |        |       |      |        |       |       |

| $f_{IN}=2.4MHz$                                      | 25℃ |      | 69.5   |       |      | 69.5   |       |      | 69.5   |       | dBc   |

| $f_{IN} = 70MHz$                                     | 25℃ |      | 69.5   |       |      | 69.5   |       |      | 69.5   |       | dBc   |

|                                                      | 全範囲 | 68.9 |        |       | 68.3 |        |       | 68.3 |        |       | dBc   |

| $f_{IN} = 100MHz$                                    | 25℃ |      | 69.4   |       |      | 69.4   |       |      | 69.4   |       | dBc   |

| $f_{IN} = 170MHz$                                    | 25℃ |      | 68.9   |       |      | 68.9   |       |      | 68.9   |       | dBc   |

| 信号/ノイズ&歪み(SINAD)                                     |     |      |        |       |      |        |       |      |        |       |       |

| $f_{IN}=2.4MHz$                                      | 25℃ |      | 69.2   |       |      | 69.2   |       |      | 69.2   |       | dBc   |

| $f_{IN} = 70MHz$                                     | 25℃ |      | 69.2   |       |      | 69.2   |       |      | 69.2   |       | dBc   |

|                                                      | 全範囲 | 68.5 |        |       | 67.3 |        |       | 67.3 |        |       | dBc   |

| $f_{IN} = 100MHz$                                    | 25℃ |      | 69.1   |       |      | 69.1   |       |      | 69.1   |       | dBc   |

| $f_{IN} = 170MHz$                                    | 25℃ |      | 68.6   |       |      | 68.6   |       |      | 68.6   |       | dBc   |

| 有効ビット数(ENOB)                                         |     |      |        |       |      |        |       |      |        |       |       |

| $f_{IN}=2.4MHz$                                      | 25℃ |      | 11.4   |       |      | 11.4   |       |      | 11.4   |       | ビッ    |

| $f_{IN} = 70MHz$                                     | 25℃ |      | 11.4   |       |      | 11.4   |       |      | 11.4   |       | ビッ    |

| $f_{IN} = 100MHz$                                    | 25℃ |      | 11.4   |       |      | 11.4   |       |      | 11.4   |       | ビッ    |

| $f_{IN} = 170MHz$                                    | 25℃ |      | 11.3   |       |      | 11.3   |       |      | 11.3   |       | ビッ    |

| 2次または3次の最悪高調波                                        |     |      |        |       |      |        |       |      |        |       |       |

| $f_{IN}=2.4MHz$                                      | 25℃ |      | -90.0  |       |      | -90.0  |       |      | -90.0  |       | dBc   |

| $f_{IN} = 70MHz$                                     | 25℃ |      | -85.0  |       |      | -85.0  |       |      | -85.0  |       | dBc   |

|                                                      | 全範囲 |      |        | -76.0 |      |        | -73.0 |      |        | -73.0 | dBc   |

| $f_{IN} = 100MHz$                                    | 25℃ |      | -85.0  |       |      | -85.0  |       |      | -85.0  |       | dBc   |

| $f_{IN} = 170MHz$                                    | 25℃ |      | -83.5  |       |      | -83.5  |       |      | -83.5  |       | dBc   |

| SFDR(スプリアスフリー・<br>ダイナミック・レンジ)                        |     |      |        |       |      |        |       |      |        |       |       |

| $f_{IN} = 2.4MHz$                                    | 25℃ |      | 90.0   |       |      | 90.0   |       |      | 90.0   |       | dBc   |

| $f_{IN} = 70MHz$                                     | 25℃ |      | 85.0   |       |      | 85.0   |       |      | 85.0   |       | dBc   |

|                                                      | 全範囲 | 76.0 |        |       | 73.0 |        |       | 73.0 |        |       | dBc   |

| $f_{IN} = 100MHz$                                    | 25℃ |      | 85.0   |       |      | 85.0   |       |      | 85.0   |       | dBc   |

| $f_{IN} = 170MHz$                                    | 25℃ |      | 83.5   |       |      | 83.5   |       |      | 83.5   |       | dBc   |

| その他の最悪高調波/スプリアス                                      |     |      |        |       |      |        |       |      |        |       |       |

| $f_{IN}$ =2.4MHz                                     | 25℃ |      | -90.0  |       |      | -90.0  |       |      | -90.0  |       | dBc   |

| $f_{IN} = 70MHz$                                     | 25℃ |      | -90.0  |       |      | -90.0  |       |      | -90.0  |       | dBc   |

|                                                      | 全範囲 |      |        | -85.0 |      |        | -81.0 |      |        | -81.0 | dBc   |

| $f_{IN} = 100MHz$                                    | 25℃ |      | -90.0  |       |      | -90.0  |       |      | -90.0  |       | dBc   |

| $f_{IN} = 170MHz$                                    | 25℃ |      | -90.0  |       |      | -90.0  |       |      | -90.0  |       | dBc   |

| 2調波SFDR                                              |     |      |        |       |      |        |       |      |        |       |       |

| $f_{IN}$ =30MHz (-7dBFS),<br>31MHz (-7dBFS)          | 25℃ |      | 87     |       |      | 87     |       |      | 85     |       | dBFS  |

| f <sub>IN</sub> =170MHz (-7dBFS),<br>171MHz (-7dBFS) | 25℃ |      | 83     |       |      | 83     |       |      | 84     |       | dBFS  |

| アナログ入力帯域幅                                            | 25℃ |      | 650    |       |      | 650    |       |      | 650    |       | MHz   |

<sup>&</sup>lt;sup>1</sup> パラメータの完全な定義については、AN-835『Understanding High Speed ADC Testing and Evaluation』を参照してください。

REV. A — 5 —

# デジタル仕様

特に指定のない限り、AVDD=1.8V、DRVDD=2.5V、最大サンプル・レート、2Vp-p差動入力、1.0V内部リファレンス、AIN= -1.0dBFS、DCSイネーブル。

## 表3

| パラメータ                                               | 温度     | Min   | AD9233BCPZ-<br>Typ | 80/105/125<br>Max | 単位    |

|-----------------------------------------------------|--------|-------|--------------------|-------------------|-------|

|                                                     | 77.2   |       | . , , ,            |                   | , i=  |

| 準拠ロジック                                              |        |       | CMOS/LVDS          | /I VPFCI          |       |

| 内部同相バイアス                                            | 全範囲    |       | 1.2                | LVILCE            | v     |

| 差動入力電圧                                              | 全範囲    | 0.2   | 1.2                | 6                 | V p-p |

| 入力電圧範囲                                              | 全範囲    | AVDD- | -0.3               | AVDD+1.6          | V     |

| 入力同相電圧範囲                                            | 全範囲    | 1.1   | 0.5                | AVDD 11.0         | v     |

| ハイレベル入力電圧 ( <b>V</b> <sub>H</sub> )                 | 全範囲    | 1.2   |                    | 3.6               | v     |

| ローレベル入力電圧 (V <sub>II</sub> )                        | 全範囲    | 0     |                    | 0.8               | v     |

| ハイレベル入力電流 (I <sub>II</sub> )                        | 全範囲    | -10   |                    | +10               | μA    |

| ローレベル入力電流 (I <sub>II</sub> )                        | 全範囲    | -10   |                    | +10               | μΑ    |

| 入力抵抗                                                | 全範囲    | 8     | 10                 | 12                | kΩ    |

| 入力容量                                                | 全範囲    |       | 4                  |                   | pF    |

| ロジック入力(SCLK/DFS、OE、PWDN)                            | 11,011 |       |                    |                   | F-    |

| ハイレベル入力電圧( $V_{ m H}$ )                             | 全範囲    | 1.2   |                    | 3.6               | V     |

| ローレベル入力電圧 (V <sub>II</sub> )                        | 全範囲    | 0     |                    | 0.8               | v     |

| ハイレベル入力電流 (I <sub>H</sub> )                         | 全範囲    | -50   |                    | <sup>-75</sup>    | μΑ    |

| ローレベル入力電流 (I <sub>II</sub> )                        | 全範囲    | -10   |                    | +10               | μΑ    |

| 入力抵抗                                                | 全範囲    |       | 30                 |                   | kΩ    |

| 入力容量                                                | 全範囲    |       | 2                  |                   | pF    |

| ロジック入力(CSB)                                         |        |       |                    |                   | Г     |

| ハイレベル入力電圧( $V_{ m H}$ )                             | 全範囲    | 1.2   |                    | 3.6               | V     |

| ローレベル入力電圧 (V <sub>II</sub> )                        | 全範囲    | 0     |                    | 0.8               | V     |

| ハイレベル入力電流 (I <sub>II</sub> )                        | 全範囲    | -10   |                    | +10               | μA    |

| ローレベル入力電流 (I <sub>II</sub> )                        | 全範囲    | +40   |                    | +135              | μA    |

| 入力抵抗                                                | 全範囲    |       | 26                 |                   | kΩ    |

| 入力容量                                                | 全範囲    |       | 2                  |                   | pF    |

| ロジック入力(SDIO/DCS)                                    |        |       |                    |                   |       |

| ハイレベル入力電圧( $\mathbf{V}_{\mathrm{H}}$ )              | 全範囲    | 1.2   |                    | DRVDD+0.3         | V     |

| ローレベル入力電圧 $(V_{II})$                                | 全範囲    | 0     |                    | 0.8               | v     |

| ハイレベル入力電流(I <sub>H</sub> )                          | 全範囲    | -10   |                    | +10               | μA    |

| ローレベル入力電流( $I_{\Pi}$ )                              | 全範囲    | +40   |                    | +130              | μA    |

| 入力抵抗                                                | 全範囲    |       | 26                 |                   | kΩ    |

| 入力容量                                                | 全範囲    |       | 5                  |                   | pF    |

| デジタル出力                                              |        |       |                    |                   |       |

| DRVDD=3.3V                                          |        |       |                    |                   |       |

| ハイレベル出力電圧( $V_{OH}$ 、 $I_{OH}$ $=50\mu A$ )         | 全範囲    | 3.29  |                    |                   | V     |

| ハイレベル出力電圧 $(V_{OH},\ I_{OH} = 0.5 mA)$              | 全範囲    | 3.25  |                    |                   | V     |

| ローレベル出力電圧( $V_{OL}$ 、 $I_{OL}$ =1.6mA)              | 全範囲    |       |                    | 0.2               | V     |

| ローレベル出力電圧( $V_{OL}$ 、 $I_{OL} = 50 \mu A$ )         | 全範囲    |       |                    | 0.05              | V     |

| DRVDD=1.8V                                          |        |       |                    |                   |       |

| ハイレベル出力電圧( $V_{OH}$ 、 $I_{OH}$ = $50\mu A$ )        | 全範囲    | 1.79  |                    |                   | V     |

| ハイレベル出力電圧( $V_{ m OH}$ 、 $I_{ m OH}{=}0.5{ m mA}$ ) | 全範囲    | 1.75  |                    |                   | V     |

| ローレベル出力電圧( $V_{OL}$ 、 $I_{OL}$ =1.6 $mA$ )          | 全範囲    |       |                    | 0.2               | V     |

| ローレベル出力電圧( $V_{OL}$ 、 $I_{OL}$ = $50\mu A$ )        | 全範囲    |       |                    | 0.05              | V     |

# スイッチング仕様

特に指定のない限り、AVDD=1.8V、DRVDD=2.5V。

|                                         |     | AD9  | 9233BC | PZ-80 | AD9  | 233BC | PZ-105 | ADS | 233BC | PZ-125 |        |

|-----------------------------------------|-----|------|--------|-------|------|-------|--------|-----|-------|--------|--------|

| パラメータ」                                  | 温度  | Min  | Тур    | Max   | Min  | Тур   | Max    | Min | Тур   | Max    | 単位     |

| クロック入力パラメータ                             |     |      |        |       |      |       |        |     |       |        |        |

| 変換レート (DCSイネーブル)                        | 全範囲 | 20   |        | 80    | 20   |       | 105    | 20  |       | 125    | MSPS   |

| 変換レート (DCSディスエーブル)                      | 全範囲 | 10   |        | 80    | 10   |       | 105    | 10  |       | 125    | MSPS   |

| CLK周期                                   | 全範囲 | 12.5 |        |       | 9.5  |       |        | 8   |       |        | ns     |

| ハイレベルのCLKパルス幅<br>(DCSイネーブル)             | 全範囲 | 3.75 | 6.25   | 8.75  | 2.85 | 4.75  | 6.65   | 2.4 | 4     | 5.6    | ns     |

| ハイレベルのCLKパルス幅<br>(DCSディスエーブル)           | 全範囲 | 5.63 | 6.25   | 6.88  | 4.28 | 4.75  | 5.23   | 3.6 | 4     | 4.4    | ns     |

| データ出力パラメータ                              |     |      |        |       |      |       |        |     |       |        |        |

| データ伝播遅延 (t <sub>PD</sub> ) <sup>2</sup> | 全範囲 | 3.1  | 3.9    | 4.8   | 3.1  | 3.9   | 4.8    | 3.1 | 3.9   | 4.8    | ns     |

| DCO伝播遅延(t <sub>DCO</sub> )              | 全範囲 |      | 4.4    |       |      | 4.4   |        |     | 4.4   |        | ns     |

| セットアップ時間( $t_{ m s}$ )                  | 全範囲 | 4.9  | 5.7    |       | 3.4  | 4.3   |        | 2.6 | 3.5   |        | ns     |

| ホールド時間 (t <sub>H</sub> )                | 全範囲 | 5.9  | 6.8    |       | 4.4  | 5.3   |        | 3.7 | 4.5   |        | ns     |

| パイプライン遅延 (レイテンシ)                        | 全範囲 |      | 12     |       |      | 12    |        |     | 12    |        | サイクル   |

| アパーチャ遅延(t <sub>A</sub> )                | 全範囲 |      | 0.8    |       |      | 0.8   |        |     | 0.8   |        | ns     |

| アパーチャ不確定性(ジッタ、 $t_{ m J}$ )             | 全範囲 |      | 0.1    |       |      | 0.1   |        |     | 0.1   |        | ps rms |

| ウェイクアップ時間3                              | 全範囲 |      | 350    |       |      | 350   |        |     | 350   |        | ms     |

| 範囲外からの回復時間                              | 全範囲 |      | 2      |       |      | 2     |        |     | 3     |        | サイクル   |

| シリアル・ポート・インターフェース⁴                      |     |      |        |       |      |       |        |     |       |        |        |

| SCLK周期(t <sub>CLK</sub> )               | 全範囲 | 40   |        |       | 40   |       |        | 40  |       |        | ns     |

| $SCLK$ のハイレベル・パルス幅の時間( $t_{HI}$ )       | 全範囲 | 16   |        |       | 16   |       |        | 16  |       |        | ns     |

| $SCLK$ のローレベル・パルス幅の時間( $t_{LO}$ )       | 全範囲 | 16   |        |       | 16   |       |        | 16  |       |        | ns     |

| SDIOからSCLKまでのセットアップ時間( $t_{DS}$ )       | 全範囲 | 5    |        |       | 5    |       |        | 5   |       |        | ns     |

| SDIOからSCLKまでのホールド時間( $t_{DH}$ )         | 全範囲 | 2    |        |       | 2    |       |        | 2   |       |        | ns     |

| CSBからSCLKまでのセットアップ時間( $t_s$ )           | 全範囲 | 5    |        |       | 5    |       |        | 5   |       |        | ns     |

| $CSB$ から $SCLK$ までのホールド時間( $t_H$ )      | 全範囲 | 2    |        |       | 2    |       |        | 2   |       |        | ns     |

<sup>「</sup>パラメータの完全な定義については、AN835 『Understanding High Speed ADC Testing and Evaluation』を参照してください。

出力遅延は、各出力に5pFの負荷を接続して、CLK50%変化からデータ50%変化まで測定。

ウェイクアップ時間はデカップリング・コンデンサの値に依存。この値はREFTとREFB間のコンデンサ0.1μFで表示。

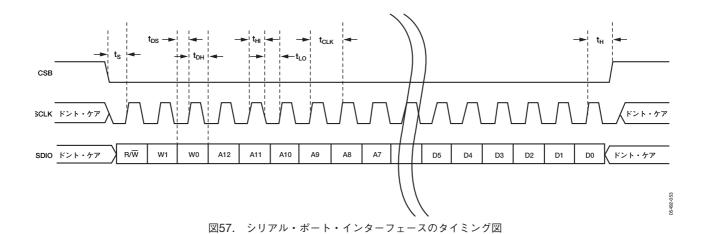

図57および「シリアル・ポート・インターフェース(SPI)」を参照してください。

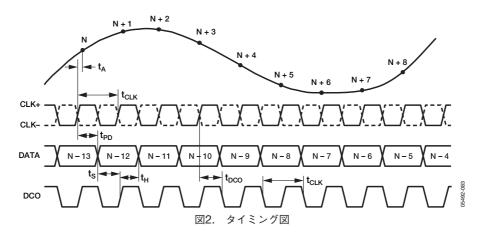

## タイミング図

REV. A -7-

# 絶対最大定格

#### 表5

| パラメータ             | 定格值                       |

|-------------------|---------------------------|

| 電気的条件             |                           |

| AGNDに対するAVDD      | $-0.3 \sim +2.0 \text{V}$ |

| DRGNDに対するDRVDD    | $-0.3 \sim +3.9 \text{V}$ |

| DRGNDに対するAGND     | $-0.3 \sim +0.3 \text{V}$ |

| DRVDDに対するAVDD     | $-3.9 \sim +2.0 \text{V}$ |

| DRGNDに対するD0~D11   | $-0.3V\sim$ DRVDD+0.3V    |

| DRGNDに対するDCO      | $-0.3V\sim$ DRVDD+0.3V    |

| DRGNDに対するOR       | $-0.3V\sim$ DRVDD+0.3V    |

| AGNDに対するCLK+      | $-0.3\sim +3.9V$          |

| AGNDに対するCLK-      | $-0.3\sim +3.9V$          |

| AGNDに対するVIN+      | $-0.3V\sim AVDD+1.3V$     |

| AGNDに対するVIN-      | $-0.3V\sim AVDD+1.3V$     |

| AGNDに対するVREF      | $-0.3V\sim AVDD+0.2V$     |

| AGNDに対するSENSE     | $-0.3V\sim AVDD+0.2V$     |

| AGNDに対するREFT      | $-0.3V\sim AVDD+0.2V$     |

| AGNDに対するREFB      | $-0.3V\sim AVDD+0.2V$     |

| DRGNDに対するSDIO/DCS | $-0.3V\sim$ DRVDD+0.3V    |

| AGNDに対するPDWN      | $-0.3\sim +3.9V$          |

| AGNDに対するCSB       | $-0.3 \sim +3.9 \text{V}$ |

| AGNDに対するSCLK/DFS  | $-0.3 \sim +3.9 \text{V}$ |

| AGNDに対するOEB       | $-0.3 \sim +3.9 \text{V}$ |

| 環境条件              |                           |

| 保存温度範囲            | -65~+125°C                |

| 動作温度範囲            | -40~+85°C                 |

| ピン温度(ハンダ処理10秒)    | 300℃                      |

| ジャンクション温度         | 150℃                      |

左記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

#### 熱抵抗

露出パドルはLFCSPパッケージのグラウンド・プレーンにハンダ付けしてください。パドルをカスタマ・ボードにハンダ付けすれば、ハンダ接続部の信頼性を高めパッケージの熱性能を最大化できます。

#### 表6. 熱抵抗

| パッケージ・タイプ           | $\theta_{JA}$ | $\theta_{JC}$ | 単位  |

|---------------------|---------------|---------------|-----|

| 48ピンLFCSP (CP-48-3) | 26.4          | 2.4           | ℃/W |

$\theta_{JA}$ および $\theta_{JC}$ (Typ値)は、自然空冷で4層ボードを使って仕様規定されます。空気流があると放熱効果が高まり、 $\theta_{JA}$ が小さくなります。また、メタル・パターン、スルーホール、グラウンド・プレーン、電源プレーンからパッケージ・ピンへ直接接続されるメタルが増えると、 $\theta_{JA}$ が小さくなります。

## 注意\_

ESD (静電放電)の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

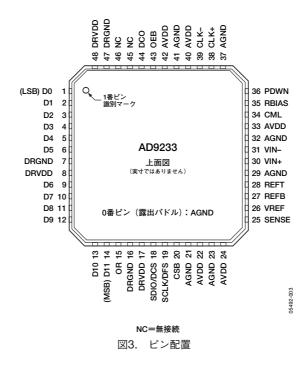

# ピン配置と機能の説明

表7. ピン機能の説明

| <br>ピン番号                  | 記号                  | 説明                                                                                                |

|---------------------------|---------------------|---------------------------------------------------------------------------------------------------|

| 0, 21, 23, 29, 32, 37, 41 | AGND                | アナログ・グラウンド。(0番ピンはパッケージ下部の露出熱パッドです。)                                                               |

| 1~6, 9~14                 | D0 (LSB) ~D11 (MSB) | データ出力ビット                                                                                          |

| 7, 16, 47                 | DRGND               | デジタル出力グラウンド                                                                                       |

| 8, 17, 48                 | DRVDD               | デジタル出力ドライバ電源(1.8~3.3V)                                                                            |

| 15                        | OR                  | アウト・オブ・レンジ・インジケータ                                                                                 |

| 18                        | SDIO/DCS            | SPI <sup>®</sup> (シリアル・ポート・インターフェース) データ入出力 (シリアル・ポート・モード)、デューティ・サイクル・スタビライザ選択 (外部ピンモード)。表 10を参照。 |

| 19                        | SCLK/DFS            | SPI (シリアル・ポート・インターフェース) クロック (シリアル・ポート・モード)、データ形式選択ピン (外部ピン・モード)。表10を参照。                          |

| 20                        | CSB                 | SPI (シリアル・ポート・インターフェース) チップ・セレクト (アクティブ・ロー)。                                                      |

| 22, 24, 33, 40, 42        | AVDD                | アナログ電源                                                                                            |

| 25                        | SENSE               | リファレンス・モード選択。表9を参照。                                                                               |

| 26                        | VREF                | 電圧リファレンス入出力                                                                                       |

| 27                        | REFB                | 差動リファレンス (-)                                                                                      |

| 28                        | REFT                | 差動リファレンス (+)                                                                                      |

| 30                        | VIN+                | アナログ入力ピン (+)                                                                                      |

| 31                        | VIN-                | アナログ入力ピン (-)                                                                                      |

| 34                        | CML                 | 同相レベル・バイアス出力                                                                                      |

| 35                        | RBIAS               | 外部バイアス抵抗接続。このピンとアナログ・グラウンド(AGND)の間に $10$ kΩ の抵抗を接続します。                                            |

| 36                        | PDWN                | パワーダウン機能選択                                                                                        |

| 38                        | CLK+                | クロック入力 (+)                                                                                        |

| 39                        | CLK-                | クロック入力 (一)                                                                                        |

| 43                        | OEB                 | 出力イネーブル (アクティブ・ロー)                                                                                |

| 44                        | DCO                 | データ・クロック出力                                                                                        |

| 45、46                     | NC                  | 無接続                                                                                               |

REV. A — 9 —

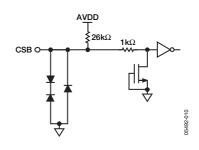

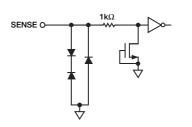

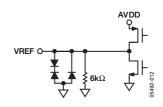

# 等価回路

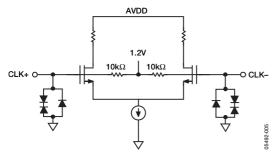

図4. アナログ入力等価回路

図5. クロック入力等価回路

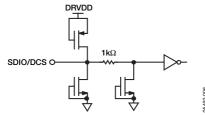

図6. SDIO/DCS入力等価回路

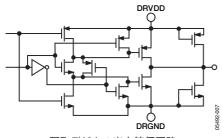

図7.デジタル出力等価回路

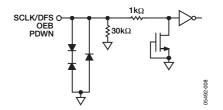

図8. SCLK/DFS、OEB、PDWN入力等価回路

図9. CSB入力等価回路

図10. 等価SENSE回路

図11. 等価VREF回路

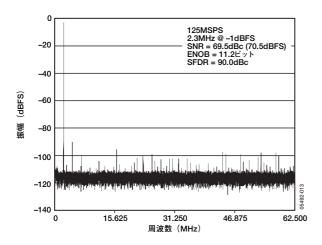

# 代表的な性能特性

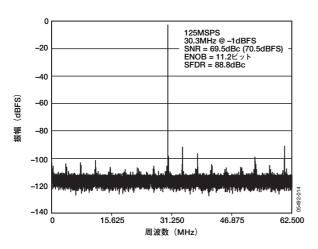

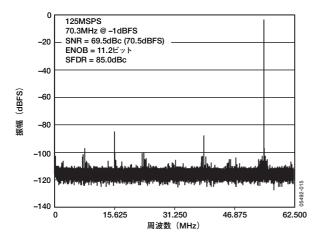

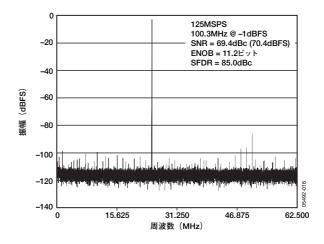

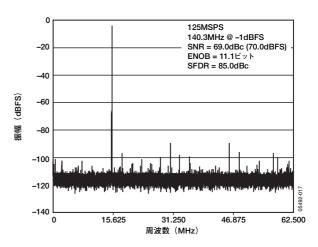

特に指定のない限り、AVDD=1.8V、DRVDD=2.5V、最大サンプル・レート、DCSイネーブル、1V内部リファレンス、2Vp-p差動入力、AIN=-1.0dBFS、64kサンプル、 $T_A$ =25 $^{\circ}$ C。すべての図は全速度グレードの代表的な性能を示しています。

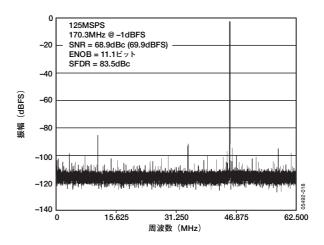

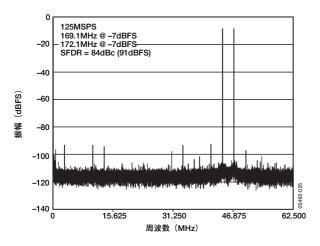

図12. AD9233-125: 単周波FFT (F<sub>IN</sub>=2.3MHz)

図13. AD9233-125: 単周波FFT (F<sub>IN</sub>=30.3MHz)

図14. AD9233-125: 単周波FFT (F<sub>IN</sub>=70.3MHz)

図15. AD9233-125:単周波FFT (F<sub>IN</sub>=100.3MHz)

図16. AD9233-125: 単周波FFT (F<sub>IN</sub>=140.3MHz)

図17. AD9233-125: 単周波FFT (F<sub>IN</sub>=170.3MHz)

REV. A — 11 —

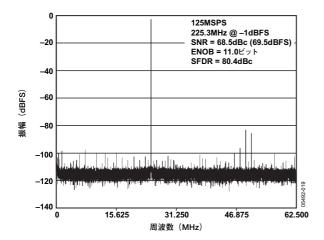

図18. AD9233-125:単周波FFT (F<sub>IN</sub>=225.3MHz)

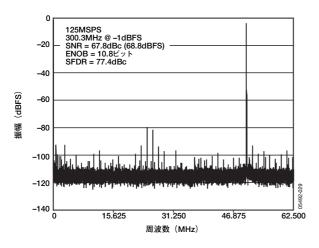

図19. AD9233-125:単周波FFT (F<sub>IN</sub>=300.3MHz)

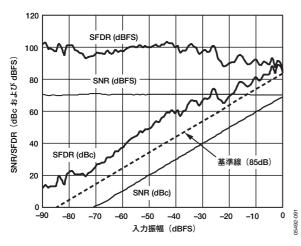

図20. AD9233:入力振幅(AIN)対 単周波 SNR/SFDR( $F_{IN}$ =2.4MHz)

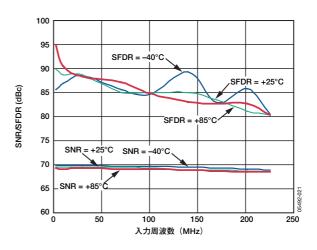

図21. AD9233: 入力周波数(F<sub>IN</sub>)対 単周波 SNR/SFDRと温度の関係 (2Vp-pフルスケール)

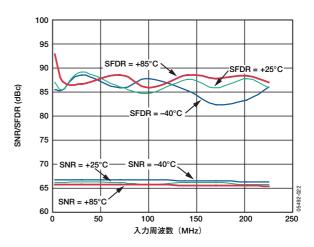

図22. AD9233:入力周波数 (F<sub>IN</sub>) 対 単周波 SNR/SFDRと温度の関係 (1Vp-pフルスケール)

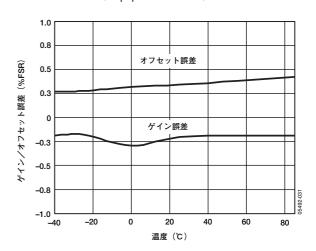

図23. AD9233: ゲインとオフセットの 温度特性

— 12 — REV. A

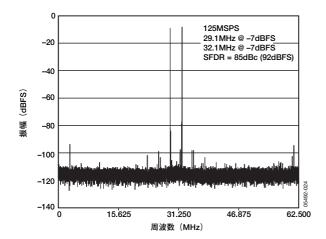

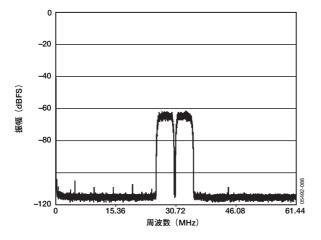

図24. AD9233-125:2周波FFT  $(F_{IN1}{=}29.1 MHz, F_{IN2}{=}32.1 MHz)$

図25. AD9233-125:2周波FFT (F<sub>IN1</sub>=169.1MHz、F<sub>IN2</sub>=172.1MHz)

図26. AD9233-125:2つの64k WCDMA キャリア ( $F_{IN1}$ =215.04MHz、  $F_{S}$ =122.88MSPS)

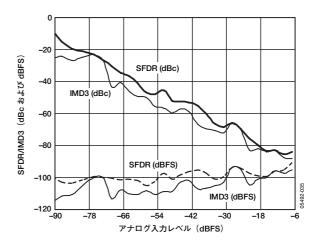

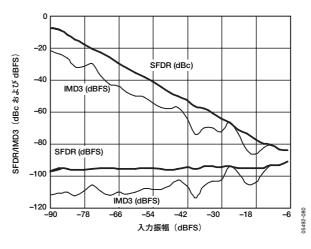

図27. AD9233:入力振幅(AIN) 対 2周波 SFDR/IMD( $F_{IN1}$ =29.1MHz、 $F_{IN2}$ =32.1MHz)

図28. AD9233:入力振幅(AIN)対 2周波 SFDR/IMD(F<sub>IN1</sub>=169.1MHz、 F<sub>IN2</sub>=172.1MHz)

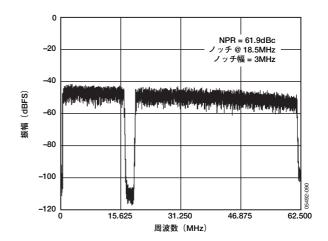

図29. AD9233-125:ノイズ電力比

REV. A — 13 —

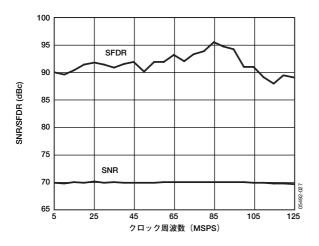

図30. AD9233:クロック周波数  $(F_S)$  対 単周波 SNR/SFDR  $(F_{IN}=2.4 MHz)$

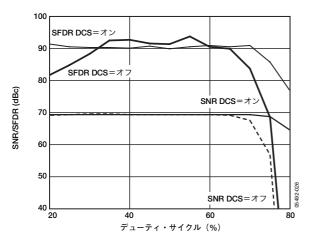

図31. AD9233:デューティ・サイクル 対 SNR/SFDR ( $F_{IN}$ =10.3MHz)

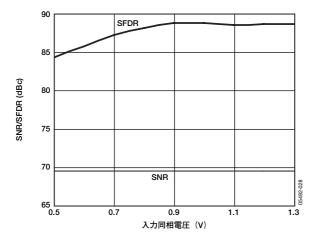

図32. AD9233:入力同相電圧  $(V_{CM})$  対 SNR/SFDR  $(F_{IN}=30MHz)$

図33. AD9233: グラウンド入力のヒストグラム

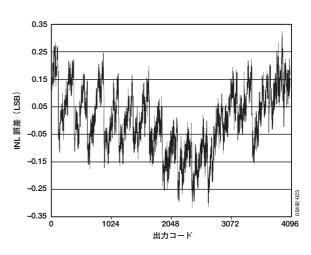

$\boxtimes 34.$  AD9233: INL (F<sub>IN</sub>=10.3MHz)

$\boxtimes 35.$  AD9233: DNL (F<sub>IN</sub>=10.3MHz)

— 14 — REV. A

# 動作原理

AD9233のアーキテクチャは、フロントエンドのサンプル&ホールド・アンプ (SHA) と、これに続くパイプライン化されたスイッチド・キャパシタ型ADCから構成されています。各ステージからの量子化された出力は、デジタル補正ロジック内で結合されて最終の12ビットになります。このパイプライン・アーキテクチャでは、最初のステージで新しい入力サンプルを処理している間に、残りのステージで前のサンプル値の処理を並行して行うことができます。サンプリングはクロックの立上がりエッジで行われます。

パイプラインの最終ステージ以外の各ステージは、スイッチド・キャパシタD/Aコンバータ(DAC)に接続された低分解能のフラッシュADCとステージ間残留アンプ(MDAC)により構成されています。この残留アンプは、再生されたDAC出力とパイプラインの次のステージに対するフラッシュ入力の差を増幅します。各ステージ内で冗長な1ビットを使って、フラッシュ誤差のデジタル補正を実現しています。最終ステージはフラッシュADCのみで構成されています。

入力ステージの差動SHAは、差動モードまたはシングルエンド・モードでAC結合またはDC結合を行うことができます。出力ステージのブロックでは、データの整列を行い、誤差補正を実行した後に、データを出力バッファに渡します。出力バッファは別電源から駆動されるため、出力電圧振幅の調整が可能です。パワーダウン時には、出力バッファは高インピーダンス状態になります。

## アナログ入力に関する考慮事項

AD9233のアナログ入力は差動スイッチド・キャパシタ型のSHAであり、差動入力信号の処理で最適な性能を提供します。

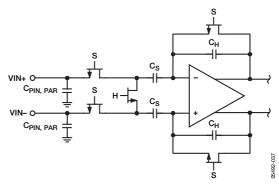

図36に示すように、クロック信号を使って、SHAのサンプル・モードとホールド・モードを交互に切り替えます。SHAがサンプル・モードに切り替わるときは、信号源がサンプル・コンデンサを充電して、クロック・サイクルの1/2以内に整定する必要があります。各入力端子に小さい抵抗を直列に挿入することによって、駆動源の出力ステージからのピーク過渡電流を抑える役割を果たします。

シャント・コンデンサを入力間に接続して、動的充電電流を供給することもできます。この受動回路はADCの入力でローパス・フィルタを構成するため、正確な値はアプリケーションに基づいて決定する必要があります。

IFのアンダーサンプリング・アプリケーションでは、このシャント・コンデンサはすべて除去する必要があります。信号源インピーダンスとこれらのコンデンサの組み合わせにより、入力帯域幅が制限されます。詳細については、アプリケーション・ノートAN-742『Frequency Domain Response of Switched-Capacitor ADCs』、AN-827『A Resonant Approach To Interfacing Amplifiers to Switched-Capacitor ADCs』、およびAnalog Dialog(技術資料)の「Transformer-Coupled Front-End for Wideband A/D Converters」を参照してください。

図36. スイッチド・キャパシタ型SHAの入力

最適な動的性能を得るには、VIN+とVIN-を駆動する信号源インピーダンスが一致していて、同相整定誤差が対称になる必要があります。そうすることによってこれらの誤差は、ADCの同相ノイズ除去性能により最小限化されます。

内部の差動リファレンス・バッファは、2つのリファレンス電圧を発生させ、これらがADCコアの入力スパンを決定します。ADCコアのスパンは、VREFの2倍となるようバッファによって設定されます。ユーザはリファレンス電圧を使用できません。2つのバイパス・ポイントREFTとREFBはデカップリングして、内部リファレンス・バッファによるノイズを低減します。「レイアウトのポイント」に示すように、REFTは $0.1\mu$ FコンデンサでREFBにデカップリングします。

#### 入力同相電圧

AD9233のアナログ入力は内部でDCバイアスされません。AC 結合されたアプリケーションでは、このバイアスを外部から提供する必要があります。最適な性能を得るには、AD9233を VCM=0.55×AVDDとなるよう設定することを推奨していますが、通常でも広範囲にわたって適度な性能を提供します(図32を参照)。オンボードの同相電圧リファレンスは設計に含まれており、CMLピンから使用できます。アナログ入力の同相電圧がCMLピン電圧で設定されている場合に、最適な性能が達成されます(通常、0.55×AVDD)。「レイアウトのポイント」に示すように、CMLピンは $0.1\mu$ Fコンデンサでグラウンドにデカップリングします。

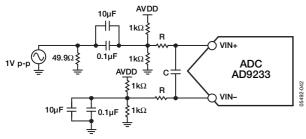

#### 差動入力構成

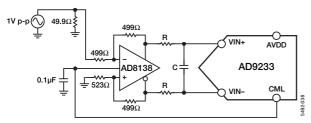

最適性能は、差動入力構成でAD9233を駆動するときに得られます。ベースバンド・アプリケーションに対しては、AD8138 差動ドライバが優れた性能とADCに対するフレキシブルなインターフェースを提供します。AD8138の出力同相電圧はAD9233のCMLピンで簡単に設定することができ(図37を参照)、ドライバは入力信号帯域を制限できるSallen Keyフィルタ回路として構成できます。

図37. AD8138を使用した差動入力構成

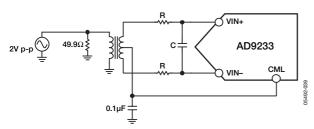

S/N比が重要なパラメータとなるベースバンド・アプリケーションに対しては、図38に示す差動トランス・カップリングの入力構成を推奨します。CML電圧は、アナログ入力をバイアスするトランスの二次巻線の中央タップに接続できます。

トランスを選択する際は、信号特性を考慮する必要があります。 ほとんどのRFトランスは数MHz以下の周波数で飽和してしま うため、信号電力が極端に大きくなるとコアの飽和も発生して、 歪みの原因になります。

図38. 差動トランス・カップリング構成

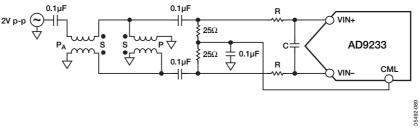

2次ナイキスト領域およびそれ以上の入力周波数では、大部分のアンプのノイズ性能はAD9233の真のS/N比性能を得るには不十分です。S/N比が重要なパラメータとなるアプリケーションには、トランス・カップリングの入力構成を推奨します。SFDRが重要なパラメータとなるアプリケーションには、図39に示す差動ダブル・バラン・カップリングの入力構成を推奨します。

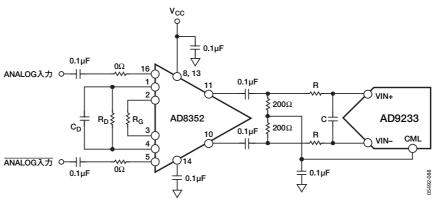

2次ナイキスト領域の周波数でトランス結合入力を使用する代わりに、図40に示すAD8352差動ドライバを使用できます。

どの構成もシャント・コンデンサ (C) の値は入力周波数と信号源インピーダンスに依存しており、場合によっては、その値を減らすかゼロにする必要があります。表8は、RC回路を設定するための推奨値を示しています。ただし、これらの値は入力信号に依存しているため、指針として最初だけ利用してください。

表8. RC回路の推奨値

| 周波数レンジ(MHz) | R直列(Ω) | C差動(pF) |

|-------------|--------|---------|

| 0~70        | 33     | 15      |

| 70~200      | 33     | 5       |

| 200~300     | 15     | 5       |

| >300        | 15     | オープン    |

図39. 差動ダブル・バラン入力構成

図40. AD8352を使用した差動入力構成

— 16 — REV. A

#### シングルエンド入力構成

推奨事項ではありませんが、入力電圧振幅がAVDD(電源)以内であれば、シングルエンド入力構成でAD9233を使用できます。シングルエンド動作は、低価格アプリケーションで妥当な性能を提供できます。この構成では、大きな入力同相電圧振幅によりSFDRと歪みの性能が低下します。ただし、各入力の信号源インピーダンスを一致させると、S/N比への影響がほぼなくなります。図41に、代表的なシングルエンド入力構成を示します。

図41. シングルエンド入力構成

## 電圧リファレンス

AD9233は、安定した正確な電圧リファレンスを内蔵しています。内部/外部リファレンスを使ってAD9233に入力されるリファレンスを変えることで、入力範囲を調整できます。ADCの入力スパンは、リファレンスの変化に比例して変わります。個々のリファレンス・モードについては、以下の各セクションで簡単に説明しています。「リファレンス・デカップリング」には、リファレンスのPCボード・レイアウトに関する最適な方法と条件を示しています。

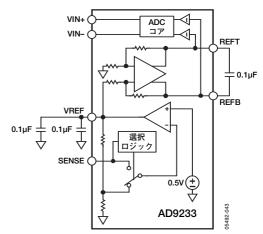

#### 内部リファレンスの接続

AD9233に内蔵されているコンパレータはSENSEピンの電位を検出し、リファレンスを表9に示す4つの状態のいずれかに設定します。SENSEがグラウンド・レベルの場合、リファレンス・アンプ・スイッチは内部抵抗分圧器(図42を参照)に接続され、VREFは1Vに設定されます。

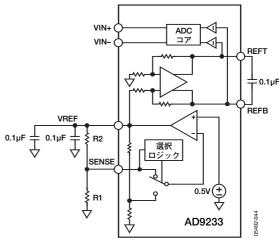

SENSEピンをVREFに接続すると、リファレンス・アンプ出力はSENSEピン側にスイッチされ、ループを構成して0.5Vのリファレンスを出力します。図43のようにチップ外部の抵抗分圧器に接続された場合にも、スイッチはSENSEピン側に接続されます。

この接続により、リファレンス・アンプは非反転モードになり、 VREF出力は次のように決定されます。

$$VREF = 0.5 \times \left(1 + \frac{R2}{R1}\right)$$

SENSEピンをAVDDピンに接続した場合は、リファレンス・アンプがディスエーブルになり、外部リファレンスをVREFピンに接続できます(「外部リファレンスによる動作」を参照)。

ADCの入力範囲は、内部/外部リファレンスに対して、常にリファレンスピンの電圧の2倍になります。

図42. 内部リファレンス構成

図43. プログラマブルなリファレンスの構成

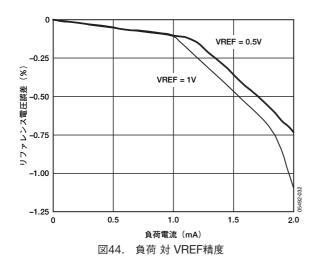

複数のコンバータを駆動してゲイン・マッチングを改善するためにAD9233の内部リファレンスを使用する場合は、他のコンバータのリファレンスの負荷を考慮する必要があります。図44は、内部リファレンスはどの程度負荷の影響を受けるのかを示しています。

REV. A — 17 —

#### 表9. リファレンス構成のまとめ

| 選択するモード        | SENSE電圧   | VREF (V)               | 差動スパン (Vp-p) |

|----------------|-----------|------------------------|--------------|

| 外部リファレンス       | AVDD      | なし                     | 2×外部リファレンス   |

| 内部固定リファレンス     | VREF      | 0.5                    | 1.0          |

| プログラマブルなリファレンス | 0.2V~VREF | 0.5×(1+R2/R1) (図43を参照) | 2×VREF       |

| 内部固定リファレンス     | AGND~0.2V | 1.0                    | 2.0          |

#### 外部リファレンスによる動作

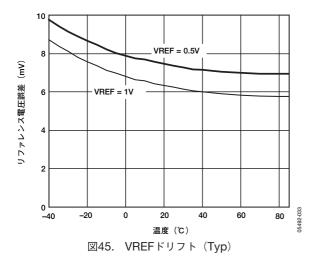

ADCのゲイン精度または熱ドリフト特性を改善するために、外部リファレンスの使用が必要になることがあります。図45に、1Vモードと0.5Vモードでの内部リファレンスのドリフト特性(Typ値)を示します。

SENSEピンをAVDDに接続すると、内部リファレンスがディスエーブルになり、外部リファレンスを使用できます。内部抵抗分圧器は、外部リファレンスに対して $6k\Omega$ の等価負荷になります(図11を参照)。また、内部バッファはADCコア用の正と負のフルスケール・リファレンスを生成します。したがって、外部リファレンスは1V以下に制限してください。

## クロック入力の考慮事項

最適な性能を得るために、AD9233のサンプル・クロック入力 (CLK+、CLK-) は差動信号で供給する必要があります。通常、この信号はトランスまたはコンデンサを介してCLK+ピンおよびCLK-ピンにAC結合されます。これらのピンは内部的にバイアスされていますので(図5を参照)、外部でのバイアスは不要となります。

#### クロック入力オプション

AD9233はかなり柔軟なクロック入力構造を備えています。クロックとしてCMOS、LVDS、LVPECL、サイン波の信号を入力できます。「ジッタに関する考慮事項」に示すように、信号の種類に関わらず、クロック・ソースのジッタは最も大きな問題となります。

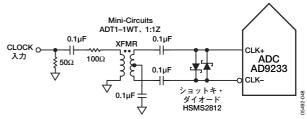

図46は、AD9233へのクロック入力に適した方法を示す回路図です。低ジッタのクロック・ソースは、RFトランスを使ってシングルエンド信号から差動信号に変換されます。トランス二次側の互いに逆向きに接続されたショットキ・ダイオードは、AD9233に入力されるクロックを約0.8Vp-pの差動に制限します。この機能は、クロックの大きな電圧振幅がAD9233の別の部分に入力されないようにし、低ジッタ性能にとって重要な、信号の高速立上がり/立下がり時間を維持します。

図46. トランス結合差動クロック

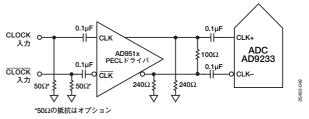

低ジッタのクロック・ソースを使用できない場合は、図47に示すように、差動PECL信号をサンプル・クロック入力ピンにAC 結合することもできます。クロック・ドライバのAD9510/AD9511/AD9512/AD9513/AD9514/AD9515ファミリーは優れたジッタ性能を提供します。

図47. 差動PECLサンプル・クロック

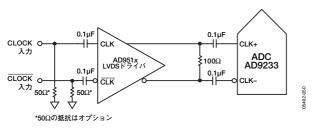

第3のオプションは、図48に示すように、差動LVDS信号をサンプル入力クロック・ピンにAC結合する方法です。クロック・ドライバのAD9510/AD9511/AD9512/AD9513/AD9514/AD9515ファミリーは優れたジッタ性能を提供します。

図48. 差動LVDSサンプル・クロック

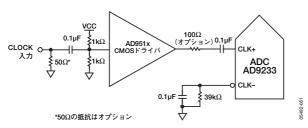

アプリケーションによっては、シングルエンドCMOS信号でサンプル・クロック入力を駆動できます。このようなアプリケーションでは、 $0.1\mu$ Fコンデンサでグラウンドに接続されている CLKーピンをバイパスし、CMOSゲートからCLK+を直接駆動します。CLK+入力回路の電源はAVDD(1.8V)ですが、この入力は最大3.6Vまでの入力電圧に耐えられるため、駆動ロジック電圧をかなり柔軟に選択できます。1.8VのCMOS信号で CLK+を駆動するときは、並列に接続した $0.1\mu$ Fのコンデンサと39k $\Omega$ の抵抗で、CLKーピンをバイアスしてください(図49を参照)。3.3VのCMOS信号でCLK+を駆動するときは、39k $\Omega$ の抵抗は不要です(図50を参照)。

図49. シングルエンドの1.8V CMOSサンプル・クロック

図50. シングルエンドの3.3V CMOSサンプル・クロック

#### クロック・デューティ・サイクル

通常の高速ADCは、両クロック・エッジを使ってさまざまな内部タイミング信号を発生させます。そのため、これらのADCはクロック・デューティ・サイクルの変化に対して敏感です。動的な性能特性を維持するには、一般にクロック・デューティ・サイクルの変化を±5%以内に抑える必要があります。

AD9233には、デューティ・サイクル・スタビライザ(DCS)が内蔵されており、非サンプリング(立下がり)エッジのタイミングを再生して、公称50%のデューティ・サイクルを持つ内部クロック信号を供給しています。この機能により、AD9233の性能に悪影響を与えずに、広範囲のデューティ・サイクルを持つクロック入力を可能にしています。図31に示すように、DCSがオンのときは、ノイズと歪みの性能が広範囲のデューティ・サイクルに対してほぼ平坦になります。

入力の立上がりエッジのジッタは最も大きな問題のひとつで、内部の安定化回路では低減できません。デューティ・サイクル制御ループは、通常、20MHz未満のクロック・レートでは機能しません。クロック・レートが動的に変化するアプリケーションでは、この制御ループの時定数を考慮する必要があり、動的クロック周波数が増加(または減少)してからDCSループが入力信号に再ロックされるまでに $1.5\sim5$  $\mu s$ の待ち時間が必要になります。DCSループがロックされていない間は、ループがバイパスされ、内部デバイスのタイミングは入力クロック信号のデューティ・サイクルに依存します。このようなアプリケーションでは、デューティ・サイクル・スタビライザをディスエーブルにしたほうがよい場合があります。それ以外の回路では、性能を最大化するためにDCS回路をイネーブルにすることを推奨します。

DCSをイネーブル/ディスエーブルにするには、外部ピン・モードを使用するときにSDIO/DCSピンを設定するか(表10を参照)、あるいは表13に示すようにSPIを使用します。

表10. モード選択(外部ピン・モード)

| ピンの電圧 | SCLK/DFS     | SDIO/DCS            |

|-------|--------------|---------------------|

| AGND  | バイナリ (デフォルト) | DCSディスエーブル          |

| AVDD  | 2の補数         | DCSイネーブル<br>(デフォルト) |

|       |              | (アノォルト)             |

#### ジッタに関する考慮事項

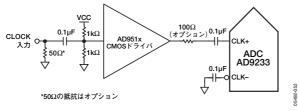

高速で高分解能のADCは、クロック入力の品質に敏感です。特定の入力周波数  $(F_{IN})$  でのジッタ  $(t_J)$  によるS/N比の低下は、次式を使って計算できます。

$S/N = -20\log (2\pi \times F_{IN} \times t_I)$

この式では、アパーチャ・ジッタ実効値( $t_j$ )は全ジッタ源の平均自乗根を表しており、これにはクロック入力、アナログ入力信号、ADCアパーチャ・ジッタ仕様値が含まれています。図 51に示すように、IFアンダーサンプリング・アプリケーションは特にジッタに敏感です。

図51. S/N比と入力周波数およびジッタの関係

REV. A — 19 —

アパーチャ・ジッタがAD9233のダイナミック・レンジに影響を与える場合は、クロック入力をアナログ信号として扱う必要があります。クロック・ドライバの電源はADC出力ドライバの電源と分離して、クロック信号がデジタル・ノイズから変調を受けないようにする必要があります。また、クロックから入力信号への変調(または逆の変調)を防止するために、電源はバッファなどのアナログ入力回路と共用しないようにします。低ジッタの水晶制御発振器は最適なクロック源です。クロックが別のタイプの信号源(ゲート、分周器など)で生成される場合は、最終段で元のクロックを使ってタイミングを再生する必要があります。

ADC関連のジッタ性能の詳細については、アプリケーション・ ノートAN-501『Aperture Uncertainty and ADC System Performance』 およびAN-756『Sampled Systems and the Effects of Clock Phase Noise and Jitter』を参照してください。

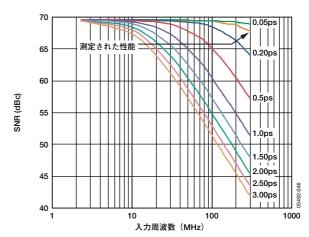

## 消費電力とスタンバイ・モード

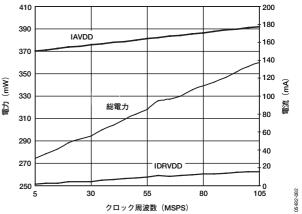

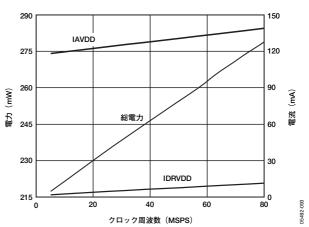

図52と図53に示すように、AD9233の消費電力はサンプル・レートに比例します。デジタル消費電力は、主にデジタル・ドライバの強さと各出力ビットの負荷によって決まります。 DRVDDの最大電流  $(I_{DRVDD})$  は次のように計算されます。

$$I_{DRVDD} = V_{DRVDD} \times C_{LOAD} \times \frac{f_{CLK}}{2} \times N$$

ここで、Nは出力ビット数で、AD9233の場合は12です。

この最大電流は、各出力ビットが各クロック・サイクルでスイッチングしている状態での値であり、この状態はナイキスト周波数( $f_{CLK}/2$ )のフルスケール方形波が入力された場合にのみ発生します。実際には、DRVDD電流はスイッチングする出力ビット数の平均値を使って計算され、この平均値はサンプル・レートとアナログ入力信号特性により決定されます。出力ドライバに与えられる容量性負荷を軽減することで、デジタル消費電力を最小限に抑えることができます。

図52と図53で使用したデータは、各出力ドライバに5pFの負荷を接続して取得した「代表的な性能特性」の各図における動作条件と同じ条件に基づいています。

図52. AD9233-125:電力および電流とクロック周波数の関係(F<sub>IN</sub>=30MHz)

図53. AD9233-105:電力および電流とクロック周波数の関係  $(F_{IN}=30MHz)$

図54. AD9233-80:電力および電流とクロック周波数の関係(F<sub>IN</sub>=30MHz)

— 20 — REV. A

#### パワーダウン・モード

PDWNピンをハイレベルにすると、AD9233はパワーダウン・モードになります。この状態では、ADCの消費電力は1.8mA (Typ) となります。パワーダウンの間、出力ドライバは高インピーダンス状態になります。PDWNピンをローレベルにすると、AD9233は通常の動作モードに戻ります。PDWNは1.8Vおよび3.3Vの両者を許容します。

パワーダウン・モードでは、リファレンス、リファレンス・バッファ、バイアス回路をシャットダウンすることにより低消費電力を実現します。パワーダウン・モードに入るとき、REFTとREFBに接続するデカップリング・コンデンサが放電し、通常動作に戻るときにこれらを再充電する必要があります。そのため、ウェイクアップ時間はパワーダウン・モードになっていた時間によって異なり、パワーダウン・サイクルが短いほどウェイクアップ時間が短くなります。REFTとREFBに推奨の $0.1\mu$ Fデカップリング・コンデンサを接続した場合、リファレンス・バッファ・デカップリング・コンデンサの放電には約0.25msを要し、フル動作に戻るには0.35msを要します。

#### スタンバイ・モード

SPIポート・インターフェースを使用するときは、ADCをパワーダウン・モードまたはスタンバイ・モードにできます。スタンバイ・モードでは、高速ウェイクアップが必要なときのために内部リファレンス回路を駆動状態にしておくことができます。詳細については、「メモリマップ」を参照してください。

## デジタル出力

AD9233の出力ドライバは、DRVDDとインターフェース・ロジックのデジタル電源を一致させることにより、1.8~3.3Vのロジック・ファミリーとインターフェースするように設定できます。出力ドライバのサイズは、さまざまなロジック・ファミリーを駆動するために十分な出力電流を提供するように設計されています。ただし、大きな駆動電流は電源にグリッチを生じさせる傾向を持つため、コンバータ性能に影響を与えることがあります。ADCにより大きな容量性負荷または大きなファンアウトを駆動する必要があるアプリケーションでは、外付けバッファまたはラッチが必要となることがあります。

出力データ形式は、外部ピン・モード時にCLK/DFSピンを設定することでオフセット・バイナリまたは2の補数を選択できます (表10を参照)。『Interfacing to High Speed ADCs via SPI User Manual』に詳述するように、SPIコントロールの使用中はオフセット・バイナリ、2の補数、グレーコードのいずれかを選択できます。

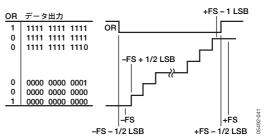

## アウト・オブ・レンジ (OR) 状態

アナログ入力電圧がADCの入力レンジを越えるとアウト・オブ・レンジ状態になります。ORは、サンプリングされた特定の出力電圧に対応するデータ出力とともに更新されるデジタル出力です。したがって、ORにはデジタル・データと同じパイプライン遅延があります。

図55. 入力電圧および出力データとORの関係

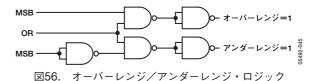

図55に示すように、ORはアナログ入力電圧がアナログ入力レンジ内にあるときはローレベルであり、アナログ入力電圧が入力レンジを越えるとハイレベルになります。ORは、アナログ入力が入力レンジ内に戻って別の変換が終了するまでハイレベルを維持します。MSBおよびその補数とORビットのANDをとることで、オーバーレンジ・ハイ状態とアンダーレンジ・ロー状態を検出できます。表11は、図56のNANDゲートを使用するオーバーレンジ/アンダーレンジ回路の真理値表です。

表11. オーバーレンジ/アンダーレンジ回路の真理値表

| OR | MSB | アナログ入力: |

|----|-----|---------|

| 0  | 0   | レンジ内    |

| 0  | 1   | レンジ内    |

| 1  | 0   | アンダーレンジ |

| 1  | 1   | オーバーレンジ |

#### デジタル出力イネーブル機能 (OEB)

AD9233にはスリーステート機能があります。OEBピンがローのときは、出力データ・ドライバはイネーブルとなります。OEBピンがハイのときは、出力データ・ドライバは高インピーダンス状態となります。これはデータ・バスへの迅速なアクセスを意図したものではありません。OEBはデジタル電源(DRVDD)を基準にしており、その電源電圧を上回らないことが必要です。

表12. 出力データ形式

| <b>状態 (V)</b>                 | バイナリ出力モード      | 2の補数モード        | グレーコード・モード<br>(SPIからアクセス可能) | OR |

|-------------------------------|----------------|----------------|-----------------------------|----|

| VIN+-VIN-<-VREF-0.5LSB        | 0000 0000 0000 | 1000 0000 0000 | 1100 0000 0000              | 1  |

| VIN + -VIN - = -VREF          | 0000 0000 0000 | 1000 0000 0000 | 1100 0000 0000              | 0  |

| VIN + -VIN = 0                | 1000 0000 0000 | 0000 0000 0000 | 0000 0000 0000              | 0  |

| VIN + -VIN - = +VREF - 1.0LSB | 1111 1111 1111 | 0111 1111 1111 | 1000 0000 0000              | 0  |

| VIN + -VIN - > +VREF - 0.5LSB | 1111 1111 1111 | 0111 1111 1111 | 1000 0000 0000              | 1  |

REV. A — 21 —

## タイミング

AD9233の最小変換レート(typ値)は10MSPSです。10MSPSより低いクロック・レートでは、ダイナミック性能が低下することがあります。

AD9233は、12クロック・サイクルのパイプライン遅延を持つラッチされたデータを出力します。データ出力は、クロック信号の立上がりエッジ後の1伝搬遅延( $t_{PD}$ )で有効になります。

出力データ・ラインの長さとそのラインに接続された負荷は最小にし、AD9233内部での過渡電圧を抑えてください。これらの過渡電圧はコンバータのダイナミック性能を低下させることがあります。

#### データ・クロック出力(DCO)

AD9233は、外部レジスタのデータを取得するためのデータ・クロック出力(DCO)を提供します。データ出力はDCOの立上がりエッジで有効となります。タイミングについては、図2を参照してください。

— 22 — REV. A

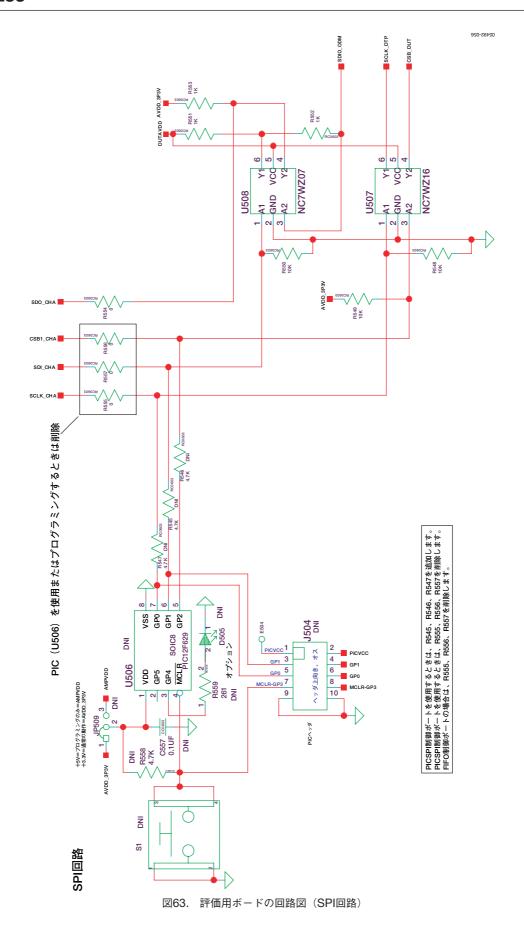

# シリアル・ポート・インターフェース(SPI)

AD9233のSPIでは、ADC内部の構造化されたレジスタ空間を使ってコンバータの特定の機能や動作を設定できます。SPIは、アプリケーションに対応したフレキシビリティやカスタマイズ機能を提供します。アドレスにはシリアル・ポートからアクセスでき、そのポートを介して書込みや読出しを行うことができます。「メモリマップ」に示すように、メモリはバイト単位で構成されており、各フィールドに分割されています。動作の詳細については、『Interfacing to High Speed ADCs via SPI User Manual』を参照してください。

## SPIによる設定

表13に示すように、3本のピンでこのADCのSPIを定義します。 SCLK/DFSピンは、ADCに対するデータの書込み/読出しの 同期をとります。二重目的のSDIO/DCSピンでは、内蔵された ADCのメモリマップ・レジスタからデータを送信または読出し できます。CSBはアクティブ・ロー制御ピンであり、読出し/ 書込みサイクルをイネーブルまたはディスエーブルできます。

表13. SPIピン

| ピン名      | 機能                                                                                   |

|----------|--------------------------------------------------------------------------------------|

| SCLK/DFS | SCLK (シリアル・クロック) はシリア<br>ル・シフト・クロック入力です。シリア<br>ル・インターフェースによる読出し/書込<br>みを同期化します。      |

| SDIO/DCS | SDIO(シリアル・データ入出力)は、二重の目的を持つピンです。このピンの主な役割は、タイミング・フレーム内の相対的な位置と送信される命令に基づいた入力および出力です。 |

| CSB      | <b>CBS</b> (チップ選択バー) は、読出し/書込みサイクルをゲートするアクティブ・ロー制御ピンです。                              |

フレーミングの開始は、CSBの立下がりエッジとSCLKの立上がりエッジで決まります。図57と表14は、シリアル・タイミングとその定義を示します。

CSBを使って他のモードも使用できます。CSBを常にローレベルに保持すれば、AD9246を常時イネーブル(ストリーミングといいます)にできます。CSBはバイト間でハイレベルを維持して、外部のタイミングを追加できるようにします。パワーアップ時にCSBをハイレベルに固定すると、SPI機能は高インピーダンス・モードになります。このモードは、SPIピンの二次機能をすべてオンにします。CSBをパワーアップ時にハイレベルにし、その後ローレベルにしてSPIを起動させると、デバイスの電源を入れ直さない限りSPIピンの二次機能は使用できません。

16ビット命令は命令フェーズで送信されます。データは命令フェーズに追従して送信され、データ長はW0ビットとW1ビットによって決まります。データはすべて8ビット・ワードから構成されています。シリアル・データの各バイトの先頭ビットは、読出しまたは書込みのどちらのコマンドが発行されているかを示します。この機能により、シリアル・データ入出力(SDIO) ピンはデータの方向を入力から出力へと変更します。

ワード長以外に、命令フェーズではシリアル・フレームの読出し動作または書込み動作を指定でき、シリアル・ポートを使用したチップのプログラミングまたはオンチップ・メモリの内容の読出しを行うことができます。命令が読出しの場合には、動作を実行すると、シリアル・データ入出力(SDIO)ピンがシリアル・フレームの適当な位置で処理方向を入力から出力に変更します。

データは、MSBファースト・モードまたはLSBファースト・モードで実行できます。パワーアップ時のデフォルトはMSBファーストですが、このモードは設定レジスタで変更できます。詳細については、『Interfacing to High Speed ADCs via SPI User Manual』を参照してください。

表14. SPIタイミング図の仕様

| 名前              | 説明                               |

|-----------------|----------------------------------|

| $t_{DS}$        | データからSCLKの立上がりエッジまでのセット<br>アップ時間 |

| $t_{DH}$        | データからSCLKの立上がりエッジまでのホールド<br>時間   |

| $t_{\rm CLK}$   | クロック周期                           |

| $t_S$           | CSBからSCLKまでのセットアップ時間             |

| $t_{\rm H}$     | CSBからSCLKまでのホールド時間               |

| $t_{\rm HI}$    | SCLKのロジック・ハイ状態の最小時間              |

| t <sub>LO</sub> | SCLKのロジック・ロー状態の最小時間              |

#### ハードウェア・インターフェース

表13に示したピンは、ユーザのプログラミング・デバイスと AD9233のシリアル・ポート間の物理的なインターフェースを 構成しています。SPIインターフェースの使用中は、SCLKピンとCSBピンは入力として機能します。SDIOピンは双方向で、 書込み中は入力として、 読出し中は出力として機能します。

SPIインターフェースは、PROMでもPICマイクロコントローラでも制御できるフレキシビリティを備えています。ユーザはいずれかの方法を用いてADCをプログラミングできます。そのうちの1つについて、アプリケーション・ノートAN-812で詳しく説明しています。

SPIインターフェースを使用しないときは、一部のピンが2つの機能を提供します。デバイスのパワーオン中にAVDDまたはグラウンドに接続すると、そのピンは特定の機能に関連付けられます。

## SPIなしの設定

SPI制御レジスタにインターフェースしないアプリケーションでは、SDIO/DCSピンとSCLK/DFSピンは、独立したCMOS互換の制御ピンとして機能します。CSBチップ・セレクトをAVDDに接続してデバイスをパワーアップすると、シリアル・ポート・インターフェースがディスエーブルになります。このモードでは、出力データ形式用のスタティック・コントロール・ラインおよびデューティ・サイクル・スタビライザとして使用されることを想定しています(表10を参照)。詳細については、『Interfacing to High Speed ADCs via SPI User Manual』を参照してください。

# メモリマップ

## メモリマップ・テーブルの読出し

メモリマップ・テーブルの各行には8つのアドレス位置があります。メモリマップは、大まかに3つのセクション(チップ設定レジスタ・マップ(アドレス0x00~0x02)、デバイス・インデックス&転送レジスタ・マップ(アドレス0xFF)、ADC機能マップ(アドレス0x08~0x18))に分かれています。

表15のメモリマップ・レジスタは、最初の列にレジスタ・アドレス値を16進値で示しています。最後の列には、各16進数アドレスのデフォルト値を示しています。デフォルトの16進値は、ビット7(MSB)の列から始まります。例えば16進数アドレス 0x14はoutput\_modeで、そのデフォルト値は0x00です。このデフォルト値は、出力データ・フォーマットはオフセット・バイナリ(0bit0,1=00)、出力ディセーブルはイネーブル(0bit0) で、そして出力ドライバ構成は0RVDD=02.5V03.3V(0bit0,7=00)の設定となっています。この機能の詳細については、0Interfacing to High Speed ADCs via SPI User Manual 00 を参照してください。

#### オープン位置

オープンと記載されている位置は、現在このデバイスでは対応していません。必要に応じて0を書き込んでください。アドレス位置の一部がオープンの場合にのみ書き込みます(アドレス0x14など)。アドレス位置全体がオープンの場合は(アドレス0x13)、書き込む必要はありません。

#### デフォルト値

リセットを終了すると、レジスタにはデフォルト値がロードされます。レジスタのデフォルト値を表15に示します。

#### ロジック・レベル

以下にレジスタ関連の表現について説明します。

- 「ビットを設定する」は、「ビットをロジック1に設定する」 「ビットにロジック1を書き込む」と同義です。

- 「ビットをクリアする」は、「ビットをロジック0に設定する」「ビットにロジック0を書き込む」と同義です。

#### SPIからアクセスできる機能

SPIを通してアクセスできる機能を簡単に説明します。これらの機能の詳細については、『Interfacing to High Speed ADCs via SPI User Manual』を参照してください。

- モード:パワーダウン・モードまたはスタンバイ・モード を設定します。

- クロック:SPIを介してDCSにアクセスします。

- オフセット:コンバータ・オフセットをデジタル的に調整 します。

- テストI/O: テスト・モードを設定して、出力ビットに関する既知のデータを取得します。

- 出力モード:出力を設定し、出力ドライバ強度を変更します。

- 出力フェーズ:出力クロックの極性を設定します。

- VREF:リファレンス電圧を設定します。

— 24 — REV. A

## 表15. メモリマップ・レジスタ

| アドレス<br>(Hex) | パラメータ名           | ビット7<br>(MSB) | ビット6                                                                        | ビット5                                    | ビット4 | ビット3                                   | ビット2                                                                                             | ビット1                                    | ビット0<br>(LSB)                                           | デフォルト<br>値(Hex)                             | デフォルトに<br>関する注記                                                                                           |

|---------------|------------------|---------------|-----------------------------------------------------------------------------|-----------------------------------------|------|----------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| チップ設定         | Eレジスタ            |               |                                                                             |                                         |      |                                        |                                                                                                  |                                         |                                                         |                                             |                                                                                                           |

| 00            | chip_port_config | 0             | LSB<br>ファースト<br>0=オフ<br>(デフォルト)<br>1=オン                                     | ソフト・<br>リセット<br>0=オフ<br>(デフォルト)<br>1=オン | 1    | 1                                      | ソフト・<br>リセット<br>0=オフ<br>(デフォルト)<br>1=オン                                                          | LSB<br>ファースト<br>0=オフ<br>(デフォルト)<br>1=オン | 0                                                       | 0x18                                        | ニブルはミ<br>ラーリングす<br>る必要があり<br>ます。<br>『Interfacing to<br>High Speed<br>ADCs via SPI<br>User Manual』<br>を参照。 |

| 01            | chip_id          |               | 8ビットのチップIDビット7:0<br>(AD9233=0x00)、(デフォルト)                                   |                                         |      |                                        |                                                                                                  |                                         | 読出し専用                                                   | デフォルトは<br>デバイスごと<br>に異なる一意<br>のチップIDで<br>す。 |                                                                                                           |

| 02            | chip_grade       | オープン          | オープン                                                                        | オープン                                    | オープン | 子ID<br>0=125<br>MSPS、<br>1=105<br>MSPS | オープン                                                                                             | オープン                                    | オープン                                                    | 読出し専用                                       | 子IDで速度グ<br>レードを区別<br>します。                                                                                 |

| デバイス・         | · インデックス/転       |               |                                                                             |                                         |      |                                        |                                                                                                  |                                         |                                                         |                                             |                                                                                                           |

| FF            | device_update    | オープン          | オープン                                                                        | オープン                                    | オープン | オープン                                   | オープン                                                                                             | オープン                                    | SW転送                                                    | 0x00                                        | データをマス<br>タ・シフト・<br>レジスタから<br>スレーブに同<br>期的に転送し<br>ます。                                                     |

| グローバル         | VADC機能           |               |                                                                             |                                         |      |                                        |                                                                                                  |                                         |                                                         | _                                           |                                                                                                           |

| 08            | モード              | オープン          | オープン                                                                        | PDWN<br>0-フル<br>1-<br>スタンバイ             | オープン | オープン                                   | 内部パワーダウン・モード 000―標準 (パワーアップ) 001―フルパワーダウン 010―スタンバイ 011―標準 (パワーアップ) 注:外部PWDNピンは この設定に優先します。      |                                         | プ)                                                      | 0x00                                        | チップ動作の<br>各種の汎用<br>モードを「消定<br>電力」、「スタ<br>ンバイ・モー<br>ド」、「SPIから<br>アクセスを参<br>照。                              |

| 09            | クロック             | オープン          | オープン                                                                        | オープン                                    | オープン | オープン                                   | オープン                                                                                             | オープン                                    | デューティ・<br>サイクル・<br>スタビライザ<br>0<br>ディスエーブル<br>1<br>イネーブル | 0x00                                        | 「クロック・<br>デューティ・<br>サイクル」お<br>よび「SPIから<br>アクセスでき<br>る機能」を参<br>照。                                          |

|               | ブルなADC機能         |               | ı                                                                           |                                         |      |                                        |                                                                                                  |                                         |                                                         |                                             |                                                                                                           |

| 10            | offset           |               | デジタル・ 011111 011110 011101 000010 000001 000000 111111 111110 111101 100001 | オフセット訳                                  | 整    |                                        | オフセット<br>+7 3/4<br>+7 1/2<br>+7 1/4<br>+1/2<br>+1/4<br>0<br>-1/4<br>-1/2<br>-3/4<br>-7 3/4<br>-8 | (LSB)                                   |                                                         | 0x00                                        | コンバータに<br>固有のオフ<br>セットが調整<br>可能。「SPIか<br>らアクセで<br>きる機能」を<br>参照。                                           |

REV. A — 25 —

| アドレス<br>(Hex) | パラメータ名       | ビット7<br>(MSB)                      | ビット6                                                  | ビット5                           | ビット4                                                           | ビット3 | ビット2                                                                                                                       | ビット1 | ビット0<br>(LSB) | デフォルト<br>値(Hex)                      | デフォルトに<br>関する注記                                                       |

|---------------|--------------|------------------------------------|-------------------------------------------------------|--------------------------------|----------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------|------|---------------|--------------------------------------|-----------------------------------------------------------------------|

| 00            | test_io      |                                    |                                                       | PN23<br>0=<br>標準<br>1=<br>リセット | PN9<br>0=<br>標準<br>1=<br>リセット                                  |      | グローバル出力テスト・オプション 000―オフ 001―ミッドスケール・ショート 010―+FSショート 011―-FSショート 100―チェッカ・ボード出力 101―PN23シーケンス 110―PN 9 111―1ワード/ゼロ・ワードのトグル |      |               | 0x00                                 | 『Interfacing to<br>High Speed<br>ADCs via SPI<br>User Manual』<br>を参照。 |

| 14            | output_mode  | 00—DRV                             | イバ設定<br>VDD=3.3V<br>VDD=1.8V                          | オープン                           | 出力<br>ディス<br>エーブル<br>1一ディス<br>エーブル<br>0一イネー<br>ブル <sup>1</sup> | オープン | 出力<br>データの<br>反転<br>1=反転<br>(デフォルト)<br>01—2の補数<br>10—グレーコード                                                                |      | 0x00          | 出力、データ<br>形式、出力ド<br>ライバ構成を<br>設定します。 |                                                                       |

| 16            | output_phase | DCOの<br>極性<br>1=反転<br>0=標準         | オープン                                                  | オープン                           | オープン                                                           | オープン | オープン                                                                                                                       | オープン | オープン          | 0x00                                 | 「SPIからアク<br>セスできる機<br>能」を参照。                                          |

| 18            | VREF         | 抵抗分圧<br>00—VRI<br>01—VRI<br>10—VRI | 器<br>器<br>EF=1.25V<br>EF=1.5V<br>EF=1.75V<br>EF=2.00V | オープン                           | オープン                                                           | オープン | オープン                                                                                                                       | オープン | オープン          | 0xC0                                 | 「SPIからアク<br>セスできる機<br>能」を参照。                                          |

<sup>&</sup>lt;sup>1</sup> 外部出力イネーブル (OEB) ピンはハイレベル。

# レイアウトのポイント

#### 電源とグラウンドに関する推奨事項

電源をAD9233に接続するときは、独立した2つの電源の使用を推奨します。1つはアナログ(AVDD、公称電圧1.8V)用で、もう1つはデジタル(DRVDD、公称電圧1.8~3.3V)用です。1.8Vの単電源しか使用できない場合は、最初にAVDDに接続し、次にデカップリング・コンデンサとフェライト・ビーズまたはフィルタ・チョークでそれを分岐・分離してから、DRVDDへの接続を行います。ユーザは、複数の異なるデカップリング・コンデンサを使用して高周波と低周波の両方に対応させます。これらのコンポーネントは、PCボード・レベルのエントリポイントの側と最小パターン長のパーツの側に配置します。

AD9233を使用するときは、1つのPCボード・グラウンド・プレーンで対応できるようにします。ボードのアナログ、デジタル、クロック部を適切に分離しデカップリングすることにより、最適な性能を簡単に実現できます。

#### 露出パドルの放熱板に関する推奨事項

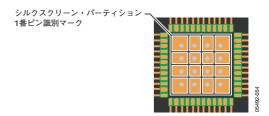

AD9233で最高の電気的/熱的性能を実現するには、ADC底部の露出パドルをアナログ・グラウンド(AGND)に接続する必要があります。PCボード上で露出している連続した銅プレーンは、AD9233の露出パドル(0番ピン)に接続します。また、PCボード底部の放熱経路の熱抵抗をできる限り小さくするために、銅プレーンに複数のビアを設けます。これらのビアにはハンダを充填します。

ADCとPCボード間の適用範囲と接合を最大化するために、シルクスクリーンを使用してPCボード上の連続したプレーンを複数の均一なセクションに区分します。このようにすると、リフロー処理中にADCとPCボード間に複数の接続ポイントが提供されます。パーティションのない1つの連続したプレーンを使用した場合は、ADCとPCボード間で1つの接続ポイントしか保証されません。PCボードのレイアウトの例は、図58を参照してください。パッケージングとチップ・スケール・パッケージのPCボード・レイアウトの詳細については、アプリケーション・ノートAN-772『A Design and Manufacturing Guide for the Lead Frame Chip Scale Package (LFCSP)』を参照してください。

図58. PCボード・レイアウトの例

#### **CML**

図38に示すように、CMLピンは $0.1\mu$ Fコンデンサでグラウンドにデカップリングします。

#### **RBIAS**

AD9233では、RBIASピンとグラウンドの間に $10k\Omega$ の抵抗を接続してください。このRBIAS抵抗でADCコアのマスタ電流リファレンスを設定します。RBIASは少なくとも1%の許容誤差が必要です。

## リファレンス・デカップリング

VREFピンは、並列に接続した低ESRの $1.0\mu$ Fコンデンサと低ESRの $0.1\mu$ Fセラミック・コンデンサで外部的にグラウンドにデカップリングする必要があります。リファレンスの設定では、REFTとREFBは内部リファレンス・バッファによるノイズを減らすためのバイパス点となります。REFT/REFBは、外部の $0.1\mu$ Fセラミック・コンデンサに接続することを推奨します。このコンデンサは必須ではありませんが、使用しない場合S/N比性能は0.1dB前後低下します。リファレンス・デカップリング・コンデンサはすべて、最小パターン長でできる限りADCの近くに配置します。

REV. A — 27 —

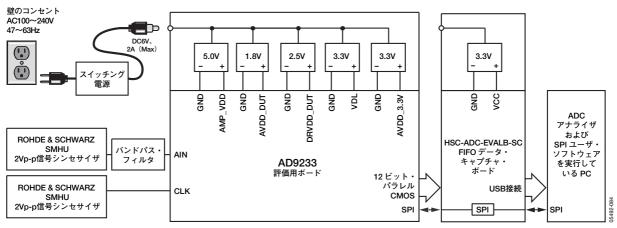

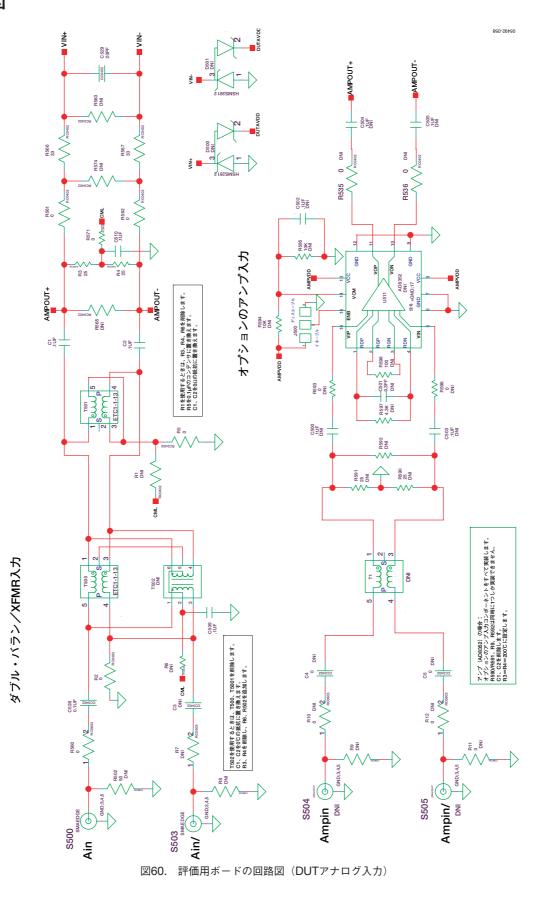

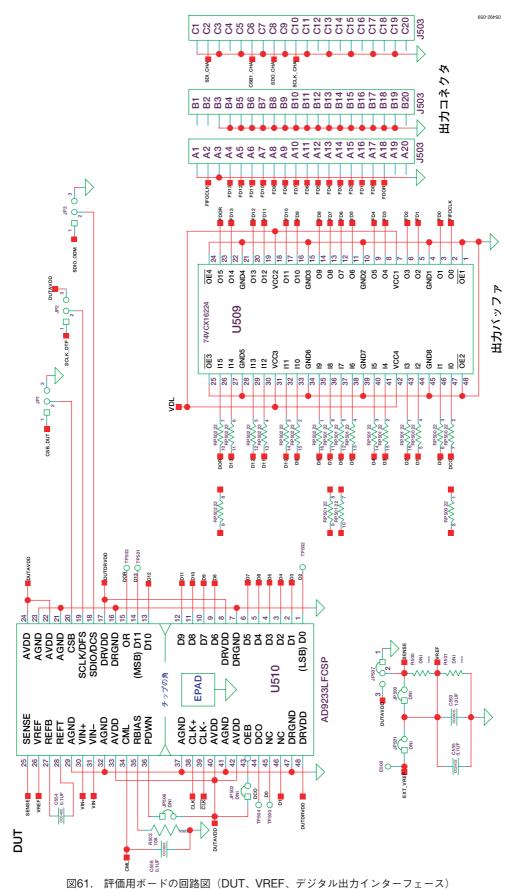

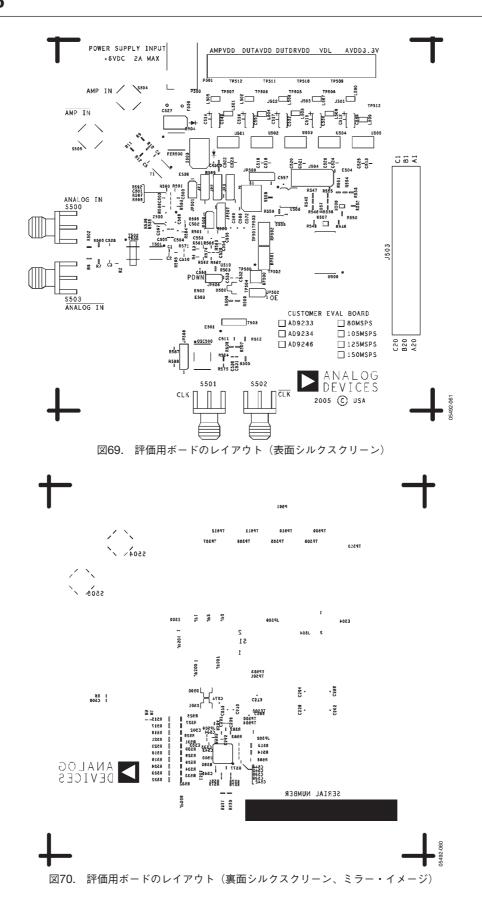

## 評価用ボード

AD9233評価用ボードは、さまざまなモードや設定でADCを動作させるためのあらゆる回路を提供します。コンバータは、ダブル・バラン構成(デフォルト)またはAD8352差動ドライバにより、差動で駆動できます。ADCは、シングルエンドでも駆動できます。DUTをAD8532駆動回路から分離するために独立した電源ピンが用意されています。各入力構成は、さまざまなコンポーネントを適切に接続することで選択できます。図59に、AD9233のAC性能を評価する場合の代表的なベンチ特性の設定を示します。

コンバータの最適な性能を得るには、アナログ入力やクロックの信号源に位相ノイズが非常に小さい(1ps未満のrmsジッタ)ものを使うことが非常に重要です。仕様規定のノイズ性能を得るには、アナログ入力信号を適切にフィルタリングして高調波を除去し、入力での総合(ブロードバンド)ノイズを小さくすることも必要です。

図60~図70の回路図とレイアウト図には、システム・レベルで適用する配線方法とグラウンディング方法を示します。

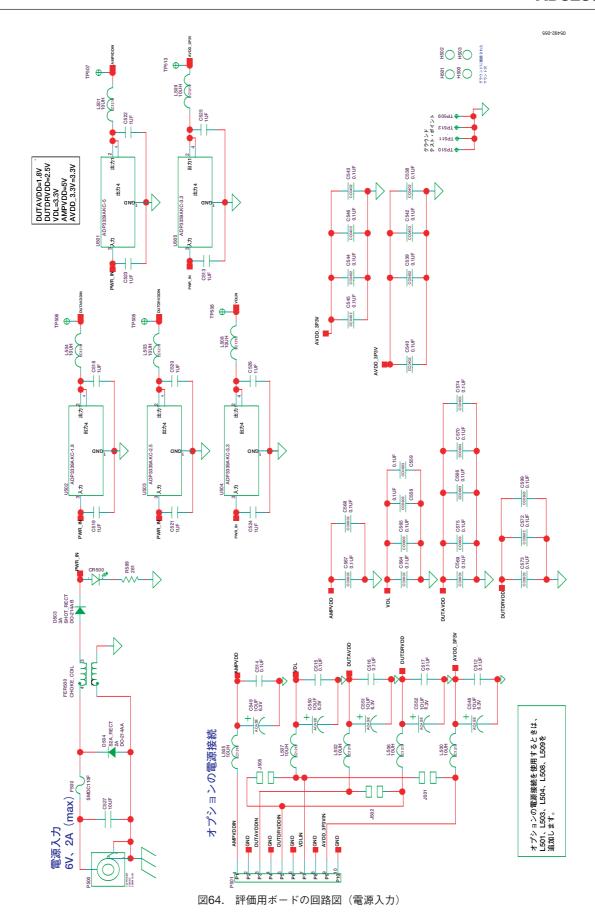

#### 雷源

この評価用ボードは、壁面取付け可能なスイッチング電源を備え、6V、2Aの最大出力を提供します。電源コードは定格電圧  $100\sim240V$ ( $47\sim63$ Hz)のコンセントに差し込み、もう一方の内径2.1mmのジャック(P500)はPCボードに接続します。PCボード上では、6V電源がヒューズで保護され調整された後、5個の低ドロップアウト・リニア・レギュレータに接続されます。レギュレータは、ボードの各セクションに適正なバイアスを与えます。評価用ボードをデフォルト以外の状態で使用するときは、L501、L503、L504、L508、L509を外してスイッチング電源を切断し、ボードの各セクションに個別にバイアスを与えることができます。P501を使ってセクションごとに異なる電源を接続してください。

AVDD\_DUTおよびDRVDD\_DUTの1Aの電流能力には最低1個の1.8V電源が必要ですが、アナログ用とデジタル用に独立した電源を使用することを推奨します。

AD8352オプションを使って評価用ボードを使用するには、独立した5.0Vのアナログ電源が必要です。この5.0V電源 (AMP\_VDD) には、1Aの電流能力が必要です。代替のSPIオプションを使って評価用ボードを操作するには、さらに3.3Vのアナログ電源が必要となります。この3.3V電源 (ADDD\_3.3V)にも1Aの電流能力が必要です。これらの電源はハンダ・ジャンパJ501、J502、J505で接続できます。詳細については、図64を参照してください。

#### 入力信号

クロックおよびアナログ・ソースを接続するときは、Rohde & Schwarz SMHU、Agilent HP8644またはこれと同等の、低位相ノイズのクリーンな信号を得られる信号発生器を使用します。評価用ボードへの接続には、長さ1mのシールドされた50 $\Omega$ の同軸ケーブル(RG-58)を使用します。ADCに必要な周波数と振幅を入力してください。通常、アナログ・デバイセズのほとんどの評価用ボードは、クロック用として約2.8Vp-pまたは13dBmのサイン波を入力できます。アナログ入力ソースを接続するときは、50 $\Omega$ の終端を接続したナローバンドの多極バンドパス・フィルタの使用を推奨します。アナログ・デバイセズでは、TTE®、Allen Avionics、K&L®タイプのバンドパス・フィルタを使用しています。可能であれば、フィルタを評価用ボードに直接接続してください。

#### 出力信号

パラレルCMOS出力は、アナログ・デバイセズの1チャンネル FIFOデータ・キャプチャ・ボード(HSC-ADC-EVALB-SC)と直接インターフェースします。FIFOボードとその設定(オプション)については、www.analog.com/FIFOをご覧ください。

図59. 評価用ボードの接続

#### デフォルトの動作とジャンパ選択の設定

AD9233評価用ボードRev.Aに関するデフォルト、オプションの設定またはモードを以下に示します。

#### 雷源

評価キットに付属のスイッチング電源は、一方のコードを定格電圧AC100~240V (47~63Hz) のコンセントに差し込み、もう一方のジャック (P500) をPCボードに差し込みます。

#### VIN

評価用ボードは、ダブル・バラン構成のアナログ入力用にセットアップされ、70MHzで最適な50Ωインピーダンス・マッチングが行われます。帯域幅応答を増やすには、アナログ入力の差動コンデンサを変更または削除します(表8を参照)。アナログ入力の同相は、ADCのCMLピンを介してトランスの中央タップから生成されます。詳細については、「アナログ入力に関する考慮事項」を参照してください。

#### **VREF**

VREFを1.0Vに設定するには、SENSEピンからJP507(1番ピン、2番ピン)を介してグラウンドに接続します。これでADCは2.0Vp-pのフルスケール範囲で動作します。評価用ボードには、独立した外部リファレンス・オプションも付属しています。2番ピンと3番ピン間でJP507を接続し、さらにJP501を接続し、E500で外部リファレンスを接続します。VREFオプションの適正な使用法については、「電圧リファレンス」で詳述しています。

#### **RBIAS**

RBIASとグラウンド間に $10k\Omega$ (R503)を接続し、このピンでADCコアのバイアス電流を設定します。

#### クロック

デフォルトのクロック入力回路は、クロック・パスにわずかなジッタを与える広帯域インピーダンス1:1トランス(T503)を用いた単純なトランス結合回路から派生したものです。クロック入力は $50\Omega$ で終端され、AC結合されて、シングルエンド・サイン波入力を処理します。トランスは、シングルエンド入力を、ADCクロックを入力する前にクリップされる差動信号に変換します。

#### **PDWN**

パワーダウン機能をイネーブルし、JP506を接続して、PDWN ピンをAVDDに短絡させます。

#### **CSB**

CSBピンは内部でプルアップされ、チップを外部ピン・モードに設定し、SDIOおよびSCLKの情報を無視します。CSBピンのコントロールを評価用ボードのSPI回路に接続するには、JP1の1番ピンおよび2番ピンを接続してください。チップをシリアル・ピン・モードにし、SDIOピンとSCLKピンのSPI情報を有効にするには、常時イネーブル・モードでJP1をローに固定します(2番ピンと3番ピンを接続します)。

#### SCLK/DFS

SPIポートが外部ピン・モードの場合は、SCLK/DFSピンで出力のデータ形式を設定します。このピンはフロート状態のままであれば、内部でプルダウンされ、デフォルト状態がバイナリに設定されます。JP2の2番ピンと3番ピンを接続すると、データ形式が2の補数に設定されます。SPIポートがシリアル・ピン・モードの場合にJP2の1番ピンと2番ピンを接続すると、SCLKピンがオンボードのSPI回路に接続されます。詳細については、「シリアル・ポート・インターフェース(SPI)」を参照してください。

#### SDIO/DCS

SPIポートが外部ピン・モードの場合は、SDIO/DCSピンによってデューティ・サイクル・スタビライザが設定されます。このピンはフロート状態のままであれば、内部でプルダウンされ、デフォルト状態がDCSイネーブルに設定されます。DCSをディスエーブルにするには、JP3の2番ピンと3番ピンを接続します。SPIポートがシリアル・ピン・モードの場合にJP3の1番ピンと2番ピンを接続すると、SDIOピンがオンボードのSPI回路に接続されます。詳細については、「シリアル・ポート・インターフェース(SPI)」を参照してください。

#### その他のクロック設定

差動LVPECLクロックを使用して、AD9516 (U500) を使ってADC入力を駆動することもできます。この駆動オプションを使用するときは、表16に示すコンポーネントを追加する必要があります。詳細については、AD9515のデータシートをご覧ください。

デフォルトのトランス・オプションの代わりにAD9515を駆動するためにアナログ入力を設定するには、下記のようにコンポーネントを適宜追加、削除、変更する必要があります。

- デフォルトのクロック経路でR507、R508、C532、C533を 削除します。

- ・ デフォルトのクロック経路に $0\Omega$ 抵抗のR505とC531を追加します。

- R511、R512、R513、R515~R524、U500、R580、R582、R583、R584、C536、C537、C586を追加します。

発振器を使用する場合は、2つの発振器フットプリント・オプション(OSC500)を使用してADCの性能をチェックすることもできます。JP508を適用すれば、ほとんどの発振器に共通するイネーブル・ピンを柔軟に使用できます。このオプションを使用する場合は、OSC500、R575、R587、R588を追加します。

## その他のアナログ入力駆動設定

ここでは、AD8352を使用したその他のアナログ入力駆動設定を簡単に説明します。この特殊な駆動オプションを使用する場合は、表16に記載する特定のコンポーネントを追加する必要があります。AD8352差動ドライバの動作原理やオプション・ピンの設定など、詳細については、AD8352のデータシートをご覧ください。

デフォルトのトランス・オプションの代わりにAD8352を駆動するためにアナログ入力を設定するには、下記のようにコンポーネントを適宜追加、削除、または変更する必要があります。

- デフォルトのアナログ入力経路でC1とC2を削除します。

- 200Ω抵抗のR3とR4を追加します。

- オプションのアンプ入力経路に、R594、R595、C502を除くすべてのコンポーネントを追加します。入力経路を終端させるために追加するコンポーネントは、これら(R9、R592、R590、R591)のうちの1つのみとします。

- アナログ入力経路で5pFのコンデンサC529を追加します。

現在は、信号接続のために $0\Omega$ のR561とR562が追加されています。この領域では、条件が追加された場合にフィルタを設計できます。

— 30 — REV. A

# 回路図

REV. A -31 -

05492-057 AD9515 ロジック セットアップ SS S K 감 AD9515 (OPT\_CLK) を使用する場合は、R507、R508、C533、C533、C532を削除します。 C531、R505=0を実装します。 C536 0.1UF DN 0.1UF 0.1UF R582 100 DNI R585 100 A R583 240 DNI CLK R584 240 DNI S1 S2 S3 S4 S5 S6 S7 S8 S9 S1( R588 10K 10K NIV DN NECE R581 DNI R578 DNI R576 DNI R579 DNII R510 DNI OPT\_CLK 1/N No. OPT\_CLK OPT\_CLK R575 0 DNI XFMR/AD9515 クロック回路 0.1UF R504 SSOIMEDGE SSOIMEDGE CLK/ 図62. 評価用ボードの回路図(DUTクロック入力)

REV. A - 33 -

REV. A - 35 -

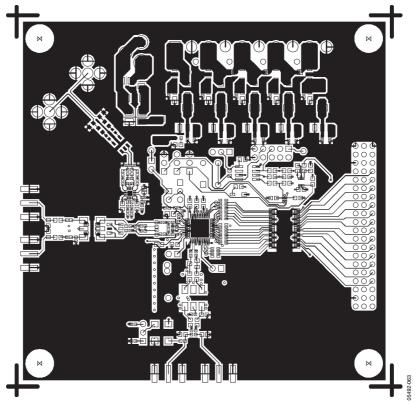

# 評価用ボードのレイアウト

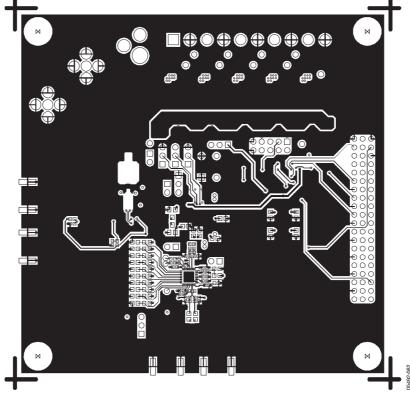

図65. 評価用ボードのレイアウト (表面)

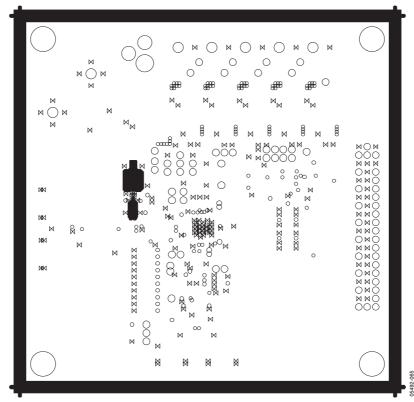

図66. 評価用ボードのレイアウト (裏面、ミラー・イメージ)

— 36 — REV. A

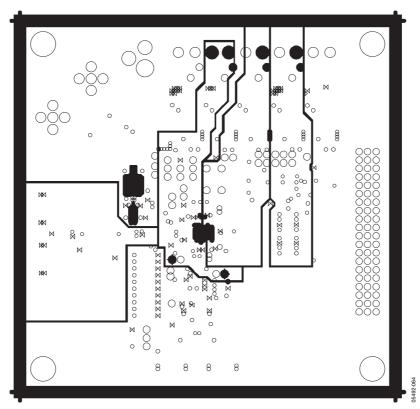

図67. 評価用ボードのレイアウト (グラウンド・プレーン)

図68. 評価用ボードのレイアウト (電源プレーン)

REV. A - 37 -

# 部品表(BOM)

表16. 評価用ボードのBOM

| 項目 | 数量 | 未実装<br>(DNI) | 参照番号                                                                                                                                       | デバイス      | パッケージ                       | 説明                                     | サプライヤ/製品番号                               |

|----|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------|----------------------------------------|------------------------------------------|

| 1  | 1  | (2.11)       | AD9246CE_REVA                                                                                                                              | PCボード     |                             | PCボード                                  | アナログ・デバイセズ                               |

| 2  | 24 |              | C1, C2, C509, C510, C511, C512, C514, C515, C516, C517, C528, C530, C532, C533, C538, C539, C540, C542, C543, C544, C545, C546, C554, C555 | コンデンサ     | 0402                        | 0.1μF                                  | 771777711                                |

|    |    | 12           | C3, C500, C502, C503, C504, C505, C531, C534, C535, C536, C537, C557                                                                       |           |                             |                                        |                                          |

| 3  |    | 1            | C501                                                                                                                                       | コンデンサ     | 0402                        | 0.3pF                                  |                                          |

| 4  |    | 2            | C4, C5                                                                                                                                     | 抵抗        | 0402                        | 0Ω                                     |                                          |

| 5  | 10 |              | C513、C518、C519、C520、C521、<br>C522、C523、C524、C525、C526                                                                                      | コンデンサ     | 0402                        | 1.0μF                                  |                                          |

| 6  | 1  |              | C527                                                                                                                                       | コンデンサ     | 1206                        | 10μF                                   |                                          |

| 7  | 1  |              | C529                                                                                                                                       | コンデンサ     | 0402                        | 20pF                                   |                                          |

| 8  | 5  |              | C548、C549、C550、C551、C552                                                                                                                   | コンデンサ     | ACASE                       | 10μF                                   |                                          |

| 9  | 1  |              | C553                                                                                                                                       | コンデンサ     | 0805                        | 1.0μF                                  |                                          |

| 10 | 15 |              | C556, C558, C559, C564, C565,<br>C566, C567, C568, C569, C570,<br>C572, C573, C574, C575, C599                                             | コンデンサ     | 0603                        | 0.1μF                                  |                                          |

| 11 | 1  |              | CR500                                                                                                                                      | LED       | 0603                        | 緑                                      | Panasonic<br>LNJ314G8TRA                 |

| 12 | 1  |              | D502                                                                                                                                       | ダイオード     | SOT-23                      | 30V、20mA、<br>デュアル・                     | HSMS2812                                 |

| 10 | 1  | 2            | D500、D501                                                                                                                                  | ダイオード     | DO 2144D                    | ショットキ                                  | W. G. 11G                                |

| 13 | 1  |              | D503                                                                                                                                       | ダイオード     | DO-214AB                    | 3 A、30V、<br>SMC                        | Micro Commercial Group<br>SK33-TPMSCT-ND |

| 14 | 1  |              | D504                                                                                                                                       | ダイオード     | DO-214AA                    | 2 A、50V、<br>SMC                        | Micro Commercial Group<br>S2A-TPMSTR-ND  |

| 15 |    | 1            | D505                                                                                                                                       | LED       | LN1461C                     | AMB                                    | Amber LED                                |

| 16 | 1  |              | F500                                                                                                                                       | ヒューズ      | 1210                        | 6.0V、2.2 A<br>トリップ電流<br>再設定可能な<br>ヒューズ | Tyco, Raychem<br>NANO SMDC110F-2         |

| 17 | 1  |              | FER500                                                                                                                                     | チョーク      | 2020                        |                                        | Murata<br>DLW5BSN191SQ2                  |

| 18 |    | 1            | J500                                                                                                                                       | ジャンパ      |                             | ハンダ・ジャンパ                               |                                          |

| 19 |    | 3            | J501、J502、J505                                                                                                                             | ジャンパ      |                             | ハンダ・ジャンパ                               |                                          |

| 20 | 1  |              | J503                                                                                                                                       | コネクタ      | 120ピン                       | オス・ヘッダ                                 | Samtec<br>TSW-140-08-G-T-RA              |