# デュアル、16 ビット、12.6GSPS RF DAC およびダイレクト・ デジタル・シンセサイザ

-タシート

- マルチバンド・ワイヤレス・アプリケーションをサポート RF DAC ごとに 3 チャンネルのバイパス可能な複素データ 入力チャンネル

- 1 入力チャンネルあたり 3.08GSPS の最大複素入力データ・ レート

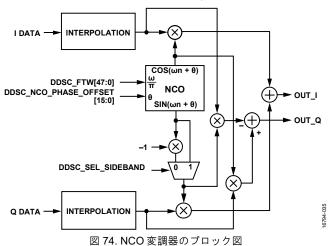

- 1入力チャンネルあたり1個の独立した NCO

- 独自の低スプリアス/低歪み設計

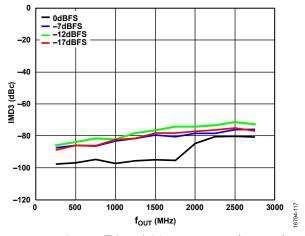

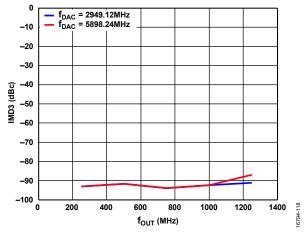

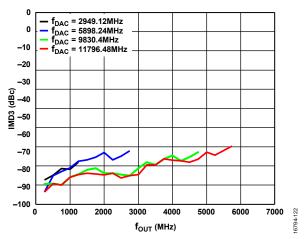

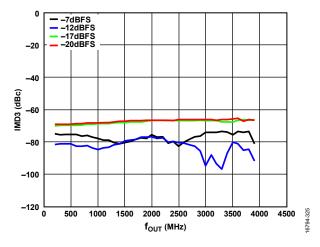

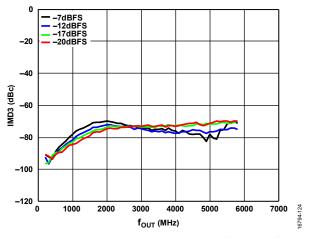

- 2 トーン IMD3 = -83dBc (1.84GHz、-7dBFS/トーンの RF 出力時)

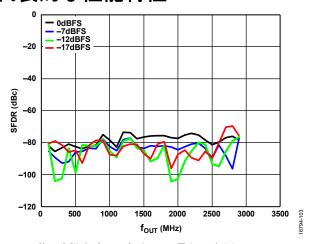

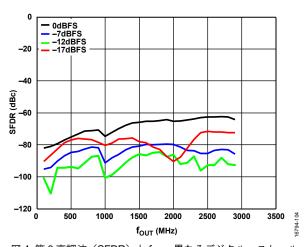

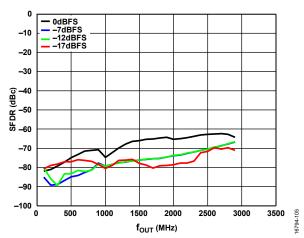

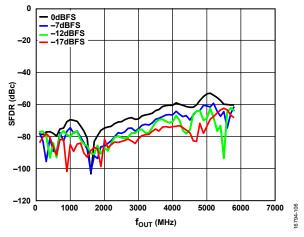

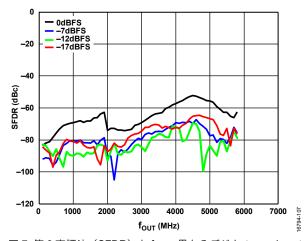

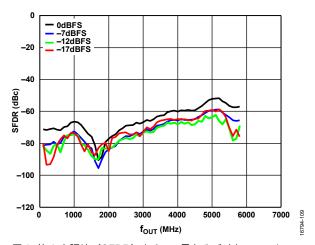

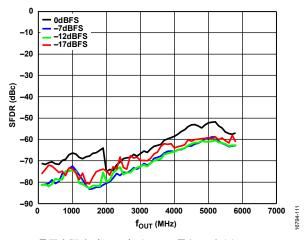

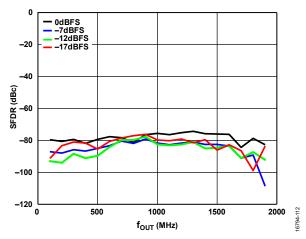

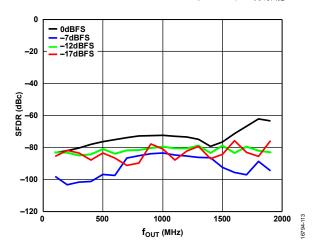

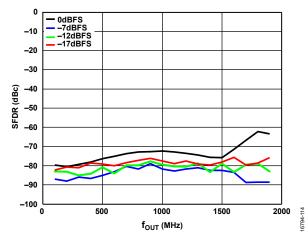

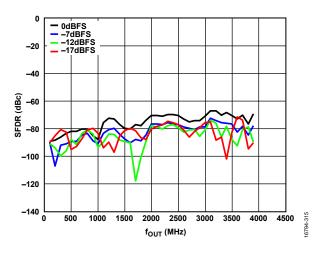

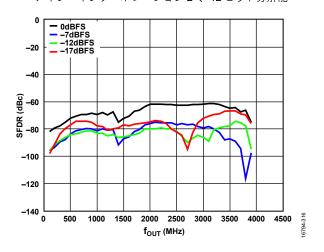

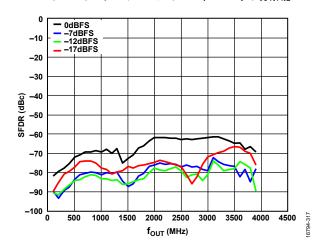

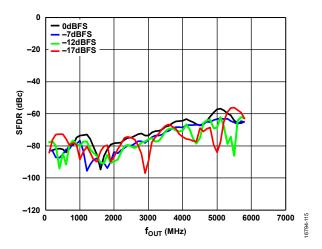

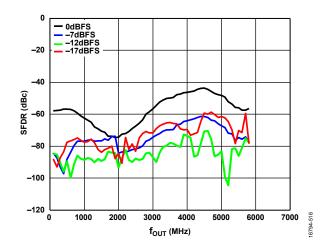

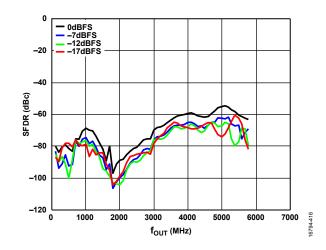

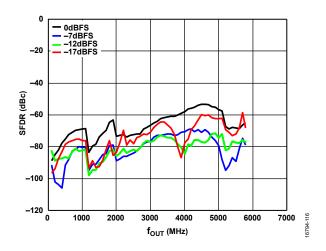

- SFDR < -80dBc(1.84GHz、-7dBFS の RF 出力時)

- 8 レーン、15.4Gbps の柔軟な JESD204B インターフェース シングルバンドおよびマルチバンドの用途に対応

- 高データ・スループットを実現する 12 ビット高密度モード をサポート

#### 複数チップの同期

JESD204B サブクラス 1 に対応

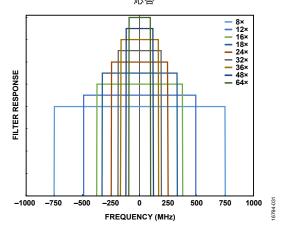

- あらゆる入力データ・レートに対応する設定変更可能な インターポレーション・フィルタ

- 構成可能なデータ・チャンネル・インターポレーション: 1×、2×、3×、4×、6×、8×

- 構成可能な最終インターポレーション:1×、2×、4×、6×、 8×、12×

- DAC レートで動作する 48 ビットの最終 NCO により、 最大 6GHz の周波数合成をサポート

- 送信イネーブル機能による極めて高い節電と下流回路の保護 高性能、低ノイズの PLL クロック逓倍器

- 12.6GSPS の DAC 更新レートをサポート 分周比を選択可能なオブザベーション ADC クロック・

#### ドライバ 低消費電力

2DAC で 2.54W(12GSPS、DAC PLL オン時)

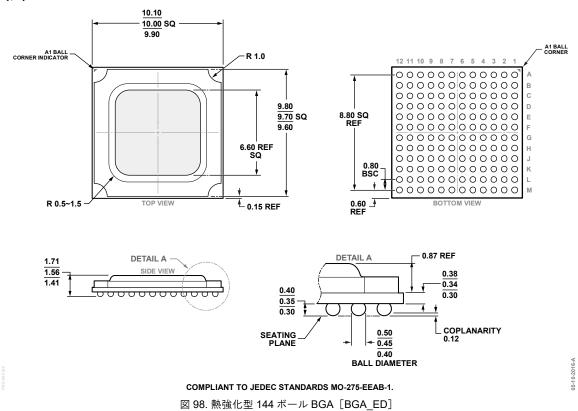

10mm×10mm、金属強化サーマル・リッド付き 144 ボール BGA\_ED、0.80mm ピッチ

#### アプリケーション

ワイヤレス通信インフラストラクチャ マルチバンド基地局無線

マイクロ波/E パンド・バックホール・システム 計測器、ATE(自動試験装置)

レーダーおよび電波妨害装置

#### 概要

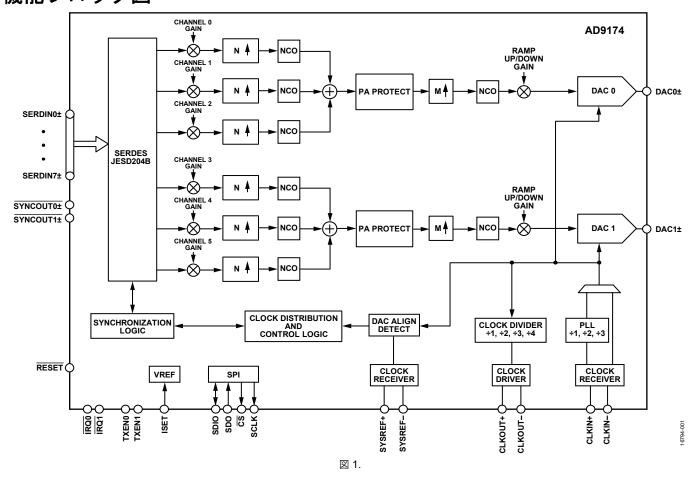

AD9174 は、最大 12.6GSPS の DAC サンプル・レートをサポー トする高性能なデュアル 16 ビット D/A コンバータ (DAC) で す。15.4Gbps、8 レーンの JESD204B データ入力ポート、高性能 のオンチップ DAC クロック逓倍器に加えて、シングルバンドと マルチバンドのダイレクト to 無線周波数 (RF) ワイヤレス・ア プリケーションを対象としたデジタル信号処理機能を備えてい るのが特長です。

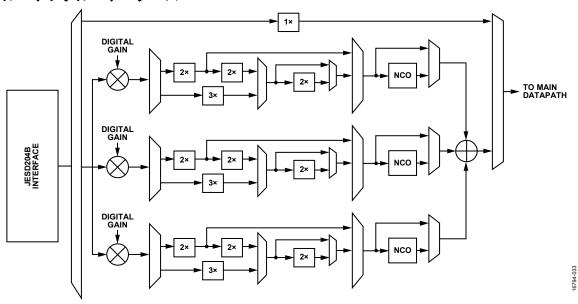

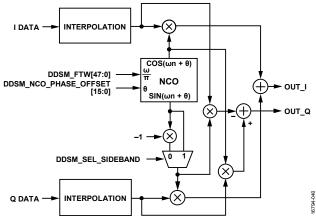

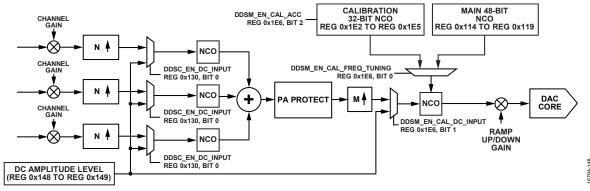

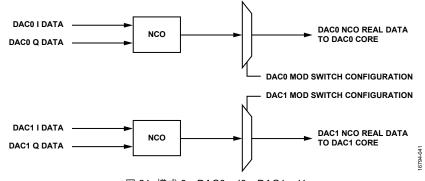

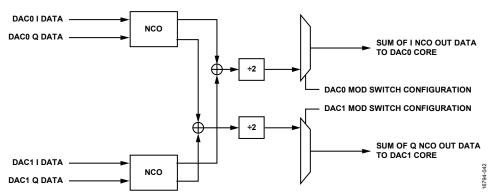

AD9174は、RF DAC データパスあたり 3 つの複素データ入力チ ャンネルを備えています。各入力チャンネルは完全にバイパス 可能です。各データ入力チャンネル(もしくはチャネライザ) は、設定変更可能なゲイン段、インターポレーション・フィル タ、チャンネル数値制御発振器(NCO)を備えているので、マ ルチバンド周波数の設計を柔軟に行えます。このデバイスは、 最大 3.08GSPS の複素(同相/直交位相(I/Q))、もしくは最 大 6.16GSPS の非複素 (実数) の入力データ・レートをサポート しています。また、個々の処理に割り当てられたチャンネルに 対して複数の複素入力データ・ストリームを配分する機能があ ります。3 つのチャネライザの各グループは、追加処理のため に必要に応じて、それぞれのメイン・データパスに加算されます。各メイン・データパスには、インターポレーション・フィル タと 1 つの 48 ビットのメイン NCO が搭載され、その後段に RF DAC コアがあります。変調器スイッチを使用すると、メイン・ データパスの出力は、DAC0 にのみ送られてシングル DAC とし て動作することも、DACO および DAC1 の両方に送られてデュ アルの中間周波数 DAC (IF DAC) として動作することもできま す。

また、AD9174 はチャネライザとメイン・データパスをバイパ スできる超広帯域データ・レート・モードをサポートしており、 シングル 16 ビット DAC として 6.16GSPS まで、デュアル 16 ビ ット DAC として 3.08GSPS まで、または、デュアル 12 ビット DAC として 4.1GSPS までの最大データ・レートを実現します。 更に、AD9174のメイン NCO ブロックには 31 個の 32 ビット NCO のバンクが組み込まれており、それぞれ個別の位相アキュムレー タを備えています。NCOを設定するための80MHzのシリアル・ ペリフェラル・インターフェース (SPI) を組み合わせることで、 動作中に NCO の周波数が連続的に調整されるアプリケーション において、このバンクは位相コヒーレントな高速周波数ホッピ ング (FFH) を可能にします。

AD9174は144ボールBGAEDパッケージを採用しています。

#### 製品のハイライト

- 広帯域幅およびマルチチャンネルのアプリケーションで は、低消費電力、マルチチャンネル、デュアル DAC の設 計により、性能を維持しながら消費電力を低減できます。

- RF DAC あたり 3 つのバイパスが可能な複素データ・チャ ンネルを備えたシングルバンドおよびマルチバンドのワイ ヤレス・アプリケーション、または、内蔵の変調器スイッ チを使用する場合に、2つのメイン・データパスを2つの 広帯域複素データ・チャンネルとして使用する構成をサポ ートしています。

- 16 ビットの分解能で 3.08GSPS まで、および 12 ビットの分 解能で4.1GSPSまでの最大複素データ・レート(Iまたは Qあたり)。また、AD9174はデュアルDACとして構成可 能で、各 DAC は個別の JESD204B リンクを通して前述の データ・レートで動作することができます。

- 16 ビットの分解能で最大 6.16GSPS までのデータ・レート をサポートする超広帯域幅のシングル DAC モード。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2019 Analog Devices, Inc. All rights reserved

Rev 0

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

# 目次

| 特長                           | 1  |

|------------------------------|----|

| アプリケーション                     | 1  |

| 概要                           | 1  |

| 製品のハイライト                     | 1  |

| 改訂履歴                         | 2  |

| 機能ブロック図                      | 3  |

| 仕様                           | 4  |

| DC 仕様                        | 4  |

| デジタル仕様                       | 5  |

| 最大 DAC 更新レート仕様               | 5  |

| 電源の DC 仕様                    | 6  |

| シリアル・ポートと CMOS ピンの仕様         | 9  |

| デジタル入力データのタイミング仕様            | 10 |

| JESD204B インターフェースの電気的仕様と速度仕様 | 11 |

| 入力データ・レートと信号帯域幅の仕様           | 12 |

| AC 仕様                        | 13 |

| 絶対最大定格                       | 15 |

| リフロー・プロファイル                  | 15 |

| 熱特性                          | 15 |

| ESD に関する注意                   | 15 |

| ピン配置およびピン機能の説明               | 16 |

| 代表的な性能特性                     | 19 |

| 用語の定義                        | 27 |

| 動作原理                         | 28 |

| シリアル・ポートの動作                  | 30 |

| データ・フォーマット                   | 30 |

| シリアル・ポート・ピンの説明               | 30 |

| シリアル・ポート・オプション               | 31 |

| JESD204B シリアル・データ・インターフェース32 |

|------------------------------|

| JESD204B の概要                 |

| 物理層36                        |

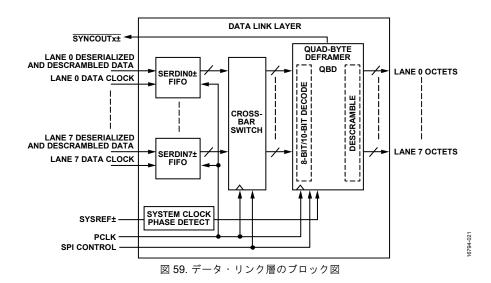

| データ・リンク層38                   |

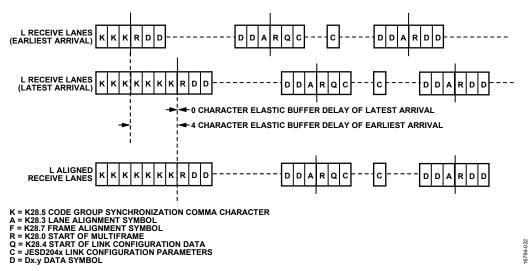

| LMFC 信号同期40                  |

| トランスポート層46                   |

| JESD204B のテスト・モード            |

| JESD204B のエラー・モニタリング49       |

| デジタル・データパス52                 |

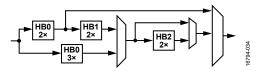

| 合計データパス・インターポレーション52         |

| チャンネル・デジタル・データパス53           |

| メイン・デジタル・データパス56             |

| NCO オンリー・モード60               |

| 変調器スイッチ62                    |

| 割込み要求動作                      |

| 割込みサービス・ルーチン66               |

| アナログ・インターフェース67              |

| DAC 入力クロック設定67               |

| クロック出力ドライバ69                 |

| アナログ出力69                     |

| アプリケーション情報71                 |

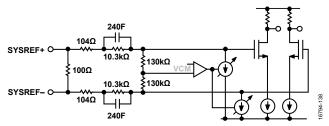

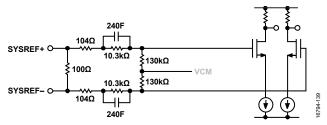

| ハードウェアに関する考慮事項71             |

| スタートアップ・シーケンス74              |

| レジスタの一覧81                    |

| レジスタの詳細93                    |

| 外形寸法                         |

| オーダー・ガイド163                  |

### 改訂履歴

11/2018—Revision 0: Initial Version

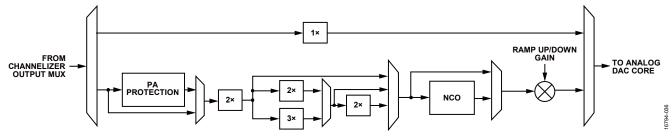

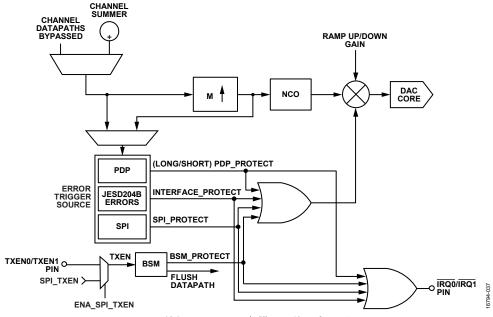

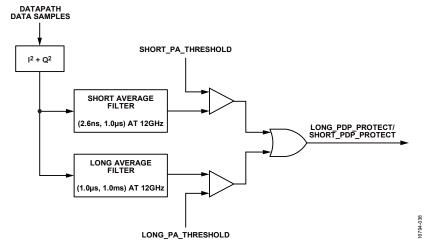

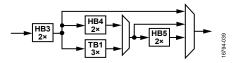

## 機能ブロック図

Rev. 0 - 3/163 -

### 仕様

### DC 仕様

特に指定のない限り、AVDD1.0 = 1.0V、AVDD1.8 = 1.8V、DVDD1.0 = 1.0V、DVDD1.8 = 1.8V、SVDD1.0 = 1.0V、DAC 出力フルスケール電流( $I_{OUTFS}$ ) = 20mA。最小値と最大値は  $I_{J}$  =  $-40^{\circ}$ C~+118 $^{\circ}$ C での値、代表値は  $I_{A}$  = 25 $^{\circ}$ C ( $I_{J}$  = 51 $^{\circ}$ C に相当)での値。

表 1.

| Parameter                                        | Test Conditions/Comments                     | Min   | Тур   | Max  | Unit   |

|--------------------------------------------------|----------------------------------------------|-------|-------|------|--------|

| RESOLUTION                                       |                                              | 16    |       |      | Bit    |

| ACCURACY                                         |                                              |       |       |      |        |

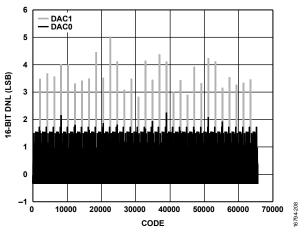

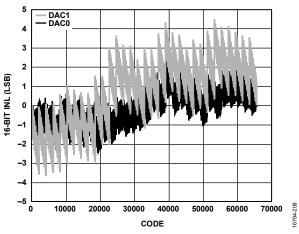

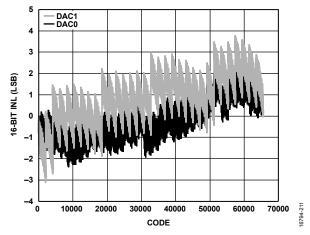

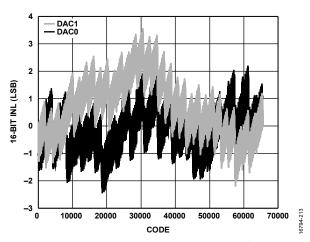

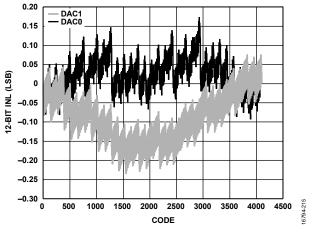

| Integral Nonlinearity (INL)                      |                                              |       | ±7    |      | LSB    |

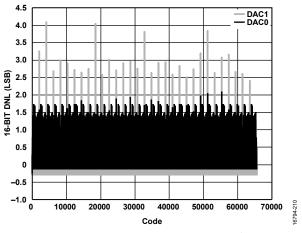

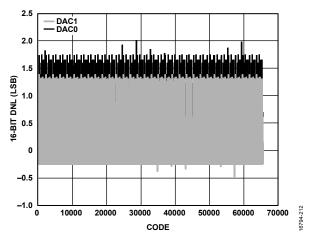

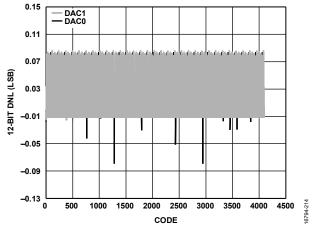

| Differential Nonlinearity (DNL)                  |                                              |       | ±7    |      | LSB    |

| ANALOG OUTPUTS (DAC0+, DAC0-, DAC1+, DAC1-)      |                                              |       |       |      |        |

| Gain Error (with Internal ISET Reference)        |                                              |       | ±15   |      | %      |

| Full-Scale Output Current                        |                                              |       |       |      |        |

| Minimum                                          | $R_{SET} = 5 k\Omega$                        | 14.2  | 16    | 17.8 | mA     |

| Maximum                                          | $R_{SET} = 5 \text{ k}\Omega$                | 23.6  | 26    | 28.8 | mA     |

| Common-Mode Voltage                              |                                              |       | 0     |      | V      |

| Differential Impedance                           |                                              |       | 100   |      | Ω      |

| DAC DEVICE CLOCK INPUT (CLKIN+, CLKIN-)          |                                              |       |       |      |        |

| Differential Input Power                         | $R_{LOAD} = 100 \Omega$ differential on-chip |       |       |      |        |

| Minimum                                          |                                              |       | 0     |      | dBm    |

| Maximum                                          |                                              |       | 6     |      | dBm    |

| Differential Input Impedance <sup>1</sup>        |                                              |       | 100   |      | Ω      |

| Common-Mode Voltage                              | AC-coupled                                   |       | 0.5   |      | V      |

| CLOCK OUTPUT DRIVER (CLKOUT+, CLKOUT-)           |                                              |       |       |      |        |

| Differential Output Power                        |                                              |       |       |      |        |

| Minimum                                          |                                              |       | -9    |      | dBm    |

| Maximum                                          |                                              |       | 0     |      | dBm    |

| Differential Output Impedance                    |                                              |       | 100   |      | Ω      |

| Common-Mode Voltage                              | AC-coupled                                   |       | 0.5   |      | V      |

| Output Frequency                                 |                                              | 727.5 |       | 3000 | MHz    |

| TEMPERATURE DRIFT                                |                                              |       |       |      |        |

| Gain                                             |                                              |       | 10    |      | ppm/°C |

| REFERENCE                                        |                                              |       |       |      |        |

| Internal Reference Voltage                       |                                              |       | 0.495 |      | V      |

| ANALOG SUPPLY VOLTAGES                           |                                              |       |       |      |        |

| AVDD1.0                                          |                                              | 0.95  | 1.0   | 1.05 | V      |

| AVDD1.8                                          |                                              | 1.71  | 1.8   | 1.89 | V      |

| DIGITAL SUPPLY VOLTAGES                          |                                              |       |       |      |        |

| DVDD1.0                                          |                                              | 0.95  | 1.0   | 1.05 | V      |

| DAVDD1.0                                         |                                              | 0.95  | 1.0   | 1.05 | V      |

| DVDD1.8                                          |                                              | 1.71  | 1.8   | 1.89 | V      |

| SERIALIZER/DESERIALIZER (SERDES) SUPPLY VOLTAGES |                                              |       |       |      |        |

| SVDD1.0                                          |                                              | 0.95  | 1.0   | 1.05 | V      |

<sup>「</sup>詳細については、DAC入力クロック設定のセクションを参照してください。

Rev. 0 - 4/163 -

#### デジタル仕様

特に指定のない限り、AVDD1.0 = 1.0V、AVDD1.8 = 1.8V、DVDD1.0 = 1.0V、DVDD1.8 = 1.8V、SVDD1.0 = 1.0V、DAC 出力フルスケール電流( $I_{OUTFS}$ ) = 20mA。最小値と最大値は  $I_{J} = -40^{\circ}C \sim +118^{\circ}C$  での値、代表値は  $I_{A} = 25^{\circ}C$  ( $I_{J} = 51^{\circ}C$  に相当)での値。

表 2.

| Parameter                                                                        | Test Conditions/Comments              | Min  | Тур | Max   | Unit |

|----------------------------------------------------------------------------------|---------------------------------------|------|-----|-------|------|

| DAC UPDATE RATE                                                                  |                                       |      |     |       |      |

| Minimum                                                                          |                                       |      |     | 2.91  | GSPS |

| Maximum <sup>1</sup>                                                             | 16-bit resolution, with interpolation | 12.6 |     |       | GSPS |

|                                                                                  | 16-bit resolution, no interpolation   | 6.16 |     |       | GSPS |

| Adjusted <sup>2</sup>                                                            | 16-bit resolution, with interpolation | 3.08 |     |       | GSPS |

|                                                                                  | 16-bit resolution, no interpolation   | 6.16 |     |       | GSPS |

| DAC PHASE-LOCKED LOOP (PLL) VOLTAGE CONTROLLED OSCILLATOR (VCO) FREQUENCY RANGES |                                       |      |     |       |      |

| VCO Output Divide by 1                                                           |                                       | 8.74 |     | 12.42 | GSPS |

| VCO Output Divide by 2                                                           |                                       | 4.37 |     | 6.21  | GSPS |

| VCO Output Divide by 3                                                           |                                       | 2.91 |     | 4.14  | GSPS |

| PHASE FREQUENCY DETECT INPUT<br>FREQUENCY RANGE                                  |                                       | 25   |     | 770   | MHz  |

| DAC DEVICE CLOCK INPUT (CLKIN+,<br>CLKIN-) FREQUENCY RANGES                      |                                       |      |     |       |      |

| PLL Off                                                                          |                                       | 2.91 |     | 12.6  | GHz  |

| PLL On                                                                           | M divider set to divide by 1          | 25   |     | 770   | MHz  |

|                                                                                  | M divider set to divide by 2          | 50   |     | 1540  | MHz  |

|                                                                                  | M divider set to divide by 3          | 75   |     | 2310  | MHz  |

|                                                                                  | M divider set to divide by 4          | 100  |     | 3080  | MHz  |

<sup>「</sup>最大 DAC 更新レートは、選択した JESD204B モードと、その構成で使用するレーン・レートによって異なります。レーン・レートと電源電圧レベルに応じた最大 DAC レートは表 3 に示します。

#### 最大 DAC 更新レート仕様

特に指定のない限り、AVDD1.0 = 1.0V、AVDD1.8 = 1.8V、DVDD1.0 = 1.0V、DVDD1.8 = 1.8V、SVDD1.0 = 1.0V、DAC 出力フルスケール電流( $I_{OUTFS}$ ) = 20mA。最小値と最大値は  $I_{J}$  =  $-40^{\circ}C$  ~ +  $118^{\circ}C$  での値、代表値は  $I_{A}$  =  $25^{\circ}C$  ( $I_{J}$  =  $51^{\circ}C$  に相当)での値。

表 3.

| Parameter Test Conditions/Comments  |                                    | Min   | Тур | Max | Unit |

|-------------------------------------|------------------------------------|-------|-----|-----|------|

| MAXIMUM DAC UPDATE RATE             |                                    |       |     |     |      |

| SVDD1.0 = $1.0 \text{ V} \pm 5\%$   | Lane rate > 11 Gbps                | 11.67 |     |     | GSPS |

|                                     | Lane rate ≤ 11 Gbps                | 12.37 |     |     | GSPS |

| SVDD1.0 = $1.0 \text{ V} \pm 2.5\%$ | Lane rate > 11 Gbps                | 11.79 |     |     | GSPS |

|                                     | Lane rate $\leq 11 \text{ Gbps}^1$ | 12.6  |     |     | GSPS |

$<sup>^{1}</sup>$ 表 2 に示すように、オンチップ PLL を使用する場合の最大 DAC 速度は、12.42GSPS の最大 PLL 速度に制限されます。

<sup>&</sup>lt;sup>2</sup> 調整 DAC 更新レートは、f<sub>DAC</sub> を使用モードの最小必要インターポレーション係数または最大チャンネル・データ・レートで除した値として計算します。表 13 に示すように、モードが異なれば最大 DAC 更新レート、最小インターポレーション係数、最大チャンネル・データ・レートも異なります。

### 電源の DC 仕様

特に指定のない限り、AVDD1.0 = 1.0V、AVDD1.8 = 1.8V、DVDD1.0 = 1.0V、DVDD1.8 = 1.8V、SVDD1.0 = 1.0V、DAC 出力フルスケール電流( $I_{OUTFS}$ ) = 20mA。最小値と最大値は  $I_{J}$  =  $-40^{\circ}$ C~+ $118^{\circ}$ C での値、代表値は  $I_{A}$  =  $25^{\circ}$ C( $I_{J}$  =  $51^{\circ}$ C に相当)での値。

表 4.

| パラメータ                             | テスト条件/コメント                                                | Min | Тур         | Max  | 単位 |

|-----------------------------------|-----------------------------------------------------------|-----|-------------|------|----|

| DUAL-LINK MODES                   |                                                           |     |             |      |    |

| Mode 1 (L = 2, M = 4, NP          | 11.7965GSPS DAC レート、184.32MHz PLL リファレンス・クロック、32×合        |     |             |      |    |

| = 16, N = 16)                     | 計インターポレーション(4×、8×)、40MHzトーン、-3dBFS、チャンネ                   |     |             |      |    |

|                                   | ル・ゲイン= $-6dB$ 、チャンネル NCO= $\pm 150$ MHz、メイン NCO= $2$ GHz、 |     |             |      |    |

|                                   | LVDS モードでSYNCOUTx±時                                       |     | <b>50.5</b> | 1000 |    |

| AVDD1.0                           | すべての電源レベルを公称値に設定                                          |     | 725         | 1020 | mA |

|                                   | すべての電源レベルを許容誤差 5%に設定                                      |     | 775         | 1120 | mA |

| AVDD1.8                           |                                                           |     | 110         | 130  | mA |

| DVDD1.0                           | DAVDD1.0 電源と組み合わせた消費電流                                    |     |             |      |    |

|                                   | すべての電源レベルを公称値に設定                                          |     | 1100        | 1670 | mA |

|                                   | すべての電源の許容誤差は5%                                            |     | 1170        | 1850 | mA |

| DVDD1.8                           |                                                           |     | 35          | 50   | mA |

| SVDD1.0                           | すべての電源レベルを公称値に設定                                          |     | 290         | 510  | mA |

|                                   | すべての電源の許容誤差は5%                                            |     | 305         | 560  | mA |

| Total Power                       |                                                           |     | 2.37        | 3.38 | W  |

| Dissipation                       |                                                           |     |             |      |    |

| Mode 4 ( $L = 4$ , $M = 4$ , $NP$ | 11.7965GSPS DAC レート、491.52 MHz PLL リファレンス・クロック、24×合       |     |             |      |    |

| = 16, N = 16)                     | 計インターポレーション (3×、8×) 、40MHzトーン、-3dBFS、チャンネ                 |     |             |      |    |

|                                   | ル・ゲイン= $-6dB$ 、チャンネル NCO= $\pm 150$ MHz、メイン NCO= $2$ GHz、 |     |             |      |    |

|                                   | LVDS モードでSYNCOUTx±時                                       |     |             |      |    |

| AVDD1.0                           |                                                           |     | 725         |      | mA |

| AVDD1.8                           |                                                           |     | 110         |      | mA |

| DVDD1.0                           | DAVDD1.0 電源と組み合わせた消費電流                                    |     | 1150        |      | mA |

| DVDD1.8                           |                                                           |     | 35          |      | mA |

| SVDD1.0                           |                                                           |     | 425         |      | mA |

| Total Power Dissipation           |                                                           |     | 2.56        |      | W  |

| Mode 0 ( $L = 1$ , $M = 2$ , $NP$ | 5.89824GSPS DAC レート、184.32MHz PLL リファレンス・クロック、16×         |     |             |      |    |

| = 16, N = 16)                     | 合計インターポレーション (2×、8×) 、40MHzトーン、-3dBFS、チャン                 |     |             |      |    |

|                                   | ネル NCO をディスエーブル、メイン NCO = $1.8425$ GHz、LVDS モードで          |     |             |      |    |

|                                   | SYNCOUTx±時                                                |     |             |      |    |

| AVDD1.0                           | すべての電源レベルを公称値に設定                                          |     | 400         | 670  | mA |

|                                   | すべての電源の許容誤差は5%                                            |     | 425         | 745  | mA |

| AVDD1.8                           |                                                           |     | 110         | 130  | mA |

| DVDD1.0                           | DAVDD1.0 電源と組み合わせた消費電流                                    |     |             |      |    |

|                                   | すべての電源レベルを公称値に設定                                          |     | 570         | 960  | mA |

|                                   | すべての電源の許容誤差は5%                                            |     | 610         | 1070 | mA |

| DVDD1.8                           |                                                           |     | 35          | 50   | mA |

| SVDD1.0                           |                                                           |     | 175         | 340  | mA |

| Total Power Dissipation           |                                                           |     | 1.40        | 2.15 | W  |

Rev. 0 - 6/163 -

| パラメータ                              | テスト条件/コメント                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min | Тур        | Max          | 単位       |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|--------------|----------|

| Mode 3 (L = 2, M = 2, NP           | 11.7965GSPS DAC レート、184.32MHz PLL リファレンス・クロック、24×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | <u> </u>   |              |          |

| = 16, N = 16)                      | 合計インターポレーション (3×、8×) 、40MHzトーン、-3dBFS、チャン                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |            |              |          |

|                                    | $\frac{1}{2}$ $1$ |     |            |              |          |

| AMDD1 0                            | SYNCOUTx±時                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 725        |              |          |

| AVDD1.0                            | すべての電源レベルを公称値に設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | 725        |              | mA       |

| AMDD1 0                            | すべての電源の許容誤差は5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 775        |              | mA       |

| AVDD1.8<br>DVDD1.0                 | <br>  DAVDD1.0 電源と組み合わせた消費電流                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 110        |              | mA       |

| טעטעיט.0                           | DAVDDI.0 电原と組み合わせた何質电流<br>すべての電源レベルを公称値に設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 1020       |              | mA       |

|                                    | すべての電源の許容誤差は5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 1070       |              | mA       |

| DVDD1.8                            | 9~~~00电線の計分映左は370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 35         |              | mA       |

| SVDD1.0                            | <br>  すべての電源レベルを公称値に設定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 245        |              | mA       |

| 5 7 5 5 1.0                        | すべての電源の許容誤差は5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 250        |              | mA       |

| Total Power                        | ) 「 ( ) 电源( ) 川石 ( ) 注( 3 ) (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 2.25       |              | W        |

| Dissipation                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 2.23       |              | ''       |

| Mode 9 ( $L = 4$ , $M = 2$ , $NP$  | 12GSPS DAC レート、187.5MHz PLL リファレンス・クロック、8×合計イ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |            |              |          |

| = 16, N = 16)                      | ンターポレーション $(1 \times .8 \times)$ 、 $10 MHz$ トーン、 $-3 dBFS$ 、チャンネル                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |            |              |          |

|                                    | NCO をディスエーブル、メイン NCO = 3.072GHz、LVDS モードで<br>SYNCOUTx±時                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |            |              |          |

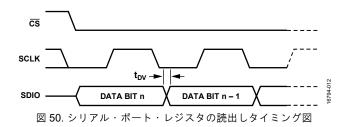

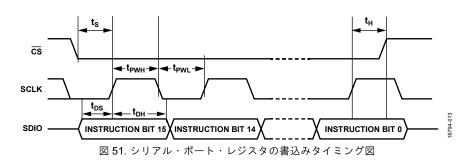

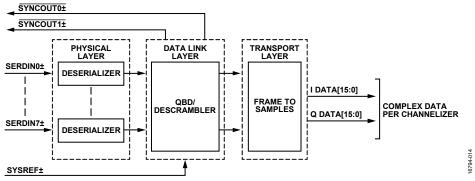

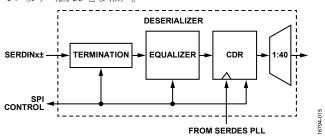

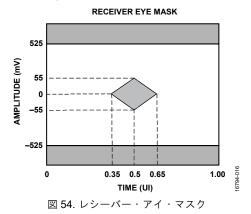

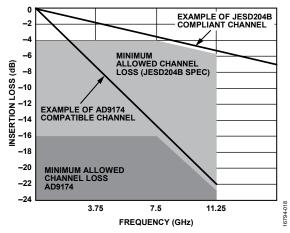

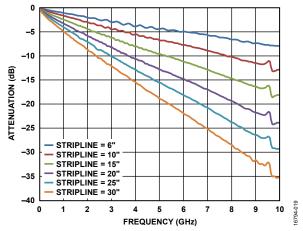

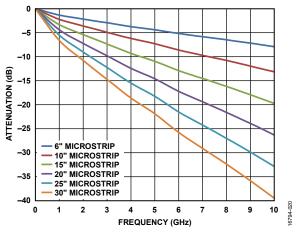

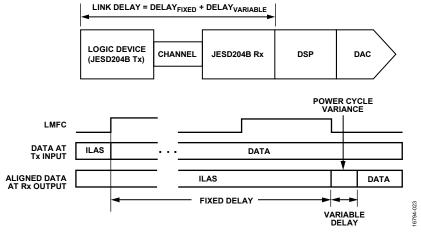

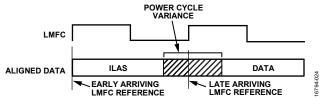

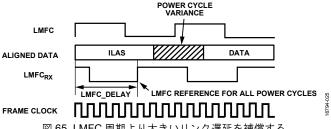

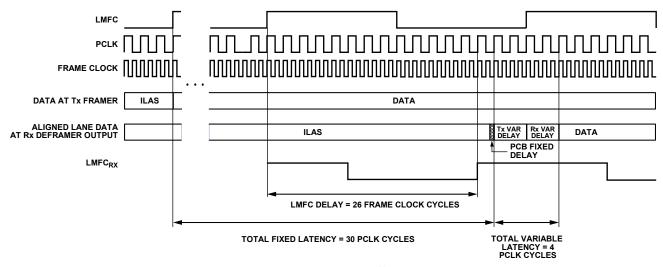

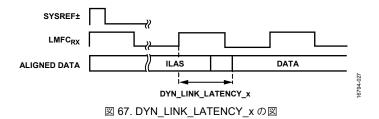

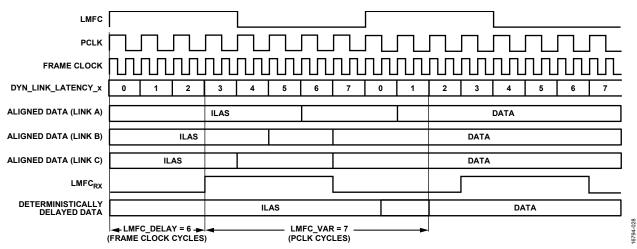

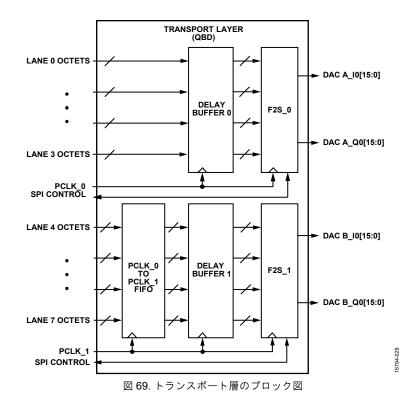

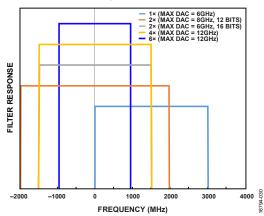

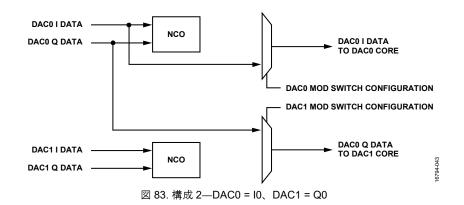

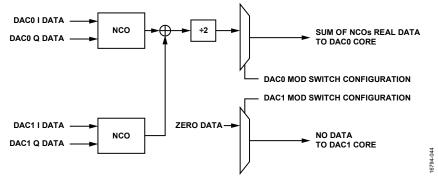

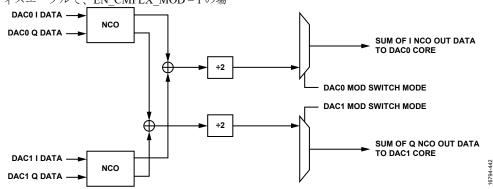

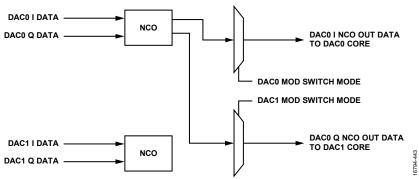

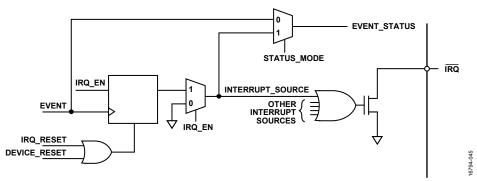

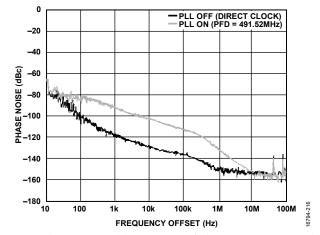

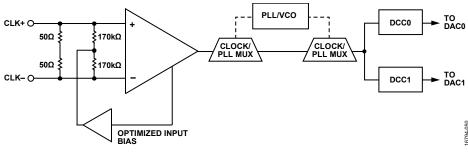

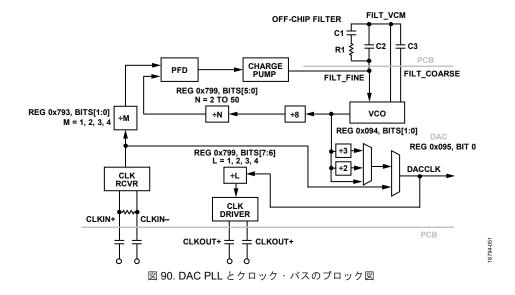

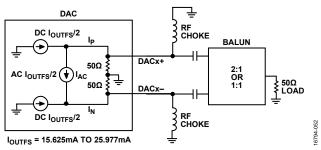

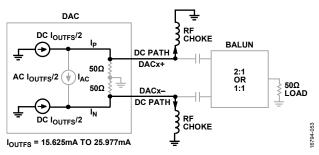

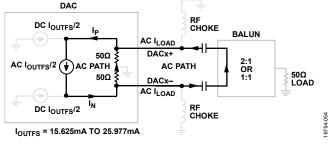

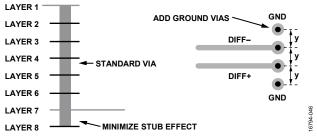

| AVDD1 0                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 740        | 1020         | 1        |