# 5 MHz ~ 500 MHz **~** 100 dB **0** リミッタ出力付き復調対数アンプ

AD8309

# 特長

## 多段構成の対数リミッタIFアンプ

100 dB**ダイナミック・レンジ:** - 78 dBm~+22 dBm(50 基準) 温度と電源に対して安定なRSSIスケーリング:

スロープ: 20 mV/dB、インターセプト(出力電圧がゼロとなる

入力電圧): - 95 dBm

200 MHzまでの60.4 dB RSSI直線性

リミッタ・ゲインと出力電流設定可能

10 mA、2.4 Vp-pまでの差動出力

合計ゲイン100 dB、帯域幅500 MHz

一定位相(±80 ps(Typ)遅延スキュー) +2.7 V~+6.5 V**の単電源、**16 mA(Typ)

**差動入力、**R<sub>IN</sub> = 1 k 、C<sub>IN</sub> = 2.5 pF

500 nsのパワーアップ時間、1 µ A以下のスリープ電流

# アプリケーション

周波数変調および位相変調の受信器

非常に広範囲なIFおよびRF電力測定

受信器信号強度表示(RSSI)

低価格レーダーおよびソーナーの信号処理

計測:ネットワーク・アナライザおよびスペクトル・アナライザ

### 概要

AD8309は完全なIFリミッタ・アンプを構成しており、5 MHz~ 500 MHz**の範囲で使用できる**100 dB**のダイナミック・レンジで入力** 信号の正確な対数(デシベル)表示(受信信号強度表示(RSSI)機能) とプログラマブルなリミッタ出力を提供します。

外付け部品点数が少なくて使い易くなっています。16 mAの + 2.7 V~ + 6.5 V**の単電源電圧で動作し、消費電力は**3 Vで50 mW以下で あり、これにアプリケーションにより決まるリミッタ・バイアス電 流が加わります(通常は2 mA程度)。200 負荷を使用した場合は、 100 dBのリミッタ・ゲインを提供します。CMOS互換のコントロー ル・インターフェースから約500 ns以内にAD8309をイネーブルす ることができ、AD8309をディスエーブルすると1 µ A以下のスタン ドバイ電流になります。

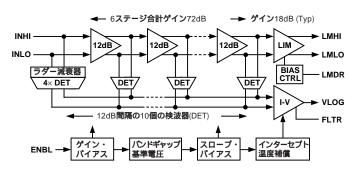

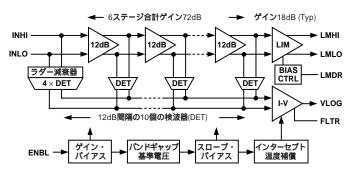

メイン・パス内にあるカスケード接続された6個の各アンプ/リ ミッタ・セルは、- 3 dB帯域幅850 MHzで12.04 dB(×4)の小信号 ゲインを持ち、72 dBの合計ゲインを提供します。プログラマブル な出力ステージは、さらに18 dBのゲインを提供します。入力は差 動であり、適度に高いインピーダンス(1k と2.5 pFの並列接続) を持っています。50 終端ソースから駆動した際の入力換算ノイ ズ・スペクトル密度は、1.28 nV/√Hzで、これは雑音指数3 dBに等 価です。入力整合ネットワークを使うとAD8309の感度を上げるこ とができます。各メイン・ゲイン・セルは全波検波器を内蔵してい ます。広帯域減衰器から駆動されるその他の4個の検波器は、ダイ ナミック・レンジの上限を48 dB以上拡張するために使用されてい ます。

#### 機能ブロック図

この組合せによる合計ダイナミック・レンジは、各々2 ∨振幅で 平衡駆動される逆位相入力を使用した場合、- 91 dBV (50 では - 78 dBmレベル)から最大許容値+9 dBVまでに拡張されます。こ れは、差動入力を50 で終端した場合の正弦波電力 + 22 dBmに相 当します。RSSI出力のスロープは厳密に20 mV/dBに制御され、イ ンターセプトは - 108 dBV( - 95 dBm - 50 )に設定されています。 これらのスケーリング・パラメータはバンドギャプ基準電圧により 決定され、実質的に温度と電源に依存しないようになっています。 対数則に対する適合度は、10 MHz~200 MHzの任意の周波数にお けるこの範囲の中心80 dBで ± 0.4 dB(typ)以内に抑えられており、 500 MHzでのみやや乖離しています。

RSSI 応答時間は公称67 ns(10%から90%)です。外付けキャパシ タの追加により限りなく、平均時間は増加します。最大入力 + 9 dBVでの2.34 Vフル出力は、50 まで下げた抵抗負荷を駆動するこ とができ、このインターフェースは出力に任意の値の容量が接続さ れても安定を維持します。

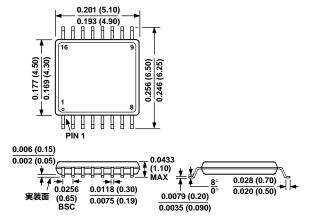

AD8309はシリコン・オン・インシュレータ絶縁技術を採用する 最新の相補型バイポーラ・プロセスで製造され、16ピンTSSOPパッ ケージを使用する - 40 ~ +85 の工業用温度範囲製品がありま す。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、 当社はその情報の利用、また利用したことにより引き起こされる第3者の特許または権 利の侵害に関して一切の責任を負いません。さらにアナログ・デバイセズ社の特許また は特許の権利の使用を許諾するものでもありません。

REV.A

**(特に指定のない限り、V。= +5 V、T。= +25 )**

| パラメータ                    | 条件                                                                        | Min <sup>1</sup> | Тур          | Max <sup>1</sup> | 単位                 |

|--------------------------|---------------------------------------------------------------------------|------------------|--------------|------------------|--------------------|

| <b>、カステージ</b>            | (INHI入力、INLO入力)                                                           | · · ·            |              |                  |                    |

| 最大入力2                    | <b>差動駆動、</b> p-p                                                          | ± 3.5            | ± 4          |                  | V                  |

|                          |                                                                           |                  | +9           |                  | dBV                |

| 50 での等価電力                | 52.3 終端                                                                   |                  | + 22         |                  | dBm                |

| ノイズ・フロア                  | 50 終端ソース                                                                  |                  | 1.28         |                  | nV/√ <del>Hz</del> |

| 50 での等価電力                | 500 MHz <b>帯域幅</b>                                                        |                  | - 78         |                  | dBm                |

| 入力抵抗                     | INHI <b>から</b> INLOへ                                                      | 800              | 1000         | 1200             |                    |

| 入力容量                     | INHI <b>から</b> INLOへ                                                      |                  | 2.5          |                  | pF                 |

| DC <b>バイアス電圧</b>         | いずれかの入力                                                                   |                  | 1.725        |                  | V                  |

| <b>リミッタ・アンプ</b>          | (LMHI出力、LMLO出力)                                                           |                  |              |                  |                    |

| リミッタ出力での                 |                                                                           | 5                |              | 500              | MHz                |

| 使用可能周波数範囲                | - 10 dB <b>点まで</b> R <sub>LOAD</sub> R <sub>LIM</sub> = 50                |                  | 875          |                  | MHz                |

| 100 MHz <b>位相変化</b>      | 入力範囲 - 60 dBm ~ + 10 dBm                                                  |                  | ± 3          |                  | Degrees            |

| リミッタ出力電流                 | 公称400 mV/R <sub>LIM</sub>                                                 | 0                | 1            | 10               | mA                 |

|                          | 温度範囲 - 40 T <sub>A</sub> +85 に対して                                         |                  | - 0.008      |                  | %/                 |

| <b>入力範囲</b> <sup>3</sup> | A                                                                         | - 78             |              | +9               | dBV                |

|                          |                                                                           | - 65             |              | + 22             | dBm                |

| 最大出力電圧                   | LMHI <b>または</b> LMLO <b>での等価</b> dBm、VPS2                                 | 1                | 1.25         | _                | V                  |

| 立上がり/立下がり時間              | R <sub>LOAD</sub> 50 . 40 R <sub>LIM</sub> 400                            |                  | 0.4          |                  | ns                 |

| (10% h 590%)             | COND V CLIWI                                                              |                  |              |                  |                    |

| 対数アンプ                    | (VLOG出力)                                                                  |                  |              |                  |                    |

| ±3dB誤差ダイナミック・レンジ         | ノイズ・フロアから最大入力まで                                                           |                  | 100          |                  | dB                 |

| 移行領域スロープ                 | 「フィス・フロアから取入入力まで<br>5 MHz f 200 MHz                                       | 18               | 20           | 22               | mV/dB              |

|                          |                                                                           | 17               | 20           | 23               |                    |

| ハッターセプト                  | 温度範囲 - 40                                                                 |                  |              |                  | mV/dB              |

| インターセプト                  | 5 MHz f 200 MHz                                                           | - 116            | <b>-</b> 108 | <b>-</b> 100     | dBV                |

| (対数オフセット)                | 等価dBm (50 基準)                                                             | - 103            | <b>-</b> 95  | - 87             | dBm                |

|                          | 温度範囲 - 40 T <sub>A</sub> + 85                                             | - 117            | - 108        | - 99             | dBV                |

|                          | 等価dBm (50 基準)                                                             | - 104            | - 95         | - 86             | dBm                |

| 去绝处也关入11 号11.5           | 温度感度                                                                      |                  | - 0.009      |                  | dB/                |

| 直線性誤差(リップル)              | - 83 dBV( - 70 dBm)~ +7 dBV( +20 dBm)の入力                                  |                  | ± 0.4        |                  | dB                 |

| 出力電圧                     | 入力 = $-91 \text{ dBV}(-78 \text{ dBm})V_s = +5 \text{ V}, +2.7 \text{ V}$ |                  | 0.34         |                  | V                  |

|                          | 入力 = +9 dBV( +22 dBm )V <sub>s</sub> = +5 V                               |                  | 2.34         | 2.75             | V                  |

| <b>国小女女好</b> 5           | 入力 = +9 dBV( +22 dBm )V <sub>S</sub> = +2.75 V                            | 4.5              | 2.10         |                  | V                  |

| 最小負荷抵抗、RL                | <b></b>                                                                   | 40               | 50           |                  |                    |

| 最大シンク電流                  | グランドへ                                                                     | 0.75             | 1.0          | 1.25             | mA                 |

| 出力抵抗                     |                                                                           |                  | 0.3          |                  | <b></b> .          |

| 小信号帯域幅                   |                                                                           |                  | 3.5          |                  | MHz                |

| 1%までの出力設定時間              | 大きいスケールの入力、+3 dBV( +16 dBm )                                              |                  | 46-          |                  |                    |

|                          | R <sub>L</sub> 50 , C <sub>L</sub> 100 pF                                 |                  | 120          | 220              | ns                 |

| 立上がり/立下がり時間              | 大きいスケールの入力、+3 dBV( +16 dBm)                                               |                  |              |                  |                    |

| (10%から90%)               | R <sub>L</sub> 50 , C <sub>L</sub> 100 pF                                 |                  | 67           | 100              | ns                 |

| ₫源インターフェース               |                                                                           |                  |              |                  |                    |

| 電源電圧、V <sub>POS</sub>    |                                                                           | 2.7              | 5            | 6.5              | V                  |

| 静止電流                     | ゼロ信号、LMDRオープン                                                             | 13               | 16           | 20               | mA                 |

| 温度範囲                     | - 40 < T <sub>A</sub> < + 85                                              | 11               | 16           | 23               | mA                 |

| ディスエーブル時電流               | - 40 < T <sub>A</sub> < + 85                                              |                  | 0.01         | 4                | μA                 |

| リミッタに対する追加バイアス           | R <sub>LIM</sub> = 400 (テキスト参照)                                           |                  | 1.4          | 1.6              | mA                 |

| 電源をイネーブルする               | High <b>状態、-</b> 40                                                       | 1.8              |              | $V_{POS}$        | V                  |

| ロジック・レベル                 |                                                                           |                  |              |                  |                    |

| High <b>時の入力電流</b>       | ENBL <b>c</b> 3 V, -40 < T <sub>A</sub> < +85                             |                  | 40           | 60               | μA                 |

| 電源をディスエーブルする             | Low <b>状態、</b> -40 <t<sub>A &lt; +85</t<sub>                              | - 0.5            |              | 1                | V                  |

| モル・ピノーハー フルッシ            |                                                                           |                  |              |                  |                    |

- 2 -REV.A

注 テストなしで保証するパラメータのMinとMaxの規定値は、6シグマ値です。 2 対数アンプは電力ではなく電圧に厳密に応答するため、入力レベルは"dBV"で規定します。0 dBVは1 V rmsの正弦波周波数入力に対応します。50 終端での電力レベル0 dBm(1 mW)は、0.2236 V rmsの入力に対応します。したがって、50 終端の特別なケースでは、dBVとdBmの間の関係は固定オフセット + 13 dBmに対応します。 3 AD8309の非常に大きなゲイン帯域幅積に起因して、LMHIまたはLMLOの出力は、- 78 dBV(50 基準の - 65 dBm)より低いレベルに対して不安定になります。 仕様は予告なく変更されることがあります。

# 絶対最大定格\*

| 電源電圧Vs                                      | + 26<br>+ 20 | dBm<br>dBm  |

|---------------------------------------------|--------------|-------------|

| JA                                          | 150<br>27.6  | /W<br>/W    |

| 動作温度範囲 - 40 保存温度範囲 - 65 端子温度範囲(ハンダ処理60 sec) | ~ +<br>~ +   | - 85<br>150 |

<sup>\*</sup> 上記の絶対最大定格を超えるストレスを加えるとデバイスに永久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

# オーダー・ガイド

| モデル             | 説明                            |

|-----------------|-------------------------------|

| AD8309ARU       | RU-16 <b>チューブ</b>             |

| AD8309ARU-REEL  | RU-16 13 <b>インチ・テープおよびリール</b> |

| AD8309ARU-REEL7 | RU-16 7 <b>インチ・テープおよびリール</b>  |

| AD8309-EVAL     | 評価ボード                         |

## 注意 -

ESD(静電放電)の影響を受けやすいデバイスです。  $4000 \lor$ もの高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることもあります。このAD8309には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電にさらされたデバイスには回復不能な損傷が残ることもあります。 したがって、性能低下や機能喪失を避けるために、適切なESD予防措置をとるようお奨めします。

# ピン機能の説明

| ピン           | 名前   | 機能                         |

|--------------|------|----------------------------|

| 1            | COM2 | RSSI出力用の特別なコモン・ピン          |

| 2            | VPS1 | 最初の5段のアンプ・ステージとメイン・        |

|              |      | パイアス・システムに対する電源ピン          |

| 3, 6, 11, 14 | PADL | ICが実装される台(グランド・レベル)        |

|              |      | に4本とも接続                    |

| 4            | INHI | 信号入力、Highすなわち正極性           |

| 5            | INLO | 信号入力、Lowすなわち負極性            |

| 7            | COM1 | メインのコモン接続                  |

| 8            | ENBL | チップ・イネーブル ; Highのときアクティブ   |

| 9            | LMDR | リミッタ駆動の設定ピン                |

| 10           | FLTR | RSSI <b>帯域幅圧縮ピン</b>        |

| 12           | LMLO | リミッタ出力、Lowすなわち負極性          |

| 13           | LMHI | リミッタ出力、High <b>すなわち正極性</b> |

| 15           | VPS2 | 6段のゲイン・ステージ、リミッタ、RSSI      |

|              |      | 出力ステージ負荷電流に対する電源ピン         |

| 16           | VLOG | 対数(RSSI)出力                 |

# ピン配置

| COM2 1 VPS1 2 PADL 3 INHI 4 INLO 5 PADL 6 COM1 7 ENBL 8 | ●<br>AD8309<br>上面図<br>(実寸ではありません) | 16<br>15<br>14<br>13<br>12<br>11<br>10<br>9 | VLOG<br>VPS2<br>PADL<br>LMHI<br>LMLO<br>PADL<br>FLTR<br>LMDR |

|---------------------------------------------------------|-----------------------------------|---------------------------------------------|--------------------------------------------------------------|

|                                                         |                                   |                                             |                                                              |

REV.A - 3 -

# AD8309 代表的な動作特性

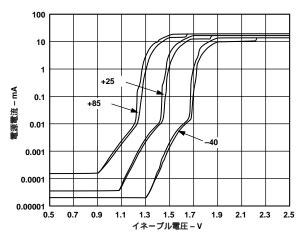

図1.電源電流とイネーブル電圧の関係@

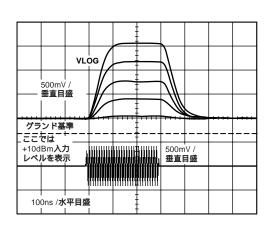

図4 . ゼロから - 63 dBV、- 43 dBV、- 23 dBV、- 3 dBVへの ステップ入力に対するRSSIパルス応答

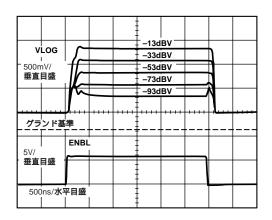

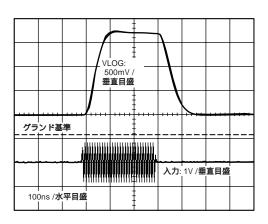

**図**2. - 93 dBV ~ - 13 dBV**の**RF**入力時の電源**On/Off**応答時間**

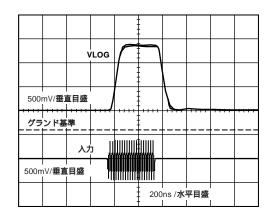

図5. R<sub>L</sub> = 100 、C<sub>L</sub> = 33 pF、100 pF、330 pF (曲線は重複)でのRSSI大信号パルス応答

図3. RSSI大信号パルス応答

C<sub>L</sub>=100 pF、R<sub>L</sub>=50 および75 (曲線は重複)

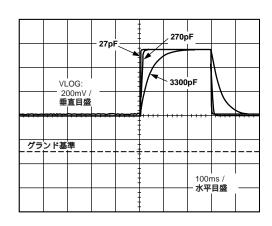

図6.RSSI出力の小信号AC応答

**外付けフィルタ容量:**27 pF、270 pF、3300 pF

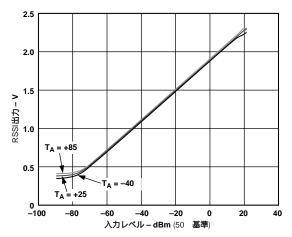

**図**7. RSSI出力と入力レベルとの関係(T<sub>A</sub> = -40 、+25 、 +85 **における**100 MHz正弦波シングル・エンド入力)

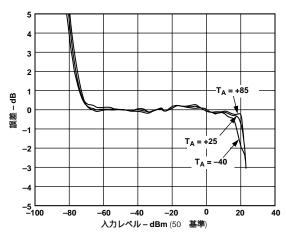

図10. RSSI出力の対数直線性と入力レベルとの関係 (T<sub>A</sub> = -40 、+25 、+85 での100 MHz正弦波入力)

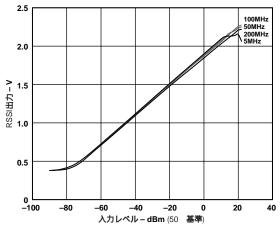

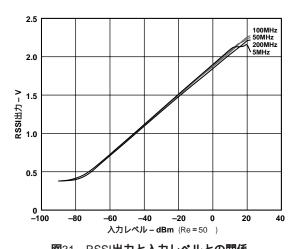

図8. RSSI出力と入力レベルとの関係(T<sub>A</sub> = +25 における 5MHz、50 MHz、100 MHz、200 MHz**の周波数入力**)

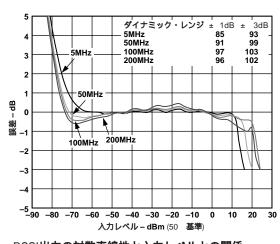

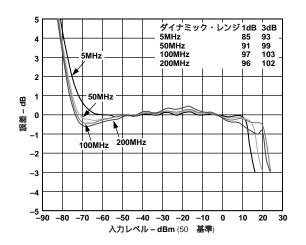

図11 . RSSI出力の対数直線性と入力レベルとの関係 (T<sub>A</sub> = +25 での5 MHz、50 MHz、100 MHz、200 MHzの周波数入力)

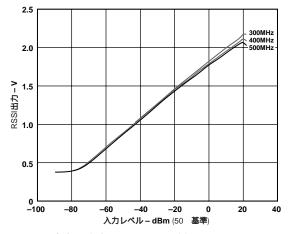

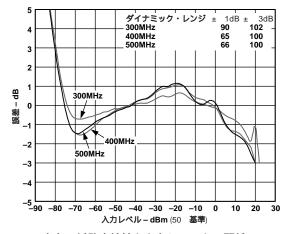

図9. RSSI出力と入力レベルとの関係(T<sub>A</sub> = +25 における 300 MHz、400 MHz、500 MHzの周波数入力)

図12 . RSSI出力の対数直線性と入力レベルとの関係 (T<sub>A</sub> = +25 での300 MHz、400 MHz、500 MHzの周波数入力F)

REV.A - 5 -

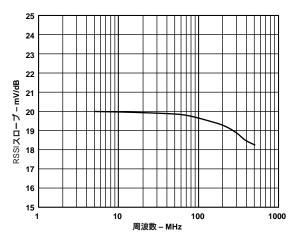

図13. RSSIスロープと周波数の関係 (52.3 と4.7 nHの直列接続による終端)

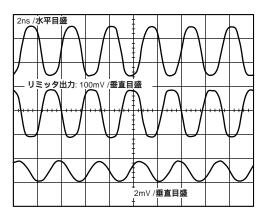

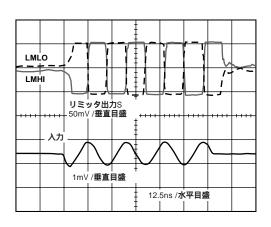

図14. - 60 dBV( - 47 dBm)の正弦波入力に対する300 MHzに おけるリミッタ出力R<sub>LOAD</sub> = 50 、R<sub>LIM</sub> = 100

図15 . 50 MHz**の** - 70 dBV( - 57 dBm ) におけるパルス化正弦 波入力時のLMHI、LMLOでのリミッタ応答(R<sub>LOAD</sub> = 50 、 R<sub>LIM</sub> = 200 )

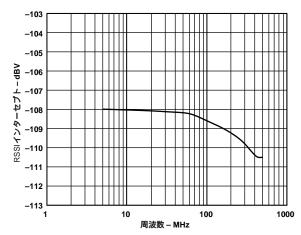

**図**16. RSSI**インターセプトと周波数の関係** (52.3 **と**4.7 nH**の直列接続による終端**)

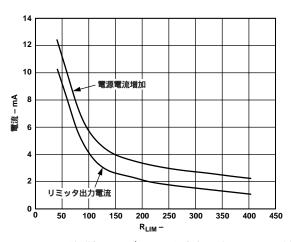

図17.電源電流増加およびリミッタ出力電流とR<sub>LIM</sub>の関係

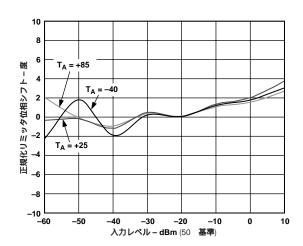

**図**18. 正規化されたリミッタ位相応答と入力レベルの関係 (周波数 = 100 MHz、T<sub>A</sub> = -40 、+25 、+85 )

### 動作原理

AD8309は、2つの主要な機能を組み合わせた高性能受信器用のIF 信号処理ICです。1つ目の機能は、段階的圧縮と組合せた大きな電圧ゲインの提供です。これを使って、広いダイナミック・レンジのIF信号が方形波出力に変換されます(ハード・リミット)。この方形波の周波数と位相から、この入力で変調された情報を、後段の信号処理により復元することができます。このような用途では、入力換算のノイズ・レベルが受信器の検出スレッショルドを決定するので、ノイズ・レベルは非常に低い必要があります。

さらに、振幅位相変換の危険を最小にするため、このアンプの群遅延が本質的に信号レベルに依存しないことがしばしば重要になります。リミットされた出力振幅が温度に対して安定であることも望まれます。AD8309では、この振幅をユーザーが制御することができます。あるいは完全にシャットオフすることもでき、非常に柔軟性があります。

2つ目の機能は、信号入力のデシベル値に比例する復調出力(ベースパンド)を提供することです。この出力は信号強度の表示に使うことができます。グランド・レベルに近い値からグランドより数V高いレベルまで変化するこの出力は受信信号強度表示(RSSI)と呼ばれます。この機能を提供するときは、対数アンプの使用が必要になります。この出力が信号強度の測定に適するためには、スケーリング属性が良く管理されている必要があります。

対数アンプはもともと電圧応答デバイスですが、これらのスケーリング属性としては、mV/dBで規定される対数スロープとアンプ入力での等価電力レベルで規定される"インターセプト"があります(下記の説明を参照)。また、対数則に対する適合性すなわち理想関数に対するRSSIの近似精度も重要です。多くの低品質対数アンプは近似ソリューションのみを提供するため、結果として対数則の適合性とスケーリングで大きな誤差になっています。アナログ・デバイセズ社の全ての対数アンプは、機能全体の精度に影響を与える項目に十分な注意を払ってデザインされています。

AD8309では、これら2つの基本信号処理機能を組み合わせて、段階的圧縮を持つ必要な電圧ゲイン、ハード・リミット機能、入力の対数振幅決定機能(RSSI)を提供しています。この組合せを対数リミッタ・アンプと呼びます。製品動作の概要を良く理解しておくと、これらのアプリケーションに潜む落とし穴を回避することができます。

### 対数アンプの基礎

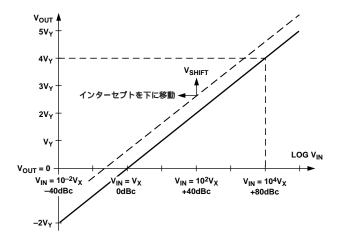

対数アンプの目的は、広いダイナミック・レンジの信号を等価なデシベル値に圧縮することです。したがって、対数アンプは基本的には計測デバイスです。対数表現は、混同やときには矛盾するような状況を発生させることがあります。例えば、対数アンプのRSSI出力に加わえられた電圧オフセットは、入力の後段でゲインが増加したことと等価になります。全変数を電圧で表すと、特定の構造とは無関係に、出力は次のように表されます。

$$V_{OUT} = V_Y \log(V_{IN} / V_X) \tag{1}$$

ここで、 $V_Y$ は"スロープ電圧"です。 $V_{IN}$ は入力電圧で、 $V_X$ は"インターセプト電圧"です。対数の底としては通常10を使います。この底10はデシベルでキャリブレーションするデバイスに適しており、この場合には、 $V_Y$ も"電圧/ディケード"で表されます。式(1)から明らかなように、対数アンプは回路のスケーリングを決定する2つの係数(ここでは $V_X$ と $V_Y$ )を必要とします。対数アンプの絶対

精度は、スケーリング基準の精度より高くなることはありません。 式(1)は、 $V_{IN}$ が反対符号になるAD8309のような復調対数アンプの 動作を表すためには数学的に不完全であることに注意してください。 ただし、基本原理には影響ありません。

図19に、式(1)を満たす理想対数アンプの入力と出力の関係を表します。横軸のスケールは対数であり、非常に広いダイナミック・レンジ(この図では、120 dBすなわち6ディケードの電圧すなわち12ディケードの入力換算電力)を表しています。出力は、固有な値 $V_{IN}$  =  $V_{X}$ でゼロ("対数インターセプト")を通過して、インターセプトより下の入力に対しては負になります。理想的なケースでは、 $V_{IN}$ の全ての値に対する $V_{OUT}$ を表す直線は、両側に無限に延びています。点線で示す直線は、オフセット電圧 $V_{SHIFT}$ を出力に加えると、インターセプト電圧 $V_{X}$ が下がることを表しています。

図19.理想対数アンプ機能

全く同じ変更が、対数アンプの後段で $V_{SHIFT}/V_V$ だけゲイン(または信号レベル)を上げることにより行うことができます。例えば、 $V_Y$  = 400 mV/ディケード(=20 mV/dB、AD8309の場合)の場合に、120 mVのオフセットを出力に加算すると、インターセプトは3/10ディケードすなわち6 dBだけ下に移動します。したがって、出力にオフセットを加えることと、6 dB高い入力レベルを加えることが区別できません。

微分の計算から明らかなように、差分ゲインD $V_{OUT}/DV_{IN}$ が $V_{IN}$ の瞬時値の関数であるという点で、式(1)で示す対数アンプ関数は線形アンプの関数と異なっています。対数の底がeの場合は、次のようにこれを簡単に示すことができます。

$$\frac{V_{OUT}}{V_{IN}} = \frac{V_{Y}}{V_{IN}} \tag{2}$$

すなわち、対数アンプの差分ゲインは入力電圧の瞬時値に反比例します。これは対数の底によらず成り立ちます。"完全な"対数アンプは、古典的な"小信号"(ゼロ振幅)条件では無限のゲインを持つ必要があります。これは、対数アンプを実現する方法によらず、小信号条件(すなわち、ダイナミック・レンジの下限)での正確なHF応答のためには、非常に大きなゲイン帯域幅積が必要であることを示しています。したがって、広帯域の対数アンプでは、多数のカスケード接続されたゲイン・セル(各々は低いゲインで広帯域)を使用する必要があります。AD8309の場合、ゲイン帯域幅(-10 dB)積は52,500 GHzです。

REV.A - 7 -

この高ゲインのため、対数アンプ入力での非常に小さい熱雑音がゼロ入力に対して有限の出力を発生させ、そのために応答直線が小入力での理想値(図19)から固定の基線に向かって乖離していきます。デザインに応じて、インターセプトの上または下に反れていきます。このインターセプトとして指定された値は、不変な値として外挿されたものであることに注意してください。すなわち、単電源で動作する場合は、RSSI出力電圧値は正確にゼロになることはあません。

# 電圧(dBV)と電力(dBm)の応答

式(1)は基本的には正しいですが、RF入力を復調するAD8309のような対数アンプのRSSIキャリプレーション属性を指定するためには、より簡単な式が必要です。通常測定するのは次の入力電力です。

$$V_{OUT} = V_{SLOPE}(P_{IN} - P_0)$$

(3)

ここで、 $V_{OUT}$ はフィルタを通した復調済みRSSI出力であり、VスロープはV/dBで表す対数スロープで、 $P_{IN}$ は何処かの電力レベルを基準にしたデシベル値で表す入力電力、 $P_{0}$ は同じ電力レベルを基準にしたデシベル値で表す対数インターセプトです。

RFシステムで広く一般に採用されている表現方法は、50 での1 mWを基準として電力をデシベルで指定してdBmと表す方法です (ただし、量[ $P_{IN}$  -  $P_{0}$ ]は単純にdBで表します)。入力をデシベルで表すことにより変換が暗黙の内に行われているため、対数関数はこの式から姿を消しています。

対数アンプ入力レベルを電力で指定することは、単に慣行に過ぎません。対数アンプは電力に応答するのではなく(暗黙には"力は入力で吸収"された電力)入力電圧に応答します。この接続では、AD8309の入力インピーダンスはその50 より遙かに大きな値になっています。このために、入力でインピーダンス変換を行って感度を13 dB上げることが可能になっています。

1 Vrmsの正弦波振幅を基準とするデシベル値dBVの使用はさらに正確です。ただし、波形は対数アンプ応答の中にも含まれ、複雑な入力に対しては(例えばCDMA信号)、対数アンプ応答に含まれている波形は正確にはrms値に一致しないため、この表現法も一般的な表現法として必要な一意性を持つことはできません。多くのユーザーが電力でRF信号を指定しているため(さらに正確にばdBm/50

)、AD8309の性能を表すときは、dBVとdBmの両方を使い、50 環境の特別なケースに対して等価なdBmレベルを表示します。

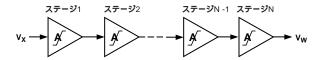

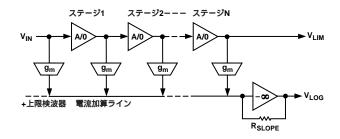

### 段階的な圧縮

高速で広いダイナミック・レンジの対数アンプでは、複数の非線形アンプ・セルのカスケード接続(図20)を使って一連の連続的セグメントから対数関数をつくる一種の折れ線近似法を使っています。この基本トポロジは、非常に大きなゲイン帯域幅積を与えます。例えば、AD8309では、メイン信号パスに各々が12.04 dB(×4)の小信号ゲインと850 MHzの - 3 dB帯域幅を持つ6個のセルを使い、その後にゲイン18 dB(typ)の最終段リミッタ・ステージを配置しています。合計ゲインは100,000(100 dB)で、リミッタ出力の - 10 dB点までの帯域幅は525 MHzになります。この非常に大きいゲイン帯域幅積(52,500 GHz)は、小信号状態と高い周波数での正確な動作にとって基本的な必要条件です。式(2)から、差分ゲインはVINの増加と共に急速に減少することが分かります。AD8309は、- 91 dBVすなわち28 μ Vrms(= -78 dBm/50 )のノイズ・フロアからブレークダウン限界値のピーク入力4 V(差動入力INHIとINLOで平衡駆動が必用)までの大部分の範囲で対数応答を示しています。

図20. 非線形ゲイン・セルのカスケード接続

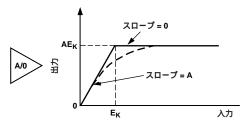

#### 対数アンプの理論

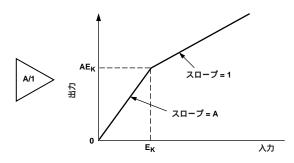

理論を展開するために、先ず、AD8309で使用した方法と異なる方法を検討します。ただし、この方法は簡単に説明でき、数学的な解析が簡単にできます。このアプローチは非線形アンプ・ユニット(A/1セルと呼びます)をベースにしており、図21に示す伝達特性を持っています。ローカル入力とこれらのセル出力を表すときは小文字の変数を使い、大文字は外部信号を表します。

小信号ゲイン  $V_{OUT}/V_{IN}$ をAで表し、このAは折れ線電圧 $E_K$ までの入力に対して一定に維持され、 $E_K$ の上では差分ゲインは単位ゲインに減少します。 関数は対称です。 すなわち、 $-E_K$ より低 $IV_{IN}$ の瞬時値に対しても同じゲインの減少があります。 大信号ゲインは、 $-E_K < V_{IN} < +E_K$ の範囲内の入力に対するAの値になりますが、非常に大きな入力に対しては単位ゲインに向かって漸近的に減少します。

この簡単な関数に基づく対数アンプでは、スロープ電圧とインターセプト電圧は1つの基準電圧E<sub>K</sub>を基準とする必要があります。したがって、この基礎的な解析では、対数アンプのキャリブレーション精度は、この電圧のみに依存します。実用的には、V<sub>Y</sub>とV<sub>X</sub>を決めるために使う基本基準電圧を分離することができます。AD8309では、V<sub>Y</sub>はオンチップ・バンドギャプ基準電圧を、V<sub>X</sub>は熱電圧kT/qから導出して精密な方法で温度補償した値をそれぞれ使用しています。

カスケード接続内のNセルの入力を $V_{\rm IN}$ で表し、最終段出力を $V_{\rm OUT}$ で表します。小信号に対しては、合計ゲインは簡単に $A^{\rm N}$ で得られます。 $A=5(14~{\rm dB})$ の6ステージのシステムに対しては、合計ゲイン15,625(84~{\rm dB})が得られます。対数関数を構成する際に非常に大きな小信号ACゲインが重要であることは既に説明しましたが、これは対数アンプ・デザインにおける付随的な関心を引くパラメータに過ぎません。より大事なのは、その非線形動作です。

図21.A/1アンプの機能

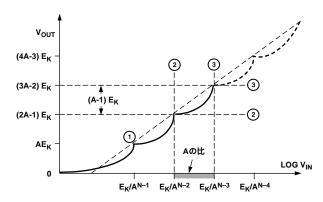

このため、ゲインの考察ではなく、式(1)の $V_{IN}$ に対応する簡単なDC入力に対する応答でのカスケード接続の非線形動作の方を解析します。非常に小さI入力に対して、最初のセル出力は $V_1 = AV_{IN}$ 、2番目のセル出力は $V_2 = A^2 V_{IN}$ 、以下同様に $V_N = A^N V_{IN}$ まで続きます。 $V_{IN}$ のある値で、N番目のセルの入力 $V_{N-1}$ が折れ線電圧 $E_K$ に一致します。このため、 $V_{OUT} = AE_K$ となり、N-1個のゲインAのセルがこの

ノードの前に存在するため、 $V_{IN} = E_K / A^{N-1}$ として計算できます。この固有の点は図22の で示される直線と対数の移行点に対応します。

この入力より下では、ゲイン・セルのカスケード接続は、簡単な線形アンプとして動作し、これより上のVIN値に対しては、対数を近似する一連のセグメントの領域に入ります。

この解析を続けると、次の移行点は(N-1)番目のステージの入力が $E_K$ に一致するとき(すなわち $V_{|N}=E_K/A^{N-2}$ のとき)に発生することが分かります。そして、このステージの出力は $AE_K$ に一致します。図21に示す機能から、最終ステージの出力が(2A-1) $E_K$ (図22でと表示)に等しくなることは容易に示すことができます。したがって、 $E_K/A^{N-1}$ から $E_K/A^{N-2}$ への $V_{|N}$ 変化(すなわちA倍の変化)に対して出力は(A-1) $E_K$ だけ変化しています。

図22.最初の3個の移行点

次の重要な点(図22の )では、入力はA倍になり、 $V_{OUT}$ は(3A-2) $E_K$ に増幅されています。すなわち、もう1回(A-1) $E_K$ 倍されています。更に解析を進めると、最初のセルに対する入力が折れ線電  $EV_{OUT}$ に到達する点の直ぐ上は、 $V_{IN}$ における比の変化Aに対して(A-1) $E_K$ だけ変化します。ディケードの分数で表わすと、これは簡単に $Ioq_{10}(A)$ と表されます。

例えば、A = 5の場合、折れ線出力関数での移行は、0.7ディケード ( $\log_{10}(A)$ )すなわち14 dB  $\div$  20 dB )の規則的な間隔で発生します。この考察により、直ちに"ディケード当たりのボルト数"のスケーリング・パラメータが得られます。底10の対数を使うと、これはまた"スケーリング電圧" $V_v$ でもあります。

$$V_{Y} = \frac{\text{Linear Change in } V_{OUT}}{\text{Decades Change in } V_{IN}} = \frac{\text{(A-1)}E_{K}}{\log_{10}(A)}$$

(4)

$V_{\nu}$ の決定には、セルのゲインAと折れ線電圧 $E_{\kappa}$ の2つだけのデザイン・パラメータしか関係していないことに注意してください。関数全体のスロープの設定には、ステージ数Nは重要でありません。 A = 5で $E_{\kappa}$  = 100 mVの場合、スロープは好ましくない値の572.3 mV/ディケード(28.6 mV/dB)になります。良くデザインされた実用的な対数アンプは、もっと合理的なスケーリング・パラメータを与えます。

インターセプト電圧は、出力関数(図22参照)上の任意の2対の移行点に対して、方程式(4)を解くことにより求められます。結果は次のようになります。

$$V_X = \frac{E_K}{\Delta(N+1/[A-1])} \tag{5}$$

この例に対して、N = 6を使うと、 $V_x$ は $4.28 \mu V$ になります。このように、この解析ではまだ簡単なDC電圧のままです。

図23 . A/0アンプの機能(理想およびtanh)

このパラメータの解釈には注意がいります。このインターセプト電圧は、前に出力がゼロを通過するときの入力電圧として定義しました(図19参照)。明らかに、ノイズとオフセットがない場合、図20に示すアンプのチェインの出力は、VIN=0のときにのみゼロになることができます。この例外は、カスケード接続アンプの有限ゲインに起因しています。この結果"直線-対数移行"点(図22のの点)より下で対数近似の維持ができなくなります。詳しく解析すると、式(5)で与えられる電圧は実際のインターセプトではなく外挿された点を表していることが分かります。

# 復調対数アンプ

A/1セルのカスケード接続に基づく対数アンプは、入力信号を復調することがないため、ベースパンド(パルス)アプリケーションで有用です。AD8309のような復調(検波)対数リミッタ・アンプでは、A/0セルと呼ぶ異なったタイプのアンプ・ステージを使います。その機能は、図23に実線で表わすように折れ線電圧Exより上のゲインがゼロになる点でA/1セルの機能と異なっています。これはリミッタ機能とも呼ばれており、FMモードとPMモードで信号を再生する際に、このようなセルのN個のチェインが単独でハード・リミット出力を発生するために使用されます。

AD640、AD606、AD608、AD8307、AD8309、AD8313、および他のアナログ・デバイセズ社の対数IFアンプを使用している通信用製品は、全てこの技術を使用しています。 $V_{IN} = E_K / A^{N-1}$ のリミット・スレッショルドを超える全ての入力に対して、最終ステージの出力は変化しないため、最終ステージの出力は対数出力を提供できないことは明かです。その代わり、全ステージの出力を加算することにより、対数出力が発生されます。このタイプの対数アンプについての完全な解析は、前のケースに比べて少し複雑になります。

実用上、インターセプト電圧VXは式(5)で与えられたインター セプト電圧に等しいことを示すことができます。一方、スロープ電 圧はつぎのようになります。

$$V_{\gamma} = \frac{AE_{\kappa}}{\log_{10}(A)} \tag{6}$$

注意深くデザインすると、多くの他のパラメータ変化に対する感受性および温度と電源電圧の影響を、無視できるように小さくすることができます。

図24. 複数のA/0ステージと加算用のトランスジューサ(gm) セルを使用する基本的な対数アンプ構成

各ゲイン・セルの出力は、セルの差動出力電圧を一対の差動電流に変換する対応する相互コンダクタンス(gm)セルを持っています。これらは全てのgm(検波器)ステージを単純に並列接続することにより加算されます。次に合計電流は対数出力のスロープを決定するトランジスタ・ステージにより電圧に戻されます。この一般的な構成を簡単化したシングル・エンド形式で図24に示します。受動減衰器から駆動されるその他の検波器は、ダイナミック・レンジの上限を拡張するために追加することができます。

ここでは、スロープ電圧を絶対温度に比例する折れ線電圧EK = 2kT/qから切り離すことができます。検波ステージはバンドギャプ基準電圧から発生できる電流でバイアスされます(図には示してありません)。そのため温度に対して安定しています。これがAD8309で使用されているアーキテクチャで、対数スロープの振幅と温度による変化を完全に制御しています。

対数リミッタ・アンプで要求される復調応答を得るためにさらに必用なステップは、交流入力を疑似DCベースパンド出力に変換することです。これは、加算用途に使用されているgmセルを変更して、整流機能を実現することにより行われます。段階的圧縮技術をベースとする前述の対数アンプは、ポスト検波フィルタを複雑にする半波整流を使っていました。AD640は最初に全波整流を使ったモノリシック対数アンプ製品であり、この当社独自の経験は後続の全アナログ・デバイセズ製品のこのタイプに使用されています。

これらの検波器を線形gmセルとしてモデル化できますが、入力に加えられる電圧の符号には無関係な出力電流を発生します。すなわち、これらは絶対値をとる機能を内蔵しています。後段のA/0ステージの出力は中程度の入力レベルにおいても振幅が対称な方形波を正確に近似するため、各検波器の電流出力は入力の各周期の間殆ど一定です。チェイン内である程度前にある検波器ステージは、入力周波数の2倍で非常に短い"抜け"を持つ波形を発生します。対数アンプの入力に近い検波器のみが正弦波に近い低いレベル波形を発生します。これら全ての(電流モード)出力が加算されると、結果として得られる信号はフィルタ済み波形を持ち、出力には小さい残留リップルが現れます。

インターセプトのキャリプレーション

アナログ・デバイセズ社のモノリシック対数アンプは、インターセプト電圧Vx(すなわち特定のインピーダンス・レベルで駆動したときの復調対数アンプに対する等価正弦波電力)を指定する正確な方法を採用しています。図 24に示す回路図を使うと、インターセプトレベルの値は簡単な式を使った予測値より大幅に乖離します。それでも、固有のインターセプト電圧は絶対温度に比例するExに比例します。

オフセットを出力に加算すると、インターセプトの変化と区別できない影響を発生することを思い出すと、E<sub>K</sub>の温度変化から生ずる VXの左右の移動は、必用な温度変化を持つ復調出力にオフセットを 加えることにより相殺できることが明らかになります。

インターセプトを指定するオフセットの精密な温度のシェイピングにより、安定なスケーリング・パラメータを持つ対数アンプが得られ、それを例えばキャリプレーション済みの受信信号強度表示器(RSSI)のような、真の計測デバイスにすることができます。このアプリケーションでは、正弦波(CW)の入力波形に対する出力値に関心がある場合があります。入力レベルは等価な電力dBmで表されますが、"電力"を測定するインピーダンス・レベルを知っておくことは重要です。インピーダンス50 では、0dBm(1mW)は正弦波振幅316.2 mV(223.6 mVrms)に対応します。

AD8309の場合は、52.3 の抵抗を並列接続して入力インピーダンスを50 に下げた場合は、インターセプトはdBmで規定し、-95 dBmになります。ただし、応答は終端抵抗内の電力ではなく、実際には入力の電圧に応答し、dBVで規定すべきです。50 抵抗両端の-95 dBm正弦波入力は、振幅5.6 μ Vすなわち - 108 dBVに対応します。ここで、0 dBVは1 Vrmsの正弦波形として規定され、2.8 Vp-pに対応します。対数アンプのインターセプトは波形の関数であることに注意してください。例えば、方形波入力では、同じ振幅の正弦波より6 dB高くなり、ガウス・ノイズ入力は同じrms値の正弦波より0.5 dB高くなります。さらに、等しい振幅を持つ2つの正弦波電圧の和により駆動される対数アンプの出力は、1つの正弦波駆動の場合の応答より、デバイスが真に入力電力に応答する場合に予想される3 dBではなく、2.1 dBだけ高くなります。これらは、全ての復調対数アンプが示す特性です。

### ダイナミック・レンジ

ダイナミック・レンジの下限は、アンプ・チェインの入力で測定される熱的なノイズ・フロアに大きく依存して決定されます。AD8309の場合、短絡回路入力換算ノイズ・スペクトル密度は1.1 nV/√Hzで、25 (50 終端)のネット・ソース・インピーダンスで駆動した場合は1.275 nV/√Hzです。これは、500 MHz帯域幅でのノイズ電力 - 78 dBmに対応します。ダイナミック・レンジの上限は、タップ付き減衰器から駆動される上限検波器の追加により上に拡張することができます。これらの小さな信号は、追加される全波検波器に入力されます。これらの全波検波器の出力はメイン検波器の出力と加算されます。

注意深くデザインすると、ダイナミック・レンジの拡張は全周波数範囲で"繋ぎ目"なく行うことができます。AD8309の場合、さらに48 dB追加されます。4.5 V以上の電源を使うと、4 Vの入力振幅が許容でき、これは50 での電力レベル+22 dBmに対応します(これより大きい入力電圧では損傷を受けます)。

したがって、最大許容入力のノイズ・フロアに対する比として定義されるAD8309の合計ダイナミック・レンジは100 dBになります。この範囲の大部分で良い精度が得られます。

## 入力の整合

モノリシック対数アンプは、50 よりかなり高い公称入力インピーダンスを持っています。AD8309の場合、300 MHzまでの周波数に対して1 k と2.5 pFの並列接続でモデル化することができます。このため、簡単な入力整合ネットワークの使用で、低インピーダンス・ソースから駆動したとき、入力を駆動する電圧を大きくすることにより、基本感度を大幅に上げることができます。50:1000変成器の場合、電圧ゲインは13 dBで、ダイナミック・レンジ全体がこの値だけ下に移動します。すなわち、インターセプトが - 121 dBV(初段50 入力で - 108 dBm)にシフトします。この方法で有用な電圧ゲインが得られますが、雑音指数は最適電力整合で最小になる訳ではないことに注意してください。

#### オフセットの制御

モノリシック対数アンプでは、ステージ間の直接結合が現実的理由から常に利用されます。チェイン内の前のステージでのDCオフセット電圧は"真の"信号から区別することはできません。400 μ V程に高くなると、識別可能な最小AC信号(40 μ V)より20 dB高くなり、この値だけダイナミック・レンジを狭くします。この問題は、最終ステージから先頭ステージへのグローバル帰還パスを使用することにより解決されます。信号の高周波成分は除去する必要があります。AD8309の場合、これはオンチップ・ローパス・フィルタを使って行われ、HF帰還の十分な抑圧を提供して、5 MHzまでの正確な動作を可能にしています。大きなDCオフセットを持つ特定のデバイスはダイナミック・レンジの下限領域で縮小を示しますが、低周波数での有用な動作は維持されています。

### 製品概要

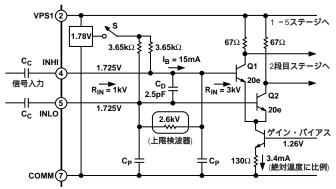

AD8309は、正確なスケーリングに薄膜抵抗技術を使う、電気的に 絶縁された相補型バイポーラ・プロセスにより製造されています。 このプロセスは絶えず改良が続けられる15年以上の実績に基づいて います。AD8309(図25)のメイン・パスは、各々が12.04 dB(×4) のゲインと850 MHzの小信号 - 3 dB帯域幅を持つ6段のメイン・ア ンプ/リミッタ・ステージのチェインで構成されています。INHIと INLC(ピン4とピン5)での入力インターフェースは差動になってい ます。したがって、シングル・エンド入力または平衡入力から駆動 することができ、後段に行くほどダイナミック・レンジの最上端を必 用とします。そこでは、差動駆動の振幅が4 Vにもなります。

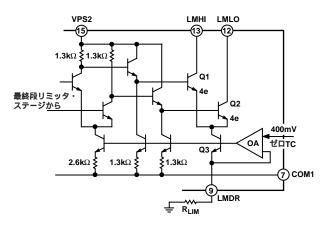

最初の6ステージは対数RSSI出力の発生にも使用され、その後段にはプログラマブルな出力、プログラマブルなゲイン、最終リミッタ・セクションが続きます。LMHIとLMLO(ピン12とピン13)のオープン・コレクタ出力も差動です。等しい値の負荷とパイアス設定抵抗およびピン間出力を使用した場合、この出力ステージはゲイン18 dBを与えます。合計電圧ゲインは100 dBになります。R<sub>LIM</sub> = R<sub>LOAD</sub> = 200 を使用した場合、リミッタ内の消費電流の増加は約2.8 mAで、その内の2 mAが負荷に流れます。この比はR<sub>LIM</sub>に依存し(例えば、20 の場合、効率は90%になります)LMDRピンにおける電圧は400 mV以上になりますが、合計負荷電流は正確に(400 mV)/R<sub>LIM</sub>になります。

100 mV以上の振幅を持つ正弦波入力で駆動され、かつR<sub>LOAD</sub> = 50 の場合、出力におけるハード・リミットされた電圧(方形波)の立上がり時間と立下がり時間は0.4 ns(typ)です。 - 83 dBV( = 振幅100 mV = 50 で - 70 dBm)から3 dBV( = 1 V = +10 dBm)の入力範囲での時間遅延の変化("位相スキュー")は、±83 ps(100 MHzで±3度)です。

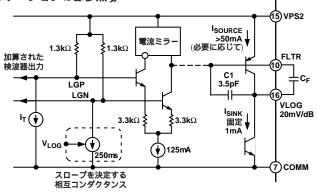

図25.AD8309の主要機能

6個のメインセルとトランスコンダクタンス(gm)形式を持つそれらに対応する全波検波器が、ダイナミック・レンジの下の部分を処理します。これらのセルに対するバイアスは2つの基準電圧から供給されます。それらの内の1つはゲインを決定し、他方は対数スロープを決定するバンド・ギャップ・セルで、電源と温度の変化に対して安定化します。特別なDCオフセット検出セル(図25には示してありません)がこのメインセクションの最終段に配置され、入力における残留オフセットをゼロにするために使用されており、ノイズ・フロアに到達する小さい信号に対しても正確な応答を保証しています。初段のアンプ・ステージは、短絡回路電圧ノイズ・スペクトル密度1.07 nV/√Hzを提供しています。

最終段検波器ステージには、対数インターセプトの温度安定化を行うための調整部が含まれています。この調整部は、出力電圧全範囲を最適に使用できるように正確に対数インターセプトを指定します。さらに、4個の"トップエンド"検波器が、受動減衰器に沿って12.04 dBタップで配置されており、タイナミック・レンジの上の部分を処理します。10個の全ての検波器ステージの差動電流・モード出力は同じ重みで加算されて、出力ステージによりシングル・サイド電圧に変換され、VLOG(ピン16)に公称値20 mV/dB(=400 mV/ディケード)にスケールされて対数(すなわちRSSI)出力が得られます。下部領域と上部領域の間の接合はシームレスで、対数則適合度は-83 dBV~+7 dBV(-70 dBm~+10 dBm)の範囲で±0.4 dBです。

コーナ周波数3.5 MHzの2極ローパス・フィルタとして動作する RSSI出力ステージのフル・スケール立上がり時間は、約200 nsです。 FLTR(ピン10)とVLOGの間に接続されたキャパシタを使って、コーナ周波数(下記参照)を下げることができます。出力の最小レベルは約0.34 V(-78 dBmのノイズ電力すなわち公称インターセプト-95 dBmの17 dB上に対応)になります。これは依然高いベースライン・レベルであり、非常に小さい入力であってもパルス応答が損なわれないこと保証しています。

最大RSSI出力は電源電圧と負荷に依存します。電源電圧が4.5 V 以上で負荷抵抗が50 以上で、差動入力が9 dBV(平衡駆動使用時 4 V正弦波振幅)の場合、出力2.34 V(=20 mV/dB×(12+105)dB) が保証されます。3 V電源使用の場合でも、最大差動入力は-3 dBV (1 V正弦波振幅)と高く、対応するRSSI出力2.1 V(=20 mV/dB× (0+105)dB)も保証されます。

ハード・リミット信号に対してはフルプログラマブルな出力インターフェースが用意されており、差動電流モード出力から最適出力電流が取り出せるように設定できます。振幅は、LMDR(ピン9)とグランドの間に接続された抵抗R<sub>LIM</sub>により決定されます。この抵抗R<sub>LIM</sub>の両端には公称バイアス電圧約400 mVが発生します。R<sub>LIM</sub> = 200 の場合、このDCバイアス電流は2 mAになります(合計電源電流はこれより大きくなります)。この電流は信号により交互に切り替えられて出力ピンLMHIとLMLOに流されます。

これらの電流は、負荷抵抗の接続により電圧に変換されます。通 常、負荷抵抗は500 MHzでの数十 から低周波数アプリケーション での2 k までの範囲になります。抵抗の代わりに、共振負荷を使 用して、帯域外ノイズを最小に抑えて基本信号と変調側波帯を取り 出すこともできます。この出力で変成器またはインピーダンス整合 ネットワークを使うこともできます。出力トランジスタが飽和する 前の電源電圧からのピーク電圧振幅の低下は1.2 ∨です(このイン ターフェースの使用についてはアプリケーションの節にも記載して あります)。RSSI出力に負荷を接続していない場合の、リミッタ出 カステージを除く全セクションに対する電源電流は、T<sub>A</sub> = 27 で公 称16 mAであり、実質的に電源電圧に依存しません。電源電流は、 絶対温度(PTAT)に正比例して変化します。RSSI負荷電流は、 VLOGでの電圧を負荷抵抗で除算した値になります(例えば、1k 負荷の場合は最大2.4 mA) リミッタ電源電流は、RIIMを流れる電流 **の**1.1**倍になります。**AD8309は、ENBL (ピン8)のCMOS互換レベ ルによりイネーブル/ディスエーブルすることができます。

以下の簡単化されたインターフェース図で、大文字'R'で示す部品は、非常に小さい抵抗温度係数と大信号状態で優れた直線性を持つ薄膜抵抗を表します。これらの絶対値(typ)は±20%以内です。大文字"C"で示すキャパシタは偏差(typ)±15%で、温度感度または電圧感度がゼロです。大部分のインターフェースには、能動デバイスまたはESD保護から発生する小さい接合容量が追加されます。これらは不正確で不安定です。これらの各インターフェース図で使用している部品番号は、その図内でのみ有効です。

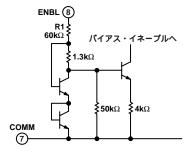

# イネーブル・インターフェース

図26にチップ・イネーブル・インターフェースを示します。R1 を流れる電流がパンドギャップ基準電圧とバイアス・ジェネレータのターンオン状態とターンオフ状態を制御し、ピン8が5  $\lor$  に接続されたとき、最大100  $\lor$  Aになります。開放または1  $\lor$  以下の電圧に接続された場合に、AD8309はディスエーブルされます。1  $\lor$  Aより遙かに小さいスリープ電流(リーク電流のみ)が流れている場合に、または電源または2  $\lor$  以上の電圧に接続されている場合に、AD8309はイネーブルされます。内部パイアス回路はOFFまたはONに約300 nsを要します。電源電流が10  $\lor$  A以下に低下するまでの遅延は約6  $\lor$  Sです。

図26.イネーブル・インターフェース

### 入力インターフェース

図27に、信号入力インターフェースの主要部を示します。グランドに対する寄生容量はCpで示してあります。主にQ1とQ2の拡散容量から生ずる差動入力容量はCpで示してあります。多くのアプリケーションで、両入力ピンはAC結合されます。イネーブルがアサートされると、スイッチSが閉じます。ディスエーブルされると、入力はフローティング状態になり、バイアス電流Ipがシャットオフされ、結合キャパシタはチャージされたままです。対数アンプが長時間ディスエーブルされると、小さいリーク電流によりこれらのキャパシタがディスチャージされます。これらの整合が不十分な場合は、パワーアップ時の充電電流は、過渡入力電圧を発生し、信号より小さくなるまで、ダイナミック・レンジの下部下方部をプロックします。

大部分のアプリケーションでは入力信号はシングル・エンドであり、ピン4またはピン5に入力されます。この際他のピンはグランドにAC結合されます。このような場合の、処理可能な最大入力信号は、3 V電源動作では - 3 dBV (正弦波振幅1 V)になります。4.5 V以上の電源を使用すると、+3 dBV入力も処理できます。平衡駆動を使用すると、電源電圧が2.7 Vまで下がっても+3 dBVレベルを処理することができます。4.5 V以上の電源電圧を使用すると、+9 dBVを処理することができます。10 MHz ~ 200 MHzの周波数範囲に対しては、整合ネットワーク(下記参照)を使うと、これらの高駆動レベルを容易に処理することができます。入力にインダクタを持つこのようなネットワークを使うと、過渡入力を除去することができます。

図27.信号入力インターフェース

### リミッタ出力インターフェース

図28に簡単化したリミッタ出力ステージを示します。このステージに対するバイアスは、公称400 mVの温度に対して安定な基準電圧から供給されます。この基準電圧はピン9(LMDRのリミッタ駆動)に接続された外部抵抗R<sub>LIM</sub>を通して特別なオペアンプ・バッファ・ステージにより制御されます。パイアス方式では、この電圧を少し持ち上げて、電流ソースQ3および出力トランジスタQ1とQ2の有限な電流ゲインを補償しています。最大電流10 mAが許容できます(R<sub>LIM</sub> = 40 )。特別なアプリケーションでは、バイアス電流を変調することが要求される場合があります。この例はアプリケーションの節に記載してあります。パイアス電流が温度に対して安定でも、このステージのACゲインは温度により変化することに注意してください(120 の範囲で - 6 dB変化します)。

電源と温度に対して安定な一対の相補電流が、差動出力LMHIとLMLO(ピン12とピン13)で発生されます。負荷抵抗50 のとき、この相補電流方形波は立上がり/立下がり時間が0.4 ns(typ)になります。これらの出力ピンでの電圧は、VPS2(ピン15)に入力される電源電圧より1.2 V低い電圧まで振れることができます。

このアンプのゲイン帯域幅積は非常に大きいため、リミッタ出力を使用する際には十分な注意が必要です。所要最小限のバイアス電流と電圧振幅を使用する必要があります。これらの出力は差動モードで最適に使用されます。磁束結合変成器すなわち出力整合ネットワーク(タンク回路)を選択して、これらの電圧をシングル・エンド信号に変換します。出力ピンを1つしか使わない場合でも、等しい負荷抵抗の使用を推奨します。また、これらは常にPCボード上の良くデカップリングされた同じノードに戻す必要があります。RSSI出力だけを発生するためにAD8309を使用する場合は、RLIMを削除し、LMHIとLMLOをVPS2に接続することにより、リミッタを完全にディスエーブルしておく必要があります。

図28.リミッタ出力インターフェース

# RSSI出力インターフェース

10個の検波器出力は信号入力レベルに依存する平均値と入力周波数の2倍の変動を持つ差動電流です。これらの電流は、図29に示す内部ノードLGPとLGNで加算されます。ゼロ入力に対するRSSI出力電圧を持ち上げてインターセプトを - 108 dBVに維持するためと温度補償のために、LGPにはさらに電流ITCも加算されて、安定なインターセプトが得られます。ゼロ信号状態に対しては、全ての検波器出力電流が等しくなります。両極性を持つ有限の入力に対しては、出力インターフェースによりそれらの差が、出力VLOC(ピン16)で公称20 mV/dB(400 mV/ディケード)にスケールされたシングル・エンド電圧に変換されます。このスケーリングは、厳密に制御されたトランスコンダクタンスを持つ個別の帰還ステージにより制御されます。対数スロープとインターセプトには小さい不確定性が残っています(仕様参照)、インターセプトは調整できます(アプリケーションの節参照)。

図29.簡単化されたRSSI出力インターフェース

RSSI出力帯域幅 $f_L$ は公称3.5 MHzです。これは補償キャパシタC1により制御されます。この補償キャパシタは外部キャパシタ $C_F$ をFLTR(ピン10)とVLOG(ピン16)の間に接続して増やすことができます。外付け33 pFにより、 $f_L$ を350 kHzに減少させることができます。360 pFを接続すると35 kHzに減少されます。各ケースとも14極の応答を持ちます。一般に、次の関係があります。

$$C_F = \frac{12.7 \times 10^{-10}}{f_{LP}} - 3.5 \, pF; \, f_{LP} = \frac{12.7 \times 10^{-6}}{C_F + 3.5 \, pF}$$

(7)

負荷抵抗50 以上を使用すると、任意の温度で、4.5 Vの電源に対してピーク出力電圧は最小2.4 Vになり、3 V電源に対しては2.1 Vになります。これらは最大許容入力レベルを満たします。出力抵抗の増加は低周波数で約0.3 で、150 kHzで1 に、非常に高い周波数で18 に、それぞれ増加します。出力は負荷容量に対して無条件に安定していますが、ピーク・ソース電流が100 mAを超え、かつ急速に容量が大きく変化しても、内部で供給されるシンク電流は1 mAに留まることに注意してください。このため、2 Vレベルからの立下がり時間は1 nF負荷に対して2 μ sと長くなります。これは、グランドに接続された負荷抵抗を追加することにより短くすることができます。

## AD8309**の使用方法**

AD8309は、1 MHz~1 GHzで非常に高いゲインを示します。この 周波数範囲でのメインパスのゲインは65 dB以上を維持しています。 したがって、入力端子に入力される非常に広い周波数範囲に含まれる全ての信号に対して、AD8309は感度を持ちます。 これは"必用な"信号を区別することを困難とし、ノイズ・フロアを持ち上げる効果を持っている(すなわち、使用可能なダイナミック・レンジを低下させます)ことに注意する必要があります。 したがって、注目する信号が例えばIF=200 MHzの場合、60 Hzの八ム、貧弱なグランドによる混入、同じPCボード上のデジタル・ロジックからのスプリアス、強力なEMIソースなどは、ダイナミック・レンジの下限でこの信号より容易に大きくなります。

このような不要な信号に対する保護のために注意深いシールドは必須であり、リミッタ出力から入力へのHF帰還から生ずる不安定の可能性を最小限に抑える必要があります。これを念頭に、可能な最小リミッタ・ゲインを使用する必要があります。対数アンプ(RSSI)の機能だけが必用な場合は、R<sub>LIM</sub>を削除し、LMHIとLMLOをVPS2に直接接続することにより、リミッタを完全にディスエーブルしておく必要があります。

良いグランド・プレーンを使用して、コモン・ピン接続、VPS1と VPS2で使用されるデカップリング・キャパシタ、出力でのグランドに対して、低いインピーダンスを提供する必要があります。全てのグランド・プレーンは同電位であると考えることは推奨できません。また信号入力をグランド・プレーンに直接AC結合しないで、それらを分離して、ソースに対応した"低電位"に戻してやる必要があります。この方法では、入力コネクタの"低電位"側をグランド・プレーンに接続した小さい抵抗を使って絶縁することが必要になります。COM2は、RSSI出力の専用グランド・ピンであることに注意してください。

2本の電源ピンの電圧が大きく異なることは許されません。許容範囲は500 mVです。VPS1をVPS2より少し負側にすることが望まれます。電源が2.7 Vより高い場合は、デカップリング抵抗R1とR2を大きくして、絶縁を良くしてICの消費電力を小さくすることができ

ます。ただし、VPS2はRSSI負荷電流を供給しており、その電流が大きくなることがあるので、R2の値には考慮が必要です。

PADLと表示された4本のピンは金属リード・フレームに接続されており、それを通してチップの裏面にも接続されています。AD8309の製造プロセスでは、ボンディド・ウェハー技術を採用してシリコン・オン・インシュレータ・アイソレーションを得ており、裏面と表面の回路の間に接合または他のDCパスは存在しません。これらのパドル・ピンは、インダクタンスを最小にするため最小長のリードでグランド・プレーンに直接接続する必要があります。

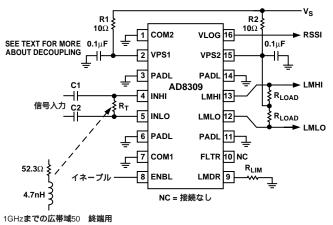

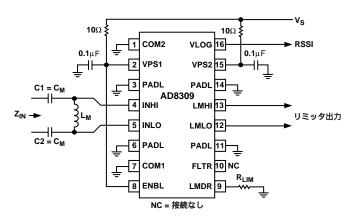

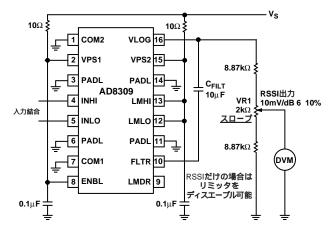

### 基本接続

図30に、多くのアプリケーションで必要とされる接続を示します。入力はC1とC2を使用してAC結合されています。これらのキャパシタは通常同じ値 $C_o$ を持ちます。結合時定数は $R_oC_o/2$ です。ここで、 $R_o=R_S+R_{IN}$ であり、3 dB減衰のハイパス・コーナは $f_{HP}=1/(R_TC_c)$ になります。高い周波数のアプリケーションでは、 $f_{HP}$ をできるだけ大きな値に選び、不要信号の混入を防止する必要があります。一方、低い周波数のアプリケーションでは、同じ理由で、ローパス・フィルタを構成する簡単なRCネットワークを入力に追加する必要があります。

図30.基本接続

低インピーダンスでソースを終端する必要がある場合は、AD8309の1 k 入力抵抗(R<sub>IN</sub>)の並列効果を考慮して、抵抗R<sub>T</sub>を追加します。例えば、50 ソースを終端するときは、約50 MHzまでの信号周波数に対して、52.3 の抵抗を使用します。終端部品は入力側または結合キャパシタの対数アンプ側に配置することができます。前者のケースでは、与えられた周波数範囲に対してより小さい値のキャパシタを使用することができます。後者のケースでは、対数アンプ入力でDC抵抗が直接下げられます。これはオフセットを最小に維持するのに役立ちます。より高い周波数では、2.5 pF入力容量のリアクタンスを考慮する必要があります。52.3 の終端抵抗に直列接続した4.7 nHインダクタが、1 GHzまで平坦な50 入力インピーダンスを提供します。50 インターフェースを用意するときは、インピーダンス変換ネットワークの使用が望まれます。これは、13 dB(typ)の平衡電圧ゲインを持ち、かつAD8309は大きな入力電圧に対して非常に大きな能力を持っているためです。

図31に、出力と入力レベルの関係を示します。正弦波入力5 MHz、50 MHz、100 MHz、200 MHzに対して、座標軸はdBm(50 終端)で示してあります。図32には、同じ条件での代表的な対数直線性(対数則適合度)を示します。

図31. RSSI出力と入力レベルとの関係 T<sub>n</sub> = +25 、周波数 = 5 MHz、50 MHz、100 MHz、200 MHz

図32.対数直線性と入力レベルの関係

T<sub>A</sub> = +25 、**周波数** = 5 MHz、50 MHz、100 MHz、200 MHz

# 入力の整合

高感度または良い高周波整合が必用な場合は、入力整合ネットワークが有効です。インピーダンス変換を行う磁束結合変成器を使うと、結合キャパシタが不要になり、入力で直接発生するDCオフセット電圧を下げ、INHIとINLOの駆動パランスをとり、AD8309の大きな入力電圧能力をフルに利用することができます。

巻数比の選択はある程度周波数に依存します。30 MHz以下の周波数では、入力容量のリアクタンスは、入力インピーダンスの実数部よりかなり大きくなります。この周波数範囲で、2:9の巻数比は、実効入力インピーダンスを50 に下げて、入力電圧を13 dBだけ上げます。ただし、入力ノイズ電流が影響しているため、これによって短絡回路ノイズ電圧は同じ量だけ低下しません。したがって、合計ノイズの減少はこれより小さい量になります。初段入力でのインターセプトは - 120 dBV(-107 dBm)に下げられます。

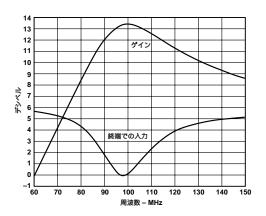

磁束結合変成器の使用によるインピーダンス整合と駆動バランスは、広帯域結合が必用な場合に常に有効です。ただし、これが常に便利とは限りません。高い周波数では、図33に示す狭帯域整合ネットワークが必用とされることがあります。これには幾つかの利点があります。1つ目は、同じ電圧ゲインが得られて、感度が上がりますが、選択性が同時に導入されます。

2つ目は、部品点数が少ないことです。2個のキャパシタと安価なチップ・インダクタが必用なだけです。3つ目は、ネットワークはタンク回路として機能します。このネットワークの解析によると、インピーダンス比が高い場合(例えば、50 ~1000 ) INHIとINLOでの電圧振幅が良く一致することが示されます。

図33. 高周波数入力での整合ネットワーク

図34に、中心周波数100 MHzに対する応答を示します。この応答は中心周波数の1/10で50 dB低下し、これより下では40 dB/ディケードで下がります。ただし、限られたケースでは、AD8309入力容量の結合キャパシタに対する比によって応答が単純に決定されているため、非常に高い周波数での減衰は比較的小さくなっています。表Iに、様々な中心周波数fcと公称50 と100 のインピーダンスZINに対する整合のソリューションを示します。正確な値が示してあるので、最寄りの標準値を選択する際は判断が必要です。

|      | 50 に対<br>(ゲイン: | する整合<br>= 10 dB) | 100 に対<br>(ゲイン= | 寸する整合<br>∶13 dB) |

|------|----------------|------------------|-----------------|------------------|

| fc   | C <sub>M</sub> | L <sub>M</sub>   | C <sub>M</sub>  | L <sub>M</sub>   |

| MHz  | pF             | nΉ               | pF              | nΉ               |

| 10   | 140            | 3500             | 100.7           | 4790             |

| 10.7 | 133            | 3200             | 94.1            | 4460             |

| 15   | 95.0           | 2250             | 67.1            | 3120             |

| 20   | 71.0           | 1660             | 50.3            | 2290             |

| 21.4 | 66.5           | 1550             | 47.0            | 2120             |

| 25   | 57.0           | 1310             | 40.3            | 1790             |

| 30   | 47.5           | 1070             | 33.5            | 1460             |

| 35   | 40.7           | 904              | 28.8            | 1220             |

| 40   | 35.6           | 779              | 25.2            | 1047             |

| 45   | 31.6           | 682              | 22.4            | 912              |

| 50   | 28.5           | 604              | 20.1            | 804              |

| 60   | 23.7           | 489              | 16.8            | 644              |

| 80   | 17.8           | 346              | 12.6            | 448              |

| 100  | 14.2           | 262              | 10.1            | 335              |

| 120  | 11.9           | 208              | 8.4             | 261              |

| 150  | 9.5            | 155              | 6.7             | 191              |

| 200  | 7.1            | 104              | 5.03            | 125              |

| 250  | 5.7            | 75.3             | 4.03            | 89.1             |

| 300  | 4.75           | 57.4             | 3.36            | 66.8             |

| 350  | 4.07           | 45.3             | 2.87            | 52.1             |

| 400  | 3.57           | 36.7             | 2.52            | 41.8             |

| 450  | 3.16           | 30.4             | 2.24            | 34.3             |

| 500  | 2.85           | 25.6             | 2.01            | 28.6             |

図34 . 100 MHz整合ネットワークの応答

### 一般的な整合手順

他の中心周波数とソース・インピーダンスに対しては、次の方法を使って基本整合パラメータを計算することができます。

ステップ1:C<sub>IN</sub>の同調

中心周波数 $f_c$ で、次式で値が決まる一時的なインダクタ $L_{IN}$ で共振させて、入力容量 $C_{IN}$ の並列インピーダンスが消えるようにします。

$$L_{IN} = 1/\{(2 f_C)^2 C_{IN}\} = 10^{10}/f_C^2$$

(8)

ここで、 $C_{IN}$  = 2.5 pF。 **例えば**、 $f_C$  = 100 MHzで、 $L_{IN}$  = 1  $\mu$  H。

ステップ2:CoとLoの計算

純粋な抵抗入力インピーダンスを持つため、結合部品 $C_o$ と $L_o$ の公称値を次式から計算します。

$$C_{O} = \frac{1}{2 f_{C} \sqrt{(R_{IN}R_{M})}}; L_{O} = \frac{\sqrt{(R_{IN}R_{M})}}{2 f_{C}}$$

(9)

AD8309の場合、 $R_{IN}$ は1 k です。したがって、50 に対する整合が必用な場合は、 $f_C$  = 100 MHzで、 $C_O$  = 7.12 pF、 $L_O$  = 356 nHになります

# ステップ3:C<sub>o</sub>を2つの部分に分割

図33に示す完全に平衡したネットワークを用意するため、各々が  $C_0$ の2倍の公称値を持つ2つのキャパシタC1 = C2(図では $C_M$ と表示)を使うことができます。この例では値14.24 pFが必用になります。これらの条件で、INHIとINLOでの電圧振幅を一致させます。2つのドライバである程度良いパランスを得るためには、C1が少しC2より大きいことが望まれます。これにより、標準値を選ぶときに、より広い範囲の選択が可能になります。例えば、キャパシタC1 = 15 pFとC2 = 13 pFを使用することができます ( $C_0$  = 6.96 pFになります)。

## ステップ4:L<sub>M</sub>の計算

$L_{IN}$ と $L_{O}$ を用意するために必用な整合インダクタは、次の並列接続で済みます。

$$L_{M} = L_{IN}L_{O}/(L_{IN} + L_{O}) \tag{10}$$

$L_{IN}$ =1  $\mu$  Hで、かつ $L_O$ =356 nHの場合、100 MHzで50 の整合をとるこの例での $L_M$ の値は262.5 nHになります。最寄りの標準値270 nHを使用しても整合精度が僅かに低下するだけで済みます。共振での電圧ゲインは、次式で示すようにインピーダンス比のみに依存します。

$$GAIN = 20 \log \left[ \sqrt{\frac{R_{IN}}{R_S}} \right] = 10 \log \left[ \frac{R_{IN}}{R_S} \right]$$

(11)

### スロープとインターセプトの調整

AD8309では、基本スケーリング・パラメータの調整チャンスは限られています。これらのパラメータは強固な設計により規格値に入るように厳密に制御されています。DVM上に測定信号レベルを表示するアプリケーションでは、10 mV/ディケードのスロープは便利です。表示は直接デシベルで行い、小数点の指定だけが必要です。これは簡単に実現でき、同時にこの正確な値を図35に示す回路を使って調整することができます。電圧をDVM上で測定する場合は、図に示すように大きなフィルタ・キャパシタCFILTを追加することができます。これにより、下位桁表示のフラツキを少なくすることができます。

10 dB間隔の複数のテストレベルを用意するときは、精密な減衰器または信号ジェネレータが必要です。調整は、ダイナミック・レンジのほぼ中央でAM変調信号を使って行うこともできます。小数値で表される変調の深さMに対して、変調周期1サイクルでのピークと谷との間のデシベル範囲は次式で与えられます。

$$dB = 20 \log_{10} (1 + M) / (1 - M)$$

(12)

**例えば、深さ70%(** M = 0.7 **)の**rms信号レベル - 40 dBmを使うと、 - 47.5 dBm ~ - 32.5 dBm**の範囲で信号が変化するため、デシベル範囲は**15 dBになります。したがって、出力はピーク間振幅150 mVを持つように調整されます。

図35.スロープの10 mV/dB ± 10%への調整

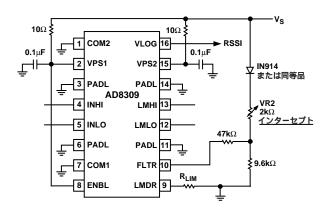

インターセプトは、図36に示す補助回路を使ってスロープを変更することなく調整することができます。スロープは20 mV/dBで不変です。この回路は、低い残留温度感度(+0.008 dB/)で、-113 dBV(-100 dBm)の公称インターセプトで約±4 dBの調整範囲を提供します。これは、AD8309のワーストケースインターセプト誤差およびシステム・レベルのゲイン誤差を吸収するためには十分です。ダイナミック・レンジの下限近くで既知のCW信号を入力しながらVR2を調節して、スロープにおける残留不確定要素の影響を最小になるようにします。例えば、インターセプトを-100 dBmに指定するときは、-60 dBmのテストレベルを入力し、VR2を調節して、インターセプトより40 dB高いDC出力(+0.8 V)を発生するようにします。この調整は、上述のスロープ調整と組み合わせて行うこともできます。

図36. インターセプトの - 113 dBV ± 4 dBへの調整

# アプリケーション

AD8309は多機能の使い易い対数リミッタ・アンプです。完結型であるため、外付け部品が少なくて済み、前節までに示した簡単な接続で多くのアプリケーションが可能です。この節では、さらに特別なアプリケーションを幾つか示します。

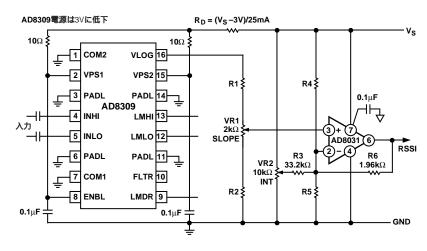

# 高いスロープ電圧を持つ対数アンプ

高いRSSIスロープ電圧および/または良い温度安定性と最小限の調整だけで済ませることが必要な場合は、図37に示すインターフェースを使うことができます。50 mV/dBでは、AD8309の100 dBの全ダイナミック・レンジは5 V振幅を必要とすることに注意してください。これは、レールtoレール出力ステージを持つ単電源動作のオペアンプを6 V電源で動作させた場合に実現できます。低い範囲で十分な場合、または40 mV/dBオプションを使用する場合は、5 V電源で十分です。

このアプリケーションでは、VPS2ピンの電源電流は負荷抵抗RLに流れる電流に少し依存します。そのため、電圧を下げる抵抗RDを追加してAD8309に対する電圧を下げることができます。これによって、2.7 V電源を持つ全ての仕様を満たすことができます。低いチップ消費電力とその結果生ずる動作温度の低下は、高い周囲温度での維音指数の低下を抑えます。RDは次のように計算されます。

$$R_D = \frac{V_S - 3}{25mA}$$

$$R_{LM} = 100$$

(13)

これにより、最大+85 までの周囲温度での動作が可能になります。表 ||を使って、種々の動作条件に対して部品値を選択することができます。スロープ調整範囲は±10%で、インターセプト調整範囲は±3 dBです。インターセプトオフセット・バイアスは電源から導出されるため、この電圧に対して感受性があります。電源電圧の安定が不十分な場合は、VR2とR4のバイアスにはレギュレータが必要になります。

図37.スロープとインターセプトの調整が可能なバッファ済みRSSI出力

| _ | _ |

|---|---|

|   |   |

|   |   |

|   |   |

| スロープ  | インターセプト | R1   | R2   | R4   | R5   | V <sub>out</sub> ( | V )at    |

|-------|---------|------|------|------|------|--------------------|----------|

| mV/dB | dBV     | k    | k    | k    | k    | - 88 dBV           | + 12 dBV |

| 40    | - 102   | 3.92 | 8.87 | O/C  | 1    | 0.56               | 4.56     |

| 50    | - 103   | 1.05 | 9.53 | O/C  | 1    | 0.75               | 5.75     |

| 40    | - 90    | 3.92 | 8.87 | 20.5 | 1.05 | 0.08               | 4.08     |

| 50    | - 90    | 1.05 | 9.53 | 15.4 | 1.07 | 0.1                | 5.10     |

# リミッタ出力レベルの設定

リミッタ出力は振幅I<sub>OUT</sub>を持つ一対の差動電流で、高インピーダンス・ソース(オープン・コレクタ)から供給されます。これらは、電源を基準とする負荷抵抗R<sub>LOAD</sub>により等しい振幅電圧に変換されます。リミッタ出力電流は、アプリケーションに応じて、ピン9(LMDR)とグランドとの間に接続される抵抗R<sub>LIM</sub>により設定され、得られた電圧は平衡接続または不平衡接続で使用することができます。どちらの出力モードを使う場合でも、両抵抗を接続しておくことが推奨されます。不平衡すなわちシングル・サイド・モードは、信号パスの非常に高いゲインに起因して不安定になりやすくなります。リミッタ出力が不要の場合は、LMDRを開放のままにし、LMHIとLMLOをVPS2に接続しておきます。

リミッタ出力電流は次式で設定されます。

$I_{OUT} = -400 \, mV/R_{UM}$

絶対精度は±5%です。

各リミッタ・ピン上の電圧は次式から得られます。

$V_{IJM} = V_S - 400 mV \times R_{IOAD} / R_{IJM}$

リミッタ電流は10 mAと大きな値に設定することができます。これは $R_{\text{LIM}}$ =40 を必要とし、この値よりある程度大きくすることができます。ただし、この広帯域幅信号パスのゲインはバイアス電流に比例し、 $R_{\text{LIM}}$ を小さくすると不安定性が増すため、大きなパイアス電流の使用はお奨めできません(推奨値=400)。

リミッタ出力は、- 78 dBV ~ +9 dBV**の入力レベルに対して規定** されています。リミッタの出力は、- 78 dBV( - 65 dBm )以上のレベルに対しては不安定になります。

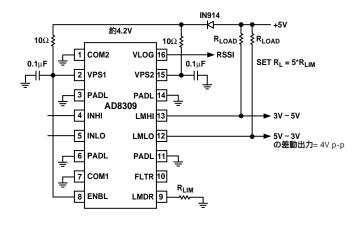

# 高出力リミッタの負荷

AD8309は、差動リミッタ出力インターフェースで大きな出力電力を発生することができます。入力整合に対して用意したものと同じラインの後段に狭帯域結合ネットワークを使用して、この出力をグランドに接続された50 負荷に接続することができます。あるいは、一次側に中心タップを持つ磁束結合変成器を使うこともできます。エミッタ・フォロアを使ってさらに大きな出力を得ることもできます。図38に、AD8309の電源電圧をダイオード使って5 Vから約4.2 Vに低下させた場合を示します。これにより、各出力での有効振幅を約2 Vに増やすことができます。両出力を差動で取り出すと、4 Vp - pの方形波出力を発生することができます。

図38.リミッタ出力電圧

高出力電力レベルと高周波数で動作する場合、安定性の問題には十分注意する必要があります。入力信号レベルが低い場合は、AD8309の非常に大きいゲイン帯域幅積に起因して発振が起こる可能性があります。200 MHz以下の周波数での動作では、信号バランス・ネットワークを使うとこれらの発振は生じにくくなります。一般に、これらの発振はノイズ・フロアより数dB高い入力レベルの信号により停止させられます。

### 変調リミッタ出力

AD8309のリミッタ出力ステージは、アナログ乗算機能も提供します。すなわち、出力方形波の振幅をLMDR(ピン9)を流れる電流で制御することができます。0 V ~ +1 Vのアナログ制御入力を使って、AD8309の内部バイアスにより約400 mVに固定された電圧にコレクタが維持されたnpnトランジスタに0 mA ~ 10 mAの正確に比例する電流を発生することができます。入力信号がリミッタ・スレッショルドよりウェハーにある場合は、出力は制御バイアスに比例した方形波振幅になります。

図39.可変リミッタ出力の設定

### インターセプトに及ぼす波形の影響

AD8309は基本的には電力ではなく電圧に応答します。この特性の直接の帰結は、入力信号で等しいrms電力値を持ちクレスト・ファクタが異なるものは、対数アンプの出力で異なる結果を発生することです。信号波形が異なるための影響は、対数アンプのインターセプトの実効値をシフトさせることです。図的には、対数アンプの伝達関数が垂直に移動することに対応します。デバイスの対数

スロープは影響を受けません。例えば、遅らされた正弦波と、それと同じrms電力を持つ1つのCDMAチャンネルが交互に入力されるAD8309のケースを考えてみます。AD8309の出力電圧には、デバイスの全ダイナミック・レンジで3.55 dB(71 mV)に等しい量だけ差が発生します(CDMA入力に対する出力の方が小さくなります)。

表IIIに、種々の信号のrms信号強度の計測に適用される補正係数を示します。正弦波入力を基準として使用します。方形波のrms電力を計測するときは、例えば、表に与えられたmVに等価なdB値(20 mV/dB×3.01 dB)をAD8309の出力電圧から減算します。

表 . 異なるクレスト・ファクタを持つ信号に対する AD8309出力のシフト

|                       | 補正係数       |

|-----------------------|------------|

| 信号タイプ                 | (出力計測値に加算) |

| 正弦波                   | 0 dB       |

| <b>方形波または</b> DC      | - 3.01 dB  |

| 三角波                   | + 0.9 dB   |

| GSMチャンネル(全タイム・スロットOn) | + 0.55 dB  |

| CDMAチャンネル             | + 3.55 dB  |

| PDCチャンネル(全タイム・スロットOn) | + 0.58 dB  |

| ガウス・ノイズ               | + 2.51 dB  |

### 評価ボード

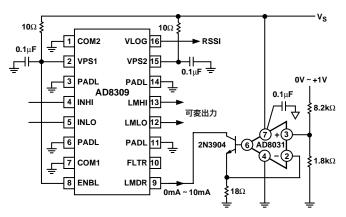

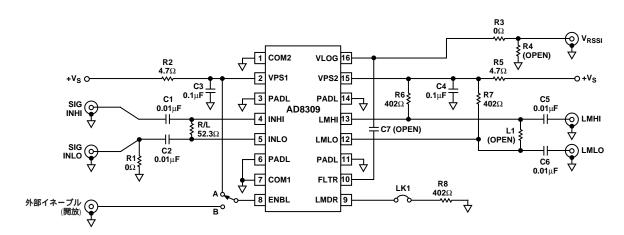

規定されたAD8309の高速性能を示すために注意深くレイアウトされ、テストされた評価ポードが提供されています。図 40 に、評価ポードの回路図を示します。この回路図は図30 に示す基本接続回路図に従ったものです。注文情報についてはオーダー・ガイドをを参照してください。表 IV に、異なるセットアップに対するリンク、スイッチ、部品の設定を示します。

図40.評価ボード回路図

表 . 評価ボードのセットアップ・オプション

| 部品             | 機能                                                                                                                                                                                                                          | デフォルト条件                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| SW1            | デバイス・イネーブル。位置Aの場合、ENBLピンが + VSに接続され、AD8309が通常の動作<br>モードになります。位置Bの場合、ENBLピンがExt Enableと表示されたSMAコネクタに続<br>続されます。入力された信号をこのコネクタに接続することができ、AD8309をイネーブル/<br>ディスエーブルします。開放の場合は、ENBLピンがフローティング状態でグランドになり、<br>デバイスをパワーダウン・モードにします。 | SW1 = A                                     |

| R1             | このパッドを使って、シングル・エンド入力の駆動をグランドにAC結合します。AD8309を<br>差動で駆動するときは、R1を取り外します。                                                                                                                                                       | R1 = 0                                      |

| R/L C1 C2      | 入力インターフェース。位置R/Lの52.3 抵抗がC1とC2一緒にハイパス入力フィルタを構成します。このフィルタのコーナ周波数(640 kHz)は1/(RC)です。ここで、C=C1=C2で、Rは52.3 とAD8309の入力インピーダンス1000 との並列接続です。代わりに、52.3 抵抗をインダクタで置き換えて入力整合ネットワークを構成こともできます。詳細については、入力整合ネットワークの節をを参照してください。           | R/L = 52.3<br>C1 = C2 = 0.01 μ F            |

| R3/R4          | スローブ調整。抵抗デバイダをVLOG出力に追加して、簡単なスロープ調整を組み込むことができます。和が約1 k で40 を超えない2つの抵抗R3とR4(仕様参照)を使うと、スロープを次式に従って設定することができます。<br>スロープ=20 mV/dB×R4/(R3+R4)                                                                                    | R3 = 0<br>R4 =                              |

| L1 £5 £6       | リミッタ出力結合。C5とC6によりリミッタの差動出力をAC結合します。これらの値を調整し、インダクタをL1に追加することにより、出力整合ネットワークを構成することができます。                                                                                                                                     | L1 = Open<br>C5 = 0.01 µ F<br>C6 = 0.01 µ F |

| R8 <b>L</b> K1 | リミッタ出力電流。LK2を実装すると、R8がリミッタ出力電流をイネーブルして設定します。<br>リミッタの出力電流は式I <sub>OUT</sub> = 400 mV/R8に従って設定されます。 リミッタ電流は10 mA<br>(R8 = 40 )まで大きくすることができます。 リミッタをディスエーブルするときは(リミッタが不要の場合に推奨 ) LK3を取り外します。                                  | LK1 Installed. R8 = 402                     |

| C7             | RSSI帯域幅調整。C7を追加すると、式 f <sub>CORNER</sub> = 12.7 × 10 <sup>-6</sup> /( C <sub>FILT</sub> + 3.5 pF <b>)に従って、</b> VLOG<br>出力のRSSI帯域幅を減少させます。                                                                                   | C7 = Open                                   |

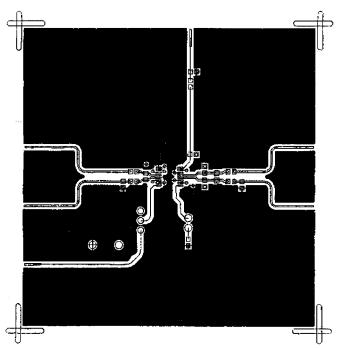

図42.電源レイヤーのレイアウト

08-006273 REV A COMPONENT SIDE

INHI

J1

INLO

J 6

EXT ENABLE J2 OB-006273 REV A CIRCUIT SIDE MAGE IN USA

Y L 0 G

COL C. J. 5

ADB309 EVALUATION BOARD REV A

ANALOG DEVICES WILMINGTON MFG

LMHI

LMI.0 J3

J 4

図44.電源レイヤー・シルクスクリーン

£3

# 外形寸法 サイズはインチと(mm)で示します。

16ピン・TSSOP (RU - 16)