# 低消費電力、350 MHzの 電圧帰還アンプ

### AD8038/AD8039

### 特長

低消費電力: アンプ1個あたりの電源電流1mA 高速動作

-3 dB 帯域幅: 350 MHz (G = +1)

スルーレート: 425 V/µs

低価格 低ノイズ

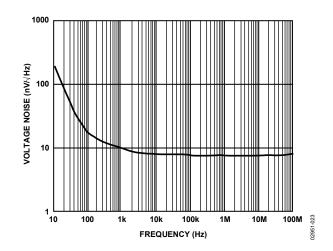

100 kHz で 8 nV/√Hz

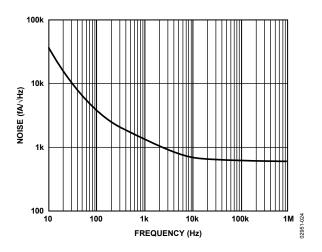

100 kHz で 600 fA/√Hz

低入力バイアス電流: 最大 750 nA

低歪み

1 MHz で-90 dB SFDR

5 MHz で-65 dB SFDR

広い電源範囲: 3 V~12 V

小型パッケージ: 8 ピン SOT-23、5 ピン SC70、8 ピン SOIC

### アプリケーション

バッテリ駆動の計装機器 フィルタ A/D ドライバ レベル・シフト バッファリング フォトマルチプライヤー

### 機能ブロック図

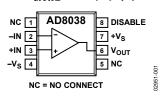

図 1.8 ピン SOIC (R)

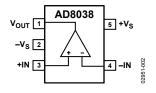

図 2.5 ピン SC70 (KS)

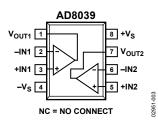

図 3.8 ピン SOIC (R)および 8 ピン SOT-23 (RJ)

### 概要

AD8038 (シングル)アンプと AD8039 (デュアル)アンプは、アンプ あたり 1.0 mA (typ)の非常に小さい静止電流(最大 1.5 mA)を持つ 高速(350 MHz)電圧帰還アンプです。8 ピン SOIC パッケージを採 用した AD8038 シングル・アンプにはディスエーブル機能があり ます。低消費電力で低価格にもかかわらず、このアンプは優れ た全体性能を提供します。さらに、425 V/μs の高いスルー・レ ートと最大3mVの低入力オフセット電圧を持っています。

アナログ・デバイス独自の XFCB 製造プロセスの採用により、 極めて小さい静止電流で低ノイズ動作(8 nV/√Hz、600 fA/√Hz)が 可能になっています。AD8038 および AD8039 アンプは、広い電 源電圧範囲(3 V~12 V)、広い帯域幅、小型パッケージを持つた め、低消費電力と省スペースが重要となる様々なアプリケーシ ョンで動作するようにデザインされています。

AD8038 および AD8039 アンプは、両電源レールの内側 1 V まで の広い同相モード入力範囲と両電源レールの内側 1 V までの出 力振幅を持っています。これらのアンプは、最大 15 pF の容量負 荷を駆動するように最適化されています。これより大きな容量 負荷を駆動する場合には、小さい直列抵抗を接続して大きなピ ーキングまたはオーバーシュートを防止する必要があります。

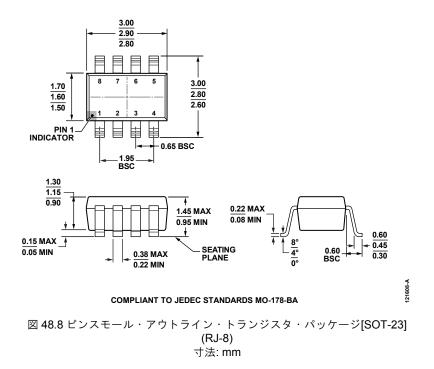

AD8039 アンプは 8 ピン SOT-23 パッケージを、シングルの AD8038 は 8 ピン SOIC または 5 ピン SC70 パッケージを、それ ぞれ採用しています。これらのアンプは、-40 ℃~+85 ℃ の工 業温度範囲で動作するように仕様が規定されています。

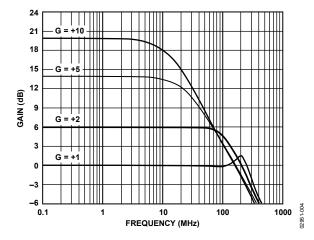

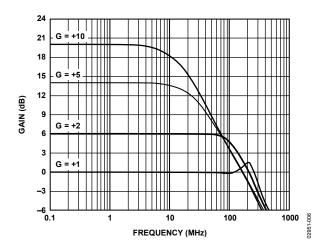

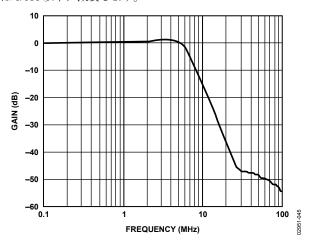

図 4.様々なゲインでの小信号周波数応答、V<sub>OUT</sub> = 500 mV p-p、  $V_S = \pm 5 V$

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に 関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様 予告なく変更される場合があります。 本紙記載の商標および登録商標は、各社の所有に属します ※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2002-2009 Analog Devices, Inc. All rights reserved.

Rev. G

## 目次

| 特長1                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------|

| アプリケーション1                                                                                                         |

| 機能ブロック図1                                                                                                          |

| 概要1                                                                                                               |

| 改訂履歴                                                                                                              |

| 仕様                                                                                                                |

| 絶対最大定5                                                                                                            |

| 最大消費電力5                                                                                                           |

| 出力の短絡5                                                                                                            |

| ESDの注意                                                                                                            |

| 代表的な性能特性6                                                                                                         |

| レイアウト、グラウンド、バイパスの考慮事項13                                                                                           |

|                                                                                                                   |

|                                                                                                                   |

| 改訂履歴                                                                                                              |

|                                                                                                                   |

| 8/09—Rev. F to Rev. G                                                                                             |

| $\mbox{8/09}\mbox{Rev.}$ F to Rev. G Changes to Applications Section and General Description Section1             |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section1                                                  |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section                                                   |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section1 Changes to Disable Section and Grounding Section |

| Changes to Applications Section and General Description Section                                                   |

|   | アイスエーブル              | 13 |

|---|----------------------|----|

|   | 電源のバイパス              | 13 |

|   | グラウンド接続              | 13 |

|   | 入力容量                 | 13 |

|   | 出力容量                 | 13 |

|   | 入力から出力へのカップリング       | 13 |

| ア | プリケーション情報            | 14 |

|   | 低消費電力ADCドライバ         | 14 |

|   | 低消費電力のアクティブ・ビデオ・フィルタ | 14 |

| 夕 | k形寸法                 | 15 |

|   | オーダー・ガイド             | 16 |

### 5/02—Rev. A to Rev. B

| Add Part Number AD8038                 | Universal |

|----------------------------------------|-----------|

| Changes to Product Title               | 1         |

| Changes to Features                    | 1         |

| Changes to Product Description         | 1         |

| Changes to Connection Diagram          | 1         |

| Update to Specifications               | 2         |

| Update to Maximum Power Dissipation    | 4         |

| Update to Output Short Circuit         | 4         |

| Update to Ordering Guide               | 4         |

| Change to Figure 2                     | 4         |

| Change to TPC 2                        | 5         |

| Change to TPC 18                       | 6         |

| Change to TPC 27                       | 7         |

| Change to TPC 29                       | 8         |

| Change to TPC 30                       | 8         |

| Change to TPC 31                       | 8         |

| Added TPC 36                           | 8         |

| Added TPC 37                           | 9         |

| Edits to Low Power Active Video Filter | 10        |

| Change to Figure 4                     | 10        |

| 4/02—Rev. 0 to Rev. A                  |           |

| Changes to Features                    | 1         |

| Update Specifications                  | 2, 3      |

| Edits to TPC 19                        | 7         |

## 仕様

特に指定がない限り、 $T_A=25^{\circ}C$ 、 $V_S=\pm 5$  V、 $R_L=2$   $k\Omega$ 、ゲイン=+1。

表 1.

| Parameter                            | Conditions                                                            | Min | Тур          | Max | Unit   |

|--------------------------------------|-----------------------------------------------------------------------|-----|--------------|-----|--------|

| DYNAMIC PERFORMANCE                  |                                                                       |     |              |     |        |

| −3 dB Bandwidth                      | $G = +1$ , $V_O = 0.5 \text{ V p-p}$                                  | 300 | 350          |     | MHz    |

|                                      | $G = +2$ , $V_O = 0.5 \text{ V p-p}$                                  |     | 175          |     | MHz    |

|                                      | $G = +1, V_0 = 2 V p-p$                                               |     | 100          |     | MHz    |

| Bandwidth for 0.1 dB Flatness        | $G = +2$ , $V_O = 0.2 \text{ V p-p}$                                  |     | 45           |     | MHz    |

| Slew Rate                            | $G = +1$ , $V_O = 2$ V step, $R_L = 2$ k $\Omega$                     | 400 | 425          |     | V/µs   |

| Overdrive Recovery Time              | G = +2, 1 V overdrive                                                 |     | 50           |     | ns     |

| Settling Time to 0.1%                | $G = +2$ , $V_O = 2$ V step                                           |     | 18           |     | ns     |

| NOISE/HARMONIC PERFORMANCE           |                                                                       |     |              |     |        |

| SFDR                                 |                                                                       |     |              |     |        |

| Second Harmonic                      | $f_C = 1 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -90          |     | dBc    |

| Third Harmonic                       | $f_C = 1 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -92          |     | dBc    |

| Second Harmonic                      | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -65          |     | dBc    |

| Third Harmonic                       | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -70          |     | dBc    |

| Crosstalk, Output-to-Output (AD8039) | f = 5  MHz, G = +2                                                    |     | -70          |     | dB     |

| Input Voltage Noise                  | f = 100  kHz                                                          |     | 8            |     | nV/√Hz |

| Input Current Noise                  | f = 100  kHz                                                          |     | 600          |     | fA/√Hz |

| DC PERFORMANCE                       |                                                                       |     |              |     |        |

| Input Offset Voltage                 |                                                                       |     | 0.5          | 3   | mV     |

| Input Offset Voltage Drift           |                                                                       |     | 4.5          |     | μV/°C  |

| Input Bias Current                   |                                                                       |     | 400          | 750 | nA     |

| Input Bias Current Drift             |                                                                       |     | 3            |     | nA/°C  |

| Input Offset Current                 |                                                                       |     | ±25          |     | nA     |

| Open-Loop Gain                       | $V_O = \pm 2.5 \text{ V}$                                             |     | 70           |     | dB     |

| INPUT CHARACTERISTICS                |                                                                       |     |              |     |        |

| Input Resistance                     |                                                                       |     | 10           |     | ΜΩ     |

| Input Capacitance                    |                                                                       |     | 2            |     | pF     |

| Input Common-Mode Voltage Range      | $R_L = 1 \text{ k}\Omega$                                             |     | ±4           |     | V      |

| Common-Mode Rejection Ratio          | $V_{CM} = \pm 2.5 \text{ V}$                                          | 61  | 67           |     | dB     |

| OUTPUT CHARACTERISTICS               |                                                                       |     |              |     |        |

| DC Output Voltage Swing              | $R_L = 2 \text{ k}\Omega$ , saturated output                          |     | ±4           |     | V      |

| Capacitive Load Drive                | 30% overshoot, $G = +2$                                               |     | 20           |     | pF     |

| POWER SUPPLY                         |                                                                       |     |              |     |        |

| Operating Range                      |                                                                       | 3.0 |              | 12  | V      |

| Quiescent Current per Amplifier      |                                                                       |     | 1.0          | 1.5 | mA     |

| Power Supply Rejection Ratio         | -Supply                                                               | -71 | -77          |     | dB     |

| 11.0                                 | +Supply                                                               | -64 | -70          |     | dB     |

| POWER-DOWN DISABLE <sup>1</sup>      | ***                                                                   |     |              |     |        |

| Turn-On Time                         |                                                                       |     | 180          |     | ns     |

| Turn-Off Time                        |                                                                       |     | 700          |     | ns     |

| Disable Voltage—Part is Off          |                                                                       |     | $+V_{S}-4.5$ |     | V      |

| Disable Voltage—Part is On           |                                                                       |     | $+V_{S}-2.5$ |     | V      |

| Disabled Quiescent Current           |                                                                       |     | 0.2          |     | mA     |

| Disabled In/Out Isolation            | f = 1  MHz                                                            |     | -60          |     | dB     |

<sup>&</sup>lt;sup>1</sup>8ピン SOIC パッケージの AD8038 の場合。

特に指定がない限り、 $T_A=25^{\circ}C$ 、 $V_S=5$  V、 $R_L=2$   $k\Omega$   $(V_S/2$  へ接続)、ゲイン=+1。

表 2.

| Parameter                          | Conditions                                                            | Min | Typ          | Max | Unit   |

|------------------------------------|-----------------------------------------------------------------------|-----|--------------|-----|--------|

| DYNAMIC PERFORMANCE                |                                                                       |     |              |     |        |

| −3 dB Bandwidth                    | $G = +1$ , $V_0 = 0.2 \text{ V p-p}$                                  | 275 | 300          |     | MHz    |

|                                    | $G = +2$ , $V_0 = 0.2 \text{ V p-p}$                                  |     | 150          |     | MHz    |

|                                    | $G = +1$ , $V_0 = 2 V p-p$                                            |     | 30           |     | MHz    |

| Bandwidth for 0.1 dB Flatness      | $G = +2$ , $V_0 = 0.2 \text{ V p-p}$                                  |     | 45           |     | MHz    |

| Slew Rate                          | $G = +1$ , $V_O = 2$ V step, $R_L = 2$ k $\Omega$                     | 340 | 365          |     | V/µs   |

| Overdrive Recovery Time            | G = +2, 1 V overdrive                                                 |     | 50           |     | ns     |

| Settling Time to 0.1%              | $G = +2$ , $V_O = 2$ V step                                           |     | 18           |     | ns     |

| NOISE/HARMONIC PERFORMANCE<br>SFDR |                                                                       |     |              |     |        |

| Second Harmonic                    | $f_C = 1 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -82          |     | dBc    |

| Third Harmonic                     | $f_C = 1 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -79          |     | dBc    |

| Second Harmonic                    | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -60          |     | dBc    |

| Third Harmonic                     | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |     | -67          |     | dBc    |

| Crosstalk, Output-to-Output        | f = 5  MHz, G = +2                                                    |     | -70          |     | dB     |

| Input Voltage Noise                | f = 100  kHz                                                          |     | 8            |     | nV/√Hz |

| Input Current Noise                | f = 100  kHz                                                          |     | 600          |     | fA/√Hz |

| DC PERFORMANCE                     |                                                                       |     |              |     |        |

| Input Offset Voltage               |                                                                       |     | 0.8          | 3   | mV     |

| Input Offset Voltage Drift         |                                                                       |     | 3            |     | μV/°C  |

| Input Bias Current                 |                                                                       |     | 400          | 750 | nA     |

| Input Bias Current Drift           |                                                                       |     | 3            |     | nA/°C  |

| Input Offset Current               |                                                                       |     | ±30          |     | nA     |

| Open-Loop Gain                     | $V_0 = \pm 2.5 \text{ V}$                                             |     | 70           |     | dB     |

| INPUT CHARACTERISTICS              |                                                                       |     |              |     |        |

| Input Resistance                   |                                                                       |     | 10           |     | ΜΩ     |

| Input Capacitance                  |                                                                       |     | 2            |     | pF     |

| Input Common-Mode Voltage Range    | $R_L = 1 \text{ k}\Omega$                                             |     | 1.0 - 4.0    |     | V      |

| Common-Mode Rejection Ratio        | $V_{CM} = \pm 1 \text{ V}$                                            | 59  | 65           |     | dB     |

| OUTPUT CHARACTERISTICS             |                                                                       |     |              |     |        |

| DC Output Voltage Swing            | $R_L = 2 \text{ k}\Omega$ , saturated output                          |     | 0.9 - 4.1    |     | V      |

| Capacitive Load Drive              | 30% overshoot                                                         |     | 20           |     | pF     |

| POWER SUPPLY                       |                                                                       |     |              |     |        |

| Operating Range                    |                                                                       | 3   |              | 12  | V      |

| Quiescent Current per Amplifier    |                                                                       |     | 0.9          | 1.5 | mA     |

| Power Supply Rejection Ratio       |                                                                       | -65 | -71          |     | dB     |

| POWER-DOWN DISABLE <sup>1</sup>    |                                                                       |     |              |     |        |

| Turn-On Time                       |                                                                       |     | 210          |     | ns     |

| Turn-Off Time                      |                                                                       |     | 700          |     | ns     |

| Disable Voltage—Part is Off        |                                                                       |     | $+V_{S}-4.5$ |     | V      |

| Disable Voltage—Part is On         |                                                                       |     | $+V_{S}-2.5$ |     | V      |

| Disabled Quiescent Current         |                                                                       |     | 0.2          |     | mA     |

| Disabled In/Out Isolation          | f = 1  MHz                                                            |     | -60          |     | dB     |

<sup>&</sup>lt;sup>1</sup>8ピン SOIC パッケージの AD8038 の場合。

### 絶対最大定

表 3.

| Parameter                            | Rating          |

|--------------------------------------|-----------------|

| Supply Voltage                       | 12.6 V          |

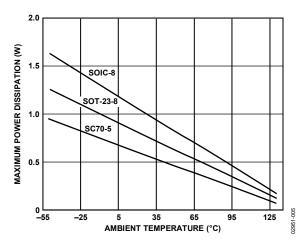

| Power Dissipation                    | See Figure 5    |

| Common-Mode Input Voltage            | $\pm V_S$       |

| Differential Input Voltage           | ±4 V            |

| Storage Temperature Range            | −65°C to +125°C |

| Operating Temperature Range          | −40°C to +85°C  |

| Lead Temperature (Soldering, 10 sec) | 300°C           |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### 最大消費電力

AD8038/AD8039 のパッケージ内での安全な最大消費電力は、チップのジャンクション温度 $(T_1)$ 上昇により制限されます。チップをプラスチック封止すると、局所的にジャンクション温度に到達します。約  $150^{\circ}$ C のガラス転移温度で、プラスチックの属性が変わります。この温度規定値を一時的に超えた場合でも、パッケージからチップに加えられる応力が変化して、AD8038/AD8039 のパラメータ性能を永久的にシフトしてしまうことがあります。 $175^{\circ}$ C のジャンクション温度を長時間超えると、シリコン・デバイス内に変化が発生して、故障の原因になることがあります。

パッケージと PCB  $(\theta_{JA})$ の自然空冷時の熱特性、周囲温度 $(T_A)$ 、パッケージ $(P_D)$ 内の合計消費電力によって、チップのジャンクション温度が決定されます。ジャンクション温度は次式で計算されます。

$$T_{\rm J} = T_A + (P_D \times \theta_{JA})$$

パッケージ内の消費電力 $(P_D)$ は、静止消費電力と全出力での負荷駆動に起因するパッケージ内の消費電力との和になります。静止電力は、電源ピン $(V_S)$ 間の電圧に静止電流 $(I_S)$ を乗算して計算されます。負荷 $(R_L)$ は電源電圧の中点を基準とするとすると、合計駆動電力は  $V_S/2 \times I_{OUT}$ になり、この電力がパッケージ内と負荷 $(V_{OUT} \times I_{OUT})$ で消費されます。合計駆動電力と負荷電力の差が、パッケージ内で消費される駆動電力です。

$P_D =$  静止電力+ (全駆動電力-負荷電力)  $P_D = [V_S \times I_S] + [(V_S/2) \times (V_{OUT}/R_L)] - [V_{OUT}^2/R_L]$

図 5.最大消費電力の温度特性、4 層ボード

RMS 出力電圧についても検討する必要があります。単電源動作の場合のように  $R_L$ が  $V_{S^-}$ を基準とすると、合計駆動電力は  $V_S \times I_{OUT}$  になります。 rms 信号レベルが不確定の場合は、電源電圧の中点を基準とする  $R_L$  に対して  $V_{OUT} = V_S/4$  とするときの、ワースト・ケースを検討します。

$$P_D = (V_S \times I_S) + (V_S/4)^2 / R_L$$

$V_{S}$ -を基準とする  $R_L$  を使う単電源動作では、ワースト・ケースは  $V_{OUT} = V_S/2$  となります。

空気流があると放熱効果が良くなり  $\theta_{JA}$  が小さくなります。 さらに、メタル・パターン、スルー・ホール、グラウンド・プレーン、電源プレーンとパッケージ・ピンが直接接触する場合、これらのメタルによっても  $\theta_{JA}$  は減少します。レイアウト、グラウンド、バイパスの考慮事項のセクションで説明するように、高速オペアンプの入力ピンでの寄生容量を小さくするように注意する必要があります。

図 5 に、パッケージ内での安全な最大消費電力と周囲温度の関係を、JEDEC 標準 4 層ボードに実装した 8 ピン SOIC (125°C/W)パッケージ、5 ピン SC70 (210°C/W)パッケージ、8 ピン SOT-23 (160°C/W)パッケージについて示します。 $\theta_{JA}$ 値は近似値です。

### 出力の短絡

出力をグラウンドへ短絡した場合、または AD8038/AD8039 から 過大な電流を流した場合には、致命的な故障が発生します。

### ESDの注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. **G** - 5/16 -

### 代表的な性能特性

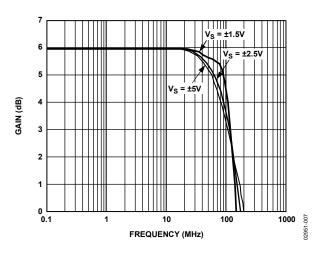

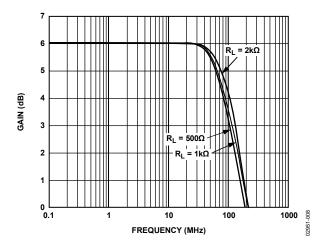

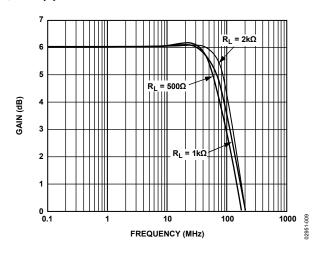

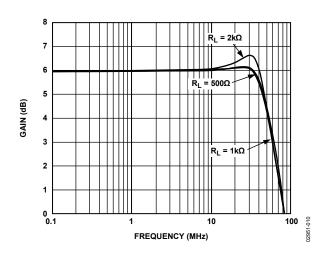

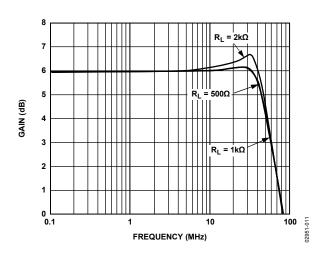

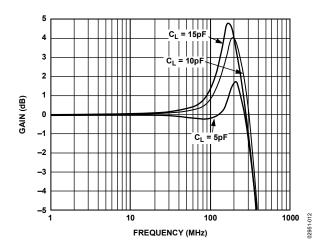

デフォルト条件:  $\pm 5$  V、 $C_L = 5$  pF、G = +2、 $R_G = R_F = 1$  k $\Omega$ 、 $R_L = 2$  k $\Omega$ 、 $V_O = 2$  V p-p、周波数= 1 MHz、 $T_A = 25$ °C。

図 6.様々なゲインでの小信号周波数応答 V<sub>OUT</sub> = 500 mV p-p

図 7.様々な電源での小信号周波数応答 V<sub>OUT</sub> = 500 mV p-p

図 8.様々な  $R_L$ での小信号周波数応答  $V_S=\pm 5~V$ 、 $V_{OUT}=500~mV~p-p$

図 9.様々な  $R_L$ での小信号周波数応答  $V_S = 5$  V、 $V_{OUT} = 500$  mV p-p

図 10.様々な  $R_L$ での大信号周波数応答  $V_{OUT}$  = 3 V P-P、 $V_S$  = 5 V

図 11.様々な  $R_L$ での大信号周波数応答  $V_{OUT}$  = 4 V p-p、  $V_S$  =  $\pm 5$  V

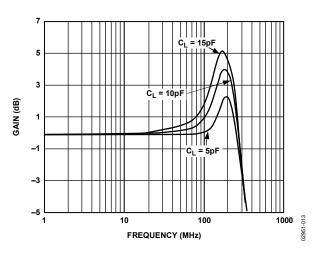

図 12.様々な  $C_L$  での小信号周波数応答  $V_{OUT}$  = 500 mV p-p、 $V_S$  = ±5 V、G = +1

図 13.様々な  $C_L$ での小信号周波数応答  $V_{OUT}$  = 500 mV p-p、 $V_S$  = 5 V、G = +1

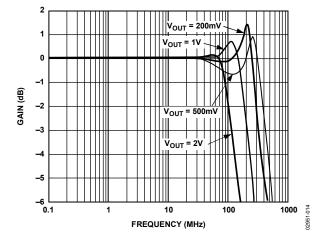

図 14.様々な出力電圧レベルでの周波数応答

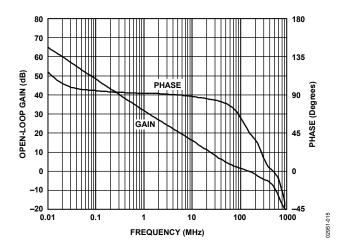

図 15.オープン・ループ・ゲインと位相  $V_S=\pm 5\ V$

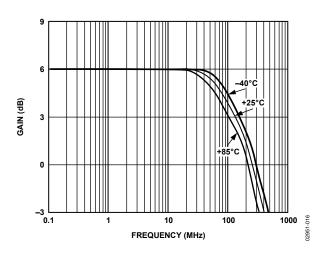

図 16.周波数応答の温度特性 ゲイン= +2、V<sub>S</sub> = ±5 V、V<sub>OUT</sub> = 2 V p-p

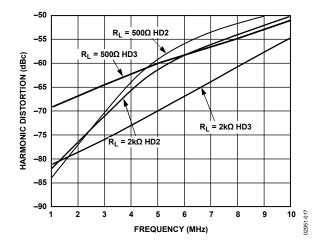

図 17.様々な負荷での高調波歪みの周波数特性  $V_S=\pm 5\ V$ 、 $V_{OUT}=2\ V$  p-p、 $G=\pm 2$

Rev. **G** - 7/16 -

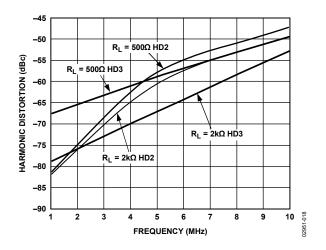

図 18.様々な負荷での高調波歪みの周波数特性  $V_S$  = 5 V、 $V_{OUT}$  = 2 V p-p、G = +2

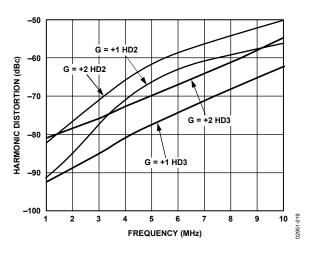

図 19.様々なゲインでの高調波歪みの周波数特性  $V_S=\pm 5~V,~V_{OUT}=2~V~p-p$

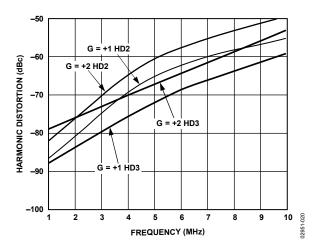

図 20.様々なゲインでの高調波歪みの周波数特性  $V_S=5\,V,\,V_{OUT}=2\,V\,p$ -p

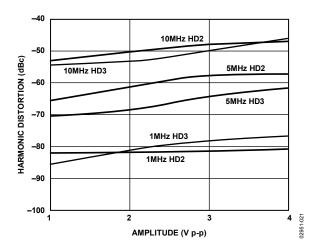

図 21.様々な周波数での  $V_{OUT}$ 振幅対高調波歪み  $V_S=\pm 5~V$ 、G=+2

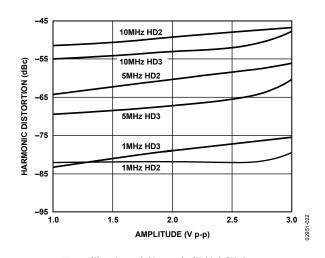

図 22.様々な周波数での振幅対高調波歪み  $V_S = 5 V$ 、G = +2

図 23.入力電圧ノイズの周波数特性

図 24.入力電流ノイズの周波数特性

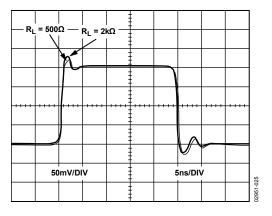

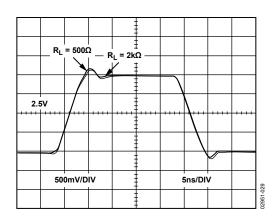

図 25.様々な  $R_L$ での小信号過渡応答、 $V_S = 5 V$

図 26.様々な  $R_L$ での小信号過渡応答、 $V_S$  =  $\pm 5~V$

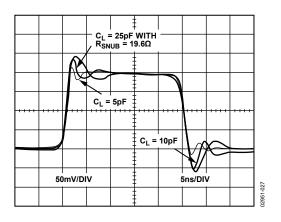

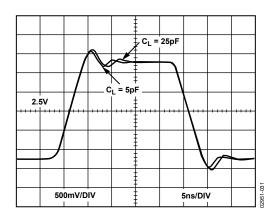

図 27.様々な  $C_L$ での小信号過渡応答、 $V_S$  = 5 V

図 28.様々な C<sub>L</sub>での小信号過渡応答、V<sub>S</sub> = ±5 V

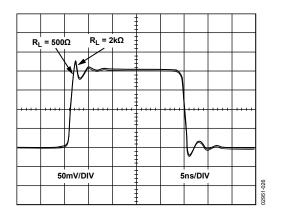

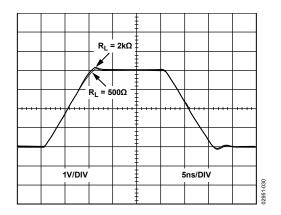

図 29.様々な R<sub>L</sub>での大信号過渡応答、V<sub>S</sub> = 5 V

Rev. **G** - 9/16 -

図 30.様々な  $R_L$ での大信号過渡応答、 $V_S$  =  $\pm 5~V$

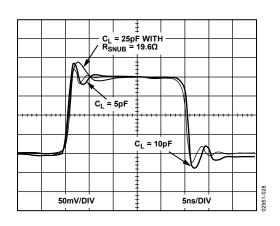

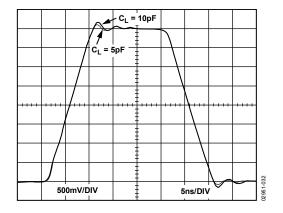

図 31.様々な  $C_L$ での大信号過渡応答、 $V_S$  = 5 V

図 32.様々な  $C_L$ での大信号過渡応答、 $V_S$  =  $\pm 5~V$

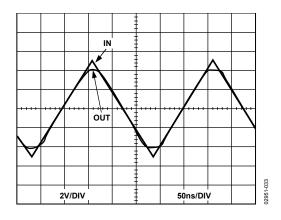

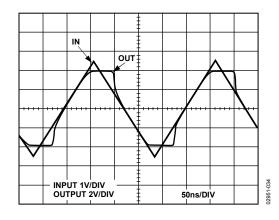

図 33.入力オーバードライブ回復、ゲイン=+1

図 34.出力オーバードライブ回復、ゲイン=+2

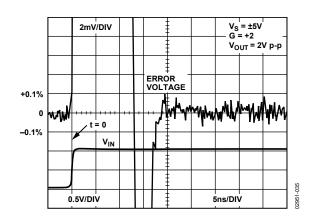

図 35.0.1%セトリング・タイム、 $V_{OUT}$  = 2  $V_{P-P}$

Rev. **G** - 10/16 -

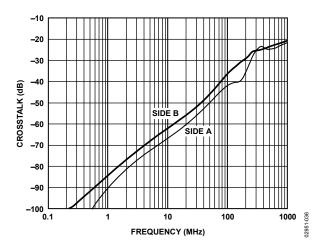

図 36.AD8039 クロストーク、 $V_{IN}$  = 1 V p-p、ゲイン= +1

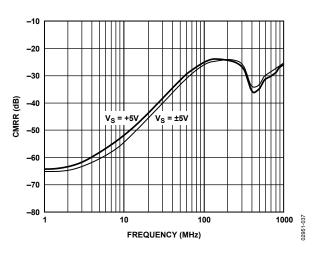

図 37.CMRR の周波数特性、V<sub>IN</sub> = 1 V p-p

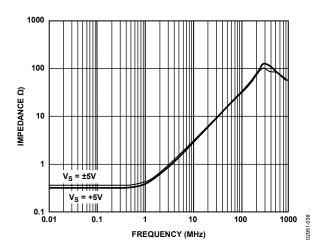

図 38.出力インピーダンスの周波数特性

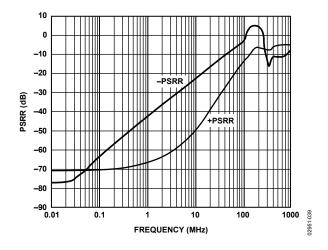

図 39.PSRR の周波数特性

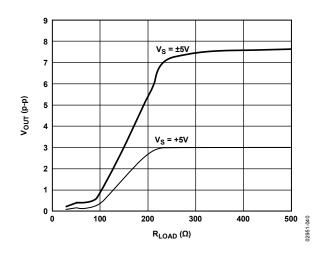

図 40.負荷抵抗対出力振幅

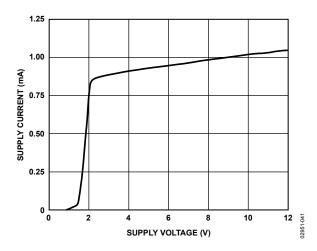

図 41.AD8038 電源電圧対電源電流

Rev. **G** — 11/16 —

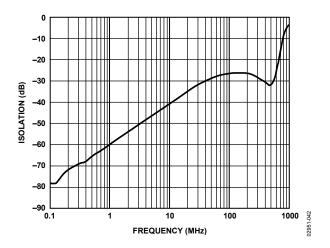

図 42.AD8038 入力—出力間アイソレーション  $G=+2,\ R_L=2\ k\Omega,\ V_S=\pm 5\ V$

Rev. **G** — 12/16 —

### レイアウト、グラウンド、バイパスの考慮事項

### ディスエーブル

8 ピン SOIC パッケージを採用した AD8038 にはディスエーブル機能があります。この機能は、入力と出力を切り離して(入力—出力間アイソレーションについては図 42 を参照)、静止電流(typ)を 1 mA から 0.2 mA へ減らします。 $\overline{DISABLE}$ ノードを正電源レールより 4.5 V 低くすると、デバイスがディスエーブルされます。デバイスをイネーブルするときは、 $\overline{DISABLE}$ ノードを( $V_S-2.5$ )より高くします。

### 電源のバイパス

電源ピンは実際には入力であるため、これらの入力に対してクリーンな低ノイズの DC 電圧源を接続するように注意する必要があります。バイパス・コンデンサの目的は、電源からグラウンドまでの低インピーダンスをすべての周波数で実現することですが、このためにノイズの大部分が除去されます。

デカップリング方法は、コンデンサの並列組み合わせを使って全周波数でバイパス・インピーダンスを小さくするようにデザインされます。 $0.01~\mu F$  または  $0.001~\mu F$  (X7R または NPO)のチップ・コンデンサは重要で、アンプ・パッケージのできるだけ近くに配置する必要があります。 $0.1~\mu F$  コンデンサのような大きなチップ・コンデンサは、同じ信号パス内の隣接する複数のアクティブ部品間で共用することができます。 $10~\mu F$  のタンタル・コンデンサは高周波バイパスに影響しないため、多くの場合、ボードあたり電源入力に  $1~\mu F$  個で済みます。

### グラウンド接続

グラウンド・プレーン層は、高密度実装の PC ボードでは電流を分散して寄生インダクタンスを小さくするために重要です。ただし、回路内の電流が流れる場所を理解することは、高速回路デザインを効果的に実現するためには重要です。電流パスの長さは寄生インダクタンスの大きさに直接比例するため、パスの高周波インピーダンスにも比例します。誘導性のグラウンド・リターンに高速電流が流れると、不要な電圧ノイズが発生します。

高周波バイパス・コンデンサのリード長は最も重要です。バイパス・グランディング内の寄生インダクタンスは、バイパス・コン

デンサによりつくられた低インピーダンスとは反対の働きをします。負荷電流は電源からも流れるため、負荷インピーダンスのグラウンドはバイパス・コンデンサのグラウンドと同じ場所に配置する必要があります。低い周波数でも効果的であることをねらった大きな値のコンデンサの場合は、電流リターン・パスの長さは問題になりません。

### 入力容量

バイパスとグラウンドの他に、高速アンプは入力とグラウンドとの寄生容量に対しても敏感です。高い周波数では、数 pF の容量でも入力インピーダンスを低下させて、アンプ・ゲインを大きくするため、周波数応答でピーキングが生じ、最悪の場合には発振することもあります。入力ピンに接続される外付けの受動部品は、寄生容量を回避するため出来るだけ入力の近くに配置することが推奨されます。グラウンド・プレーンと電源プレーンは、ボードの全層で入力ピンから少なくとも 0.05 mm 離す必要があります。

### 出力容量

出力にある寄生容量が小さい程、周波数応答でのピーキングは小さくなります。この影響を小さくするためには、次の方法があります。

- 小さい値の抵抗を出力に直列に挿入して、アンプの出力ステージから負荷容量を分離します。図 12、図 13、図 27、図 28 を参照してください。

- ノイズ・ゲインを大きくして位相マージンを増やすか、または-IN から出力までに並列抵抗とコンデンサを接続して、極を追加します。

### 入力から出力へのカップリング

入力と出力の間の容量結合を小さくして、正帰還を防止するため、 入力信号パターンと出力信号パターンを並行させないようにして ください。

Rev. **G** - 13/16 -

### アプリケーション情報

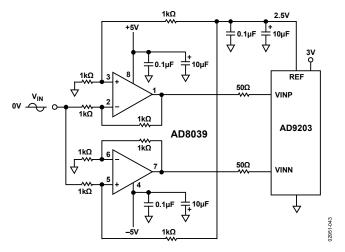

#### 低消費電力ADCドライバ

図 43.AD8039 で AD9203 を駆動する回路図

AD9203 は、低消費電力(5 V 電源で 125 mW)の 40 MSPS 10 ビット・コンバータです。したがって、この低消費電力高性能の AD8039 はこれを駆動するのに適したアンプです。

低電源電圧アプリケーションでは、差動アナログ入力が ADC 入力のダイナミックレンジを広げるために必要です。差動駆動により、2次およびその他の偶数次歪み積を小さくすることもできます。 AD8039 を使用してこれらの ADC に対する DC 結合のシングルエンド/差動変換ドライバを構成することができます。 図 43 に、AD9203(10 ビット、40 MSPS ADC)を駆動するこのような回路図を示します。

AD9203 は入力の同相モード電圧が電源中心すなわち 2.5 V のとき に最適動作します。AD8039 の出力ステージ・デザインにより、これらのタイプの ADC 駆動に最適になっています。

この回路では、オペアンプの内の 1 つが反転モードに、他の 1 つが非反転モードに、それぞれ構成されていますが、帯域幅の一致を良くするため、各オペアンプはノイズ・ゲイン=+2 に設定しています。反転オペアンプはゲイン=-1 に、非反転オペアンプはゲイン=+2 に、それぞれ設定しています。各々は良く一致した AC 応答を示します。非反転オペアンプの入力信号を 1/2 倍して電圧レベルに正規化し、反転出力に一致させます。

オペアンプ出力の中心は 2.5 V、すなわち ADC 電源レベルの中心にします。これは、ADC の 2.5 V リファレンス出力を使用し、これを一対の 1 kΩ 抵抗を使って 1/2 にすることにより実現しています。こうして得られた 1.25 V を各オペアンプの正入力に接続します。次にこの電圧はオペアンプのゲインで増幅されて各出力で 2.5 V レベルになります。

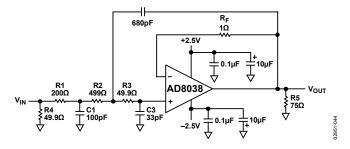

### 低消費電力のアクティブ・ビデオ・フィルタ

デジタル・ソースから得られるコンポジット・ビデオ信号によっては、画像品質を制限するクロック・フイードスルーを含むものがあります。このアプリケーションではオペアンプで構成するアクティブ・フィルタを使用することができますが、各チャンネルあたり 25 mW~30 mW の消費電力になります。消費電力に厳しいアプリケーションでは、この消費電力は大き過ぎるため、受動フィルタの使用が必要になりますが、大きな負荷を駆動する際に受動フィルタによりインピーダンス整合問題が生じます。

AD8038 を使用すると、オペアンプで構成するアクティブ・フィルタ消費電力の 1/5 で済む効果的なローパス・アクティブ・フィルタを構成することができます。図 44 に、 $\pm 2.5$  V 電源で AD8038 を使用して 3 極 Sallen-Key フィルタを構成する回路図を示します。この回路では、標準の 2 極アクティブ・セクションの前に RC の 1 極を使用しています。

図 44.ビデオ用ローパス・フィルタ

図 45 に、このフィルタの周波数応答を示します。応答は 6 MHz で 3 dB 低下するため、ビデオ帯域は減衰なしで通過します。27 MHz での除去比は 45 dB であるため、この周波数でのクロック成分は 1/100 以下に減衰します。

図 45.ビデオ・フィルタの応答

Rev. **G** — 14/16 —

### 外形寸法

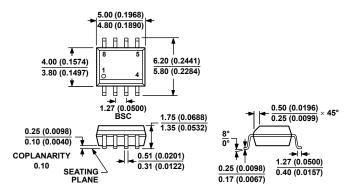

#### COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

図 46.8 ピン標準スモール・アウトライン・パッケージ[SOIC\_N] ナロー・ボディ (R-8) 寸法: mm (インチ)

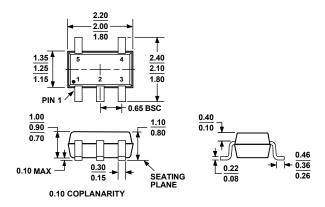

COMPLIANT TO JEDEC STANDARDS MO-203-AA

図 47.5 ピン薄型シュリンク・スモール・アウトライン・トランジスタ・パッケージ[SC70] (KS-5) 寸法: mm

Rev. **G** — 15/16 —

オーダー・ガイド

| Model                         | Temperature Range | Package Description                                        | Package Option | Branding |

|-------------------------------|-------------------|------------------------------------------------------------|----------------|----------|

| AD8038AR                      | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8038AR-REEL                 | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8038AR-REEL7                | −40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8038ARZ <sup>1</sup>        | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8038ARZ-REEL <sup>1</sup>   | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8038ARZ-REEL7 <sup>1</sup>  | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8038AKSZ-R21                | -40°C to +85°C    | 5-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-5           | H1C      |

| AD8038AKSZ-REEL <sup>1</sup>  | −40°C to +85°C    | 5-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-5           | H1C      |

| AD8038AKSZ-REEL7 <sup>1</sup> | −40°C to +85°C    | 5-Lead Thin Shrink Small Outline Transistor Package [SC70] | KS-5           | H1C      |

| AD8039AR                      | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8039AR-REEL                 | −40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8039AR-REEL7                | −40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8039ARZ <sup>1</sup>        | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8039ARZ-REEL <sup>1</sup>   | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8039ARZ-REEL7 <sup>1</sup>  | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N]             | R-8            |          |

| AD8039ART-R2                  | −40°C to +85°C    | 8-Lead Small Outline Transistor Package [SOT-23]           | RJ-8           | HYA      |

| AD8039ART-REEL                | −40°C to +85°C    | 8-Lead Small Outline Transistor Package [SOT-23]           | RJ-8           | HYA      |

| AD8039ART-REEL7               | −40°C to +85°C    | 8-Lead Small Outline Transistor Package [SOT-23]           | RJ-8           | HYA      |

| AD8039ARTZ-R21                | −40°C to +85°C    | 8-Lead Small Outline Transistor Package [SOT-23]           | RJ-8           | HYA#     |

| AD8039ARTZ-REEL <sup>1</sup>  | −40°C to +85°C    | 8-Lead Small Outline Transistor Package [SOT-23]           | RJ-8           | HYA#     |

| AD8039ARTZ-REEL7 <sup>1</sup> | -40°C to +85°C    | 8-Lead Small Outline Transistor Package [SOT-23]           | RJ-8           | HYA#     |

$<sup>^1</sup>$  Z = RoHS 準拠品。#は RoHS 準拠品を表し、上部または下部に表示。

Rev. **G** — 16/16 —