# | ANALOG 1MSPSのプログラマブルな差動入力 | DEVICES 14ビットPulSAR®A/Dコンバータ

**AD7952**

### 特長

複数ピン/ソフトウェアからプログラム可能な入力範囲  $+5V (10Vp-p) + 10V (20Vp-p) \pm 5V (20Vp-p)$ ±10V (40Vp-p)

ピンまたはシリアルSPI®互換の入力範囲/モードが選択可能 スループット:

1MSPS (ワープ・モード)

800kSPS (ノーマル・モード)

670kSPS (インパルス・モード)

14ビット分解能、ノー・ミッシング・コード

INL:  $\pm 0.3$ LSB (typ),  $\pm 1$ LSB (max) (FSR $\mathcal{O}\pm 61$ ppm)

SNR: 85dB@2kHz iCMOS®製造プロセス

5V内部リファレンス電圧:3ppm/℃のドリフト (typ)、

TEMP出力

パイプライン遅延なし(SARアーキテクチャ)

パラレル(14または8ビット・バス)およびシリアル5V/3.3V インターフェース

SPI/QSPI™/MICROWIRE™/DSP互換

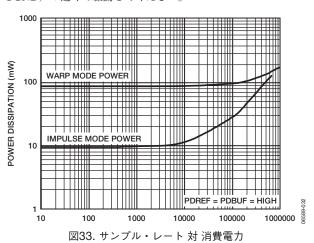

消費電力

235mW@1MSPS

10mW@1kSPS

48ピンLQFPおよび48ピンLFCSP (7mm×7mm)

# アプリケーション

プロセス制御

高速データ・アクイジション

デジタル・シグナル・プロセッシング

スペクトル分析

ATE

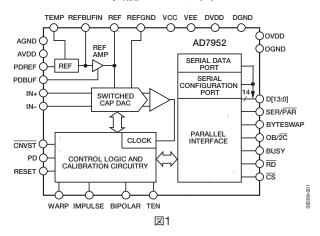

AD7952は14ビットの電荷再配分型SAR(逐次比較) A/Dコン バータ (ADC) であり、アナログ・デバイセズの*i*CMOS高電 圧プロセスで製造されています。入力範囲と動作モードは、 ハードウェアまたは書込み専用のシリアル設定ポートを使って 設定します。AD7952は、14ビットの高速サンプリングADC、 内部変換クロック、内部リファレンス電圧 (およびバッファ)、 誤差補正回路、シリアルおよびパラレルのシステム・インター フェース・ポートを持っています。CNVSTの立下がりエッジ で、IN+とIN-の差動アナログ入力をサンプルします。 AD7952には、4種類のアナログ入力範囲と3種類のサンプリン グ・モードがあります。3種類のサンプリング・モードは、最 速スループットのワープ・モード、最速非同期スループットの ノーマル・モード、それに消費電力がスループットに比例する インパルス・モードです。動作は-40~+85℃で仕様規定され ています。

#### 機能ブロック図

表1. 48ピンPulSAR ADCの選択肢

| Input Type               | Res<br>(Bits) | 100 to<br>250 (kSPS) | 500 to<br>570 (kSPS) | 570 to<br>1000<br>(kSPS) | >1000<br>(kSPS)  |

|--------------------------|---------------|----------------------|----------------------|--------------------------|------------------|

| Bipolar                  | 14            |                      |                      | AD7951                   |                  |

| Differential<br>Bipolar  | 14            |                      |                      | AD7952                   |                  |

| Unipolar                 | 16            | AD7651               |                      | AD7653                   |                  |

|                          |               | AD7660               | AD7650               | AD7667                   |                  |

|                          |               | AD7661               | AD7652               |                          |                  |

|                          |               |                      | AD7664               |                          |                  |

|                          |               |                      | AD7666               |                          |                  |

| Bipolar                  | 16            | AD7610               | AD7665               | AD7612                   |                  |

|                          |               | AD7663               |                      | AD7671                   |                  |

| Differential             | 16            | AD7675               | AD7676               | AD7677                   | AD7621           |

| Unipolar                 |               |                      |                      |                          | AD7622           |

|                          |               |                      |                      |                          | AD7623           |

| Simultaneous/            | 16            |                      | AD7654               |                          |                  |

| Multichannel<br>Unipolar |               |                      | AD7655               |                          |                  |

| Differential<br>Unipolar | 18            | AD7678               | AD7679               | AD7674                   | AD7641<br>AD7643 |

| Differential<br>Bipolar  | 18            | AD7631               |                      | AD7634                   |                  |

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の 利用に関して、あるいは利用によって生じる論とされている。 せん。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもので もありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有 に属します。

- トはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2007 Analog Devices, Inc. All rights reserved.

REV. 0

本 社/ 〒105-6891

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル

電話03 (5402) 8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号 電話06 (6350) 6868

# 目次

| 特長1             | ドライバ・アンプの選択         | 21 |

|-----------------|---------------------|----|

| アプリケーション1       | 電圧リファレンス入出力         | 22 |

| 概要              | 電源                  | 22 |

| 機能ブロック図1        | 変換制御                | 23 |

| 改訂履歴2           | インターフェース            | 24 |

| 仕様3             | デジタル・インターフェース       | 24 |

| タイミング仕様5        | パラレル・インターフェース       | 24 |

| 絶対最大定格7         | シリアル・インターフェース       | 25 |

| ESDに関する注意7      | マスター・シリアル・インターフェース  | 25 |

| ピン配置およびピン機能の説明8 | スレーブ・シリアル・インターフェース  | 27 |

| 代表的な性能特性12      | ハードウェア設定            | 29 |

| 用語の説明16         | ソフトウェア設定            | 29 |

| 動作原理17          | マイクロプロセッサとのインターフェース | 30 |

| 概要17            | アプリケーション情報          | 31 |

| コンバータの動作17      | レイアウトのガイドライン        | 31 |

| 動作モード18         | 性能評価                | 31 |

| 伝達関数18          | 外形寸法                | 32 |

| 代表的な接続図18       | オーダー・ガイド            | 32 |

| アナログ入力20        |                     |    |

# 改訂履歴

2/07—Revision 0: Initial Version

# 仕様

特に指定のない限りAVDD=DVDD=5V、OVDD=2.7~5.5V、VCC=15V、VEE=-15V、VREE=-15V、  $V_{REF}$ =5Vで、仕様はすべて $T_{MIN}$ ~ $T_{MAX}$ 条件下の値。

表2

| Parameter                                   | Conditions/Comments                                             | Min               | Тур                          | Max               | Unit             |

|---------------------------------------------|-----------------------------------------------------------------|-------------------|------------------------------|-------------------|------------------|

| RESOLUTION                                  |                                                                 | 14                |                              |                   | Bits             |

| ANALOG INPUTS                               |                                                                 |                   |                              |                   |                  |

| Differential Voltage Range, $V_{\text{IN}}$ | $(V_{IN+}) - (V_{IN-})$                                         |                   |                              |                   |                  |

| 0 V to 5 V                                  | $V_{IN} = 10 \text{ V p-p}$                                     | $-V_{REF}$        |                              | $+V_{REF}$        | V                |

| 0 V to 10 V                                 | $V_{IN} = 20 \text{ V p-p}$                                     | $-2 V_{REF}$      |                              | $+2 V_{REF}$      | V                |

| ±5 V                                        | $V_{IN} = 20 \text{ V p-p}$                                     | $-2 V_{REF}$      |                              | $+2 V_{REF}$      | V                |

| ±10 V                                       | $V_{IN} = 40 \text{ V p-p}$                                     | $-4 V_{REF}$      |                              | $+4 V_{REF}$      | V                |

| Operating Voltage Range                     | $V_{IN+}, V_{IN-}$ to AGND                                      |                   |                              |                   |                  |

| 0 V to 5 V                                  |                                                                 | -0.1              |                              | +5.1              | V                |

| 0 V to 10 V                                 |                                                                 | -0.1              |                              | +10.1             | V                |

| ±5 V                                        |                                                                 | -5.1              |                              | +5.1              | V                |

| ±10 V                                       |                                                                 | -10.1             |                              | +10.1             | V                |

| Common-Mode Voltage Range                   | $V_{\text{IN+}}, V_{\text{IN-}}$                                |                   |                              |                   |                  |

| 5 V                                         |                                                                 | $V_{REF}/2 - 0.1$ | $V_{REF}/2$                  | $V_{REF}/2 + 0.1$ | V                |

| 10 V                                        |                                                                 | $V_{REF} - 0.2$   | $V_{\scriptscriptstyle REF}$ | $V_{REF} + 0.2$   | V                |

| Bipolar Ranges                              |                                                                 | -0.1              | 0                            | +0.1              | V                |

| Analog Input CMRR                           | $f_{IN} = 100 \text{ kHz}$                                      |                   | 75                           |                   | dB               |

| Input Current                               | $V_{IN} = \pm 5 \text{ V}, \pm 10 \text{ V} @ 670 \text{ kSPS}$ |                   | $220^{1}$                    |                   | μΑ               |

| Input Impedance                             | See Analog Inputs section                                       |                   |                              |                   |                  |

| THROUGHPUT SPEED                            |                                                                 |                   |                              |                   |                  |

| Complete Cycle                              | In warp mode                                                    |                   |                              | 1                 | μs               |

| Throughput Rate                             | In warp mode                                                    | 1                 |                              | 1                 | MSPS             |

| Time Between Conversions                    | In warp mode                                                    |                   |                              | 1                 | ms               |

| Complete Cycle                              | In normal mode                                                  |                   |                              | 1.25              | μs               |

| Throughput Rate                             | In normal mode                                                  | 0                 |                              | 800               | kSPS             |

| Complete Cycle                              | In impulse mode                                                 |                   |                              | 1.49              | μs               |

| Throughput Rate                             | In impulse mode                                                 | 0                 |                              | 670               | kSPS             |

| DC ACCURACY                                 |                                                                 |                   |                              |                   |                  |

| Integral Linearity Error <sup>2</sup>       |                                                                 | -1                | ±0.3                         | +1                | LSB <sup>3</sup> |

| No Missing Codes <sup>2</sup>               |                                                                 | 14                |                              |                   | Bits             |

| Differential Linearity Error <sup>2</sup>   |                                                                 | -1                |                              | +1                | LSB              |

| Transition Noise                            |                                                                 |                   | 0.55                         |                   | LSB              |

| Zero Error (Unipolar or Bipolar)            |                                                                 | -15               |                              | +15               | LSB              |

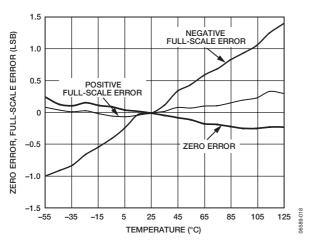

| Zero Error Temperature Drift                |                                                                 |                   | ±1                           |                   | ppm/℃            |

| Full-Scale Error (Unipolar or Bipolar)      |                                                                 | -20               |                              | +20               | LSB              |

| Full-Scale Error Temperature Drift          |                                                                 |                   | ±1                           |                   | ppm/℃            |

| Power Supply Sensitivity                    | $AVDD = 5 V \pm 5\%$                                            |                   | ±0.8                         |                   | LSB              |

| AC ACCURACY                                 |                                                                 |                   |                              |                   |                  |

| Dynamic Range                               | $f_{IN} = 2 \text{ kHz}, -60 \text{ dB}$                        | 84.5              | 85.5                         |                   | $dB^4$           |

| Signal-to-Noise Ratio, SNR                  | $f_{IN} = 2 \text{ kHz}$                                        | 84.5              | 85.5                         |                   | dB               |

|                                             | $f_{IN} = 20 \text{ kHz}$                                       |                   | 85.5                         |                   | dB               |

| a a                                         |                                                                 |                   |                              |                   |                  |

| Signal-to-(Noise + Distortion),<br>SINAD    | $f_{IN} = 2 \text{ kHz}$                                        | 83                | 85.4                         |                   | dB               |

| Total Harmonic Distortion                   | $f_{IN} = 2 \text{ kHz}$                                        |                   | -105                         |                   | dB               |

| Spurious-Free Dynamic Range                 | $f_{IN} = 2 \text{ kHz}$                                        |                   | 102                          |                   | dB               |

| -3 dB Input Bandwidth                       | $V_{IN} = 0 \text{ V to 5 V}$                                   |                   | 45                           |                   | MHz              |

| Aperture Delay                              |                                                                 |                   | 2                            |                   | ns               |

| Aperture Jitter                             |                                                                 |                   | 5                            |                   | ps rms           |

| Transient Respons                           | Full-scale step                                                 |                   | -                            | 500               | 1                |

| Transient Kespons                           | 1 un-scare step                                                 |                   |                              | 500               | ns               |

REV. 0 — 3 —

| Parameter                        | Conditions/Comments                        | Min      | Тур   | Max        | Unit       |

|----------------------------------|--------------------------------------------|----------|-------|------------|------------|

| INTERNAL REFERENCE               | PDREF = PDBUF = low                        |          |       |            |            |

| Output Voltage                   | REF @ 25℃                                  | 4.965    | 5.000 | 5.035      | V          |

| Temperature Drift                | -40°C to +85°C                             |          | ±3    |            | ppm/℃      |

| Line Regulation                  | $AVDD = 5 V \pm 5\%$                       |          | ±15   |            | ppm/V      |

| Long-Term Drift                  | 1000 hours                                 |          | 50    |            | ppm        |

| Turn-On Settling Time            | $C_{REF} = 22 \mu F$                       |          | 10    |            | ms         |

| REFERENCE BUFFER                 | PDREF = high                               |          |       |            |            |

| REFBUFIN Input Voltage Range     |                                            | 2.4      | 2.5   | 2.6        | V          |

| EXTERNAL REFERENCE               | PDREF = PDBUF = high                       |          |       |            |            |

| Voltage Range                    | REF                                        | 4.75     | 5     | AVDD + 0.1 | V          |

| Current Drain                    | 1 MSPS throughput                          |          | 200   |            | μA         |

| TEMPERATURE PIN                  |                                            |          |       |            |            |

| Voltage Output                   | @ 25℃                                      |          | 311   |            | mV         |

| Temperature Sensitivity          |                                            |          | 1     |            | mV/℃       |

| Output Resistance                |                                            |          | 4.33  |            | kΩ         |

| DIGITAL INPUTS                   |                                            |          |       |            |            |

| Logic Level                      |                                            |          |       |            |            |

| $V_{IL}$                         |                                            | -0.3     |       | +0.6       | V          |

| $ m V_{IH}$                      |                                            | 2.1      |       | OVDD + 0.3 | V          |

| $ m I_{IL}$                      |                                            | -1       |       | +1         | μA         |

| $ m I_{IH}$                      |                                            | -1       |       | +1         | μA         |

| DIGITAL OUTPUTS                  |                                            |          |       |            |            |

| Data Format                      | Parallel or serial 14-bit                  |          |       |            |            |

| Pipeline Delay <sup>5</sup>      |                                            |          |       |            |            |

| $V_{OL}$                         | $I_{SINK} = 500 \mu A$                     |          |       | 0.4        | V          |

| $ m V_{OH}$                      | $I_{SOURCE} = -500 \mu\text{A}$            | OVDD - 0 | 0.6   |            | V          |

| POWER SUPPLIES                   |                                            |          |       |            |            |

| Specified Performance            |                                            |          |       |            |            |

| AVDD                             |                                            | 4.756    | 5     | 5.25       | V          |

| DVDD                             |                                            | 4.75     | 5     | 5.25       | V          |

| OVDD                             |                                            | 2.7      |       | 5.25       | V          |

| VCC                              |                                            | 7        | 15    | 15.75      | V          |

| VEE                              |                                            | -15.75   | -15   | 0          | V          |

| Operating Current <sup>7,8</sup> | @ 1 MSPS throughput                        |          |       |            |            |

| AVDD                             |                                            |          |       |            |            |

| With Internal Reference          |                                            |          | 20    |            | mA         |

| With Internal Reference Disabled |                                            |          | 18.5  |            | mA         |

| DVDD                             |                                            |          | 7     |            | mA         |

| OVDD                             |                                            |          | 0.5   |            | mA         |

| VCC                              | VCC = 15 V, with internal reference buffer |          | 4     |            | mA         |

|                                  | VCC = 15 V                                 |          | 3     |            | mA         |

| VEE                              | VEE = -15  V                               |          | 2     |            | mA         |

| Power Dissipation                | @ 1 MSPS throughput                        |          | 26.7  | 260        |            |

| With Internal Reference          | PDREF = PDBUF = low                        |          | 235   | 260        | mW         |

| With Internal Reference Disabled | PDREF = PDBUF = high                       |          | 215   | 240        | mW         |

| In Power-Down Mode <sup>9</sup>  | PD = high                                  |          | 10    |            | μW         |

| TEMPERATURE RANGE <sup>10</sup>  |                                            |          |       |            |            |

| Specified Performance            | $T_{MIN}$ to $T_{MAX}$                     | -40      |       | +85        | $^{\circ}$ |

<sup>-</sup> V<sub>IN</sub>が5Vまたは10Vのユニポーラ範囲の場合、入力電流は70μA (typ) です。すべての入力範囲で、入力電流はスループットに比例します。「アナログ入力」を参照してくださ い。

<sup>2</sup> 直線性をテストする場合は、最適直線近似ではなくエンドポイントを使用し、また常に5Vの外部リファレンス電圧を使用しています。

<sup>3</sup> LSBは下位ビットを意味します。LSBの仕様には外部リファレンス電圧による誤差分は含まれません。

<sup>4</sup> dB表示の仕様はすべてフルスケール入力 (FSR) を基準とします。特に指定のない限り、フルスケールより0.5dB低い入力信号でテストします。

<sup>5</sup> 変換結果は、変換完了後直ちに出力されます。

$<sup>^{7}</sup>$  パラレル読出しモードでテスト。

<sup>\*\*</sup> 内部リファレンス電圧使用時は、PDREFとPDBUFはローレベル。内部リファレンス電圧なしでは、PDREFとPDBUFはハイレベル。内部リファレンス電圧バッファ使用時は PDBUFはローレベル。 すべてのデジタル入力をOVDDに接続。

<sup>10</sup> 拡張温度範囲については、代理店および弊社営業部にお問い合わせください。

**タイミング仕様** 特に指定のない限り、AVDD=DVDD=5V、OVDD=2.7~5.5V、VCC=15V、VEE=-15 V、V<sub>REF</sub>=5Vで、仕様はすべてT<sub>MIN</sub>~ T<sub>MAX</sub>条件下の数値。

#### 表3

| Parameter                                                                | Symbol          | Min        | Тур          | Max           | Unit |

|--------------------------------------------------------------------------|-----------------|------------|--------------|---------------|------|

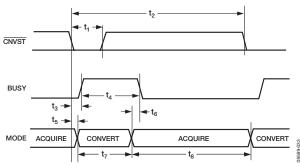

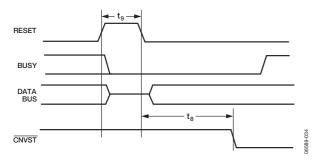

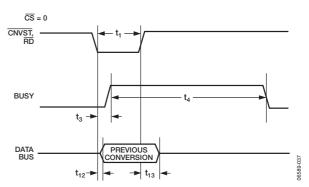

| CONVERSION AND RESET (See Figure 34 and Figure 35)                       |                 |            |              |               |      |

| Convert Pulse Width                                                      | $t_1$           | 10         |              |               | ns   |

| Time Between Conversions                                                 | $t_2$           |            |              |               |      |

| Warp Mode/Normal Mode/Impulse Mode <sup>1</sup>                          |                 | 1/1.25/1.4 | 9            |               | μs   |

| CNVST Low to BUSY High Delay                                             | $t_3$           |            |              | 35            | ns   |

| BUSY High All Modes (Except Master Serial Read After Convert)            | $t_4$           |            |              |               |      |

| Warp Mode/Normal Mode/Impulse Mode                                       |                 |            |              | 850/1100/1350 | ns   |

| Aperture Delay                                                           | t <sub>5</sub>  |            | 2            |               | ns   |

| End of Conversion to BUSY Low Delay                                      | t <sub>6</sub>  | 10         |              |               | ns   |

| Conversion Time                                                          | t <sub>7</sub>  |            |              |               |      |

| Warp Mode/Normal Mode/Impulse Mode                                       |                 |            |              | 850/1100/1350 | ns   |

| Acquisition Time                                                         | t <sub>8</sub>  |            |              |               |      |

| Warp Mode/Normal Mode/Impulse Mode                                       |                 | 200        |              |               | ns   |

| RESET Pulse Width                                                        | t <sub>9</sub>  | 10         |              |               | ns   |

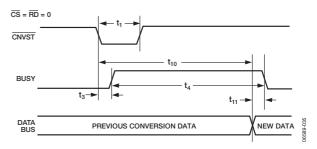

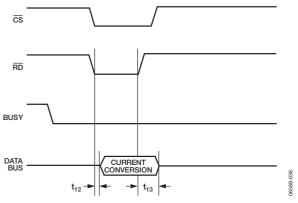

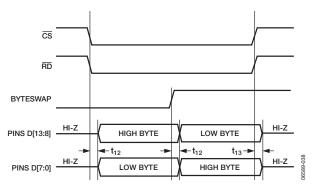

| PARALLEL INTERFACE MODES (See Figure 36 and Figure 38)                   |                 |            |              |               |      |

| CNVST Low to DATA Valid Delay                                            | t <sub>10</sub> |            |              |               |      |

| Warp Mode/Normal Mode/Impulse Mode                                       |                 |            |              | 850/1100/1350 | ns   |

| DATA Valid to BUSY Low Delay                                             | t <sub>11</sub> | 20         |              |               | ns   |

| Bus Access Request to DATA Valid                                         | t <sub>12</sub> |            |              | 40            | ns   |

| Bus Relinquish Time                                                      | t <sub>13</sub> | 2          |              | 15            | ns   |

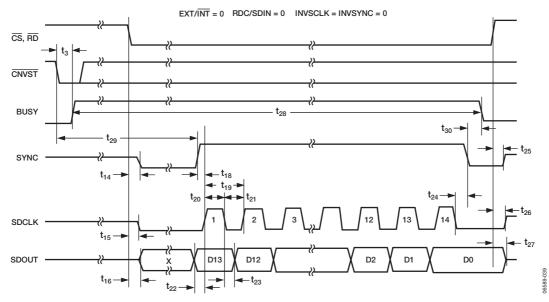

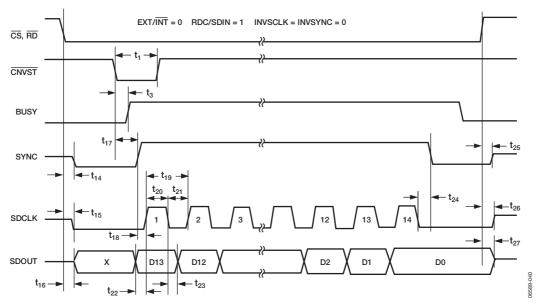

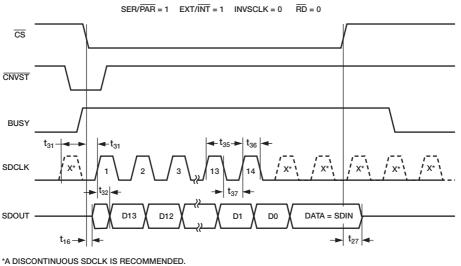

| MASTER SERIAL INTERFACE MODES <sup>2</sup> (See Figure 40 and Figure 41) |                 |            |              |               |      |

| CS Low to SYNC Valid Delay                                               | t <sub>14</sub> |            |              | 10            | ns   |

| CS Low to Internal SDCLK Valid Delay <sup>2</sup>                        | t <sub>15</sub> |            |              | 10            | ns   |

| CS Low to SDOUT Delay                                                    | t <sub>16</sub> |            |              | 10            | ns   |

| CNVST Low to SYNC Delay, Read During Convert                             | t <sub>17</sub> |            |              |               |      |

| Warp Mode/Normal Mode/Impulse Mode                                       | 1,              |            | 50/290/530   |               | ns   |

| SYNC Asserted to SDCLK First Edge Delay                                  | t <sub>18</sub> | 3          |              |               | ns   |

| Internal SDCLK Period <sup>3</sup>                                       | t <sub>19</sub> | 30         |              | 45            | ns   |

| Internal SDCLK High <sup>3</sup>                                         | t <sub>20</sub> | 15         |              |               | ns   |

| Internal SDCLK Low <sup>3</sup>                                          | t <sub>21</sub> | 10         |              |               | ns   |

| SDOUT Valid Setup Time <sup>3</sup>                                      | t <sub>22</sub> | 4          |              |               | ns   |

| SDOUT Valid Hold Time <sup>3</sup>                                       | t <sub>23</sub> | 5          |              |               | ns   |

| SDCLK Last Edge to SYNC Delay <sup>3</sup>                               | t <sub>24</sub> | 5          |              |               | ns   |

| CS High to SYNC High-Z                                                   | t <sub>25</sub> |            |              | 10            | ns   |

| CS High to Internal SDCLK High-Z                                         | t <sub>26</sub> |            |              | 10            | ns   |

| CS High to SDOUT High-Z                                                  | t <sub>27</sub> |            |              | 10            | ns   |

| BUSY High in Master Serial Read After Convert <sup>3</sup>               | t <sub>28</sub> |            | See Table 4  |               |      |

| CNVST Low to SYNC Delay Read After Convert                               | t <sub>29</sub> |            |              |               |      |

| Warp Mode/Normal Mode/Impulse Mode                                       |                 |            | 710/950/1190 | )             | ns   |

| SYNC Deasserted to BUSY Low Delay                                        | t <sub>30</sub> |            | 25           |               | ns   |

REV. 0 -5-

| Parameter                                                                                                | Symbol          | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

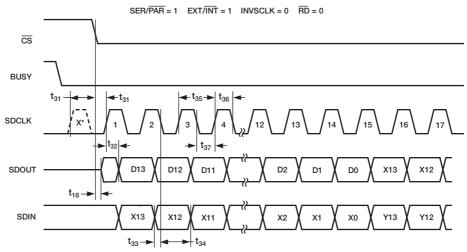

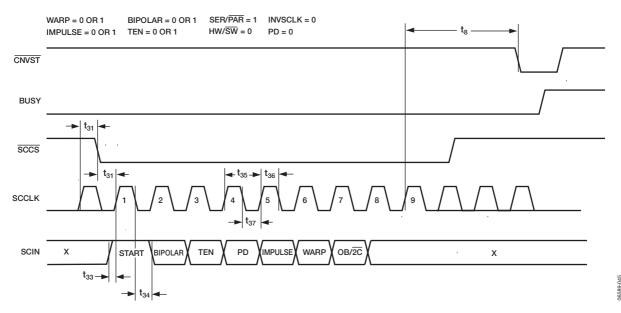

| SLAVE SERIAL/SERIAL CONFIGURATION INTERFACE MODES <sup>2</sup> (See Figure 43, Figure 44, and Figure 46) |                 |     |     |     |      |

| External SDCLK, SCCLK Setup Time                                                                         | t <sub>31</sub> | 5   |     |     | ns   |

| External SDCLK Active Edge to SDOUT Delay                                                                | t <sub>32</sub> | 2   |     | 18  | ns   |

| SDIN/SCIN Setup Time                                                                                     | t <sub>33</sub> | 5   |     |     | ns   |

| SDIN/SCIN Hold Time                                                                                      | t <sub>34</sub> | 5   |     |     | ns   |

| External SDCLK/SCCLK Period                                                                              | t <sub>35</sub> | 25  |     |     | ns   |

| External SDCLK/SCCLK High                                                                                | t <sub>36</sub> | 10  |     |     | ns   |

| External SDCLK/SCCLK Low                                                                                 | t <sub>37</sub> | 10  |     |     | ns   |

#### 表4. 変換モード後のマスタ読出し時のシリアル・クロック・タイミング

| DIVSCLK[1] DIVSCLK[0]                  | Symbol          | 0    | 0    | 1    | 1    | Unit |

|----------------------------------------|-----------------|------|------|------|------|------|

| SYNC to SDCLK First Edge Delay Minimum | t <sub>18</sub> | 3    | 20   | 20   | 20   | ns   |

| Internal SDCLK Period Minimum          | t <sub>19</sub> | 30   | 60   | 120  | 240  | ns   |

| Internal SDCLK Period Maximum          | t <sub>19</sub> | 45   | 90   | 180  | 360  | ns   |

| Internal SDCLK High Minimum            | $t_{20}$        | 12   | 30   | 60   | 120  | ns   |

| Internal SDCLK Low Minimum             | $t_{21}$        | 10   | 25   | 55   | 115  | ns   |

| SDOUT Valid Setup Time Minimum         | t <sub>22</sub> | 4    | 20   | 20   | 20   | ns   |

| SDOUT Valid Hold Time Minimum          | $t_{23}$        | 5    | 8    | 35   | 90   | ns   |

| SDCLK Last Edge to SYNC Delay Minimum  | $t_{24}$        | 5    | 7    | 35   | 90   | ns   |

| BUSY High Width Maximum                | $t_{28}$        |      |      |      |      |      |

| Warp Mode                              |                 | 1.60 | 2.35 | 3.75 | 6.75 | μs   |

| Normal Mode                            |                 | 1.85 | 2.60 | 4.00 | 7.00 | μs   |

| Impulse Mode                           |                 | 2.10 | 2.85 | 4.25 | 7.25 | μs   |

$t_{\text{DELAY}}$ t<sub>DELAY</sub> - 2V -2V - 0.8V - 0.8V

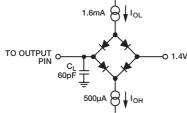

図2. デジタル・インターフェース・タイミングの負荷回路、 SDOUT、SYNC、SDCLKの各出力、 $C_L$ =10pF

図3. タイミングの電圧リファレンスのレベル

-6-REV. 0

<sup>1</sup> ワープ・モードでのみ、変換と変換の間隔は1 msとなります。これ以外の場合、最大時間は不要です。 2 シリアル・インターフェース・モードでSYNC、SDCLK、SDOUTのタイミングは、最大負荷 $C_L=10pF$ で規定。その他の場合は、最大負荷60pFで規定。 3 変換モードでのシリアル・マスタ読出し時。変換モード後のシリアル・マスタ読出しについては表4を参照。

NOTES

1. IN SERIAL INTERFACE MODES, THE SYNC, SDCLK, AND SDOUT ARE DEFINED WITH A MAXIMUM LOAD C<sub>L</sub> OF 10pF; OTHERWISE, THE LOAD IS 60pF MAXIMUM.

# 絶対最大定格

#### 表5

| Parameter                                   | Rating                          |

|---------------------------------------------|---------------------------------|

| Analog Inputs/Outputs                       |                                 |

| IN+ <sup>1</sup> , IN- <sup>1</sup> to AGND | VEE – 0.3 V to VCC<br>+0.3 V    |

| REF, REFBUFIN, TEMP, REFGND to AGND         | AVDD + 0.3 V to<br>AGND – 0.3 V |

| Ground Voltage Differences                  |                                 |

| AGND, DGND, OGND                            | ±0.3 V                          |

| Supply Voltages                             |                                 |

| AVDD, DVDD, OVDD                            | -0.3 V to +7 V                  |

| AVDD to DVDD, AVDD to OVDD                  | ±7 V                            |

| DVDD to OVDD                                | ±7 V                            |

| VCC to AGND, DGND                           | -0.3 V to +16.5 V               |

| VEE to GND                                  | +0.3 V to -16.5 V               |

| Digital Inputs                              | -0.3 V to OVDD<br>+0.3 V        |

| PDREF, PDBUF                                | ±20 mA                          |

| Internal Power Dissipation <sup>2</sup>     | 700 mW                          |

| Internal Power Dissipation <sup>3</sup>     | 2.5 W                           |

| Junction Temperature                        | 125℃                            |

| Storage Temperature Range                   | -65°C to +125°C                 |

<sup>「</sup>アナログ」入力の項を参照。

左記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作セクションに記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くと、デバイスの 信頼性に影響を与えることがあります。

### ESDに関する注意

ESD(静電放電)の影響を受けやすいデバイス です。電荷を帯びたデバイスや回路ボードは、 検知されないまま放電することがあります。本 製品は当社独自の特許技術であるESD保護回路 を内蔵してはいますが、デバイスで高エネル ギーの静電放電が発生した場合、損傷を生じる 可能性があります。性能劣化や機能低下を防止 するため、ESDに対して適切な予防措置をとる ことが推奨されます。

REV. 0 -7-

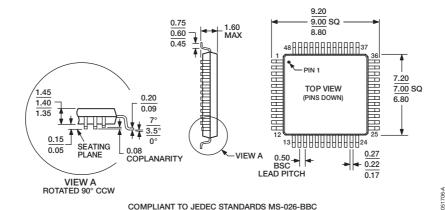

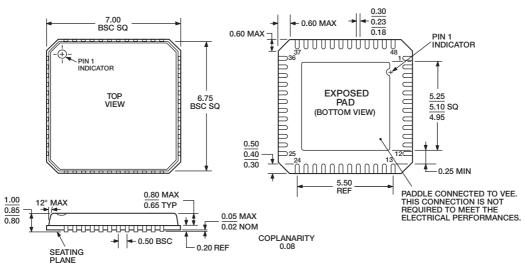

<sup>2</sup> 自然空冷、48ビンLQFP、θ<sub>IA</sub>=91℃/W、θ<sub>IC</sub>=30℃/W時のデバイス仕様。

3 自然空冷、48ビンLFCSP、θ<sub>IA</sub>=26℃/Wでのデバイス仕様。

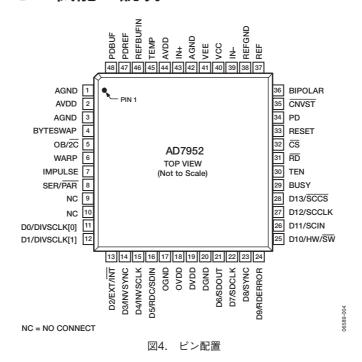

# ピン配置およびピン機能の説明

表6. ピン機能の説明

| ピン番号     | 記号           | タイプ1            | 説明                                                                                                                                    |                                                |                                                                                                           |  |

|----------|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| 1, 3, 42 | AGND         | Р               | アナログ電源のグラウンド・ピン。全アナログ入出力に対するグラウンド・リファレンス電<br>圧ポイント。全アナログ入出力信号はAGND電圧を基準とし、システムのアナログ・グラウ<br>ンド・プレーンに接続します。また、AGND、DGND、OGNDは同じ電位になります。 |                                                |                                                                                                           |  |

| 2, 44    | AVDD         | P               | アナログ電源ピン。公称4.75~5.25Vであり、10μFと100pFのコンデンサでデカップリング<br>します。                                                                             |                                                |                                                                                                           |  |

| 4        | BYTESWAP     | DI              | パラレル・モードの選択 $(8/14$ ビット)。ハイレベルにすると、LSBがD[15:8]に、MSBがD[7:0]にそれぞれ出力されます。ローレベルにすると、LSBがD[7:0]に、MSBがD[15:8] にそれぞれ出力されます。                  |                                                |                                                                                                           |  |

| 5        | OB/2C        | DI <sup>2</sup> | ストレート・バイナリ $/2$ の補数出力。 $OB/2C$ をハイレベルにするとデジタル出力はストレート・バイナリになり、ローレベルにすると $MSB$ が反転されて内部シフト・レジスタから2の補数が出力されます。                          |                                                |                                                                                                           |  |

| 6        | WARP         | $DI^2$          | 変換モードの選択                                                                                                                              | !。下記に従って <b>IN</b> F                           | PULSE入力と組み合わせて使用します。                                                                                      |  |

|          |              |                 | 変換モード                                                                                                                                 | WARP                                           | IMPULSE                                                                                                   |  |

|          |              |                 | ノーマル                                                                                                                                  | ローレベル                                          | ローレベル                                                                                                     |  |

|          |              |                 | インパルス                                                                                                                                 | ローレベル                                          | ハイレベル                                                                                                     |  |

|          |              |                 | ワープ                                                                                                                                   | ハイレベル                                          | ローレベル                                                                                                     |  |

|          |              |                 | ノーマル                                                                                                                                  | ハイレベル                                          | ハイレベル                                                                                                     |  |

|          |              |                 | 詳細については、                                                                                                                              | 「動作モード」を参                                      | 照。                                                                                                        |  |

| 7        | IMPULSE      | $DI^2$          | 変換モードの選択<br>参照。                                                                                                                       | え。この表のWARP                                     | ピンの説明を参照。詳細については、「動作モード」を                                                                                 |  |

| 8        | SER/PAR      | DI              | れ、ハイレベルに                                                                                                                              | :するとシリアル・3                                     | PARをローレベルにするとパラレル・ポートが選択さ<br>Eードが選択されます。データ・バスの一部のビットが<br>りのデータ・ビットが高インピーダンス出力となりま                        |  |

| 9, 10    | NC           | DO              | 無接続。接続し                                                                                                                               | ません。                                           |                                                                                                           |  |

| 11, 12   | D[0:1] or    | DI/O            |                                                                                                                                       |                                                | 出力をパラレル・ポート・データ出力バスのビット0お                                                                                 |  |

|          | DIVSCLK[0:1] |                 | ドを使用するとき<br>ベル)、これらの                                                                                                                  | 分周ク <u>ロック</u> の選打<br>(SER/PAR=ハイ<br>入力を使用して、テ | 尺。変換モード終了後のシリアル・マスター読出しモーレベル、EXT/INT =ローレベル、RDC/SDIN=ローレータ出力する内部シリアル・クロックの速度を低下さ・モードでは、これらのピンは高インピーダンス出力と |  |

| ピン番号 | 記号      | タイプ1 | 説明                                                                                                                                     |

|------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| 13   | D2 or   | DI/O | パラレル・モードのとき、これらの出力をパラレル・ポート・データ出力バスのビット2として使用します。                                                                                      |

|      | EXT/INT |      | シリアル・データ・クロック源の選択。シリアル・モードとき、この入力を使用して<br>AD7952出力データの内部(マスター)シリアル・データ・クロックや外部(スレーブ)シ                                                  |

|      |         |      | $  U \cap V \cap$                                                              |

|      |         |      | タ・ <u>クロッ</u> クを選択します。<br>EXT/INTをハイレベル(スレーブ・モード)にすると、出力データがSDCLK入力に接続さ                                                                |

| 14   | D3 or   | DI/O | れた外部クロック信号(CSでゲーティングされる)に同期します。<br>  パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット3として                                                         |

|      | INVSYNC |      | 使用します。<br> シリアル・データ反転同期の選択。シリアル・マスター・モード(SER/PAR=ハイレベル、                                                                                |

|      |         |      | EXT/INT=ローレベル)のとき、この入力を使用してSYNC信号のアクティブ状態を選択します。<br>INVSYNCがローレベルのとき、SYNCはアクティブ・ハイになります。                                               |

|      |         |      | INVSYNCがハイレベルのとき、SYNCはアクティブ・ローになります。                                                                                                   |

| 15   | D4 or   | DI/O | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット4として<br>  使用します。                                                                                  |

|      | INVSYNC |      | すべてのシリアル・モードで反転SDCLK/SCCLKの選択。この入力をSDCLKとSCCLKの<br>反転に使用します。                                                                           |

|      |         |      | INVSYNCがローレベルのとき、SDCLK/SCCLKの立上がりエッジを使用します。 INVSYNCがハイレベルのとき、SDCLK/SCCLKの立下がりエッジを使用します。                                                |

| 16   | D5 or   | DI/O | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット5として<br>  使用します。                                                                                  |

|      | RDC or  |      | 変換中のシリアル・データ読出し。シリアル・マスター・モード(SER/PAR=ハイレベル、EXT/INT=ローレベル)のとき、RDCは読出しモードの選択に使用されます。「マスター・シリアル・インターフェース」を参照。                            |

|      |         |      | RDCがローレベルの場合、変換終了後に現在の結果が読み出されます。このモードで最大スレープットを達成することはできません。                                                                          |

|      | SDIN    |      | RDCがハイレベルの場合、現在の変換中に前の変換結果が読み出され <u>ます。</u><br>  シリ <u>アル</u> ・データ入力。シリアル・スレーブ・モード(SER/PAR=ハイレベル、                                      |

|      |         |      | EXT/INT=ハイレベル)のとき、SDINをデータ入力として使って、1本のSDOUTラインに接続された複数のADCの変換結果をデイジーチェーン接続できます。SDINのデジタル・                                              |

|      |         |      | データ・レベルは、読出しシーケンス開始からSCLKの16周期分の遅延でSDOUT上に出力されます。                                                                                      |

| 17   | OGND    | P    | I/O入出力インターフェースのデジタル電源グラウンド。デジタル出力のグラウンド・リファレンス電圧ポイント。AGNDおよびDGNDと同じ電位のシステム・デジタル・グラウンドに接続するのが理想です。                                      |

| 18   | OVDD    | P    | $I/O$ インターフェースのデジタル電源。通常は、ホスト・インターフェース電源(2.5V、3V、または $5$ V)と同じ電源です。 $10$ $\mu$ Fコンデンサと $100$ nFコンデンサでデカップリングします。                       |

| 19   | DVDD    | P    | デジタル電源。通常は $4.75\sim5.25$ Vです。 $10\mu$ Fコンデンサと $100n$ Fコンデンサでデカップリングされます。 $AVDD$ から電源を供給できます。                                          |

| 20   | DGND    | P    | デジタル電源グラウンド。デジタル出力のグラウンド・リファレンス電圧ポイント。AGND<br>およびDGNDと同じ電位でシステム・デジタル・グラウンドに接続するのが理想的です。                                                |

| 21   | D6 or   | DO   | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット6として<br>使用します。                                                                                    |

|      | SDOUT   |      | シリアル・データ出力。シリアル・モードのとき、このピンをSDCLKに同期するシリアル・データ出力として使用します。変換結果は内蔵レジスタに保持されます。AD7952は内部シフト・レジスタからMSBファーストで変換結果を出力します。データ・フォーマット          |

|      |         |      | はOB <u>/2C</u> のロジック・レベルで指定されます。<br>EXT/INT=ローレベル(マスター・モード)の場合:SDOUTはSDCLKの両エッジで有効                                                     |

|      |         |      | です。<br>EXT/INT=ハイレベル(スレーブ・モード)の場合:                                                                                                     |

|      |         |      | INVSCLK=ローレベルのとき、SDOUTはSDCLKの立上がりエッジで更新されます。<br>  INVSCLK=ハイレベルのとき、SDOUTはSDCLKの立下がりエッジで更新されます。                                         |

| 22   | D7 or   | DI/O | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット7として使用します。                                                                                        |

|      | SDCLK   |      | シリアル・データ・クロック。シリアル・モードのとき、このピンは、EXT/INTのロジック<br>状態に応じてシリアル・データ・クロック入力または出力として使用します。データ<br>SDOUTが更新されるアクティブ・エッジは、INVSCLKピンのロジック状態により決定さ |

| 23   | D8 or   | DO   | れます。<br>パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット <b>8</b> として                                                                             |

| 23   | SYNC    |      | 使用します。<br>  シリアル・データ・フレーム同期。シリアル・マスター・モード(SER/PAR = ハイレベル、                                                                             |

|      | SINC    |      | EXT/INT=ローレベル)のとき、この出力を、内部データ・クロックとともに使用されるデジタル出力フレーム同期として使用します。読出しシーケンスが開始され、かつ                                                       |

|      |         |      | INVSYNC=ローレベルのとき、SYNCはハイレベルに駆動され、SDOUT出力が有効な間ハイレベルが維持されます。                                                                             |

|      |         |      | 読出しシーケンスが開始され、かつINVSYNC=ハイレベルのとき、SYNCはローレベルに<br>駆動され、SDOUT出力が有効な間ローレベルが維持されます。                                                         |

REV. 0 — 9 —

| ピン番号 | 記号      | タイプ1            | 説明                                                                                                                                                                                                                                         |                |

|------|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 24   | D9 or   | DO              | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット9とし                                                                                                                                                                                                   | して             |

|      | RDERROR |                 | 使用します。<br>シリアル・データ読出しエラー。シリアル・スレーブ・モード(SER/PAR=ハイレベ<br>EXT/INT=ハイレベル)のとき、この出力を、未完了データ読出しエラー・フラグとし<br>使用します。現在の変換が完了してデータ読出しが開始され、その処理が完了しない場合<br>現在のデータが失われて、RDERRORにハイレベル・パルスが出力されます。                                                     | して             |

| 25   | D10 or  | DI/O            | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット10と                                                                                                                                                                                                   | して             |

|      | HW/SW   |                 | 使用します。<br>シリアル・モードでのハードウェア/ソフトウェア設定の選択。シリアル・モードのとき<br>この入力により、ハードウェアかソフトウェアによるAD7952の設定を選択できま<br>「ハードウェア設定」と「ソフトウェア設定」を参照してください。<br>HW/SW=ローレベルのときは、シリアル設定レジスタを使ってAD7952をソフトウェス<br>ら設定できます。<br>HW/SW=ハイレベルのときは、入力ピンを使ってAD7952をハードウェア設定できます | す。<br>アか       |

| 26   | D11 or  | DI/O            | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット11と                                                                                                                                                                                                   | して             |

|      | SCIN    |                 | 使用します。<br>シリアル設定データ入力。シリアル・ソフトウェア設定モード(SER/PAR=ハイレベ<br>HW/SW=ローレベル)のとき、この入力は、設定データをMSBファーストでシリアル<br>レジスタにシリアルに書き込むために使用します。この入力データはSCCLKでラッチで<br>ます。「ソフトウェアの設定」を参照してください。                                                                  | 設定             |

| 27   | D12 or  | DI/O            | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット12と                                                                                                                                                                                                   | して             |

|      | SCCLK   |                 | 使用します<br>シリアル設定クロック。シリアル・ソフトウェア設定モード(SER/PAR = ハイレベ<br>HW/SW = ローレベル)のとき、この入力を使って、SCINにデータを入力します。デー<br>SCINが更新されるアクティブ・エッジは、INVSCLKピンのロジック状態により決定され<br>す。「ソフトウェアの設定」を参照してください。                                                             | ータ             |

| 28   | D13 or  | DI/O            | パラレル・モードのとき、この出力をパラレル・ポート・データ出力バスのビット13とし使用します                                                                                                                                                                                             | して             |

|      | SCCS    |                 | 使用しょり<br>シリアル設 <u>定チップ・セレクト。シリアル・ソフトウェア設定モード(SER/PAR</u> =ハッベル、HW/SW=ローレベル)のとき、この入力でシリアル設定ポートをイネーブルしま<br>「ソフトウェアの設定」を参照してください。                                                                                                             | イレ<br>:す。      |

| 29   | BUSY    | DO              | ビジー出力。変換開始時にハイレベルになり、変換が完了してデータが内蔵シフト・レミタにラッチされるまでハイレベルを維持します。BUSYの立下がりエッジは、データディ・クロック信号として使うことができます。変換モード後のマスタ読出して(SER/PAR=ハイレベル、EXT/INT=ローレベル、RDC=ローレベル)、ビジー時間はに従い変動します。                                                                 | ・レでは           |

| 30   | TEN     | $DI^2$          | 入力範囲の選択。これは次のようにBIPOLARと組み合わせて使用します。                                                                                                                                                                                                       |                |

|      |         |                 | 入力範囲(V) BIPOLAR TEN                                                                                                                                                                                                                        |                |

|      |         |                 | 0~5 ローレベル ローレベル<br>0~10 ローレベル ハイレベル                                                                                                                                                                                                        |                |

|      |         |                 | ±5 ハイレベル ローレベル                                                                                                                                                                                                                             |                |

|      |         |                 | ±10 ハイレベル ハイレベル                                                                                                                                                                                                                            |                |

| 31   | RD      | DI              | データの読出し。 $\overline{\text{CS}}$ と $\overline{\text{RD}}$ がともにローレベルのとき、インターフェースのパラレルまプシリアル出力バスが有効になります。                                                                                                                                     |                |

| 32   | CS      | DI              | チップ・セレクト。 $CS$ と $RD$ がともにロー $V$ でルのとき、インターフェースのパラレルはシリアル出力バスが有効になります。 $CS$ は、スレーブ・シリアル・モードで外部シリル・クロックのゲーティングにも使用します(シリアル設定ポートには使用されません)。                                                                                                  | リア             |

| 33   | RESET   | DI              | リセット入力。ハイレベルに設定すると、AD7952がリセットされ、変換中であれ <u>ば変われませます。RESETの立下がりエッジでデータ出力がすべてゼロになり(OB/2C=アレベル)、設定レジスタがクリアされます。「デジタル・インターフェース」を参照。このンは、未使用時にOGNDに接続しておきます。</u>                                                                                | 換を<br>ハイ       |

| 34   | PD      | DI <sup>2</sup> | パワーダウン入力。PDをハイレベルにすると、ADCがパワーダウンします。消費電力に少して、現在の変換が完了した後に変換が禁止されます。パワーダウン中、デジタル・ペターフェースはアクティブ状態を維持します。                                                                                                                                     |                |

| 35   | CNVST   | DI              | 変換の開始。CNVSTの次の立下がりエッジで内部サンプル/ホールドがホールド状態しり、変換が開始されます。                                                                                                                                                                                      | にな             |

| 36   | BIPOLAR | $DI^2$          | 入力範囲の選択。ピン30の説明を参照。                                                                                                                                                                                                                        |                |

| 37   | REF     | AI/O            | リファレンス電圧入出力。PDREF/PDBUFがローレベルの場合、内部リファレンス電圧バッファが有効になり、このピン上に5Vが出力されます。PDREF/PDBUFがハイレベル場合、内部リファレンス電圧とバッファが無効になり、AVDDまでのリファレンス電圧を部から供給できるようになります。内部リファレンス電圧およびバッファの有無とは無限に、最小でも22μFのコンデンサによるデカップリングが必要です。「リファレンス電圧力」を参照。                    | ルの<br>を外<br>関係 |

|      | i .     | 1               | リファレンス電圧入力のアナログ・グラウンド。アナログ・グラウンド・プレーンに接続                                                                                                                                                                                                   | (-t- )         |

— 10 — REV. 0

| ピン番号 | 記号       | タイプ1 | 説明                                                                                                                                                                                                                                                                                                                                                         |

|------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39   | IN-      | AI   | アナログ入力。 $IN+$ を基準とします。 $0\sim5$ Vの入力範囲の場合、 $IN-$ は $V_{REF}/2$ を中心とする $0\sim V_{REF}$ の範囲の電圧となります。 $0\sim10$ Vの入力範囲の場合は、 $V_{REF}$ を中心とする $0\sim2V_{REF}$ の範囲の電圧となります。 $\pm5$ Vまたは $\pm10$ Vの範囲の場合、 $IN-$ は $0$ Vを中心とする最大 $\pm2V_{REF}$ ( $\pm5$ Vの範囲)または最大 $\pm4V_{REF}$ ( $\pm10$ Vの範囲)の真のバイポーラ入力範囲になります。 全範囲で、 $IN+$ とは $180$ °逆位相で $IN-$ を駆動する必要があります。 |

| 40   | VCC      | P    | 正側高電圧電源。通常は7~15V。                                                                                                                                                                                                                                                                                                                                          |

| 41   | VEE      | P    | 負側高電圧電源。通常は $0 \sim -15 \mathrm{V}$ (ユニポーラ範囲での $0 \mathrm{V}$ )。                                                                                                                                                                                                                                                                                           |

| 43   | IN+      | AI   | アナログ入力。 $IN-e$ 基準とします。 $0\sim5$ Vの入力範囲の場合、 $IN+$ は $V_{REF}/2$ を中心とする $0\sim V_{REF}$ の範囲の電圧となります。 $0\sim10$ Vの入力範囲の場合は、 $V_{REF}$ を中心とする $0\sim2V_{REF}$ の範囲の電圧となります。 $\pm5$ Vまたは $\pm10$ Vの範囲の場合、 $IN+$ は $0$ Vを中心とする最大 $\pm2V_{REF}$ ( $\pm5$ Vの範囲)または最大 $\pm4V_{REF}$ ( $\pm10$ Vの範囲)の真のバイポーラ入力範囲となります。 全範囲で、 $IN-$ とは $180$ °逆位相で $IN+$ を駆動する必要があります。 |

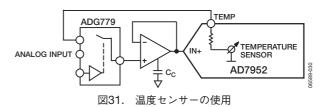

| 45   | TEMP     | AO   | 温度センサ・アナログ出力。内部リファレンス電圧が有効の場合(PDREF=PDBUF=ローレベル)、このピンはAD7952の温度に比例する電圧を出力します。「温度センサー」を参照してください。                                                                                                                                                                                                                                                            |

| 46   | REFBUFIN | AI   | リファレンス電圧バッファ入力。内部リファレンス電圧バッファで外部リファレンス電圧を使用する場合(PDBUF=ローレベル、PDREF=ハイレベル)、このピンに2.5Vを供給すると、REFピン上に5Vが出力されます。「シングルエンド/差動変換ドライバ」を参照してください。                                                                                                                                                                                                                     |

| 47   | PDREF    | DI   | 内部リファレンス電圧パワーダウン入力。<br>ローレベルのときに内部リファレンス電圧が有効になります。<br>ハイレベルのときに内部リファレンス電圧がパワーダウンされるため、外部リファレンス電<br>圧を使用する必要があります。                                                                                                                                                                                                                                         |

| 48   | PDBUF    | DI   | 内部リファレンス電圧バッファのパワーダウン入力。<br>ローレベルのときに、バッファが有効になります(内部リファレンス電圧を使用するときは<br>ローレベルに設定)。<br>ハイレベルのときに、バッファがパワーダウンされます。                                                                                                                                                                                                                                          |

REV. 0 -11-

# 代表的な性能特性

$AVDD = DVDD = 5V, \ OVDD = 5V, \ VCC = 15V, \ VEE = -15V, \ V_{REF} = 5V, \ T_A = 25\% \circ 10^{-1} \circ 10^{-1$

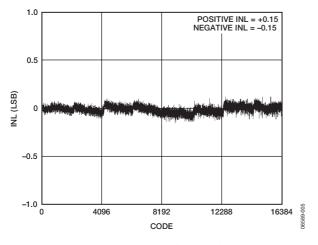

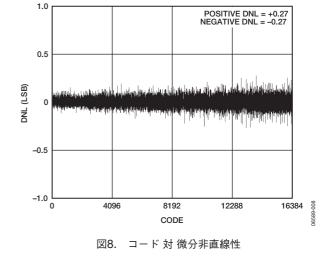

図5. コード 対 積分非直線性

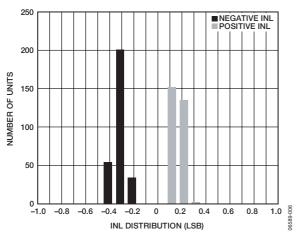

図6. 積分非直線性分布(239デバイス)

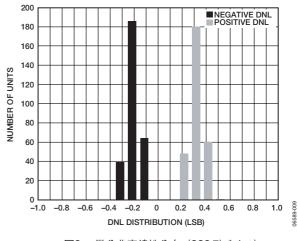

図9. 微分非直線性分布(239デバイス)

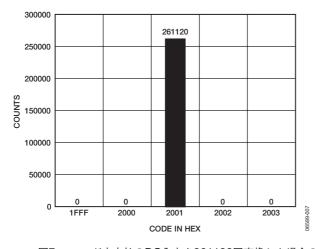

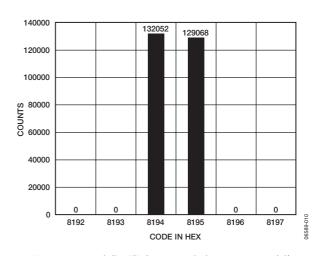

図7. コード中央値のDC入力を261120回変換した場合の ヒストグラム

図10. コード変化が発生するDC入力を261120回変換した 場合のヒストグラム

— 12 — REV. 0

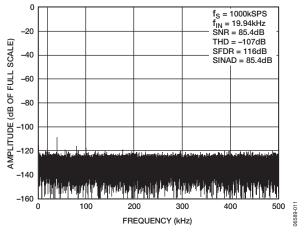

図11. FFT 20kHz

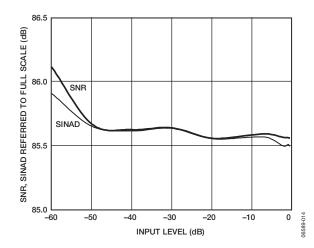

図14. 入力レベル 対 S/N比およびSINAD (フルスケール基準)

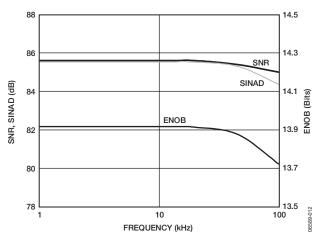

図12. S/N比、SINAD、およびENOBの周波数特性

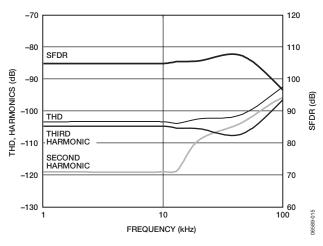

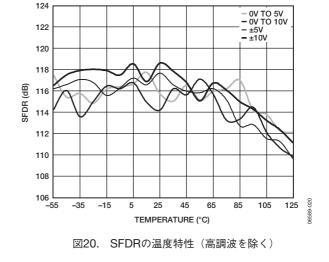

図15. THD、高調波、およびSFDRの周波数特性

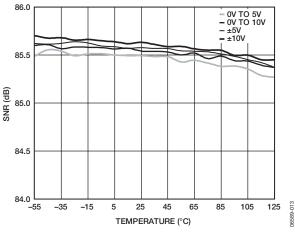

図13. S/N比の温度特性

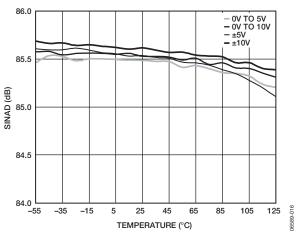

図16. SINADの温度特性

REV. 0 — 13 —

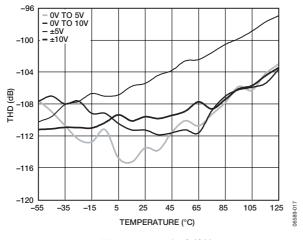

図17. THDの温度特性

図18. ゼロ/オフセット誤差および正側/負側フルスケール 誤差の温度特性、すべて25℃に正規化

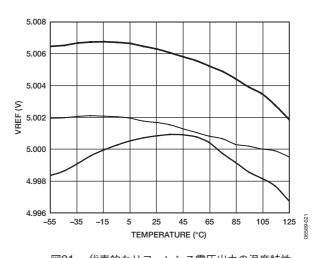

図21. 代表的なリファレンス電圧出力の温度特性 (3個のデバイス)

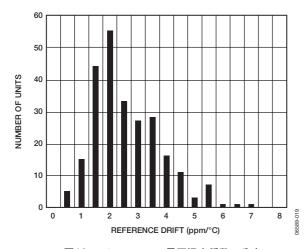

図19. リファレンス電圧温度係数の分布 (247個のデバイス)

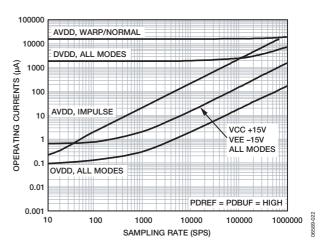

図22. サンプリング・レート 対 動作電流

— 14 — REV. 0

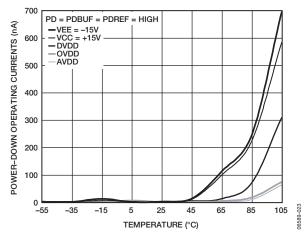

図23. パワーダウン動作電流の温度特性

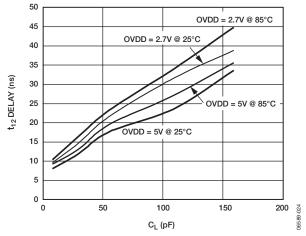

図24. 代表的な負荷容量℃ 対遅延

REV. 0 — 15 —

# 用語の説明

#### 最下位ビット(LSB)

最下位ビットすなわちLSBは、コンバータで表すことができる 最小増分です。Nビットの分解能を持つ完全差動入力ADCの場 合、LSBは次式のように電圧単位で表されます。

$$LSB(V) = \frac{V_{INp-p}}{2^N}$$

#### 積分非直線性誤差 (INL)

直線性誤差とは、負側フルスケールと正側フルスケールとを結ぶ直線と実際の各コード出力との偏差を意味します。負側フルスケールとして使用するポイントは、最初のコード遷移より0.5LSBだけ下に存在します。正側フルスケールは、最後のコード遷移より1.5LSB高いレベルと定義されます。偏差は各コードの中央と真の直線との間の距離として測定されます。

#### 微分非直線性誤差 (DNL)

理想的なADCでは、各コード遷移は1LSBだけ離れた位置で発生します。微分非直線性とは、この理論値からの最大偏差のことです。ノー・ミッシング・コードが保証される分解能として規定されることもあります。

#### バイポーラ・ゼロ誤差

理想的なミッドスケール入力電圧 (**0V**) と、ミッドスケール出力コードを生成する実際の電圧との差をいいます。

#### ユニポーラ・オフセット誤差

最初の遷移はアナログ・グラウンドより0.5LSB上のレベルで発生します。ユニポーラ・オフセット誤差は、その点からの実際の遷移の偏差をいいます。

#### フルスケール誤差

最後の遷移(ストレート・バイナリ・フォーマットで111…10から111…11)は、公称フルスケールより1.5LSB低いアナログ電圧で発生します。フルスケール誤差は、最後の遷移での理想的なレベルから実際のレベルへの偏差をLSB(またはフルスケール範囲の%値)で表し、オフセット誤差の影響を含みます。これは、オフセットの誤差の影響を含まないゲイン誤差(同じくLSB、またはフルスケール範囲の%値で表す)と密接な関連があります。

#### ダイナミック・レンジ

フルスケールのRMS値と、-60dBの入力を使用して測定したRMSノイズとの比を意味し、dB値で表します。

#### S/N比 (SNR)

実際の入力信号のRMS値と、ナイキスト周波数より下の全スペクトル成分のRMS値総和から高調波成分とDC成分を除いた値との比で、dB値で表します。

#### 全高調波歪み (THD)

最初の5つの高調波成分のRMS値の総和と、フルスケール入力信号のRMS値との比であり、dB値で表します。

#### 信号/ノイズ&歪み比(SINAD)

実際の入力信号のRMS値と、ナイキスト周波数より下の全スペクトル成分のRMS値総和(DC以外の高調波成分を含む)との比を意味し、dB値で表します。

#### スプリアスフリー・ダイナミック・レンジ (SFDR)

入力信号のRMS振幅値とピーク・スプリアス信号のRMS値との差を意味し、dB値で表します。

#### 有効ビット数(ENOB)

サイン波を入力したときの分解能の測定値です。SINADとの 関係は次式で表します。

$$ENOB = [(SINAD_{dB} - 1.76)/6.02]$$

#### アパーチャ遅延

アクイジション性能を表し、CNVST入力の立下がりエッジから、入力信号が変換用にホールドされるまでの時間を測定します。

#### 過渡応答

AD7952の入力にフルスケールのステップ関数が与えられてから、AD7952が定格精度を達成するまでに要する時間です。

#### リファレンス電圧の温度係数

リファレンス電圧の温度係数は、 $T_{MIN}$ 、 $T(25^{\circ})$ 、 $T_{MAX}$ の3点で測定されたリファレンス出力電圧( $V_{REF}$ )の最大値と最小値の差の電圧と、 $25^{\circ}$ での出力電圧の代表的なシフトから得られ、次のようにppm/ ${\circ}$ で表します。

$$TCV_{REF} ({\rm ppm/C}) = \frac{V_{REF} (Max) - V_{REF} (Min)}{V_{REF} (25\,{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{}^{\circ}{$$

ここで.

$V_{REF}$  (Max)= $T_{MIN}$ 、T(25°C)、または $T_{MAX}$ での最大 $V_{REF}$  ( $V_{REF}$  (Min)= $V_{MIN}$ 、T(25°C)、または $V_{MAX}$ での最小 $V_{REF}$  ( $V_{REF}$  ( $V_{REF}$  ( $V_{REF}$  ( $V_{REF}$  )= $V_{REF}$  ( $V_{REF}$  )= $V_{REF}$

$T_{MAX} = +85^{\circ}C$

$T_{MIN} = -40$ °C

# 動作原理

概要

AD7952は、非常に高速な低消費電力単電源動作の高精度14 ビットADCであり、逐次比較型の容量DAC(CDAC)コン バータ・アーキテクチャを採用しています。

AD7952では、変換モードまたは4種類の入力範囲のいずれか1つをいつでも設定できます。この設定は、パラレル・モード/シリアル・ハードウェア・モードで特定の入力ピンを使って行うか、あるいはシリアル・ソフトウェア・モードで設定レジスタを使って書込み専用のSPI互換インターフェースから行います。AD7952はアナログ・デバイセズの特許技術であるiCMOS高電圧プロセスで製造しており、従来の薄膜を使用せずに $0\sim+5V$ 、 $0\sim+10V$ 、 $\pm5V$ 、 $\pm10V$ の入力範囲に対応します。入力を適正な設定にロックするときは、1アクイジション・サイクル ( $t_8$ ) のみで十分です。ADCを設定し直すためにリセットを行う(電源を入れ直す)必要はありません。

AD7952は個々のアプリケーションに応じて性能を最適化するために、数種類のモードを提供しています。ワープ・モードでは1MSPS(毎秒1,000,000サンプルを変換)、ノーマル・モードでは800kSPS、インパルス・モードでは670kSPSで変換処理を行います。

AD7952はトラック/ホールドを内蔵し、パイプラインまたは 遅延のない逐次比較型ADCを提供できるため、多重化された複 数チャンネルのアプリケーションにも最適です。

ユニポーラ入力範囲の場合、AD7952は通常3つの電源VCC、AVDD(DVDDを供給可能)、およびOVDD(5V、3.3V、または2.5Vのデジタル・ロジックにインターフェース可能)を必要とします。バイポーラ入力範囲の場合は、追加のVEE電源を使用する必要があります。

このデバイスは、省スペースと柔軟性という2つの特性をあわせ持つ鉛フリーの48ピンLQFPまたは小型の48ピン、7mm×7mm LFCSPを採用しています。本製品はパラレルまたはシリアルSPI互換のインターフェースとして構成できます。

#### コンバータの動作

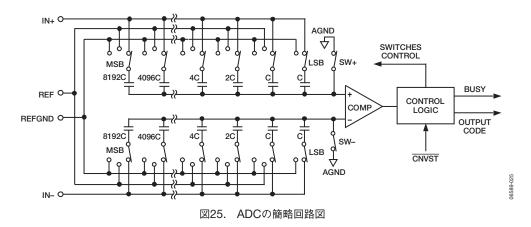

AD7952は、電荷再分配型DACを採用した逐次比較型ADCです。図25に、簡略化したADC回路図を示します。この容量性DACは、2進数ウェイトの16個のコンデンサのアレイ2個から構成されています。コンデンサは、2つのコンパレータ入力に接続されています。

アクイジション・フェーズでは、コンパレータの入力に接続さ れたアレイの端子は、SW+とSW-を経由してAGNDに接続 されます。すべての独立したスイッチはアナログ入力に接続さ れます。したがって、コンデンサ・アレイはサンプリング・コ ンデンサとして使用され、IN+入力とIN-入力上のアナログ信 号を取り込みます。アクイジション・フェーズが終了して、 CNVST入力がローレベルになると、変換フェーズが開始され ます。変換フェーズが開始されると、SW+とSW-が開きます。 次に、2つのコンデンサ・アレイが入力から切り離されて、 REFGND入力に接続されます。そうすると、アクイジショ ン・フェーズの終わりに取り込まれた、IN+とIN-の間の差動 電圧がコンパレータ入力に接続され、コンパレータは平衡しな くなります。コンデンサ・アレイの各エレメントをREFGND とREFの間で切り替えることにより、コンパレータ入力を2進 数ウェイトの電圧ステップ( $V_{REF}/2$ 、 $V_{REF}/4$  ... $V_{REF}/16384$ )で 変化させます。制御ロジックがこれらのスイッチをトグルして (MSBファースト)、コンパレータを再度平衡させます。

この処理が終了すると、制御ロジックがADC出力コードを発生して、BUSY出力をローレベルにします。

REV. 0 — 17 —

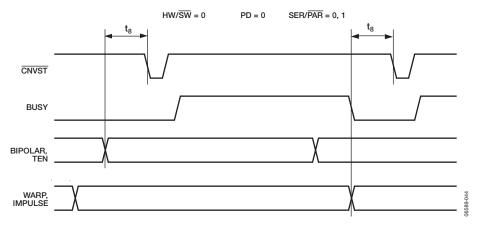

#### 動作モード

AD7952は、ワープ、ノーマル、インパルスという3つの動作モードを提供します。各モードはそれぞれ個別のアプリケーションに適用できます。モードは、入力ピンのWARPとIMPULSE、または設定レジスタを使って選択できます。ピンの詳細は、表6を参照してください。設定レジスタまたはピンを使用したモードの選択については、「ハードウェア設定」と「ソフトウェア設定」を参照してください。設定レジスタを使用する場合は、入力ピンWARPとIMPULSE(ドント・ケア)はハイレベルまたはローレベルに固定します。

### ワープ・モード

WARPをハイレベル、IMPULSEをローレベルに設定した場合は、最高速度の変換レート(最大1MSPS)が可能となります。ただし、このモードで仕様規定された精度が保証されるのは、変換と変換の間隔が1ms以内のときのみです。ワープ・モードではADCがSAR変換処理中にバックグラウンドでキャリブレーションを実行するため、変換と次の変換との間隔が1msを超えると(パワーアップ後)最初の変換の結果は無視されます。この間隔が1msを超えて最初の変換にオフセットが加わるので、キャリブレーションがドリフトする可能性があります。このモードを持つAD7952 は、高精度と高速サンプル・レートの両方が要求されるアプリケーションに最適です。

#### ノーマル・モード

WARPとIMPULSEをローレベルに、またはWARPとIMPULSEをハイレベルに設定した場合は、ハイスピード・モード(800kSPS)を使用でき、変換と変換の間の時間制限をすべてなくすことができます。このモードをサポートしている本製品は、高精度と高速サンプル・レートの両方が要求されるデータ・アクイジション・システムなどの非同期アプリケーションに最適です。

#### インパルス・モード

WARPをローレベルに、IMPULSEをハイレベルに設定した場合は、最小消費電力モードを使用でき、変換と変換の間の時間に節電を行うことができます。この消費電力モードの最大スループットは670kSPSです。このモードのときはADCが変換処理後にパワーダウンするため、本品はバッテリ駆動のアプリケーションに最適です。

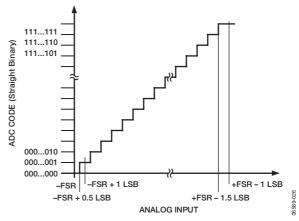

#### 伝達関数

OB/2Cデジタル入力または設定レジスタを使って、ストレート・バイナリと2の補数の2種類から出力コーディングを選択できます。各アナログ入力範囲(VIN)の理論伝達特性とデジタル出力コードについては、図26と表7を参照してください。設定レジスタを使用する場合、OB/2C入力(ドント・ケア)はハイレベルまたはローレベルに接続します。

図26. ADCの理論伝送関数

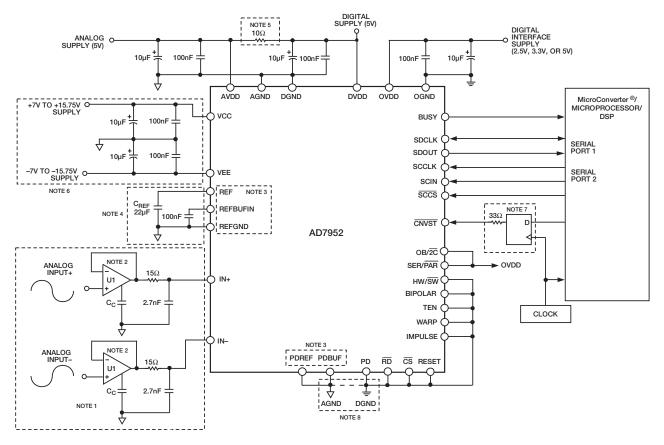

### 代表的な接続図

図27は、内部リファレンス電圧、シリアル・データ・インターフェース、シリアル設定ポートを使用するAD7952の代表的な接続図を示しています。この図に示した各回路はオプションであり、この後で説明します。

表7. 出力コードと理論入力電圧

|                  | V <sub>REF</sub> = 5 V                      |                                                       |                                          |                                           | Digital Output Code |                     |

|------------------|---------------------------------------------|-------------------------------------------------------|------------------------------------------|-------------------------------------------|---------------------|---------------------|

| Description      | $V_{IN} = 0 \text{ V to 5 V}$<br>(10 V p-p) | $V_{IN} = 0 \text{ V to } 10 \text{ V}$<br>(20 V p-p) | $V_{IN} = \pm 5 \text{ V}$<br>(20 V p-p) | $V_{IN} = \pm 10 \text{ V}$<br>(40 V p-p) | Straight Binary     | Twos Complement     |

| FSR – 1 LSB      | 4.999695 V                                  | 9.999389 V                                            | +4.999389 V                              | +9.998789 V                               | 0x3FFF <sup>1</sup> | 0x1FFF¹             |

| FSR – 2 LSB      | 4.999390 V                                  | 9.998779 V                                            | +9.998779 V                              | +9.997558 V                               | 0x3FFE              | 0x1FFE              |

| Midscale + 1 LSB | 2.500610 V                                  | 5.000610 V                                            | +1.228 mV                                | +2.442 mV                                 | 0x2001              | 0x0001              |

| Midscale         | 2.5 V                                       | 5.000000 V                                            | 0 V                                      | 0 V                                       | 0x2000              | 0x0000              |

| Midscale – 1 LSB | 2.499390 V                                  | 4.999389 V                                            | -1.228 mV                                | −2.442 mV                                 | 0x1FFF              | 0x3FFF              |

| -FSR + 1 LSB     | 610.4 μV                                    | 1.228 mV                                              | -4.999389 V                              | –9.998779 V                               | 0x0001              | 0x2001              |

| -FSR             | 0 V                                         | 0 V                                                   | -5 V                                     | -10 V                                     | 0x0000 <sup>2</sup> | 0x2000 <sup>2</sup> |

ューアナログ入力範囲より上のコードでもあります。 $(V_{\text{IN+}} - V_{\text{IN-}} は V_{\text{REF}} - V_{\text{REFGND}}$ より上)

$<sup>^2</sup>$  アナログ入力範囲より下のコードでもあります。 $(V_{\rm IN^+}-V_{\rm IN^-}$ は $V_{\rm REF}-V_{\rm REFGND}$ より下)

- NOTES

1. ANALOG INPUTS ARE DIFFERENTIAL (ANTIPHASE). SEE ANALOG INPUTS SECTION.

2. THE AD8021 IS RECOMMENDED. SEE DRIVER AMPLIFIER CHOICE SECTION.

3. THE CONFIGURATION SHOWN IS USING THE INTERNAL REFERENCE. SEE VOLTAGE REFERENCE INPUT/OUTPUT SECTION.

4. A 22µF CERAMIC CAPACITOR (X5R, 1206 SIZE) IS RECOMMENDED (FOR EXAMPLE, PANASONIC ECJ4YB1A226M).

SEE VOLTAGE REFERENCE INPUT/OUTPUT SECTION.

5. OPTIONAL, SEE POWER SUPPLIES SECTION.

6. THE VCC AND VEE SUPPLIES SHOULD BE VCC = [VIN(MAX) + 2V] AND VEE = [VIN(MIN) 2V] FOR BIPOLAR INPUT RANGES.

FOR UNIPOLAR INPUT RANGES, VEE CAN BE 0V. SEE POWER SUPPLIES SECTION.

7. OPTIONAL LOW JITTER CNVST, SEE CONVERSION CONTROL SECTION.

8. A SEPARATE ANALOG AND DIGITAL GROUND PLANE IS RECOMMENDED, CONNECTED TOGETHER DIRECTLY UNDER THE ADC.

SEE LAYOUT GUIDELINES SECTION.

図27. シリアル・インターフェースおよびシリアル・プログラマブル・ポートの代表的な接続図

#### アナログ入力

#### 入力範囲の選択

パラレル・モードとシリアル・ハードウェア・モードでは、BIPOLAR(バイポーラ)入力とTEN(10V範囲)を使って入力範囲を選択します。ピンの詳細については表6を、ピンまたは設定レジスタによるモードの選択については「ハードウェア設定」と「ソフトウェア設定」を、それぞれ参照してください。設定レジスタを使用する場合は、BIPOLAR入力とTEN入力(両方ともドント・ケア)はハイレベルまたはローレベルに接続します。

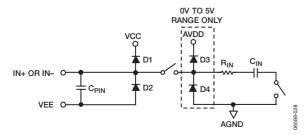

#### 入力構造

図28に、AD7952の入力構造と等価回路を示します。

図28. アナログ入力の簡略回路図

4つのダイオードD1~D4は、アナログ入力IN+とIN-のESD 保護用です。アナログ入力信号が電源レールより0.3V以上高くならないように注意する必要があります。この機能では、これらのダイオードが順方向にバイアスされて、電流が流れるようになります。ダイオードは、最大120mAの順方向バイアス電流を処理できます。たとえば、この状態は入力バッファ(U1)の電源がAVDD、VCC、VEEと異なるときなどに発生します。このような場合、短絡電流制限機能のある入力バッファを使うとデバイスを保護できます。ただし、ほとんどのオペアンプの短絡電流は100mA未満です。D3およびD4は0~5Vの範囲でのみ使用され、高い電圧範囲でスイッチングするアプリケーションでは追加の保護が可能です。

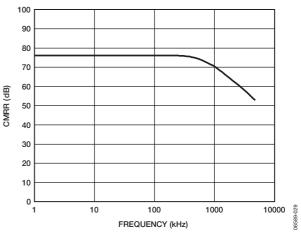

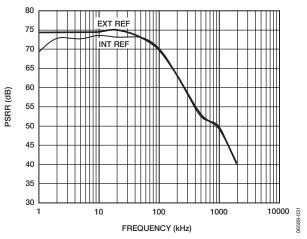

このアナログ入力回路により、IN+とIN-間の差動信号をサンプリングできます。この差動入力の採用により、両入力に共存する小信号が除去されます。図29に代表的なCMRRの周波数特性を示します。

たとえば、IN-を使ってリモート信号グラウンドを検出すると、センサーとローカルADCグラウンド間のグラウンド電位差をなくすことができます。

図29. アナログ入力CMRRの周波数特性

AC信号のアクイジション・フェーズでは、アナログ入力IN+とIN-のインピーダンスは、 $R_{\rm IN}$ と $C_{\rm IN}$ の直列接続で構成された 回路とコンデンサ $C_{\rm PIN}$ との並列組み合わせとしてモデル化できます。 $C_{\rm PIN}$ はもともとピン容量です。 $R_{\rm IN}$ は70 $\Omega$ (typ)で、いくつかの直列抵抗とスイッチのオン抵抗で構成される集中定数素子です。 $C_{\rm IN}$ は主にADCサンプリング・コンデンサとして機能し、選択した入力範囲に依存します。 $0\sim5$ Vの範囲では48pF (typ)、 $0\sim10$ Vおよび±5Vの範囲では24pF(typ)、±10Vの範囲では12pF(typ)となります。スイッチが開かれている変換フェーズでは、入力インピーダンスは $C_{\rm PIN}$ に制限されます。

AD7952の入力インピーダンスはきわめて高いため、低インピーダンス信号源から直接駆動してもゲイン誤差はありません。図27に示すように、アンプ出力とADCアナログ入力との間に外付けの単極RCフィルタを挿入して、AD7952アナログ入力回路によるノイズ・フィルタ処理を強化できます。ただし、ソース・インピーダンスが大きい場合は、AC性能、特に全高調波歪み(THD)に大きな影響を与えます。最大ソース・インピーダンスは、許容可能なTHDの大きさに依存します。THDはソース・インピーダンスと最大入力周波数の関数となっており、それに応じて劣化します。

#### ドライバ・アンプの選択

AD952の駆動は簡単ですが、ドライバ・アンプは次の条件を満たす必要があります。

- マルチチャンネル、多重化アプリケーションの場合、ドライバ・アンプとAD7952アナログ入力回路はともに、コンデンサ・アレイのフルスケール・ステップに対して14ビット・レベル (0.006%) でセトリングできる必要があります。アンプのデータシートでは、一般に0.1~0.01%でのセトリングが規定されています。14ビット・レベルでのセトリング時間とは大幅に異なることがあるため、ドライバを選択する前に確認する必要があります。オペアンプAD8021は超低ノイズと大きなゲイン帯域幅を兼ね備えているため、最大13のゲインで使用するときでも、このセトリング時間条件を満たします。

- AD7952の過渡ノイズ性能とS/N比を維持するためは、ドライバ・アンプによって生じるノイズをできるだけ低く抑える必要があります。ドライバから発生するノイズは、外付けの単極ローパス・フィルタによって除去されます(図27)。アンプに起因するS/N比の低下は、次式で求められます。

$SNR_{LOSS} =$

$$20 \log \left( \frac{V_{NADC}}{\sqrt{V_{NADC}^2 + \frac{\pi}{2} f_{-3 \text{dB}} (Ne_{N+})^2 + \frac{\pi}{2} f_{-3 \text{dB}} (Ne_{N-})^2}} \right)$$

ここで、

$V_{NADC}$ はADCのノイズであり、次式で表されます。

$$V_{NADC} = \frac{\frac{2V_{INp-p}}{2\sqrt{2}}}{\frac{\frac{SNR}{20}}{10^{\frac{20}{20}}}}$$

$f_{-3dB}$ は、入力フィルタのカットオフ周波数です (3.9MHz)。 Nは、アンプのノイズ係数です (バッファ構成の場合は1)。

$e_{N+}$ と $e_{N-}$ は、 $\mathbf{IN}+$ と $\mathbf{IN}-$ に接続されたオペアンプの等価入力電圧ノイズ密度( $\mathbf{nV}/\sqrt{\mathbf{Hz}}$ )です。

この近似式は、アンプ周りに使用される抵抗が小さいときに使用できます。抵抗が大きい場合は、ノイズ寄与も二乗和平方根になります。

• ドライバには、AD7952のTHD性能に見合うTHD性能が必要です。図15に、ドライバが満たすべきTHDの周波数特性を示します。

AD8021はこれらの条件を満たしているため、ほとんどすべてのアプリケーションに適しています。AD8021では優れた直線性を得るために、NPOセラミックやマイカ・タイプのような10pFの外付け補償コンデンサが必要となります。さらに、ゲイン+1の非反転構成を推奨しますが、これを使うと最適なS/N比が得られます。

デュアル・バージョンが必要でゲイン=1を使用する場合は、AD8022も使用できます。高周波(100kHz超)性能を必要としないアプリケーションでは、AD829も使用できます。ゲイン=1のアプリケーションでは、82pFの補償コンデンサが必要です。低周波アプリケーションで低バイアス電流が必要な場合は、AD8610を使用できます。

AD7952 は大きな形状の高電圧入力スイッチを使用するため、最大のフルパワー帯域幅でアンプを使用するときに最高の直線性性能が得られます。アンプにADCの広いダイナミック・レンジを使用させると、直線性誤差は大きくなります。高い分解能を必要とするアプリケーションの場合は、AD7952を駆動するユニティ・フォロワの前にゲインを持つアンプを追加する必要があります。推奨のオペアンプについては、表8を参照してください。

表8. 推奨ドライバ・アンプ

| Amplifier         | Typical Application                                                            |

|-------------------|--------------------------------------------------------------------------------|

| AD829             | ±15 V supplies, very low noise, low frequency                                  |

| AD8021            | ±12 V supplies, very low noise, high frequency                                 |

| AD8022            | ±12 V supplies, very low noise, high                                           |

|                   | frequency, dual                                                                |

| ADA4922-1         | ±12 V supplies, low noise, high frequency, single-ended-to-differential driver |

| AD8610/<br>AD8620 | ±13 V supplies, low bias current, low frequency, single/dual                   |

#### シングルエンド/差動変換ドライバ

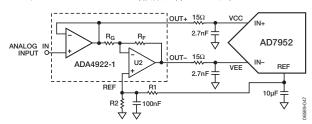

シングルエンド・ソースの場合、ADA4922-1のようなシングルエンド/差動変換ドライバを使うと、AD7592の差動駆動が可能になります。 $R=15\Omega$ とC=2.7nFを使用する単極フィルタでは、3.9MHzのコーナー周波数が得られます。

図30. ADA4922-1を使用したシングルエンド/差動 変換ドライバ

5Vと10Vのユニポーラ入力範囲の場合は、内部(または外部)リファレンス電圧源を使ってU2をレベル・シフトし、入力スパンを調整します。外付けのリファレンス電圧を使用する場合は、R1/R2の値を小さくして抵抗のジョンソン・ノイズ( $1.29E-10\times\sqrt{R}$ )を減少させます。  $\pm 5$ Vと $\pm 10$ Vのバイポーラ入力範囲の場合は、同相電圧が0Vとなるためリファレンス電圧の接続は不要です。 R1/R2の差動入力範囲については、表9を参照してください。

表9. R1/R2構成

| Input Range (V) | R1 (Ω) | R2 (Ω) | Common-Mode Voltage (V) |

|-----------------|--------|--------|-------------------------|

| 5               | 2.5 k  | 2.5 k  | 2.5                     |

| 10              | 2.5 k  | Open   | 5                       |

| ±5, ±10         |        | 100    | 0                       |

この回路は、表8の推奨低ノイズ・アンプを使ってディスクリートで構成することもできます。コンバータのS/N比を維持するときは、抵抗 $R_F$ および $R_G$ を小さく抑える必要があります。

REV. 0 — 21 —

#### リファレンス電圧入出力

AD7952では、温度ドリフトが非常に小さい内部リファレンス 電圧、外部リファレンス電圧、または外付けバッファ付きリファレンス電圧を選択できます。

AD7952の内部リファレンス電圧の性能は非常に優れているため、ほとんどすべてのアプリケーションで使用できます。ただし、直線性性能は外部リファレンス電圧でのみ保証されます。

# 内部リファレンス電圧(REF=5V)(PDREF=ローレベル、PDBUF=ローレベル)

内部リファレンス電圧を使用する場合は、PDREF入力とPDBUF入力をローレベルにします。これによって内蔵のバンド・ギャップ・リファレンス電圧、バッファ、およびTEMPセンサが有効となり、REFピン上に5.00Vのリファレンス電圧が出力されます。

内部リファレンス電圧は、 $5.000V\pm35$ mVに温度補償されています。リファレンス電圧は、ドリフトが3ppm/C(typ)に調整されています。このドリフト特性(typ)を図19に示します。

#### 外部2.5Vリファレンス電圧と内部バッファ(REF=5V) (PDREF=ハイレベル、PBBUF=ローレベル)

内部バッファ付きの外部リファレンス電圧を使用するときは、PDREFをハイレベル、PDBUFをローレベルにする必要があります。これにより、内部リファレンス電圧がパワーダウンされ、REFBUFINに2.5Vリファレンス電圧が入力されて、REFピン上に5Vが出力されます。内部リファレンス電圧バッファは、一般にマルチコンバータ・アプリケーションで必要となります。

### 外部5Vリファレンス電圧(PDREF=ハイレベル、 PRBUF=ハイレベル)

外部リファレンス電圧を直接REFピン上で使うときは、PDREFとPDBUFは両方ともハイレベルにする必要があります。PDREFとPDBUFは、それぞれ内部リファレンス電圧と内部リファレンス電圧バッファをパワーダウンします。ドリフト性能を高めるために、ADR445またはADR435などの外部リファレンス電圧の使用を推奨します。

#### リファレンス電圧のデカップリング

内部リファレンス電圧と外部リファレンス電圧のいずれを使用しても、AD7952のリファレンス電圧入力(REF)には動的入力インピーダンスがあります。したがって、REF入力とREFGND入力との間に効率的なデカップリングを行い、低インピーダンス信号源を使用して駆動する必要があります。デカップリングは使用するリファレンス電圧によって異なりますが、通常は、寄生インダクタンスを最小に抑えた、REFとREFGNDに接続された低ESRコンデンサから構成されます。内部リファレンス電圧を使用する場合や、外部リファレンス電圧(ADR445/ADR435)を使用する場合は、 $22\mu F$ (X5R、1206サイズ)のセラミック・チップ・コンデンサ(または $47\mu F$ のタンタル・コンデンサ)が適しています。

AD7952の性能には、リファレンス電圧デカップリングの配置も重要です。デカップリング・コンデンサは、ADCと同じ側に太いPCボード・パターンでREFピンに接続する必要があります。また、REFGNDを最短距離でリファレンス電圧のデカップリング・コンデンサに接続し、複数のビアを使ってアナログ・グラウンド・プレーンに接続します。

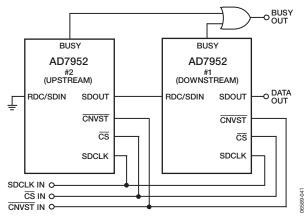

複数のAD7952デバイスまたは他のPulSARデバイスを使用するアプリケーションでは、外付けの2.5Vリファレンス電圧のバッファリングに内部リファレンス電圧バッファを使用することが推奨されます。