# 2チャンネル、2.35~5.25V 1MSPS、10/12ビットADC

# AD7912/AD7922

### 特長

高速スループット・レート:1MSPS 2.35~5.25Vの $V_{DD}$ に対して仕様を規定

低消費電力:

4.8mW (typ) (1MSPSで3V電源時) 15.5mW (typ) (1MSPSで5V電源時)

広い入力帯域幅:

最小値71dBのS/N比(100kHzの入力周波数時)

柔軟性に優れたパワー/シリアル・クロック速度マネジメント パイプライン遅延なし

高速シリアル・インターフェース:

SPI®/QSPI™/MICROWIRE™/DSP互換 スタンバイ・モード時の消費電流:1µA(max)

デイジーチェーン接続モード

8ピンTSOTパッケージ 8ピンMSOPパッケージ

### アプリケーション

バッテリ駆動システム:

携帯情報端末

医療用計測器

移動体通信

計測および制御システム

データ・アクイジション・システム

高速モデム

光センサー

#### 概要

AD7912/AD7922<sup>1</sup>は、それぞれ10ビットおよび12ビットの高速、低消費電力の2チャンネル逐次比較型A/Dコンバータ (SAR ADC)です。各デバイスは2.35~5.25Vの電圧範囲の単電源で動作し、最大1MSPSまでのスループット・レートが可能です。いずれも、6MHzを超える入力周波数を扱うことができる低ノイズ、広帯域幅のトラック&ホールド・アンプを内蔵しています。

$\overline{\mathbf{CS}}$ とシリアル・クロックを使用して変換プロセスとデータ・アクイジション動作を制御することにより、マイクロプロセッサやDSPとのインターフェースが可能です。変換レートは、 $\mathbf{SCLK}$ 信号によって決まります。入力信号は $\overline{\mathbf{CS}}$ の立下がりエッジでサンプリングし、変換もこの時点で開始します。変換するチャンネルは $\mathbf{DIN}$ ピンによって選択し、動作モードは $\overline{\mathbf{CS}}$ で制御します。 $\mathbf{DOUT}$ ピンから出力するシリアル・データ・ストリームにはチャンネル識別ビットとモード識別ビットがあり、変換されたチャンネルと現在選択されている動作モードに関する情報が得られます。

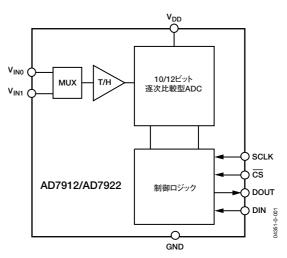

### 機能ブロック図

図1

複数のAD7912/AD7922はデイジーチェーン接続が可能です。AD7912/AD7922には、チェーンの中の複数のADCから変換結果を読み出すことができるデイジーチェーン接続モードがあります。AD7912/AD7922は最新の設計技術により、高速スループット・レートで消費電力を非常に低く抑えます。リファレンス電圧を $V_{DD}$ から内部で取るため、このADCは最大限に広いダイナミック入力レンジを利用できます。

### 製品のハイライト

- 1. TSOTパッケージの2チャンネル、1MSPS、10/12ビット ADC。

- 2. 低い消費電力で高速スループット・レートを実現。

- 3. 柔軟性に優れたパワー/シリアル・クロック速度マネジメント。変換レートは、シリアル・クロックによって決まります。低いスループット・レートでパワー効率を最大限に高めるパワーダウン・モードもあります。パワーダウン・モードに設定し、変換動作を実行しないときに平均消費電力を低減できます。パワーダウン・モード時の消費電流は最大1μA、代表値で50nAです。

- 4. デイジーチェーン接続モード。

- 5. パイプライン遅延なし。

標準の逐次比較型ADCで、CS入力を使用し、変換制御を一度オフにする方法でサンプリング時間を高精度に制御します。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。© 2004 Analog Devices, Inc. All rights reserved.

REV. 0

本 社/〒105-6891 東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 電話03 (5402) 8200

<sup>1</sup> 米国特許番号6,681,332によって保護されています。

# 目次

| 仕様           | DIN入力               | 17 |

|--------------|---------------------|----|

| AD7912の仕様3   | DOUT出力              |    |

| AD7922の仕様5   | 動作モード               | 18 |

| タイミング仕様7     | ノーマル・モード            | 18 |

| タイミング図7      | パワーダウン・モード          | 18 |

| タイミング例8      | パワーアップ時間            | 20 |

| 絶対最大定格       | デイジーチェーン接続モード       | 20 |

| ESDに関する注意9   | デイジーチェーン接続の例        | 22 |

| ピン配置と機能の説明10 | 消費電力とスループット・レートの関係  | 24 |

| 用語の説明        | シリアル・インターフェース       | 25 |

| 代表的な性能特性13   | マイクロプロセッサとのインターフェース | 26 |

| 回路情報         | アプリケーションのヒント        | 28 |

| コンバータの動作15   | グラウンディングとレイアウト      | 28 |

| ADCの伝達関数15   | AD7912/AD7922の性能評価  | 29 |

| 代表的な接続図16    | 外形寸法                | 30 |

| アナログ入力16     | オーダー・ガイド            | 30 |

| デジタル入力17     |                     |    |

**改訂履歴** リビジョン0:初版

# 仕様

# AD7912の仕様

Aグレードの温度範囲は $-40\sim+85$ ℃です。 特に指示がない限り、 $V_{DD}\!=\!2.35\sim\!5.25V$ 、 $f_{SCLK}\!=\!18MHz$ 、 $f_{SAMPLE}\!=\!1MSPS$ 、 $T_{A}\!=\!T_{MIN}\!\sim\!T_{MAX}$ です。

#### 表1

| パラメータ                                                                                                                                                                                                                       | Aグレード <sup>1</sup>                                                                                                       | 単位                                                                                             | テスト条件/備考                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>ダイナミック性能</b><br>信号/ノイズ&歪み (SINAD) <sup>2</sup><br>全高調波歪み (THD) <sup>2</sup><br>ピーク高調波または<br>スプリアス・ノイズ (SFDR) <sup>2</sup>                                                                                                | 61<br>-71<br>-72                                                                                                         | dB (min)<br>dB (max)<br>dB (max)                                                               | f <sub>IN</sub> =100kHzの正弦波                                                                                                                                                                                                                               |

| 相互変調歪み(IMD) <sup>2</sup> 2次項 3次項 アパーチャ遅延 アパーチャ・ジッタ チャンネル間アイソレーション <sup>2</sup> フルパワー帯域幅                                                                                                                                     | -82<br>-83<br>10<br>30<br>90<br>8.5                                                                                      | dB (typ) dB (typ) ns (typ) ps (typ) dB (typ) MHz (typ) MHz (typ)                               | fa=100.73 kHz, fb=90.7 kHz<br>fa=100.73 kHz, fb=90.7 kHz<br>@3dB<br>@0.1dB                                                                                                                                                                                |

| DC精度         分解能       積分非直線性²         微分非直線性²       オフセット誤差²         オフセット誤差マッチング²、³       ゲイン誤差²         ゲイン誤差マッチング²、³       総合未調整誤差 (TUE) ²                                                                              | 10<br>±0.5<br>±0.5<br>±0.5<br>±0.3<br>±0.5<br>±0.3<br>±0.5                                                               | ピット<br>LSB (max)<br>LSB (max)<br>LSB (max)<br>LSB (max)<br>LSB (max)<br>LSB (max)<br>LSB (max) | 10ビットまでノー・ミスコードを保証                                                                                                                                                                                                                                        |

| アナログ入力<br>入力電圧範囲<br>DC漏れ電流<br>入力容量                                                                                                                                                                                          | $0 \sim V_{DD} \\ \pm 0.3 \\ 20$                                                                                         | V<br>μA (max)<br>pF (typ)                                                                      |                                                                                                                                                                                                                                                           |

| ロジック入力 入力ハイ電圧( $V_{\rm INH}$ ) 入力ロー電圧( $V_{\rm INL}$ )  入力電流( $I_{\rm IN}$ 、 $\overline{\rm SCLK}$ ピン) 入力電流( $I_{\rm IN}$ 、 $\overline{\rm CS}$ ピン) 入力電流( $I_{\rm IN}$ 、 $\overline{\rm DIN}$ ピン) 入力容量( $C_{\rm IN}$ ) $^3$ | $\begin{array}{c} 0.7 \ (V_{DD}) \\ 2 \\ 0.3 \\ 0.2 \ (V_{DD}) \\ 0.8 \\ \pm 0.3 \\ \pm 0.3 \\ \pm 0.3 \\ 5 \end{array}$ | V (min) V (min) V (max) V (max) V (max)  HA (max)  HA (max)  HA (max)  HA (max)  HA (max)      | $2.35$ V $\leq$ V <sub>DD</sub> $\leq$ 2.7V<br>$2.7$ V $<$ V <sub>DD</sub> $\leq$ 5.25V<br>V <sub>DD</sub> =2.35V<br>$2.35$ V $<$ V <sub>DD</sub> $\leq$ 2.7V<br>$2.7$ V $<$ V <sub>DD</sub> $\leq$ 5.25V<br>代表値8nA、V <sub>IN</sub> =0VまたはV <sub>DD</sub> |

| ロジック出力       出力ハイ電圧(V <sub>OH</sub> )       出力ロー電圧(V <sub>OL</sub> )       フローティング状態漏れ電流       フローティング状態出力容量³       出力コーディング                                                                                                | $V_{DD} - 0.2$ $0.2$ $\pm 0.3$ $5$                                                                                       | V (min)<br>V (max)<br>µA (max)<br>pF (max)                                                     | $I_{SOURCE} = 200\mu A, V_{DD} = 2.35 \sim 5.25V$ $I_{SINK} = 200\mu A$                                                                                                                                                                                   |

REV. 0 — 3 —

| パラメータ                                                   | Aグレード <sup>1</sup> | 単位                   | テスト条件/備考                                              |

|---------------------------------------------------------|--------------------|----------------------|-------------------------------------------------------|

| <b>変換レート</b> 変換時間 トラック&ホールド・アンプの アクイジション時間 <sup>2</sup> | 777<br>290         | ns (max)<br>ns (max) | SCLKが18MHzのときに14 SCLKサイクル                             |

| スループット・レート                                              | 1                  | MSPS (max)           |                                                       |

| 電源条件                                                    |                    |                      |                                                       |

| $V_{ m DD}$                                             | 2.35/5.25          | V (min/max)          |                                                       |

| ${ m I}_{ m DD}$                                        |                    |                      | デジタル入力 $=0$ Vまたは $\mathrm{V}_{\mathrm{DD}}$           |

| ノーマル・モード(スタティック時)                                       | 3                  | mA (typ)             | $V_{DD}$ =4.75~5.25V、SCLKオンまたはオフ                      |

|                                                         | 1.5                | mA (typ)             | $V_{DD}$ =2.35~3.6V、SCLKオンまたはオフ                       |

| ノーマル・モード (動作時)                                          | 4                  | mA (max)             | $V_{DD}$ =4.75~5.25V, $f_{SAMPLE}$ =1MSPS             |

|                                                         | 2                  | mA (max)             | $V_{DD}=2.35\sim3.6V$ , $f_{SAMPLE}=1MSPS$            |

| フル・パワーダウン・モード                                           | 1                  | μA (max)             | SCLKオンまたはオフ、代表値50nA                                   |

| (スタティック時)                                               |                    |                      |                                                       |

| フル・パワーダウン・モード                                           | 0.48               | mA (typ)             | $V_{DD}=5V$ , $f_{SCLK}=18MHz$ , $f_{SAMPLE}=100kSPS$ |

| (ダイナミック時)                                               | 0.26               | mA (typ)             | $V_{DD}=3V$ , $f_{SCLK}=18MHz$ , $f_{SAMPLE}=100kSPS$ |

| 消費電力4                                                   |                    |                      |                                                       |

| ノーマル・モード (動作時)                                          | 20                 | mW (max)             | $V_{DD}=5V$ , $f_{SAMPLE}=1MSPS$                      |

|                                                         | 6                  | mW (max)             | $V_{DD}=3V$ , $f_{SAMPLE}=1MSPS$                      |

| フル・パワーダウン・モード                                           | 5                  | μW (max)             | $V_{DD}=5V$                                           |

$<sup>^1</sup>$   $V_{H}$  = 1.9V (min) ,  $V_{L}$  = 0.1V (max) で、 $V_{DD}$  = 2V から動作する条件を適用。  $^2$  「用語の説明」を参照。  $^3$  特性評価によって保証。  $^4$  「消費電力とスループット・レートの関係」を参照。

# AD7922の仕様

Aグレードの温度範囲は $-40\sim+85$ ℃です。 特に指示がない限り、 $V_{DD}\!=\!2.35\sim\!5.25V$ 、 $f_{SCLK}\!=\!18MHz$ 、 $f_{SAMPLE}\!=\!1MSPS$ 、 $T_{A}\!=\!T_{MIN}\!\sim\!T_{MAX}$ です。

#### 表2

| パラメータ                                    | Aグレード <sup>1</sup>                            | 単位        | テスト条件/備考                             |

|------------------------------------------|-----------------------------------------------|-----------|--------------------------------------|

| ダイナミック性能                                 |                                               |           | f <sub>IN</sub> =100 kHzの正弦波         |

| 信号/ノイズ&歪み(SINAD) <sup>2</sup>            | 70                                            | dB (min)  |                                      |

|                                          | 72                                            | dB (typ)  |                                      |

| 信号対ノイズ比 (SNR) <sup>2</sup>               | 71                                            | dB (min)  |                                      |

|                                          | 72.5                                          | dB (typ)  |                                      |

| 全高調波歪み (THD) <sup>2</sup>                | -81                                           | dB (typ)  |                                      |

| ピーク高調波またはスプリアス・                          | -84                                           | dB (typ)  |                                      |

| ノイズ (SFDR) <sup>2</sup>                  |                                               |           |                                      |

| 相互変調歪み (IMD) <sup>2</sup>                |                                               |           |                                      |

| 2次項                                      | -84                                           | dB (typ)  | fa=100.73 kHz, fb=90.72 kHz          |

| 3次項                                      | -86                                           | dB (typ)  | fa=100.73 kHz, fb=90.72 kHz          |

| アパーチャ遅延                                  | 10                                            | ns (typ)  | ,                                    |

| アパーチャ・ジッタ                                | 30                                            | ps (typ)  |                                      |

| チャンネル間アイソレーション <sup>2</sup>              | 90                                            | dB (typ)  |                                      |

| フルパワー帯域幅                                 | 8.5                                           | MHz (typ) | @3dB                                 |

| у у с у прожущ                           | 1.5                                           | MHz (typ) | @0.1dB                               |

| DOM: #                                   |                                               |           |                                      |

| DC精度                                     | 12                                            | 18 1      |                                      |

| 分解能                                      | 12                                            | ビット       |                                      |

| 積分非直線性 <sup>2</sup>                      | ±1.5                                          | LSB (max) | $V_{DD} = 2.35 \sim 3.6 V$           |

| object. De la relation                   | $\pm 0.7$                                     | LSB (typ) | $V_{DD} = 4.75 \sim 5.25 V$          |

| 微分非直線性 <sup>2</sup>                      |                                               |           | 12ビットまでノー・ミスコードを保証                   |

|                                          | -0.9/+1.5                                     | LSB (max) | $V_{DD} = 2.35 \sim 3.6V$            |

|                                          | -0.7/+1.2                                     | LSB (typ) | $V_{DD} = 4.75 \sim 5.25 V$          |

| オフセット誤差 <sup>2</sup>                     | ±1                                            | LSB (max) | $V_{DD} = 2.35 \sim 3.6 V$           |

|                                          | $\pm 0.1$                                     | LSB (typ) | $V_{DD} = 4.75 \sim 5.25 V$          |

| オフセット誤差マッチング <sup>2、3</sup>              | $\pm 0.5$                                     | LSB (max) | $V_{DD} = 2.35 \sim 3.6 V$           |

|                                          | $\pm 0.02$                                    | LSB (typ) | $V_{DD} = 4.75 \sim 5.25 V$          |

| ゲイン誤差 <sup>2</sup>                       | ±2                                            | LSB (max) | $V_{DD} = 2.35 \sim 3.6 V$           |

|                                          | $\pm 0.5$                                     | LSB (typ) | $V_{DD} = 4.75 \sim 5.25 V$          |

| ゲイン誤差マッチング <sup>2、3</sup>                | ±1                                            | LSB (max) | $V_{DD} = 2.35 \sim 3.6 V$           |

|                                          | $\pm 0.2$                                     | LSB (typ) | $V_{DD} = 4.75 \sim 5.25 V$          |

| 総合未調整誤差(TUE) <sup>2</sup>                | ±1.5                                          | LSB (max) | $V_{DD} = 2.35 \sim 3.6 V$           |

|                                          | ±0.5                                          | LSB (typ) | $V_{DD} = 4.75 \sim 5.25 V$          |

|                                          |                                               |           |                                      |

| 入力電圧範囲                                   | $0 \sim V_{DD}$                               | V         |                                      |

| DC漏れ電流                                   | $\pm 0.3$                                     | μA (max)  |                                      |

| 入力容量                                     | $\begin{bmatrix} \pm 0.3 \\ 20 \end{bmatrix}$ | pF (typ)  |                                      |

|                                          | 20                                            | pr (typ)  |                                      |

| ロジック入力                                   | 0.7 (31)                                      | X7 / · ·  | 2.2571 < 71 < 2.571                  |

| 入力ハイ電圧(V <sub>INH</sub> )                | $0.7 (V_{DD})$                                | V (min)   | $2.35V \le V_{DD} \le 2.7V$          |

| 7 L                                      | 2                                             | V (min)   | $2.7V < V_{DD} \le 5.25V$            |

| 入力ロー電圧(V <sub>INL</sub> )                | 0.3                                           | V (max)   | $V_{DD}=2.35V$                       |

|                                          | $0.2 (V_{DD})$                                | V (max)   | $2.35V < V_{DD} \le 2.7V$            |

|                                          | 0.8                                           | V (max)   | $2.7V < V_{DD} \le 5.25V$            |

| 入力電流(I <sub>IN</sub> 、SCLKピン)            | $\pm 0.3$                                     | μA (max)  | 代表値 $8nA$ 、 $V_{IN}=0V$ または $V_{DD}$ |

| 入力電流(I <sub>IN</sub> 、 <del>CS</del> ピン) | $\pm 0.3$                                     | μA (max)  |                                      |

| 入力電流(I <sub>IN</sub> 、DINピン)             | $\pm 0.3$                                     | μA (max)  |                                      |

| 入力容量 (C <sub>IN</sub> ) <sup>3</sup>     | 5                                             | pF (max)  |                                      |

REV. 0 — 5 —

| パラメータ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Aグレード <sup>1</sup>                                  | 単位                                                                               | テスト条件/備考                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ロジック出力<br>出力ハイ電圧( $V_{OH}$ )<br>出力ロー電圧( $V_{OL}$ )<br>フローティング状態漏れ電流<br>フローティング状態出力容量 $^3$<br>出力コーディング                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{DD} = 0.2$ 0.2 $\pm 0.3$ 5                      | V (min)<br>V (max)<br>µA (max)<br>pF (max)                                       | $I_{SOURCE}$ =200 μA ; $V_{DD}$ =2.35~5.25V $I_{SINK}$ =200 μA                                                                                                                                                                                                                                                                                                                                 |

| <b>変換レート</b> 変換時間 トラック&ホールド・アンプの アクイジション時間 <sup>2</sup> スループット・レート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 888<br>290                                          | ns (max)<br>ns (max)<br>MSPS (max)                                               | SCLKが18MHzのときに16 SCLKサイクル<br>「シリアル・インターフェース」を参照。                                                                                                                                                                                                                                                                                                                                               |

| 電源条件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                   | Wist's (max)                                                                     | 「フリアル・インノーノエーハ」を参照。                                                                                                                                                                                                                                                                                                                                                                            |

| $V_{DD}$ $I_{DD}$ | 2.35/5.25<br>3<br>1.5<br>4<br>2<br>1<br>0.5<br>0.28 | MA (typ) mA (typ) mA (max) mA (max) mA (max) μA (max) mA (typ) mA (typ) mA (typ) | デジタル入力=0Vまたは $V_{DD}$ $V_{DD}$ =4.75~5.25 $V$ 、SCLKオンまたはオフ $V_{DD}$ =2.35~3.6 $V$ 、SCLKオンまたはオフ $V_{DD}$ =4.75~5.25 $V$ 、 $f_{SAMPLE}$ =1MSPS $V_{DD}$ =2.35~3.6 $V$ 、 $f_{SAMPLE}$ =1MSPS SCLKオンまたはオフ、代表値50nA $V_{DD}$ =5 $V$ 、 $f_{SCLK}$ =18MHz、 $f_{SAMPLE}$ =100kSPS $V_{DD}$ =3 $V$ 、 $f_{SCLK}$ =18MHz、 $f_{SAMPLE}$ =100kSPS $V_{DD}$ =5 $V$ 、 $f_{SCLK}$ =18MHz、 $f_{SAMPLE}$ =100kSPS |

| フル・パワーダウン・モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6 5 3                                               | mW (max)<br>µW (max)<br>µW (max)                                                 | $V_{DD} = 3V$ , $f_{SAMPLE} = 1MSPS$<br>$V_{DD} = 5V$<br>$V_{DD} = 3V$                                                                                                                                                                                                                                                                                                                         |

$<sup>^1</sup>$   $V_{IH}$  = 1.9V (min) 、  $V_{IL}$  = 0.1V (max) で、  $V_{DD}$  = 2V から動作する条件を適用。  $^2$  「用語の説明」を参照。

3 特性評価によって保証。

4 「消費電力とスループット・レートの関係」を参照。

### タイミング仕様

特性評価によって保証しています。

tr=tf=5ns( $V_{DD}$ の $10\sim90\%$ )ですべての入力信号を規定し、1.6Vの電圧レベルから時間を測定しています。 特に指示がない限り、 $V_{DD}$ =2.35~5.25V、 $T_{A}$ = $T_{MIN}$ ~ $T_{MAX}$ です。

### 表3

| パラメータ                              | T <sub>MIN</sub> 、T <sub>MAX</sub> 時の制限値 | 単位                     | 説明                                            |

|------------------------------------|------------------------------------------|------------------------|-----------------------------------------------|

| f <sub>SCLK</sub> <sup>1</sup>     | 10                                       | kHz (min) <sup>2</sup> |                                               |

|                                    | 18                                       | MHz (max)              |                                               |

| $t_{CONVERT}$                      | $16 \times t_{SCLK}$                     |                        | AD7922                                        |

|                                    | $14 \times t_{SCLK}$                     |                        | AD7912                                        |

| $t_{QUIET}$                        | 30                                       | ns (min)               | バス開放の後、次の変換が開始されるまでに必要な最小の静止時間                |

| $t_1$                              | 15                                       | ns (min)               | 最小のCSパルス幅                                     |

| $t_2$                              | 10                                       | ns (min)               | CSからSCLKまでのセットアップ時間                           |

| $t_3^{\ 3}$                        | 30                                       | ns (max)               | <del>CS</del> からDOUTスリーステートがディスエーブルになるまでの遅延時間 |

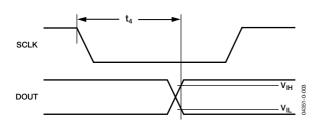

| $t_4^{\ 3}$                        | 45                                       | ns (max)               | SCLKの立下がりエッジ後のDOUTアクセス時間                      |

| $t_5$                              | $0.4 t_{SCLK}$                           | ns (min)               | SCLKロー・パルス幅                                   |

| $t_6$                              | 0.4 t <sub>SCLK</sub>                    | ns (min)               | SCLKハイ・パルス幅                                   |

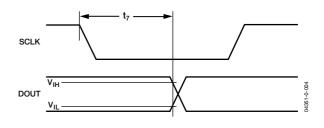

| $t_{7}^{4}$                        | 10                                       | ns (min)               | SCLKからDOUT有効までのホールド時間                         |

| $t_8$                              | 5                                        | ns (min)               | SCLKの立下がりエッジ前のDINセットアップ時間                     |

| $t_9$                              | 6                                        | ns (min)               | SCLKの立下がりエッジ後のDINホールド時間                       |

| $t_{10}^{5}$                       | 30                                       | ns (max)               | SCLKの立下がりエッジからDOUTスリーステートまでの時間                |

|                                    | 10                                       | ns (min)               | SCLKの立下がりエッジからDOUTスリーステートまでの時間                |

| t <sub>POWER-UP</sub> <sup>6</sup> | 1                                        | μs (max)               | フル・パワーダウンからのパワーアップ時間                          |

<sup>&</sup>lt;sup>1</sup> SCLK入力のマーク/スペース比は、40/60~60/40です。

# タイミング図

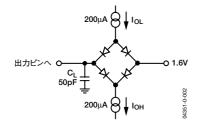

図2. デジタル出力タイミング仕様の負荷回路

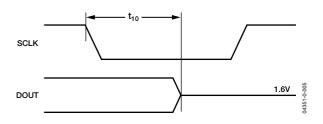

図4. SCLKの立下がりエッジ後のホールド時間

図3. SCLKの立下がりエッジ後のアクセス時間

図5. SCLKの立下がりエッジからDOUTスリーステート までの時間

REV. 0 — 7 —

<sup>&</sup>lt;sup>2</sup> 仕様が保証される最小のf<sub>SCLK</sub>。

<sup>・</sup> 在版が味証される版がが $I_{SCIR}$ 。 3 図2の負荷回路で測定し、出力が $V_{IH}$ または $V_{IL}$ 電圧に達するまでに必要な時間と定義されます。 4 50pFの負荷コンデンサで測定。 5  $t_{10}$ は、図2の負荷回路でデータ出力が0.5V変化するのに要する時間から導出しています。測定した時間を外挿して、50pFコンデンサの充放電の影響を受けない値としているため、タイミング特性で使用する時間 $t_{10}$ はAD7912/AD7922の真のバス開放時間であり、バスの負荷容量とは無関係です。 6 「パワーアップ時間」を参照。

### タイミング例

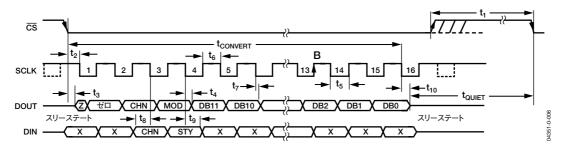

図6と図7に、「タイミング仕様」から取ったタイミング・パラメータの一部を示します。

### タイミング例1

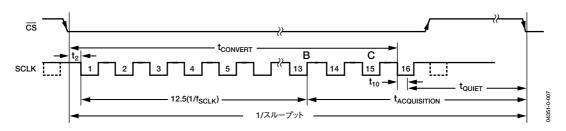

図7に示すように、 $f_{SCLK}$ =18MHzで、スループット・レートが1MSPSのときのサイクル時間は、以下のようになります。

$$t_2 + 12.5 (1/f_{SCLK}) + t_{ACO} = 1 \mu s$$

$t_2$ の最小値を10nsとして、 $t_{ACQ}$ が295nsのときに、 $t_{ACQ}$ が290nsという条件を満たします。

図7において、 $t_{10}$ の最大値が30nsの場合、 $t_{ACQ}$ =2.5(1/ $f_{SCLK}$ ) + $t_{10}$ + $t_{QUIET}$ になります。これにより、 $t_{QUIET}$ が126nsの値になり、最小値30nsの条件を満たします。

### タイミング例2

AD7922は、低いクロック周波数による動作もできます。図7に示すように、 $f_{SCLK} = 5$  MHz で、スループット・レートが 315kSPSのときのサイクル時間は、以下のようになります。

$$t_2 + 12.5 (1/f_{SCLK}) + t_{ACO} = 3.17 \,\mu\text{s}$$

$t_2$ の最小値を10nsとして、 $t_{ACQ}$ が664nsのときに、 $t_{ACQ}$ が290nsという条件を満たします。

図7において、 $t_{10}$ の最大値が30nsの場合、 $t_{ACQ}$ =2.5(1/ $f_{SCLK}$ ) + $t_{10}$ + $t_{QUIET}$ になります。これにより、 $t_{QUIET}$ が134nsの値になり、最小値30nsの条件を満たします。

この例では、その他の低速クロック値の場合と同様に、変換が完了する前に信号がすでに取得されている可能性がありますが、変換終了後、次の変換が開始されるまでに最小30nsの $t_{QUIET}$ を確保する必要があります。この例では、図7のポイントCの付近で信号を完全に取得します。

図6. AD7922シリアル・インターフェースのタイミング図

図7. シリアル・インターフェースのタイミング例

# 絶対最大定格

特に指示がない限り、T<sub>A</sub>=25℃です。

### 表4

| パラメータ                  | 定格值                        |

|------------------------|----------------------------|

| GNDに対するV <sub>DD</sub> | -0.3~+7V                   |

| GNDに対するアナログ入力電圧        | $-0.3V \sim V_{DD} + 0.3V$ |

| GNDに対するデジタル入力電圧        | $-0.3 \sim +7V$            |

| GNDに対するデジタル出力電圧        | $-0.3V \sim V_{DD} + 0.3V$ |

| 電源を除くすべてのピンに対する        | ±10mA                      |

| 入力電流1                  |                            |

| 動作温度範囲                 |                            |

| 商用(Aグレード)              | -40~+85℃                   |

| 保存温度範囲                 | -65~+150°C                 |

| ジャンクション温度              | 150℃                       |

| TSOTパッケージ              |                            |

| $	heta_{JA}$ 熱抵抗       | 207℃/W                     |

| MSOPパッケージ              |                            |

| $	heta_{JA}$ 熱抵抗       | 205.9℃/W                   |

| $	heta_{JC}$ 熱抵抗       | 43.74℃/W                   |

| リード温度、ハンダ付け            |                            |

| リフロー (10~30秒)          | 235 (0/+5) ℃               |

| ESD                    | 1.5kV                      |

絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

#### 注意

ESD(静電放電)の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

REV. 0 — 9 —

<sup>1</sup> 最大100mAまでの過渡電流でSCRのラッチアップが発生することはありません。

# ピン配置と機能の説明

図8. 8ピンMSOPのピン配置

図9. 8ピンTSOTのピン配置

### 表5. ピン機能の説明

| MSOPの | TSOTの |                                     |                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ピン番号  | ピン番号  | 記号                                  | 機能                                                                                                                                                                                                                                                                                                                                                |

| 1     | 4     | DOUT                                | データ出力。ロジック出力です。AD7912/AD7922からの変換結果は、この出力からシリアル・データ・ストリームで取り出されます。ビットは、SCLK信号の立下がりエッジでクロック出力されます。 AD7922の場合、データ・ストリームは先頭の2つのゼロ、変換結果がどのチャンネルに対応するかを示すチャンネル識別子ビット、現在の動作モードを示すモード・ビット、そして最後にMSBファーストの12ビットの変換データで構成されます。 AD7912の場合、データ・ストリームは先頭の2つのゼロ、変換結果がどのチャンネルに対応するかを示すチャンネル識別子ビット、現在の動作モードを示すモード・ビット、そして最後にMSBファーストの10ビットの変換データと2つの末尾ゼロで構成されます。 |

| 2     | 3     | CS                                  | チップ・セレクト。アクティブ・ローレベルのロジック入力です。この入力は AD7912/AD7922の変換動作を開始し、さらにシリアル・データ転送をフレーミング する2つの機能を備えています。                                                                                                                                                                                                                                                   |

| 3     | 2     | SCLK                                | シリアル・クロック。ロジック入力です。SCLKは、AD7912/AD7922にデータを<br>リード/ライトするためのシリアル・クロックを供給します。このクロック入力は、<br>AD7912/AD7922の変換プロセスのクロック源としても使用されます。                                                                                                                                                                                                                    |

| 4     | 1     | DIN                                 | データ入力。ロジック入力です。変換されるチャンネルはこの入力データ上に設定され、SCLKの立下がりエッジで内部レジスタにクロック入力されます。                                                                                                                                                                                                                                                                           |

| 6、5   | 7、8   | V <sub>IN0</sub> , V <sub>IN1</sub> | アナログ入力。この2つのシングルエンド・アナログ入力チャンネルは、オンチップのトラック&ホールド・アンプ内部で多重化されます。変換されるアナログ入力チャンネルは、DINピン上で3番目のMSBに書き込むことによって選択します。入力範囲は0 $\sim$ V <sub>DD</sub> です。                                                                                                                                                                                                 |

| 7     | 6     | GND                                 | アナログ・グラウンド。AD7912/AD7922上のすべての回路のグラウンド基準ポイントです。アナログ入力信号はすべて、このGND電圧を基準にする必要があります。                                                                                                                                                                                                                                                                 |

| 8     | 5     | $V_{ m DD}$                         | 電源入力。AD7912/AD7922のV <sub>DD</sub> は2.35~5.25Vです。                                                                                                                                                                                                                                                                                                 |

# 用語の説明

#### **看分非直線性**

ADCの伝達関数のエンドポイントを通過する直線からの最大偏差です。AD7912/AD7922の場合、伝達関数のエンドポイントは最初のコード遷移よりも1LSB下のゼロスケールと最後のコード遷移よりも1LSB上のフルスケールです。

#### 微分非直線性

ADCの任意の2つの隣接するコード間で測定された実際の変化と理想的な1LSBの変化との差です。

#### オフセット誤差

(00...000) から (00...001) への最初のコード遷移レベルの、理想的なレベル、すなわちAGND+1LSBからの偏差です。

#### オフセット誤差マッチング

任意の2つのチャンネル間のオフセット誤差の差です。

### ゲイン誤差

オフセット誤差の調整が完了した後、(111...110) から (111...111) への最後のコード遷移レベルが理想的なレベル、すなわち $\mathbf{V}_{\mathrm{DD}}$ -1LSBと相違する偏差のことです。

### ゲイン誤差マッチング

任意の2つのチャンネル間のゲイン誤差の差です。

#### 総合未調整誤差

ゲイン誤差、直線性誤差、オフセット誤差を含む総合的な仕様です。

#### チャンネル間アイソレーション

チャンネル間で測定されたクロストークのレベルです。 $20\sim500k$ Hzのフルスケール正弦波信号を任意の入力チャンネルに加え、その信号が10kHzの信号で選択されたチャンネルでどの程度減衰するかを調べて測定します。この値は、AD7912/AD7922の両方のチャンネル間における最悪値になります。

#### トラック&ホールド・アンプのアクイジション時間

変換終了後、トラック&ホールド・アンプの出力がその最終値の±1LSB以内に達するまでに必要な時間です。トラック&ホールド・アンプは、変換終了後にトラック・モードに戻ります。詳細については、「シリアル・インターフェース」を参照してください。

### 信号/ノイズ&歪み比(SINAD)

A/Dコンバータの出力で測定される信号対ノイズおよび歪みの比です。信号は正弦波のrms値です。ノイズは高調波を含み、DCを除くサンプリング周波数の半分( $f_s/2$ )までの基本波以外のすべての信号のrms値を合計したものです。

### 信号対ノイズ比 (SNR)

A/Dコンバータの出力で測定される信号対ノイズの比です。信号は正弦波入力のrms値です。ノイズは、ナイキスト帯域幅  $(f_s/2)$  の範囲内のrms量子化誤差です。正弦波のrms値はそのピークtoピーク値の1/2を $\sqrt{2}$ で除算した値であり、量子化ノイズのrms値は $q/\sqrt{12}$ です。この比はデジタル変換プロセスで使用される量子化レベル値に依存し、量子化レベルが高くなるほど、量子化ノイズが小さくなります。理想的なNビット・コンバータのSNRは、以下のように定義されます。

#### SNR = 6.02 N + 1.76 dB

したがって、12ビット・コンバータのSNRは74dB、10ビット・コンバータのSNRは62dBになります。

ただし、ADC内部の各種の誤差発生源によって、SNRの測定値は理論値よりも小さくなります。こうした誤差は、積分および微分非直線性や内部のACノイズ源などによるものです。

### 全高調波歪み (THD)

高調波のrms値の和と基本波のrms値との比であり、以下のよう に定義されます。

$$THD(dB) = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

ここで、

$V_1$ は基本波のrms振幅値です。

$V_2$ 、 $V_3$ 、 $V_4$ 、 $V_5$ 、 $V_6$ は、2次から6次までの高調波のrms振幅値です

### ピーク高調波またはスプリアス・ノイズ

ADCの出力スペクトル(最大f<sub>s</sub>/2までの周波数で、DCを除く)のうち2番目に大きい成分のrms値と基本波のrms値との比です。一般にこの仕様値はスペクトルのうち最大の高調波成分によって決まりますが、高調波がノイズ・フロアに埋もれるADCの場合はノイズのピークになります。

REV. 0 — 11 —

### 相互変調歪み

2つの周波数の正弦波faとfbを入力することにより、非直線性をもつアクティブ・デバイスは、必ず和と差の周波数mfa $\pm$ nfb (m、n=0、1、2、3...) で歪み成分を生じます。相互変調歪み項は、mとnがどちらも0でない場合です。たとえば、2次項には(fa+fb)と(fa-fb)があり、3次項には(2fa+fb)、(2fa-fb)、(fa-2fb)があります。

AD7912/AD7922は、2つの入力周波数を使用するCCIF規格を適用してテストされています(「仕様」のfaとfbを参照)。この場合、2次項は一般に基本波の正弦波から離れた周波数となり、3次項は一般に入力周波数に近い周波数となります。その結果、2次項と3次項が別々に規定されます。相互変調歪みの計算はTHD仕様の場合と同様に、個々の歪み積のrms値の和と基本波の振幅のrms値との比として定義され、dBの単位で表します。

— 12 — REV. 0

# 代表的な性能特性

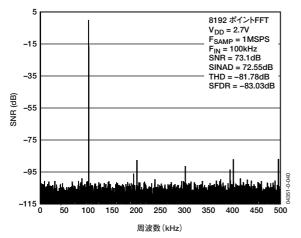

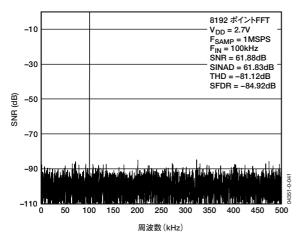

図10と図11に、1MSPSのサンプリング・レートと100kHzの入力 周波数の場合のAD7922とAD7912の代表的なFFTプロットを示 します。

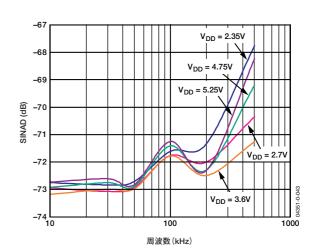

図12には、1MSPSのサンプリング・レートと18MHzのSCLK周 波数でAD7922を動作させる場合の各種電源時における入力周波 数対SINADの性能特性を示します。

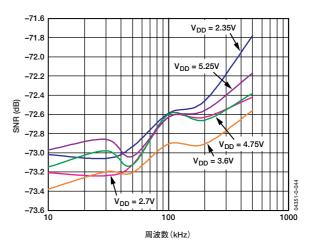

図13には、1MSPSのサンプリング・レートと18MHzのSCLK周 波数でAD7922を動作させる場合の各種電源時における入力周波 数対SNRの性能特性を示します。

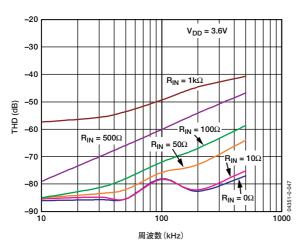

図16には、3.6Vの電源電圧と1MSPSのサンプリング・レートを 使用する場合の各種の信号源インピーダンス条件におけるアナロ

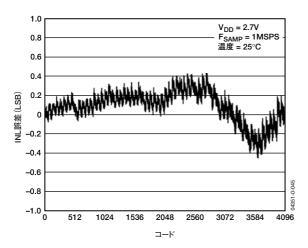

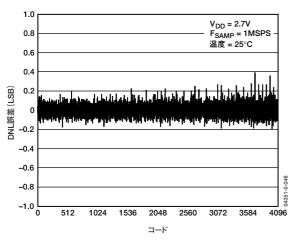

図14と図15は、AD7922のINLおよびDNL性能特性図です。

グ入力周波数対THDの性能特性を示します。詳細については、 「アナログ入力」を参照してください。

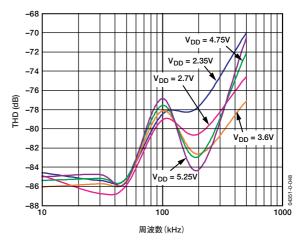

図17には、1MSPSのサンプリング・レートと18MHzのSCLK周 波数を使用する場合の各種電源時におけるアナログ入力周波数対 THDの性能特性を示します。

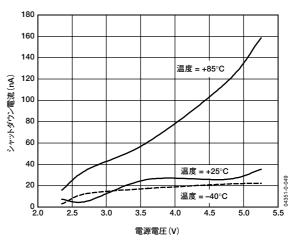

図18には、各種の動作温度時における電源電圧対シャットダウ ン電流の性能特性を示します。

図10. AD7922のダイナミック性能 (1MSPS時)

図12. AD7922の入力周波数 対 SINAD特性 (1MSPS時)

図11. AD7912のダイナミック性能 (1MSPS時)

図13. AD7922の入力周波数 対 SNR特性 (1MSPS時)

REV. 0 — 13 —

図14. AD7922のINL性能

図15. AD7922のDNL性能

図16. 各種の信号源インピーダンス時の アナログ入力周波数 対 THD特性

図17. 各種の電源電圧時のアナログ入力周波数 対 THD特性

図18. 電源電圧 対 シャットダウン電流

— 14 — REV. 0

# 回路情報

AD7912/AD7922は、それぞれ10/12ビットの高速、2チャンネル、単電源動作のA/Dコンバータ(ADC)です。各デバイスは、 $2.35\sim5.25$ Vの電源電圧範囲で動作します。5V電源または3V電源の動作時に、18MHzのクロックを使用し、1MSPSのスループット・レートを実現できます。

AD7912/AD7922は、オンチップのトラック&ホールド・アンプ、ADC、シリアル・インターフェースをすべて小型サイズの8ピンTSOTパッケージまたは8ピンMSOPパッケージに内蔵しており、他のデバイスよりも大幅にスペースを節約できるという利点があります。シリアル・クロック入力はこのデバイスのデータにアクセスし、またADCに書き込まれるデータの転送を制御すると同時に、逐次比較型ADCに対応するクロック源を提供します。アナログ入力レンジは0~ $V_{DD}$ です。各ADCは外付け電圧リファレンスを必要とせず、オンチップの電圧リファレンスもありません。AD7912/AD7922のリファレンス電圧は電源から供給されるため、最大限に広いダイナミック入力レンジが得られます。

AD7912/AD7922には、変換と変換の間に消費電力を低減できるパワーダウン・オプションがあります。このパワーダウン機能は、「動作モード」で説明するように、標準のシリアル・インターフェースを介して実行されます。さらに、複数のAD7912/AD7922をデイジーチェーン構成で接続するデイジーチェーン接続モードでの使用も可能です。この動作モードは、 $\overline{\mathbf{CS}}$ 信号のロジック状態を制御することによって選択します。DOUTピン上の4番目のMSBによって、ADCがノーマル・モードまたはデイジーチェーン接続モードのどちらに設定されているかが示されます。

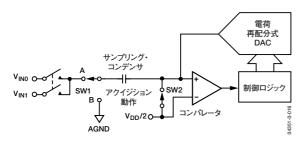

### コンバータの動作

AD7912/AD7922は、電荷再配分式DACを中心にして構成される10/12ビットの逐次比較型ADCです。ADCの簡略回路図を図19と図20に示します。図19には、アクイジション動作中のADCの回路図を示します。このときに、SW2は閉じ、SW1はAの位置にあります。コンパレータは平衡状態に維持され、サンプリング・コンデンサが選択された $V_{\rm IN}$ チャンネルの信号を収集します。

図19. ADCのアクイジション動作を示す回路図

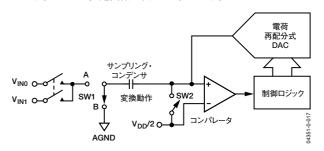

ADCが変換を開始すると(図20を参照)、SW2が開き、SW1がBの位置に移動します。この動作によって、コンパレータが平衡を失った状態になります。制御ロジックと電荷再配分式D/Aコンバータ(DAC)を使用し、サンプリング・コンデンサの固定電荷量を加算または減算します。これによってコンパレータが平衡状態に戻ります。コンパレータが再び平衡状態になると、変換が終了します。制御ロジックは、ADCの出力コードを生成します。ADCの伝達関数を図21に示します。

図20. ADCの変換動作を示す回路図

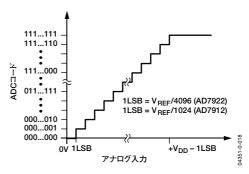

### ADCの伝達関数

AD7912/AD7922の出力コーディングは、ストレート・バイナリです。指定されたコード遷移は、連続するLSB整数値、すなわち1LSB、2LSBなどで発生します。LSBサイズはAD7922が $V_{DD}$ /4096、AD7912が $V_{DD}$ /1024です。AD7912/AD7922の理想的な伝達特性を図21に示します。

図21. AD7912/AD7922の伝達特性

REV. 0 — 15 —

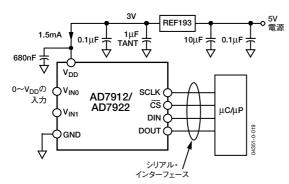

### 代表的な接続図

図22に、AD7912/AD7922の代表的な接続図を示します。 $V_{REF}$  は内部で $V_{DD}$ から取るため、 $V_{DD}$ を十分にデカップリングする必要があります。これによって、 $0\sim V_{DD}$ のアナログ入力レンジが得られます。変換結果は16ビット・ワードで出力されます。この16ビット・ワードは、先頭の2つのゼロ、変換されたチャンネルを示すチャンネル識別用ビット、現在の動作モードを示すモード・ビット、最後にMSBファーストの12ビットまたは10ビットの変換データで構成されます。AD7912の場合は、10ビット結果の後に2つの末尾ゼロが続きます。「シリアル・インターフェース」を参照してください。

AD7912/AD7922が必要とする電源電流は非常に低いので、別 の方法として電源に高精度電圧リファレンスを使用することも できます。REF19x電圧リファレンス(5V用のREF195または 3V用のREF193)を使用し、必要な電圧をADCに供給すること ができます (図22を参照)。使用する電源のノイズが大きいか、 システム電源電圧が5Vまたは3V以外の電圧値(15Vなど)の 場合は、この設定が特に効果的です。REF19xは、安定した電 圧をAD7912/AD7922に対して出力します。低ドロップアウト のREF193を使用する場合、AD7912/AD7922に供給しなけれ ばならない電流は1.5mA (typ) です。ADCが1MSPSのレート で変換を実行しているとき、REF193は最大2mAの電流を供給 する必要があります。REF193の負荷レギュレーションは標準 で10ppm/mA (REF193、VS=5V) なので、REF193から2mA の電流を消費するときの誤差は20ppm (60μV) になります。 REF193から $V_{DD}$ =3Vを供給する場合、これはAD7922で 0.082LSBの誤差、AD7912で0.061LSBの誤差に相当します。

低消費電力が必要なアプリケーションでは、ADCのパワーダウン・モードとREF19x電圧リファレンスのスリープ・モードを利用して、消費電力性能を改善してください。詳細については、「動作モード」を参照してください。

図22. AD7912/AD7922の電源にREF193を使用する場合

表6に、同じセットアップ条件で $V_{DD}$ 電源として各種の電圧リファレンスを使用し、50kHzの入力信号を適用する場合の代表的な性能データを示します。

表6. 各種の電圧リファレンスICを使用する場合のAD7922の 性能

| V <sub>DD</sub> に接続する電圧リファレンス | AD7922のSNR性能(dB) |

|-------------------------------|------------------|

| AD780 (3V)                    | -73              |

| REF193                        | -72.42           |

| ADR433                        | -72.9            |

| AD780 (2.5V)                  | -72.86           |

| REF192                        | -72.27           |

| ADR421                        | -72.75           |

### アナログ入力

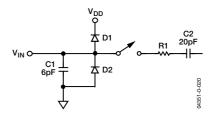

AD7912/AD7922のアナログ入力の等価回路を図23に示します。D1とD2の2個のダイオードが、アナログ入力のESD保護を行います。アナログ入力信号が300mV以上電源レールを超えることがないように注意してください。この値を超えると、ダイオードが順方向にバイアスし、サブストレート内に電流が流れ始めます。ADCに修復不能な損傷を与えることなく、ダイオードが許容できる最大電流は10mAです。

図23. アナログ入力等価回路

図23に示すコンデンサC1の容量は約6pF(typ)であり、主にこれがリード・ピン容量になります。抵抗R1はトラック&ホールド・スイッチのオン抵抗で構成される集中抵抗であり、入力マルチプレクサのオン抵抗も含まれます。この抵抗は約100 $\Omega$ (typ)です。コンデンサC2はADCサンプリング・コンデンサとして使用され、その容量は20pF(typ)です。

ACアプリケーションでは、該当するアナログ入力ピン上にバンドパス・フィルタを使用して、アナログ入力信号から高周波数成分を除去することを推奨します。高調波歪みと信号対ノイズ比が重要なアプリケーションでは、アナログ入力をインピーダンスの低い信号源で駆動してください。信号源インピーダンスが大きいと、ADCのAC性能を著しく損うことがあります。このような場合は、入力バッファ・アンプを使用する必要があります。特定のアプリケーションに合った最適なオペアンプを選択してください。

各種のオペアンプを入力バッファとして使用し、同じセットアップ条件で50kHzの入力信号を適用する場合の代表的な性能データを表7に示します。

表7. 各種の入力バッファを使用する場合のAD7922の性能

| 入力バッファとして<br>使用するオペアンプ | AD7922のSNR性能 (dB)、<br>50kHz入力、V <sub>DD</sub> =3.6V |  |  |

|------------------------|-----------------------------------------------------|--|--|

| シングル・オペアンプ             |                                                     |  |  |

| AD8038                 | -72.79                                              |  |  |

| AD8510                 | -72.35                                              |  |  |

| AD8021                 | -72.2                                               |  |  |

| デュアル・オペアンプ             |                                                     |  |  |

| AD712                  | -72.68                                              |  |  |

| AD8022                 | -72.88                                              |  |  |

アンプを使用してアナログ入力を駆動しない場合には、信号源インピーダンスを低い値に制限する必要があります。信号源インピーダンスの最大値は、許容できる全高調波歪み(THD)に応じて異なります。信号源インピーダンスが増加すると、それに応じてTHDの値も高くなり、これにともなって性能が劣化します(図16を参照)。

### デジタル入力

AD7912/AD7922のデジタル入力は、アナログ入力を制限する最大定格値によって制限されません。デジタル入力は7Vまで印加することができ、アナログ入力のように $V_{DD}$ +0.3Vという制約はありません。たとえば、AD7912/AD7922を3Vの $V_{DD}$ で動作させる場合は、5Vのロジック・レベルをデジタル入力上で使用できます。ただし、 $V_{DD}$ =3Vのときに、DOUT上のデータ出力が3Vのロジック・レベルを維持するようにしてください。SCLK、DIN、 $\overline{CS}$ が $V_{DD}$ +0.3Vに制限されないことから得られるもう1つの利点として、電源シーケンスの問題を回避できることです。 $\overline{CS}$ 、DIN、SCLKが $V_{DD}$ よりも先に印可されるなら、ラッチアップの心配はまったくありません。これに対してアナログ入力の場合は、0.3Vよりも大きい信号を $V_{DD}$ よりも先に印加すると、ラッチアップが生じる可能性があります。

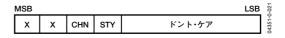

#### DIN入力

次の変換動作で変換するチャンネルは、DINピンの書込みによって選択します。DINピン上のデータは、SCLKの立下がりエッジでAD7912/AD7922にロードされます。データがDINピンからAD7912/AD7922に転送されると同時に、変換結果が読み出されます。使用するのはDINワードの3番目と4番目のビットのみです。ADCは、その他のビットを無視します。

3番目のMSBはチャンネル識別用ビットであり、次の変換動作で変換するチャンネルを示します。これは $V_{\rm IN0}$ (CHN=0)または $V_{\rm IN1}$ (CHN=1)です。

4番目のMSBのSTYは、デバイスの動作モードに関係しています。AD7912/AD7922をデイジーチェーン接続モードにしておくには、変換動作中にCHNとSTYの各ビットを反転する必要があります(STY  $\pm$  CHN)。変換サイクル中にDINワードでSTY  $\pm$  CHNに設定すると、デバイスは次のサイクルでノーマル・モードに強制設定されます。詳細については、「デイジーチェーン接続モード」を参照してください。

AD7912/AD7922をデイジーチェーン接続モードで使用する必要がない場合は、STYとCHNの各ビットを同じ値(STY=CHN)に設定することを推奨します。この場合、変換サイクル中にDINをハイまたはローいずれかのレベルに設定することで、チャンネルを選択できます。

まとめると、以下のようになります。

**CHN=0**:次の変換でチャンネル0が選択されます。

CHN=1:次の変換でチャンネル1が選択されます。

CHN=STY: 次のサイクルでノーマル・モードが強制設定さ

れます。

**CHN ≠ STY**: AD7912/AD7922のデイジーチェーン接続モー

ドを維持します。

図24. AD7912/AD7922のDINワード

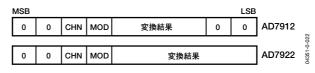

### DOUT出力

AD7912/AD7922からの変換結果は、シリアル・データ・ストリームとして出力されます。変換が実行されると同時に、各ビットがSCLKの立下がりエッジでクロック出力されます。

AD7922のシリアル・データ・ストリームは、先頭の2つのゼロ、変換されたチャンネルを示すチャンネル識別用ビット、現在の動作モードを示すモード・ビット、最後にMSBファーストの12ビットの変換データで構成されます。

AD7912の場合、シリアル・データ・ストリームは先頭の2つのゼロ、変換されたチャンネルを示すチャンネル識別用ビット、現在の動作モードを示すモード・ビット、最後にMSBファーストの10ビットの変換データと2つの末尾ゼロで構成されます。

DOUT上のCHNとMODの各ビットから、ADCの現在の動作モードがわかります。CHN=MODの場合、AD7912/AD7922はノーマル・モードです。CHN $\pm$ MODのときには、デイジーチェーン接続モードに設定されています。

図25. AD7912/AD7922のDOUTワード

REV. 0 — 17 —

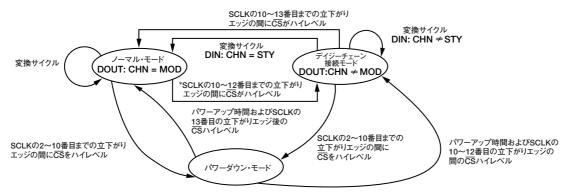

# 動作モード

AD7912/AD7922には、ノーマル・モード、パワーダウン・モード、デイジーチェーン接続モードの3つの動作モードがあります。動作モードを選択するには、 $\overline{CS}$ 信号のロジック状態を制御します。変換開始後に $\overline{CS}$ がハイレベルになるポイントに応じて、AD7912/AD7922がパワーダウン・モードに入るか、デイジーチェーン接続モードに設定されるかが決まります。同様に、すでにデイジーチェーン接続モードになっている場合も、デバイスを通常の動作に戻すか、パワーダウン・モードに設定するかを $\overline{CS}$ によって制御します。 $\overline{DIN}$ 入力」で説明したように、 $\overline{DIN}$ ピンへの書込みによって、デイジーチェーン接続モードからノーマル・モードに変更することもできます。

パワーダウン・モードによって、柔軟なパワー・マネジメント・オプションを利用し、さまざまなアプリケーションの条件に応じて消費電力対スループット・レート比を最適化することができます。

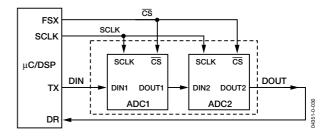

デイジーチェーン接続モードは、高速のスループット・レートが要求されず、図33に示すように複数のAD7912/AD7922をデイジーチェーン構成で接続するアプリケーションのために用意されています。

### ノーマル・モード

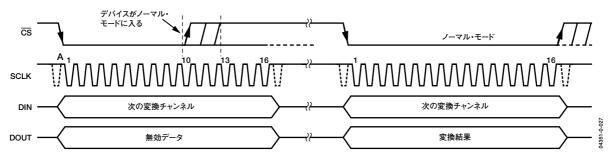

ノーマル・モードは、最高速のスループット・レート性能を達成できる動作モードです。AD7912/AD7922は常に完全なパワーアップ状態を維持するため、パワーアップ時間を心配する必要がありません。このモードでのAD7912/AD7922の動作を図26に示します。

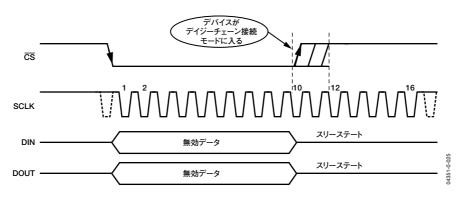

「シリアル・インターフェース」で説明するように、 $\overline{\text{CS}}$ の立下がりエッジで変換が開始されます。デバイスを常に完全なパワーアップ状態にしておくには、 $\overline{\text{CS}}$ の立下がりエッジ後、最低10サイクルのSCLKの立下がりエッジが経過するまで $\overline{\text{CS}}$ をローレベルに維持する必要があります。図27に示すように、SCLKの10番目の立下がりエッジが終了してから、12番目の立下がりエッジが発生するまでの間に $\overline{\text{CS}}$ がハイレベルになると、デバイスはデイジーチェーン接続モードに入ります。変換が終了し、DOUTはスリーステート状態に戻ります。SCLKの13番目の立下がりエッジの後、 $t_{\text{CONVERT}}$ が終了する前に $\overline{\text{CS}}$ がハイレベルになると、変換が終了し、DOUTはスリーステート状態に戻りますが、デバイスはノーマル・モードのままになります。

AD7922の場合は、変換が完了し、すべての変換結果にアクセスできるまでに16シリアル・クロック・サイクルが必要です。AD7912では、変換が完了し、すべての変換結果にアクセスできるまで少なくとも14シリアル・クロック・サイクルが必要です。

次の変換が開始されるまで $\overline{\text{CS}}$ をハイレベルのアイドル状態にするか、ローレベルのアイドル状態にしておき、次の変換の前のどこかで $\overline{\text{CS}}$ をハイレベルに戻すことができます(実質的に $\overline{\text{CS}}$ をローレベルのアイドル状態に設定)。データ転送が完了した時点で(DOUTはスリーステート状態に戻ります)、静止時間  $t_{\text{QUIET}}$ が経過した後、 $\overline{\text{CS}}$ を再びローレベルに設定すると、次の変換動作を開始できます。

### パワーダウン・モード

パワーダウン・モードは、低速のスループット・レートが必要とされるアプリケーションでの使用を目的としています。変換と変換の間でADCをパワーダウン状態にするか、何回かの変換を高速スループット・レートで実行した後、こうした変換バーストの間に比較的長い期間ADCをパワーダウン状態にすることができます。AD7912/AD7922がパワーダウン・モードに入っているときは、すべてのアナログ回路がパワーダウン状態になります。

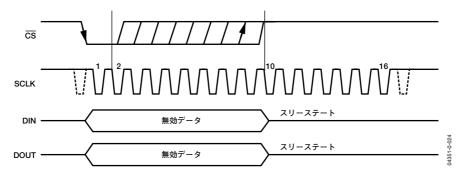

パワーダウン・モードに入るには、図28に示すように、SCLK の2番目の立下がりエッジの後、10番目の立下がりエッジが発生するまでに $\overline{CS}$ をハイレベルにして、変換プロセスを中断する必要があります。このSCLKの期間中に $\overline{CS}$ をハイレベルに設定すると、デバイスがパワーダウン・モードに入り、 $\overline{CS}$ の立下がりエッジによって開始された変換が終了し、DOUTはスリーステート状態に戻ります。SCLKの2番目の立下がりエッジの前に $\overline{CS}$ をハイレベルに設定すると、デバイスはノーマル・モードのままになり、パワーダウンしません。このようにして、 $\overline{CS}$ ライン上で発生するグリッチのために予期しないパワーダウンが生じるのを防ぎます。

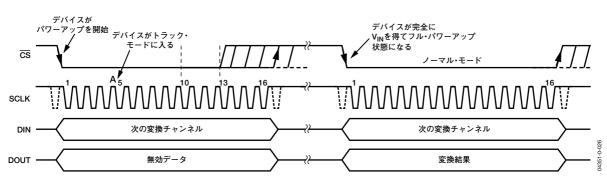

この動作モードを終了して、AD7912/AD7922を再びパワーアップ状態にする場合、ダミー変換を実行します。 $\overline{CS}$ の立下がりエッジでデバイスはパワーアップを開始し、SCLKの10番目の立下がりエッジが終了するまで $\overline{CS}$ がローレベルになっている間パワーアップ状態を続けます。図29に示すように、16サイクルのSCLKが経過するとデバイスは完全なパワーアップ状態になり、次の変換から有効なデータ結果を出力します。SCLKの10番目の立下がりエッジの前に $\overline{CS}$ がハイレベルになると、AD7912/AD7922はパワーダウン・モードに戻ります。これによって、 $\overline{CS}$ ライン上のグリッチによる予期しないパワーダウンや、 $\overline{CS}$ がローレベルに設定されている間の8 SCLKサイクルの偶発的なバーストを防止します。このため、デバイスが $\overline{CS}$ の立下がりエッジでパワーアップを開始していても、SCLKの10番目の立下がりエッジの前に $\overline{CS}$ の立上がりエッジがあれば、その時点でデバイスは再びパワーダウンします。

図26. ノーマル・モード動作

図27. デイジーチェーン接続モードの開始

図28. パワーダウン・モードの開始

図29. パワーダウン・モードの終了

REV. 0 — 19 —

### パワーアップ時間

AD7912/AD7922のパワーアップ時間は1 $\mu$ sであるため、18MHzまでの任意のSCLK周波数で、デバイスを完全にパワーアップするのにダミー・サイクル1つで十分です。ダミー・サイクルが終了すると、ADCは完全にパワーアップし、入力信号をすべて収集できます。ただし、ダミー変換の後、バスがスリーステート状態に戻った時から $\overline{Cs}$ の次の立下がりエッジまでに、静止時間 $t_{QUIET}$ を設ける必要があります。1MSPSのスループット・レートの動作時に、AD7912/AD7922は1ダミー・サイクル、すなわち1 $\mu$ sでパワーアップし、 $\pm 1$ LSB以内の精度で信号を収集します。

図29に示すように、ダミー・サイクルでパワーダウン・モードからパワーアップするとき、デバイスがパワーダウンのときにホールド・モードになっていたトラック&ホールド・アンプが、 $\overline{\text{CS}}$ の立下がりエッジ後にデバイスが受け取るSCLKの5番目の立下がりエッジでトラック・モードに復帰します。図29のポイントAがこれを示しています。この時点で、デバイスは現在のダミー変換で選択されているチャンネルで信号の収集を開始します。

任意のSCLK周波数で、デバイスをパワーアップし、 $V_{IN}$ を取得 するには1ダミー・サイクルで十分ですが、16個のSCLKの完 全なダミー・サイクルが経過しないと、デバイスの完全なパ ワーアップや $V_{\rm IN}$ の完全な取得ができないというわけではあり ません。1μsで十分にデバイスをパワーアップし、入力信号を 収集できます。たとえば、5MHzのSCLK周波数をADCに供給 する場合、サイクル時間は3.2μsになります。3.2μsの1ダミー・ サイクルでデバイスが完全にパワーアップし、 $\mathbf{V}_{\mathrm{IN}}$ を完全に取 得できます。5MHzのSCLKでは、 $1\mu s$ で5つのSCLKサイクル しか経過していません。しかし、この時点でADCは完全にパ ワーアップし、信号を取得します。したがって、この場合、 SCLKの10番目の立下がりエッジの後に $\overline{CS}$ をハイレベルにする ことができます。SCLKの13番目の立下がりエッジ以降に $\overline{CS}$ を ハイレベルに設定すると、デバイスは次の変換でノーマル・ モードに入ります。変換を開始するには、tourerの時間が経過し た後に $\overline{\mathbf{CS}}$ を再びローレベルにする必要があります。これに対し、 SCLKの10番目の立下がりエッジ後、12番目の立下がりエッジ までに $\overline{\mathbb{CS}}$ をハイレベルにすると、デバイスはデイジーチェーン 接続モードに入ります。

AD7912/AD7922に電源を最初に投入するときに、ADCをパワーダウン・モード、ノーマル・モード、デイジーチェーン接続モードのいずれかの動作モードでパワーアップできます。このため、デバイスを完全にパワーアップしてから有効な変換が実行できるように、ダミー・サイクルが終わるまで待つほうがよいでしょう。デバイスを使用しないときにパワーダウン・モードにしておくために、パワーダウン・モードでパワーアップする必要がある場合も、ダミー・サイクルを利用すれば、図28に示すサイクルの実行によってデバイスを確実にパワーダウン・モードにすることができます。

AD7912/AD7922に電源を投入すれば、パワーアップ時間はパワーダウン・モードからパワーアップするときと同じです。ノーマル・モードでデバイスを完全にパワーアップするには約1 $\mu$ sかかります。所望の動作モードにするためにダミー・サイクルの実行前に1 $\mu$ s待つ必要はありません。ADCの電源投入の直後にダミー・サイクルを実行できます。ダミー変換のすぐ後に初めて有効な変換を実行する場合は、十分なアクイジション時間をとるように注意する必要があります。電源投入後ADCが最初にパワーアップするとき、トラック&ホールド・アンプはホールド・モードになっています。 $\overline{CS}$ の立下がりエッジの後でデバイスが受信するSCLKの5番目の立下がりエッジで、トラック・モードに復帰します。

### デイジーチェーン接続モード

この動作モードのときは、ADCはシフト・レジスタとして動作します。このモードは、複数のADCをデイジーチェーン構成で接続するアプリケーションのためにあります(図33を参照)。すべてのADCに同じ $\overline{CS}$ 信号と同じシリアル・クロックを使用します。各ADCの内部シフト・レジスタに格納された変換結果は、チェーンの1つのデバイスから次のデバイスにシフト出力されます。詳細については、次の「デイジーチェーン接続の例」を参照してください。

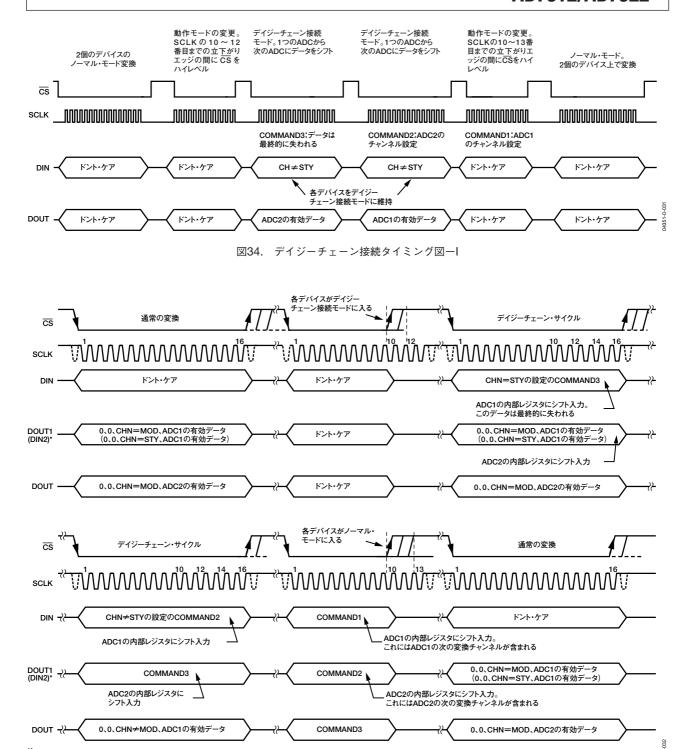

デイジーチェーン接続モードに入るときは、図27に示すように、SCLKの10番目の立下がりエッジ後、12番目の立下がりエッジが発生するまでに $\overline{CS}$ をハイレベルにし、変換プロセスを中断する必要があります。AD7912/AD7922を確実にデイジーチェーン接続モードにするには、SCLKの10番目の立下がりエッジの終了後、また12番目の立下がりエッジの前少なくとも20nsの間は $\overline{CS}$ をハイレベルにしないでください。この期間のSCLKで $\overline{CS}$ をハイレベルにすると、デバイスがデイジーチェーン接続モードに入り、このとき $\overline{CS}$ の立下がりエッジで開始された変換が終了し、DOUTがスリーステートの状態に戻ります。

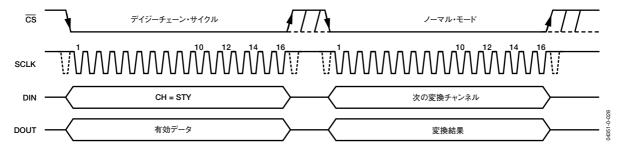

SCLKの10番目から12番目までの立下がりエッジの間に $\overline{\mathbf{CS}}$ を ハイレベルにすると、デバイスがデイジーチェーン接続モード に入り、このときにチェーンを構成する1つのADCから次の ADCにシフト出力されるデータが有効データとなります(図 34と図35を参照)。SCLKの12番目から13番目までの立下がり エッジの間に $\overline{\mathbf{CS}}$ がハイレベルになると、デバイスはデイジーチェーン接続モードに入りますが、チェーンでシフトされた データは無効データになります。

デバイスをデイジーチェーン接続モードにしておくためには、DINワードのCHNとSTYの各ビットを各16 SCLKサイクルで互いに反転させる必要があります。デバイスがデイジーチェーン接続モードのときに、DINワードのCHNとSTYの各ビットを同じ値に設定して変換すると、図30に示すようにデバイスは次のサイクルで強制的にノーマル・モードに戻ります。

この動作モードを終了するときは、ダミー・サイクルを実行するか、変換サイクルの実行中にDINワードのSTYビットをCHNビットの値に設定してください。このモードを終了するためにダミー変換を実行するときは、図31に示すようにSCLKの10番目の立下がりエッジの終了後、13番目の立下がりエッジの前までに $\overline{\text{CS}}$ をハイレベルにする必要があります。デバイスはノーマル・モードに入り、ダミー・サイクルで選択されたチャンネルからの有効データによって次の変換が行われます。

図32に、各種の動作モード、動作モードを変更する方法、各種モード時およびモード遷移時のDINとDOUTのビット設定値をまとめて示します。

04351-0-029

図30. DINピンのビットCH=STYの設定によるデイジーチェーン接続モードの終了

図31. デイジーチェーン接続モードの終了

\*SCLKの10番目から12番目までの立下がりエッジの間にCSがハイレベルになると、デバイスがデイジーチェーン接続モードになり、チェーン を構成する1つのADCから次のADCにシフト出力されるデータが有効データとなります。 SCLKの12番目から13番目までの立下がりエッジの間にCSがハイレベルになると、デバイスがデイジーチェーン接続モードになりますが、 チェーンの1つのADCから次のADCにシフト出力されるデータは無効データになります。

図32. 各動作モードの遷移

REV. 0 — 21 —

### デイジーチェーン接続の例

高速のスループットを必要としないアプリケーションでは、複数のADCをデイジーチェーンで接続することで、マイクロコントローラ/DSPポートからのI/Oライン数を最小限にし、チェーン内のすべてのADCの同時サンプリングを実行できます。

この場合、ADCの動作モードをオルタネートする必要があります。各デバイスがノーマル・モードのときに変換が行われると、各ADCからの変換結果は内部レジスタに格納されます。変換終了後にデバイスがデイジーチェーン接続モードになると、1つのADCから次のADCにデータをシフト出力することによって、各ADCからの変換結果を読み出すことができます。

以下の例では説明のために、デバイス2個だけのデイジーチェーン接続とします。2つのAD7912/AD7922には、同じ $\overline{CS}$ とSCLKの信号を使用します。2個のデバイスは図33に示す設定によって、同時に変換を実行し、その後で読出し動作をシフトします。左側のデバイスADC1の出力が、右側のデバイスADC2に入力されます。

通常の変換動作時は、変換結果を内部に格納し、DOUTピンから出力します。デイジーチェーン接続モードのときは、内部に格納した値をDOUTピンから出力し、DINピンに入力する情報を内部レジスタにシフト入力します。

複数のAD7912/AD7922をデイジーチェーンで接続する場合のシーケンスは、以下のとおりです。

#### 1. 通常の変換

各AD7912/AD7922は選択されたチャンネルで変換を実行し、その変換結果を内部シフト・レジスタに格納します。

### 2. デイジーチェーン接続モードに入る

このサイクルでは、SCLKの10番目から12番目までの立下がりエッジの間に $\overline{CS}$ がハイレベルになり、すべてのデバイスがデイジーチェーン接続モードに入ります。

#### 3. デイジーチェーン・サイクル

AD7912/AD7922がデイジーチェーン接続モードになっている間に、チェーン内のすべてのデバイスからの変換結果が読み出され、各デバイスは次の変換を実行するように設定されます。

チェーン内にあるデバイスの数と同じ回数の読出しサイクル を実行する必要があります。AD7912/AD7922をデイジー チェーン接続モードにしておくには、DIN入力のCHNと STYの各ビットを常に反転しなければなりません。データは チェーン内の各デバイスを経由してシフトされます。データ のクロック出力に使用するのと同じクロックを使用して、 チェーン内の各デバイスにデータをクロック入力します。各 デバイスがデイジーチェーン接続モードに入ったときにDIN ピンにクロック入力される最初のワードは、最終的に失われ ます。DINピンにクロック入力される2番目のワードには チェーン内の最後のデバイスのチャンネル設定データが含ま れ、DINピンにクロック入力される3番目のワードには チェーン内の最後から2番目のデバイスのチャンネル設定 データが含まれ、以下同じようにデータが割り当てられます。 すべてのデータが読み出された後で実行されるサイクル、す なわち動作モードの変更に使用する短いサイクルで、チェー ン内の最初のデバイスで選択されたチャンネルがクロック入 力されます。図34を参照してください。

#### 4. ノーマル・モードに入る

AD7912/AD7922から変換結果を読み出した後、各デバイスをノーマル・モードに設定して、新しい変換を実行する必要があります。そのため、このサイクルでSCLKの10番目から13番目までの立下がりエッジの間に $\overline{\text{CS}}$ をハイレベルにします。DOUTラインには無効なデータが含まれ、DINにはチェーン内の最初のデバイスで選択されたチャンネルが含まれます。チェーン内の残りのデバイスについては、デイジーチェーン接続モード時にデータがシフト入力されるため、次の変換のためのチャンネル設定がすでに完了しています。

#### 5. 通常の変換

新しく選択されたチャンネルで新しい変換を実行できます。 上記のステップに従って、このプロセスを繰り返すことができます。

図33に示すデイジーチェーン接続された2個のAD7912/AD7922について、図34にタイミング図を示します。DIN信号はチェーン内の最初のAD7912/AD7922のDINピンに対応し、DOUT信号はチェーン内の最後のAD7912/AD7922のDOUTピンに対応します。2個のAD7912/AD7922の次の変換チャンネルを設定するためにDINピンにクロック入力されるワードをそれぞれCOMMAND1およびCOMMAND2とします。最初にクロック入力されるワードCOMMAND3は、チェーン内のどのADCにも残らず、最終的に失われます。チェーン内の最初のデバイスに対応するチャンネル設定データのCOMMAND1は、デイジーチェーン接続モードからノーマル・モードに移行するときにクロック入力されます。

図33のように構成された各AD7912/AD7922のDINピンに入力し、DOUTピンからクロック出力されるデータについて、図35に詳細なタイミング図を示します。DOUT1(またはDIN2)信号を無視する場合は、図35と図34は同じになります。

図33. AD7912/AD7922のデイジーチェーン接続

図35. デイジーチェーン接続タイミング図ーⅡ

REV. 0 — 23 —

\*カッコ内の記述は、DIN2ピンにクロック入力されるデータに対応します。

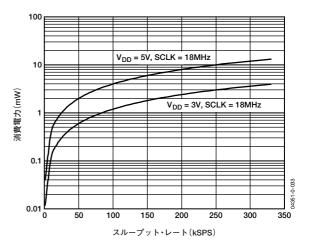

# 消費電力とスループット・レート の関係

変換を行わないときにAD7912/AD7922をパワーダウン・モードにすると、低いスループット・レートでADCの平均消費電力を低減できます。図36に示すように、スループット・レートが低くなるにつれて、デバイスのパワーダウン時間が長くなり、長期的な平均消費電力が低減します。

たとえば、100kSPSのスループット・レートと18MHzのSCLK ( $V_{DD}$ =5V時)を使用し、AD7912/AD7922を連続的なサンプリング・モードで動作させ、変換と変換の間にデバイスをパワーダウン・モードに設定する場合、その消費電力は次のように計算できます。通常の動作時の消費電力は20mW ( $V_{DD}$ =5V時)ですが、パワーアップ時間を1ダミー・サイクル (1µs)とし、残りの変換時間をさらに1サイクル (1µs)とすると、各変換サイクル中の2µsでAD7912/AD7922が消費する電力は20mWになります。スループット・レートが100kSPSで、サイクル時間が10µsの場合は、各変換サイクルの平均消費電力は、以下のようになります。

$(2/10) \times (20 \text{ mW}) = 4 \text{ mW}$

$V_{DD}$ =3V、SCLK=18MHzで、変換と変換の間にデバイスを再びパワーダウン・モードに設定する場合、通常の動作時の消費電力は $6\,\mathrm{m}\,\mathrm{W}\,\mathrm{cr}$ です。つまり、各変換サイクル中の $2\,\mu\mathrm{s}\,\mathrm{cr}$ AD7912/AD7922が消費する電力は、 $6\,\mathrm{m}\,\mathrm{W}\,\mathrm{s}\,\mathrm{cr}\,\mathrm{G}$ 域することになります。スループット・レートを $100\,\mathrm{kSPS}$ とすると、各サイクルの平均消費電力は、以下のようになります。

$(2/10) \times (6 \text{ mW}) = 1.2 \text{ mW}$

前の計算では、デバイスがパワーダウン・モードになっているときの消費電力は考慮しませんでした。変換と変換の間にデバイスをパワーダウン・モードに設定すると、ADCのパワーダウン時間が長くなるため、平均消費電力はスループット・レートの低速化に比例して低減します。

5Vと3Vの電源を使用する場合について、変換と変換の間にパワーダウン・モードにするときの消費電力とスループット・レートの関係を図36に示します。

パワーダウン・モードは、スループット・レートを約330kSPS 以下にするときに利用することを目的としています。サンプリング・レートが高速の場合はパワーダウン時間が短くなるため、ADCの平均消費電力に対する効果はありません。

図36. スループット・レート 対 消費電力の特性

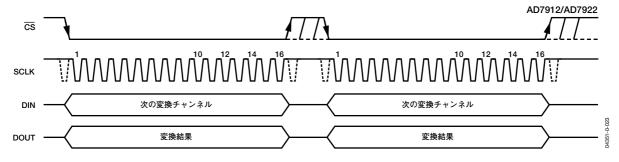

# シリアル・インターフェース

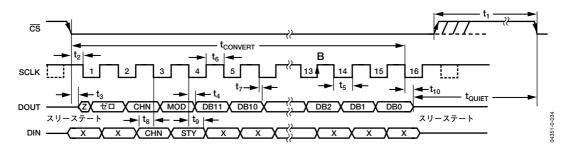

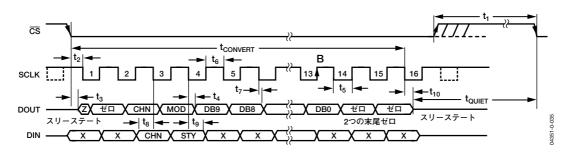

AD7922とAD7912のシリアル・インターフェースの詳細なタイミング図をそれぞれ図37と図38に示します。シリアル・クロックが変換クロックを供給し、さらに変換中のAD7912/AD7922からのデータ転送も制御します。

**CS**信号がデータの転送と変換プロセスを開始します。**CS**の立下がりエッジでトラック&ホールド・アンプがホールド・モードに入り、バスのスリーステート状態を解除します。この時点でアナログ入力がサンプリングされ、変換が開始されます。

AD7922の場合には、変換が完了するまでに16 SCLKサイクルが必要です。13個のSCLKの立下がりエッジが経過すると、図37のポイントBに示す次のSCLKの立上がりエッジでトラック&ホールド・アンプがトラック・モードに戻ります。SCLKの16番目の立下がりエッジで、DOUTラインがスリーステート状態に戻ります。16個のSCLKの立下がりエッジが経過しないうちに $\overline{\text{CS}}$ のエッジが立ち上がると、変換が終了し、DOUTラインがスリーステートに戻ります。これ以外の場合は、図37に示すようにSCLKの16番目の立下がりエッジでDOUTラインがスリーステートに戻ります。AD7922で変換を実行し、そのデータを読書きするには、16のシリアル・クロック・サイクルが必要です。

AD7912の場合は、変換の実行が完了するまでに14 SCLKサイクルが必要です。13個のSCLKの立下がりエッジが経過すると、図38のポイントBに示す次のSCLKの立上がりエッジでトラック&ホールド・アンプがトラック・モードに戻ります。

14個のSCLKの立下がりエッジが経過しないうちに区のエッジが立ち上がると、変換が終了し、DOUTラインがスリーステートに戻ります。サイクルに16個のSCLKがある場合は、図38に示すようにSCLKの16番目の立下がりエッジでDOUTラインがスリーステートの状態に戻ります。

でSがローレベルになると、先頭のゼロがクロック出力され、マイクロコントローラかDSPがこれを読み出します。残りのデータは2番目のゼロを先頭にして、その後のSCLKの立下がりエッジのたびにクロック出力されます。したがって、シリアル・クロックの最初の立下がりクロック・エッジで最初の先頭のゼロが出力され、2番目のゼロもクロック出力されます。データ転送の最後のビットは15番目の立下がりエッジでクロック出力され、16番目の立下がりエッジで有効になります。

低速のSCLKを使用するアプリケーションでは、SCLKのエッジが立ち上がるごとにデータを読み出すことができます。この場合、SCLKの最初の立下がりエッジで先頭から2番目のゼロがクロック出力され、最初の立上がりエッジでこれを読み出すことができます。ただし、 $\overline{\text{CS}}$ がローレベルのときにクロック出力される一番最初のゼロは、SCLKの最初の立下がりエッジで読み出されない限り失われます。SCLKの15番目の立下がりエッジで最後のビットがクロック出力され、SCLKの15番目の立上がりエッジで読出しができます。

SCLKの立下がりエッジが経過した直後に $\overline{CS}$ がローレベルになると、すでに説明したように $\overline{CS}$ によって一番最初のゼロがクロック出力され、SCLKの立上がりエッジで読み出すことができます。次のSCLKの立下がりエッジでは先頭から2番目のゼロがクロック出力され、次の立上がりエッジで読み出すことができます。

図37. AD7922シリアル・インターフェースのタイミング図

図38. AD7912シリアル・インターフェースのタイミング図

REV. 0 — 25 —

### マイクロプロセッサとのインターフェース

AD7912/AD7922のシリアル・インターフェースにより、さまざまなマイクロプロセッサに直接接続することができます。ここでは、一般的なマイクロプロセッサとDSPのシリアル・インターフェース・プロトコルのいくつかとAD7912/AD7922を接続する方法を説明します。

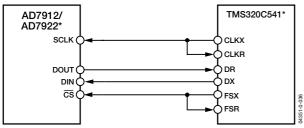

#### AD7912/AD7922とTMS320C541とのインターフェース

TMS320C541のシリアル・インターフェースは連続的なシリア ル・クロックとフレーム同期信号を使用し、AD7912/AD7922 などの周辺デバイスとデータ転送を同期化します。CS入力を使 用することで、周辺の付加ロジックを使わずに、TMS320C541 とAD7912/AD7922間の接続が簡単にできます。TMS320C541 のシリアル・ポートは、バースト・モードで動作するように設 定し(シリアル・ポート制御レジスタSPCでFSM=1)、内部シ リアル・クロックCLKX(SPCレジスタでMCM=1)と内部フ レーム信号 (SPCレジスタでTXM=1) を使用します。した がって、この2つのピンは出力に設定されます。AD7922の場合 は、ワード長を16ビットに設定する必要があります(SPCレジ スタでFO=0)。このDSPでは、ワード長が16ビットまたは8ビットのフレームしか使えません。したがって、14ビットが必 要なAD7912の場合も、FOビットを16ビットに設定し、16個 のSCLKが必要になります。AD7912では、最後の2クロック・ サイクルで2つの末尾ゼロをクロック出力します。

SPCレジスタの値は、以下のとおりです。

FO = 0

FSM=1

MCM = 1

TXM = 1

AD7912/AD7922でパワーダウン・モードを実行するときには、フォーマット・ビットFOを1に設定してください。これによって、ワード長が8ビットに設定されます。

接続図を図39に示します。信号処理アプリケーションの場合は、TMS320C541からのフレーム同期信号により等間隔サンプリングを行う必要があります。

\* わかりやすくするためにその他のピンを省略しています。

図39. TMS320C541とのインターフェース

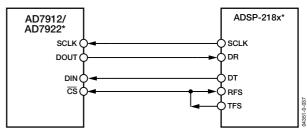

# **AD7912/AD7922とADSP-218xとのインターフェース** ADSP-218xファミリーのDSPも、周辺の付加ロジックを使用

ADSP-218xファミリーのDSPも、周辺の付加ロジックを使用 せず、AD7912/AD7922に直接接続できます。SPORT制御レジ スタを以下のように設定してください。

TFSW=RFSW=1、オルタネート・フレーミング

INVRFS、INVTFS=1、アクティブ・ローレベルのフレーム信号

DTYPE=00、右揃えデータ

ISCLK=1、内部シリアル・クロック

TFSR=RFSR=1、各ワードのフレーム

IRFS=0、入力としてRFSを設定

ITFS=1、出力としてTFSを設定

SLEN=1111、AD7922では16ビット

パワーダウン・モードを実行するときは、SLENを0111に設定し、8ビットのSCLKバーストを発行してください。接続図を図40に示します。ADSP-218XではSPORTのTFSとRFSを互いに接続しますが、TFSを出力、RFSを入力に設定します。DSPはオルタネート・フレーミング・モードで動作し、SPORT制御レジスタを上述のように設定します。TFS上で生成されるフレーム同期信号は $\overline{CS}$ に接続され、あらゆる信号処理アプリケーションではそうですが、等間隔サンプリングが必要になります。ただし、この例ではタイマー割込みによってADCのサンプリング・レートを制御するため、場合によっては等間隔サンプリングにならないことがあります。

\* わかりやすくするためにその他のピンを省略しています。

SLEN=1101、AD7912では14ビット

図40. ADSP-218xとのインターフェース

必要なサンプル・インターバルで割込みをかける値がタイマー・レジスタにロードされます。割込みが受信されると、その値がTFS/DT(ADCの制御ワード)とともに送信されます。 TFSを使用してRFSを制御し、データの読出しを制御します。 シリアル・クロックの周波数はSCLKDIVレジスタで設定します。 TFSとともに送信する命令、すなわちTX0=AX0があると、SCLKの状態がチェックされます。 SCLKがハイレベル、ローレベル、そして再びハイレベルになって送信が開始されるまで、DSPは待機します。 SCLKの立上がりエッジまたはその近くで送信命令が実行されるようにタイマーとSCLKの値を選択すれば、データを送信したり、次のクロック・エッジが発生するまで待機させることができます。

たとえば、ADSP-2189では40MHzのマスター・クロック周波数を使用します。SCLKDIVレジスタに3の値をロードすると、5MHzのSCLKが得られ、マスター・クロックの8サイクルがSCLKの1クロック・サイクルに相当します。選択したスループット・レートによって異なりますが、803 (803+1=804)の値をタイマー・レジスタにロードすると、各割込みの間およびその後の送信命令の間に100.5のSCLKが発生します。送信命令はSCLKのエッジで生じるため、このような状況では等間隔サンプリングができません。割込みの間のSCLKの数がNの整数値であれば、DSPは等間隔サンプリングを実行できます。

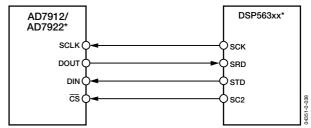

#### AD7912/AD7922とDSP563xxとのインターフェース

図41の接続図は、モトローラのDSP563xxファミリーのSSI (同期シリアル・インターフェース) にAD7912/AD7922を接続する方法を示しています。SSIは同期のノーマル・モードで動作し (制御レジスタB [CRB] でSYN=1およびMOD=0)、TxおよびRxの2つのワード・フレーム同期信号が内部で生成されます (CRBのFSL1ビット=0およびFSL0ビット=0)。AD7922の接続では、WL2ビット=0、WL1ビット=1、WL0ビット=0に設定して、制御レジスタA (CRA) のワード長を16に設定してください。このDSPには14ビット・ワード長のオプションがないので、AD7912のワード長をAD7922と同様に16ビットに設定します。AD7912では変換プロセスで16 SCLKサイクルを使用し、最終の2クロック・サイクル中に2つの末尾ゼロをクロック出力して、16ビット・ワードを埋めます。

AD7912/AD7922でパワーダウン・モードにするときは、CRA でWL2ビット=0、WL1ビット=0、WL0ビット=0に設定し、ワード長を8ビットに変更してください。CRBレジスタのFSP ビットを1に設定すると、フレームがローレベルになり、変換が開始されます。同様にCRBレジスタのSCD2、SCKD、SHFDの各ビットを使用して、シリアル・ポートのSC2(フレーム同期信号)とSCKの各ピンを出力に設定し、MSBファーストのシフトを行います。

次の値を設定します。

MOD = 0

SYN=1

WL2、WL1、WL0はワード長によって異なります。

FSL1=0, FSL0=0

FSP=1、負のフレーム同期

SCD2=1

SCKD=1

SHFD=0

信号処理アプリケーションの場合、DSP563xxからのフレーム同期信号によって等間隔サンプリングを実行する必要があります。

\* わかりやすくするためにその他のピンを省略しています。

図41. DSP563xxとのインターフェース

REV. 0 — 27 —

# アプリケーションのヒント

### グラウンディングとレイアウト

AD7912/AD7922を実装するPCボードは、アナログ部とデジタル部を分離して、ボード内の特定の場所にそれぞれまとめて配置するように設計してください。これにより、簡単に分離できるグラウンド・プレーンを使用できるようになります。グラウンド・プレーンのエッチングを最小限にすれば、最良のシールド効果が得られるため一般に一番よい方法といえます。デジタル・グラウンド・プレーンとアナログ・グラウンド・プレーンは、1点で接続してください。複数のデバイスがAGNDとDGNDの接続を必要とするシステム内でAD7912/AD7922を使用する場合も、接続は1点で行い、AD7912/AD7922のできるだけ近くにスター結線してください。

ノイズが混入するのを防ぐために、デバイスの真下にデジタル・ラインを配置しないようにしてください。アナログ・グラウンド・プレーンは、ノイズを防止するため、AD7912/AD7922の下を通します。AD7912/AD7922に接続する電源ラインはできるだけ太いパターンにしてインピーダンスを下げ、電源ライン上のグリッチによる影響を小さくします。クロックなどの高速スイッチング信号は、デジタル・グラウンドでシールドしてボードの他の部分にノイズが放射しないようにし、アナログ入力の近くを通さないようにしてください。デジタル信号とアナログ信号は、交差しないようにしてください。ボードの反対面のパターンは互いに直角になるように配置し、ボードを通過するフィードスルーの影響を抑えます。マイクロストリップ技法は非常に優れていますが、両面ボードには使用できないこともあります。この技法では、ボードの部品面をグラウンド・プレーン専用とし、信号はハンダ面に配置します。

優れたデカップリングも非常に大切です。AGNDとの間に  $10\mu F$ のタンタル・コンデンサと $0.1\mu F$ のコンデンサを並列に接続して、アナログ電源をデカップリングしてください。デカップリング用部品から最大限の性能を引き出すために、デカップリング・コンデンサと $V_{DD}$ およびGNDの各ピン間の距離を最小限にし、それぞれのピンを接続するパターン配線長をできるだけ短くしてください。

-28- REV. 0

# AD7912/AD7922の性能評価

評価用ボードのパッケージには、すべて組立て済みおよびテスト済みの評価用ボード、マニュアル、EVAL-CONTROL BRD2を介してPCからボードを制御するためのソフトウェアが同梱されています。

EVAL-CONTROL BRD2をAD7912CB/AD7922CB評価用ボード、またモデル名の末尾にCBの記号があるアナログ・デバイセズの他の数多くの評価用ボードとともに利用することで、AD7912/AD7922のAC性能とDC性能のデモンストレーションと評価を行うことができます。

このソフトウェアを利用して、AD7912/AD7922のAC(高速フーリエ変換)とDC(コードのヒストグラム)のテストを実施できます。

その他の詳細については、AD7912/AD7922テクニカル・ノートを参照してください。このテクニカル・ノートはソフトウェアに収録されていますが、ウェブサイト $\underline{www.analog.com}$ のAD7912/AD7922製品ページのDesign Toolsリンクから入手することもできます。

REV. 0 — 29 —

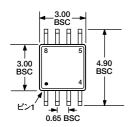

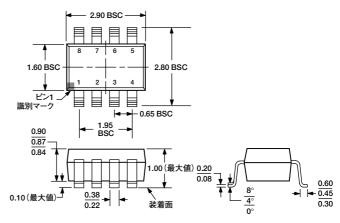

# 外形寸法

JEDEC規格MO-187AAに準拠

図42. 8ピン・ミニスモールアウトライン・ パッケージ [MSOP] (RM-8)

寸法単位:mm

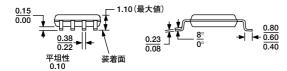

JEDEC規格MO-193BAに準拠

図43. 8ピン薄型スモールアウトライン・トランジスタ・ パッケージ [TSOT]

(UJ-8)

寸法単位:mm

### オーダー・ガイド

| 製品                                                                                         | 温度範囲                                                     | 直線性誤差<br>(LSB) <sup>1</sup>                                                                                                                                     | パッケージ                                               | パッケージ・<br>オプション                      | マーキング                           | 数量                               |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------|---------------------------------|----------------------------------|

| AD7912ARM<br>AD7912ARM-REEL<br>AD7912ARM-REEL7<br>AD7912AUJ-R2<br>AD7912AUJ-REEL7          | -40~+85℃<br>-40~+85℃<br>-40~+85℃<br>-40~+85℃<br>-40~+85℃ | $\begin{array}{l} \pm 0.5 \;\; (max) \\ \pm 0.5 \;\; (max) \end{array}$ | 8ピンMSOP<br>8ピンMSOP<br>8ピンMSOP<br>8ピンTSOT<br>8ピンTSOT | RM-8<br>RM-8<br>RM-8<br>UJ-8<br>UJ-8 | C1A<br>C1A<br>C1A<br>C1A<br>C1A | 1<br>3000<br>1000<br>250<br>3000 |

| AD7922ARM<br>AD7922ARM-REEL<br>AD7922ARM-REEL7<br>AD7922AUJ-R2<br>AD7922AUJ-REEL7          | -40~+85℃<br>-40~+85℃<br>-40~+85℃<br>-40~+85℃<br>-40~+85℃ | ±1.5 (max)<br>±1.5 (max)<br>±1.5 (max)<br>±1.5 (max)<br>±1.5 (max)                                                                                              | 8ピンMSOP<br>8ピンMSOP<br>8ピンMSOP<br>8ピンTSOT<br>8ピンTSOT | RM-8<br>RM-8<br>RM-8<br>UJ-8<br>UJ-8 | C1B<br>C1B<br>C1B<br>C1B        | 1<br>3000<br>1000<br>250<br>3000 |

| EVAL-AD7912CB <sup>2</sup><br>EVAL-AD7922CB <sup>2</sup><br>EVAL-CONTROL BRD2 <sup>3</sup> |                                                          |                                                                                                                                                                 | 評価用ボード<br>評価用ボード<br>評価制御用ボード                        |                                      |                                 |                                  |

<sup>1</sup> この直線性誤差は積分非直線性のことです。

-30 -REV. 0

この画派由ボードは、評価およびデモンストレーションのために単独で使用することも、EVAL-CONTROL BRD2とともに使用することもできます。

3 このボードはフル機能のユニットであり、PCから制御でき、モデル名の末尾にCBの記号があるアナログ・デバイセズのすべての評価用ボードと通信できます。完全な評価用キットを注文される場合は、特定のADC評価用ボード (EVAL-AD7922CBなど)、EVAL-CONTROL BRD2、12V ACのトランスをご注文ください。詳細は、該当の評価用ボードのテクニカル・ノートを参照してください。

REV. 0 — 31 —

D04351-0-4/04(0)-J