## 3V/5V、入力範囲 ± 10V、1mW 3チャンネル、16ビット、シグマ・デルタA/Dコンバータ

## **AD7707**

### 特長

チャージバランスA/Dコンバータ 16ビット・ノーミス・コード

0.003%非直線性

高レベル( $\pm$ 10 $\lor$ )と低レベル( $\pm$ 10 $\lor$ 0の入力チャンネルチャージポンプなしで、低レベル入力チャンネルで真のバ

イポーラ±100mV性能

プログラマブル・ゲイン・フロントエンド

**ゲイン範囲:**1~128

3線式シリアル・インターフェース

SPI™/QSPI™/MICROWIRE™/DSP互換

SCLKはSchmittトリガ入力

アナログ入力をバッファ可能

**動作範囲:**2.7~3.3V、4.75~5.25V

低消費電力: 1mW max@3V スタンパイ電流: 8 µ A max 20ピンSOIC / TSSOPパッケージ

#### 概要

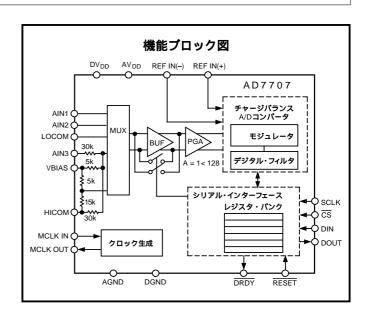

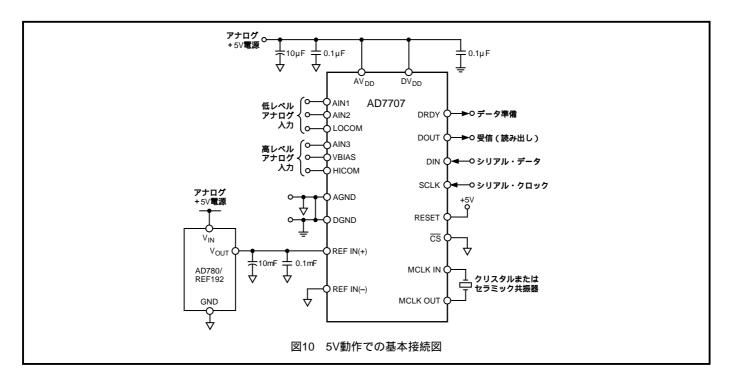

AD7707は、低周波数測定用の、完全なアナログ・フロントエンドです。トランスデューサからの低レベル入力信号の直接入力、または高レベル(±10V)信号を受け取って、シリアル・デジタル出力を生成する、3チャンネルのA/Dコンバータです。シグマ・デルタ変換技術を用いて、最大16ビットのノーミス・コード性能を実現しています。選択した入力信号は、アナログ・モジュレータ周辺の専用プログラマブル・ゲイン・フロントエンドに加えられます。モジュレータ出力は内部デジタル・フィルタで処理されます。このデジタル・フィルタの最初のノッチは、内蔵の制御レジスタ経由でプログラムできるので、フィルタ・カットオフと出力アップデート・レートを調整できます。

AD7707は、単電源2.7~3.3Vまたは4.75~5.25Vで動作します。低レベル疑似差動アナログ入力チャンネル×2、高レベル入力チャンネル×1、差動リファレンス入力を備えています。V<sub>DD</sub> = 5V、2.5Vリファレンスで動作した場合、低レベル入力チャンネル両方で、0~+20mV、0~+2.5Vの入力信号範囲が可能です。また、LCOM入力を基準として、±20mV~±2.5Vの範囲のバイポーラ信号も入力できます。3V電源、1.225Vリファレンスでは、0~+10mVから0~+1.225Vのユニポーラ入力信号範囲を実現。同じ条件のバイポーラ入力信号範囲は±10mV~±1.225Vです。高レベル入力チャンネルでは、±10V、±5V、0~+10Vと、0~+5Vの入力信号範囲が可能です。このようにAD7707は、3チャンネル・システムでのあらゆる信号調整と変換を実行できます。AD7707は、スマート、マイクロコントローラ、DSPなどをベースとし

SPI、QSPIはMotorola, Inc.の商標です。

MICROWIRE は National Semiconductor Corporationの商標です。

REV.0

たシステムでの使用に理想的です。3線式動作可能なシリアル・インターフェースを備えています。ゲイン設定、信号極性、アップデート・レート設定は、入力シリアル・ポート経由でソフトウェア設定可能です。セルフ・キャリブレーション、システムのゲイン誤差とオフセット誤差を除去するシステム・キャリブレーションのオプションを内蔵しています。

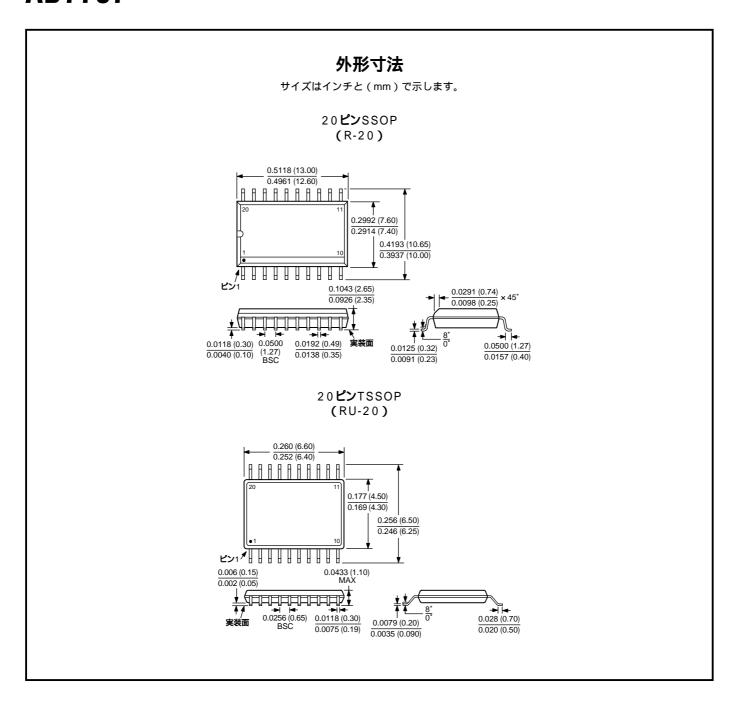

CMOS構造は、極めて低消費電力を実現し、パワーダウン・モードでは、スタンバイ消費電力を $20 \mu$  W maxに低減します。 AD7707は、20ピン広体SOIC(0.3インチ幅)、薄型20ピンTSSOP パッケージで供給されます。

#### 製品のハイライト

- 1. AD7707は、3V電源と1MHzマスター・クロックで、消費電力 1mW未満なので、低電力システムでの使用に最適です。スタンバイ電流は8 μ A未満です。

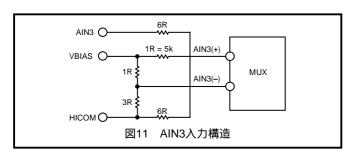

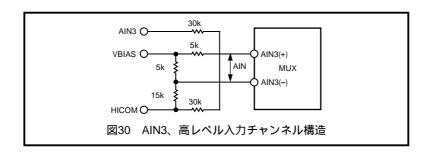

- 2. 内部の薄膜抵抗により、±10V、±5V、0~+10V、0~+5Vまでの高レベル入力信号を、スプリット電源やチャージポンプを使わず、アナログ入力に入力できます。

- 3. 低レベル入力チャンネルでは、歪みゲージやトランスデューサから 直接入力信号を受け取るので、信号調整を大幅に減らせます。

- 4. 16ビット、ノーミス・コード、±0.003%精度、ローrms ノイズなど、優れたスタティック性能を備えています。エンドポイント誤差と、温度ドリフトの影響は、ゼロ・スケールとフル・スケールの誤差を除く内部のキャリブレーションによって除去できます。

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利用したことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものでもありません。

本 社/東京都港区海岸1-16-1 電話03(5402)8400 〒105-6891 ニューピア竹芝サウスタワービル

大阪営業所 / 大阪市淀川区宮原3-5-36 電話00(6350)6860(代) 〒532-0003 新大阪第二森ビル

AD7707 一仕様 (特に指定しない場合、 $AV_{DD} = DV_{DD} = +3V/5V$ 、REFIN(+ ) = +1.225V ( $AV_{DD} = 3V$  時)、または +2.5V ( $AV_{DD} = 5V$  時)。REFIN(- ) = GND、VBIAS = REFIN(+ ) MCLKIN = 2.4576MHz。T<sub>MAX</sub> ~ T<sub>MIN</sub>で全仕様を規定)

| パラメータ                                            | Bバージョン <sup>1</sup>                        | 単位              | テスト条件/備考                                                                   |

|--------------------------------------------------|--------------------------------------------|-----------------|----------------------------------------------------------------------------|

| スタティック性能                                         |                                            | · <del>-</del>  |                                                                            |

| 低レベル入力チャンネル( AIN1、AIN2 )                         |                                            |                 |                                                                            |

| ノーミス・コード                                         | 16                                         | ビット min         | │<br>│設計により保証。フィルタ・ノッチ<60Hz                                                |

| ァーニハーコート<br>出力ノイズ                                | 表Ⅰ、表Ⅲ参照                                    | C 9 1 111111    | フィルタ・カットオフと選択ゲインに依存                                                        |

| 面別がする<br>積分非直線性 <sup>2</sup>                     | ± 0.003                                    | FSRの% max       | フィルタ・ノッチ < 60Hz。 ± 0.0003% typ                                             |

| <sup>預力・正直縁に</sup><br>ユニポーラ・オフセット誤差              | 注3参照                                       | 1 SINO 70 IIIAX | J 1 10 J 1 J 3 J 1 00112,                                                  |

| ユニポーラ・オフセット・ドリフト4                                |                                            | 11.\// tvn      |                                                                            |

| バイポーラ・ゼロ誤差                                       | i.5<br>  注3参照                              | μV/ typ         |                                                                            |

| バイポーラ・ゼロ・ドリフト⁴                                   | 0.5                                        | μV/ typ         | ゲイン1、2、4の場合                                                                |

| ハイホーク・ピロ・トラント                                    | 0.1                                        | μV/ typ         | ゲイン8、16、32、64、128の場合                                                       |

| 正のフルスケール誤差5                                      | 0.1<br>  注3参照                              | μν/ ιγρ         | 7 1 7 0、10、32、04、12000場日                                                   |

| フルスケール・ドリフト4.6                                   | 0.5                                        | μV/ typ         |                                                                            |

| ブルスケール・1-りフト <sup>**</sup><br>ゲイン誤差 <sup>7</sup> |                                            | μν/ ιγρ         |                                                                            |

| ゲイン・ドリフト <sup>4、8</sup>                          | 注3参照<br>  0.5                              | ECD/ tun Onnm   |                                                                            |

| バイポーラ負のフルスケール誤差 <sup>2</sup>                     |                                            | FSR/ typのppm    | . 0.00070/, tup                                                            |

|                                                  |                                            | FSRの%typ        | ± 0.0007% typ                                                              |

| バイポーラ負のフルスケール・ドリフト⁴                              |                                            | μV/ typ         | ゲイン1~4の場合                                                                  |

| -1 AU 1 + - 1 + U (1 WA)                         | 0.6                                        | μ V/ typ        | ゲイン8~128の場合                                                                |

| 高レベル入力チャンネル(AIN3)                                |                                            |                 | <br>  ±8±1   10./5±7   11.5                                                |

| ノーミス・コード                                         | 16                                         | ビットmin          | 設計により保証。フィルタ・ノッチ < 60Hz                                                    |

| 出力ノイズ                                            | 表IV、表VI参照                                  |                 | フィルタ・カットオフと選択ゲインに依存                                                        |

| 積分非直線性 <sup>2</sup>                              | ± 0.003                                    | FSRの% max       | フィルタ・ノッチ<60Hz。 ± 0.0003% typ                                               |

| ユニポーラ・オフセット誤差 <sup>9</sup>                       | ± 10                                       | mV max          | ± 1.5mV以内 typ                                                              |

| ユニポーラ・オフセット・ドリフト                                 | 4                                          | μV/ typ         |                                                                            |

| バイポーラ・ゼロ誤差 <sup>。</sup>                          | ± 10                                       | mV max          | ± 1.5mV以内typ                                                               |

| バイポーラ・ゼロ・ドリフト                                    | 4                                          | μV/ typ         | ゲイン1、2、4の場合                                                                |

|                                                  | 1                                          | μV/ typ         | ゲイン8、16、32、64、128の場合                                                       |

| ゲイン誤差                                            | ± 0.2                                      | % typ           | ± 0.05%以内 typ                                                              |

| ゲイン・ドリフト                                         | 0.5                                        | FSR/ typのppm    | 313 34                                                                     |

| う・・・・・・・<br>負のフルスケール誤差 <sup>2</sup>              | ± 0.0012                                   | FSRØ% typ       |                                                                            |

| 低レベルアナログ入力/リファレンス                                |                                            |                 | 注記しない場合、AINとREFINの仕様                                                       |

| 入力コモン・モード除去比( CMR ) <sup>2</sup>                 |                                            |                 | 低レベル入力チャンネル、AIN1とAIN2                                                      |

| AV <sub>DD</sub> = 5V                            |                                            |                 | 100 00000000000000000000000000000000000                                    |

| ゲイン=1                                            | 100                                        | dB typ          |                                                                            |

| ゲイン=2                                            | 105                                        | dB typ          |                                                                            |

| ゲイン=4                                            | 110                                        | dB typ          |                                                                            |

| ゲイン=8~128                                        | 130                                        | dB typ          |                                                                            |

| AVDD = 3V                                        | 130                                        | ив тур          |                                                                            |

| ゲイン = 1                                          | 105                                        | dD tun          |                                                                            |

| ゲイン=2                                            | 105<br>  110                               | dB typ          |                                                                            |

|                                                  |                                            | dB typ          |                                                                            |

| ゲイン = 4                                          | 120                                        | dB typ          |                                                                            |

| ゲイン = 8 ~ 128                                    | 130                                        | dB typ          | II 5                                                                       |

| 通常モード50Hz除去比 <sup>2</sup>                        | 98                                         | dB typ          | フィルタ・ノッチ10Hz、25Hz、50Hz、±0.02×f <sub>NOTCH</sub> の場合                        |

| 通常モード60Hz除去比 <sup>2</sup>                        | 98                                         | dB typ          | フィルタ・ノッチ10Hz、20Hz、60Hz、±0.02×f <sub>NOTCH</sub> の場合                        |

| コモン・モード50Hz除去比 <sup>2</sup>                      | 150                                        | dB typ          | フィルタ・ノッチ10Hz、25Hz、50Hz、±0.02×f <sub>NOTCH</sub> の場合                        |

| コモン・モード60Hz除去比 <sup>2</sup>                      | 150                                        | dB typ          | フィルタ・ノッチ10Hz、20Hz、60Hz、±0.02×f <sub>NOTCH</sub> の場合                        |

| 絶対 / コモン・モードREFIN電圧 <sup>2</sup>                 | AGND ~ AV <sub>DD</sub>                    | V min ~ V max   |                                                                            |

| 絶対 / コモン・モ <i>ー</i> ドAIN電圧 <sup>2、10</sup>       | AGND - 100mV                               | V min           | セットアップ・レジスタのBUFビット=0                                                       |

|                                                  | AV <sub>DD</sub> + 30mV                    | V max           |                                                                            |

|                                                  | AGND + 50mV                                | V min           | セットアップレジスタのBUFビット=1                                                        |

|                                                  | AV <sub>DD</sub> - 1.5V                    | V max           |                                                                            |

| AIN DC入力電流 <sup>2</sup>                          | 1                                          | nA max          |                                                                            |

| $AIN$ サンプリング容量 $^2$                              | 10                                         | pF max          | BUF = 0                                                                    |

| AIN差動電圧範囲 <sup>11</sup>                          | 0 ~ + V <sub>REF</sub> /GAIN <sup>12</sup> | nom             | ユニポーラ入力範囲( セットアップ・レジスタのB/Uビット = 1 )                                        |

|                                                  | ± V <sub>REF</sub> /GAIN                   | nom             | バイポーラ入力範囲(セットアップ・レジスタのB/Uビット=0)                                            |

| AIN入力サンプリング速度、fs                                 | GAIN × fclkin/64                           |                 | ゲイン1~4の場合                                                                  |

|                                                  | f <sub>CLKIN</sub> /8                      |                 | ゲイン8~128の場合                                                                |

| リファレンス入力範囲                                       | 32                                         |                 |                                                                            |

| REF IN( + ) - REF IN( - )電圧                      | 1/1.75                                     | V min/max       | <br>  AV <sub>DD</sub> = 2.7~3.3V、V <sub>REF</sub> = 1.225V ± 1%で仕様の性能を実現  |

| REF IN( + ) - REF IN( - )電圧                      | 1/3.5                                      | V min/max       | AV <sub>DD</sub> = 2.7 ~ 3.3 V、V <sub>REF</sub> = 1.223 V ± 1 % C 仕様の性能を実現 |

| REFIN入力サンプリング速度、fs                               | f <sub>CLKIN</sub> /64                     | v IIIIII/IIIaA  | T. T. O. Z.O V 、 V REF - Z.O V エ 1 /0 C IL 1水のI工配で 夫坑                      |

| <u>REFIN人</u>                                    | I CLKIN/ UT                                |                 | <br> 低レベル入力チャンネル(AIN1、AIN2)                                                |

| エロリロスノノノオの日                                      |                                            |                 | 低レヘルベルテャンネル(AINI、AIN2)<br> ゲイン=16、バッファなしモード                                |

| INIL 2                                           | . 0.003                                    | ESDO 04 mass    |                                                                            |

| INL <sup>2</sup><br>入力コエン、エード®全土トヒ/ CMD シ        | ± 0.003                                    | FSRの% max       | フィルタ・ノッチ<60Hz                                                              |

| 入力コモン・モード除去比( CMR ) <sup>2</sup>                 | 80                                         | dB typ          |                                                                            |

| 電源除去比(PSR) <sup>2</sup>                          | 90                                         | dB typ          |                                                                            |

| パラメータ                      | B <b>バージョン</b> 1                  | 単位          | テスト条件/備考                                                                         |

|----------------------------|-----------------------------------|-------------|----------------------------------------------------------------------------------|

| 高レベル・アナログ入力チャンネル( AIN3 )   |                                   |             | HICOMに関するAIN3                                                                    |

| AIN3電圧範囲                   | + 10                              | V max       |                                                                                  |

|                            | - 10                              | V min       |                                                                                  |

| 通常モード50Hz除去比               | 78                                | dB typ      | フィルタ・ノッチ10Hz、25Hz、50Hz、±0.02×f <sub>NOTCH</sub> の場合                              |

| 通常モード60Hz除去比               | 78                                | dB typ      | フィルタ・ノッチ10Hz、20Hz、60Hz、±0.02×f <sub>NOTCH</sub> の場合                              |

| AIN3入力サンプリング速度、fs          | GAIN × f <sub>CLKIN</sub> /64     |             | ゲイン1~4の場合                                                                        |

|                            | f <sub>CLKIN</sub> /8             |             | ゲイン8~128の場合                                                                      |

| AIN3入力インピーダンス <sup>2</sup> | 27                                | k min       | 30k ± 10%typ、抵抗温度係数typ値は - 30ppm/                                                |

| $AIN3$ サンプリング容量 $^2$       | 10                                | pF max      |                                                                                  |

| VBIAS入力範囲                  | 0V/AV <sub>DD</sub>               | V min/max   | typ = REFIN(+) = 2.5V                                                            |

| ロジック入力                     |                                   |             |                                                                                  |

| 入力電流                       |                                   |             |                                                                                  |

| MCLKIN以外の全入力               | ±1                                | μ A max     | ± 20nA typ                                                                       |

| MCLK                       | ± 10                              | μ A max     | ±2μA typ                                                                         |

| SCLKとMCLKIN以外の全入力          |                                   |             |                                                                                  |

| V <sub>INL</sub> 、入力ロー電圧   | 0.8                               | V max       | $DV_{DD} = 5V$                                                                   |

|                            | 0.4                               | V max       | $DV_{DD} = 3V$                                                                   |

| V <sub>INH</sub> 、入力ハイ電圧   | 2.0                               | V min       | $DV_{DD} = 3V/5V$                                                                |

| SCLKのみ( シュミット・トリガ入力 )      |                                   |             | DV <sub>DD</sub> = 公称5V                                                          |

| $V_{T+}$                   | 1.4/3                             | V min/V max |                                                                                  |

| V <sub>T</sub> .           | 0.8/1.4                           | V min/V max |                                                                                  |

| $V_{T+}$ - $V_{T-}$        | 0.4/0.8                           | V min/V max |                                                                                  |

| SCLKのみ( シュミット・トリガ入力)       |                                   |             | DV <sub>DD</sub> = 公称3V                                                          |

| $V_{T+}$                   | 1/2.5                             | V min/V max |                                                                                  |

| V <sub>T</sub> .           | 0.4/1.1                           | V min/V max |                                                                                  |

| $V_{T+} - V_{T-}$          | 0.375/0.8                         | V min/V max |                                                                                  |

| MCLKINのみ                   |                                   |             | DV <sub>DD</sub> = 公称5V                                                          |

| V <sub>INL</sub> 、入力ロー電圧   | 0.8                               | V max       |                                                                                  |

| V <sub>INH</sub> 、入力八イ電圧   | 3.5                               | V min       |                                                                                  |

| MCLKINのみ                   |                                   |             | DV <sub>DD</sub> = 公称3V                                                          |

| V <sub>INL</sub> 、入力ロー電圧   | 0.4                               | V max       |                                                                                  |

| V <sub>INH</sub> 、入力八イ電圧   | 2.5                               | V min       |                                                                                  |

| ロジック出力( MCLKOUT出力を含む )     |                                   |             |                                                                                  |

| Vol、出力ロー電圧                 | 0.4                               | V max       | I <sub>SINK</sub> = 800 µ A(MCLKOUTを除いて)¹³。 DV <sub>DD</sub> = 5V                |

|                            | 0.4                               | V max       | I <sub>SINK</sub> = 100 µ A(MCLKOUTを除いて)¹³。 DV <sub>DD</sub> = 3V                |

| Vон、出力ハイ電圧                 | 4                                 | V min       | I <sub>SOURCE</sub> = 200 μ A (MCLKOUTを除いて) <sup>13</sup> 。DV <sub>DD</sub> = 5V |

|                            | DV <sub>DD</sub> - 0.6            | V min       | $I_{SOURCE} = 100 \mu A (MCLKOUTを除いて)$ <sup>13</sup> 。DV <sub>DD</sub> = 3V      |

| フロート状態リーク電流                | ± 10                              | μ A max     |                                                                                  |

| フロート状態出力容量14               | 9                                 | pF typ      |                                                                                  |

| データ出力コーディング                | バイナリ                              |             | ユニポーラ・モード                                                                        |

|                            | オフセット・バイナリ                        |             | バイポーラ・モード                                                                        |

| システム・キャリブレーション             |                                   |             |                                                                                  |

| 低レベル入力チャンネル(AIN1、AIN2)     |                                   |             |                                                                                  |

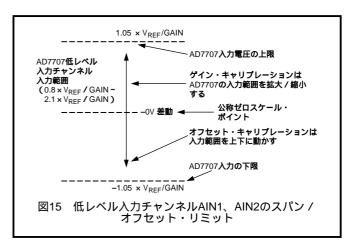

| 正のフルスケール・キャリブレーション・リミット15  | (1.05 x V <sub>REF</sub> )/ ゲイン   |             | ゲインはPGAで選択 (1~128)                                                               |

| 負のフルスケール・キャリブレーション・リミット15  | -( 1.05 x V <sub>REF</sub> )/ ゲイン |             | ゲインはPGAで選択(1~128)                                                                |

| オフセット・キャリブレーション・リミットჼ      | -( 1.05 x V <sub>REF</sub> )/ ゲイン |             | ゲインはPGAで選択(1~128)                                                                |

| 入力スパン16                    | ( 0.8 x V <sub>REF</sub> )/ ゲイン   |             | ゲインはPGAで選択(1~128)                                                                |

|                            | ( 2.1 x V <sub>REF</sub> )/ ゲイン   | V max       | ゲインはPGAで選択(1~128)                                                                |

| 高レベル入力チャンネル(AIN3)          |                                   |             |                                                                                  |

| 正のフルスケール・キャリブレーション・リミット15  | (8.4 x V <sub>REF</sub> )/ ゲイン    | V max       | ゲインはPGAで選択(1~128)                                                                |

| 負のフルスケール・キャリブレーション・リミット15  | -( 8.4 x V <sub>REF</sub> )/ ゲイン  | V max       | ゲインはPGAで選択(1~128)                                                                |

| オフセット・キャリブレーション・リミット16     | -( 8.4 x V <sub>REF</sub> )/ ゲイン  | V max       | ゲインはPGAで選択(1~128)                                                                |

| 入力スパン <sup>16</sup>        | (6.4 x V <sub>REF</sub> )/ ゲイン    | V min       | ゲインはPGAで選択(1~128)                                                                |

|                            | ( 16.8 × V <sub>REF</sub> )/ ゲイン  | V max       | ゲインはPGAで選択(1~128)                                                                |

| 電源要件                       |                                   |             |                                                                                  |

| 電源電圧                       |                                   |             |                                                                                  |

| AV <sub>DD</sub> 電圧        | +2.7~+3.3、または                     | V           | 規定の性能が得られる範囲                                                                     |

|                            | + 4.75 ~ + 5.25                   |             |                                                                                  |

| DVD電圧                      | + 2.7 ~ + 5.25                    | V           | 規定の性能が得られる範囲                                                                     |

| 電源電流                       |                                   |             |                                                                                  |

| AV <sub>DD</sub> 電流        |                                   |             | AV <sub>DD</sub> =3Vまたは5V、ゲイン=1~4                                                |

|                            | 0.27                              | mA max      | 0.22mA typ、BUF = 0、f <sub>CLKIN</sub> = 1MHz、または2.4576MHz                        |

|                            | 0.6                               | mA max      | $0.45$ mA typ、BUF = 1、 $f_{CLKIN}$ = 1MHz、または2.4576MHz、                          |

|                            |                                   |             | AV <sub>DD</sub> =3Vまたは5V、ゲイン=8~128                                              |

|                            | 0.5                               | mA max      | 0.38mA typ、BUF = 0、f <sub>CLKIN</sub> = 2.4576MHz                                |

|                            | 0.0                               |             | 71,                                                                              |

| パラメータ                             | B <b>バージョン</b> 1 | 単位      | テスト条件 / 備考                                                                          |

|-----------------------------------|------------------|---------|-------------------------------------------------------------------------------------|

| 電源要件(つづき)                         |                  |         |                                                                                     |

| DV <sub>DD</sub> 電流 <sup>17</sup> |                  |         | デジタルI/P = 0VまたはDV <sub>DD</sub> 。外部MCLKIN                                           |

|                                   | 0.080            | mA max  | $0.06$ mA typ, $DV_{DD} = 3V$ , $f_{CLKIN} = 1$ MHz                                 |

|                                   | 0.15             | mA max  | 0.13mA typ, $DV_{DD} = 5V$ , $f_{CLKIN} = 1MHz$                                     |

|                                   | 0.18             | mA max  | 0.15mA typ, $DV_{DD} = 3V$ , $f_{CLKIN} = 2.4576MHz$                                |

|                                   | 0.35             | mA max  | 0.3mA typ, $DV_{DD} = 5V$ , $f_{CLKIN} = 2.4576MHz$                                 |

| 電源除去比19                           | 注20参照            | dB typ  |                                                                                     |

| 通常モード消費電力17                       |                  |         | $AV_{DD} = DV_{DD} = +3V$ 。デジタルI/P = $0V$ または $DV_{DD}$ 、                           |

|                                   |                  |         | AIN3の損失を除き、外部MCLKIN減衰器                                                              |

|                                   | 1.05             | mW max  | 0.84mW typ、BUF = 0、f <sub>CLKIN</sub> = 1MHz、全ゲイン                                   |

|                                   | 2.04             | mW max  | 1.53mW typ、BUF = 1、f <sub>CLKIN</sub> = 1MHz、全ゲイン                                   |

|                                   | 1.35             | mW max  | 1.11mW typ、BUF = 0、f <sub>CLKIN</sub> = 2.4576MHz、ゲイン = 1 ~ 4                       |

|                                   | 2.34             | mW max  | 1.9mW typ、BUF = 1、f <sub>CLKIN</sub> = 2.4576MHz、ゲイン = 1 ~ 4                        |

| 通常モード消費電力17                       |                  |         | AV <sub>DD</sub> = DV <sub>DD</sub> = +5V、デジタルI/P = 0VまたはDV <sub>DD</sub> 、外部MCLKIN |

|                                   | 2.1              | mW max  | 1.75mW typ、BUF = 0、f <sub>CLKIN</sub> = 1MHz、全ゲイン                                   |

|                                   | 3.75             | mW max  | 2.9mW typ、BUF = 1、f <sub>CLKIN</sub> = 1MHz、全ゲイン                                    |

|                                   | 3.1              | mW max  | 2.6mW typ、BUF = 0、 f <sub>CLKIN</sub> = 2.4576MHz                                   |

|                                   | 4.75             | mW max  | 3.75mW typ, BUF = 1, $f_{CLKIN} = 2.4576MHz$                                        |

| スタンバイ( パワーダウン )電流¹ଃ               | 18               | μ A max | 外部MCLKININ=0VまたはDV <sub>DD</sub> 、4 µ A typ、AV <sub>DD</sub> = +5V                  |

|                                   | 8                | μ A max | 外部MCLKIN IN = 0VまたはDV <sub>DD</sub> 、4 µ A typ、AV <sub>DD</sub> = +3V               |

#### 注

- 1. 温度範囲は以下の通り:Bバージョン、-40~+85。

- 2. これらの数字は、最初の製品リリース時の特性決定、または設計で確定。

- 3. キャリブレーションは、実際は変換なので、これらの誤差は、低レベル入力チャンネルAIN1とAIN2において、表I、IIIに表示した変換ノイズの大きさにあたる。これは、対象となる温度で、キャリブレート後に適用します。

- 4. 任意の温度での再キャリブレートによって、これらのドリフト誤差を除去できます。

- 5. 正のフルスケール誤差はゼロスケール誤差を含み(ユニボーラ・オフセット誤差またはバイボーラ・ゼロ誤差)、ユニボーラとバイボーラ両入力範囲に適用されます。

- 6. フルスケール・ドリフトはゼロスケール誤差を含み(ユニポーラ・オフセット・ドリフトまたはパイポーラ・ゼロ・ドリフト)ユニポーラとパイポーラ両入力範囲に適用されます。

- 7. ゲイン誤差はゼロスケールを含まない。ユニポーラ範囲では、フルスケール、誤差ユニポーラ・オフセットとして計算され、バイポーラ範囲では、フルスケール誤差、バイポーラ・ゼロ誤差として計算されます。

- 8. ゲイン誤差ドリフトは、ユニポーラ・オフセット・ドリフト / バイポーラ・ゼロドリフトを含まない。ゼロスケール・キャリブレーションのみを行うと、事実上製品のドリフトです

- 9. システム・キャリプレーションの後、誤差は除去される。

- 10. このコモン・モード電圧範囲は、アナログ入力の入力電圧がAV<sub>DD</sub> + 30mV以上になるか、 AGND 100mV以下にならない限り許容されます。製品は最低AGND 200mVの電圧まで機能できますが、 高温ではリーク電流が増えます。

- 11. AIN(+)の入力電圧範囲は、低レベル入力チャンネル(AIN1、AIN2)では、LCOMの電圧に関連して決定し、高レベル入力チャンネルAIN3ではHCOMの電圧に関連して決定します。仕様の性能を得るには、低レベル・アナログ入力の絶対電圧は、AV<sub>DD</sub> + 100mV以上、またはGND 100mV以下にならないようにします。入力電圧はAGND 200mVまで可能ですが、高温ではリーク電流が増えます。

- 12. V<sub>REF</sub> = REFIN ( + ) REFIN ( )

- 13. これらのロジック出力レベルは、CMOS負荷1つを設けている場合のみ、MCLKOUTに適用します。

- 14. 正確な結果を得るため、サンプルを + 25 でテストしています

- 15. キャリブレーション後、アナログ入力が正のフルスケールを超えると、コンパータの出力はすべて1になります。アナログ入力が負のフルスケールを下回ると、出力はすべて0になります。

- 16. これらのキャリブレーションとスパンのリミットは、アナログ入力の絶対電圧が、AV<sub>00</sub> + 30mVを超えず、AGND 30mVを下回らない場合に適用します。オフセット・キャリブレーション・リミットは、ユニポーラ・ゼロポイントとバイポーラ・ゼロポイント両方に適用します。

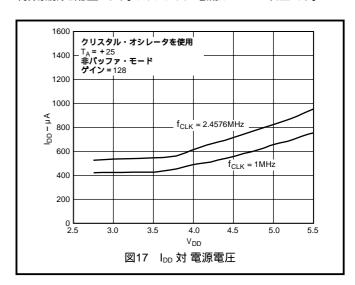

- 17. デバイスのクロックソースとして、MCLKピン経由でクリスタルまたはセラミック共振器を用いる場合、DV<sub>DD</sub>電流と消費電力は、クリスタルまたは共振器のタイプに応じて変わります(クロックと発振器回路の項参照)。

- 18. 外部マスター・クロックをスタンパイ・モードに動作させると、スタンパイ電流は、5Vで150 μ A typまで、3Vで75 μ Aまで増加します。クロックソースとして、MCLKビン経由でクリスタルまたはセラミック共振器を用いる場合、内部オシレータはスタンパイ・モードで動作し、消費電力はクリスタルまたは共振器のタイプに応じて変わります(スタンパイ・モードの項参照)。

4

19. DCで測定し、選択した通過帯域で適用。50HzのPSRRは、フィルタ・ノッチ25Hzまたは50Hzで、120dBを超えます。60HzでのPSRRは、フィルタ・ノッチ20Hzまたは60Hzで、120dBを超えます。20. PSRRは、ゲインとAV<sub>bo</sub>両方によって決定します。

#### 低レベル入力チャンネル、AIN1、AIN2

| ゲイン            | 1  | 2  | 4  | 8~128 |

|----------------|----|----|----|-------|

| $AV_{DD} = 3V$ | 86 | 78 | 85 | 93    |

| $AV_{DD} = 5V$ | 90 | 78 | 84 | 91    |

仕様は予告なく変更することがあります。

#### 高レベル入力チャンネル、AIN3

| ゲイン            | 1  | 2  | 4  | 8~128 |  |

|----------------|----|----|----|-------|--|

| $AV_{DD} = 3V$ | 68 | 60 | 67 | 75    |  |

| $AV_{DD} = 5V$ | 72 | 60 | 66 | 73    |  |

# **タイミング特性1、2** (特に指定しない限り、AV<sub>DD</sub> = DV<sub>DD</sub> = +2.7~ +5.25V、AGND = DGND = 0V、 f<sub>CLKIN</sub> = 2.4576MHz、入力ロジック = 0、ロジック1 = DV<sub>DD</sub>)

|                             | T <sub>MIN</sub> 、T <sub>MAX</sub> における |         |                                                           |

|-----------------------------|-----------------------------------------|---------|-----------------------------------------------------------|

| パラメータ                       | リミット<br>(Bバージョン)                        | 単位      | テスト条件/備考                                                  |

| f <sub>CLKIN</sub> 3、4      | 400                                     | kHz min | マスター・クロック周波数                                              |

|                             | 5                                       | MHz max | (仕様の性能を得るには、クリスタル・オシレータまたは外部供給を使用)                        |

| t <sub>CLKIN LO</sub>       | $0.4 \times t_{CLKIN}$                  | ns min  | マスター・クロック入力ロー時間、t <sub>CLKIN</sub> = 1/f <sub>CLKIN</sub> |

| t <sub>CLKIN HI</sub>       | $0.4 \times t_{CLKIN}$                  | ns min  | マスター・クロック入力ハイ時間                                           |

| $t_1$                       | 500 x t <sub>CLKIN</sub>                | ns nom  | DRDY八イ時間                                                  |

| $t_2$                       | 100                                     | ns min  | RESETパルス幅                                                 |

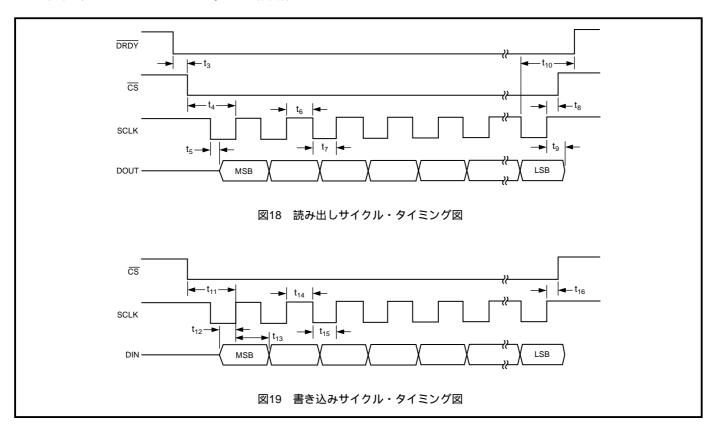

| 読み出し動作                      |                                         |         |                                                           |

| $t_3$                       | 0                                       | ns min  | DRDY ~ CSのセットアップ時間                                        |

| $t_4$                       | 120                                     | ns min  | CS立ち下がりエッジからSCLK立ち上がりエッジのセットアップ時間                         |

| t <sub>5</sub> <sup>5</sup> | 0                                       | ns min  | SCLK立ち下がりエッジからデータ有効までの遅延                                  |

|                             | 80                                      | ns max  | $DV_{DD} = +5V$                                           |

|                             | 100                                     | ns max  | $DV_{DD} = +3.0V$                                         |

| t <sub>6</sub>              | 100                                     | ns min  | SCLK高パルス幅                                                 |

| t <sub>7</sub>              | 100                                     | ns min  | SCLK低パルス幅                                                 |

| t <sub>8</sub>              | 0                                       | ns min  | CS立ち上がりエッジからSCLK立ち上がりエッジのホールド時間                           |

| t <sub>9</sub> <sup>6</sup> | 10                                      | ns min  | SCLK立ち上がリエッジ後のバス解放時間                                      |

|                             | 60                                      | ns max  | $DV_{DD} = +5V$                                           |

|                             | 100                                     | ns max  | $DV_{DD} = +3.0V$                                         |

| t <sub>10</sub>             | 100                                     | ns max  | SCLK立ち下がりエッジからDRDYハイ <sup>7</sup>                         |

| 書き込み動作                      |                                         |         |                                                           |

| t <sub>11</sub>             | 120                                     | ns min  | CS立ち下がりエッジからSCLK立ち上がりエッジのセットアップ時間                         |

| t <sub>12</sub>             | 30                                      | ns min  | データ有効から、SCLK立ち上がりエッジのセットアップ時間                             |

| t <sub>13</sub>             | 20                                      | ns min  | データ有効からSCLK立ち上がりエッジのホールド時間                                |

| t <sub>14</sub>             | 100                                     | ns min  | SCLKハイ・パルス幅                                               |

| t <sub>15</sub>             | 100                                     | ns min  | SCLKロー・パルス幅                                               |

| t <sub>16</sub>             | 0                                       | ns min  | CS立ち上がりエッジからSCLK立ち上がりエッジのホールド時間                           |

#### 注:

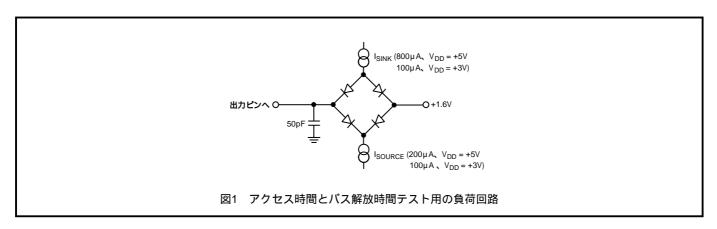

- 1. 正確な結果を得るため、サンプルを+25 でテスト。全入力信号は、tr=tf=5ns(DVppの10~90%)に規定され、電圧レベル1.6Vから時間測定しています。

- 2. 図16、17参照。

- 3.fcLKINデューティ・サイクルは、45~55%。AD7707がスタンパイ・モードでないときは、必ずfcLKINを供給してください。クロック供給がない場合、仕様より高い電流を引き出すことができ、非キャリブレート状態となります。

- 4. AD7707は、fclkin=2.4576MHzとして生産テストされています(looテストの一部では1MHz)。特性により、400kHzで動作することが保証されています。

- 5. これらの数値は図1の負荷回路で測定し、出力が $V_{OL}$ または $V_{OH}$ の限度を超えるのに必要な時間として定義されています。

- 6. これらの数値は、図1の回路に負荷を加えたときに、データ出力が0.5V変化するのにかかる測定時間から引き出します。次に、測定した数字を外挿して、50pFコンデンサの充/放電による影響を除去します。つまり、タイミング特性を表す時間は、デバイスの真のバス解放時間であり、外部バス負荷容量の影響を受けていません。

- 7. DRDYは、出力アップデートの後で、デバイスから最初の読み出しをしてからハイに戻ります。必要なら同じデータの読み出しも可能ですが、DRDYがハイになっている間、次の出力アップデートの近くで次の読み出しが起こらないように注意してください。

#### 絶対最大定格\*

| (とくに指定しない場合、T <sub>A</sub> = +25 ) |                             | 工業用(Bバージョン)     |

|------------------------------------|-----------------------------|-----------------|

| $AV_{DD} \sim AGND$                | - 0.3 ~ +7V                 | 保管温度範囲          |

| AV <sub>DD</sub> ~ DGND            | - 0.3 ~ + 7V                | 接合温度            |

| DV <sub>DD</sub> ~ AGND            | - 0.3 ~ + 7V                | SOICパッケージ、ワット損  |

| DV <sub>DD</sub> ~ DGND            | - 0.3 ~ + 7V                | JA熱インピーダンス      |

| DV <sub>DD</sub> ~ AGND            | $-0.3V \sim AV_{DD} + 0.3V$ | ピン温度(ハンダ付け)     |

| DGND ~ AGND                        | - 0.3 ~ + 0.3V              | 蒸着(60秒)         |

| AIN1、AIN2入力電圧~LOCOM                | $-0.3V \sim AV_{DD} + 0.3V$ | 赤外線(15秒)        |

| AIN3~HICOM入力電圧                     | - 11 ~ + 30V                | TSSOPパッケージ、ワット損 |

| V <sub>BIAS</sub> ~ AGND           | $-0.3V \sim AV_{DD} + 0.3V$ | JA熱インピーダンス      |

| HICOM、LOCOM~AGND                   | $-0.3V \sim AV_{DD} + 0.3V$ | ピン温度(ハンダ付け)     |

| REF( + ) REF( - )~ AGND            | $-0.3V \sim DV_{DD} + 0.3V$ | 蒸着(60秒)         |

| DGNDへのデジタル入力電圧                     | $-0.3V \sim DV_{DD} + 0.3V$ | 赤外線(15秒)        |

| DGNDへのデジタル出力電圧                     | $-0.3V \sim DV_{DD} + 0.3V$ | ESD定格           |

|                                    |                             |                 |

\*上記の絶対最大定格を超えるストレスを加えると、デバイスに永久的な損傷を与えることがあります。この定格はストレス定格の規定のみを目的とするものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長期間絶対最大定格条件に置くと、デバイスの信頼度に影響を与えることがあります。

#### オーダー・ガイド

動作温度範囲

| モデル           | V <sub>DD</sub> 電源 | 温度範囲        | パッケージ | パッケージ・オプション |

|---------------|--------------------|-------------|-------|-------------|

| AD7707BR      | 2.7 ~ 5.25V        | - 40 ~ + 85 | SOIC  | R-20        |

| AD7707BRU     | 2.7 ~ 5.25V        | - 40 ~ + 85 | TSSOP | RU-20       |

| EVAL-AD7707EB |                    | 評価ボード       |       |             |

6

#### 注意

ESD(静電放電)の影響を受けやすいデバイスです。4000Vもの高圧の静電気が人体やテスト装置に容易に帯電し、 検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネル ギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪 失を回避するために、適切なESD予防措置をとるようお奨めします。

- 40 ~ + 85 - 65 ~ + 150 + 150 450mW 75 /W

> + 215 + 220 450mW 139 /W

+ 215 + 220 3kV

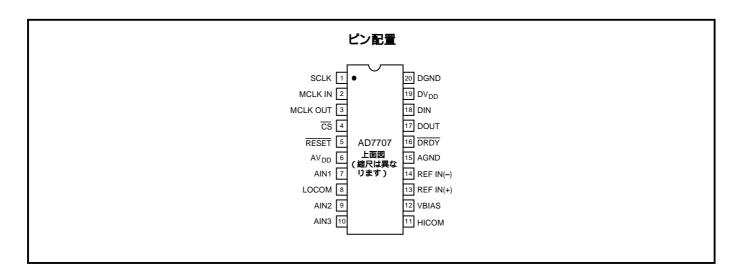

#### ピン機能の説明

| ピン番号 | 記号               | 機能                                                                                                                                                                                                                                                 |

|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | SCLK             | シリアルクロック。シュミット・トリガ・ロジック入力。AD7707からシリアルデータにアクセスするために、外部シリアルクロックをこの入力に適用します。このシリアルクロックは、全データを連続パルス列で送信する、連続クロックとすることも、小さいバッチデータでAD7707に情報を送信する、非連続クロックとすることもできます。                                                                                    |

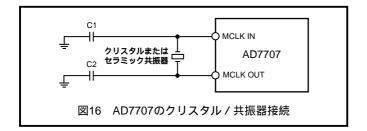

| 2    | MCLK IN          | デバイスのマスター・クロック信号。これは、クリスタル/共振器または外部クロックから供給されます。<br>クリスタル/共振器は、MCLKINとMCLKOUTピンにまたがって接続されます。別の方法として、<br>MCLKINピンを、CMOS対応クロックとMCLKOUTを非接続にして、ドライブすることも可能です。<br>AD7707は、500kHz~5MHzのクロック周波数で動作できます。                                                  |

| 3    | MCLK OUT         | デバイスのマスター・クロックがクリスタル/共振器の場合、クリスタル/共振器をMCLKINとMCLK-OUTの間に接続します。外部クロックをMCLKINに適用した場合、MCLKOUTからは反転クロック信号が供給されます。このクロックは、外部回路へのクロックソース供給に使用でき、1つのCMOS負荷をドライブできます。不要な場合、MCLKOUTは、クロック・レジスタのCLKDISビットを介してオフにできます。これにより、MCLKOUTでの不要な容量性負荷駆動による電力浪費をなくせます。 |

| 4    | CS               | チップ選択。AD7707を選択するのに用いるアクティブ・ロー・ロジック入力。この入力をローにハード設定してあると、AD7707は、デバイスにインターフェースするのに用いられる、SCLK、DIN、DOUTによる3線式インターフェース・モードで動作できます。CSは、シリアルバスに複数のデバイスを接続したシステムでデバイスを選択するのに用いたり、AD7707と通信する際のフレーム同期信号として用いたりできます。                                       |

| 5    | RESET            | ロジック入力。部品のコントロール・ロジック、インターフェース・ロジック、キャリブレーション係数、<br>デジタル・フィルタ、アナログ・モジュレータを、電源オンの状態にリセットする、アクティブ・ロー入力。                                                                                                                                              |

| 6    | AV <sub>DD</sub> | アナログ電源電圧、 + 2.7 ~ + 5.25Vで動作。                                                                                                                                                                                                                      |

| 7    | AIN1             | 低レベル・アナログ入力チャンネル1。LOCOMに対する疑似差動入力として使用します。                                                                                                                                                                                                         |

| 8    | LOCOM            | 低レベル・入力チャンネルのCOMMON入力。AIN1、AIN2のアナログ入力はこの入力を基準とします。                                                                                                                                                                                                |

| 9    | AIN2             | 低レベル・アナログ入力チャンネル2。LOCOMに対する疑似差動入力として使用します。                                                                                                                                                                                                         |

| 10   | AIN3             | HICOMに対するシングルエンド高レベル・アナログ入力チャンネル。                                                                                                                                                                                                                  |

| 11   | нісом            | 高レベル入力チャンネルのCOMMON入力。AIN3のアナログ入力はこの入力を基準とします。                                                                                                                                                                                                      |

| 12   | VBIAS            | VBIASは、ハイ・レベル入力チャンネル信号のレベル・シフトに使用します。この信号は、内部モジュレータに見られるAIN(+)とAIN(-)信号が、コモン・モード範囲に入るように使用します。VBIASは、通常、AV <sub>DD</sub> = 5Vのとき2.5V、AV <sub>DD</sub> = 3Vのとき1.225Vに接続します。                                                                         |

| 13   | REF IN (+)       | リファレンス入力。AD7707の差動リファレンス入力の正の入力。リファレンス入力は、REFIN ( + ) が REFIN ( - ) より大きくなければならないという前提で、区別されます。REFIN ( - ) は、 $AV_{DD}$ とAGND の間の、任意の場所が可能です。                                                                                                      |

| ピン番号 | 記号               | 機能                                                                                                                                                                                                                                                                                                                         |

|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | REF IN ( - )     | リファレンス入力。AD7707の差動リファレンス入力の負の入力。REFIN( - )は、REFIN( + )がREFIN( - )<br>より大きければ、AV <sub>DD</sub> とAGNDの間の任意の地点が可能です。                                                                                                                                                                                                          |

| 15   | AGND             | AD7707の内部アナログ回路のグラウンド・リファレンス・ポイント。                                                                                                                                                                                                                                                                                         |

| 16   | DRDY             | ロジック出力。この出力がロジック・ローの場合、AD7707データ・レジスタから新たな出力ワードが得られることを示します。DRDYピンは、フル出力ワードの読み出し動作終了時にハイに戻ります。出力アップデート中にデータ読み出しが行われないと、DRDYラインは、次の出力アップデートの500×tclkinサイクル前に、ハイに戻ります。DRDYがハイの間は、アップデートされているデータ・レジスタからの読み出しを防ぐため、読み出し動作を試みたり、開始しないようにしてください。DRDYラインは、アップデートが発生した場合、再びローに戻ります。DRDYは、AD7707が内部キャリブレーション・シーケンスを終えた時間の表示にも使用します。 |

| 17   | DOUT             | 出力シフト・レジスタからシリアルデータを読み出すシリアル・データ出力。この出力シフト・レジスタは、通信レジスタのレジスタ選択ビットに応じて、セットアップレジスタ、通信レジスタ、クロック・レジスタ、データ・レジスタの情報を収集できます。                                                                                                                                                                                                      |

| 18   | DIN              | 入力シフト・レジスタに、シリアル・データを書き込むシリアルデータ入力。この入力のデータは、通信レジスタのレジスタ選択ビットに応じて、セットアップ・レジスタ、クロック・レジスタ、通信レジスタに伝送されます。                                                                                                                                                                                                                     |

| 19   | DV <sub>DD</sub> | デジタル電源電圧、 + 2.7~ + 5.25Vで動作。                                                                                                                                                                                                                                                                                               |

| 20   | DGND             | AD7707の内部デジタル回路のグラウンド・リファレンス・ポイント。                                                                                                                                                                                                                                                                                         |

#### 低レベル入力チャンネルの出力ノイズ(5/動作)

表Iは、非バッファ・モードでの選択ノッチと - 3dB周波数における、AD7707の出力rmsノイズと、ピークtoピーク分解能を示します。ノッチはクロック・レジスタのFS0、FS1、FS2によって選択されます。数値は、 $V_{REF}$  = +2.5V、 $AV_{DD}$  = 5Vにおけるバイポーラ入力範囲です。これらの数値はtyp値で、アナログ入力電圧0Vで生成されています。表IIは、非バッファ・モード動作時の、rmsノイズとピークtoピーク分解能を表します。ピークtoピークの数値が、コード・フリッカーのない分解能を表していることに注意してください。これらは、rmsノイズではなく、ピークtoピーク・ノイズに基づいて、計算されています。これは $V_{REF}$  = +2.5Vのバイポーラ入力範囲の数値です。これらの数値はtyp値で、最も近いLSBに丸め込みされています。数値は、0に設定されたクロック・レジスタのCLKDIVビットに適用されます。出力ノイズは、2つのノイズ源から発生します。第1は、モジュレータの実現に使用する、半導体デバイスの電気ノイズ(デバイス・ノイズ)。第2に、アナログ入力がデジタル領域に変換される時の定量化ノイズが加わります。デバイス・ノイズは低レベルで、周波数と無関係です。定量化ノイズはさらに低いレベルで始まりますが、周波数の増大に伴って急激に上昇して、主要なノイズ源となります。表の数値は、バイポーラ入力範囲についてです。ユニポーラ範囲については、rmsノイズ数値はバイポーラ範囲と同じになりますが、ピークtoピーク分解能は信号範囲の半分に基づくので、事実上、分解能1ビットを失うことになります。

表I. 出力RMSノイズ / ピーク to ピーク分解能 対 ゲインと出力アップデート・レート (+5 V) (AIN 1、AIN 2 非パッファ・モード時のみ)

| フィルタ第1          |         |            | μ V <b>単位の出力</b> RMS <b>ノイズ</b> typ <b>値(ピーク</b> to <b>ピーク分解能、ビット)</b> |              |             |               |             |               |               |  |

|-----------------|---------|------------|------------------------------------------------------------------------|--------------|-------------|---------------|-------------|---------------|---------------|--|

| <b>ノッチと</b> O/P | - 3dB   | ゲイン        | ゲイン                                                                    | ゲイン          | ゲイン         | ゲイン           | ゲイン         | ゲイン           | ゲイン           |  |

| データ速度           | 周波数     | 1          | 2                                                                      | 4            | 8           | 16            | 3 2         | 6 4           | 128           |  |

| MCLK IN = 2.4   | 1576MHz |            |                                                                        |              |             |               |             |               |               |  |

| 10Hz            | 2.62Hz  | 1.2 (16)   | 0.7 (16)                                                               | 0.7 (16)     | 0.54 (16)   | 0.28 (16)     | 0.28 (16)   | 0.28 (15.5)   | 0.27 ( 14.5 ) |  |

| 50Hz            | 13.1Hz  | 3.6 (16)   | 2.1 (16)                                                               | 1.25 (16)    | 0.89 (16)   | 0.62 (16)     | 0.60 (15)   | 0.56 (14.5)   | 0.56 (13.5)   |  |

| 60Hz            | 15.72Hz | 4.7 (16)   | 2.6 (16)                                                               | 1.5 (16)     | 0.94 (16)   | 0.73 (16)     | 0.68 (15)   | 0.66 (14)     | 0.63 (13)     |  |

| 250Hz           | 65.5Hz  | 95 (13)    | 65 (13)                                                                | 23.4 (13)    | 11.6 (13)   | 6.5 (13)      | 3.4 (13)    | 2.1 (13)      | 1.5 ( 12.5 )  |  |

| 500Hz           | 131Hz   | 600 (10.5) | 316 ( 10.5 )                                                           | 138 ( 10.5 ) | 71 ( 10.5 ) | 38 ( 10.5 )   | 18 ( 10.5 ) | 10 (10)       | 5.7 (10)      |  |

| MCLK IN = 1     | MHz     |            |                                                                        |              |             |               |             |               |               |  |

| 4.05Hz          | 1.06Hz  | 1.26 (16)  | 0.716 ( 16 )                                                           | 0.703 (16)   | 0.653 (16)  | 0.3 (16)      | 0.3 (16)    | 0.28 ( 15.5 ) | 0.27 ( 14.5 ) |  |

| 20Hz            | 5.24Hz  | 1.76 (16)  | 0.95 (16)                                                              | 0.61 (16)    | 0.46 (16)   | 0.29 (16)     | 0.29 (16)   | 0.29 (15.5)   | 0.28 ( 14.5 ) |  |

| 25Hz            | 6.55Hz  | 2.5 (16)   | 1.3 (16)                                                               | 0.74 (16)    | 0.51 (16)   | 0.35 (16)     | 0.33 (16)   | 0.32 (15)     | 0.32 (14)     |  |

| 100Hz           | 26.2Hz  | 43 (14)    | 26.4 ( 14 )                                                            | 12.2 ( 14 )  | 5.8 (14)    | 3.2 (14)      | 1.7 (14)    | 1.06 ( 13.5 ) | 0.78 (13)     |  |

| 200Hz           | 52.4Hz  | 267 (11.5) | 151 (11.5)                                                             | 72 ( 11.5 )  | 33 (11.5)   | 15.4 ( 11.5 ) | 9 (11.5)    | 4.8 (11.5)    | 2.9 ( 11.5 )  |  |

8

表II. 出力RMSノイズ / ピークtoピーク分解能 対 ゲインと出力アップデート・レート (+5 V時) (AIN 1、AIN 2 パッファ・モード時のみ)

| フィルタ第1          |         |              | μ V <b>単位の出</b> 力RMS <b>ノイズ</b> typ <b>値(ピーク</b> to <b>ピーク分解能、ビット)</b> |              |           |               |               |               |               |  |

|-----------------|---------|--------------|------------------------------------------------------------------------|--------------|-----------|---------------|---------------|---------------|---------------|--|

| <b>ノッチと</b> O/P | - 3dB   | ゲイン          | ゲイン                                                                    | ゲイン          | ゲイン       | ゲイン           | ゲイン           | ゲイン           | ゲイン           |  |

| データ速度           | 周波数     | 1            | 2                                                                      | 4            | 8         | 16            | 32            | 6 4           | 128           |  |

| MCLK IN = 2.4   | 576MHz  |              |                                                                        |              |           |               |               |               |               |  |

| 10Hz            | 2.62Hz  | 1.47 (16)    | 0.95 (16)                                                              | 0.88 (16)    | 0.55 (16) | 0.42 (16)     | 0.42 (16)     | 0.42 (14)     | 0.41 (14)     |  |

| 50Hz            | 13.1Hz  | 4.2 (16)     | 2.6 (16)                                                               | 1.6 (16)     | 1 (16)    | 0.89 (15.5)   | 0.94 ( 14.5 ) | 0.9 (14)      | 0.9 (13)      |  |

| 60Hz            | 15.72Hz | 4.9 (16)     | 3 (16)                                                                 | 1.8 (16)     | 1.1 (16)  | 1 (15.5)      | 1 (14.5)      | 0.94 ( 14 )   | 0.94 (13)     |  |

| 250Hz           | 65.5Hz  | 104 (13)     | 52 (13)                                                                | 26 (13)      | 14 (13)   | 6.5 (13)      | 4.1 ( 12.5 )  | 2.7 (12)      | 2.3 (11)      |  |

| 500Hz           | 131Hz   | 572 ( 10.5 ) | 293 ( 10.5 )                                                           | 125 ( 10.5 ) | 69 (10.5) | 40 (10)       | 19 (10)       | 10 (10)       | 5.9 (10)      |  |

| MCLK IN = 1     | MHz     |              |                                                                        |              |           |               |               |               |               |  |

| 4.05Hz          | 1.06Hz  | 1.35 ( 16 )  | 0.967 (16)                                                             | 0.83 (16)    | 0.66 (16) | 0.45 (16)     | 0.43 (16)     | 0.43 (15)     | 0.43 ( 14 )   |  |

| 20Hz            | 5.24Hz  | 2.27 (16)    | 1.41 (16)                                                              | 1 (16)       | 0.8 (16)  | 0.49 (16)     | 0.46 (16)     | 0.45 ( 14.5 ) | 0.45 ( 13.5 ) |  |

| 25Hz            | 6.55Hz  | 2.82 (16)    | 1.79 (16)                                                              | 1.18 (16)    | 0.9 (16)  | 0.56 (16)     | 0.56 (15.5)   | 0.49 ( 14.5 ) | 0.49 ( 13.5 ) |  |

| 100Hz           | 26.2Hz  | 51 (14)      | 26 (14)                                                                | 11 (14)      | 6.5 (14)  | 3.48 ( 13.5 ) | 1.9 ( 13.5 )  | 1.35 ( 13 )   | 1.1 ( 12.5 )  |  |

| 200Hz           | 52.4Hz  | 254 ( 11.5 ) | 132 (11.5)                                                             | 60 (11.5)    | 34 (11.5) | 16.5 (11.5)   | 8.7 (11.5)    | 4.9 (11)      | 2.8 ( 11 )    |  |

#### 低レベル入力チャンネルの出力ノイズ(3/動作)

表IIIは、非バッファ・モード時での選択ノッチと - 3dB周波数における、AD7707の出力rmsノイズと、ピークtoピーク分解能を示します。ノッチはクロック・レジスタのFSO、FS1、FS2によって選択されます。数値は、 $V_{REF}$  = +1.225V、AVDD = 3Vにおけるバイポーラ入力範囲です。これらの数値はtyp値で、アナログ入力電圧0Vで生成されています。表IVは、非バッファ・モード動作時の、rmsノイズとピークtoピーク分解能を表します。ピークtoピークの数値が、コード・フリッカーのない分解能を表していることに注意してください。これらは、rmsノイズではなく、ピークtoピークノイズに基づいて計算されます。数値は $V_{REF}$  = +1.225Vのバイポーラ入力範囲のもので、バッファ・モード、非バッファ・モード両方のものです。これらの数値はtyp値で、最も近いLSBに丸め込みされます。数値は、0に設定されたクロック・レジスタのCLKDIVビットに適用されます。出力ノイズには2つのノイズ源があります。第1は、モジュレータの実現に使用する、半導体デバイスの電気ノイズ(デバイス・ノイズ)。第2に、アナログ入力がデジタル領域に変換される時の定量化ノイズが加わります。デバイスノイズは低レベルで、周波数と無関係です。定量化ノイズはさらに低いレベルで始まりますが、周波数増大に伴って急激に上昇して、主要なノイズ源となります。表の数値は、バイポーラ入力範囲についてです。ユニポーラ範囲については、rmsノイズ数値はバイポーラ範囲と同じになりますが、ピークtoピーク分解能は信号範囲の半分に基づくので、事実上、分解能1ビットを失うことになります。

表III. 出力RMS Jイズ / ピーク to ピーク分解能 対 ゲインと出力アップデート・レート (+3 V) (AIN 1、AIN 2 非パッファ・モードのみ)

| フィルタ第1          |         |            | μV           | <b>単位の出力</b> RI | MS <b>ノイズ</b> ty <sub>l</sub> | p <b>値(ピーク</b> t | ○ピーク分解値      | 能、ビット)       |             |

|-----------------|---------|------------|--------------|-----------------|-------------------------------|------------------|--------------|--------------|-------------|

| <b>ノッチと</b> O/P | - 3dB   | ゲイン        | ゲイン          | ゲイン             | ゲイン                           | ゲイン              | ゲイン          | ゲイン          | ゲイン         |

| データ速度           | 周波数     | 1          | 2            | 4               | 8                             | 16               | 3 2          | 6 4          | 128         |

| MCLK IN = 2.4   | 576MHz  |            |              |                 |                               |                  |              |              |             |

| 10Hz            | 2.62Hz  | 1.60 (16)  | 0.8 (16)     | 0.48 (16)       | 0.29 (16)                     | 0.29 (16)        | 0.27 (15.5)  | 0.26 (14.5)  | 0.26 (13.5) |

| 50Hz            | 13.1Hz  | 3.8 (16)   | 1.9 (16)     | 1.1 (16)        | 0.64 (16)                     | 0.60 (15)        | 0.6 (14)     | 0.6 (13)     | 0.6 (12)    |

| 60Hz            | 15.72Hz | 4.4 (16)   | 2.2 (16)     | 1.35 (16)       | 0.78 (16)                     | 0.7 (15)         | 0.68 (14)    | 0.64 (13)    | 0.64 (12)   |

| 250Hz           | 65.5Hz  | 53 (13)    | 24 (13)      | 15 ( 12.5 )     | 6.8 (13.5)                    | 3.6 (12.5)       | 2.1 (12.5)   | 1.5 ( 12 )   | 1.3 (11)    |

| 500Hz           | 131Hz   | 300 (10.5) | 138 ( 10.5 ) | 80 (10.5)       | 34 ( 10.5 )                   | 18 ( 10.5 )      | 8.7 ( 10.5 ) | 4.8 (10)     | 3.4 (10)    |

| MCLK IN = 1     | MHz     |            |              |                 |                               |                  |              |              |             |

| 4.05Hz          | 1.06Hz  | 1.45 (16)  | 0.713 (16)   | 0.494 (16)      | 0.273 (16)                    | 0.252 (16)       | 0.30 (15)    | 0.24 ( 15 )  | 0.24 ( 14 ) |

| 20Hz            | 5.24Hz  | 1.98 (16)  | 1.04 (16)    | 0.56 (16)       | 0.33 (16)                     | 0.3 (16)         | 0.3 (15)     | 0.3 (14)     | 0.3 (13)    |

| 25Hz            | 6.55Hz  | 2.3 (16)   | 1.2 (16)     | 0.66 (16)       | 0.41 (16)                     | 0.34 (16)        | 0.33 (15)    | 0.32 (14)    | 0.32 (13)   |

| 100Hz           | 26.2Hz  | 24.6 (14)  | 14 (14)      | 6.4 (14)        | 3.3 (14)                      | 1.63 ( 14 )      | 1 (13.5)     | 0.8 (13)     | 0.65 (12)   |

| 200Hz           | 52.4Hz  | 136 (11.5) | 67 (11.5)    | 32.5 ( 11.5 )   | 17.3 ( 11.5 )                 | 8.9 ( 11.5 )     | 4.4 ( 11.5 ) | 2.3 ( 11.5 ) | 1.6 ( 11 )  |

表IV. 出力RMSノイズ / ピークtoピーク分解能 対 ゲインと出力アップデート・レート (+3V) (AIN1、AIN2パッファ・モードのみ)

| フィルタ第1          |         |              | μV           | <b>単位の出力</b> R | MS <b>ノイズ</b> ty | p <b>値(ピーク</b> t | o <b>ピーク分解</b> ℓ | 兆、ビット)        |               |

|-----------------|---------|--------------|--------------|----------------|------------------|------------------|------------------|---------------|---------------|

| <b>ノッチと</b> O/P | - 3dB   | ゲイン          | ゲイン          | ゲイン            | ゲイン              | ゲイン              | ゲイン              | ゲイン           | ゲイン           |

| データ速度           | 周波数     | 1            | 2            | 4              | 8                | 16               | 32               | 6 4           | 128           |

| MCLK IN = 2.4   | 576MHz  |              |              |                |                  |                  |                  |               |               |

| 10Hz            | 2.62Hz  | 1.80 (16)    | 1 (16)       | 0.7 (16)       | 0.41 (16)        | 0.41 (16)        | 0.41 (15)        | 0.41 (14)     | 0.41 (13)     |

| 50Hz            | 13.1Hz  | 4.1 (16)     | 2.4 (16)     | 1.5 (16)       | 1 (15.5)         | 0.91 (14.5)      | 0.89 ( 13.5 )    | 0.86 (12.5)   | 0.83 (12)     |

| 60Hz            | 15.72Hz | 5.1 (16)     | 3 (16)       | 1.8 (16)       | 1.1 ( 15.5 )     | 0.94 ( 14.5 )    | 0.94 ( 13.5 )    | 0.99 ( 12.5 ) | 0.99 (11.5)   |

| 250Hz           | 65.5Hz  | 50 (13)      | 27 (13)      | 12.3 (13)      | 6.4 (13)         | 4 ( 12.5 )       | 2.7 (12)         | 2.2 (11.5)    | 1.8 (11)      |

| 500Hz           | 131Hz   | 275 ( 10.5 ) | 125 ( 10.5 ) | 80 ( 10.5 )    | 39 ( 10.5 )      | 16 ( 10.5 )      | 8.9 ( 10.5 )     | 5.2 (10)      | 4.2 ( 9.5 )   |

| MCLK IN = 1     | MHz     |              |              |                |                  |                  |                  |               |               |

| 4.05Hz          | 1.06Hz  | 7.72 (16)    | 1.3 (16)     | 0.73 (16)      | 0.41 (16)        | 0.41 (16)        | 0.41 (15)        | 0.41 (14)     | 0.41 (13)     |

| 20Hz            | 5.24Hz  | 2.14 ( 16 )  | 1.22 (16)    | 0.71 (16)      | 0.5 (16)         | 0.47 ( 15.5 )    | 0.47 ( 14.5 )    | 0.45 ( 13.5 ) | 0.42 (13)     |

| 25Hz            | 6.55Hz  | 2.5 (16)     | 1.4 (16)     | 0.88 (16)      | 0.54 (16)        | 0.53 ( 15.5 )    | 0.50 ( 14.5 )    | 0.50 ( 13.5 ) | 0.50 ( 12.5 ) |

| 100Hz           | 26.2Hz  | 24.5 ( 14 )  | 12.6 (14)    | 6.3 (14)       | 3.1 (14)         | 1.87 ( 13.5 )    | 1.2 ( 13 )       | 1.1 ( 12.5 )  | 1 (11.5)      |

| 200Hz           | 52.4Hz  | 133 ( 11.5 ) | 70 (11.5)    | 37 (11.5)      | 18 ( 11.5 )      | 8.4 ( 11.5 )     | 4.2 ( 11.5 )     | 2.4 ( 11 )    | 2.1 ( 10.5 )  |

#### 高レベル入力チャンネルAIN3の出力ノイズ(5V動作)

表Vは、非バッファ・モード時での選択ノッチと - 3dB周波数におけるAD7707の出力rmsノイズと、ピークtoピーク分解能を示しています。ノッチはクロックレジスタのFS0、FS1、FS2で選別します。数値は、 $V_{REF}$  = +2.5V、HBIAS = 2.5V、HICOM = AGND、AV<sub>DD</sub> = 5Vで、 $\pm$ 10V、 $\pm$ 5V、0  $\sim$  5V、0  $\sim$  +10Vの範囲でのものです。これらの数値はtyp値で、アナログ入力電圧0Vで生成されています。一方、表VIは、バッファ・モードにおける、出力rmsノイズとピークtoピーク分解能を示しています。ピークtoピーク数値が、コード・フリッカーのない分解能を表していることに注意してください。これらは、rmsノイズではなく、ピークtoピーク・ノイズに基づいて計算されます。バイポーラ・モードで、ゲイン2で高レベル・チャンネルを動作させると、 $\pm$ 10Vの動作範囲が得られます。ユニポーラ・モードで、ゲイン2で動作させると、0  $\sim$  +10Vの動作範囲が得られます。バイポーラ・モードで、ゲイン4で高レベル・チャンネルを動作させると、 $\pm$ 5Vの動作範囲が得られます。ユニポーラ・モードで、ゲイン4で動作させると、0  $\sim$ 5Vの動作範囲が得られます。すべての入力範囲でのノイズは、付属書1に掲載されています。出力ノイズは、2つのノイズ源から発生します。第1は、モジュレータの実現に使用する、半導体デバイスの電気ノイズ(デバイス・ノイズ)。第2に、アナログ入力がデジタル領域に変換される時の定量化ノイズが加わります。デバイス・ノイズは低レベルで、周波数と無関係です。定量化ノイズはさらに低いレベルで始まりますが、周波数の増大に伴って急激に上昇して、主要なノイズ源となります。表の数値は、バイポーラ入力範囲についてです。ユニポーラ範囲については、rmsノイズ数値はバイポーラ範囲と同じになりますが、ピークtoピーク分解能は信号範囲の半分に基づくので、事実上、分解能1ビットを失うことになります。

表 $\lor$ . 出力RMSノイズ/ピークtoピーク分解能 対 ゲインと出力アップデート・レート ( + 5 $\lor$  ) ( AIN 3 非パッファ・モードのみ )

| フィルタ第1        |         | ± 1 0  | ∨範囲               | ± 5\   | /範囲               | 0 ~ + 1 | 0 V範囲             | 0 ~ +       | 5 V <b>範囲</b>     |

|---------------|---------|--------|-------------------|--------|-------------------|---------|-------------------|-------------|-------------------|

| ノッチとO/P       | - 3dB   | RMSノイズ | P-P( <b>ビット</b> ) | RMSノイズ | P-P( <b>ビット</b> ) | RMSノイズ  | P-P( <b>ビット</b> ) | RMSノイズ      | P-P( <b>ビット</b> ) |

| データ速度         | 周波数     | (µ∨)   | 分解能               | (μV)   | 分解能               | (µV)    | 分解能               | <b>(μV)</b> | 分解能               |

| MCLK IN = 2.4 | 4576MHz |        |                   |        |                   |         |                   |             | _                 |

| 10Hz          | 2.62Hz  | 5.10   | 16                | 3.52   | 16                | 5.10    | 16                | 3.52        | 16                |

| 50Hz          | 13.1Hz  | 15.82  | 16                | 9.77   | 16                | 15.82   | 16                | 9.77        | 16                |

| 60Hz          | 15.72Hz | 20.36  | 16                | 12.29  | 16                | 20.36   | 16                | 12.29       | 16                |

| 250Hz         | 65.5Hz  | 430    | 13                | 212    | 13                | 430     | 12                | 212         | 12                |

| 500Hz         | 131Hz   | 2350   | 10                | 1287   | 10                | 2350    | 9                 | 1287        | 9                 |

| MCLK IN = 1   | MHz     |        |                   |        |                   |         |                   |             |                   |

| 4.05Hz        | 1.06Hz  | 5.13   | 16                | 3.53   | 16                | 5.13    | 16                | 3.53        | 16                |

| 20Hz          | 5.24Hz  | 18.9   | 16                | 13.25  | 16                | 18.9    | 16                | 13.25       | 16                |

| 25Hz          | 6.55Hz  | 23.7   | 16                | 15.3   | 16                | 23.7    | 16                | 15.3        | 15.5              |

| 100Hz         | 26.2Hz  | 406    | 13                | 174    | 13                | 406     | 12                | 174         | 12                |

| 200Hz         | 52.4Hz  | 2184   | 10.5              | 1144   | 10.5              | 2184    | 9.5               | 1144        | 9.5               |

| フィルタ第1          |         | ± 1 0  | V <b>範囲</b> | ± 5\   | /範囲               | 0 ~ + 1 | 0 V 範囲   | 0 ~ + 5 | 5 V <b>範囲</b>     |

|-----------------|---------|--------|-------------|--------|-------------------|---------|----------|---------|-------------------|

| <b>ノッチと</b> O/P | - 3dB   | RMSノイズ | P-P(ビット)    | RMSノイズ | P-P( <b>Ľット</b> ) | RMSノイズ  | P-P(ビット) | RMSノイズ  | P-P( <b>ビット</b> ) |

| データ速度           | 周波数     | (µV)   | 分解能         | (µV)   | 分解能               | (µV)    | 分解能      | (µV)    | 分解能               |

| MCLK IN = 2.4   | 576MHz  |        |             |        |                   |         |          |         | _                 |

| 10Hz            | 2.62Hz  | 7.4    | 16          | 5.2    | 16                | 7.4     | 16       | 5.2     | 16                |

| 50Hz            | 3.1Hz   | 22.2   | 16          | 14.3   | 16                | 22.2    | 16       | 14.3    | 16                |

| 60Hz            | 15.72Hz | 26.6   | 16          | 15.85  | 16                | 26.6    | 16       | 15.85   | 16                |

| 250Hz           | 65.5Hz  | 475    | 13          | 187    | 13                | 475     | 12       | 18      | 12                |

| 500Hz           | 131Hz   | 2423   | 10.5        | 1097   | 10.5              | 2423    | 9.5      | 1097    | 9.5               |

| MCLK IN = 1     | MHz     |        |             |        |                   |         |          |         |                   |

| 4.05Hz          | 1.06Hz  | 7.63   | 16          | 5.45   | 16                | 7.63    | 16       | 5.45    | 16                |

| 20Hz            | 5.24Hz  | 20.25  | 16          | 13.3   | 16                | 20.25   | 16       | 13.3    | 16                |

| 25Hz            | 6.55Hz  | 23.5   | 16          | 14.6   | 16                | 23.5    | 16       | 14.6    | 15.5              |

| 100Hz           | 26.2Hz  | 377    | 13          | 210    | 13                | 377     | 12       | 210     | 12                |

| 200Hz           | 52.4Hz  | 2226   | 10.5        | 1132   | 10.5              | 2226    | 9.5      | 1132    | 9.5               |

#### 高レベル入力チャンネルAIN3の出力ノイズ(5V動作)

表VIIは、選択ノッチと - 3dB周波数におけるAD7707の出力rmsノイズと、ピークtoピーク分解能を示しています。ノッチはクロック・レジスタのFS0、FS1、FS2で選別します。数値は、 $V_{REF}$  = +1.225V、HBIAS = 1.225V、HICOM = AGND、AVDD = 3Vで、 $\pm$ 5V、0~+5V、0~+10Vの範囲でのものです。これらの数値はtyp値で、非バッファ・モード動作のアナログ入力電圧0Vで生成されています。上述の動作範囲は、入力アンプのコモン・モードの制限のため、3V動作の場合、非バッファ・モードでのみで実現できます。ピークtoピーク数値が、コード・フリッカーのない分解能を表していることに注意してください。これらは、rmsノイズではなく、ピークtoピーク かノイズに基づいて計算されます。ユニポーラ・モードで、ゲイン1で動作させると、0~+10Vの動作範囲が得られます。バイポーラ・モードで、ゲイン2で高レベル・チャンネルを動作させると、 $\pm$ 5Vの動作範囲が得られます。コニポーラ・モードで、ゲイン2で動作させると、0~+5Vの動作範囲が得られます。出力ノイズは、2つのノイズ源から発生します。第1は、モジュレータの実現に使用する、半導体デバイスの電気ノイズ(デバイス・ノイズ)。第2に、アナログ入力がデジタル領域に変換される時の定量化ノイズが加わります。デバイス・ノイズは低レベルで、周波数と無関係です。定量化ノイズはさらに低いレベルで始まりますが、周波数の増大に伴って急激に上昇して、主要なノイズ源となります。表の数値は、バイポーラ入力範囲についてです。ユニポーラ範囲については、rmsノイズ数値は、バイポーラ範囲と同じになりますが、ピークtoピーク分解能は信号範囲の半分に基づくので、事実上、分解能1ビットを失うことになります。

| フィルタ第1          |         | 0 ~ +  | 10V <b>範囲</b>     | ±      | 5 V <b>範囲</b>     | 0 ~    | + 5 V <b>範囲</b>   |

|-----------------|---------|--------|-------------------|--------|-------------------|--------|-------------------|

| <b>ノッチと</b> O/P | - 3dB   | RMSノイズ | P-P( <b>ビット</b> ) | RMSノイズ | P-P( <b>ビット</b> ) | RMSノイズ | P-P( <b>ビット</b> ) |

| データ速度           | 周波数     | (μV)   | 分解能               | (μV)   | 分解能               | (µV)   | 分解能               |

| MCLK IN = 2.4   | 1576MHz |        |                   |        |                   |        |                   |

| 10Hz            | 2.62Hz  | 12.4   | 16                | 7.02   | 16                | 7.02   | 16                |

| 50Hz            | 13.1Hz  | 30.35  | 16                | 16.4   | 16                | 16.4   | 15.5              |

| 60Hz            | 15.72Hz | 34.55  | 16                | 19.13  | 16                | 19.13  | 15                |

| 250Hz           | 65.5Hz  | 498    | 12.5              | 204    | 13                | 204    | 12                |

| 500Hz           | 131Hz   | 2266   | 10.5              | 1151   | 10.5              | 1151   | 9.5               |

| MCLK IN = 1     | MHz     |        |                   |        |                   |        |                   |

| 4.05Hz          | 1.06Hz  | 13.9   | 16                | 7.3    | 16                | 7.3    | 16                |

| 20Hz            | 5.24Hz  | 32.2   | 16                | 17.4   | 16                | 17.4   | 15                |

| 25Hz            | 6.55Hz  | 33.4   | 16                | 18.57  | 16                | 18.57  | 15                |

| 100Hz           | 26.2Hz  | 430    | 13                | 200    | 13                | 200    | 12                |

| 200Hz           | 52.4Hz  | 2207   | 10.5              | 1048   | 10.5              | 1048   | 9.5               |

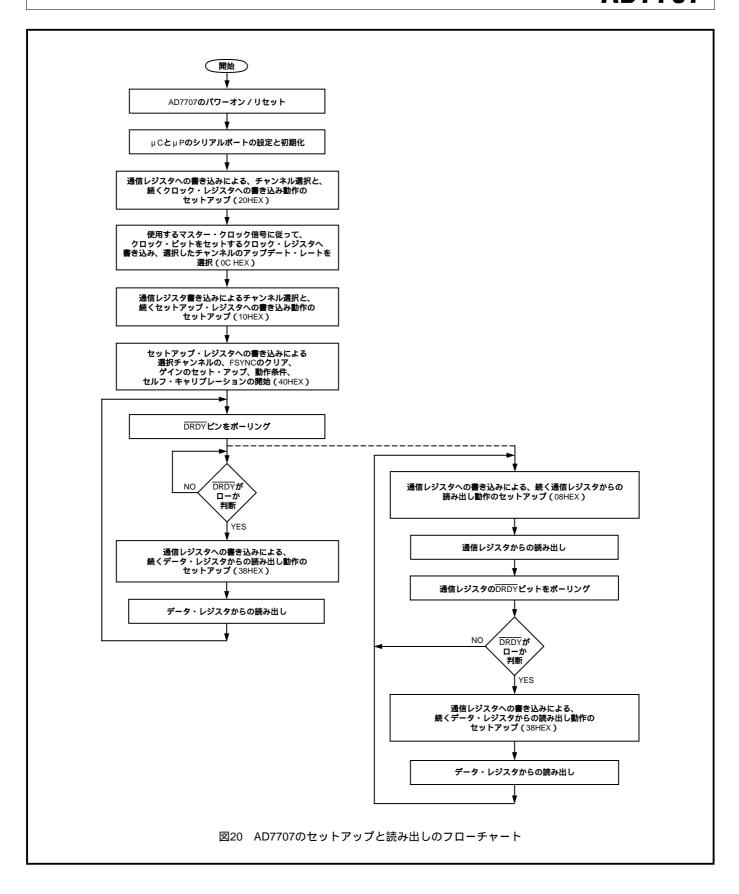

#### 内部レジスタ

AD7707は、シリアル・ポート経由でアクセスできる、8個のレジスタを内蔵しています。第1はチャンネル選択を制御する通信レジスタで、次の動作が読み出し / 書き込みのどちらかを決定し、どのレジスタに次の読み出し / 書き込み動作がアクセスするかを決定します。AD7707へのすべての通信は、通信レジスタへの書き込み動作から始まります。電源オンまたはRESETの後、デバイスは通信レジスタへの書き込みを予想します。このレジスタに書き込まれたデータによって、次の動作が書き込み / 読み出しのどちらかが決定され、また、どのレジスタにこの読み出し / 書き込み動作が発生するかも決定します。従って、AD7707の他のレジスタへの書き込みアクセスは、通信レジスタへの書き込みで始まり、その後に選択したレジスタへの書き込みが行われます。また、他のレジスタからの読み出し動作(通信レジスタ自体と、出力データ・レジスタを含む)は、通信レジスタへの書き込み動作で始まり、その後に選択したレジスタからの読み出し動作が行われます。通信レジスタはまた、スタンバイ・モードとチャンネル選択を制御し、通信レジスタからの読み出しによって DRDY 状態も得られます。第2のレジスタはキャリブレーション・モード、ゲイン設定、バイポーラ / ユニポーラ動作、バッファ・モードを判定する、セットアップ・レジスタです。第3のレジスタは、クロック・レジスタと呼ばれ、フィルタ選択ビットとクロック制御ビットを内蔵しています。第4のレジスタは、AD7707の出力データにアクセスできる、データ・レジスタです。最後のレジスタは、チャンネル・キャリブレーション・データを保存する、キャリブレーション・レジスタです。レジスタについては、次項で詳しく扱います。

#### 通信レジスタ(RS2、RS1、RS0=0、0、0)

通信レジスタは、データの読み出し/書き込みができる、8ビットレジスタです。AD7707とのすべての通信は、通信レジスタへの書き込み動作から始めなければなりません。通信レジスタに書き込まれるデータによって、次の動作が読み出し/書き込みのどちらかと、どのレジスタで動作が発生するかが決定します。選択したレジスタへの、次の読み出し/書き込み動作が終了すると、インターフェースは通信レジスタへの書き込み動作を予想する場所へ戻ります。これはインターフェースのデフォルト状態で、AD7707は電源オン時やRESET後にこのデフォルト状態になり、通信レジスタへの書き込み動作を待ちます。インターフェース・シーケンスが失われている状態で、DINハイで、十分な長さの書き込み動作、最低32シリアル・クロック・サイクルが発生すると、AD7707がこのデフォルト状態に戻ります。表VIIIは、通信レジスタのビット指定を表しています。

表 / III. 通信レジスタ

| 0/DRDY (0) | RS2 (0) | RS1 (0) | RS0 (0) | R/W (0) | STBY(0) | CH1 (0) | CH0 (0) |

|------------|---------|---------|---------|---------|---------|---------|---------|

|            | 1       |         |         | 1       |         |         |         |

0/DRDY 書き込み動作では、通信レジスタへの書き込み動作を発生させるために、このビットに「0」を書き込む必要があります。このビットに「1」を書き込むと、AD7707はレジスタの後続ビットへクロック・オンしません。このビットに「0」が書き込まれるまで、このビット位置に留まります。このビットに「0」が書き込まれると、次の7つのビットが通信レジスタにロードされます。読み出し動作では、このビットは、DRDYフラグの状態を提供します。このビットの状態は、DRDY出力ピンと同じです。

RS2~RS0 レジスタ選択ビット。これら3ビットは、8個の内蔵レジスタの内、どれに次の読み出し/書き込み動作が行われるかを、表IX の通りレジスタ・サイズに従って選択します。選択したレジスタの読み出し/書き込み動作が終わると、AD7707は通信レジスタへの書き込み動作を待っている状態に戻ります。AD7707は、レジスタにアクセスし続ける状態には留まりません。

表IX. レジスタ選択

| RS2 | RS1 | RS0 | レジスタ        | レジスタ・サイズ |

|-----|-----|-----|-------------|----------|

| 0   | 0   | 0   | 通信レジスタ      | 8ビット     |

| 0   | 0   | 1   | セットアップ・レジスタ | 8ビット     |

| 0   | 1   | 0   | クロック・レジスタ   | 8ビット     |

| 0   | 1   | 1   | データ・レジスタ    | 16ビット    |

| 1   | 0   | 0   | テスト・レジスタ    | 8ビット     |

| 1   | 0   | 1   | 動作なし        |          |

| 1   | 1   | 0   | オフセット・レジスタ  | 24ビット    |

| 1   | 1   | 1   | ゲイン・レジスタ    | 24ビット    |

- Read/Write選択。このビットは、選択したレジスタの次の動作が読み出し/書き込み動作のどちらかを選択します。「0」は、該当レジスタの次の動作の書き込みサイクルを表し、「1」は、該当レジスタの読み出し動作を表します。

- STBY スタンバイ。このビットに「1」を書き込むと、AD7707はスタンバイまたはパワーダウン・モードになります。このモードでのAD7707の消費電力は、わずか8 μ Aです。AD7707は、スタンバイ状態でもキャリブレーション係数と制御ワード情報を保持します。このビットに「0」を書き込むと、AD7707は通常動作モードに入ります。AD7707のシリアル・インターフェースは、STBYモードでも動作できます。

- CH1~CH0 チャンネル選択。これら2つのビットは、表Xの通り、変換または、キャリブレーション係数にアクセスするチャンネルを選択します。チャンネルのキャリブレーションの後、キャリブレーション係数を保存するために3対のキャリブレーション・レジスタを使用します。これらは表VIIに掲載され、どのチャンネル組み合せが、独立のキャリブレーション係数を備えているかを示します。CH1をロジック1、CH0をロジック0にすると、AD7707はそれ自体に内部ショートされたLOCOM入力を調べます。これは、外部ノイズ源のない状態で部品のノイズ性能を評価する試験法として用いられます。このモードでは、LOCOM入力をAD7707の許容コモン・モード範囲内の外部電源に接続します。

表X. AD7707のチャンネル選択

| CH1 | CH0 | AIN   | リファレンス | キャリプレーション・レジスタ・ペア |

|-----|-----|-------|--------|-------------------|

| 0   | 0   | AIN1  | LOCOM  | レジスタ・ペア0          |

| 0   | 1   | AIN2  | LOCOM  | レジスタ・ペア1          |

| 1   | 0   | LOCOM | LOCOM  | レジスタ・ペア0          |

| 1   | 1   | AIN3  | HICOM  | レジスタ・ペア2          |

**セットアップ・レジスタ(RS2、RS1、RS0=0、0、1);電源オン/リセット状態:**01Hex

セットアップ・レジスタは、データを読み出し/書き込みできる、8ビット・レジスタです。表XIは、セットアップレジスタのビット指定を示します。

#### 表XI セットアップ・レジスタ

| MD1 (0) MD0 (0) G2 (0) G1 (0) G0 (0) B/U (0) BUF (0) FSYNC |

|------------------------------------------------------------|

|------------------------------------------------------------|

| MD1 | MD0 | 動作モード                                                                                                                                                                                                                                                                                                           |

|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 通常モード:これは、デバイスが通常の変換を実行している、デバイス動作の通常モードです。                                                                                                                                                                                                                                                                     |

| 0   | 1   | セルフ・キャリブレーション:これは、通信レジスタのCH1とCH0が選択したチャンネルで、セルフ・キャリブレーションを起動します。ワンステップのキャリブレーション・シーケンスなので、完了すると部品は通常モードに戻り、MD1とMD0はそれぞれ0に戻ります。DRDY出力またはビットは、キャリブレーションが始まるとハイになり、キャリブレーションが終わるとローに戻り、データ・レジスタに新たに有効ワードが印加できます。ゼロスケール・キャリブレーションは、内部短絡(ゼロ)入力の選択ゲインで行われ、フルスケール・キャリブレーションは、内部生成のV <sub>REF</sub> /選択ゲインの選択ゲインで実行します。 |

| 1   | 0   | ゼロスケール・システム・キャリブレーション。通信レジスタのCH1とCH0が選択するチャンネルで、ゼロスケール・システム・キャリブレーションを起動します。このキャリブレーション・シーケンス中、アナログ入力の入力電圧の選択ゲインで、キャリブレーションを実行します。入力電圧はキャリブレーションの期間中、安定していることが必要です。DRDY出力またはビットは、キャリブレーションが始まるとハイになり、ゼロスケール・キャリブレーションが終わるとローに戻り、データ・レジスタに新たに有効ワードが印加できます。キャリブレーションが完了すると部品は通常モードに戻り、MD1とMD2はそれぞれ0に戻ります。         |

| 1   | 1   | フルスケール・システム・キャリブレーション:選択した入力チャンネルで、フルスケール・システム・キャリブレーションを起動します。このキャリブレーション・シーケンス中、アナログ入力の入力電圧の選択ゲインで、キャリブレーションを行います。キャリブレーション期間中、この入力電圧は、安定していること。同じく、DRDY出力またはビットは、キャリブレーションが始まると、ハイになり、フルスケール・システム・キャリブレーションが終わると、ローに戻り、データ・レジスタに新たに有効ワードが印加できます。キャリブレーションが完了すると部品は通常モードに戻り、MD1とMD2はそれぞれ0に戻ります。               |

G2~G0 ゲイン選択ビット。表XIIの通り、これらのビットは、内蔵PGAのゲイン設定を選択します。

表XII. ゲイン選択

|    |    |    | •     |

|----|----|----|-------|

| G2 | G1 | G0 | ゲイン設定 |

| 0  | 0  | 0  | 1     |

| 0  | 0  | 1  | 2     |

| 0  | 1  | 0  | 4     |

| 0  | 1  | 1  | 8     |

| 1  | 0  | 0  | 16    |

| 1  | 0  | 1  | 32    |

| 1  | 1  | 0  | 64    |

| 1  | 1  | 1  | 128   |

Bipolar/Unipolar動作。このビットが「0」の場合、Bipolar動作を選びます。このビットが「1」の場合、ユニポーラ動作を選びます。

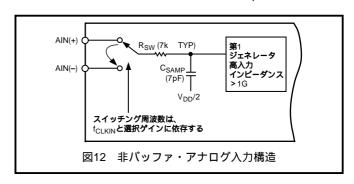

BUF バッファ制御。このビットが「0」では、アナログ入力のオンチップ・バッファがショートします。バッファがショートすると、Vppラインを流れる電流が減ります。このビットがハイの場合、内蔵バッファがアナログ入力と直列になり、入力がより高い電源インピーダンスを扱えます。

FSYNC フィルタ同期。このビットが八イの場合、デジタル・フィルタのノード、フィルタ制御ロジック、キャリブレーション制御ロジックはリセット状態に保持され、アナログ・モジュレータもリセット状態に保持されます。このビットがローになると、モジュレータとフィルタがデータ処理を開始し、有効なワードは、3×1/(出力アップデート・レート)、すなわちフィルタのセトリング・タイムで使用できます。FSYNCビットは、デジタル・インターフェースに影響せず、もしローなら、DRDY出力をリセットしません。

クロック・レジスタ (RS2、RS1、RS0=0、1、0);電源オン/リセット状態:05Hex

クロック・レジスタは、データを読み出し/書き込みできる8ビット・レジスタです。XIIIは、クロック・レジスタのビット指定を示します。

#### 表XIII. クロック・レジスタ

| ZERO (0)   ZERO (0)   CLKDIS (0)   CLKDIS (0)   CLK (1)   FS2 (0)   FS1 (0)   FS0 |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

ZERO ゼロ。AD7707の正しい動作を保証するために、これらのビットにゼロを書き込む必要があります。これをしないと、デバイスが仕様外の動作を行います。

CLKDIS マスター・クロック・ディスエーブル・ビット。このビットがロジック1の場合、マスター・クロックは MCLKOUTピンに現れません。MCLKOUTピンは、ディスエーブルの時、強制的にローになります。この機能により、MCLKOUTをシステムの他のデバイスのクロック・ソースとして使う柔軟性が得られ、また MCLKOUTをオフにして電力削減も可能です。MCLKINピンを外部マスター・クロックとして使う場合、AD7707は、内部クロックを保持し、通常CLKDISビットをアクティブにして変換します。MCKLINとMCLK-OUTピンの間にクリスタル・オシレータかセラミック共振器を使用すると、AD7707のクロックは停止し、CLKDISビットがアクティブの時も変換は起こりません。

CLKDIV クロック分割ビット。このクロックがロジック1の場合、MCLKINに現れるクロック周波数は、AD7707が内部で使用する前に二分されます。例えば、このビットを1に設定すると、MCLKINとMCLKOUTの間に4.9152MHzクリスタルを配置でき、AD7707は内部で規定の2.4576MHzで動作します。このビットがロジックの場合、MCLKINピンに現れるクロック周波数は、部品内部で用いる周波数になります。