# ANALOG 8ピンSOT-23パッケージ、差動入力、 DEVICES 555kSPSの12ビットADC

**AD7452**

#### 特長

Vnn仕様:3Vおよび5V

最大スループットでの低消費電力:

3V電源時、555kSPSで3.3mW (max) 5V電源時、555kSPSで7.25mW (max)

フル差動アナログ入力 広い入力帯域幅:

入力周波数100kHzで70dB SINAD

フレキシブルなパワー/シリアル・クロック速度マネジメント

パイプライン遅延なし

高速シリアル・インターフェース:

SPI®/QSPI™/MICROWIRE™/DSP互換

パワーダウン・モード:1μA (max)

8ピンSOT-23パッケージ

#### アプリケーション

トランスデューサ・インターフェース バッテリ駆動のシステム データ・アクイジション・システム 携帯型計装機器

モーター制御

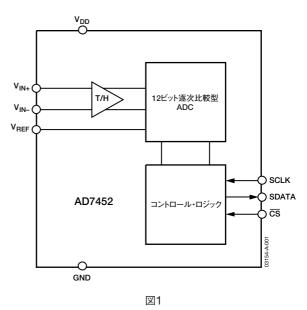

#### 概要

AD74521は、12ビットの高速、低消費電力の逐次比較型 (SAR) A/Dコンバータで、フル差動アナログ入力を備えてい ます。このデバイスは、3Vまたは5Vの単電源で動作し、 555kSPSまでのスループット・レートが可能です。

内蔵するローノイズ、広帯域幅の差動トラック・アンド・ホー ルド・アンプ (T/H) は、3.5MHzまでの入力周波数を扱うこ とができます。リファレンス電圧は、外部から $V_{REF}$ ピンに印可 し、電源とアプリケーションに応じて100mV~3.5Vの範囲が あります。デバイスのコモン・モード電圧レンジは、リファレ ンス電圧値によって決まります。真の差動入力構成と可変リ ファレンス電圧入力により、多様な入力レンジとバイアス・ポ イントを選択できます。

変換プロセスとデータ・アクイジションをCSとシリアル・ク ロックによって制御するため、マイクロプロセッサやDSPにデ バイスを接続することができます。CSの立ち下がりエッジで入 力信号をサンプリングし、変換もこの時点で開始します。

SARアーキテクチャを採用しているため、パイプライン遅延は ありません。

AD7452は高度な設計技法を利用し、きわめて低い消費電力を 実現します。

#### 機能ブロック図

#### 製品のハイライト

- 1. 3V電源または5V電源による動作

- 2. 低消費電力で高スループット 3V電源の場合、AD7452は555kSPSのスループットで最大 消費電力が3.3mWになります。

- 3. フル差動アナログ入力

- 4. フレキシブルなパワー/シリアル・クロック速度マネジメ ント

変換レートはシリアル・クロックによって決まります。こ のため、シリアル・クロック速度を上げて変換時間を短く すれば、消費電力を低減することができます。低いスルー プット・レートで電力効率を高めるシャットダウン・モー ドも備えています。

- 5. 電圧が可変のリファレンス入力

- 6. パイプライン遅延なし

- 7. CS入力とワンショット変換制御により、サンプリング・タ イミングを正確に制御

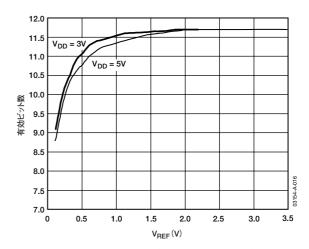

- 8. 100mVリファレンス電圧で、ENOB>8ビット (typ)

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。 © 2004 Analog Devices, Inc. All rights reserved.

REV. B

<sup>1</sup> 米国特許番号6.681.332によって保護されています。

| AD7452—仕様       | 3  | リファレンス                    | 18 |

|-----------------|----|---------------------------|----|

| タイミング仕様         |    | シングルエンド動作                 | 18 |

| 絶対最大定格          | 6  | シリアル・インターフェース             | 19 |

| ESDに関する注意       | 6  | 動作モード                     | 20 |

| ピン配置および機能の説明    | 7  | ノーマル・モード                  | 20 |

| 用語集             | 8  | パワーダウン・モード                | 20 |

| AD7452—代表的な性能特性 | 10 | パワーアップ時間                  | 21 |

| 回路情報            | 13 | 消費電力とスループット・レートの関係        | 22 |

| コンバータ動作         | 13 | マイクロプロセッサおよびDSPとのインターフェース | 22 |

| ADCの伝達関数        | 13 | アプリケーション情報                | 24 |

| 代表的な接続図         | 14 | AD7452の性能評価               | 24 |

| アナログ入力          | 14 | 外形寸法                      |    |

| 差動入力の駆動         | 16 | オーダー・ガイド                  | 25 |

| デジタル入力          | 18 |                           |    |

|                 |    |                           |    |

|                 |    |                           |    |

#### **REVISION HISTORY**

| TIEVISION TIISTOTTI                           |

|-----------------------------------------------|

| 2/04—Data Sheet changed from Rev. A to Rev. B |

| Added Patent Note                             |

| 2/04—Data Sheet changed from Rev. 0 to Rev. A |

| Updated Formatting                            |

| Changes to Applications section               |

| Changes to General Description                |

| Changes to Specifications                     |

| Changes to Timing Specifications              |

| Changes to Timing Example                     |

|                                               |

9/03—Revision 0: Initial Version

## AD7452—仕様

特に指定のない限り、 $V_{DD}$ =2.7~3.6V、 $f_{SCLK}$ =10MHz、 $f_{S}$ =555kSPS、 $V_{REF}$ =2.0V; $V_{DD}$ =4.75~5.25V、 $f_{SCLK}$ =10MHz、 $f_{S}$ =555kSPS、 $V_{REF}$ =2.5V; $V_{CM}$ 1= $V_{REF}$ ; $V_{AE}$ 7= $V_{REF}$ 5.555kSPS、 $V_{REF}$ 2.5V; $V_{CM}$ 1= $V_{REF}$ 5.7 ( $V_{CM}$ 1) ( $V_{CM}$ 1) ( $V_{CM}$ 2) ( $V_{CM}$ 3) ( $V_{CM}$ 3) ( $V_{CM}$ 4) ( $V_{CM}$ 5) ( $V_{CM}$ 5) ( $V_{CM}$ 5) ( $V_{CM}$ 6) ( $V_{CM}$ 6) ( $V_{CM}$ 7) ( $V_{CM}$ 7) ( $V_{CM}$ 8) (

#### 表1

| パラメータ                                                                                                                                                                  | テスト条件/備考                                                                                                                                                                                                                                                                                     | Bバージョン <sup>2</sup>                                                                     | 単位                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| <b>動的性能</b> 信号対 (ノイズ+歪み) 比 (SINAD) <sup>3</sup> 全高調波歪み (THD) <sup>3</sup> ピーク高調波またはスプリアス・ノイズ <sup>3</sup>                                                              | $\begin{split} f_{IN} &= 100 \text{kHz} \\ V_{DD} &= 4.75 \sim 5.25 \text{V},  -86 \text{dB (typ)} \\ V_{DD} &= 2.7 \sim 3.6 \text{V},  -84 \text{dB (typ)} \\ V_{DD} &= 4.75 \sim 5.25 \text{V},  -86 \text{dB (typ)} \\ V_{DD} &= 2.7 \sim 3.6 \text{V},  -84 \text{dB (typ)} \end{split}$ | 70<br>-76<br>-74<br>-76<br>-74                                                          | dB (min) dB (max) dB (max) dB (max) dB (max)                         |

| 相互変調歪み(IMD) <sup>3</sup> 2次項 3次項 アパーチャ遅延 <sup>3</sup> アパーチャ・ジッター <sup>3</sup> フルパワー帯域幅 <sup>3、4</sup>                                                                  | fa=90kHz, fb=110kHz<br>@-3dB<br>@-0.1dB                                                                                                                                                                                                                                                      | -89<br>-89<br>5<br>50<br>20<br>2.5                                                      | dB (typ) dB (typ) ns (typ) ps (typ) MHz (typ) MHz (typ)              |

| DC精度<br>分解能<br>積分非直線性 (INL) <sup>3</sup><br>微分非直線性 (DNL) <sup>3</sup><br>ゼロ・コード誤差 <sup>3</sup><br>正のゲイン誤差 <sup>3</sup><br>負のゲイン誤差 <sup>3</sup>                         | 12ビットまでノー・ミスコード保証                                                                                                                                                                                                                                                                            | $ \begin{array}{c} 12 \\ \pm 1 \\ \pm 0.95 \\ \pm 6 \\ \pm 2 \\ \pm 2 \end{array} $     | ピット<br>LSB (max)<br>LSB (max)<br>LSB (max)<br>LSB (max)<br>LSB (max) |

| <b>アナログ入力</b> フルスケール入力スパン 絶対入力電圧 V <sub>IN+</sub> V <sub>IN-</sub> DCリーク電流 入力容量                                                                                        | $2	imes V_{REF}^5$ $V_{CM} = V_{REF}$ $V_{CM} = V_{REF}$ トラック/ホールド時                                                                                                                                                                                                                          | $V_{IN+} - V_{IN-}$ $V_{CM}^{1} \pm V_{REF}/2$ $V_{CM}^{1} \pm V_{REF}/2$ $\pm 1$ 30/10 | V V V µA (max) pF (typ)                                              |

| リファレンス入力<br>V <sub>REF</sub> 入力電圧<br>DCリーク電流<br>V <sub>REF</sub> 入力容量                                                                                                  | $V_{DD}$ =4.75~5.25 $V$<br>(仕様性能を得るには許容偏差±1%)<br>$V_{DD}$ =2.7~3.6 $V$<br>(仕様性能を得るには許容偏差±1%)                                                                                                                                                                                                 | $ \begin{array}{c} 2.5^{6} \\ 2.0^{7} \\ \pm 1 \\ 10/30 \end{array} $                   | V<br>V<br>μA (max)<br>pF (typ)                                       |

| ロジック入力<br>ハイレベル入力電圧、 $\mathbf{V}_{\mathrm{INH}}$<br>ローレベル入力電圧、 $\mathbf{V}_{\mathrm{INL}}$<br>入力電流、 $\mathbf{I}_{\mathrm{IN}}$<br>入力容量、 $\mathbf{C}_{\mathrm{IN}}^{8}$ | 標準で $10$ nA、 $V_{IN}$ = $0$ Vまたは $V_{DD}$                                                                                                                                                                                                                                                    | 2.4<br>0.8<br>±1<br>10                                                                  | V (min)<br>V (max)<br>μA (max)<br>pF (max)                           |

| ロジック出力 ハイレベル出力電圧、 $V_{OH}$ ローレベル出力電圧、 $V_{OL}$ フローティング状態リーク電流 フローティング状態出力容量 $^8$ 出力コーディング                                                                              | $V_{DD}\!=\!4.75\!\sim\!5.25 V,\ I_{SOURCE}\!=\!200 \mu A \ V_{DD}\!=\!2.7\!\sim\!3.6 V,\ I_{SOURCE}\!=\!200 \mu A \ I_{SINK}\!=\!200 \mu A$                                                                                                                                                 | 2.8<br>2.4<br>0.4<br>±1<br>10<br>2の補数                                                   | V (min) V (min) V (max) μA (max) pF (max)                            |

REV. B — 3 —

| パラメータ                    | テスト条件/備考                                  | Bバージョン <sup>1</sup> | 単位               |

|--------------------------|-------------------------------------------|---------------------|------------------|

|                          |                                           |                     |                  |

| 変換時間                     | 10MHz SCLKで1.6µs                          | 16                  | SCLKサイクル         |

| トラック・アンド・ホールド・アクイジション時間3 | サイン波入力                                    | 200                 | ns (max)         |

|                          | ステップ入力                                    | 290                 | ns (max)         |

| スループット・レート               |                                           | 555                 | kSPS (max)       |

|                          |                                           |                     |                  |

| $V_{ m DD}$              | レンジ:3V+20/-10%;                           | 2.7/5.25            | V (min) /V (max) |

|                          | 5V±5%                                     |                     |                  |

| $I_{\rm DD}^{-9}$ , 10   |                                           |                     |                  |

| ノーマル・モード (静止時)           | SCLK OnまたはOff                             | 0.5                 | mA (typ)         |

| ノーマル・モード(動作時)            | $V_{DD} = 4.75 \sim 5.25 V$               | 1.5                 | mA (max)         |

|                          | $V_{DD} = 2.7 \sim 3.6 V$                 | 1.2                 | mA (max)         |

| フルパワーダウン・モード             | SCLK OnまたはOff                             | 1                   | μA (max)         |

| 消費電力                     |                                           |                     |                  |

| ノーマル・モード (動作時)           | V <sub>DD</sub> =5V、100kSPSに対して           | 7.25                | mW (max)         |

|                          | 1.55mW (typ) <sup>9</sup>                 |                     |                  |

|                          | V <sub>DD</sub> =3V、100kSPSに対して           | 3.3                 | mW (max)         |

|                          | 0.64mW (typ) <sup>9</sup>                 |                     |                  |

| フルパワーダウン・モード             | $V_{DD} = 5V$ , SCLK On $\sharp t$ it Off | 5                   | μW (max)         |

|                          | V <sub>DD</sub> =3V、SCLK OnまたはOff         | 3                   | μW (max)         |

<sup>」</sup>コモン・モード電圧。入力信号の中心は、図23と図24で規定される範囲内のDCコモン・モード電圧にすることができます。 2 温度範囲:Bバージョンでー40~+85℃。

REV. B -4-

<sup>2</sup> 温度範囲:Bバージョンでー40~+85℃。

3 「用語集」を参照。

4 アクイジション時間中に27V/ $\mu$ sを超える(フルスケール入力サイン波>3.5MHz)スルーレートのアナログ入力があると、コンバータが不正な結果を返すことがあります。

5  $V_{\text{IN-L}} \times V_{\text{IN-}}$ の入力スパンは両方とも $V_{\text{REF}}$ で、位相が180度ずれているため、差動電圧は $2 \times V_{\text{REF}}$ になります。

6  $V_{\text{DD}}$ =5 $V_{\text{OB}}$ 46、AD7452は100mVのリファレンス入力で動作し、リファレンスの範囲は最大3.5 $V_{\text{EF}}$ 5です。

7  $V_{\text{DD}}$ 53 $V_{\text{OB}}$ 63 $V_{\text{OB}}$ 70の場合、AD7452は100mVのリファレンス入力で動作し、リファレンスの範囲は最大2.2 $V_{\text{CF}}$ 7。

8 特性評価により保証。

9 「消費電力とスループット・レートの関係」を参照。

10 ミッドスケールのDC入力で測定。

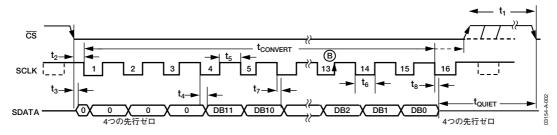

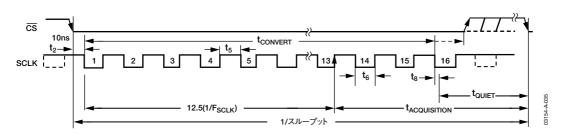

#### タイミング仕様

適合性を保証するために25℃でサンプル・テスト済み。すべての入力信号は、tr=tf=5ns( $V_{DD}$ の $10\sim90\%$ )で規定され、1.6Vの電圧 レベルからタイミングがとられます。図2と「シリアル・インターフェース」を参照。

特に指定のない限り、 $V_{DD}$ =2.7~3.6V、 $f_{SCLK}$ =10MHz、 $f_{S}$ =555kSPS、 $V_{REF}$ =2.0V; $V_{DD}$ =4.75~5.25V、 $f_{SCLK}$ =10MHz、  $\rm f_S{=}555kSPS$  ,  $\rm V_{REF}{=}2.5V$  ;  $\rm V_{CM}{}^1{=}V_{REF}$  ;  $\rm T_A{=}T_{MIN}{\sim}T_{MAX}$

| パラメータ                          | T <sub>MIN</sub> 、T <sub>MAX</sub> での限界 | 単位        | 説明                                                  |

|--------------------------------|-----------------------------------------|-----------|-----------------------------------------------------|

| f <sub>SCLK</sub> <sup>2</sup> | 10                                      | kHz (min) |                                                     |

|                                | 10                                      | MHz (max) |                                                     |

| $t_{CONVERT}$                  | $16 \times t_{SCLK}$                    |           | $t_{SCLK} = 1/t_{SCLK}$                             |

|                                | 1.6                                     | μs (max)  |                                                     |

| $t_{QUIET}$                    | 60                                      | ns (min)  | シリアル読み出し完了とCSの次の立ち下がりエッジとの間の最小静止時間                  |

| $t_1$                          | 10                                      | ns (min)  | 最小CSパルス幅                                            |

| $t_2$                          | 10                                      | ns (min)  | <del>CS</del> の立ち下がりエッジからSCLKの立ち下がりエッジまでのセットアップ・タイム |

| $t_3^3$                        | 20                                      | ns (max)  | CSの立ち下がりエッジからSDATAスリーステート・ディスエーブルまでの遅延              |

| $t_4^{\ 3}$                    | 40                                      | ns (max)  | SCLK立ち下がりエッジ後のデータ・アクセス時間                            |

| $t_5$                          | $0.4 t_{SCLK}$                          | ns (min)  | SCLKのハイレベル・パルス幅                                     |

| $t_6$                          | $0.4 t_{SCLK}$                          | ns (min)  | SCLKのローレベル・パルス幅                                     |

| $t_7$                          | 10                                      | ns (min)  | SCLKエッジからデータ有効までのホールド・タイム                           |

| $t_8^4$                        | 10                                      | ns (min)  | SCLK立ち下がりエッジからSDATAスリーステート・イネーブルまで                  |

|                                | 35                                      | ns (max)  | SCLK立ち下がりエッジからSDATAスリーステート・イネーブルまで                  |

| $t_{POWER\text{-}UP}^{5}$      | 1                                       | μs (max)  | フルパワーダウンからのパワーアップ時間                                 |

図2. シリアル・インターフェースのタイミング図

REV. B -5-

<sup>&</sup>lt;sup>1</sup> コモン・モード電圧。 <sup>2</sup> SCLK入力のマーク/スペース比は40/60~60/40。

図3の負荷回路で測定。 $V_{DD}$ =5Vの場合は出力が0.8Vまたは2.4Vを超えるまでに必要な時間で、 $V_{DD}$ =3Vの場合は出力が0.4Vまたは2.0Vを超えるまでに必要な時間です。  $t_{\rm g}$ は、図3の回路を接続したときに、データ出力が0.5V変化するために要する時間を測定して得られます。測定した数値を後方に外挿して、25pFコンデンサの充/放電による影響を除去します。つまり、タイミング仕様で示される時間 $t_{\rm g}$ は、デバイスの真のバス開放時間であり、バス負荷に左右されません。

<sup>5「</sup>パワーアップ時間」を参照。

## 絶対最大定格

特に指定のない限り、T<sub>A</sub>=25℃

#### 表3

| パラメータ                   | 定格                         |

|-------------------------|----------------------------|

| GNDに対するV <sub>DD</sub>  | $-0.3 \sim +7V$            |

| GNDに対する $V_{{ m IN}^+}$ | $-0.3V \sim V_{DD} + 0.3V$ |

| GNDに対する $V_{{ m IN}-}$  | $-0.3V \sim V_{DD} + 0.3V$ |

| GNDに対するデジタル入力電圧         | $-0.3 \sim +7V$            |

| GNDに対するデジタル出力電圧         | $-0.3V \sim V_{DD} + 0.3V$ |

| $GND$ に対する $V_{REF}$    | $-0.3V \sim V_{DD} + 0.3V$ |

| 電源以外のピンへの入力電流1          | $\pm 10$ mA                |

| 動作温度範囲                  |                            |

| コマーシャル (Bバージョン)         | -40~+85°C                  |

| 保存温度範囲                  | -65~+150°C                 |

| ジャンクション温度               | 150℃                       |

| $	heta_{JA}$ 熱抵抗        | 211.5℃/W                   |

| $	heta_{JC}$ 熱抵抗        | 91.99℃/W                   |

| ピン温度、ハンダ処理              |                            |

| ベーキング時間(60秒)            | 215℃                       |

| 赤外線(15秒)                | 220℃                       |

| ESD                     | 1kV                        |

上記の絶対最大定格を超えるストレスを加えると、デバイスに 恒久的な損傷を与えることがあります。この規定はストレス定 格のみを指定するものであり、この仕様の動作に関するセク ションに記載されている規定値以上でのデバイス動作を定めた ものではありません。長時間デバイスを絶対最大定格状態に置 くと、デバイスの信頼性に影響を与えることがあります。

図3. デジタル出力タイミング仕様の負荷回路

#### 注意

ESD (静電放電)の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

─6 ─ REV. B

<sup>&</sup>lt;sup>1</sup> 100mAまでの過渡電流では、SCRラッチアップは発生しません。

## ピン配置および機能の説明

図4. 8ピンSOT-23

#### 表4. ピン機能の説明

| 記号                 | 機能                                                                                                                                                                                            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{REF}$          | AD7452のリファレンス入力。この入力に外部リファレンスを接続する必要があります。仕様性能を得るには、 $5$ V電源で $2.5$ V( $\pm 1$ %)、 $3$ V電源で $2$ V( $\pm 1$ %)のリファレンスになります。このピンは、 $0.1$ μF以上のコンデンサでGNDにデカップリングしてください。詳細については「リファレンス」を参照してください。 |

| $V_{\rm IN^+}$     | 差動アナログ入力用の正端子                                                                                                                                                                                 |

| $V_{\mathrm{IN}-}$ | 差動アナログ入力用の負端子                                                                                                                                                                                 |

| GND                | アナログ・グラウンド。AD7452上のすべての回路のグラウンド・リファレンス・ポイント。すべてのアナログ入力<br>信号と外部リファレンス信号は、このGND電圧を基準にします。                                                                                                      |

| CS                 | チップ・セレクト。アクティブ・ローのロジック入力。この入力には、AD7452での変換開始とシリアル・データの<br>転送制御という2つの機能があります。                                                                                                                  |

| SDATA              | シリアル・データ。ロジック出力。AD7452からの変換結果がシリアル・データ・ストリームとしてこの出力から得られます。SCLK入力の立ち下がりエッジで、ビットをクロック出力します。データ・ストリームは、4つの先行ゼロと、それに続く12ビットの変換データ(MSBファースト)で構成されています。出力コーディングは2の補数です。                            |

| SCLK               | シリアル・クロック。ロジック入力。SCLKは、デバイスからのデータにアクセスするためのシリアル・クロックを<br>提供します。このクロック入力は、変換プロセスのクロック源にもなります。                                                                                                  |

| $V_{DD}$           | 電源入力。 $V_{DD}$ は3 $V$ ( $+20\%/-10\%$ )または5 $V$ ( $\pm5\%$ )です。この電源は、 $0.1\mu$ Fコンデンサと $10\mu$ Fタンタル・コンデンサの並列接続によってGNDにデカップリングしてください。                                                         |

REV. B — 7 —

## 用語集

#### 信号対(ノイズ十歪み)比

A/Dコンバータ出力で測定した信号対(ノイズ+歪み)比です。信号は基本波のrms振幅で、ノイズは1/2サンプリング周波数  $(f_s/2)$  までのすべての非基本波信号の和になります(DCを除く)。信号対(ノイズ+歪み)比はデジタル化プロセスの量子化レベル数に依存し、レベル数が大きいほど、量子化ノイズが小さくなります。サイン波を入力した場合の理想のNビット・コンバータでの信号対(ノイズ+歪み)比の理論値は、次式で得られます。

信号対 (ノイズ+歪み) 比=(6.02N+1.76)dB

これによると、12ビット・コンバータでは74dBになります。

#### 全高調波歪み (THD)

全高調波歪みは、高調波のrms値総和と基本波の比です。 AD7452の場合、次のようになります。

$$THD(dB) = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

ここで、 $V_1$ は基本波のrms振幅、 $V_2$ 、 $V_3$ 、 $V_4$ 、 $V_5$ 、 $V_6$ は2次~6次高調波のrms振幅です。

#### ピーク高調波またはスプリアス・ノイズ

ピーク高調波またはスプリアス・ノイズは、ADC出力スペクトル内の2番目に大きい成分のrms値(DCを除き、 $f_s$ /2まで)の基本波rms値に対する比です。通常、この仕様値はスペクトル内の最大の高調波によって決まりますが、高調波がノイズ・フロアに埋め込まれているADCの場合は、ノイズ・ピークになります。

#### 相互変調歪み

非線形性のアクティブ・デバイスに2つの周波数faおよびfbのサイン波を入力すると、和および差の周波数mfa $\pm$ nfb(mおよび nは、0、1、2、3など)で歪み成分が発生します。相互変調歪み項とは、このmとnが非ゼロの項をいいます。たとえば、2次項には(fa+fb)と(fa-fb)があり、3次項には(2fa+fb)、(2fa-fb)、(fa+2fb)、(fa-2fb)があります。

AD7452は、入力帯域幅の上限に近い2つの入力周波数を使う CCIF標準でテストされています。この場合、通常、2次項は元 のサイン波の周波数から離れ、3次項は入力周波数に近い周波 数になります。このため、2次項と3次項は別々の仕様になりま す。相互変調歪みの計算は、THDの仕様に従い、基本波の和の rms振幅に対する個々の歪み成分のrms総和の比になり、dBで 表します。

#### アパーチャ遅延

サンプリング・クロックの立ち上がりエッジから、ADCが実際にサンプルを行うまでに要する時間です。

#### アパーチャ・ジッター

実際のサンプル取得が行われる有効時点についてのサンプルご との変動です。

#### フルパワー帯域幅

ADCのフルパワー帯域幅とは、再構成された基本波の振幅がフルスケール入力に対して0.1 dBまたは3 dB低下する入力周波数です。

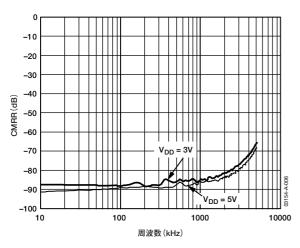

#### コモン・モード除去比(CMRR)

コモン・モード除去比とは、フルスケール周波数fでのADC出力の電力と、周波数 $f_s$ でのコモン・モード電圧 $V_{IN-}$ と $V_{IN-}$ に加えられた100mVp-pのサイン波の電力との比です。

#### $CMRR(dB) = 10 \log (Pf/Pfs)$

PfはADC出力における周波数fでの電力、 $Pf_s$ はADC出力における周波数f、での電力です。

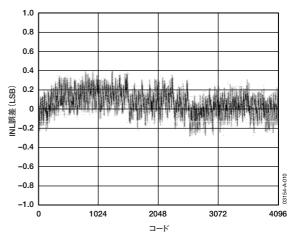

#### 積分非直線性 (INL)

ADC伝達関数の両端を結ぶ直線からの最大偏差です。

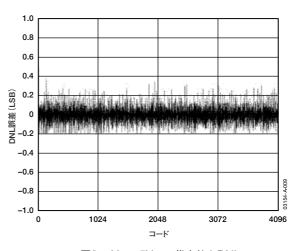

#### 微分非直線性(DNL)

ADCの2つの隣接コード間における1LSB変化の測定値と理想値の差です。

#### ゼロ・コード誤差

ミッドスケール・コード遷移(111…111から000…000)と理想値 $V_{\rm IN+}$ - $V_{\rm IN-}$ (つまり、0LSB)との偏差です。

#### 正のゲイン誤差

ゼロ・コード誤差を調整した後の、最後のコード遷移 (011…110から011…111) と理想値 $V_{\rm IN+}-V_{\rm IN-}$  (つまり、+  $V_{\rm REF}-1$ LSB) との偏差です。

#### 負のゲイン誤差

ゼロ・コード誤差を調整した後の、最初のコード遷移 (100…000から100…001) と理想値 $V_{\rm IN^+} - V_{\rm IN^-}$  (つまり、 $-V_{\rm REF} + 1 L S B$ ) との偏差です。

#### トラック・アンド・ホールド・アクイジション時間

トラック・アンド・ホールド・アンプがトラック・モードにと どまり、トラック・アンド・ホールド・アンプの出力が、印加 された入力信号の0.5LSB以内に達して整定するまでに必要と する最小時間です。

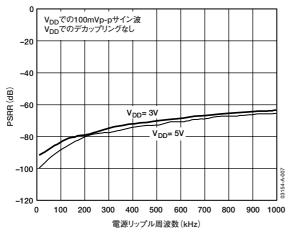

#### 電源電圧変動除去比(PSRR)

電源除去比は、フルスケール周波数fでのADC出力の電力と、周波数 $f_s$ のADC  $V_{DD}$ 電源に加えられる100 mVp-pサイン波の電力との比です。この入力の周波数は、 $1kHz\sim1MHz$ の範囲で変動します。

#### PSRR(dB) = 10 log (Pf/Pfs)

PfはADC出力における周波数fでの電力で、 $Pf_s$ はADC出力における周波数f $_s$ での電力です。

REV. B — 9 —

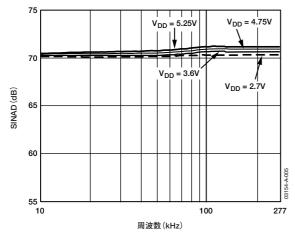

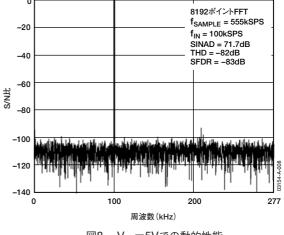

## AD7452—代表的な性能特性

特に指定のない限り、 $T_A$ =25℃、 $f_S$ =555kSPS、 $f_{SCLK}$ =10MHz

図5. さまざまな電源電圧でのSINADと アナログ入力周波数の関係

図8. V<sub>DD</sub>=5Vでの動的性能

図6. V<sub>DD</sub>=5Vおよび3VでのCMRRと 周波数の関係

図9.  $V_{DD}$ =5Vでの代表的なDNL

図7. 電源デカップリングなしでのPSRRと 電源リップル周波数の関係

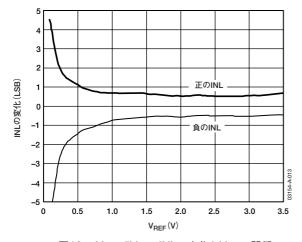

図10. V<sub>DD</sub>=5Vでの代表的なINL

— 10 — REV. B

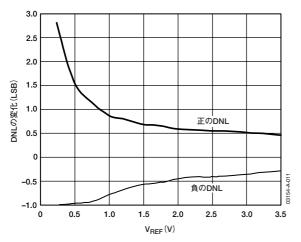

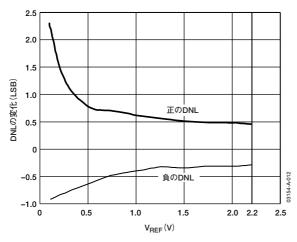

図11.  $V_{DD}$ =5VでのDNLの変化と $V_{REF}$ の関係

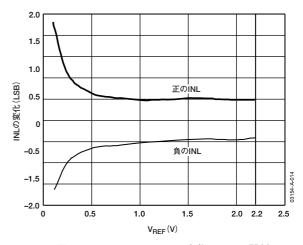

図14.  $V_{DD}$ =3VでのINLの変化と $V_{REF}$ の関係

図12.  $V_{DD}$ =3VでのDNLの変化と $V_{REF}$ の関係

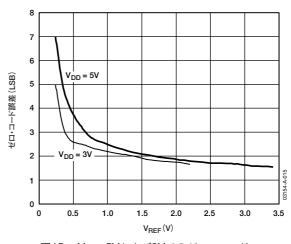

図15. V<sub>DD</sub>=5Vおよび3Vでのゼロ・コード 誤差の変化とリファレンス電圧の関係

図13.  $V_{DD}$ =5VでのINLの変化と $V_{REF}$ の関係

図16.  $V_{DD}$ =5VおよU3VでのENOBの変化と リファレンス電圧の関係

REV. B — 11 —

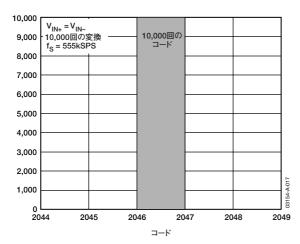

図17. V<sub>DD</sub>=5VでのDC入力の10,000回変換の ヒストグラム

## 回路情報

AD7452は、高速、低消費電力、単電源の12ビットの逐次比較型A/Dコンバータ(ADC)です。デバイスは5Vまたは3V電源で動作し、10MHzのSCLKによる最大スループット・レートは555kSPSです。外部リファレンス電圧を $V_{REF}$ ピンに入力する必要がありますが、リファレンス電圧値は電源とアプリケーションに応じて選択できます。

5V電源での動作の場合、入力できる最大リファレンス電圧は 3.5Vです。3V電源では、2.2Vまでのリファレンス電圧を入力できます(「リファレンス」を参照)。

AD7452は、8ピンのSOT-23パッケージを採用し、オンチップ差動トラック・アンド・ホールド・アンプ、逐次比較型(SAR)ADC、シリアル・インターフェースを備えています。デバイスからのデータの読み出しに使用するシリアル・クロック入力は、逐次比較型ADCのクロック源にも使用されます。AD7452には、変換と変換の間で消費電力を低減させるパワーダウン・オプションがあります。「動作モード」で説明しますが、パワーダウン機能は標準のシリアル・インターフェースを使って実行します。

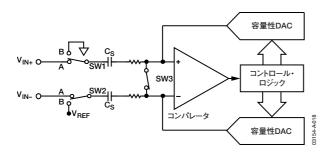

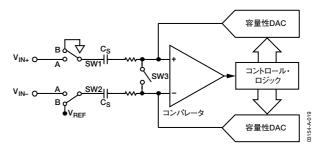

#### コンバータ動作

AD7452は、2個の容量性DACをベースとする逐次比較型ADCです。図18と図19に、アクイジション・フェーズと変換フェーズのADCの簡略回路図を示します。ADCは、コントロール・ロジック、SAR、2個の容量性DACで構成されています。図18(アクイジション・フェーズ)では、SW3が閉じ、SW1とSW2がポジションA、コンパレータが平衡状態にあり、サンプリング・コンデンサ・アレイが入力の差動信号を取得します。

図18. ADCのアクイジション・フェーズ

ADCが変換を開始すると(図19)、SW3が開き、SW1とSW2がポジションBに移動するため、コンパレータが不平衡状態になります。変換が始まると、2つの入力が切り離されます。コントロール・ロジックと電荷再配分式DACを使用し、サンプリング・コンデンサ・アレイに対して一定量の電荷を加算/減算することで、コンパレータを平衡状態に戻します。コンパレータが平衡状態に戻ると、変換が完了します。コントロール・ロジックはADCの出力コードを生成します。 $V_{\rm IN-}$ ピンを駆動する信号源の出力インピーダンスは一致しなければなりません。これが一致しないと、2つの入力で異なるセトリング・タイムになり、誤差が生じます。

図19. ADCの変換フェーズ

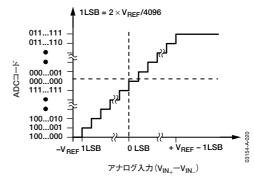

#### ADCの伝達関数

AD7452の出力コーディングは2の補数です。設計されたコード 遷移は連続したLSB値で発生します(1LSB、2LSB…と続く)。LSBサイズは2 $\times$ V<sub>REF</sub>/4096です。図20に、AD7452の理想的な 伝達特性を示します。

図20. 理想的な伝達特性

REV. B — 13 —

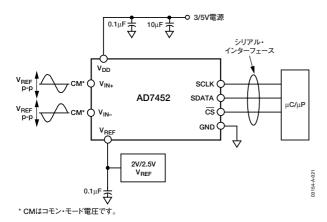

#### 代表的な接続図

図21に、5V電源および3V電源でのAD7452の代表的な接続図を示します。この接続では、GNDピンはシステムのアナログ・グラウンド・プレーンに接続します。 $V_{REF}$ ピンは、電源に応じて2.5Vまたは2Vのデカップリングされたリファレンス源に接続し、アナログ入力レンジを設定します。コモン・モード電圧は外部で用意する必要があり、その電圧は2つの入力の中心となる値にします。変換結果は16ビット・ワードで出力され、4つの先行ゼロに続いて12ビット結果のMSBが来ます。差動入力の駆動とコモン・モード設定の詳細については、「差動入力の駆動」を参照してください。

図21. 代表的な接続図

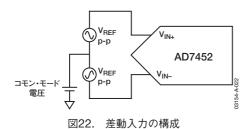

#### アナログ入力

AD7452のアナログ入力はフル差動です。差動信号には、デバイスのコモン・モード除去比に基づくノイズ耐性、歪み性能の改善、対応ダイナミック・レンジの倍増、入力レンジとバイアス・ポイントの柔軟性など、シングルエンド信号に比べて多くの利点があります。図22に、AD7452のフル差動アナログ入力の構成を示します。

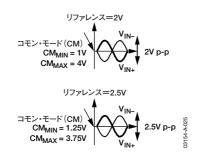

差動信号の振幅は、 $V_{\rm IN+}$ ピンと $V_{\rm IN-}$ ピンに加えられた信号の差(すなわち $V_{\rm IN+}$ - $V_{\rm IN-}$ )です。 $V_{\rm IN+}$ と $V_{\rm IN-}$ は、それぞれ振幅が $V_{\rm REF}$ で位相差が180度の2つの信号で同時に駆動されます。したがって、差動信号の振幅は $-V_{\rm REF}$ ~+ $V_{\rm REF}$ P-p(すなわち2× $V_{\rm REF}$ )になります。これはコモン・モード(CM)に無関係です。

コモン・モードは、2つの信号の平均値つまり( $V_{\text{IN+}}+V_{\text{IN-}}$ )/2であるため、2つの入力の中心になる電圧になります。このため、各入力のスパンは $CM\pm V_{\text{REF}}$ /2となります。この電圧は外部で設定する必要があり、その範囲は $V_{\text{REF}}$ によって変化します。 $V_{\text{REF}}$ の値が大きくなると、コモン・モード・レンジが小さくなります。アンプで入力を駆動するときには、実際のコモン・モード・レンジはアンプの出力電圧スイングによって決まります。

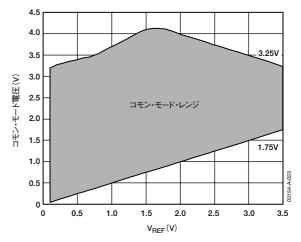

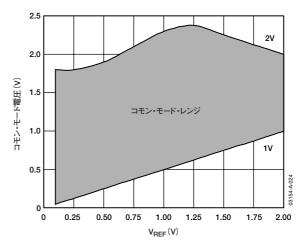

図23と図24に、5V電源時と3V電源時にコモン・モード・レンジが $V_{REF}$ によって変化する様子を示します。AD7452の機能を保証するには、コモン・モードはこの範囲内でなければなりません。

使いやすくするため、コモン・モードを $V_{REF}$ に等しい値に設定することができます。この場合、差動信号は $V_{REF}$ 七 $V_{REF}$ になります。変換が行われると、コモン・モードが除去されて、振幅が $-V_{REF}$ ~+ $V_{REF}$ のほとんどノイズのない信号が得られます。この振幅は、デジタル・コード0~4096に対応します。

図23. 入力コモン・モード・レンジ 対  $V_{REF}$   $(V_{DD}=5V,\ V_{REF}\ (max)=3.5V)$

図24. 入力コモン・モード・レンジ 対  $V_{REF}$   $(V_{DD}=3V,\ V_{REF}\ (max)=2V)$

図25に、 $V_{DD}$ =5Vの場合についてさまざまな $V_{REF}$ 値に対する  $V_{IN+}$ と $V_{IN-}$ への入力例を示します。また、図23に基づいて、リファレンス値ごとの最大と最小のコモン・モード電圧も示します。

図25.  $V_{DD}$ =5Vにおける、さまざまな $V_{REF}$ 値に対する  $V_{IN+}$ と $V_{IN-}$ へのアナログ入力例

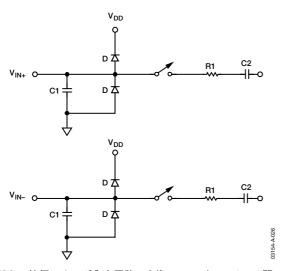

#### アナログ入力構造

図26に、AD7452のアナログ入力構造の等価回路を示します。4個のダイオードがアナログ入力に対するESD保護機能を提供します。アナログ入力信号が電源レールより300mV以上高くならないように注意してください。この値を超えると、これらのダイオードが順方向にバイアスされて、サブストレートに電流が流れるようになります。ダイオードがデバイスに修復不可能な損傷を与えずに許容できる最大電流は10mAです。図26のコンデンサC1は標準で4pFで、主にピン容量に起因します。抵抗は、スイッチのオン抵抗で構成される集中部品です。これらの抵抗の値は、標準で約100 $\Omega$ です。コンデンサC2は、ADCのサンプリング・コンデンサで、標準で16pFの容量があります。

ACアプリケーションの場合は、該当するアナログ入力ピンにRCローパス・フィルタを使用して、アナログ入力信号から高周波成分を除去することを推奨します。高調波歪みやS/N比が重要なアプリケーションでは、アナログ入力を低インピーダンス・ソースから駆動してください。ソース・インピーダンスが大きいと、ADCのAC性能が大きく影響されます。このため、入力バッファ・アンプが必要になることもあります。オペアンプの選択は、アプリケーションによって異なります。

図26. 等価アナログ入力回路、変換フェーズ—スイッチ開、 トラック・フェーズ—スイッチ閉

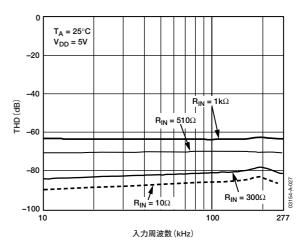

アンプを使わないでアナログ入力を駆動するときは、ソース・インピーダンスを低い値にする必要があります。最大ソース・インピーダンスは、許容可能な全高調波歪み(THD)の大きさに依存します。ソース・インピーダンスが増加するとTHDが大きくなり、性能が低下します。図27に、 $\mathbf{V}_{DD}$ =5 $\mathbf{V}$ のときのさまざまなソース・インピーダンスでの全高調波歪みとアナログ入力信号周波数の関係を示します。

図27.  $V_{DD}$ =5Vにおける、さまざまなソース・インピーダンス での全高調波歪み(THD) 対 アナログ入力周波数

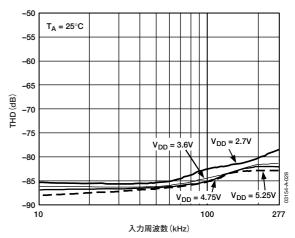

図28に、10MHzのSCLKによって555kSPSでサンプリングする際に、5V $\pm 5$ %と3V+20/-10%の $V_{DD}$ に対する全高調波歪みとアナログ入力周波数の関係を示します。この場合、ソース・インピーダンスは10 $\Omega$ です。

図28. 3Vと5Vの電源電圧での全高調波歪み (THD) 対 アナログ入力周波数

REV. B — 15 —

#### 差動入力の駆動

差動動作では、 $V_{\rm IN+}$ と $V_{\rm IN-}$ を、180度位相がずれている2つの等しい信号で同時に駆動する必要があります。コモン・モードは外部で設定する必要があり、その範囲は、 $V_{\rm REF}$ 、電源、アナログ入力の駆動に使用する特定のアンプにより決まります(図23と図24を参照)。AC結合入力またはDC結合入力のどちらでも、差動動作モードは広い周波数レンジにわたって最適なTHD性能を提供します。アプリケーションによっては信号を差動動作用にあらかじめ調整していないものもあるため、シングルエンドから差動への変換が必要になることもあります。

#### 差動アンプ

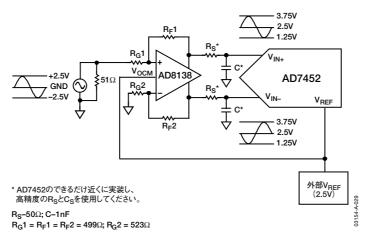

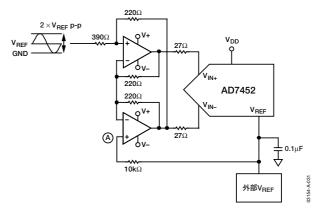

AD7452を差動駆動する理想的な方法は、AD8138のような差動アンプを使うことです。AD8138は、シングルエンド/差動変換アンプまたは差動/差動アンプとして使うことができます。いずれの場合でも、アナログ入力はバイポーラでなければなりません。また、コモン・モード・レベルのシフト機能とバイポーラ入力信号のバッファ機能もあります。図29に、AD8138をシングルエンド/差動変換アンプとして使用する方法を示します。AD8138の正側と負側の出力を、ADCのフロン

トエンドでスイッチされる容量の影響を最小化するために1対の直列抵抗を介して、ADCのそれぞれの入力に接続します。ACアプリケーションではアナログ入力の高周波成分を除去するため、各アナログ入力にRCローパス・フィルタを使用することを推奨します。AD8138のアーキテクチャにより、厳密に一致した外付け部品を使用せずに、広い周波数レンジできわめて優れた平衡を持つ出力が得られます。使用するアナログ入力ソースがゼロ・インピーダンスの場合、4個のすべての抵抗(R<sub>G</sub>1、R<sub>G</sub>2、R<sub>F</sub>1、R<sub>F</sub>2)を同じ値にする必要があります。たとえば、ソースに50 $\Omega$ のインピーダンスと50 $\Omega$ の終端がある場合、入力でのパラレル・インピーダンスをバランスさせて、正側と負側のアナログ入力に同じゲインを持たせるために、R<sub>G</sub>2の値を25 $\Omega$ だけ大きくする必要があります(図29)。アンプの出力は完全に一致した同一の振幅を持つ平衡差動出力になり、位相が正確に180度ずれたものになります。

AD8138は+3V、+5V、 $\pm5V$ の電源で仕様規定されていますが、 $\pm5V$ 電源のときに最適な結果が得られます。AD8138と特性は少し異なっていても、同様の性能と動作を備え、この構成で使用できる低価格品としては、AD8132があります。

図29. AD8138をシングルエンド/差動変換アンプとして使用する場合

#### オペアンプ対

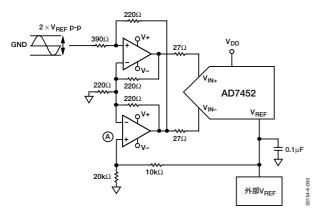

オペアンプ対を使って、差動信号をAD7452に直接接続することができます。図30と図31の回路構成で、それぞれバイポーラ入力信号とユニポーラ入力信号について、デュアル・オペアンプを使ってシングルエンド信号を差動信号に変換する方法を示します。

ポイントAに入力される電圧がコモン・モード電圧を設定します。この2つの図では、コモン・モード電圧が何らかの方法でリファレンス電圧に接続されていますが、コモン・モード・レンジ内の任意の値をここに入力してコモン・モードを設定することができます。この構成でAD7452を差動駆動するのに最適なデュアル・オペアンプとしては、AD8022があります。

必要な電源とシステムの性能目標によって異なるため、オペアンプは注意して選択する必要があります。図30と図31のドライバ回路は、最適な歪み性能を必要とするDC結合アプリケーション用に最適化されています。

図30の差動オペアンプ・ドライバ回路は、シングルエンドでグラウンド・リファレンス電圧の信号(バイポーラ)を、ADCの $V_{REF}$ レベルを中心とする差動信号に変換し、レベル・シフトするように構成されています。

図31に示す回路構成では、ユニポーラのシングルエンド信号を 差動信号に変換します。

図30. シングルエンド・バイポーラ信号を差動信号に 変換するデュアル・オペアンプ回路

図31. シングルエンド・ユニポーラ信号を差動信号に 変換するデュアル・オペアンプ回路

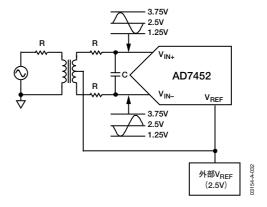

#### RFトランス

DC結合を必要としないシステムでは、差動入力を生成するためにセンター・タップ付きのRFトランスが適しています。図32に、トランスを使用してシングルエンドから差動に変換する方法を示します。この方法には、ノイズや歪みを加えることなく、ADCを差動モードで動作できるという利点があります。RFトランスには、信号源とADCとの間を電気的に分離するという長所もあります。トランスは、ほとんどのACアプリケーションで使用できます。センター・タップを使って、差動信号を必要なコモン・モード・レベルまでシフトします。この場合センター・タップをリファレンスに接続するため、コモン・モード・レベルはリファレンス電圧値になります。

図32. RFトランスによる差動入力の生成

REV. B — 17 —

#### デジタル入力

AD7452に対するデジタル入力は、アナログ入力を制限する最大定格によって制限されることはありません。印可されるデジタル入力( $\overline{CS}$ とSCLK)はTVに達することもあり、アナログ入力のように $V_{DD}$ +0.3V限界によって制限されません。

入力に $V_{DD}$ +0.3Vの制限がないことから得られる主な利点は、電源シーケンスの問題を回避できることです。 $V_{DD}$ よりも前に  $\overline{CS}$ とSCLKに電圧が印加された場合でも、ラッチアップの危険 はありません。アナログ入力では、 $V_{DD}$ より前に0.3Vより大きい信号が印加されると、ラッチアップの危険があります。

#### リファレンス

AD7452にリファレンス電圧を供給するには、外付けのリファレンス源が必要です。このリファレンス電圧の入力レンジは  $100 \text{mV} \sim 3.5 \text{V}$ です。5 V電源では2.5 Vのリファレンスが仕様規定され、最大リファレンスは3.5 Vです。3 V電源では2 Vのリファレンスが仕様規定され、最大リファレンスは2.2 Vです。いずれの場合も、リファレンスは100 mVから可能です。

特定のアプリケーションのリファレンス電圧値を選択するときには、デバイスの最大定格に従い、最大アナログ入力レンジ  $(V_{IN}\ (max))$  が $V_{DD}$ +0.3Vを超えないように注意する必要があります。次に、AD7452をそれぞれ5Vと3Vの $V_{DD}$ で使用する場合に、使用できる最大 $V_{REF}$ 入力を計算する例を示します。

#### 例1

$V_{IN} (max) = V_{DD} + 0.3$

$V_{IN}$   $(max) = V_{REF} + V_{REF}/2$

$V_{DD}$ =5Vの場合、 $V_{IN}$  (max) =5.3V

したがって、次のようになります。

$3 \times V_{REF} / 2 = 5.3 V$

$V_{REF}$  (max) = 3.5V

したがって、 $V_{DD}$ =5Vで動作するとき、 $V_{REF}$ の値は100mVから3.5Vの最大値まで変化します。 $V_{DD}$ =4.75Vのとき、 $V_{REF}$ (max) =3.17Vです。

#### 例2

$V_{IN} (max) = V_{DD} + 0.3$

$V_{IN}$   $(max) = V_{REF} + V_{REF}/2$

$V_{DD}$ =3Vの場合、 $V_{IN}$  (max) =3.3V

したがって、次のようになります。

$3 \times V_{REF}/2 = 3.3V$

$V_{REF}$  (max) = 2.2V

したがって、 $V_{DD}$ =3Vで動作するとき、 $V_{REF}$ の値は100mVから2.2Vの最大値まで変化します。 $V_{DD}$ =2.7Vのとき、 $V_{REF}$ (max) =2Vです。

これらの例からわかるように、AD7452に印加される最大リファレンスは $V_{\mathrm{DD}}$ に印加される値に直接依存します。

リファレンスの値によって、アナログ入力スパンとコモン・モード電圧レンジが設定されます。リファレンス源の誤差から AD7452の伝達関数でのゲイン誤差が生じ、デバイスで仕様規定されたフルスケール誤差に加算されます。 $\mathbf{V}_{REF}$ ピンは、 $0.1\mu F$ のコンデンサを使ってGNDにデカップリングする必要があります。

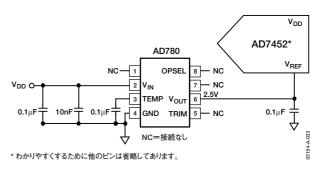

図33に、 $V_{RFF}$ ピンの代表的な接続図を示します。

図33.  $V_{DD}$ =5Vの場合の代表的な $V_{REF}$ 接続図

表5. 適切な電圧リファレンスの例

| リファレンス | 出力電圧(V) | 初期精度(%) | 動作電流(µA) |

|--------|---------|---------|----------|

| AD780  | 2.5/3   | 0.04    | 1000     |

| ADR421 | 2.5     | 0.04    | 500      |

| ADR420 | 2.048   | 0.05    | 500      |

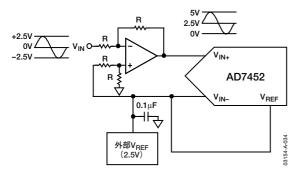

#### シングルエンド動作

5V電源を使用すると、AD7452はシングルエンド入力を処理できます。AD7452の設計は差動動作用に最適化されているため、シングルエンド入力では性能が低下します。直線性は標準で0.2LSB低下し、フル・スケール誤差も標準で1LSB低下し、AC性能も保証されません。

AD7452をシングルエンド・モードで動作させるには、 $V_{\text{IN}+}$ 入力を信号源に接続し、 $V_{\text{IN}-}$ 入力をミッドスケール・コード遷移に対応する適切な電圧にバイアスします。この電圧はコモン・モードであり、固定のDC電圧(通常はリファレンス)になります。 $V_{\text{IN}+}$ 入力はこの値を中心にしてスイングし、デバイスのフルダイナミックレンジを使用するには $2\times V_{\text{REF}}$ の電圧スパンが必要になります。このため、入力信号はコモン・モード± $V_{\text{REF}}$ のピークも0ピーク値になります。アナログ入力がユニポーラの場合は、非反転ユニティ・ゲイン構成のオペアンプを使って $V_{\text{IN}+}$ ピンを駆動することができます。ADCが単電源で動作するため、入力条件を満たすようにグラウンド・ベースのバイポーラ信号をレベル・シフトする必要があります。オペアンプを使えば、グラウンド・ベースのバイポーラ信号のスケーリングおよびレベル・シフトができ、AD7452の選択した入力レンジに合わせることができます(図34を参照)。

図34. AD7452へのバイポーラ・シングルエンド 入力

### シリアル・インターフェース

図2に、AD7452のシリアル・インターフェースの詳細なタイミング図を示します。シリアル・クロックが変換クロックを提供し、変換時にデバイスからのデータの転送も制御します。 (TSで変換プロセスが開始し、データ転送をフレーミングします。 (TSの立ち下がりエッジでトラック・アンド・ホールドがホールド・モードになり、バスがスリーステートから抜け出します。この時点で、アナログ入力をサンプリングし、変換を開始します。変換完了には、SCLKで16サイクル必要です。

13個のSCLK立ち下がりエッジが経過すると、トラック・アンド・ホールドが次のSCLKの立ち上がりエッジでトラック状態に戻ります(図2のポイントB)。SCLKの16番目の立ち下がりエッジで、SDATAラインがスリーステートに戻ります。SCLKの16サイクルが経過する前に $\overline{\text{CS}}$ の立ち上がりエッジが発生すると、変換が中止され、SDATAラインがスリーステートに戻ります。

AD7452の変換結果は、シリアル・データ・ストリームで SDATA出力から得られます。SCLK入力の立ち下がりエッジで ビットをクロック出力します。データ・ストリームは、4つの 先行ゼロと、それに続く12ビットの変換データ(MSBファースト)で構成されます。出力コーディングは2の補数です。 変換を完了してAD7452の変換結果にアクセスするには、シリアル・クロックで16サイクルが必要です。 CSがローレベルになると、マイクロコントローラやDSPによって最初の先行ゼロが読み出せるようになります。次に、後続のSCLK立ち下がりエッジで、2番目の先行ゼロから残りのデータをクロック出力します。シリアル・クロックの最初の立ち下がりクロック・エッジが、2番目の先行ゼロを出力することになります。前の(15番目の) 立ち下がりエッジで出力されていたデータ転送の最終ビットは、16番目の立ち下がりエッジで有効になります。変換が完了し、16クロック・サイクル後にデータのアクセスが行われた後は、次の変換を開始する前に、規定のアクイジション時間と静止時間を満たすことができるように十分な時間を空けることが重要です(「タイミング例」を参照)。

低速のSCLKを使用するアプリケーションでは、各SCLK立ち上がりエッジでデータを読み出すことができます。つまり、でSの立ち下がりエッジ後の最初のSCLK立ち上がりエッジで先行ゼロを、15番目のSCLKエッジでDB0を読み出すことができます。

#### タイミング例

$F_{SCLK}$ =10MHzでスループット・レート=555kSPSのとき、サイクル・タイムは次のようになります。

$$1/$$

スループット= $1/555,000=1.8$ μs

1サイクルは次の時間で構成されます。

$$t_2 + 12.5 (1/F_{SCLK}) + t_{ACQ} = 1.8 \mu s$$

したがって、 $t_2=10$ nsの場合は、次のようになります。

$$10ns + 12.5 (1/18 MHz) + t_{ACO} = 1 \mu s$$

$$t_{ACO} = 540 ns$$

540nsという値は、 $t_{ACO}$ で290nsの条件を満たします。

図35より、t<sub>ACO</sub>は次のようになります。

$$2.5 (1/F_{SCLK}) + t_8 + t_{QUIET}$$

ここで、 $t_8$ =35nsです。これにより、 $t_{QUIET}$ の値として225nsが得られ、60nsの最小条件を満たすことになります。

図35. シリアル・インターフェースのタイミング例

REV. B — 19 —

## 動作モード

AD7452の動作モードは、変換時に $\overline{\mathbf{CS}}$ 信号のロジック状態を制御して選択します。動作モードには、ノーマルとパワーダウンの2つがあります。変換開始後に $\overline{\mathbf{CS}}$ がハイレベルになるポイントで、AD7452がパワーダウン・モードになるかどうかが決まります。また、すでにパワーダウン・モードになっている場合も、 $\overline{\mathbf{CS}}$ によってノーマル動作に戻るか、パワーダウン・モードにとどまるかを制御します。この2つの動作モードから、柔軟なパワーマネジメント・オプションが得られます。これらのオプションを選ぶことで、さまざまなアプリケーションの要求に最適な消費電力/スループット・レート比を選択できます。

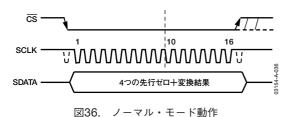

#### ノーマル・モード

最高のスループット・レート性能を得るためのモードです。 AD7452は常時フルパワーアップ状態にとどまるため、パワーアップ時間を気にする必要はありません。図36に、このモードでのAD7452の一般的な動作図を示します。「シリアル・インターフェース」で説明したように、 $\overline{\text{CS}}$ の立ち下がりエッジで変換を開始します。デバイスを常時パワーアップさせておくには、 $\overline{\text{CS}}$ の立ち下がりエッジの後、少なくとも10個のSCLK立ち下がりエッジが経過するまで $\overline{\text{CS}}$ をローレベルに維持しておく必要があります。

10番目のSCLK立ち下がりエッジの後、16番目のSCLK立ち下がりエッジの前までに任意のタイミングで $\overline{\mathbf{CS}}$ をハイレベルにすると、デバイスはパワーアップ状態のままですが、変換が終了して、SDATAがスリーステートに戻ります。変換を完了して完全な変換結果にアクセスするには、シリアル・クロックで16サイクルが必要です。 $\overline{\mathbf{CS}}$ は、次の変換までアイドルのハイレベルを維持するか、次の変換の前の一定の時点までアイドルのローレベルにすることができます。データ転送が完了して、SDATAがスリーステートに戻った後は、静止時間 $\mathbf{t}_{\mathbf{QUIET}}$ の経過後に $\overline{\mathbf{CS}}$ を再度ローレベルにして、次の変換を開始することができます。

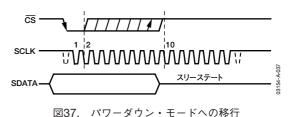

#### パワーダウン・モード

このモードは、低スループット・レートが必要なアプリケーションでの使用を目的としています。各変換の間にADCをパワーダウンしたり、一連の変換を高スループット・レートで実行した後、このようなバースト的な複数の変換と変換の間に比較的長時間にわたってADCをパワーダウンします。AD7452がパワーダウン・モードになると、全アナログ回路がパワーダウンします。パワーダウン・モードにするには、図37に示すように、SCLKの2番目の立ち下がりエッジの後、SCLKの10番目の立ち下がりエッジの前までに任意の時点でで気をハイレベルにして変換プロセスを中断させる必要があります。

SCLKのこのウインドウ内で $\overline{\mathbf{CS}}$ をハイレベルにすると、デバイスがパワーダウン状態に入り、 $\overline{\mathbf{CS}}$ の立ち下がりエッジで開始した変換を終了し、SDATAがスリーステートに戻ります。 $\overline{\mathbf{CS}}$ の立ち上がりエッジからSDATAスリーステート・イネーブルまでの時間は、 $\mathbf{t_8}$ を超えることはできません(「タイミング仕様」を参照)。SCLKの2番目の立ち下がりエッジの前に $\overline{\mathbf{CS}}$ がハイレベルになっても、デバイスはノーマル・モードのままで、パワーダウンしません。この機能によって、 $\overline{\mathbf{CS}}$ ラインのグリッチによって偶発的にパワーダウンが生じるのを防ぎます。

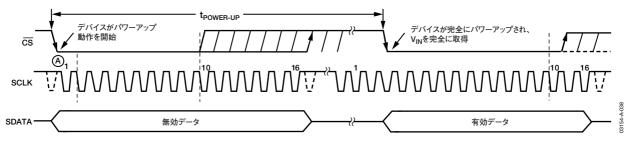

この動作モードを終了してAD7452を再度パワーアップするために、ダミー変換を実行します。 $\overline{CS}$ の立ち下がりエッジでパワーアップを開始し、 $\overline{CS}$ がローレベルになっている間パワーアップを続け、SCLKの10番目の立ち下がりエッジで終了します。デバイスは $1\mu$ s経過後に完全にパワーアップし、図38に示すように、次の変換から有効なデータが得られます。

SCLKの10番目の立ち下がりエッジの前に $\overline{CS}$ がハイレベルになると、AD7452は再びパワーダウン・モードに戻ります。これにより、 $\overline{CS}$ ラインのグリッチや、 $\overline{CS}$ がローレベルのときの不注意な8サイクルのSCLKによって偶発的にパワーアップするのを防ぎます。このため、デバイスは $\overline{CS}$ の立ち下がりエッジでパワーアップを開始できますが、SCLKの10番目の立ち下がりエッジの前に $\overline{CS}$ の立ち上がりエッジが発生すると、再びパワーダウン状態に戻ります。

#### パワーアップ時間

AD7452のパワーアップ時間は1 $\mu$ s(typ)です。10MHzまでの任意のSCLK周波数で、1ダミー・サイクルさえあればデバイスがパワーアップできることになります。ダミー・サイクルが完了すると、ADCはフルパワーアップして、正常な入力信号を取り込むことができます。この場合も、ダミー変換後にバスがスリーステートに戻った時点から $\overline{CS}$ の次の立ち下がりエッジまで、静止時間 $t_{OUIET}$ が必要です。

555kSPSの最大スループット・レートでの動作時、AD7452は、1ダミー・サイクルつまり1µsでパワーアップして±0.5LSBの範囲内で信号を取得します。1ダミー・サイクルでパワーダウン・モードからパワーアップするとき(図38)、デバイスのパワーダウン中はホールド・モードにあったトラック・アンド・ホールドが、 $\overline{CS}$ の立ち下がりエッジ後にデバイスが受け取る最初のSCLKエッジの後でトラック・モードに戻ります。これを図38のポイントAに示します。

任意のSCLK周波数でデバイスをパワーアップさせて $V_{IN}$ を入力するにはダミー・サイクル1つで十分ですが、必ずしも16 SCLKというフルのダミー・サイクルがないとデバイスをパワーアップして $V_{IN}$ を完全に得られないわけではありません。デバイスのパワーアップと入力信号の取得には $1\mu s$ で十分です。

たとえば、5MHzのSCLK周波数をADCに入力する場合、サイクル・タイムは $3.2\mu s$ (つまり、 $1/(5MHz) \times 16$ )になります。 $3.2\mu s$ の1 ダミー・サイクルで、デバイスはパワーアップして $V_{IN}$ を完全に入力します。ただし、5MHzのSCLKでは $1\mu s$ 後に、SCLKの5 サイクル分しか経過していません。この時点でも、ADCは完全にパワーアップして信号が取得できます。したがって、この場合は、10 番目のSCLKの立ち下がりエッジの後に $\overline{CS}$ をハイレベルにし、さらに $t_{QUIET}$  経過後に再度ローレベルにして、変換を開始します。

最初にAD7452に電源を供給するとき、パワーダウン・モードかノーマル・モードのいずれかでADCがパワーアップします。このため、デバイスが完全にパワーアップしてから有効な変換を開始できるように、1ダミー・サイクルを経過させることを推奨します。同様に、デバイスをパワーダウン・モードでパワーアップしたい場合も、図37に示すようなサイクルを実行することで、ダミー・サイクルを使ってデバイスを確実にパワーダウン・モードにすることができます。

AD7452に電源を供給した後のパワーアップ時間は、パワーダウン・モードからのパワーアップ時と同じです。デバイスがノーマル・モードで完全にパワーアップする場合は、約1µs必要です。希望する動作モードにするためのダミー・サイクルは、1µs待ってから行う必要はありません。ADCに電源を入れた直後にダミー・サイクルを発生させることができます。ダミー変換の直後に最初の有効な変換を実行する場合は、十分なアクイジション時間を確保できるように注意してください。

前述のように、パワーダウン・モードからパワーアップする際には、デバイスは、でSの立ち下がりエッジの後に入力された最初のSCLKエッジでトラック・モードに戻ります。ただし、電源を入れた後初めてADCがパワーアップする際は、トラック・アンド・ホールドはすでにトラック・モードになっています。つまり、ADCが希望の動作モードでパワーアップしたため、モードの変更にダミー・サイクルが不要な場合は、トラック・アンド・ホールドをトラック・モードにするためのダミー・サイクルも不要ということになります(ADCの電源電流をモニターできることを前提としています)。

図38. パワーダウン・モードの終了

REV. B — 21 —

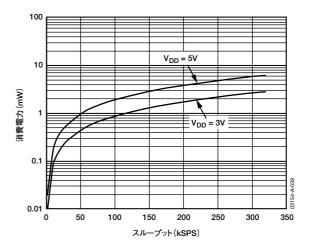

#### 消費電力とスループット・レートの関係

変換しないときにAD7452をパワーダウン・モードにしておけば、低いスループット・レートでADCの平均消費電力が低減します。図39は、スループット・レートを減少させると、それだけデバイスがパワーダウン状態にとどまる時間が長くなり、その結果、平均消費電力が減少することを示しています。5Vおよび3Vの電源の場合を示しています。

たとえば、AD7452が連続サンプリング・モードで、スループット・レート=100kSPS、SCLK=10MHzで、変換と変換の間にパワーダウン・モードになる場合、消費電力は次のようになります。

ノーマル動作時の消費電力=7.25mW (max) ( $V_{DD}=5V$ の場合)

パワーアップ時間が1ダミー・サイクル(サイクルの10番目の SCLKの立ち上がりエッジ後に $\overline{CS}$ がハイレベルになり、次いで静止時間後にローレベルになる場合、 $1.06\mu s$ )で、残りの変換時間が別のサイクル( $1.6\mu s$ )になる場合、AD7452は各変換サイクル中の $2.66\mu s^*$ の間に7.25mWを消費することになります。

スループット・レートが100kSPSの場合は、サイクル・タイムは $10\mu$ sとなり、各サイクルの平均消費電力は、次のようになります。

#### $(2.66/10) \times 7.25 mW = 1.92 mW$

同様に、 $V_{DD}$ =3Vの場合、ノーマル動作時の最大消費電力は3.3mWになります。

このことから、AD7452は各変換サイクル中の2.66 $\mu$ s\*の間に 3.3 $\mu$ Wを浪費することになります。

したがって、スループット・レート=100kSPSでの各サイクルの平均消費電力は、次のようになります。

#### $(2.66/10) \times 3.3 mW = 0.88 mW$

図39に示す消費電力は、このようにして計算した値です。

320kSPSを上回るスループット・レートでは、最適な消費電力性能を得るためにシリアル・クロック周波数を下げることが推奨します。

図39. パワーダウン・モードでの電力と スループット・レートの関係

#### マイクロプロセッサおよびDSPとの インターフェース

AD7452内蔵のシリアル・インターフェースを使えば、さまざまな種類のマイクロプロセッサに直接接続することができます。ここでは、いくつかの一般的なマイクロコントローラやDSPのシリアル・インターフェース・プロトコルとAD7452をインターフェースさせる方法について説明します。

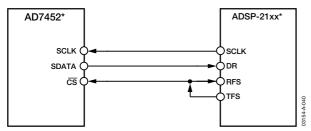

AD7452とADSP-21xxとのインターフェース

ADSP-21xxファミリーのDSPは、グルーロジックなしで直接 AD7452にインターフェースすることができます。

SPORT制御レジスタを次のように設定します。

TFSW=RFSW=1、オルタネート・フレーミング INVRFS=INVTFS=1、アクティブ・ロー・フレーム信号 DTYPE=00、データ右揃え

SLEN=1111、16ビット・データ・ワード

ISCLK=1、内部シリアル・クロック

TFSR = RFSR = 1, ワードごとのフレーム

IRFS = 0

ITFS=1

パワーダウン・モードにするときは、SLENを1001に設定して 8ビットのSCLKバーストを発生させます。

接続図を図40に示します。ADSP-21xxでは、SPORTのTFSとRFSを一緒にし、TFSを出力、RFSを入力に設定します。DSPをオルタネート・フレーミング・モードで動作させ、SPORT制御レジスタを上記のように設定します。TFSで発生するフレーム同期化信号を $\overline{\mathbb{CS}}$ に接続し、すべての信号処理アプリケーションでそうであるように、等間隔サンプリングを行う必要があります。ただし、この例では、タイマー割り込みを使ってADCのサンプリング・レートを制御するため、場合によっては等間隔サンプリングにならないことがあります。

— 22 — REV. B

<sup>\*</sup> この数値は、パワーダウン・モードに入るための時間がきわめて短いことを前提にしています。パワーダウン・モードに入るために使用するクロックのパーストが長くなると、この数値も大きくなります。

\* わかりやすくするために他のピンは省略してあります。

#### 図40. ADSP-21xxとのインターフェース

タイマー・レジスタなどには、必要なサンプル間隔で割り込みを発生させる値が書き込まれます。割り込みを受け付けると、TFS/DT(ADC制御ワード)と一緒に値を転送します。TFSを使って、RFS、つまりデータの読み出しを制御します。シリアル・クロックの周波数は、SCLKDIVレジスタで設定します。TFSと一緒に送信する命令が与えられると(AX0=TX0)、SCLKの状態をチェックします。SCLKがハイレベル、ローレベル、ハイレベルに変化するのを待ってから、DSPが送信を開始します。送信命令がSCLKの立ち上がりエッジまたはその近くで発生するようにタイマーとSCLKの値が設定されていれば、データの送信が行われるか、または次のクロック・エッジまで待つことになります。

たとえば、ADSP-2111には16MHzのマスター・クロック周波数があります。SCLKDIVレジスタに値3を書き込むと、2MHzのSCLKが得られ、各1 SCLK周期が8マスター・クロック周期に等しくなります。タイマー・レジスタに値803を書き込んだ場合、割り込みと割り込みの間、およびその後の送信命令と送信命令の間に、100.5回のSCLKが発生します。この場合、送信命令がSCLKのエッジで発生するため、不等間隔のサンプリングになります。割り込みと割り込みの間のSCLKの数が整数Nの場合は、DSPは等間隔サンプリングを実行します。

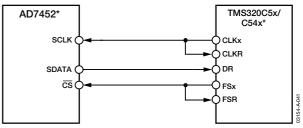

#### AD7452とTMS320C5x/C54xとのインターフェース

TMS320C5x/C54xのシリアル・インターフェースでは、連続シリアル・クロックとフレーム同期信号を使って、データ転送動作をAD7452などのペリフェラル・デバイスに同期化しています。 CS 入力を使えば、グルーロジックなしで、TMS320C5x/C54xとAD7452のインターフェースが簡単にできます。TMS320C5x/C54xのシリアル・ポートを内部CLKX(Txシリアル・クロック)とFSX(Txフレーム同期)を使うバースト・モードで動作するように設定します。シリアル・ポート制御レジスタ(SPC)は、FO=0、FSM=1、MCM=1、TxM=1に設定しておきます。AD7452にパワーダウン・モードにするには、フォーマット・ビットFOを「1」に設定してワード長を8ビットに設定します。図41に接続図を示します。なお、信号処理アプリケーションでは、TMS320C5x/C54xからのフレーム同期信号で等間隔サンプリングを実行する必要があります。

\* わかりやすくするために他のピンは省略してあります。

図41. TMS320C5x/C54xとのインターフェース

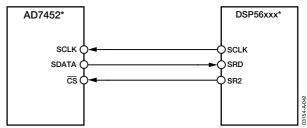

#### AD7452とDSP56xxxとのインターフェース

図42の接続図に、AD7452と、モトローラ社のDSPファミリー、DSP56xxxのSSI(同期シリアル・インターフェース)との接続方法を示します。SSIは同期モードで動作し(CRBレジスタのSYNビット=1)、TxとRxに対する1ワードのフレーム同期を内部で発生します(CRBのFSL1ビット=0かつFSL0ビット=0)。CRAでWL1ビット=1かつWL0ビット=0に設定し、ワード長=16に設定します。AD7452をパワーダウン・モードで動作する場合、CRAでWL1ビット=0かつWL0ビット=0に設定してワード長を8ビットに変更できます。信号処理アプリケーションでは、DSP56xxxからのフレーム同期信号で等間隔サンプリングを実行する必要があります。

\* わかりやすくするために他のピンは省略してあります。

図42. DSP56xxxとのインターフェース

REV. B — 23 —

#### アプリケーション情報

#### グラウンディングとレイアウト

AD7452を実装するプリント回路ボードは、アナログ部とデジタル部を分離して、ボード内でそれぞれをまとめて配置するように設計する必要があります。これによって、分離が簡単にできるグラウンド・プレーンを使用できるようになります。一般に、エッチング部分を最小化すると最適なシールド効果が得られるため、グラウンド・プレーンではそのような技術を使用してください。デジタル・グラウンド・プレーンとアナログ・グラウンド・プレーンは1点のみで接続し、AD7452のGNDピンにできるだけ近い場所に星型グラウンド・ポイントを構成してください。チップにノイズが混入しないよう、デバイスの真下にデジタル・ラインを通さないようにしてください。ノイズ混入を防止するため、アナログ・グラウンド・プレーンをAD7452の下に配置するようにします。AD7452の電源ラインをできるだけ太いパターンにしてインピーダンスを下げ、電源ライン上のグリッチによる影響を軽減します。

クロックなどの高速のスイッチング信号をデジタル・グラウンドでシールドして、ボードの他の部分にノイズが拡散しないようにします。また、クロック信号がアナログ入力の近くを通らないようにします。デジタル信号とアナログ信号は交差しないようにしてください。ボードの反対側のパターンは、互いに直角になるように配置します。これにより、ボードを通過するフィードスルーの影響を低減できます。マイクロストリップ技術は最善ですが、両面ボードでは常に使用できるとは限りません。

この技術では、ボードの部品面をグラウンド・プレーン専用にして、信号をハンダ面に配線します。デカップリングを正しく行うことも重要です。すべてのアナログ電源とGNDの間に $10\mu$ Fのタンタル・コンデンサと $0.1\mu$ Fのコンデンサを並列接続してデカップリングします。デカップリング部品の効果を最大にするため、できるだけデバイスの近くに配置します。

#### AD7452の性能評価

評価ボード・パッケージには、組み立ておよびテスト済みの評価ボード、ドキュメント、および評価ボード・コントローラを介してPCからボードを制御するためのソフトウェアが含まれています。評価ボード・コントローラは、AD7452評価ボードのほか、多くのアナログ・デバイセズの評価ボード(末尾にCB識別子が付くもの)と組み合わせて使用できます。これによって、AD7452のAC性能とDC性能のデモ/評価ができます。

ソフトウェアを使うと、AD7452のACテスト (高速フーリエ変換) とDCテスト (コードのヒストグラム) ができます。詳細については、評価ボードのアプリケーション・ノートをご覧ください。

— 24 — REV. B

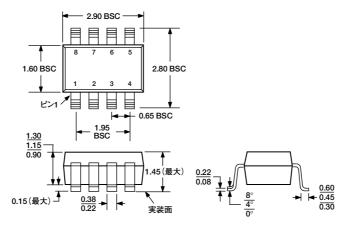

## 外形寸法

JEDEC規格MO-178BAに準拠

図43. 8ピン・スモール・アウトライン・トランジスタ・パッケージ [SOT-23] (RT-8) 寸法単位:mm

#### オーダー・ガイド

| モデル                                                                                             | 温度範囲                 | 直線性誤差(LSB) <sup>1</sup> | パッケージ・オプション <sup>2</sup>            | ブランド       |

|-------------------------------------------------------------------------------------------------|----------------------|-------------------------|-------------------------------------|------------|

| AD7452BRT-R2<br>AD7452BRM-REEL7<br>EVAL-AD7452CB <sup>3</sup><br>EVAL-CONTROL BRD2 <sup>4</sup> | -40~+85℃<br>-40~+85℃ |                         | RT-8<br>RT-8<br>評価ボード<br>コントローラ・ボード | C07<br>C07 |

<sup>1</sup> この直線性誤差は、積分非直線性誤差を意味します。

REV. B -25-

<sup>&</sup>lt;sup>2</sup> RT=SOT-23

<sup>-</sup> RI=SOI-23 3 単独の評価ボードとしても、評価ボード・コントローラと組み合わせて評価/デモ用に使用することもできます。 4 評価ボード・コントローラ。このボードは完備したユニットになっており、末尾番号CBが付くすべてのアナログ・デバイセズ製評価ボードに対し、PCで制御と通信ができます。 完備した評価キットとして、ADC評価ボード(EVAL-AD7452CB、EVAL-CONTROL BRD2、および12VのACトランス)を注文する必要があります。詳細については、 AD7452のアプリケーション・ノートを参照してください。

— 26 — REV. B

REV. B — 27 —

303154-0-2/04(B)-J