この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。 この正誤表は、 2011 年 2 月 9 日現在、アナログ・デバイセズ株式会社で確認した誤りを 記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

**正誤表作成年月日**: 2011 年 2 月 9 日

製品名: AD7356

対象となるデータシートのリビジョン(Rev): Rev.0

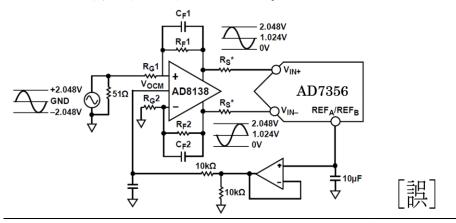

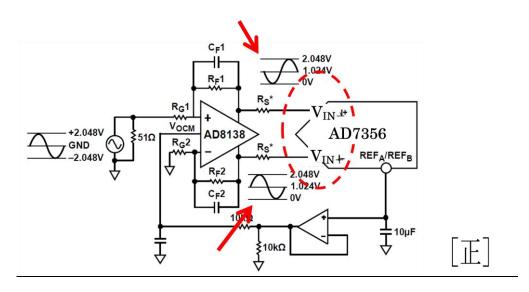

訂正箇所: 14頁 図20 (Fig 20) AD8138 と AD7356 の接続が間違っています。

下記の図を参照してください。

アナログ・デバイセズ株式会社

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹 芝サウスタワービル

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪 MT ビル 2 号

電話 06 (6350) 6868

# 差動入力、同時サンプリング、5 MSPS 12ビット・デュアルSAR ADC

**AD7356**

#### 特長

デュアル 12 ビット SAR ADC 同時サンプリング スループット・レート: チャンネルあたり 5 MSPS V<sub>DD</sub> = 2.5 V の仕様 変換レイテンシなし 消費電力: 5 MSPS で 36 mW 内蔵リファレンス電圧: 2.048 V ± 0.25%、6 ppm/°C

SPI/QSPI™/MICROWIRE™/DSP に互換 動作温度範囲: -40°C~+125°C

デュアル・リザルト読み出し機能

高速シリアル・インターフェース:

16 ピン TSSOP パッケージを採用

### 概要

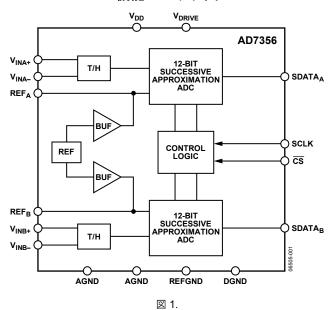

AD7356<sup>1</sup>は、高速低消費電力の 12 ビット・デュアル逐次比較型 ADCであり、2.5 Vの単電源で動作し、最大 5 MSPSのスループ ット・レートを持っています。デバイスは2個のADCを内蔵し ており、各々の前には低ノイズで広帯域幅のトラック・アン ド・ホールド・アンプが配置されており、このアンプは 110 MHzを超える入力周波数を処理することができます。

変換プロセスとデータ・アクイジションは、標準のコントロー ル入力を使って制御されるため、マイクロプロセッサまたは DSP に対して容易にインターフェースすることができます。入 力信号はCSの立ち下がりエッジでサンプルされ、この時点で変 換も開始されます。変換時間は SCLK 周波数によって決定され ます。

AD7356 では高度なデザイン技術を使い、非常に小さい消費電 力で高いスループット・レートを実現しています。2.5 V電源動 作時、5 MSPS スループット・レートでのデバイス消費電流(typ) は 14 mAです。デバイスには、柔軟な消費電力/スループット・ レート管理オプションもあります。

デバイスのアナログ入力範囲は、±V<sub>REF</sub>/2 の差動同相モードです。 AD7356 は 2.048 V のリファレンス電圧を内蔵していますが、外 付けリファレンス電圧を使う場合には、これを上書き接続するこ とができます。

AD7356 は、16 ピンの薄型シュリンク・スモール・アウトライ ン(TSSOP)パッケージを採用しています。

# 1米国特許 No. 6,681,332 により保護されています。

#### 機能ブロック図

#### 製品のハイライト

- 1. 2 系統の ADC 機能を内蔵。これらの機能を使うと、2 チャ ンネルのサンプリングと変換を同時に実行することができ ます。両チャンネルの変換結果は別々のデータ・ラインに 同時に出力。あるいはシリアル・ポートが 1 個しかない場 合には、両チャンネルの変換結果を 1 本のデータ・ライン にマルチプレクスして出力。

- 低消費電力で高スループット。AD7356 は、36 mW の消費 電力で5MSPSのスループット・レートを提供。

- 変換レイテンシなし。AD7356 は 2 個の標準逐次比較型 ADC を内蔵し、CS入力を使用して、またオフの場合には 変換制御を使用して、サンプリング時点の正確な制御が可 能。

#### 表 1.関連デバイス

| Generic | Resolution | Throughput | Analog Input              |

|---------|------------|------------|---------------------------|

| AD7352  | 12-bit     | 3 MSPS     | Differential              |

| AD7266  | 12-bit     | 2 MSPS     | Differential/single ended |

| AD7866  | 12-bit     | 1 MSPS     | Single-ended              |

| AD7366  | 12-bit     | 1 MSPS     | Single-ended bipolar      |

| AD7367  | 14-bit     | 1 MSPS     | Single-ended bipolar      |

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に 関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、 アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様 予告なく変更される場合があります。 本紙記載の商標および登録商標は、各社の所有に属します トは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ©2008 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03 (5402) 8200

# 目次

| 特長            | 1  |

|---------------|----|

| 機能ブロック図       | 1  |

| 概要            | 1  |

| 製品のハイライト      | 1  |

| 改訂履歴          | 2  |

| 仕様            | 3  |

| タイミング仕様       | 5  |

| 絶対最大定格        | 6  |

| ESD の注意       | 6  |

| ピン配置およびピン機能説明 | 7  |

| 代表的な性能特性      | 8  |

| 用語            | 10 |

| 動作原理          | 12 |

| 回路説明          | 12 |

| コンバータの動作      | 12 |

| アナログ入力構造      | 12 |

| アナログ入力              | 13 |

|---------------------|----|

| 差動入力の駆動             | 14 |

| ADC の伝達関数           | 14 |

| 動作モード               | 15 |

| ノーマル動作モード           | 15 |

| パーシャル・パワーダウン・モード    | 15 |

| フル・パワーダウン・モード       | 16 |

| パワーアップ時間            | 17 |

| 消費電力とスループット・レートとの関係 | 17 |

| シリアル・インターフェース       | 18 |

| アプリケーション情報          | 19 |

| グラウンド接続とレイアウト       | 19 |

| AD7356 の性能評価        | 19 |

| 外形寸法                | 20 |

| オーダー・ガイド            | 20 |

### 改訂履歴

10/08—Revision 0: Initial Version

# AD7356

# 仕様

特に指定がない限り、 $V_{DD}$  = 2.5 V ± 10%、 $V_{DRIVE}$  = 2.25 V  $\sim$  3.6 V、内蔵リファレンス電圧= 2.048 V、 $f_{SCLK}$  = 80 MHz、 $f_{SAMPLE}$  = 5 MSPS、 $T_{A}$  =  $T_{MIN} \sim T_{MAX}^{-1}$ 。

表 2.

| Parameter                                             | Min         | Тур  | Max         | Unit   | Test Conditions/Comments                                                                                  |

|-------------------------------------------------------|-------------|------|-------------|--------|-----------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                   |             |      |             |        | $f_{IN} = 1$ MHz sine wave                                                                                |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>              | 70          | 71.5 |             | dB     |                                                                                                           |

| Signal-to-(Noise and Distortion) (SINAD) <sup>2</sup> | 69.5        | 71   |             | dB     |                                                                                                           |

| Total Harmonic Distortion (THD) <sup>2</sup>          |             | -84  | -77.5       | dB     |                                                                                                           |

| Spurious Free Dynamic Range (SFDR) <sup>2</sup>       |             | -85  | -78.5       | dB     |                                                                                                           |

| Intermodulation Distortion (IMD) <sup>2</sup>         |             |      |             |        | fa = 1  MHz + 50  kHz, fb = 1  MHz - 50  KHz                                                              |

| Second-Order Terms                                    |             | -84  |             | dB     |                                                                                                           |

| Third-Order Terms                                     |             | -76  |             | dB     |                                                                                                           |

| ADC-to-ADC Isolation <sup>2</sup>                     |             | -100 |             | dB     | $f_{IN} = 1$ MHz, $f_{NOISE} = 100$ kHz to 2.5 MHz                                                        |

| CMRR <sup>2</sup>                                     |             | -100 |             | dB     | $f_{NOISE} = 100 \text{ kHz to } 2.5 \text{ MHz}$                                                         |

| SAMPLE AND HOLD                                       |             |      |             |        |                                                                                                           |

| Aperture Delay                                        |             |      | 3.5         | ns     |                                                                                                           |

| Aperture Delay Match                                  |             |      | 40          | ps     |                                                                                                           |

| Aperture Jitter                                       |             | 16   |             | ps     |                                                                                                           |

| Full Power Bandwidth                                  |             |      |             |        |                                                                                                           |

| @ 3 dB                                                |             | 110  |             | MHz    |                                                                                                           |

| @ 0.1 dB                                              |             | 77   |             | MHz    |                                                                                                           |

| DC ACCURACY                                           |             |      |             |        |                                                                                                           |

| Resolution                                            | 12          |      |             | Bits   |                                                                                                           |

| Integral Nonlinearity (INL) <sup>2</sup>              |             | ±0.5 | ±1          | LSB    |                                                                                                           |

| Differential Nonlinearity (DNL) <sup>2</sup>          |             | ±0.5 | ±0.99       | LSB    | Guaranteed no missed codes to 12 bits                                                                     |

| Positive Full-Scale Error <sup>2</sup>                |             | ±1   | ±6          | LSB    |                                                                                                           |

| Positive Full-Scale Error Match <sup>2</sup>          |             | ±2   | ±8          | LSB    |                                                                                                           |

| Midscale Error <sup>2</sup>                           |             | +5   | 0/+11       | LSB    |                                                                                                           |

| Midscale Error Match <sup>2</sup>                     |             | ±2   | ±8          | LSB    |                                                                                                           |

| Negative Full-Scale Error <sup>2</sup>                |             | ±1   | ±6          | LSB    |                                                                                                           |

| Negative Full-Scale Error Match <sup>2</sup>          |             | ±2   | ±8          | LSB    |                                                                                                           |

| ANALOG INPUT                                          |             |      |             |        |                                                                                                           |

| Fully Differential Input Range (V <sub>IN+</sub> and  |             |      | $V_{CM}\pm$ | V      | $V_{CM}$ = common-mode voltage, $V_{IN+}$ and                                                             |

| $V_{IN-}$ )                                           |             |      | $V_{REF}/2$ |        | $V_{\text{IN-}}$ must remain within GND and $V_{\text{DD}}$                                               |

| Common-Mode Voltage Range                             | 0.5         |      | 1.9         | V      | The voltage around which $V_{\text{IN+}}$ and $V_{\text{IN-}}$ are centered                               |

| DC Leakage Current                                    |             | ±0.5 | ±5          | μΑ     |                                                                                                           |

| Input Capacitance                                     |             | 32   |             | pF     | When in track mode                                                                                        |

|                                                       |             | 8    |             | pF     | When in hold mode                                                                                         |

| REFERENCE INPUT/OUTPUT                                |             |      |             |        |                                                                                                           |

| V <sub>REF</sub> Input Voltage Range                  | 2.048 + 0.1 |      | $V_{DD}$    | V      |                                                                                                           |

| V <sub>REF</sub> Input Current                        |             | 0.3  | 0.45        | mA     | When in reference overdrive mode                                                                          |

| V <sub>REF</sub> Output Voltage                       | 2.038       |      | 2.058       | V      | $2.048 \text{ V} \pm 0.5\% \text{ max } @ \text{V}_{DD} = 2.5 \text{ V} \pm 5\%$                          |

|                                                       | 2.043       |      | 2.053       | V      | $2.048 \text{ V} \pm 0.25\% \text{ max } @V_{DD} = 2.5 \text{ V} \pm 5\% \text{ and } 25^{\circ}\text{C}$ |

| V <sub>REF</sub> Temperature Coefficient              |             | 6    | 20          | ppm/°C |                                                                                                           |

| V <sub>REF</sub> Long Term Stability                  |             | 100  |             | ppm    | For 1000 hours                                                                                            |

| V <sub>REF</sub> Thermal Hysteresis <sup>2</sup>      |             | 50   |             | ppm    |                                                                                                           |

| V <sub>REF</sub> Noise                                |             | 60   |             | μV rms |                                                                                                           |

| V <sub>REF</sub> Output Impedance                     |             | 1    |             | Ω      |                                                                                                           |

Rev. 0 - 3/20 -

| Parameter                                    | Min                        | Тур        | Max                                                    | Unit    | Test Conditions/Comments                     |

|----------------------------------------------|----------------------------|------------|--------------------------------------------------------|---------|----------------------------------------------|

| LOGIC INPUTS                                 |                            |            |                                                        |         |                                              |

| Input High Voltage (V <sub>INH</sub> )       | $0.6 \times V_{DRIVE}$     |            |                                                        | V       |                                              |

| Input Low Voltage (V <sub>INL</sub> )        |                            |            | $\begin{array}{l} 0.3 \times \\ V_{DRIVE} \end{array}$ | V       |                                              |

| Input Current (I <sub>IN)</sub> )            |                            |            | ±1                                                     | μΑ      | $V_{IN} = 0 \text{ V or } V_{DRIVE}$         |

| Input Capacitance (C <sub>IN</sub> )         |                            | 3          |                                                        | pF      |                                              |

| LOGIC OUTPUTS                                |                            |            |                                                        |         |                                              |

| Output High Voltage (VOH)                    | $V_{DRIVE} - 0.2$          |            |                                                        | V       |                                              |

| Output Low Voltage (VoL)                     |                            |            | 0.2                                                    | V       |                                              |

| Floating-State Leakage Current               |                            |            | ±1                                                     | μΑ      |                                              |

| Floating-State Output Capacitance            |                            | 5.5        |                                                        | pF      |                                              |

| Output Coding                                | Str                        | aight bina | ary                                                    |         |                                              |

| CONVERSION RATE                              |                            |            |                                                        |         |                                              |

| Conversion Time                              | $t_2 + 13 \times t_{SCLK}$ |            |                                                        | ns      |                                              |

| Track-and-Hold Acquisition Time <sup>2</sup> |                            |            | 30                                                     | ns      | Full-scale step input, settling to 0.5 LSBs  |

| Throughput Rate                              |                            |            | 5                                                      | MSPS    |                                              |

| POWER REQUIREMENTS <sup>3</sup>              |                            |            |                                                        |         |                                              |

| $ m V_{DD}$                                  | 2.25                       |            | 2.75                                                   | V       | Nominal $V_{DD} = 2.5 \text{ V}$             |

| $V_{ m DRIVE}$                               | 2.25                       |            | 3.6                                                    | V       |                                              |

| ${ m I_{TOTAL}}^4$                           |                            |            |                                                        |         | Digital inputs = $0 \text{ V or } V_{DRIVE}$ |

| Normal Mode (Operational)                    |                            | 14         | 20                                                     | mA      |                                              |

| Normal Mode (Static)                         |                            | 6          | 7.8                                                    | mA      | SCLK on or off                               |

| Partial Power-Down Mode                      |                            | 3.5        | 4.5                                                    | mA      | SCLK on or off                               |

| Full Power-Down Mode                         |                            | 5          | 40                                                     | μΑ      | SCLK on or off, -40°C to +85°C               |

|                                              |                            |            | 90                                                     | μΑ      | SCLK on or off, 85°C to 125°C                |

| Power Dissipation                            |                            |            |                                                        |         |                                              |

| Normal Mode (Operational)                    |                            | 36         | 59                                                     | mW      |                                              |

| Normal Mode (Static)                         |                            | 16         | 21.5                                                   | mW      | SCLK on or off                               |

| Partial Power-Down Mode                      |                            | 9.5        | 11.5                                                   | mW      | SCLK on or off                               |

| Full Power-Down Mode                         |                            | 16         | 110                                                    | $\mu W$ | SCLK on or off, -40°C to +85°C               |

|                                              |                            |            | 250                                                    | μW      | SCLK on or off, 85°C to 125°C                |

<sup>&</sup>lt;sup>1</sup> 温度範囲: Y グレード: −40°C~+125°C; B グレード: −40°C~+85°C。

Rev. 0 - 4/20 -

$<sup>^2</sup>$  用語 のセクション参照。

$<sup>^3</sup>$  電流と消費電力の typ 値仕様は、 $\rm V_{DD}$  = 2.5 V かつ  $\rm V_{DRIVE}$  = 3.0 V の場合の結果に基づきます。

$<sup>^4\,</sup>I_{TOTAL}$ は $\,V_{DD}$ と $\,V_{DRIVE}$ に流入する合計電流。

### タイミング仕様

特に指定がない限り、 $V_{DD}$  = 2.5 V ± 10%、 $V_{DRIVE}$  = 2.25 V ~ 3.6 V、内蔵リファレンス電圧 = 2.048 V、 $T_A$  =  $T_{MAX\sim}T_{MIN}^{-1}$ 。

表 3.

| Parameter      | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Description                                                                                         |

|----------------|----------------------------------------------|---------|-----------------------------------------------------------------------------------------------------|

| $f_{SCLK}$     | 50                                           | kHz min |                                                                                                     |

|                | 80                                           | MHz max |                                                                                                     |

| $t_{CONVERT}$  | $t_2 + 13 \times t_{SCLK}$                   | ns max  | $t_{SCLK} = 1/f_{SCLK}$                                                                             |

| $t_{QUIET}$    | 5                                            | ns min  | Minimum time between end of serial read and next falling edge of $\overline{\text{CS}}$             |

| $t_2$          | 5                                            | ns min  | CS to SCLK setup time                                                                               |

| $t_3^2$        | 6                                            | ns max  | Delay from $\overline{CS}$ until SDATA <sub>A</sub> and SDATA <sub>B</sub> are three-state disabled |

| $t_4^{2,3}$    |                                              |         | Data access time after SCLK falling edge                                                            |

|                | 12.5                                         | ns max  | $1.8 \text{ V} \le \text{V}_{\text{DRIVE}} < 2.25 \text{ V}$                                        |

|                | 11                                           | ns max  | $2.25 \text{ V} \le \text{V}_{\text{DRIVE}} < 2.75 \text{ V}$                                       |

|                | 9.5                                          | ns max  | $2.75 \text{ V} \le \text{V}_{\text{DRIVE}} < 3.3 \text{ V}$                                        |

|                | 9                                            | ns max  | $3.3 \text{ V} \leq \text{V}_{\text{DRIVE}} \leq 3.6 \text{ V}$                                     |

| $t_5$          | 5                                            | ns min  | SCLK low pulse width                                                                                |

| $t_6$          | 5                                            | ns min  | SCLK high pulse width                                                                               |

| $t_7^2$        | 3.5                                          | ns min  | SCLK to data valid hold time                                                                        |

| $t_8^2$        | 9.5                                          | ns max  | CS rising edge to SDATA <sub>A</sub> , SDATA <sub>B</sub> high impedance                            |

| t <sub>9</sub> | 5                                            | ns min  | CS rising edge to falling edge pulse width                                                          |

| $t_{10}^{2}$   | 4.5                                          | ns min  | SCLK falling edge to SDATA <sub>A</sub> , SDATA <sub>B</sub> high impedance                         |

|                | 9.5                                          | ns max  | SCLK falling edge to SDATA <sub>A</sub> , SDATA <sub>B</sub> high impedance                         |

<sup>&</sup>lt;sup>1</sup> 温度範囲: Y グレード: −40°C~+125°C; B グレード: −40°C~+85°C。

$<sup>^2</sup>$  SDATA<sub>A</sub> と SDATA<sub>B</sub>に負荷容量 10 pF を接続して規定。

$<sup>^3</sup>$  出力が 0.4~V または 2.4~V を横切るために要する時間。

### 絶対最大定格

表 4.

| Parameter                                                | Rating                                        |  |

|----------------------------------------------------------|-----------------------------------------------|--|

| V <sub>DD</sub> to AGND, DGND, REFGND                    | -0.3 V to +3 V                                |  |

| V <sub>DRIVE</sub> to AGND, DGND, REFGND                 | -0.3 V to +5 V                                |  |

| $V_{DD}$ to $V_{DRIVE}$                                  | -5  V to  +3  V                               |  |

| AGND to DGND to REFGND                                   | -0.3 V to +0.3 V                              |  |

| Analog Input Voltages <sup>1</sup> to AGND               | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$    |  |

| Digital Input Voltages <sup>2</sup> to DGND              | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$ |  |

| Digital Output Voltages <sup>3</sup> to DGND             | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$ |  |

| Input Current to Any Pin Except Supply Pins <sup>4</sup> | ±10 mA                                        |  |

| Operating Temperature Range                              |                                               |  |

| Y Grade                                                  | -40°C to +125°C                               |  |

| B Grade                                                  | −40°C to +85°C                                |  |

| Storage Temperature Range                                | −65°C to +150°C                               |  |

| Junction Temperature                                     | 150°C                                         |  |

| TSSOP                                                    |                                               |  |

| $\theta_{JA}$ Thermal Impedance                          | 143°C/W                                       |  |

| $\theta_{JC}$ Thermal Impedance                          | 45°C/W                                        |  |

| Lead Temperature, Soldering                              |                                               |  |

| Reflow Temperature (10 sec to 30 sec)                    | 255°C                                         |  |

| ESD                                                      | 1.5 kV                                        |  |

$<sup>^1</sup>$ アナログ入力電圧は、 $V_{INA+}$ 、 $V_{INA-}$ 、 $V_{INB+}$ 、 $V_{INB-}$ 、REFA、REFB。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒 久的な損傷を与えることがあります。この規定はストレス定格 の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものでは ありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

#### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 — 6/20 —

$<sup>^2</sup>$ デジタル入力電圧は、 $\overline{\text{CS}}$ と SCLK。

<sup>&</sup>lt;sup>3</sup>デジタル出力電圧は、SDATA<sub>A</sub>と SDATA<sub>B</sub>。

<sup>&</sup>lt;sup>4</sup>最大 100 mA までの過渡電流では SCR ラッチ・アップは生じません。

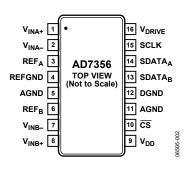

# ピン配置およびピン機能説明

図 2.ピン配置

### 表 5.ピン機能の説明

| <br>ピン番<br>号 | 記号                                         | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2         | V <sub>INA+</sub> , V <sub>INA-</sub>      | ADC A のアナログ入力。これらのアナログ入力でフル差動入力対を構成します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3、6          | REF <sub>A</sub> 、REF <sub>B</sub>         | リファレンス電圧デカップリング・コンデンサ・ピン。各 ADC のリファレンス・バッファをデカップリングするため、これらのピンと REFGND ピンの間にデカップリング・コンデンサを接続します。各リファレンス・ピンを 10 μF のコンデンサでデカップリングすることが推奨されます。出力にバッファが付いている場合、内蔵リファレンス電圧をこれらのピンから出力して、システムの他の部分に供給することができます。公称内蔵リファレンス電圧は 2.048 Vで、これらのピンに出力されます。これらのピンを外部リファレンス電圧で上書き駆動することもできます。外部リファレンス電圧の入力電圧範囲は、2.048 V + 100 mV~V <sub>DD</sub> です。                                                                                                                                                                                      |

| 4            | REFGND                                     | リファレンス電圧グラウンド。AD7356上のリファレンス回路に対するグラウンド基準ポイントです。すべての外部<br>リファレンス信号は、この REFGND 電圧を基準とします。デカップリング・コンデンサをこのピンと REF <sub>A</sub> ピンお<br>よび REF <sub>B</sub> ピンとの間に接続する必要があります。REFGND ピンをシステムの AGND プレーンへ接続してくださ<br>い。                                                                                                                                                                                                                                                                                                            |

| 5、11         | AGND                                       | アナログ・グラウンド。AD7356上の全アナログ回路に対するグラウンド基準ポイントです。すべてのアナログ入力信号はこの AGND 電圧を基準とする必要があります。AGND 電圧と DGND 電圧は理想的には同電位である必要があり、過渡的なバイアスであっても差が 0.3 V を超えないようにする必要があります。                                                                                                                                                                                                                                                                                                                                                                  |

| 7、8          | $V_{INB-}$ , $V_{INB+}$                    | ADC B のアナログ入力。これらのアナログ入力でフル差動入力対を構成します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9            | $V_{DD}$                                   | 電源入力。AD7356の $V_{DD}$ 範囲は $2.5~V \pm 10\%$ です。 $0.1~\mu F$ のコンデンサと $10~\mu F$ のタンタル・コンデンサの並列接続により、電源を AGND ヘデカップリングしてください。                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10           | CS                                         | チップ・セレクト。アクティブ・ローのロジック入力。この入力は、AD7356上での変換開始機能とシリアル・データ転送フレーミング機能により共用されています。                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12           | DGND                                       | デジタル・グラウンド。AD7356上の全デジタル回路に対するグラウンド基準ポイントです。このピンをシステムのDGNDプレーンへ接続してください。DGND電圧と AGND電圧は理想的には同電位である必要があり、過渡的なバイアスであっても差が 0.3 V を超えないようにする必要があります。                                                                                                                                                                                                                                                                                                                                                                             |

| 13、14        | SDATA <sub>B</sub> ,<br>SDATA <sub>A</sub> | シリアル・データ出力。データが各ピンにシリアル・データ・ストリームとして出力されます。ビットは SCLK 入力の立ち下がりエッジで出力されます。AD7356 からの $12$ ビット・データをアクセスするときは、 $14$ 個の SCLK 立ち下がりエッジが必要です。両 ADC の同時変換結果が両データ出力ピンに同時に出力されます。データ・ストリームでは、 $2$ ビットのゼロの後に $12$ ビットの変換データが続きます。データは MSB ファーストです。AD7356 上で、SCLK の $14$ サイクル間ではなく $16$ サイクル間、 $\overline{CS}$ がロー・レベルにされると、 $12$ ビット・データの後ろに $2$ ビットのゼロが出力されます。SDATAA または SDATAB 上で、 $\overline{CS}$ がさらに SCLK の $16$ サイクル間ロー・レベルにされると、SDATA ピン上で他の ADC からのデータが続きます。この機能を使うと、両 ADC の同時変換データをSDATAA または SDATAB にシリアル・フォーマットで出力することができます。 |

| 15           | SCLK                                       | シリアル・クロック。ロジック入力。シリアル・クロック入力は、AD7356からのデータをアクセスするシリアル・クロックを提供します。このクロックは、変換プロセスのクロック・ソースとしても使われます。                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16           | V <sub>DRIVE</sub>                         | ロジック電源入力。このピンに入力された電圧が、インターフェースで使用する電圧を決定します。このピンの電圧は、 $V_{DD}$ の電圧と異なることができます。 $V_{DRIVE}$ 電源は、 $0.1~\mu F$ のコンデンサと $10~\mu F$ のタンタル・コンデンサの並列接続により DGND ヘデカップリングする必要があります。                                                                                                                                                                                                                                                                                                                                                  |

Rev. 0 - 7/20 -

## **AD7356**

## 代表的な性能特性

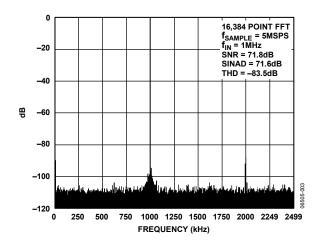

図 3.代表的な FFT

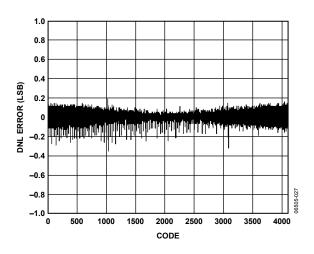

図 4.DNL 誤差(Typ)

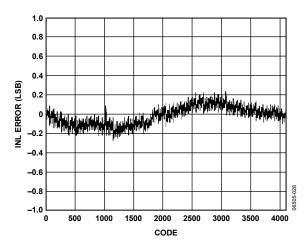

図 5.INL 誤差(Typ)

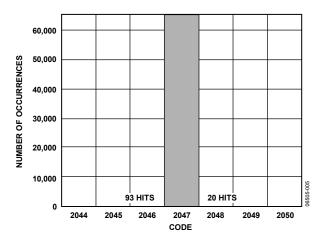

図 6.65,000 個のサンプルに対するコードのヒストグラム

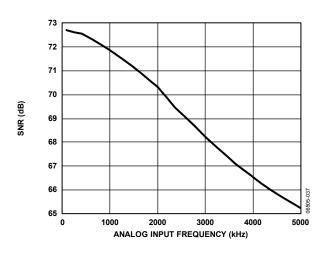

図 7.SNR 対アナログ入力周波数

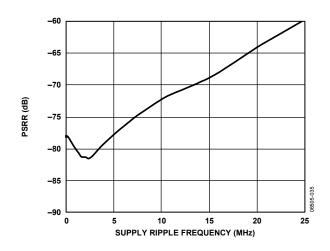

図 8.PSRR 対電源リップル周波数、電源デカップリングなし

Rev. 0 - 8/20 -

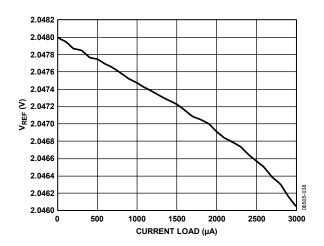

図 9.V<sub>REF</sub>対リファレンス電圧出力電流駆動

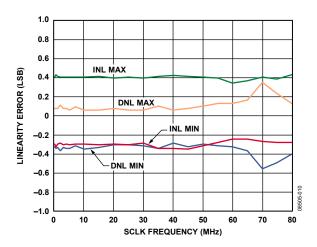

図 10.直線性誤差対 SCLK 周波数

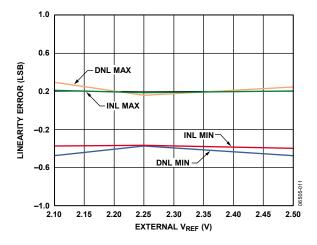

図 11.直線性誤差対外部 V<sub>REF</sub>

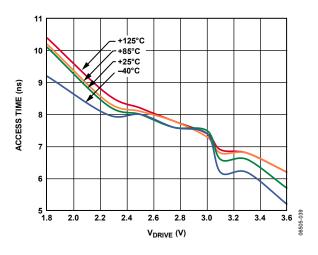

図 12.アクセス・タイム対 V<sub>DRIVE</sub>

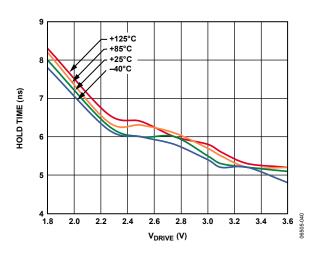

図 13.ホールド・タイム対 V<sub>DRIVE</sub>

Rev. 0 - 9/20 -

### 用語

#### 積分非直線性(INL)

ADC 伝達関数の両端を結ぶ直線からの最大偏差をいいます。伝達関数の両端とは、ゼロ・スケール(最初のコード遷移より1LSB下のポイント)とフル・スケール(最後のコード遷移より1LSB上のポイント)をいいます。

#### 微分非直線性(DNL)

ADCの2つの隣接コード間における1LSB変化の測定値と理論値の差をいいます。

#### 負のフル・スケール誤差

負のフルスケール誤差は、ミッドスケール誤差調整後の最初のコード変化((00...000)から(00...001))と理論値 $(-V_{REF}+0.5LSB)$ との差を意味します。

#### 負のフル・スケール誤差マッチ

負のフルスケール誤差マッチは、2つの ADC 間の負フルスケール誤差の差を意味します。

#### ミッドスケール誤差

ミッドスケール誤差は、ミッドスケール・コード変化((011 ... 111)から(100 ... 000))と理論値(0 V)との差を意味します。

#### ミッドスケール誤差マッチ

ミッドスケール誤差マッチは、2つの ADC 間のミッドスケール 誤差の差を意味します。

#### 正のフル・スケール誤差

正のフルスケール誤差は、ミッドスケール誤差調整後の最後のコード変化((111 ... 110)から(111 ... 111))と理論値( $V_{REF}-1.5$  LSB)との差を意味します。

#### 正のフル・スケール誤差マッチ

正のフルスケール誤差マッチは、2つの ADC 間の正フルスケール誤差の差を意味します。

#### ADC 間アイソレーション

ADC 間アイソレーションは、ADC A と ADC B の間でのクロストークのレベルの大きさを表します。フル・スケールの 1 MHz 正弦波信号を片方の ADC に入力し、他方の ADC に可変周波数のフル・スケール信号を入力して測定します。ADC 間アイソレーションは、変換中の ADC の 1 MHz 信号電力と、FFT に現れる他方の ADC のノイズ信号電力との比として定義されます。非選択チャンネル上のノイズ周波数は、100 kHz~2.5 MHz の範囲で変化します。

#### 電源変動除去比(PSRR)

電源変動除去比は、ADC 出力でのフル・スケール周波数 fの電力と、ADC の  $AV_{DD}$ 電源に加えられた周波数  $f_s$ の 100~mV 正弦波の電力との比として定義されます。入力周波数は  $5~kHz\sim25~mHz$ の範囲で変化します。

PSRR (dB) = 10 log (Pf/Pfs)

ここで、

$Pf_S$ は、ADC 出力での周波数  $f_S$ の電力。  $Pf_S$ は、ADC 出力での周波数  $f_S$ の電力。

#### 同相モード除去比(CMRR)

除去比は、ADC 出力でのフル・スケール周波数 fの電力と、 $V_{IN+}$ と  $V_{IN-}$ の同相モード電圧に加えられた周波数  $f_s$ の  $100~mV_{P-}$  p 正弦波の電力との比として定義されます。

CMRR (dB) =  $10 \log(Pf/Pf_S)$

-- 7

Pfは ADC 出力での周波数(f)の電力。  $Pf_S$ は、ADC 出力での周波数( $f_S$ )の電力。

#### トラック・アンド・ホールド・アクイジション時間

変換終了後、トラック・アンド・ホールド・アンプはトラック・モードに戻ります。トラック・アンド・ホールド・アクイジション時間は、変換終了後にトラック・アンド・ホールド・アンプが最終値の±0.5 LSB 以内に出力が収まるために要する時間です。

#### 信号対ノイズおよび歪み比(SINAD)

SINADは、A/Dコンバータ出力での信号対(ノイズ+歪み)比の測定値です。信号は基本波の rms 振幅で表します。ノイズは 1/2 サンプリング周波数(fs/2)までの全高調波の和で表します(DC を除く)。この比はデジタル化処理の量子化レベル数に依存し、レベル数が大きいほど、量子化ノイズは小さくなります。

正弦波を入力した場合の、理論 N ビット・コンバータに対する SINAD の理論値は次式で表されます。

SINAD = (6.02 N + 1.76) dB

したがって、12 ビット・コンバータの場合 SINAD は 74 dB に、14 ビット・コンバータの場合 SINAD は 86 dB に、それぞれなります。

#### 総合高調波歪み(THD)

THD は高調波の rms 値総和と基本波の比です。AD7356 の場合、次式で与えられます。

THD (dB) = -20 log

$$\frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

ここで、

V」は基本波の rms 振幅。

$V_2$ 、 $V_3$ 、 $V_4$ 、 $V_5$ 、 $V_6$ は、2次~6次の高調波の rms 振幅。

#### スプリアス・フリー・ダイナミック・レンジ(SFDR)

SFDR は、ADC 出力スペクトル内の(DC を除いて fs/2 まで)次に大きい成分の rms 値の、基本波 rms 値に対する比として定義されます。通常、この仕様の値はスペクトル内の最大の高調波により決定されますが、高調波がノイズ・フロアに埋めこまれている ADC の場合は、ノイズ・ピークにより決定されます。

#### 相互変調歪み(IMD)

非線形性を持つアクティブ・デバイスに 2つの周波数 fa および fb を含む正弦波を入力すると、さまざまな和および差の周波数  $mfa \pm nfb$  を持つ歪み成分が発生します。ここで、m、n=0、1、2、3、…です。相互変調歪みの項とは、m またはn がゼロでない項をいいます。相互変調歪項とは、m とn が非ゼロの項をいいます。たとえば、2 次項には(fa+fb)と(fa-fb)が含まれ、3 次項には(2fa+fb)、(2fa-fb)、(fa+2fb)、(fa-2fb)が含まれます。

AD7356は、入力帯域幅の上限に近い2つの入力周波数を使う CCIF標準を使ってテストされています。この場合、2次項は通 常、元の正弦波の周波数から離れて位置し、3次項は通常、入 力周波数に近い周波数に位置します。そのため、2次項と3次 項は別々に指定されます。相互変調歪みの計算はTHDの仕様に 従います。すなわち、dBで表した個々の歪み成分のrms 総和の、 基本波の和のrms 振幅に対する比になります。

#### サーマル・ヒステリシス

サーマル・ヒステリシスは、 $T_HYS+を+25^{\circ}C \to T_{MAX} \to +25^{\circ}C$  で、または  $T_HYS-e+25^{\circ}C \to T_{MIN} \to +25^{\circ}C$  で、温度サイクルを加えた後のリファレンス出力電圧の絶対最大変化として定義されます。

サーマル・ヒステリシスは、次式を使って ppm で表されます。

$$V_{HYS}$$

(ppm) =  $\left| \frac{V_{REF}(25^{\circ}C) - V_{REF}(T_{-}HYS)}{V_{REF}(25^{\circ}C)} \right| \times 10^{6}$

---

V<sub>REF</sub>(25°C)は、25°C での V<sub>REF</sub>。

$V_{REF}(T\ HYS)$ は、 $T\_HYS+$ または  $T\_HYS-$ での  $V_{REF}$ の最大変化。

Rev. 0 — 11/20 —

### 動作原理

#### 回路説明

AD7356 は、単電源で動作する高速な逐次比較型 12 ビット・デュアル A/D コンバータ(ADC)です。このデバイスは 2.5 V 電源で動作し、最大 5 MSPS のスループット・レートを持っています。

AD7356 は、2 個のトラック・アンド・ホールド差動アンプ、2 個の逐次比較型 ADC、シリアル・インターフェースを内蔵し、2 本の個別データ出力ピンを持っています。このデバイスは、16 ピンの TSSOP パッケージを採用し、他のソリューションに比べて優れた省スペースを提供します。

シリアル・クロック入力は、デバイスからのデータ読み出しに使用し、さらに逐次比較型 ADC のクロック・ソースとしても使われます。AD7356 は、2.048~V のリファレンス電圧を内蔵しています。外部リファレンス電圧が必要な場合には、内蔵リファレンス電圧を(2.048~V+100~mV) $\sim V_{DD}$  の範囲のリファレンス電圧で上書き駆動することができます。内部リファレンス電圧をシステム内の他の場所で使う場合には、出力をバッファする必要があります。AD7356 の差動アナログ入力範囲は  $V_{CM} \pm V_{REF}/2$ です。

AD7356 はパワーダウン・オプションを持っているため、変換の間で消費電力を節約することができます。パワーダウン機能は標準のシリアル・インターフェースを使って実現されています(動作モードのセクション参照)。

#### コンバータの動作

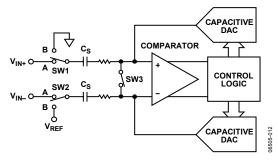

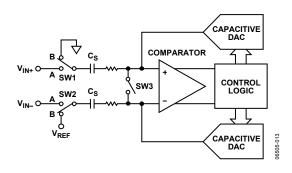

AD7264 は、容量 DAC を採用した 2 個の逐次比較型 ADC を内蔵しています。図 14 と図 15 に、片方の ADC についての簡略化した回路図(アクイジション・フェーズと変換フェーズ)を示します。ADC は、コントロール・ロジック、SAR、2 個の容量 DAC から構成されています。図 14(アクイジション・フェーズ)では、SW3 は閉じて、SW1 と SW2 は位置 A にあり、コンパレータは平衡状態にあり、サンプリング・コンデンサ・アレイは入力の差動信号を取得します。

図 14.ADC アクイジション・フェーズ

ADC が変換を開始すると(図 15)、SW3 が開いて、SW1 と SW2 が位置 B に移動して、コンパレータが不平衡状態になります。変換が開始されると、両入力は切り離されます。コントロール・ロジックと電荷再配分型 DAC を使って、サンプリング・コンデンサ・アレイに対して一定量の電荷を加算および減算して、コンパレータを平衡状態に戻すようにします。コンパレータが平衡状態に戻ると、変換が完了します。コントロール・ロジックは ADC の出力コードを発生します。 $V_{\text{IN-}}$ ピンを駆動する信号源の出力インピーダンスを一致させる必要があります。そうしないと、両入力ピンのセットリング時間が異なり誤差が発生します。

図 15.ADC 変換フェーズ

#### アナログ入力構造

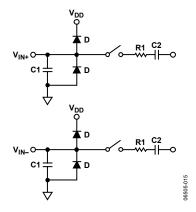

図 16 に、AD7356 のアナログ入力構造の等価回路を示します。 4 個のダイオードがアナログ入力に対して ESD 保護機能を提供します。アナログ入力信号は電源レールより 300mV 以上高くならないよう注意する必要があります。超えると、これらのダイオードが順方向にバイアスされて、サブストレートに電流が流れるようになります。これらのダイオードが損傷なしに許容できる最大電流は 10 mA です。

図 16 に示すコンデンサ C1 は約 8 pF(typ)で、主にピン容量に起因します。R1 抵抗はスイッチのオン抵抗で構成される集中定数部品です。これらの抵抗は約 30  $\Omega$ (typ)です。コンデンサ C2 はADC のサンプリング・コンデンサであり、容量は 32 pF (typ)です。

図 16.等価アナログ入力回路、変換フェーズ・スイッチはオープン、 トラック・フェーズ・スイッチはクローズ

AC アプリケーションの場合は、アナログ入力ピンに RC ローパス・フィルタを使用して、アナログ入力信号から高周波成分を除去することが推奨されます。高調波歪みと信号対ノイズ比が重要であるアプリケーションでは、アナログ入力を低インピー

ダンス・ソースで入力する必要があります。ソース・インピー ダンスが大きいと、ADC の AC 性能に大きな影響を与えるため、 入力バッファ・アンプの使用が必要になります。オペ・アンプ の選択は、アプリケーションに依存します。

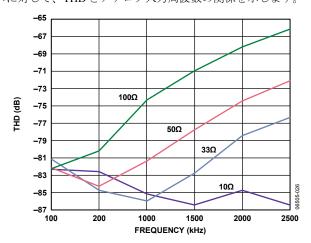

アンプを使わないでアナログ入力を駆動するときは、ソース・インピーダンスを小さい値に制限する必要があります。最大ソース・インピーダンスは、許容可能な THD の大きさに依存します。ソース・インピーダンスが増加すると THD が大きくなるため、性能が低下します。図 17 に、種々のソース・インピーダンスに対して、THD とアナログ入力周波数の関係を示します。

図 17.種々のソース・インピーダンスに対する THD 対アナログ入力 信号周波数

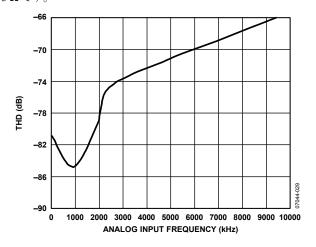

図 18 に、5 MSPS でサンプリング時の、THD とアナログ入力周 波数の関係を示します。この場合、ソース・インピーダンスは 33  $\Omega$  です。

図 18.THD 対アナログ入力周波数

#### アナログ入力

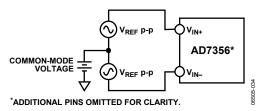

差動信号はシングルエンド信号に比べて、デバイスのコモン・モード除去比に基づくノイズ耐性、歪性能の改善などの幾つかの利点を持っています。図 19 に、AD7356 のフル差動アナログ入力を定義します。

図 19.差動入力の定義

差動信号の振幅は、各差動対の  $V_{\rm IN+}$ ピンと  $V_{\rm IN-}$ ピンに加えられた信号の差( $V_{\rm IN+}$  -  $V_{\rm IN-}$ )です。 $V_{\rm IN+}$ と  $V_{\rm IN-}$ は、それぞれ振幅が VREF で位相差が 180°である 2 つの信号で同時に駆動されます。このため、差動信号のこの振幅は、同相モード(CM)に関係なく  $-V_{\rm REF}$   $\sim$   $+V_{\rm REF}$  の p-p 値になります。

CM は 2 つの信号の平均値であるため、2 つの入力の中心となる電圧です。

$$CM = (V_{IN+} + V_{IN-})/2$$

このため各入力スパンは  $CM \pm V_{REF}/2$  となります。この電圧は外部で設定する必要があります。CM を設定するときは、 $V_{IN+}$ と  $V_{IN-}$ は  $GND/V_{DD}$  内に留まるようにする必要があります。変換が行われると、CM が除去されて、デジタル・コード  $0\sim4095$  に対応する振幅 $-V_{REF}\sim+V_{REF}$  の実質的にノイズのない信号が得られます。

#### 差動入力の駆動

差動動作では、 $V_{\text{IN+}}$ と  $V_{\text{IN-}}$ を 180°位相がずれている 2 つの等しい信号で駆動する必要があります。すべてのアプリケーションが差動動作用に信号を予めコンデショニングしていないため、シングルエンドから差動への変換が必要になることがあります。

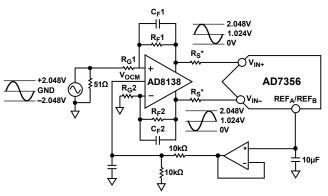

#### 差動アンプ

AD7356 を差動駆動する最適な方法は、AD8138 のような差動アンプを使う方法です。このデバイスは、シングルエンド/差動変換アンプまたは差動-差動アンプとして使うことができます。また、AD8138 は同相モード・レベルのシフト機能も提供します。図 20 に、AD8138 をシングルエンド/差動変換アンプとして使用する方法を示します。AD8138 の正側出力と負側出力は、スイチされる容量の ADC フロントエンドに対する影響を小さくするための 1 対の直列抵抗を介してそれぞれの ADC 入力に接続されます。AD8138 のアーキテクチャにより、厳密に一致する外付け部品が不要で広い周波数範囲で平衡を維持する出力が得られます。

\*MOUNT AS CLOSE TO THE AD7356 AS POSSIBLE AND ENSURE THAT HIGH PRECISION  $R_S$  RESISTORS ARE USED.  $R_S-33\Omega$ ;  $R_G1=R_F1=R_F2=499\Omega$ ;  $C_F1=C_F2=39pF$ ;  $R_G2=523\Omega$

図 20.シングルエンド/差動変換アンプとして AD8138 を使用

使用するアナログ入力ソースがゼロ・インピーダンスを持つ場合、4個のすべての抵抗( $R_G1$ 、 $R_G2$ 、 $R_F1$ 、 $R_F2$ )は同じである必要があります。たとえば、ソースが 50  $\Omega$  のインピーダンスと 50  $\Omega$  の終端を持つ場合、入力での並列インピーダンスをバランスさせて、正側アナログ入力と負側アナログ入力が同じゲインを持つようにするために、 $R_G2$ 値を 25  $\Omega$  だけ大きくする必要があります。アンプ出力は完全に一致して、同じ振幅と正確に位相が 180°ずれたバランスした差動出力が得られます。

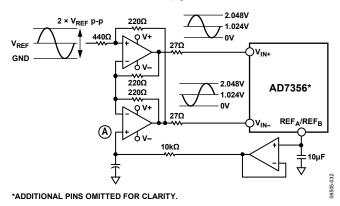

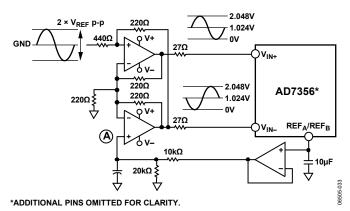

#### オペアンプ対

オペアンプ対を使って、差動信号を AD7356 のアナログ入力対の1つに直接接続することができます。図 21 と図 22 に示す回路構成は、それぞれバイポーラ入力信号とユニポーラ入力信号について、オペアンプを使って、シングルエンド信号を差動信号に変換する方法を示しています。

ポイントAに入力される電圧が同相モード電圧を設定します。 両図では、これはリファレンスに接続されています。AD7356 を差動駆動するこの構成で使用できる最適なデュアル・オペア ンプとしてはAD8022があります。

図 21.シングルエンド・ユニポーラ信号を差動信号へ変換するデュ アル・オペアンプ回路

図 22.シングルエンド・バイポーラ信号を差動ユニポーラ信号に変

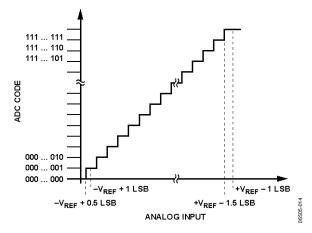

## ADC の伝達関数

AD7356 の出力コーディングはストレート・バイナリ数です。 コード変化は LSB の連続する整数倍値(1 LSB、2 LSB など)で発生します。LSB サイズは(2 ×  $V_{REF}$ )/4096 です。AD7356 の理論伝達特性を223に示します。

換するデュアル・オペアンプ回路

図 23.AD7356 の理論伝達特性

Rev. 0

### 動作モード

AD7356 の動作モードは、変換時に $\overline{\text{CS}}$ 信号のロジック状態を制御することにより選択されます。ノーマル・モード、パーシャル・パワーダウン・モード、フル・パワーダウン・モードの3つの動作モードがあります。変換開始後の $\overline{\text{CS}}$ がハイ・レベルになるポイントで、デバイスのパワーダウン・モードが決定されます。同様に、すでにパワーダウン・モードにある場合、デバイスがノーマル動作に戻るか、パワーダウン・モードに留まるかが $\overline{\text{CS}}$ によって制御されます。

これらの動作モードは、柔軟なパワー・マネジメント・オプションを提供するためにデザインされています。これらのオプションを選択して、さまざまなアプリケーションの要求に対して消費電力/スループット・レート比を最適化することができます。

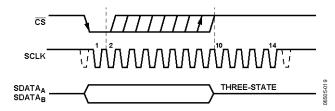

#### ノーマル動作モード

このモードでは、AD7356 が常時フル・パワーオン状態にあるためパワーアップ時間を気にする必要がないので、最高スループット・レート性能を得ることができます。図24に、このモードでのAD7356動作の一般的な動作図を示します。

図 24.ノーマル・モード動作

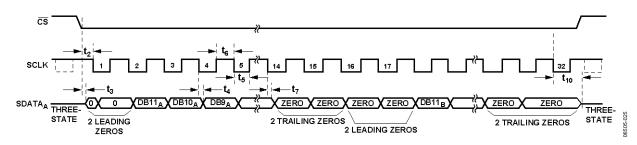

変換はシリアル・インターフェースのセクションで説明するよ うにCSの立ち下がりエッジで開始されます。デバイスを常時パ ワーアップさせておくために、CSの立ち下がりエッジの後 SCLK の少なくとも 10 個の立ち下がりエッジが経過するまで、 CSをロー・レベルに維持しておく必要があります。10 番目の SCLK の立ち下がりエッジの後で、かつ 14番目の SCLK の立ち 下がりエッジの前の任意のタイミングでCSをハイ・レベルにす ると、デバイスはパワーアップ状態を維持しますが、変換は終 了して、SDATA<sub>A</sub>と SDATA<sub>B</sub> はスリー・ステートに戻ります。 変換を完了して AD7356 の変換結果をアクセスするためには、 シリアル・クロックで 14 サイクルが必要です。SDATA ライン は SCLK で 14 サイクル経過してもスリー・ステートに戻りませ んが、 $\overline{\text{CS}}$ がハイ・レベルに戻ると、スリー・ステートに戻りま す。SCLK の 16 サイクル間、 $\overline{CS}$ がロー・レベルにされると、デ ータの後ろに 2 ビットのゼロが出力されます。 さらに SCLK で 14 サイクル間 $\overline{\text{CS}}$ がロー・レベルに維持されると、他の内蔵 ADC の結果も同じ SDATA ラインからアクセスすることができ ます(図 31 とシリアル・インターフェースのセクションを参照 してください)。

SCLK で 32 サイクルが経過すると、SCLK の 32 番目の立ち下が りエッジで SDATA ラインはスリー・ステートに戻ります。こ の前に、 $\overline{CS}$ をハイ・レベルにすると、SDATA ラインはその時 点でスリー・ステートに戻ります。したがって、SCLK の 32 サイクル後に $\overline{CS}$ はロー・レベルになり、次の変換の前にハイ・レベルに戻すまでこの状態が続きます。これでも、バスはデュアル・リザルト読み出しが完了したとき、スリー・ステートに戻ります。

データ転送が完了して、 $SDATA_A$  と  $SDATA_B$  がスリー・ステートに戻った後、静止時間  $t_{QUIET}$  が経過した後(アクイジッション時間を確保して)に、 $\overline{CS}$ を再度ロー・レベルにして、次の変換を開始することができます。

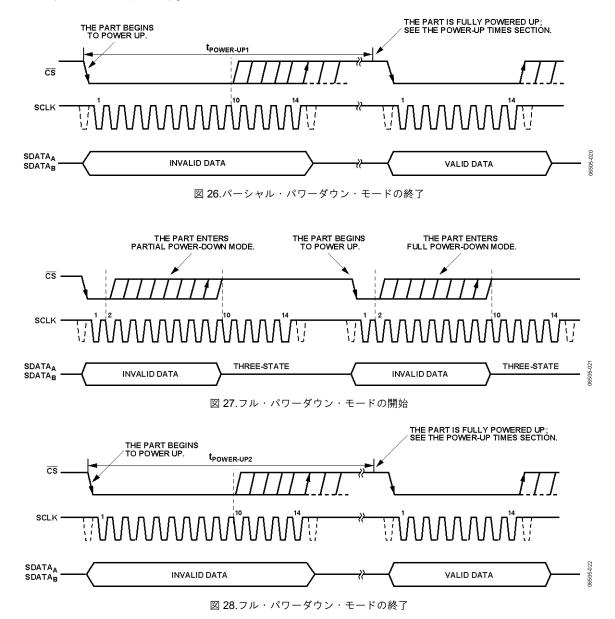

#### パーシャル・パワーダウン・モード

このモードは、低いスループット・レートが必要とされるアプリケーションでの使用を目的にしています。いずれかの ADC が各変換の間にパワーダウンされるか、または一連の変換を高いスループット・レートで実行した後に、これら複数の変換バーストの間に ADC がパワーダウンされます。AD7356 を 100 μs以上パーシャル・パワーダウン・モードにしないことが推奨されます。AD7356 がパーシャル・パワーダウンになると、内蔵リファレンスとリファレンス・バッファ以外の全アナログ回路がパワーダウンされます。

パワーダウン・モードにするときは、SCLK の 2 番目の立ち下がりエッジの後で、かつ SCLK の 10 番目の立ち下がりエッジの前にCSをハイ・レベルにすることにより、変換プロセスを中断させる必要があります(図 25)。SCLK のこのウインドウ内で、CSをハイ・レベルにすると、デバイスはパワーダウン状態に入りますが、CSの立ち下がりエッジで開始された変換は終了して、SDATAAと SDATABはスリー・ステートに戻ります。SCLK の 2 番目の立ち下がりエッジの前にCSをハイ・レベルにすると、デバイスはノーマル・モードに留まり、パワーダウンしません。この機能により、CSライン上のグリッチに起因して偶発的にパワーダウンしてしまうことを防止します。

図 25.パーシャル・パワーダウン・モードの開始

この動作モードを終了して、AD7356 を再度パワーアップする ときは、ダミー変換が実行されます。CSの立ち下がりエッジで デバイスはパワーアップを開始し、 $\overline{\text{CS}}$ がロー・レベルに維持さ れている間パワーアップを続けて、SCLKの10番目の立ち下が りエッジに終了します。デバイスは 200 ns 経過後(1回の変換後) にフルにパワーアップし、有効なデータが次の変換から得られ ます(図 26 参照)。SCLK の 2 番目の立ち下がりエッジの前にCS をハイ・レベルにすると、AD7356 は再びパーシャル・パワー ダウン・モードに戻ります。この機能により、CSライン上のグ リッチに起因して偶発的にパワーダウンしてしまうことを防止 します。デバイスはCSの立ち下がりエッジでパワーアップでき ますが、CSの立ち上がりエッジで再びパワーダウンします。 AD7356 がすでにパーシャル・パワーダウン・モードにあり、か つ SCLK の 2番目と 10番目の立ち下がりエッジの間にCSをハ イ・レベルにした場合、デバイスはフル・パワーダウン・モー ドになります。

#### フル・パワーダウン・モード

このモードは、フル・パワーダウンからのパワーアップにはパ ーシャル・パワーダウンからのパワーアップよりさらに長い時 間が必要なため、パーシャル・パワーダウン・モードより低い スループット・レートが要求されるアプリケーションでの使用 を目的としています。このモードは、比較的高スループット・ レートで実行される一連の変換の後ろに長い無動作時間(すなわ ちパワーダウン)が続くアプリケーションに適しています。 AD7356 がフル・パワーダウン・モードになると、内蔵リファ レンスとリファレンス・バッファを含む全アナログ回路がパワ ーダウンされます。パーシャル・パワーダウンと同じ方法でフ ル・パワーダウンに入りますが、図 25 に示すタイミング・シー ケンスを 2 回実行する点が異なります。SCLK の 2 番目の立ち 下がりエッジの後の、SCLK の 10 番目の立ち下がりエッジの前 にCSをハイ・レベルにすることにより、同様の方法で変換プロ セスを中断させる必要があります。デバイスはこの時点でパー シャル・パワーダウン・モードに入ります。

フル・パワーダウンに到達するためには、次の変換サイクル<u>を</u>図 27 に示す方法と同じ方法で中断させる必要があります。CS を SCLK のこのウインドウ内でハイ・レベルにすると、デバイスはフル・パワーダウンします。

**CS**をハイ・レベルにしてパワーダウン・モードに入った後は、 SCLK で 14 または 16 サイクルを完了させる必要がないことに 注意してください。

フル・パワーダウン・モードを終了して AD7356 をパワーアップさせるときは、パーシャル・パワーダウンからのパワーアップと同様にダミー変換を実行してください。CSの立ち下がりエッジでデバイスはパワーアップを開始し、CSがロー・レベルに維持されている間パワーアップを続けて、SCLK の 10番目の立ち下がりエッジに終了します。必要とされるパワーアップ時間が経過した後に、変換を開始することができます(図 28)。

Rev. 0 — 16/20 —

#### パワーアップ時間

AD7356 には、パーシャル・パワーダウンとフル・パワーダウンの2つのパワーダウン・モードがあります。これらについては、ノーマル動作モード、パーシャル・パワーダウン・モード、フル・パワーダウン・モードの各セクションで説明します。このセクションでは、いずれかのモードから抜け出す際のパワーアップ時間について説明します。パワーアップ時間を適用するためには、推奨デカップリング・コンデンサを  $REF_A$ ピンと  $REF_B$ ピンに接続する必要がることに注意してください。

パーシャル・パワーダウン・モードからパワーアップするときは、1 ダミー・サイクルが必要です。デバイスは、 $\overline{CS}$ の立ち下がりエッジから約 200 ns 後にフル・パワーアップします。パーシャル・パワーアップ時間が経過すると、 $\overline{ADC}$  がフル・パワーアップして、入力信号を正常に取り込みます。この場合でも、ダミー変換後にバスがスリー・ステートに戻った時点から、 $\overline{CS}$  の次の立ち下がりエッジまでの休止時間  $\overline{LO}$  to 大のます。

$\frac{\mathcal{D}}{CS}$ の立ち下がりエッジから  $t_{POWER\ UP}$  (図 28 参照)として約 6 ms を確保する必要があります。

パーシャル・パワーダウンからパワーアップする際、CSの立ち下がりエッジの後にデバイスが受け取る最初の SCLK エッジの後で、デバイスのパワーダウン中にホールド・モードにあったトラック・アンド・ホールドがトラック・モードに戻ることに、注意する必要があります。

電源が最初に AD7356 に加えられるとき、ADC はパワーダウン・モードまたはノーマル・モードからパワーアップすることができます。このため、デバイスが完全にパワーアップした後に有効な変換を開始させるようにするため、1 ダミー・サイクルを経過させることが最適です。同様に、電源を加えた直後にデバイスをパーシャル・パワーダウン・モードにする場合にも、2 ダミー・サイクルを経過させる必要があります。最初のダミー・サイクルでは 10 番目の SCLK 立ち下がりエッジが経過するまで $\overline{\text{CS}}$ をロー・レベルに維持する必要があります。2 番目のサイクルでは、2 番目の SCLK 立ち下がりエッジと 10 番目の SCLK エッジの間に $\overline{\text{CS}}$ をハイ・レベルにする必要があります(図 25 参照)。

あるいは、電源を加えたときにデバイスをフル・パワーダウン・モードにする場合にも、3 ダミー・サイクルの経過が必要です。最初のダミー・サイクルでは 10 番目の SCLK 立ち下がりエッジが経過するまでCSをロー・レベルに維持する必要があります。2 番目と 3 番目のダミー・サイクルで、デバイスがフル・パワーダウン・モードになります(図 27 と動作モードのセクション参照)。

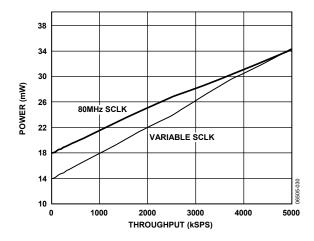

#### 消費電力とスループット・レートとの関係

AD7356 の消費電力はスループット・レートにより変わります。非常に低速なスループット・レートで、かつできるだけ高速な SCLK 周波数を使う場合には、種々のパワーダウン・オプションを使って大幅な消費電力の削減を行うことができますが、パワーダウン・オプションを使わなくとも AD7356 の静止電流が十分小さいため、サンプリング・レートによる消費電力の大きな変化はありません。これは、固定 SCLK 値を使うか、またはサンプリング・レートでスケールするかによらず言えることです。図 29 に、固定の最大 SCLK 周波数およびサンプリング・レートでスケールした SCLK 周波数およびサンプリング・レートでスケールした SCLK 周波数によるノーマル・モード動作時の、電力対スループット・レートのプロットを示します。図 29 では内蔵リファレンス電圧を使用しています。

図 29.消費電力とスループット・レートとの関係

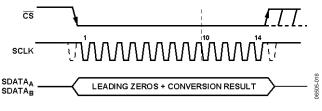

### シリアル・インターフェース

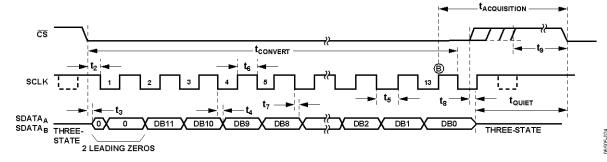

図 30 に、AD7356 に対するシリアル・インターフェースの詳細なタイミング図を示します。シリアル・クロックは変換クロックとして使用され、変換時に AD7356 に入出力される情報の転送制御にも使用されます。

CS信号が、データ転送と変換プロセスを開始させます。 CSの立ち下がりエッジでトラック・アンド・ホールドがホールド・モードになり、この時点でアナログ入力がサンプルされ、バスがスリー・ステートから抜け出します。変換もこの時点で開始され、完了までに最小 14 SCLK サイクルが必要です。 SCLK の13 個の立ち下がりエッジが経過すると、トラック・アンド・ホールドが次の SCLK 立ち上がりエッジでトラック状態に戻ります(図 30 のポイント B)。 AD7356 上で、16 ビットのデータ転送を使用する場合には、最後の LSB の後ろに 2 ビットのゼロが出力されます。

$\overline{\text{CS}}$ の立ち上がりエッジで、変換が終了して  $\overline{\text{SDATA}}_A$  と  $\overline{\text{SDATA}}_B$  はスリー・ステートに戻ります。 $\overline{\text{CS}}$ をハイ・レベルにしないで、さらに  $\overline{\text{SCLK}}$  の 14 サイクル間ロー・レベルを維持させると、 $\overline{\text{ADC B}}$  からの変換データは、 $\overline{\text{SDATA}}_A$  に出力されます(図 31 参照)。同様に、 $\overline{\text{ADC A}}$  からの変換データは、 $\overline{\text{SDATA}}_B$ に出力され

ます。この場合、使用している SDATA ラインが、32 番目の SCLK の立ち下がりエッジまたはCSの立ち上がりエッジのいず れか早い方でスリー・ステートに戻ります。変換プロセスを実 行して AD7356 のいずれかのデータ・ライン上に 1 変換データ を取り出すためには、シリアル・クロックで14サイクル必要で す。CS がロー・レベルになると、マイクロコントローラまたは DSP によって前縁のゼロが読み出されます。次に 2 番目の前縁 ゼロの後に、残りのデータが後続の SCLK 立ち下がりエッジで 出力されます。このようにして、シリアル・クロックの最初の 立ち下がりクロック・エッジで前縁のゼロ・ビットが出力され た後、2番目のゼロ・ビットも出力されます。12ビットの変換 結果、その後ろにデータ転送の最終ビットが続き、14番目の立 ち下がりエッジで有効になります(前の 13 番目の立ち下がりエ ッジは出力済み)。低速 SCLK を使うアプリケーションでは、 SCLK 周波数に応じて SCLK の各立ち上がりエッジでデータを 読み込むことができます。低速 SCLK では、CSの立ち下がりエ ッジの後の、最初の SCLK 立ち上がりエッジで前縁ゼロ・ビッ トが出力され、SCLKの13番目の立ち上がりエッジでDB0が出 力されます。

図 30. シリアル・インターフェースのタイミング図

図 31.1本の SDATA ラインへの両 ADC からのデータ読み出し、32 SCLK サイクル使用

Rev. 0 — 18/20 —

## アプリケーション情報

#### グラウンド接続とレイアウト

AD7356 のアナログ電源とデジタル電源は独立しており、別々のピンを使用することにより、デバイスのアナログ部とデジタル部の間の結合を最小にしています。AD7356 を実装するプリント回路ボード(PCB)は、アナログ部とデジタル部を分離して、ボード内でそれぞれをまとめて配置するようにデザインする必要があります。そうすると、グラウンド・プレーンの使用が可能になり、それらを容易に分離できるようになります。

最適なシールド効果を実現するために、一般にエッチング部分を最小することが最適です。AD7356 の 2 本の AGND ピンをAGND プレーンに接続する必要があります。REFGND ピンもAGND プレーンに接続する必要があります。デジタル・グラウンド・プレーンとアナログ・グラウンド・プレーンは 1 点で接続する必要があります。複数のデバイスが AGND と DGND の接続を必要とするシステム内で AD7356 を使用する場合にも、この接続は 1 ヵ所で行う必要があります。すなわち、AD7356 のできるだけ近くで星型グラウンド接続点を構成します。

ノイズがチップに混入するので、デバイスの真下をデジタル・ラインが通らないようにしてください。ノイズ混入を防止するため、アナログ・グラウンド・プレーンが AD7356 の下を通過することは可能です。AD7356 の電源ラインはできるだけ太いパターンにしてインピーダンスを下げ、電源ライン上のグリッチによる影響を軽減させます。

クロックなどの高速なスイッチング信号は、デジタル・グラウンドでシールドしてボードの他の部分に対するノイズの放射を防止します。また、クロック信号はアナログ入力の近くを通過しないようにします。デジタル信号とアナログ信号の交差は回避する必要があります。ボードの反対側のパターンは、互いに右角度となるように配置してボードを通過するフィードスルー

効果を減少させます。マイクロストリップ技術の使用は最善ですが、両面ボードでは常に使用できるとは限りません。この技術では、ボードの部品面はグラウンド・プレーン専用にして、信号はハンダ面に配線します。

すべての電源を、 $10\mu F$  のタンタル・コンデンサと 0.1 nF のコンデンサの並列接続を使って GND ヘデカップリングします。デカップリング部品の効果を最大にするためには、これらの部品をデバイスのできるだけ近くに、理想的にはデバイスの隣に配置します。 $0.1\mu F$  コンデンサは、一般的なセラミック型コンデンサや表面実装型のような実効直列抵抗(ESR)が小さく、かつ実効直列インダクタンス(ESI)が小さいものを使う必要があります。これらの低 ESR および低 ESI のコンデンサは、ロジックのスイッチングにより発生する過渡電流に起因する高周波に対してグラウンドへの低インピーダンス・パスを提供します。

#### AD7356 の性能評価

AD7356 の推奨レイアウトの概要は評価ボードのドキュメントに記載してあります。評価ボードの梱包には、アセンブル/テスト済みの評価ボード、ドキュメント、コンバータ評価/開発ボード(CED)を介して PC からボードを制御するソフトウェアが添付されています。CED は、AD7356 評価ボード(さらにアナログ・デバイセズのその他の多くの評価ボードで終わりに CB 識別マークが付くもの)と組み合わせて使用して、AD7356 の AC 性能と DC 性能のデモ/評価を行うことができます。

ソフトウェアを使うと、ユーザーは AD7356 の AC テスト(高速 フーリェ変換)と DC テスト(直線性)を行うことができます。ソ フトウェアとドキュメントは、評価ボードに添付されている CD-ROM で提供しています。

Rev. 0 — 19/20 —

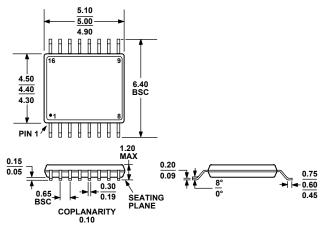

## 外形寸法

COMPLIANT TO JEDEC STANDARDS MO-153-AB

図 32.16 ピン薄型シュリンク・スモール・アウトライン・パッケージ[TSSOP] (RU-16) 寸法: mm

### オーダー・ガイド

| Model                          | Temperature Range | Package Description                        | Package Option |

|--------------------------------|-------------------|--------------------------------------------|----------------|

| AD7356BRUZ <sup>1</sup>        | −40°C to +85°C    | 16-Lead TSSOP                              | RU-16          |

| AD7356BRUZ-500RL7 <sup>1</sup> | −40°C to +85°C    | 16-Lead TSSOP                              | RU-16          |

| AD7356BRUZ-RL <sup>1</sup>     | −40°C to +85°C    | 16-Lead TSSOP                              | RU-16          |

| AD7356YRUZ <sup>1</sup>        | −40°C to +125°C   | 16-Lead TSSOP                              | RU-16          |

| AD7356YRUZ-500RL7 <sup>1</sup> | −40°C to +125°C   | 16-Lead TSSOP                              | RU-16          |

| AD7356YRUZ-RL <sup>1</sup>     | −40°C to +125°C   | 16-Lead TSSOP                              | RU-16          |

| EVAL-AD7356EDZ <sup>1, 2</sup> |                   | Evaluation Board                           |                |

| EVAL-CED1Z <sup>1, 3</sup>     |                   | Converter Evaluation and Development Board |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品

$<sup>^2</sup>$  これは単独の評価ボードとして、または EVAL-CED1Z ボードと組み合わせて、評価/デモ目的で使用することができます。

$<sup>^3</sup>$  この評価ボードを使うと、ED サフィックスが付くすべてのアナログ・デバイセズ評価ボードを PC から制御して通信することができます。