### マルチチャンネルADC、DAC、温度センサー 電流検出器を内蔵する 12ビット監視/制御システム

**AD7294**

### 特長

変換時間 3 µs の 12 ビット SAR ADC を内蔵

汎用のアナログ入力×4

差動/シングルエンド

入力範囲: V<sub>REF</sub> および 2 x V<sub>REF</sub>

ハイサイド電流検出入力×2

動作範囲: 5 V~59.4 V

ゲイン誤差: 最大 0.5%

入力範囲: ±200 mV

外付けダイオード温度センサー入力×2

計測範囲: -55°C~+150°C

精度: ±2°C

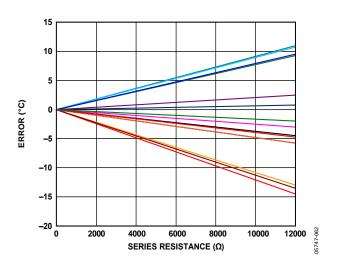

直列抵抗の相殺

内部温度センサー×1

精度: ±2℃

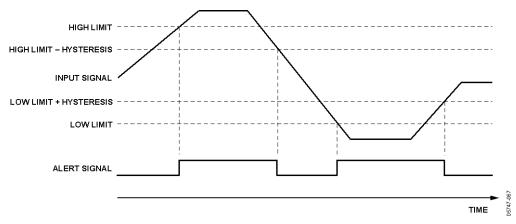

内蔵の監視機能

各チャンネルの最小/最大レコーダ

警報スレッショールドが設定可能

ヒステリシスが設定可能

単調性の優れた 12 ビット 15 V DAC×4

5 V 振幅、0 V~10 V のオフセット

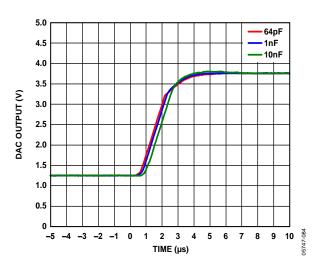

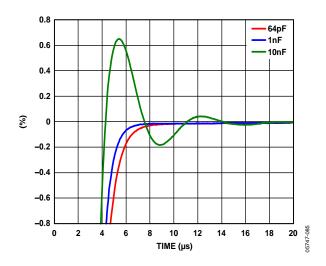

セトリング・タイム: 8 μs

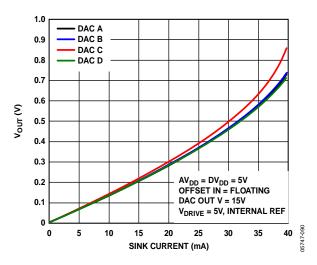

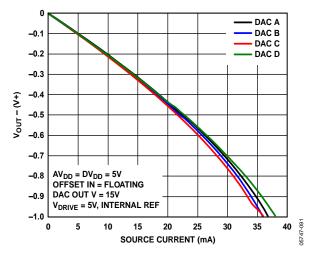

シンク能力とソース能力: 10 mA

パワーオン・リセット (POR) 時に 0 V 出力

内部リファレンス電圧: 2.5 V

2線式高速モード I2C インターフェース

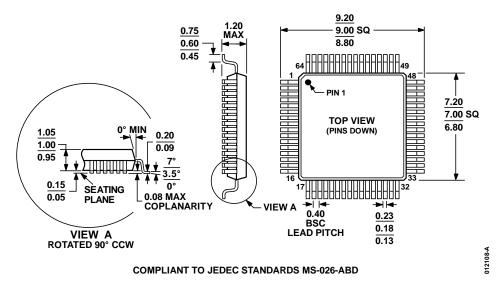

温度範囲: -40°C~+105°C 64 ピン TQFP パッケージを採用

### アプリケーション

携帯電話基地局

GSM、EDGE、UMTS、CDMA、TD-SCDMA、W-CDMA、 WiMAX

1 対多およびその他の RF 送信システム 12 V、24 V、48 V の車載アプリケーション

工業用制御

### 概要

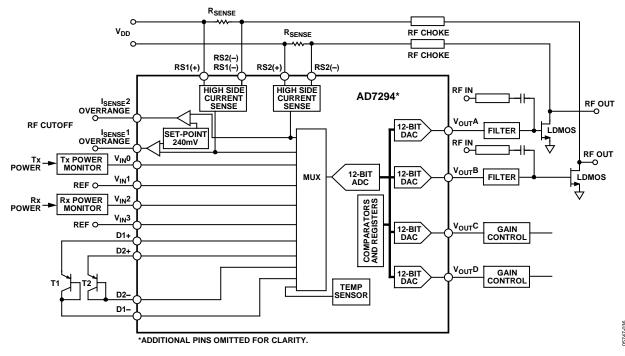

AD7294 は、汎用の監視機能および電流、電圧、温度特性の制 御に必要なすべての機能をシングル・チップ・ソリューション として内蔵しています。このデバイスには、シャント抵抗の電 流を監視する低電圧 (±200 mV) アナログ入力検出アンプ、温度 検出入力、変換時間 3 μs の SAR A/D コンバータ (ADC) ヘマルチ プレクス入力する 4 チャンネルの汎用アナログ入力が内蔵されて います。D/A コンバータ (DAC) と ADC に供給される高精度なリ ファレンス電圧も内蔵しています。4個の12ビット DACは、電 圧制御用の出力を提供します。AD7294 には、アラーム機能用の リミット・レジスタも内蔵されています。このデバイスは、電 流検出入力および最大 15 V の DAC 出力電圧で 59.4 V の高電圧 耐性を実現するためにアナログ・デバイセズの高電圧 DMOS 製 造プロセスを採用してデザインされています。

AD7294 は、携帯電話基地局アプリケーションでパワー・アンプ の精密制御に必要なすべての機能を提供する集積度の高いソリ ューションです。これらのタイプのアプリケーションで、この DAC はパワー・トランジスタのバイアス電流を制御するために 12 ビットの分解能を提供します。サーマル・ダイオード採用の 温度センサーは、温度の影響を補償するために内蔵されています。 この ADC は、ハイサイド電流と温度特性を監視します。これら すべての機能を 1 個の 64 ピン TQFP パッケージで提供し、 -40°C~+105°C の温度範囲で動作します。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に ファロファ アハド にへてはた、近次ドップ 同報が上端に自想ところ ものしての るここ とが じといるすが、くの情報が一角で 関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、 アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様 予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。 本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。 ※日本語デ ©2008 Analog Devices, Inc. All rights reserved.

## 目次

| 特長                    | 1  |

|-----------------------|----|

| アプリケーション              | 1  |

| 概要                    | 1  |

| 改訂履歴                  | 2  |

| 機能ブロック図               | 3  |

| 仕様                    | 4  |

| DAC 仕様                | 4  |

| ADC 仕様                | 5  |

| 全体仕様                  | 7  |

| タイミング特性               | 8  |

| 絶対最大定格                | 9  |

| 熱抵抗                   | 9  |

| ESD の注意               | 9  |

| ピン配置およびピン機能説明         | 10 |

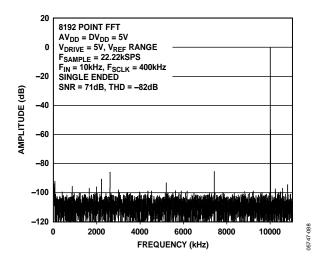

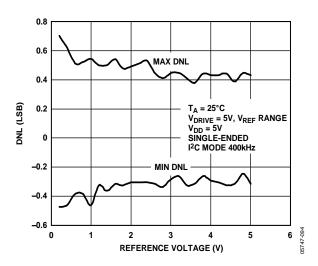

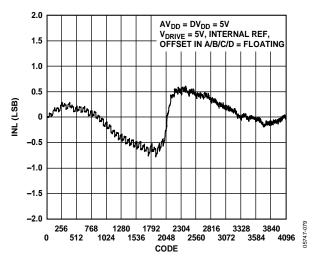

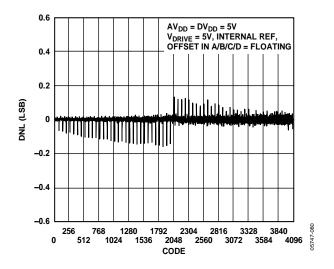

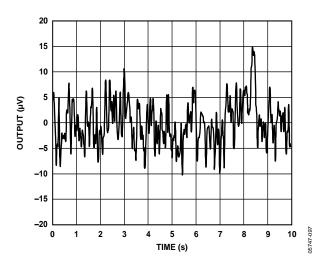

| 代表的な性能特性              | 12 |

| 用語                    | 17 |

| DAC 用語                | 17 |

| ADC 用語                | 17 |

| 動作原理                  | 18 |

| ADC の概要               | 18 |

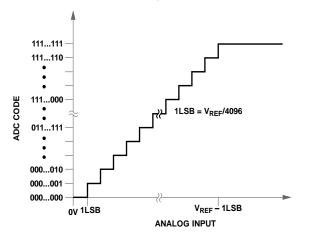

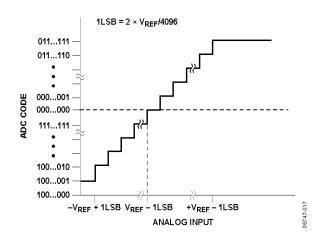

| ADC の伝達関数             | 18 |

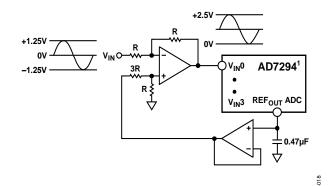

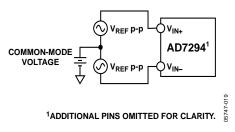

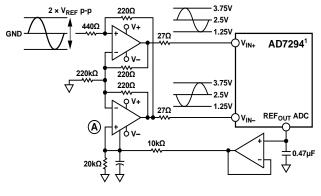

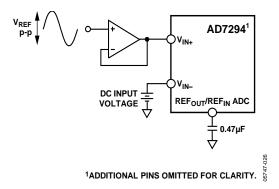

| アナログ入力                | 18 |

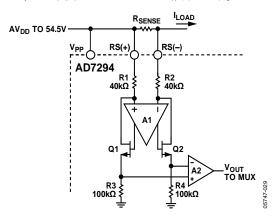

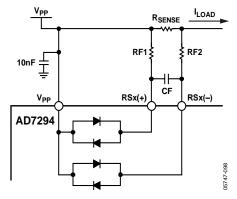

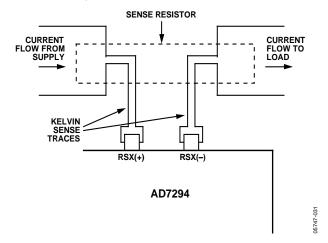

| 電流センサー                | 20 |

| アナログ・コンパレータ・ループ       | 21 |

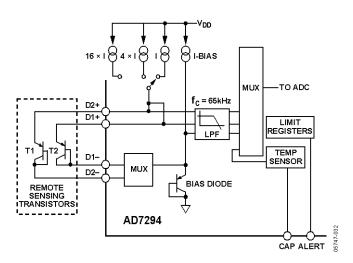

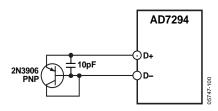

| 温度センサー                | 21 |

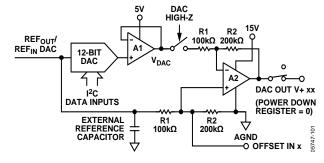

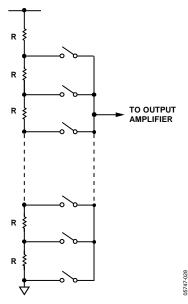

| <b>DAC</b> の動作        | 22 |

| ADC と DAC のリファレンス電圧   | 24 |

| V <sub>DRIVE</sub> 機能 | 24 |

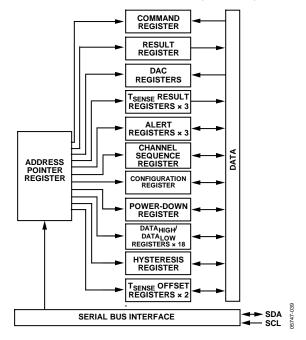

| レジスタの設定               | 25 |

| アドレス・ポインタ・レジスタ        | 25 |

| コマンド・レジスタ (0x00)      | 26 |

| リザルト・レジスタ (0x01)      | 26 |

| $1_{SENSE}1$ リザルト・レンスタと $1_{SENSE}2$ リザルト・レン、 $(0x02 \ge 0x03)$                                                                                                    |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| T <sub>SENSE</sub> INT リザルト・レジスタ (0x04)                                                                                                                            | 27    |

| DAC <sub>A</sub> 、DAC <sub>B</sub> 、DAC <sub>C</sub> 、DAC <sub>D</sub> の各レジスタ (0x01~0x0                                                                            | 04)28 |

| 警報ステータス・レジスタ A (0x05)、警報ステータス                                                                                                                                      | ・レジ   |

| スタ B (0x06)、警報ステータス・レジスタ C (0x07)                                                                                                                                  | 28    |

| チャンネル・シーケンス・レジスタ (0x08)                                                                                                                                            | 28    |

| 設定レジスタ (0x09)                                                                                                                                                      | 29    |

| パワーダウン・レジスタ (0x0A)                                                                                                                                                 | 30    |

| DATA <sub>HIGH</sub> /DATA <sub>LOW</sub> レジスタ: $0x0B$ , $0x0C$ ( $V_{IN}0$ ); $0x0E$ , $(V_{IN}1)$ ; $0x11$ , $0x12$ ( $V_{IN}2$ ); $0x14$ , $0x15$ ( $V_{IN}3$ ) |       |

| ヒステリシス・レジスタ: $0x0D(V_{IN}0)$ 、 $0x10(V_{IN}1)$ 、 $0x10(V_{IN}1)$                                                                                                   |       |

| $(V_{IN}2)$ , $0x16(V_{IN}3)$                                                                                                                                      |       |

| T <sub>SENSE</sub> オフセット・レジスタ (0x26 と 0x27)                                                                                                                        |       |

| I <sup>2</sup> Cインターフェース                                                                                                                                           |       |

| 一般的な I <sup>2</sup> C のタイミング                                                                                                                                       |       |

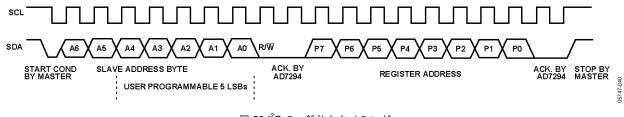

| シリアル・バスのアドレス・バイト                                                                                                                                                   | 33    |

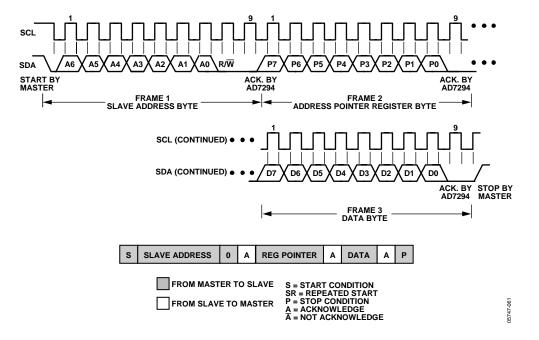

| インターフェース・プロトコル                                                                                                                                                     | 33    |

| 動作モード                                                                                                                                                              | 37    |

| コマンド・モード                                                                                                                                                           | 37    |

| 自動サイクル・モード                                                                                                                                                         | 38    |

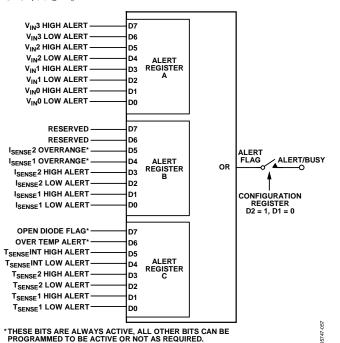

| 警報およびリミットの動作原理                                                                                                                                                     | 39    |

| Alert_Flag ビット                                                                                                                                                     | 39    |

| 警報ステータス・レジスタ                                                                                                                                                       | 39    |

| DATA <sub>HIGH</sub> と DATA <sub>LOW</sub> の監視機能                                                                                                                   | 39    |

| ヒステリシス                                                                                                                                                             | 40    |

| アプリケーション情報                                                                                                                                                         | 41    |

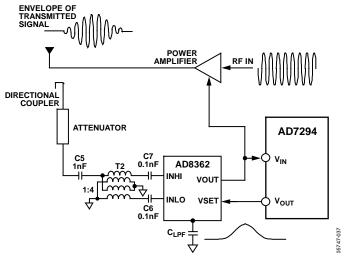

| 基地局パワー・アンプの監視と制御                                                                                                                                                   | 41    |

| パワー・アンプのゲイン制御                                                                                                                                                      | 42    |

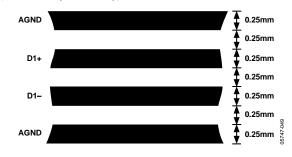

| レイアウトおよび構成                                                                                                                                                         | 43    |

| 電源のバイパスとグラウンド接続                                                                                                                                                    |       |

| 外形寸法                                                                                                                                                               |       |

| オーダー・ガイド                                                                                                                                                           |       |

|                                                                                                                                                                    |       |

### 改訂履歴

1/08—Revision 0: Initial Version

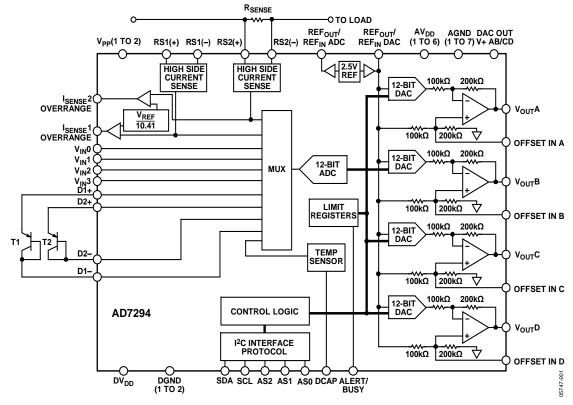

### 機能ブロック図

図 1.

### 仕様

### DAC 仕様

特に指定のない限り、 $AV_{DD}$  =  $DV_{DD}$  = 4.5  $V \sim 5.5$  V、AGND = DGND = 0 V、2.5 V の内部リファレンス;  $V_{DRIVE}$  = 2.7  $V \sim 5.5$  V;  $T_A$  = -40°C  $\sim +105$ °C。 DAC OUTV+ AB および DAC OUTV+ CD = 4.5  $V \sim 16.5$  V、OFFSET IN x はフローティングのため DAC 出力範囲 = 0  $V \sim 5$  V。

表 1.

| Parameter                                       | Min   | Тур         | Max                      | Unit      | Test Conditions/Comments                                                                                                                                                                       |

|-------------------------------------------------|-------|-------------|--------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                        |       |             |                          |           |                                                                                                                                                                                                |

| Resolution                                      | 12    |             |                          | Bits      |                                                                                                                                                                                                |

| Relative Accuracy (INL)                         |       | ±1          | ±3                       | LSB       |                                                                                                                                                                                                |

| Differential Nonlinearity (DNL)                 |       | ±0.3        | ±1                       | LSB       | Guaranteed monotonic                                                                                                                                                                           |

| Zero-Scale Error                                |       | 2.5         | 8                        | mV        |                                                                                                                                                                                                |

| Full-Scale Error of DAC and Output<br>Amplifier |       |             | 15.5 <sup>1</sup>        | mV        | DAC OUTV+ = $5.0 \text{ V}$                                                                                                                                                                    |

| Full-Scale Error of DAC                         |       | 2           |                          | mV        | DAC OUTV+ = $15.0 \text{ V}$                                                                                                                                                                   |

| Offset Error                                    |       |             | $\pm 8.575$              | mV        | Measured in the linear region, $T_A = -40^{\circ}\text{C}$ to $+105^{\circ}\text{C}$                                                                                                           |

|                                                 |       |             | ±2                       | mV        | Measured in the linear region, $T_A = 25^{\circ}C$                                                                                                                                             |

| Offset Error Temperature Coefficient            |       | ±5          |                          | ppm/°C    |                                                                                                                                                                                                |

| Gain Error                                      |       | $\pm 0.025$ | $\pm 0.155$              | % FSR     |                                                                                                                                                                                                |

| Gain Temperature Coefficient                    |       | ±5          |                          | ppm/°C    |                                                                                                                                                                                                |

| DAC OUTPUT CHARACTERISTICS                      |       |             |                          |           |                                                                                                                                                                                                |

| Output Voltage Span                             | 0     |             | $2\times V_{\text{REF}}$ | V         | 0 V to 5 V for a 2.5 V reference                                                                                                                                                               |

| Output Voltage Offset                           | 0     |             | 10                       | V         | The output voltage span can be positioned in the 0 V to 15 V range; if the OFFSET IN x is left floating, the offset pin = $2/3 \times V_{REF}$ , giving an output of 0 V to $2 \times V_{REF}$ |

| Offset Input pin range                          | 0     |             | 5                        |           | $V_{OUT} = 3 V_{OFFSET} - 2 \times V_{REF} + V_{DAC}$ , DAC HIGH-Z = 0 V                                                                                                                       |

|                                                 | 1.667 |             | 5                        |           | $V_{OUT} = OFFSET IN x, DAC HIGH-Z = V_{DRIVE}$                                                                                                                                                |

| DC Input Impedance <sup>2</sup>                 |       | 75          |                          | $k\Omega$ | $100~k\Omega$ to $V_{REF},$ and $200~k\Omega$ to AGND, see Figure 47                                                                                                                           |

| Output Voltage Settling Time <sup>2</sup>       |       | 8           |                          | μs        | 1/4 to 3/4 change within 1/2 LSB, measured from last SCL edge                                                                                                                                  |

| Slew Rate <sup>2</sup>                          |       | 1.1         |                          | V/µs      |                                                                                                                                                                                                |

| Short-Circuit Current <sup>2</sup>              |       | 40          |                          | mA        | Full-scale current shorted to ground                                                                                                                                                           |

| Load Current <sup>2</sup>                       |       | ±10         |                          | mA        | Source and/or sink within 200 mV of supply                                                                                                                                                     |

| Capacitive Load Stability <sup>2</sup>          | 10    |             |                          | nF        | $R_L = \infty$                                                                                                                                                                                 |

| DC Output Impedance <sup>2</sup>                |       | 1           |                          | Ω         |                                                                                                                                                                                                |

| REFERENCE                                       |       |             |                          |           |                                                                                                                                                                                                |

| Reference Output Voltage                        | 2.49  | 2.5         | 2.51                     | V         | $\pm 0.4\%$ maximum @ 25°C, $AV_{DD} = DV_{DD} = 4.5 \text{ V}$ to 5.5 V                                                                                                                       |

| Reference Input Voltage Range                   | 0     |             | $AV_{DD} - 2$            | V         |                                                                                                                                                                                                |

| Input Current                                   |       | 100         | 125                      | μΑ        | $V_{REF} = 2.5 \text{ V}$                                                                                                                                                                      |

| Input Capacitance <sup>2</sup>                  |       | 20          |                          | pF        |                                                                                                                                                                                                |

| V <sub>REF</sub> Output Impedance <sup>2</sup>  |       | 25          |                          | Ω         |                                                                                                                                                                                                |

| Reference Temperature Coefficient               |       | 10          | 25                       | ppm/°C    |                                                                                                                                                                                                |

<sup>&</sup>lt;sup>1</sup> この値は DAC 出力アンプが DAC OUTV+電源より 15.5 mV 低い電圧を出力できることを示します。高い DAC OUTV+電源電圧を使用する場合、DAC のフル・スケール誤差は無負荷で 2 mV (typ)です。

$<sup>^2</sup>$ 初期リリース時はサンプル・テストにより適合性を保証。出荷テストは行いません。

### ADC 仕様

特に指定のない限り、 $V_{DD}$  =  $DV_{DD}$  =  $4.5~V\sim5.5~V$ 、AGND = DGND = 0~V、 $V_{REF}$  = 2.5~V (内部または外部)、 $V_{DRIVE}$  =  $2.7~V\sim5.5~V$ 、 $V_{PP}$  =  $AV_{DD}\sim59.4~V$ ;  $T_A$  =  $-40^{\circ}C\sim+105^{\circ}C$ 。

表 2.

| Parameter                                                           | Min                | Typ       | Max                      | Unit | Test Conditions/Comments                                                           |

|---------------------------------------------------------------------|--------------------|-----------|--------------------------|------|------------------------------------------------------------------------------------|

| DC ACCURACY                                                         |                    |           |                          |      |                                                                                    |

| Resolution                                                          |                    | 12        |                          | Bits |                                                                                    |

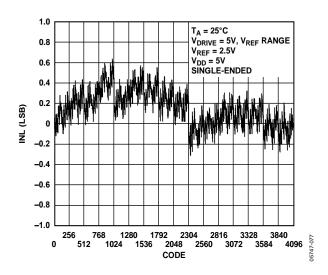

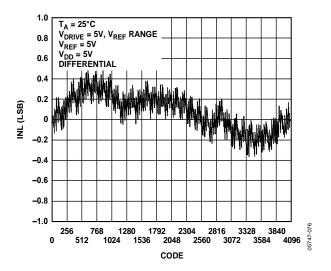

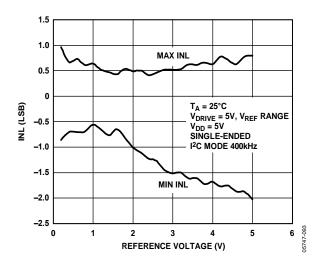

| Integral Nonlinearity (INL) <sup>1</sup>                            |                    | ±0.5      | ±1                       | LSB  | Differential mode                                                                  |

|                                                                     |                    | ±0.5      | ±1.5                     | LSB  | Single-ended or pseudo differential mode                                           |

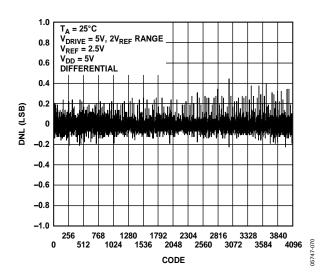

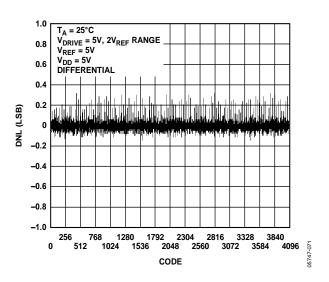

| Differential Nonlinearity (DNL) <sup>1</sup>                        |                    | ±0.5      | ±0.99                    | LSB  | Differential, single-ended, and pseudo differential modes                          |

| Single-Ended Mode                                                   |                    |           |                          |      |                                                                                    |

| Offset Error                                                        |                    | $\pm 1$   | ±7                       | LSB  |                                                                                    |

| Offset Error Match                                                  |                    | $\pm 0.4$ |                          | LSB  |                                                                                    |

| Gain Error                                                          |                    | ±0.5      | ±2.5                     | LSB  |                                                                                    |

| Gain Error Match                                                    |                    | $\pm 0.4$ |                          | LSB  |                                                                                    |

| Differential Mode                                                   |                    |           |                          |      |                                                                                    |

| Positive Gain Error                                                 |                    |           | ±3                       | LSB  |                                                                                    |

| Positive Gain Error Match                                           |                    | ±0.5      |                          | LSB  |                                                                                    |

| Zero Code Error                                                     |                    | ±3        | ±10                      | LSB  |                                                                                    |

| Zero Code Error Match                                               |                    | ±0.5      |                          | LSB  |                                                                                    |

| Negative Gain Error                                                 |                    |           | ±3                       | LSB  |                                                                                    |

| Negative Gain Error Match                                           |                    | ±0.5      |                          | LSB  |                                                                                    |

| CONVERSION RATE                                                     |                    |           |                          |      |                                                                                    |

| Conversion Time <sup>2</sup>                                        |                    | 3         |                          | μs   |                                                                                    |

| Autocycle Update Rate <sup>2</sup>                                  |                    | 50        |                          | μs   |                                                                                    |

| Throughput Rate                                                     |                    |           | 22.22                    | kSPS | $f_{SCL} = 400 \text{ kHz}$                                                        |

| ANALOG INPUT <sup>3</sup>                                           |                    |           |                          |      |                                                                                    |

| Single-Ended Input Range                                            | 0                  |           | $V_{\text{REF}}$         | V    | 0 V to V <sub>REF</sub> mode                                                       |

|                                                                     | 0                  |           | $2\times V_{\text{REF}}$ | V    | $0 \text{ V to } 2 \times V_{REF} \text{ mode}$                                    |

| Pseudo Differential Input Range: $V_{IN+} - V_{IN-}^{4}$            | 0                  |           | $V_{\text{REF}}$         |      | 0 V to V <sub>REF</sub> mode                                                       |

|                                                                     | 0                  |           | $2\times V_{\text{REF}}$ |      | $0 \text{ V to } 2 \times V_{REF} \text{ mode}$                                    |

| Fully Differential Input Range: V <sub>IN+</sub> - V <sub>IN-</sub> | $-V_{REF}$         |           | $+V_{REF}$               |      | 0 V to V <sub>REF</sub> mode                                                       |

|                                                                     | $-2 \times V_{RE}$ |           | $+2 \times$              |      | $0 \text{ V to } 2 \times V_{REF} \text{ mode}$                                    |

|                                                                     | F                  |           | $V_{REF}$                |      |                                                                                    |

| Input Capacitance <sup>2</sup>                                      |                    | 30        |                          | pF   |                                                                                    |

| DC Input Leakage Current                                            |                    |           | ±1                       | μΑ   |                                                                                    |

| DYNAMIC PERFORMANCE                                                 |                    |           |                          |      |                                                                                    |

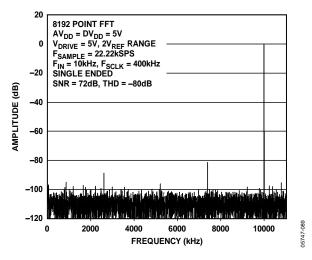

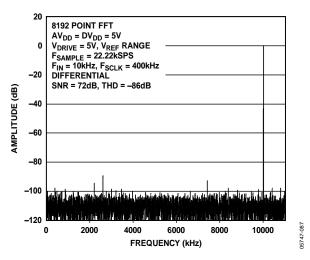

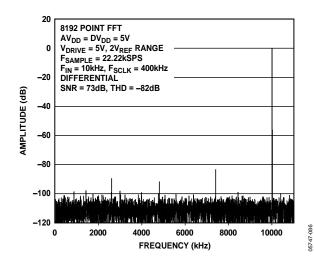

| Signal-to-Noise Ratio (SNR) <sup>1</sup>                            | 72.5               | 73        |                          | dB   | $f_{IN} = 10 \text{ kHz}$ sine wave; differential mode                             |

|                                                                     | 71                 | 72        |                          | dB   | $f_{IN} = 10 \text{ kHz}$ sine wave; single-ended and pseudo differential          |

|                                                                     |                    |           |                          |      | modes                                                                              |

| Signal-to-Noise + Distortion (SINAD) Ratio <sup>1</sup>             | 69                 | 71.5      |                          | dB   | $f_{IN} = 10 \text{ kHz}$ sine wave; differential mode                             |

|                                                                     | 71                 | 72.5      |                          | dB   | $f_{\rm IN}$ = 10 kHz sine wave; single-ended and pseudo differential modes        |

| Total Harmonic Distortion (THD) <sup>1</sup>                        |                    | -81       | -74                      | dB   | $f_{IN} = 10 \text{ kHz}$ sine wave; differential mode                             |

|                                                                     |                    | -79       | <del>-72</del>           | dB   | $f_{\rm IN} = 10~\text{kHz}$ sine wave; single-ended and pseudo differential modes |

| Spurious-Free Dynamic Range (SFDR) <sup>1</sup>                     |                    | -91       | -84.5                    | dB   | $f_{IN} = 10$ kHz sine wave; differential mode                                     |

|                                                                     |                    | -93       | -85.5                    |      | $f_{\rm IN}$ = 10 kHz sine wave; single-ended and pseudo differential modes        |

| Channel-to-Channel Isolation <sup>2</sup>                           |                    | -90       |                          | dB   | $f_{IN} = 10 \text{ kHz to } 40 \text{ kHz}$                                       |

| TEMPERATURE SENSOR—INTERNAL                                         |                    |           |                          |      |                                                                                    |

| Operating Range                                                     | -40                |           | +105                     | °C   |                                                                                    |

| Accuracy                                                            |                    |           | ±2                       | °C   | Internal temperature sensor, $T_A = -30$ °C to $+90$ °C                            |

| -                                                                   |                    |           | ±2.5                     | °C   | Internal temperature sensor, $T_A = -40$ °C to $+105$ °C                           |

| Resolution                                                          |                    | 0.25      |                          | °C   | LSB size                                                                           |

| Update Rate                                                         |                    | 5         |                          | ms   |                                                                                    |

| Parameter                                                                                                        | Min       | Тур  | Max           | Unit   | Test Conditions/Comments                                                                     |

|------------------------------------------------------------------------------------------------------------------|-----------|------|---------------|--------|----------------------------------------------------------------------------------------------|

| TEMPERATURE SENSOR—EXTERNAL                                                                                      |           |      |               |        | External transistor is 2N3906                                                                |

| Operating Range                                                                                                  | -55       |      | +150          | °C     | Limited by external diode                                                                    |

| Accuracy                                                                                                         |           |      | ±2            | °C     | $T_A = T_{DIODE} = -40$ °C to $+105$ °C                                                      |

| Resolution                                                                                                       |           | 0.25 |               | °C     | LSB size                                                                                     |

| Low Level Output Current Source <sup>2</sup>                                                                     |           | 8    |               | μΑ     |                                                                                              |

| Medium Level Output Current Source <sup>2</sup>                                                                  |           | 32   |               | μΑ     |                                                                                              |

| High Level Output Current Source <sup>2</sup>                                                                    |           | 128  |               | μΑ     |                                                                                              |

| Maximum Series Resistance (R <sub>S</sub> ) for External Diode <sup>2</sup>                                      |           |      | 100           | Ω      | For $< \pm 0.5$ °C additional error, $C_P = 0$ , see Figure 30                               |

| $\begin{array}{c} \text{Maximum Parallel Capacitance } (C_P) \text{ for External} \\ \text{Diode}^2 \end{array}$ |           |      | 1             | nF     | $R_S = 0$ , see Figure 29                                                                    |

| CURRENT SENSE                                                                                                    |           |      |               |        | $V_{PP} = AV_{DD}$ to 59.4 V                                                                 |

| V <sub>PP</sub> Supply Range                                                                                     | $AV_{DD}$ |      | 59.4          | V      |                                                                                              |

| Gain                                                                                                             | 12.4375   | 12.5 | 12.5625       |        | Gain of 12.5 gives a gain error = 0.5% maximum; delivers ±200 mV range with +2.5 V reference |

| RS(+)/RS(-) Input Bias Current                                                                                   |           | 25   | 32            | μΑ     |                                                                                              |

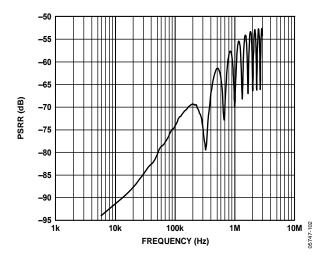

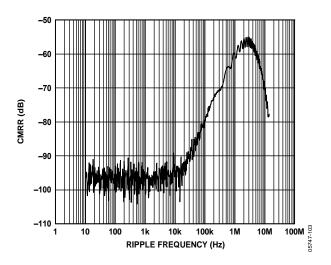

| CMRR/PSRR <sup>2</sup>                                                                                           |           | 80   |               | dB     | Inputs shorted to V <sub>PP</sub>                                                            |

| Offset Error                                                                                                     |           | ±50  | ±340          | μV     |                                                                                              |

| Offset Drift                                                                                                     |           | 1    |               | μV/°C  |                                                                                              |

| Amplifier Peak-To-Peak Noise <sup>2</sup>                                                                        |           | 400  |               | μV     | Referred to input                                                                            |

| V <sub>PP</sub> Supply Current                                                                                   |           | 0.18 | 0.22          | mA     | $V_{PP} = 59.4 \text{ V}$                                                                    |

| REFERENCE                                                                                                        |           |      |               |        |                                                                                              |

| Reference Output Voltage                                                                                         | 2.49      |      | 2.51          | V      | ±0.2% maximum at 25°C only                                                                   |

| Reference Input Voltage Range                                                                                    | 0.1       |      | 4.1           | V      | For four uncommitted ADCs                                                                    |

|                                                                                                                  | 1         |      | $AV_{DD} - 2$ |        | For current sense                                                                            |

| DC Leakage Current                                                                                               |           |      | ±2            | μΑ     |                                                                                              |

| V <sub>REF</sub> Output Impedance <sup>2</sup>                                                                   |           | 25   |               | Ω      |                                                                                              |

| Input Capacitance <sup>2</sup>                                                                                   |           | 20   |               | pF     |                                                                                              |

| Reference Temperature Coefficient                                                                                |           | 10   | 25            | ppm/°C |                                                                                              |

<sup>1</sup>詳細については、用語のセクションを参照してください。

$<sup>^2</sup>$ 初期リリース時はサンプル・テストにより適合性を保証。出荷テストは行いません。

$<sup>^3\,</sup>V_{\text{IN+}}$ または $\,V_{\text{IN-}}$ は、 $\,GND$  と $\,V_{DD}$ の間に維持する必要があります。

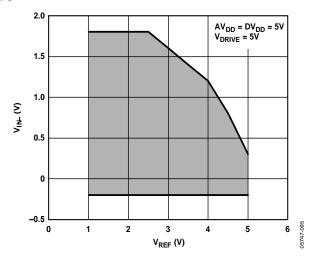

$<sup>^4</sup>$ 規定性能に対して  $V_{\text{IN}^-}$  = 0  $V_{\circ}$   $V_{\text{IN}^-}$ のフル入力範囲については、図 39 を参照してください。

### 全体仕様

特に指定のない限り、 $V_{DD}$  =  $DV_{DD}$  =  $4.5~V\sim5.5~V$ 、AGND = DGND = 0~V、 $V_{REF}$  = 2.5~V (内部または外部)、 $V_{DRIVE}$  =  $2.7~V\sim5.5~V$ 、 $V_{PP}$  =  $AV_{DD}\sim59.4~V$ 、DAC OUTV+ AB および DAC OUTV+ CD =  $4.5~V\sim16.5~V$ ; OFFSET IN x はフローティング(したがって DAC 出力範囲 =  $0~V\sim5~V$ )、 $T_A$  =  $-40^{\circ}C\sim+105^{\circ}C$ 。

表 3.

| Parameter                                                                  | Min              | Тур                                                 | Max               | Unit | Test Conditions/Comments                                   |

|----------------------------------------------------------------------------|------------------|-----------------------------------------------------|-------------------|------|------------------------------------------------------------|

| LOGIC INPUTS                                                               |                  |                                                     |                   |      |                                                            |

| Input High Voltage, VIH                                                    | $0.7 V_{DRIVE}$  |                                                     |                   | V    | SDA, SCL only                                              |

| Input Low Voltage, V <sub>IL</sub>                                         |                  |                                                     | $0.3~V_{DRIVE}$   | V    | SDA, SCL only                                              |

| Input Leakage Current, IIN                                                 |                  |                                                     | ±1                | μΑ   |                                                            |

| Input Hysteresis, V <sub>HYST</sub>                                        | $0.05~V_{DRIVE}$ |                                                     |                   | V    |                                                            |

| Input Capacitance, C <sub>IN</sub>                                         |                  | 8                                                   |                   | pF   |                                                            |

| Glitch Rejection                                                           |                  | 50                                                  |                   | ns   | Input filtering suppresses noise spikes of less than 50 ns |

| I <sup>2</sup> C® Address Pins Maximum External<br>Capacitance if Floating |                  |                                                     | 30                | pF   | Tristate input                                             |

| DAC HIGH-Z Pin Leakage                                                     |                  | 10                                                  |                   | μΑ   | Input with pull-down resistor, $V_{IN} = 5.5 \text{ V}$    |

|                                                                            |                  | 1                                                   |                   | μΑ   | Input with pull-down resistor, $V_{IN} = 0 \text{ V}$      |

| LOGIC OUTPUTS                                                              |                  |                                                     |                   |      |                                                            |

| SDA, ALERT                                                                 |                  |                                                     |                   |      | SDA and ALERT/BUSY are open-drain outputs                  |

| Output Low Voltage, VoL                                                    |                  |                                                     | 0.4               | V    | $I_{SINK} = 3 \text{ mA}$                                  |

|                                                                            |                  |                                                     | 0.6               | V    | $I_{SINK} = 6 \text{ mA}$                                  |

| Floating-State Leakage Current                                             |                  |                                                     | ±1                | μΑ   |                                                            |

| Floating-State Output Capacitance                                          |                  | 8                                                   |                   | pF   |                                                            |

| I <sub>SENSE</sub> OVERRANGE                                               |                  |                                                     |                   |      | I <sub>SENSE</sub> OVERRANGE is a push-pull output         |

| Output High Voltage, V <sub>OH</sub>                                       |                  |                                                     | $V_{DRIVE} - 0.2$ | V    | $I_{SOURCE} = 200 \mu A$ for push-pull outputs             |

| Output Low Voltage, Vol                                                    |                  |                                                     | 0.2               | V    | $I_{SINK} = 200 \mu A$ for push-pull outputs               |

| Overrange Setpoint                                                         | $V_{FS}$         | $\begin{array}{c} V_{FS} \times \\ 1.2 \end{array}$ |                   | mV   | $V_{FS} = \pm V_{REF} ADC/12.5$                            |

| POWER REQUIREMENTS                                                         |                  |                                                     |                   |      |                                                            |

| $V_{ m PP}$                                                                | $AV_{ m DD}$     |                                                     | 59.4              | V    |                                                            |

| $\mathrm{AV}_{\mathrm{DD}}$                                                | 4.5              |                                                     | 5.5               | V    |                                                            |

| V(+)                                                                       | 4.5              |                                                     | 16.5              | V    |                                                            |

| $\mathrm{DV}_{\mathrm{DD}}$                                                | 4.5              |                                                     | 5.5               | V    | Tie DV <sub>DD</sub> to AV <sub>DD</sub>                   |

| $V_{ m DRIVE}$                                                             | 2.7              |                                                     | 5.5               | V    |                                                            |

| I <sub>DD</sub> Dynamic                                                    |                  | 5.3                                                 | 6.5               | mA   | $AV_{DD} + DV_{DD} + V_{DRIVE}$ , DAC outputs unloaded     |

| DAC OUTV+ $x$ , $I_{DD}$                                                   |                  | 0.6                                                 | 0.9               | mA   | @ midscale output voltage, DAC outputs unloaded            |

| Power Dissipation                                                          |                  | 70                                                  | 92                | mW   |                                                            |

| Power-Down                                                                 |                  |                                                     |                   |      |                                                            |

| ${ m I}_{ m DD}$                                                           |                  | 0.5                                                 | 1                 | μΑ   | For each $AV_{DD}$ and $V_{DRIVE}$                         |

| $\mathrm{DI}_{\mathrm{DD}}$                                                |                  | 1                                                   | 16.5              | μΑ   |                                                            |

| DAC OUTV+ $x$ , $I_{DD}$                                                   |                  | 35                                                  | 60                | μΑ   |                                                            |

| Power Dissipation                                                          |                  |                                                     | 2.5               | mW   |                                                            |

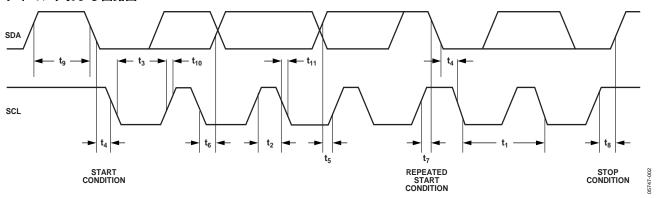

### タイミング特性

### I<sup>2</sup>C シリアル・インターフェース

特に指定のない限り、 $V_{DD}$  =  $DV_{DD}$  =  $4.5~V\sim5.5~V$ 、AGND = DGND = 0~V、 $V_{REF}$  = 2.5~V (内部または外部)、 $V_{DRIVE}$  =  $2.7~V\sim5.5~V$ 、 $V_{PP}$  =  $AV_{DD}\sim59.4~V$ 、DAC OUTV+ AB および DAC OUTV+ CD =  $4.5~V\sim16.5~V$ ; OFFSET IN x はフローティング(したがって DAC 出力範囲 =  $0~V\sim5~V$ )、 $T_A$  =  $-40^{\circ}C\sim+105^{\circ}C$ 。

表 4.

| Parameter <sup>1</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Description                                                                |

|------------------------|----------------------------------------------|---------|----------------------------------------------------------------------------|

| $f_{SCL}$              | 400                                          | kHz max | SCL clock frequency                                                        |

| $t_1$                  | 2.5                                          | μs min  | SCL cycle time                                                             |

| $t_2$                  | 0.6                                          | μs min  | t <sub>HIGH</sub> , SCL high time                                          |

| $t_3$                  | 1.3                                          | μs min  | t <sub>LOW</sub> , SCL low time                                            |

| $t_4$                  | 0.6                                          | μs min  | t <sub>HD,STA</sub> , start/repeated start condition hold time             |

| $t_5$                  | 100                                          | ns min  | t <sub>SU,DAT</sub> , data setup time                                      |

| $t_6^2$                | 0.9                                          | μs max  | t <sub>HD,DAT</sub> , data hold time                                       |

|                        | 0                                            | μs min  | t <sub>HD,DAT</sub> , data hold time                                       |

| $t_7$                  | 0.6                                          | μs min  | t <sub>SU,STA</sub> , setup time for repeated start                        |

| $t_8$                  | 0.6                                          | μs min  | t <sub>SU,STO</sub> , stop condition setup time                            |

| t <sub>9</sub>         | 1.3                                          | μs min  | t <sub>BUF</sub> , bus free time between a stop and a start condition      |

| $t_{10}$               | 300                                          | ns max  | t <sub>R</sub> , rise time of SCL and SDA when receiving                   |

|                        | 0                                            | ns min  | t <sub>R</sub> , rise time of SCL and SDA when receiving (CMOS compatible) |

| t <sub>11</sub>        | 300                                          | ns max  | t <sub>F</sub> , fall time of SDA when transmitting                        |

|                        | 0                                            | ns min  | t <sub>F</sub> , fall time of SDA when receiving (CMOS compatible)         |

|                        | 300                                          | ns max  | t <sub>F</sub> , fall time of SCL and SDA when receiving                   |

|                        | $20 + 0.1C_b^3$                              | ns min  | t <sub>F</sub> , fall time of SCL and SDA when transmitting                |

| $C_b$                  | 400                                          | pF max  | Capacitive load for each bus line                                          |

$<sup>^{1}</sup>$  図 2 を参照してください。

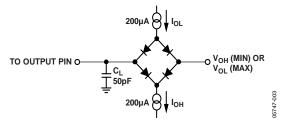

### タイミングおよび回路図

図 2.I2C 互換シリアル・インターフェースのタイミング図

図 3.デジタル出力の負荷回路

Rev. 0 - 8/44 -

$<sup>^2</sup>$  SCL の立ち下がりエッジの不定領域を避けるため、マスター・デバイスは、SDA 信号に対して最小 300 ns のホールド・タイムを保証する必要があります (SCL 信号の  $V_{IH}$  min を基準として)。

$<sup>^3</sup>$   $C_b$  は 1 本のバス・ラインの合計容量(pF)です。  $t_R$  と  $t_F$  は、 $0.3 \times DV_{DD}$  と  $0.7 \times DV_{DD}$  との間で測定。

### 絶対最大定格

特に指定のない限り、 $T_A = 25$ °C。

表 5.

| 12 0.                                             |                                                      |

|---------------------------------------------------|------------------------------------------------------|

| Parameter                                         | Rating                                               |

| V <sub>PP</sub> x to AGND                         | -0.3 V to +70 V                                      |

| AV <sub>DD</sub> x to AGND                        | -0.3 V to +7 V                                       |

| DAC OUTV+ AB to AGND                              | -0.3 V to +17 V                                      |

| DAC OUTV+ CD to AGND                              | -0.3 V to +17 V                                      |

| DV <sub>DD</sub> to DGND                          | -0.3 V to +7 V                                       |

| $V_{DRIVE}$ to OPGND                              | -0.3 V to +7 V                                       |

| Digital Inputs to OPGND                           | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$        |

| SDA/SCL to OPGND                                  | -0.3 V to +7 V                                       |

| Digital Outputs to OPGND                          | $-0.3 \text{ V to V}_{\text{DRIVE}} + 0.3 \text{ V}$ |

| $RS(+)/RS(-)$ to $V_{PP}X$                        | $V_{PP} - 0.3 \text{ V to } V_{PP} + 0.3 \text{ V}$  |

| REF <sub>OUT</sub> /REF <sub>IN</sub> ADC to AGND | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$          |

| REF <sub>OUT</sub> /REF <sub>IN</sub> DAC to AGND | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$          |

| OPGND to AGND                                     | -0.3 V to +0.3 V                                     |

| OPGND to DGND                                     | -0.3 V to +0.3 V                                     |

| AGND to DGND                                      | -0.3 V to +0.3 V                                     |

| V <sub>OUT</sub> x to AGND                        | -0.3 V to DAC OUTV(+) + 0.3 V                        |

| Analog Inputs to AGND                             | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$          |

| Operating Temperature Range                       |                                                      |

| B Version                                         | −40°C to +105°C                                      |

| Storage Temperature Range                         | −65°C to +150°C                                      |

| Junction Temperature (T <sub>J</sub> Max)         | 150°C                                                |

| ESD Human Body Model                              | 1 kV                                                 |

| Reflow Soldering Peak Temperature                 | 230°C                                                |

$<sup>^{1}</sup>$ 最大  $100\,\mathrm{mA}$  までの過渡電流では SCR ラッチ・アップは生じません。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒 久的な損傷を与えることがあります。この規定はストレス定格 の規定のみを目的とするものであり、この仕様の動作の節に記 載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くとデバイスの信 頼性に影響を与えます。

IPC 2221 工業規格に準拠するためは、高電圧ピンに絶縁保護コーティングを使用することが推奨されます。

### 熱抵抗

表 6.熱抵抗

| Package Type | $\theta_{\mathrm{JA}}$ | $\theta_{ m JC}$ | Unit |

|--------------|------------------------|------------------|------|

| 64-Lead TOFP | 54                     | 16               | °C/W |

### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. 0 — 9/44 —

### ピン配置およびピン機能説明

表 7.ピン機能の説明

| -<br>ピン番号                          | 記号                                        | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 61                              | RS2(-)、RS1(-)                             | 外付けシャント抵抗の接続。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3, 60                              | RS2(+)、RS1(+)                             | 外付けシャント抵抗の接続。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1, 4, 16,<br>17, 32, 33,<br>59, 64 | NC                                        | 未接続。これらのピンは接続しないでください。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

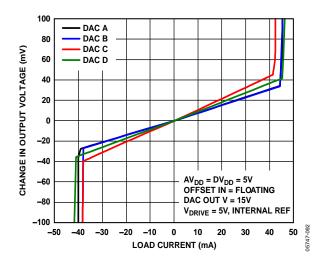

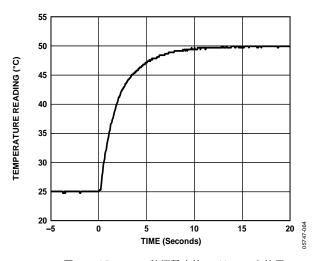

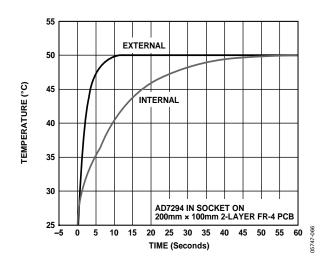

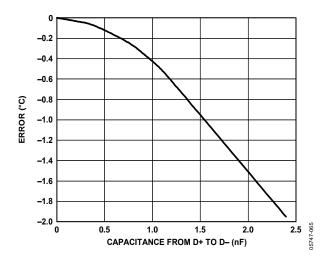

| 5、8、14、<br>25、56、57                | $AV_{DD}1\sim AV_{DD}6$                   | アナログ電源ピン。動作範囲は $4.5\mathrm{V}\sim5.5\mathrm{V}$ 。これらのピンは、 $\mathrm{AD7294}$ 内のすべてのアナログ回路へ電源電圧を供給します。 $\mathrm{AV}_\mathrm{DD}$ ピンと $\mathrm{DV}_\mathrm{DD}$ ピンを接続して、すべての電源ピンが同電位になるようにする必要があります。各 $\mathrm{AV}_\mathrm{DD}$ ピンごとに $10\mu\mathrm{F}$ のタンタル・コンデンサと $0.1\mu\mathrm{F}$ のセラミック・コンデンサを使って、 $\mathrm{AGND}$ ヘデカップリングする必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |