# 4 チャンネル、低ノイズ、低消費電力 24 ビット、シグマ・デルタ(Σ-Δ) ADC、PGA およびリファレンス内蔵

データシート

AD7124-4

# 特長

3つの消費電力モード

RMS ノイズ

低消費電力:24 nV rms @ 1.17 SPS、

ゲイン = 128 (255 µA typ)

中消費電力:20 nV rms @ 2.34 SPS、

ゲイン = 128 (355  $\mu$ A typ)

通常消費電力:23 nV rms @ 9.4 SPS、

ゲイン = 128 (930 µA typ)

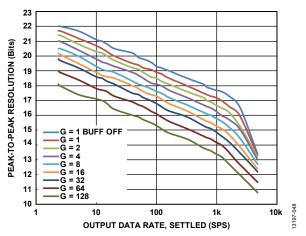

すべての消費電力モードで最大 22 ノイズ・フリー・ビット

(ゲイン=1)

出力データ・レート

通常消費電力:9.38 SPS ~ 19,200 SPS

中消費電力:2.34 SPS ~4800 SPS

低消費電力:1.17 SPS ~2400 SPS

レール to レール・アナログ入力 (ゲイン > 1)

25 SPS (シングル・サイクル・セトリング) での

50 Hz/60 Hz 同時除去

診断機能 (安全度水準 (SIL) 認定取得に有用)

クロスポイント・マルチプレクサ・アナログ入力

4個の差動入力/7個の疑似差動入力

プログラマブル・ゲイン (1 ~ 128)

バンド・ギャップ・リファレンス、

ドリフト 10 ppm/°C (max) (70 μA)

マッチングがとれたプログラマブル励起電流

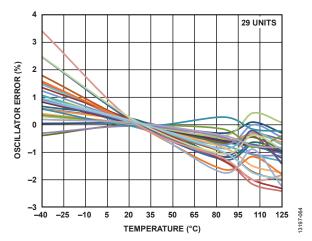

内部クロック発振器

内蔵バイアス電圧発生器

ローサイド・パワー・スイッチ

汎用出力

複数のフィルタ・オプション

内部温度センサー

セルフ/システム・キャリブレーション

センサー・バーンアウト検出

自動チャンネル・シーケンサ

チャンネルごとに設定

電源:2.7 V ~ 3.6 V および ±1.8 V

独立したインターフェース電源

パワーダウン電流: 5 μA (max)

動作温度範囲: -40°C ~ +125°C

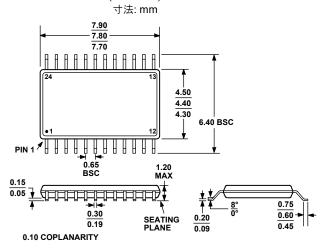

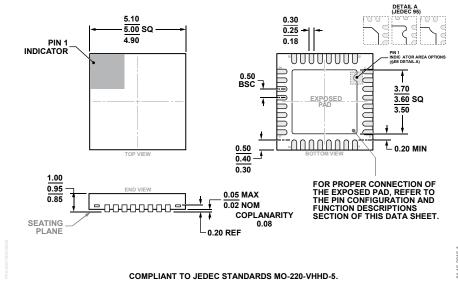

32 ピン LFCSP / 24 ピン TSSOP

3線式または4線式シリアル・インターフェース

SPI、QSPI、MICROWIRE、DSP 互換

SCLK にシュミット・トリガー内蔵

ESD: 4 kV

# アプリケーション

温度計測

圧力計測

工業用プロセス制御

計測器

スマート・トランスミッタ

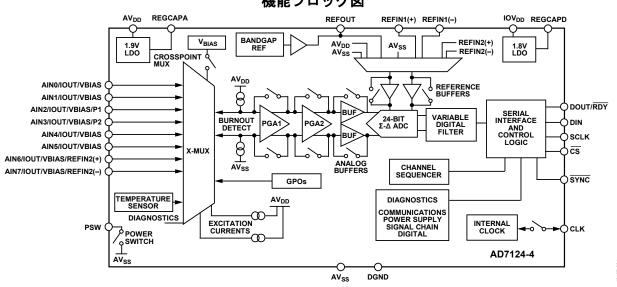

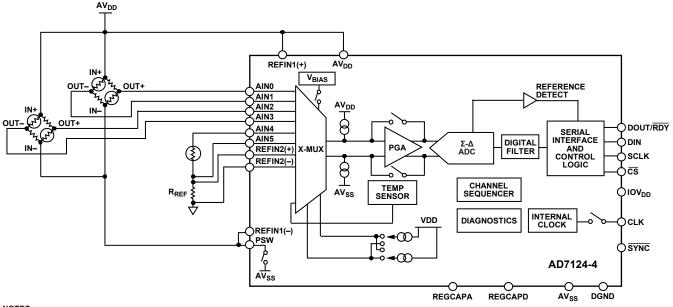

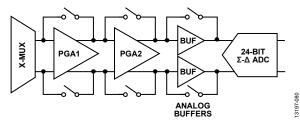

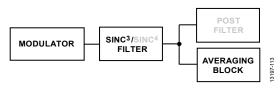

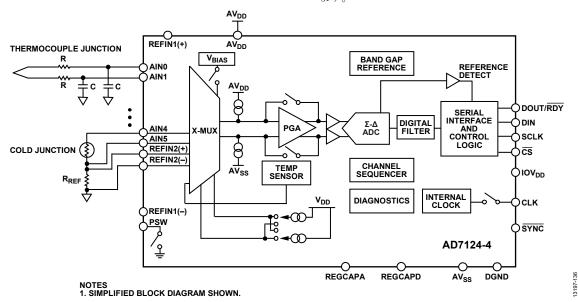

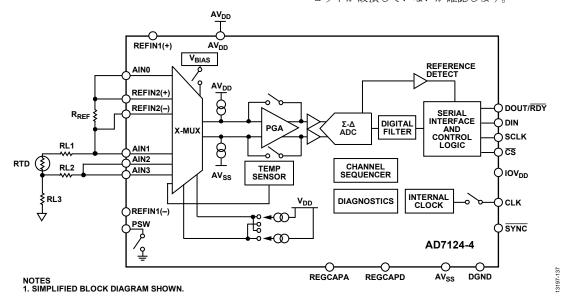

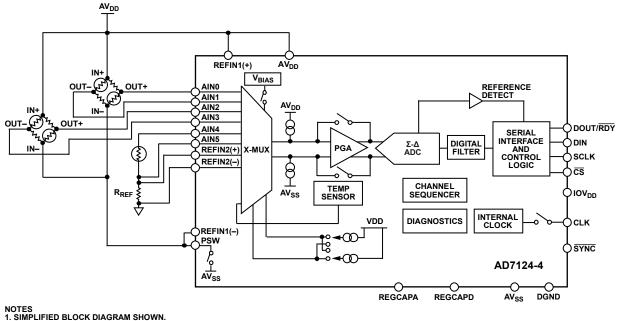

# 機能ブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2019 Analog Devices, Inc. All rights reserved.

Rev. D

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03 (5402) 8200

大 阪営業所/〒532-0003

図 1.

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F電話 06 (6350) 6868

名古屋営業所/〒451-6038

愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300

アナログ・デバイセズ株式会社

# データシート

# 目次

| 特長                          | 1  |

|-----------------------------|----|

| アプリケーション                    | 1  |

| 機能ブロック図                     | 1  |

| 改訂履歴                        | 3  |

| 概要                          | 5  |

| 仕様                          | 6  |

| タイミング特性                     | 11 |

| 絶対最大定格                      | 14 |

| 熱抵抗                         | 14 |

| ESD に関する注意                  | 14 |

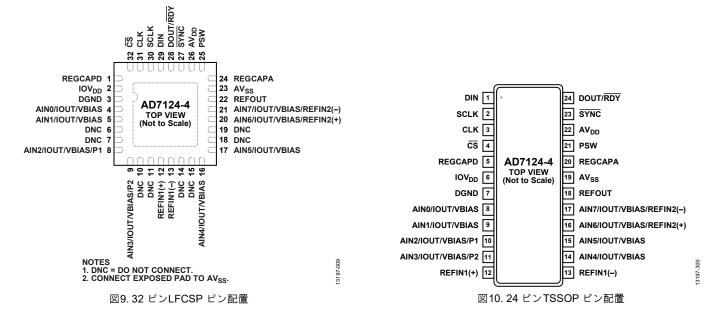

| ピン配置およびピン機能の説明              | 15 |

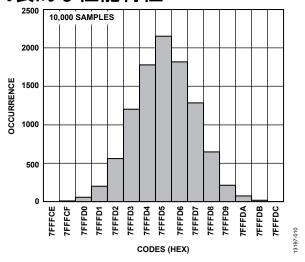

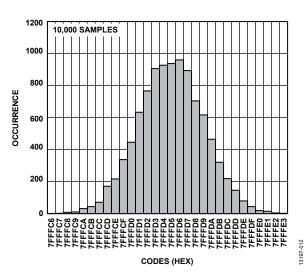

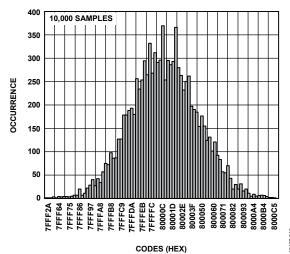

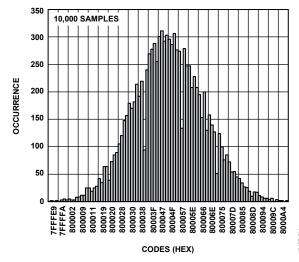

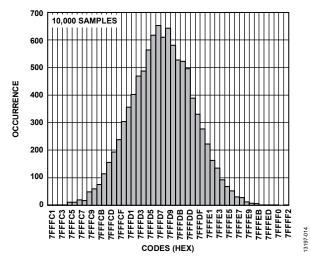

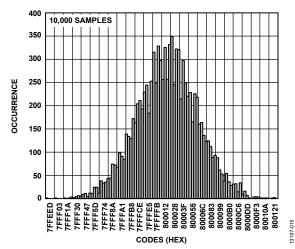

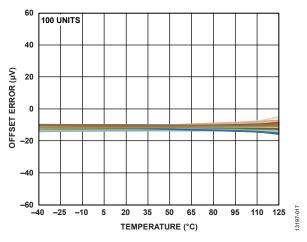

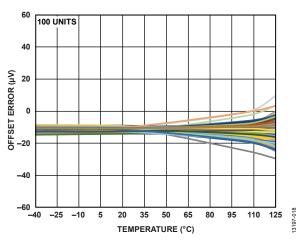

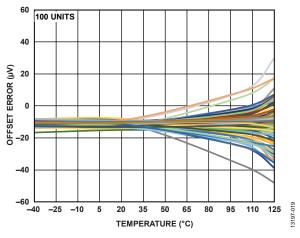

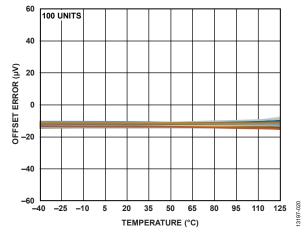

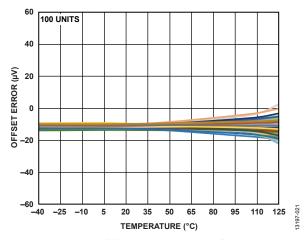

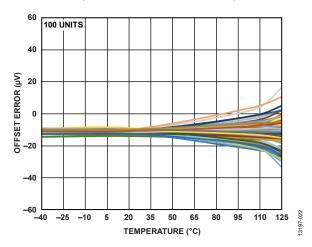

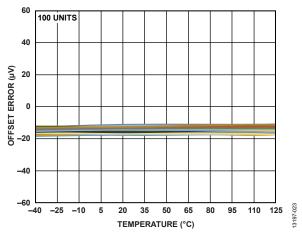

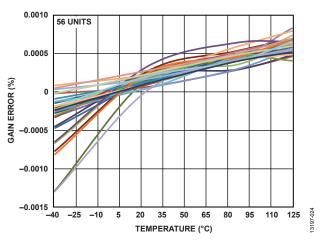

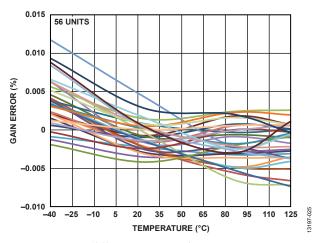

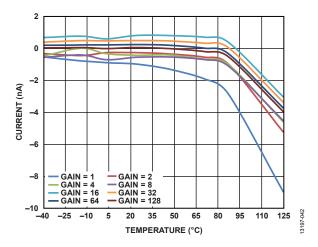

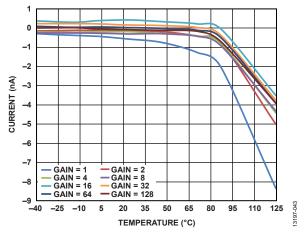

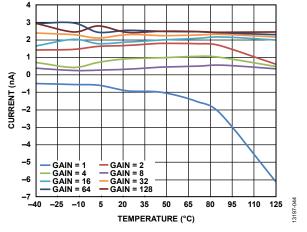

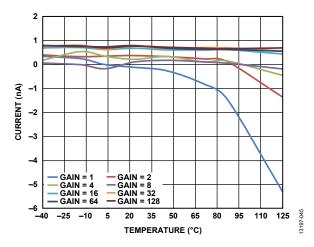

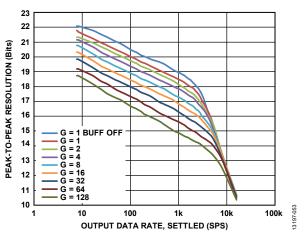

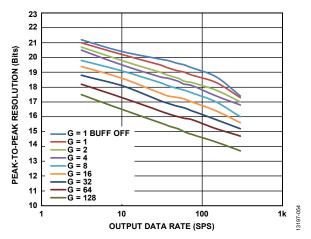

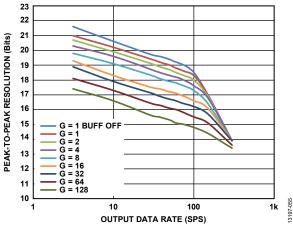

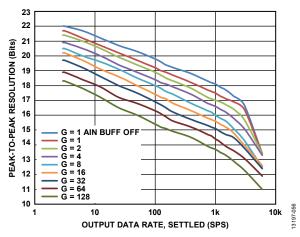

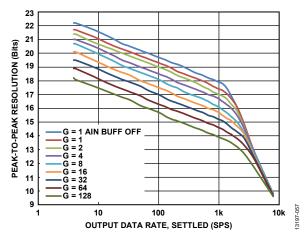

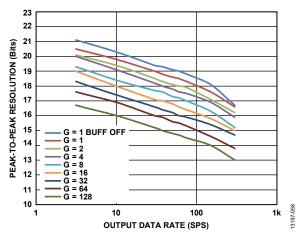

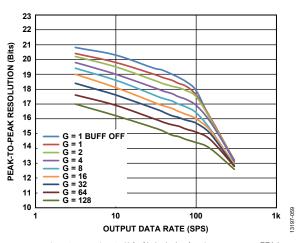

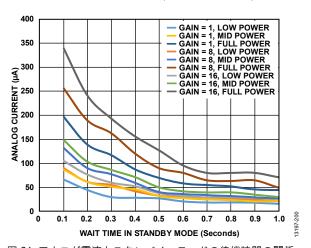

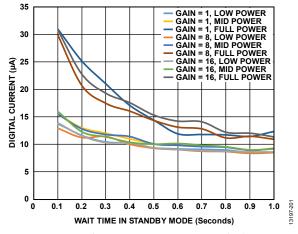

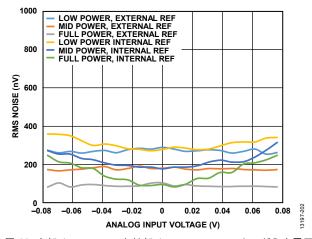

| 代表的な性能特性                    | 18 |

| 用語の定義                       | 27 |

| RMS ノイズと分解能                 | 28 |

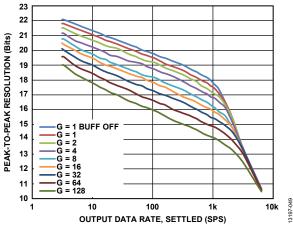

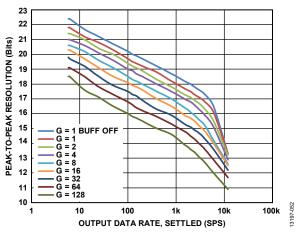

| 通常消費電力モード                   | 28 |

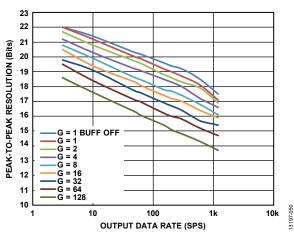

| 中消費電力モード                    | 31 |

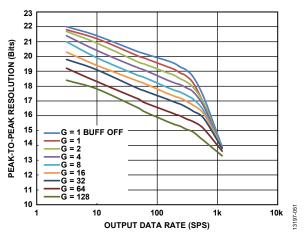

| 低消費電力モード                    | 34 |

| 評価開始にあたって                   | 37 |

| 概要                          | 37 |

| 電源                          | 38 |

| デジタル通信                      | 38 |

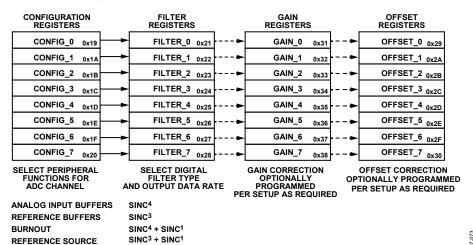

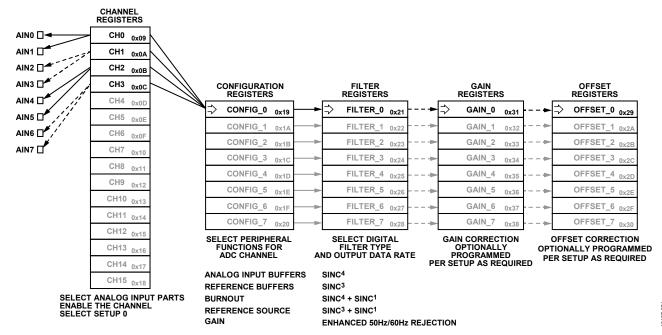

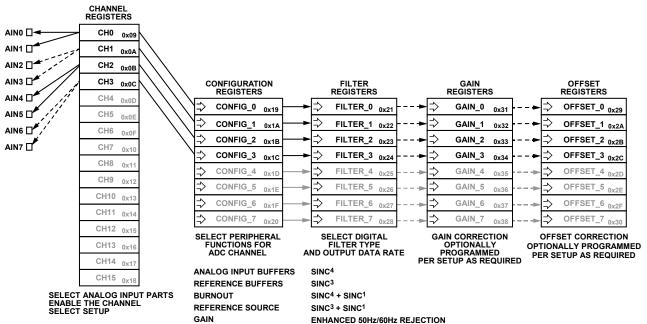

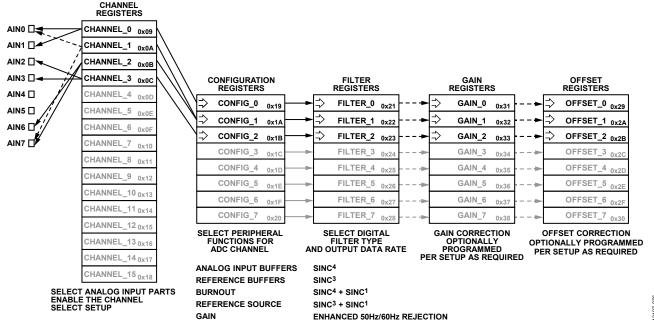

| 構成概要                        | 40 |

| ADC 回路情報                    | 45 |

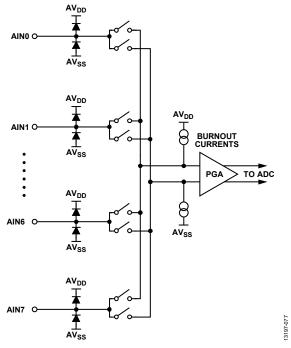

| アナログ入力チャンネル                 | 45 |

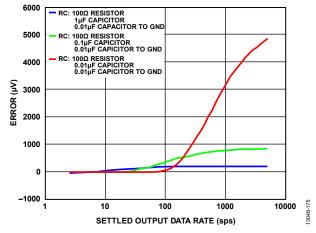

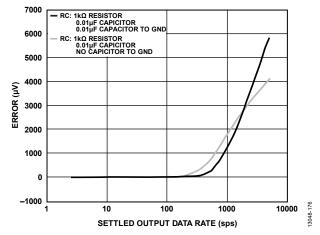

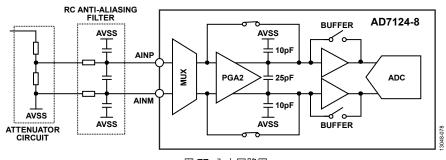

| ゲイン 1 使用時の外部インピーダンス         | 46 |

| プログラマブル・ゲイン・アレイ (PGA)       | 47 |

| リファレンス                      | 47 |

| バイポーラ/ユニポーラ構成               | 47 |

| データ出力コーディング                 | 48 |

| 励起電流                        | 48 |

| ブリッジ・パワーダウン・スイッチ            | 49 |

| ロジック出力                      | 49 |

| バイアス電圧発生器                   | 49 |

| クロック                        | 49 |

| 消費電力モード                     | 49 |

| スタンバイ・モードとパワーダウン・モード        | 49 |

| デジタル・インターフェース               | 50 |

| DATA_STATUS                 |    |

| シリアル・インターフェース・リセット (DOUT_RI |    |

| および CS_EN ビット)              |    |

| リセット                        | 52 |

|   | キャリブレーション                                                | 5 | 3 |

|---|----------------------------------------------------------|---|---|

|   | スパンとオフセットの限界値                                            | 5 | 4 |

|   | システム同期                                                   | 5 | 4 |

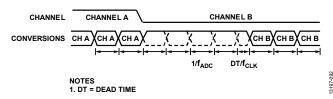

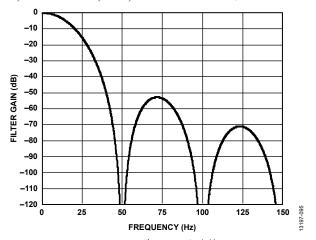

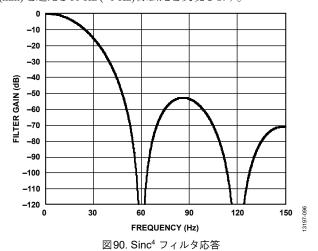

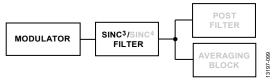

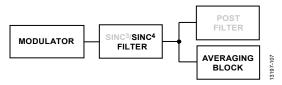

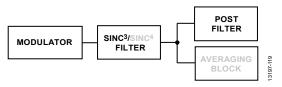

| ラ | ゙゙ジタル・フィルタ                                               | 5 | 5 |

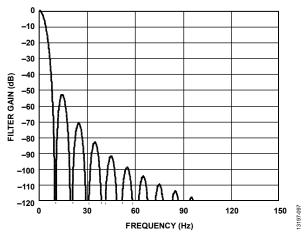

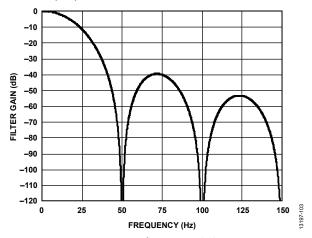

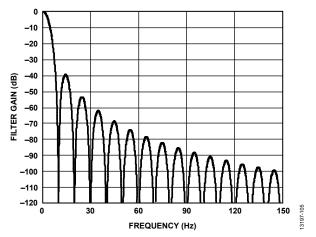

|   | Sinc <sup>4</sup> フィルタ                                   | 5 | 5 |

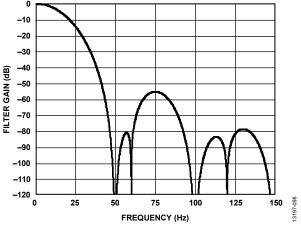

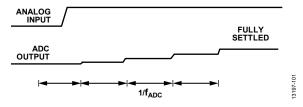

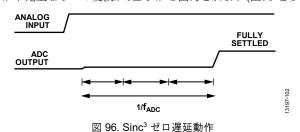

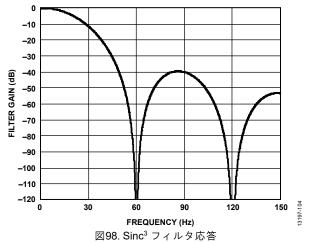

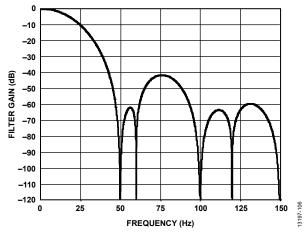

|   | Sinc <sup>3</sup> フィルタ                                   | 5 | 7 |

|   | 高速セトリング・モード (Sinc <sup>4</sup> + Sinc <sup>1</sup> フィルタ) | 5 | 9 |

|   | 高速セトリング・モード (SINC³ + SINC¹ フィルタ)                         | 6 | 1 |

|   | ポスト・フィルタ                                                 | 6 | 3 |

|   | フィルタ・オプション一覧                                             | 6 | 6 |

| 診 | 》断機能                                                     | 6 | 7 |

|   | シグナル・チェーンのチェック                                           | 6 | 7 |

|   | リファレンス電圧の検出                                              | 6 | 7 |

|   | キャリブレーション・エラー、変換エラー、飽和エラー                                | 6 | 7 |

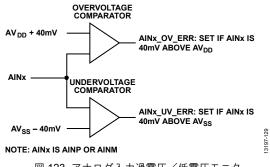

|   | 過電圧/低電圧の検出                                               | 6 | 7 |

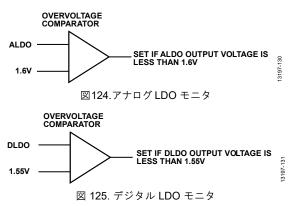

|   | 電源モニタ                                                    | 6 | 8 |

|   | LDO モニタリング                                               | 6 | 8 |

|   | MCLK カウンタ                                                | 6 | 8 |

|   | SPI SCLK カウンタ                                            | 6 | 8 |

|   | SPI 読出し/書込みエラー                                           | 6 | 9 |

|   | SPI_IGNORE エラー                                           | 6 | 9 |

|   | チェックサム保護                                                 | 6 | 9 |

|   | メモリ・マップ・チェックサム保護                                         | 6 | 9 |

|   | ROM チェックサム保護                                             | 7 | 0 |

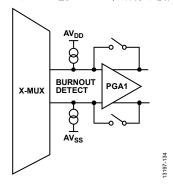

|   | バーンアウト電流                                                 | 7 | 1 |

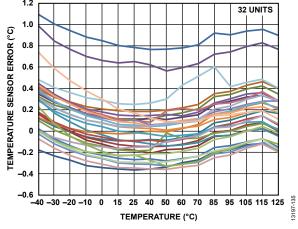

|   | 温度センサー                                                   | 7 | 1 |

| ク | 「ラウンディングとレイアウト                                           | 7 | 2 |

| ア | プリケーション情報                                                | 7 | 3 |

|   | 熱電対を使用した温度計測                                             | 7 | 3 |

|   | RTD を使用した温度計測                                            | 7 | 4 |

|   | 流量計                                                      | 7 | 6 |

| Þ | H蔵レジスタ                                                   |   |   |

|   | コミュニケーション・レジスタ                                           |   |   |

|   | ステータス・レジスタ                                               | 7 | 9 |

|   | ADC_CONTROL レジスタ                                         |   |   |

|   | データ・レジスタ                                                 |   |   |

|   | IO_CONTROL_1 レジスタ                                        |   |   |

|   | IO_CONTROL_2 レジスタ                                        | 8 |   |

|   |                                                          |   |   |

|   | ID レジスタ<br>エラー・レジスタ                                      |   |   |

| ERROR_EN レジスタ85                                                        | オフセット・レジスタ                                                                               | 91 |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----|

| MCLK_COUNT レジスタ87                                                      | ゲイン・レジスタ                                                                                 | 91 |

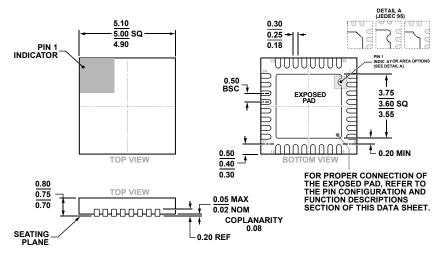

| -<br>チャンネル・レジスタ87                                                      | 外形寸法                                                                                     | 92 |

| 設定レジスタ89                                                               | オーダー・ガイド                                                                                 | 93 |

| フィルタ・レジスタ90                                                            |                                                                                          |    |

| -1                                                                     |                                                                                          |    |

| 改訂履歴                                                                   |                                                                                          |    |

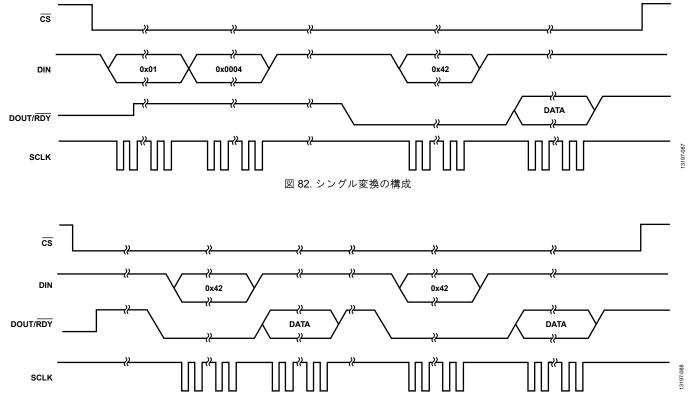

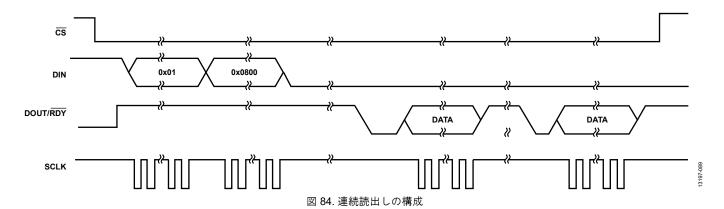

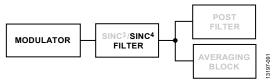

| 6/2018—Rev. C to Rev. D                                                | Changes to Single Conversion Mode Section                                                |    |

| Changes to Features Section                                            | Changes to Continuous Read Mode Section                                                  |    |

| Changes to General Description Section5                                | Changes to Sinc <sup>4</sup> Output Data Rate/Settling Time Section                      |    |

| Added Table 1; Renumbered Sequentially5                                | Changes to Sinc <sup>4</sup> Zero Latency Section                                        |    |

| Changes to Drift Parameter, External REFIN Voltage Parameter, and      | Changes to Sinc <sup>3</sup> Output Data Rate and Settling Time Section                  |    |

| Note 12, Table 38                                                      | Changes to Sinc <sup>3</sup> Zero Latency Section                                        |    |

| Changes to Table 716                                                   | Change to Output Data Rate and Settling Time, Sinc <sup>4</sup> + Sinc <sup>1</sup> File |    |

| Changes to Figure 13 and Figure 15                                     | Section                                                                                  |    |

| Changes to Figure 44, Figure 45, and Figure 4623                       | Change to Output Data Rate and Settling Time, Sinc <sup>3</sup> + Sinc <sup>1</sup> File |    |

| Changes to Reference Section                                           | Section                                                                                  |    |

| Changes to Accessing the ADC Register Map Section and Reset            | Changes to SPI_IGNORE Error Section                                                      |    |

| Column, Table 39                                                       | Added ROM Checksum Protection Section                                                    |    |

| Changes to External Impedance When Using a Gain of 1 Section46         | Changes to Table 63                                                                      |    |

| Changes to Reference Section                                           | Changes to ID Register Section and Error Register Section                                |    |

| Changes to Standby and Power-Down Modes Section                        | Changes to Table 70 and ERROR_EN Register Section                                        |    |

| Changes to Calibration Section                                         | Changes to Table 71                                                                      |    |

| Change to Sinc <sup>3</sup> Output Data Rate and Settling Time Section | Changes to Table 73                                                                      | 87 |

| Change to Calibration, Conversion, and Saturation Errors Section67     |                                                                                          |    |

| Changes to MCLK Counter Section                                        | 12/2015—Rev. A to Rev. B                                                                 |    |

| Changes to Memory Map Checksum Protection Section                      | Changed +105°C to +125°CThrough                                                          |    |

| Changes to Reset Column and Note 1, Table 64                           | Changes to Table 2                                                                       |    |

| Changes to Description Column, Table 68                                | Added Endnote 4, Table 2; Renumbered Sequentially                                        |    |

| Changes to ID Register Section                                         | Changes to Figure 17 Through Figure 22.                                                  |    |

| Changes to Description Column, Table 73                                | Changes to Figure 23 Through Figure 26                                                   |    |

| Changes to Description Column, Table 74                                | Changes to Figure 30, Figure 33, and Figure 34                                           |    |

| Changes to Configuration Registers Section                             | Changes to Figure 37 Through Figure 40                                                   |    |

| Updated Outline Dimensions                                             | Changes to Figure 41 Through Figure 46                                                   |    |

| Changes to Ordering Guide93                                            | Changes to Figure 47 and Figure 48                                                       |    |

| 7/0016 Day D to Day C                                                  |                                                                                          |    |

| 7/2016—Rev. B to Rev. C                                                | Changes to Table 17                                                                      |    |

| Change to Features Section                                             | Change to Table 17                                                                       |    |

| Changes to Specifications Section and Table 2                          | Changes to Accessing the ADC Register Map Section and                                    | 30 |

| Change to Table 8                                                      | Table 38                                                                                 | 20 |

| Changes to Table 9 and Table 10                                        | Change to Table 63                                                                       |    |

| Change to Table 25                                                     | Change to Table 03                                                                       | 70 |

| Changes to Table 28                                                    | Change to Table 73                                                                       | 02 |

| Change to Table 29                                                     | Change to Table 73                                                                       |    |

| Changes to Accessing the ADC Register Map and Table 3838               | Changes to the Ordering Guide                                                            |    |

| Changes to Accessing the ADC Register Map and Table 38                 | Changes to the Ordering Oulde                                                            | 90 |

| Added External Impedance When Using a Gain of 1 Section, Figure 74,    | 7/2015—Rev. 0 to Rev. A                                                                  |    |

| Figure 75, and Figure 76; Renumbered Sequentially45                    | Change to Data Sheet Title                                                               | 1  |

| Changes to Standby and Power-Down Modes Section                        | Changes to Internal Reference Drift Parameter, Table 2                                   |    |

| Changes to Standoy and I ower-bown blodes Section40                    | Changes to Figure 30                                                                     |    |

|                                                                        | Change to Digital Outputs Section                                                        |    |

|                                                                        | Change to Digital Outputs accitoil                                                       | 5/ |

| Change to Single Conversion Mode Section | 49 |

|------------------------------------------|----|

| Changes to Calibration Section           |    |

| Changes to Figure 83                     | 53 |

| Changes to Figure 91                     |    |

| Changes to Figure 99                     |    |

| Changes to Figure 105                    |    |

| Changes to Reference Detect Section and Figure 119 | 65 |

|----------------------------------------------------|----|

| Change to Table 70                                 | 83 |

| Changes to Table 71                                | 84 |

5/2015—Revision 0: Initial Version

# 概要

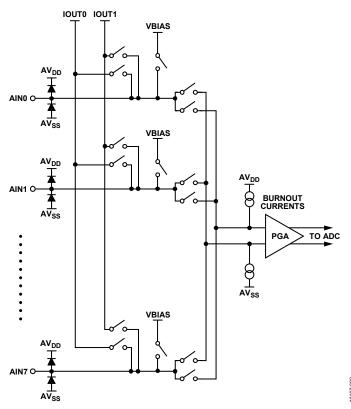

AD7124-4 は、高精度計測アプリケーション向けの低消費電力、低ノイズの完全統合型アナログ・フロントエンドです。このデバイスは、低ノイズ、24 ビット  $\Sigma$ - $\Delta$  型の A/D コンバータ(ADC) を搭載しており、4 個の差動入力または 7 個のシングルエンド入力または疑似差動入力を使用するように構成できます。オンチップの低ゲイン段により、小さな振幅の信号を直接 ADC に入力できます。

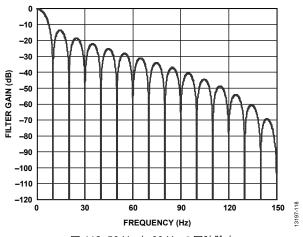

3 つの内蔵消費電力モードから選択できることが、AD7124-4 の主な利点の1つです。消費電流、出力データ・レートの範囲、およびRMSノイズは、選択した消費電力モードでカスタマイズできます。また、このデバイスは、複数のフィルタ・オプションを備えているので、優れた柔軟性を発揮します。

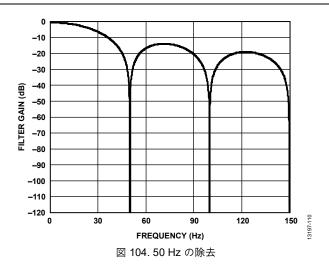

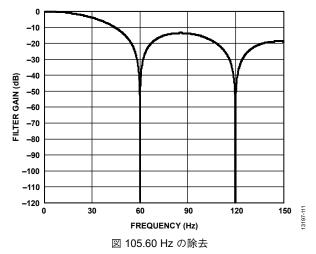

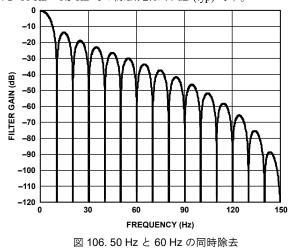

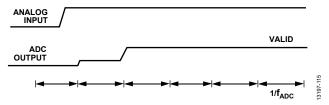

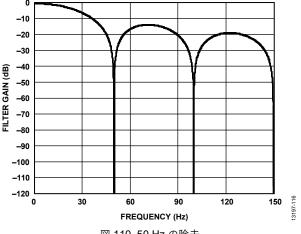

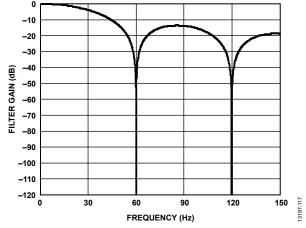

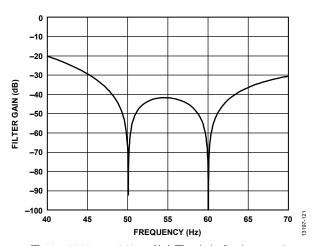

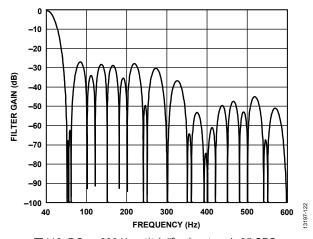

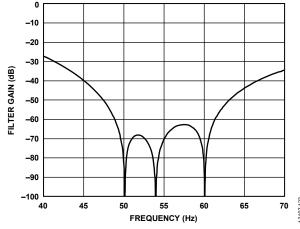

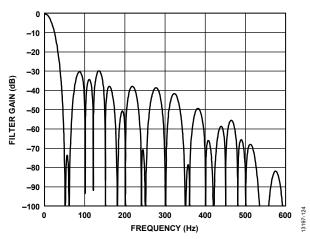

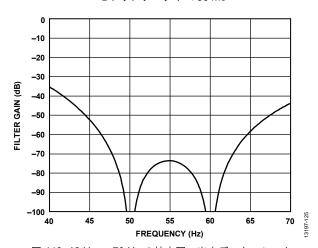

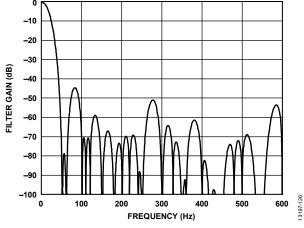

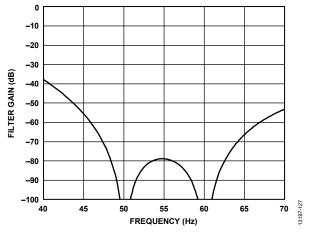

AD7124-4 では、25 SPS (シングル・サイクル・セトリング) の出力データ・レートで動作しているときに 50~Hz と60~Hz の同時除去が可能で、低い出力データ・レートでは 80~dB を超える除去比を達成できます。

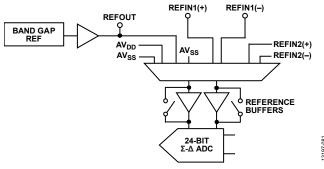

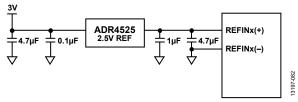

AD7124-4 により、高度なシグナル・チェーン集積化を実現できます。このデバイスは、高精度、低ノイズ、低ドリフトの内部バンド・ギャップ・リファレンスを備えており、内蔵のバッファを使用した外部差動リファレンスにも対応しています。その他の主な内蔵機能として、プログラマブルの低ドリフト励起電流源、バーンアウト電流、チャンネルのコモンモード電圧を AVDO2 に設定するバイアス電圧発生器があります。ローサイド・パワー・スイッチにより、変換と変換の間にブリッジ・センサーへの電力供給を停止でき、システムの消費電力を最小限に抑えることができます。また、内部クロックまたは外部クロックでデバイスを動作させることが可能です。

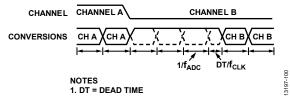

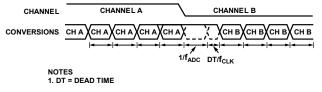

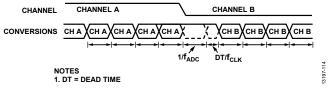

内蔵チャンネル・シーケンサにより、複数のチャンネルを同時にイネーブルに設定できます。これにより、AD7124-4 は、イネーブルにされた各チャンネルで順番に変換を実行するので、デバイスとの通信がシンプルになります。アナログ入力のほかに、電源チェックやリファレンス・チェックなどの診断用に定義され

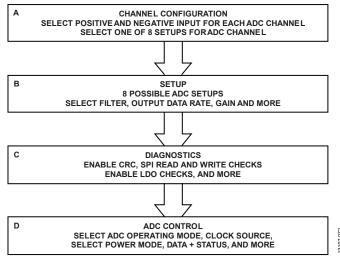

た最大 16 個のチャンネルを同時にイネーブルに設定できます。この独自の機能により、診断機能と AD 変換をインターリーブすることができます。 AD7124-4 は、チャンネルごとの設定もサポートしています。このデバイスでは、8 つの設定またはセットアップが可能です。各設定は、ゲイン、フィルタ・タイプ、出力データ・レート、バッファリング、リファレンス電源で構成されます。これらのセットアップをチャンネルごとに割り当てることができます。

AD7124-4 には、充実した機能セットの一部として広範な診断機能も備えています。これらの診断機能には、巡回冗長性チェック (CRC)、シグナル・チェーン・チェック、シリアル・インターフェース・チェックが含まれ、より信頼性の高いソリューションになっています。これらの診断機能により、診断用の外付け部品数を削減でき、必要なボード・スペース、設計時間、およびコストを節約できます。IEC 61508 に従って実施した、代表的なアプリケーションの故障モードの影響と診断解析(FMEDA) において、安全側故障割合(SFF)は 90%を超える値を示しました。

このデバイスは、 $2.7 \, \text{V} \sim 3.6 \, \text{V}$  のアナログ単電源または  $1.8 \, \text{V}$  の両電源で動作します。デジタル電源の範囲は  $1.65 \, \text{V} \sim 3.6 \, \text{V}$  です。仕様温度範囲は  $40 \, \text{C} \sim +125 \, \text{C}$  です。AD7124-4 には、 $32 \, \text{C}$  LFCSP パッケージと  $24 \, \text{C}$  ンTSSOP パッケージが採用されています。

このデータシートでは、DOUT/RDYなどの複数の機能を備えたピンをすべてのピン名で表記しますが、特定の機能のみが該当するような説明箇所ではRDYのようにピンの1つの機能で表記しています。

AD7124-4 B グレードは、動作および性能に関して AD7124-4 といくつか異なる点があります。表 1 に相違点を示します。特に指定のない限り、AD7124-4 という表記はすべてこのデバイスを指すものであり、B グレードを指すものではありません。

表 1. AD7124-4 と AD7124-4 B グレードの相違点

| X               | 1 5 指定派                       |                                |

|-----------------|-------------------------------|--------------------------------|

| パラメータ           | AD7124-4                      | AD7124-4 B グレード                |

| LFCSP パッケージの高さ  | 0.75 mm                       | 0.95 mm                        |

| 内部リファレンスのドリフト   | 15 ppm/°C                     | 10 ppm/°C                      |

| スタンバイ・モードでの励起電流 | ディスエーブル                       | イネーブルの場合は、アクティブ状態を維持           |

| ゲイン1、高インピーダンス負荷 | チャンネル切り替え時のセトリング・タイム<br>に影響する | チャンネル切り替え時のセトリング・タイムに影響し<br>ない |

### 表 2. AD7124-4 の概要

| Parameter                                      | Low Power Mode | Mid Power Mode | Full Power Mode |

|------------------------------------------------|----------------|----------------|-----------------|

| Maximum Output Data Rate                       | 2400 SPS       | 4800 SPS       | 19,200 SPS      |

| RMS Noise (Gain = 128)                         | 24 nV          | 20 nV          | 23 nV           |

| Peak-to-Peak Resolution at 1200 SPS (Gain = 1) | 16.4 bits      | 17.1 bits      | 18 bits         |

| Typical Current (ADC + PGA)                    | 255 μΑ         | 355 μΑ         | 930 μΑ          |

Rev. D - 5/93 -

# 仕様

$AV_{DD}$ =2.9 V  $\sim$ 3.6 V (通常消費電力モード)、2.7 V  $\sim$ 3.6 V (中消費電力および低消費電力モード)、 $IOV_{DD}$ =1.65 V  $\sim$ 3.6 V、 $AV_{SS}$ =DGND=0 V、REFINx (+) = 2.5 V、REFINx (-) =  $AV_{SS}$ 、マスター・クロック = 614.4 kHz。特に指定のない限り、すべての仕様は  $T_{MIN}$   $\sim$   $T_{MAX}$  です。

表 3.

| Parameter <sup>1</sup>                                    | Min     | Тур         | Max     | Unit       | Test Conditions/Comments                            |

|-----------------------------------------------------------|---------|-------------|---------|------------|-----------------------------------------------------|

| ADC                                                       |         |             |         |            |                                                     |

| Output Data Rate, f <sub>ADC</sub>                        |         |             |         |            |                                                     |

| Low Power Mode                                            | 1.17    |             | 2400    | SPS        |                                                     |

| Mid Power Mode                                            | 2.34    |             | 4800    | SPS        |                                                     |

| Full Power Mode                                           | 9.38    |             | 19,200  | SPS        |                                                     |

| No Missing Codes <sup>2</sup>                             | 24      |             | ,       | Bits       | FS <sup>3</sup> > 2, sinc <sup>4</sup> filter       |

|                                                           | 24      |             |         | Bits       | $FS^3 > 8$ , sinc <sup>3</sup> filter               |

| Resolution                                                |         |             |         | J. I.      | See the RMS Noise and Resolution                    |

| RMS Noise and Update Rates                                |         |             |         |            | section See the RMS Noise and Resolution            |

|                                                           |         |             |         |            | section                                             |

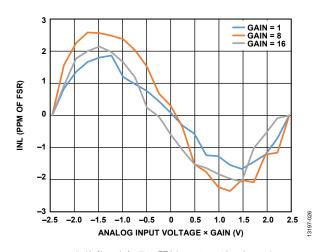

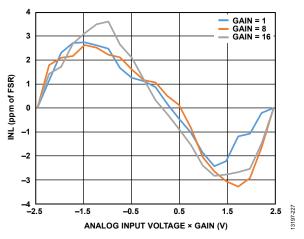

| Integral Nonlinearity (INL)                               | -4      | ±1          | +4      | ppm of FSR | $Gain = 1^2$                                        |

|                                                           | -15     | ±2          | +15     | ppm of FSR | Gain > 1 <sup>4</sup>                               |

| Offset Error <sup>5</sup>                                 |         |             |         |            |                                                     |

| Before Calibration                                        |         | ±15         |         | $\mu V$    | Gain = 1 to 8                                       |

|                                                           |         | 200/gain    |         | $\mu V$    | Gain = 16 to 128                                    |

| After Internal Calibration/System                         |         | In order of |         |            |                                                     |

| Calibration                                               |         | noise       |         |            |                                                     |

| Offset Error Drift vs. Temperature <sup>6</sup>           |         |             |         |            |                                                     |

| Low Power Mode                                            |         | 10          |         | nV/°C      | Gain = 1  or  gain > 16                             |

|                                                           |         | 80          |         | nV/°C      | Gain = 2  to  8                                     |

|                                                           |         | 40          |         | nV/°C      | Gain = 16                                           |

| Mid Power Mode                                            |         | 10          |         | nV/°C      | Gain = 1  or  gain > 16                             |

|                                                           |         | 40          |         | nV/°C      | Gain = 2  to  8                                     |

|                                                           |         | 20          |         | nV/°C      | Gain = 16                                           |

| Full Power Mode                                           |         | 10          |         | nV/°C      |                                                     |

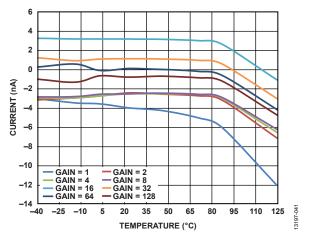

| Gain Error <sup>5, 7</sup>                                |         |             |         |            |                                                     |

| Before Internal Calibration                               | -0.0025 |             | +0.0025 | %          | Gain = 1, $T_A = 25$ °C                             |

|                                                           |         | -0.3        |         | %          | Gain > 1                                            |

| After Internal Calibration                                | -0.016  | +0.004      | +0.016  | %          | Gain = 2 to 8, $T_A = 25^{\circ}C$                  |

|                                                           |         | $\pm 0.025$ |         | %          | Gain = 16 to 128                                    |

| After System Calibration                                  |         | In order of |         |            |                                                     |

| G: F D:0 T                                                |         | noise       | 2       | /0.0       |                                                     |

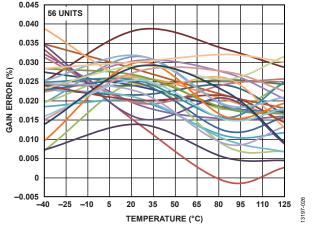

| Gain Error Drift vs. Temperature                          |         | 1           | 2       | ppm/°C     | 137/                                                |

| Power Supply Rejection                                    | 0.7     |             |         | ID.        | $A_{IN} = 1$ V/gain, external reference             |

| Low Power Mode                                            | 87      |             |         | dB         | Gain = 2 to 16                                      |

| VC1D VC12                                                 | 96      |             |         | dB         | Gain = 1 or gain > 16                               |

| Mid Power Mode <sup>2</sup>                               | 92      |             |         | dB         | Gain = 2 to 16                                      |

|                                                           | 100     |             |         | dB         | Gain = 1  or  gain > 16                             |

| Full Power Mode                                           | 99      |             |         | dB         |                                                     |

| Common-Mode Rejection <sup>8</sup>                        |         |             |         |            |                                                     |

| At DC <sup>2</sup>                                        | 85      | 90          |         | dB         | $A_{IN} = 1$ V, gain = 1                            |

|                                                           | 105     | 115         |         | dB         | $A_{IN} = 1$ V/gain, gain 2 or 4                    |

|                                                           | 1029,2  |             |         | dB         | $A_{IN} = 1$ V/gain, gain 2 or 4                    |

|                                                           | 115     | 120         |         | dB         | $A_{IN} = 1 \text{ V/gain, gain} \ge 8$             |

|                                                           | 1059, 2 |             |         | dB         | $A_{IN} = 1 \text{ V/gain, gain} \ge 8$             |

| Sinc <sup>3</sup> , Sinc <sup>4</sup> Filter <sup>2</sup> |         |             |         |            |                                                     |

| At 50 Hz, 60 Hz                                           | 120     |             |         | dB         | 10 SPS, 50 Hz $\pm$ 1 Hz, 60 Hz $\pm$ 1 H           |

| At 50 Hz                                                  | 120     |             |         | dB         | $50 \text{ SPS}$ , $50 \text{ Hz} \pm 1 \text{ Hz}$ |

| At 60 Hz                                                  | 120     |             |         | dB         | $60 \text{ SPS}, 60 \text{ Hz} \pm 1 \text{ Hz}$    |

Rev. D - 6/93 -

| Parameter <sup>1</sup>                               | Min Ty           | p Max                  | Unit | Test Conditions/Comments                                                         |

|------------------------------------------------------|------------------|------------------------|------|----------------------------------------------------------------------------------|

| Fast Settling Filters <sup>2</sup>                   |                  |                        |      |                                                                                  |

| At 50 Hz                                             | 115              |                        | dB   | First notch at 50 Hz, 50 Hz ± 1 Hz                                               |

| At 60 Hz                                             | 115              |                        | dB   | First notch at 60 Hz, 60 Hz ± 1 Hz                                               |

| Post Filters <sup>2</sup>                            |                  |                        |      |                                                                                  |

| At 50 Hz, 60 Hz                                      | 130              |                        | dB   | 20 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                                               |

|                                                      | 130              |                        | dB   | 25 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                                               |

| Normal Mode Rejection <sup>2</sup>                   |                  |                        |      |                                                                                  |

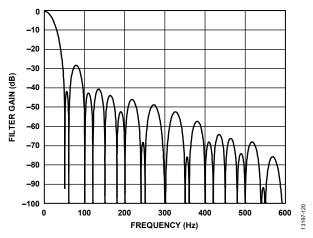

| Sinc <sup>4</sup> Filter                             |                  |                        |      |                                                                                  |

| External Clock                                       |                  |                        |      |                                                                                  |

| At 50 Hz, 60 Hz                                      | 120              |                        | dB   | 10 SPS, 50 Hz $\pm$ 1 Hz, 60 Hz $\pm$ 1 Hz                                       |

| 11000 1111, 00 1111                                  | 80               |                        | dB   | 50 SPS, REJ60 <sup>10</sup> =1, 50 Hz $\pm$ 1 Hz,                                |

|                                                      | 00               |                        | dD . | 60 Hz ± 1 Hz                                                                     |

| At 50 Hz                                             | 120              |                        | dB   | $50 \text{ SPS}, 50 \text{ Hz} \pm 1 \text{ Hz}$                                 |

| At 60 Hz                                             | 120              |                        | dB   | 60 SPS, 60 Hz ± 1 Hz                                                             |

| Internal Clock                                       |                  |                        |      | 1                                                                                |

| At 50 Hz, 60 Hz                                      | 98               |                        | dB   | 10 SPS, 50 Hz $\pm$ 1 Hz, 60 Hz $\pm$ 1 Hz                                       |

| 11000 1111, 00 1111                                  | 66               |                        | dB   | 50 SPS, REJ $60^{10} = 1,50 \text{ Hz} \pm 1 \text{ Hz},$                        |

|                                                      |                  |                        | u.b  | 60 Hz ± 1 Hz                                                                     |

| At 50 Hz                                             | 92               |                        | dB   | 50 SPS, 50 Hz ± 1 Hz                                                             |

| At 60 Hz                                             | 92               |                        | dB   | 60 SPS, 60 Hz ± 1 Hz                                                             |

| Sinc <sup>3</sup> Filter                             | /-               |                        |      | 00 51 5, 00 111 = 1 111                                                          |

| External Clock                                       |                  |                        |      |                                                                                  |

| At 50 Hz, 60 Hz                                      | 100              |                        | dB   | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                                               |

| 711 30 112, 00 112                                   | 65               |                        | dB   | 50 SPS, REJ $60^{10} = 1$ , 50 Hz $\pm 1$ Hz,                                    |

|                                                      | 03               |                        | ub   | 60 Hz ± 1 Hz                                                                     |

| At 50 Hz                                             | 100              |                        | dB   | $50 \text{ SPS}, 50 \text{ Hz} \pm 1 \text{ Hz}$                                 |

| At 60 Hz                                             | 100              |                        | dB   | 60 SPS, 60 Hz ± 1 Hz                                                             |

| Internal Clock                                       | 100              |                        | ub   | 00 51 5, 00 112 ± 1 112                                                          |

| At 50 Hz, 60 Hz                                      | 73               |                        | dB   | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                                               |

| At 50 Hz, 60 Hz                                      | 52               |                        | dB   | $50 \text{ SPS}, \text{ REJ}60^{10} = 1, 50 \text{ Hz} \pm 1 \text{ Hz},$        |

|                                                      | 32               |                        | uБ   | 60 Hz ± 1 Hz                                                                     |

| At 50 Hz                                             | 68               |                        | dB   | 50 SPS, 50 Hz ± 1 Hz                                                             |

| At 60 Hz                                             | 68               |                        | dB   | 60 SPS, 60 Hz ± 1 Hz                                                             |

| Fast Settling Filters                                | 00               |                        | ub   | 00 51 5, 00 112 ± 1 112                                                          |

| External Clock                                       |                  |                        |      |                                                                                  |

| At 50 Hz                                             | 40               |                        | dB   | Einst motels at 50 Hz 50 Hz 1 0 5 Hz                                             |

|                                                      | 40               |                        |      | First notch at 50 Hz, 50 Hz ± 0.5 Hz                                             |

| At 60 Hz                                             | 40               |                        | dB   | First notch at 60 Hz, 60 Hz $\pm$ 0.5 Hz                                         |

| Internal Clock                                       | 24.5             |                        | 175  |                                                                                  |

| At 50 Hz                                             | 24.5             |                        | dB   | First notch at 50 Hz, 50 Hz $\pm$ 0.5 Hz                                         |

| At 60 Hz                                             | 24.5             |                        | dB   | First notch at 60 Hz, 60 Hz $\pm$ 0.5 Hz                                         |

| Post Filters                                         |                  |                        |      |                                                                                  |

| External Clock                                       |                  |                        |      |                                                                                  |

| At 50 Hz, 60 Hz                                      | 86               |                        | dB   | $20 \text{ SPS}, 50 \text{ Hz} \pm 1 \text{ Hz}, 60 \text{ Hz} \pm 1 \text{ Hz}$ |

|                                                      | 62               |                        | dB   | 25 SPS, 50 Hz $\pm$ 1 Hz, 60 Hz $\pm$ 1 Hz                                       |

| Internal Clock                                       |                  |                        |      |                                                                                  |

| At 50 Hz, 60 Hz                                      | 67               |                        | dB   | 20 SPS, 50 Hz $\pm$ 1 Hz, 60 Hz $\pm$ 1 Hz                                       |

|                                                      | 50               |                        | dB   | 25 SPS, 50 Hz $\pm$ 1 Hz, 60 Hz $\pm$ 1 Hz                                       |

| ANALOG INPUTS <sup>11</sup>                          |                  |                        |      |                                                                                  |

| Differential Input Voltage Ranges 12                 | ±V               | r <sub>REF</sub> /gain | V    | $V_{REF} = REFINx(+) - REFINx(-)$ , or internal reference                        |

| Absolute A <sub>IN</sub> Voltage Limits <sup>2</sup> |                  |                        |      |                                                                                  |

| Gain = 1 (Unbuffered)                                | $AV_{SS} - 0.05$ | $AV_{DD} + 0.05$       | V    |                                                                                  |

| Gain = 1 (Buffered)                                  | $AV_{SS} + 0.1$  | $AV_{DD} - 0.1$        | V    |                                                                                  |

| Gain > 1                                             | $AV_{SS} - 0.05$ | $AV_{DD} + 0.05$       | V    |                                                                                  |

Rev. D - 7/93 -

| Parameter <sup>1</sup>                     | Min              | Тур   | Max              | Unit        | Test Conditions/Comments                 |

|--------------------------------------------|------------------|-------|------------------|-------------|------------------------------------------|

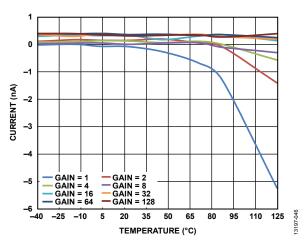

| Analog Input Current                       |                  |       |                  |             |                                          |

| Gain > 1 or $Gain = 1$ (Buffered)          |                  |       |                  |             |                                          |

| Low Power Mode                             |                  |       |                  |             |                                          |

| Absolute Input Current                     |                  | ±1    |                  | nA          |                                          |

| Differential Input Current                 |                  | ±0.2  |                  | nA          |                                          |

| Analog Input Current Drift                 |                  | 25    |                  | pA/°C       |                                          |

| Mid Power Mode                             |                  |       |                  |             |                                          |

| Absolute Input Current                     |                  | ±1.2  |                  | nA          |                                          |

| Differential Input Current                 |                  | ±0.4  |                  | nA          |                                          |

| Analog Input Current Drift                 |                  | 25    |                  | pA/°C       |                                          |

| Full Power Mode                            |                  |       |                  | 1           |                                          |

| Absolute Input Current                     |                  | ±3.3  |                  | nA          |                                          |

| Differential Input Current                 |                  | ±1.5  |                  | nA          |                                          |

| Analog Input Current Drift                 |                  | 25    |                  | pA/°C       |                                          |

| Gain = 1 (Unbuffered)                      |                  | 20    |                  | p. z. c     | Current varies with input voltage        |

| Absolute Input Current                     |                  | ±2.65 |                  | μA/V        | Current varies with input voltage        |

| Analog Input Current Drift                 |                  | 1.1   |                  | nA/V/°C     |                                          |

| REFERENCE INPUT                            |                  | 1.1   |                  | III U VI C  |                                          |

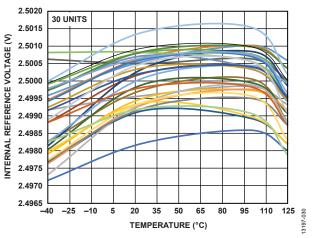

| Internal Reference                         |                  |       |                  |             |                                          |

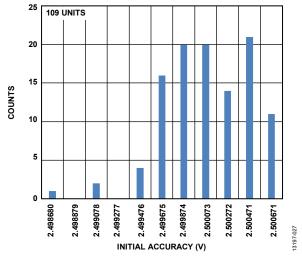

| Initial Accuracy                           | 2.5 - 0.2%       | 2.5   | 2.5 + 0.2%       | V           | $T_A = 25^{\circ}C$                      |

| Drift                                      | 2.3 0.270        | 2.3   | 10               | ppm/°C      | TSSOP                                    |

| AD7124-4                                   |                  | 2     | 15               | ppm/°C      | LFCSP                                    |

| AD7124-4<br>AD7124-4 B Grade               |                  | 2     | 10               | ppm/°C      | LFCSP                                    |

| Output Current                             |                  | ۷     | 10               | mA          | LICSF                                    |

| -                                          |                  | 50    | 10               |             |                                          |

| Load Regulation                            |                  | 85    |                  | μV/mA<br>dB |                                          |

| Power Supply Rejection                     |                  | 83    |                  | uБ          |                                          |

| External Reference                         | 0.5              | 2.5   | A 3.7            | V           | DEEDI - DEEDI-(1) DEEDI-(1)              |

| External REFIN Voltage <sup>2</sup>        | $AV_{SS} - 0.05$ | 2.5   | $AV_{DD}$        | V           | REFIN = REFINx(+) - REFINx(-) Unbuffered |

| Absolute REFIN Voltage Limits <sup>2</sup> |                  |       | $AV_{DD} + 0.05$ |             | Buffered                                 |

| P.C. I. (C. )                              | $AV_{SS} + 0.1$  |       | $AV_{DD} - 0.1$  | V           | Bullered                                 |

| Reference Input Current                    |                  |       |                  |             |                                          |

| Buffered                                   |                  |       |                  |             |                                          |

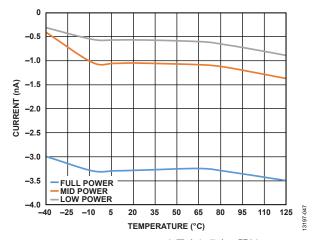

| Low Power Mode                             |                  | .0.7  |                  |             |                                          |

| Absolute Input Current                     |                  | ±0.5  |                  | nA          |                                          |

| Reference Input Current Drift              |                  | 10    |                  | pA/°C       |                                          |

| Mid Power Mode                             |                  |       |                  |             |                                          |

| Absolute Input Current                     |                  | ±1    |                  | nA          |                                          |

| Reference Input Current Drift              |                  | 10    |                  | pA/°C       |                                          |

| Full Power Mode                            |                  |       |                  |             |                                          |

| Absolute Input Current                     |                  | ±3    |                  | nA          |                                          |

| Reference Input Current Drift              |                  | 10    |                  | pA/°C       |                                          |

| Unbuffered                                 |                  |       |                  |             |                                          |

| Absolute Input Current                     |                  | ±12   |                  | μΑ          |                                          |

| Reference Input Current Drift              |                  | 6     |                  | nA/°C       |                                          |

| Normal Mode Rejection                      |                  |       |                  |             | Same as for analog inputs                |

| Common-Mode Rejection                      |                  | 100   |                  | dB          |                                          |

Rev. D - 8/93 -

| Parameter <sup>1</sup>                         | Min                    | Тур                               | Max                   | Unit     | Test Conditions/Comments                                                                                         |

|------------------------------------------------|------------------------|-----------------------------------|-----------------------|----------|------------------------------------------------------------------------------------------------------------------|

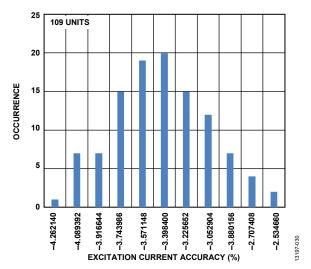

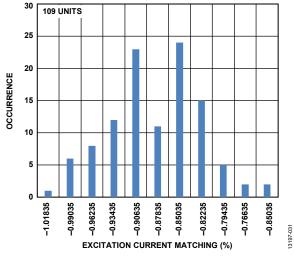

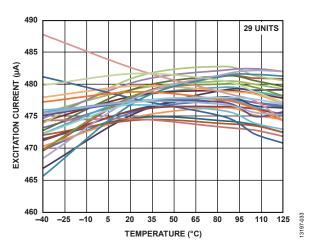

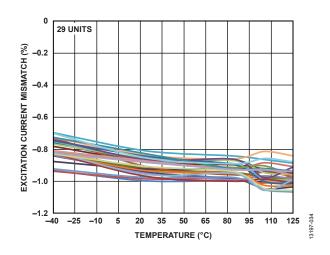

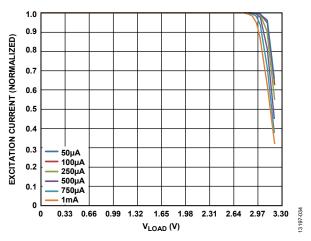

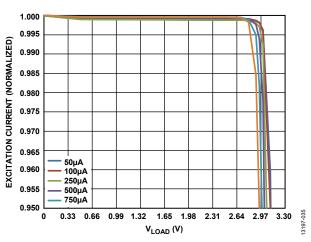

| EXCITATION CURRENT SOURCES                     |                        |                                   |                       |          | Available on any analog input pin                                                                                |

| (IOUT0/IOUT1)                                  |                        |                                   |                       |          |                                                                                                                  |

| Output Current                                 |                        | 50/100/250/<br>500/750/1000       |                       | μΑ       |                                                                                                                  |

| Initial Tolerance                              |                        | ±4                                |                       | %        | $T_A = 25^{\circ}C$                                                                                              |

| Drift                                          |                        | 50                                |                       | ppm/°C   |                                                                                                                  |

| Current Matching                               |                        | ±0.5                              |                       | %        | Matching between IOUT0 and IOUT1, V <sub>OUT</sub> = 0 V                                                         |

| Drift Matching <sup>2</sup>                    |                        | 5                                 | 30                    | ppm/°C   |                                                                                                                  |

| Line Regulation (AV <sub>DD</sub> )            |                        | 2                                 |                       | %/V      | $AV_{DD} = 3 V \pm 5\%$                                                                                          |

| Load Regulation                                |                        | 0.2                               |                       | %/V      |                                                                                                                  |

| Output Compliance <sup>2</sup>                 | $AV_{SS} - 0.05$       |                                   | $AV_{DD}-0.37$        | V        | 50 μΑ/100 μΑ/250 μΑ/500 μΑ                                                                                       |

|                                                | $AV_{SS} - 0.05$       |                                   | $AV_{DD} - 0.48$      | V        | current sources, 2% accuracy 750 µA and 1000 µA current sources,                                                 |

| DIAGNOLTA CE (II. ) CENERATOR                  |                        |                                   |                       |          | 2% accuracy                                                                                                      |

| BIAS VOLTAGE ( $V_{BIAS}$ ) GENERATOR          |                        | ATT . (ATT                        |                       | **       | Available on any analog input pin                                                                                |

| $ m V_{BIAS}$                                  |                        | $AV_{SS} + (AV_{DD} - AV_{SS})/2$ |                       | V        |                                                                                                                  |

| $V_{\scriptsize BIAS}$ Generator Start-Up Time |                        | 6.7                               |                       | μs/nF    | Dependent on the capacitance connected to AINx                                                                   |

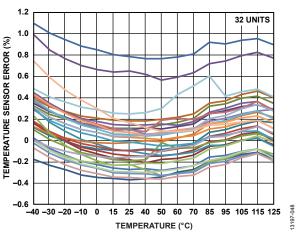

| TEMPERATURE SENSOR                             |                        |                                   |                       |          |                                                                                                                  |

| Accuracy                                       |                        | ±0.5                              |                       | °C       |                                                                                                                  |

| Sensitivity                                    |                        | 13,584                            |                       | Codes/°C |                                                                                                                  |

| LOW-SIDE POWER SWITCH                          |                        |                                   |                       |          |                                                                                                                  |

| On Resistance (R <sub>ON</sub> )               |                        | 7                                 | 10                    | Ω        |                                                                                                                  |

| Allowable Current <sup>2</sup>                 |                        |                                   | 30                    | mA       | Continuous current                                                                                               |

| BURNOUT CURRENTS                               |                        |                                   |                       |          |                                                                                                                  |

| A <sub>IN</sub> Current                        |                        | 0.5/2/4                           |                       | μA       | Analog inputs must be buffered                                                                                   |

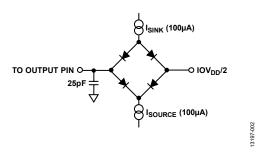

| DIGITAL OUTPUTS (P1 AND P2)                    |                        |                                   |                       |          |                                                                                                                  |

| Output Voltage                                 |                        |                                   |                       |          |                                                                                                                  |

| High, V <sub>OH</sub>                          | $AV_{DD} - 0.6$        |                                   |                       | V        | $I_{SOURCE} = 100 \mu A$                                                                                         |

| Low, V <sub>OL</sub>                           |                        |                                   | 0.4                   | V        | $I_{SINK} = 100 \mu A$                                                                                           |

| DIAGNOSTICS                                    |                        |                                   |                       |          |                                                                                                                  |

| Power Supply Monitor Detect Level              |                        |                                   |                       |          |                                                                                                                  |

| Analog Low Dropout Regulator (ALDO)            |                        |                                   | 1.6                   | V        | $AV_{DD} - AV_{SS} \ge 2.7 \text{ V}$                                                                            |

| Digital LDO (DLDO)                             |                        |                                   | 1.55                  | V        | $IOV_{DD} \ge 1.75 \text{ V}$                                                                                    |

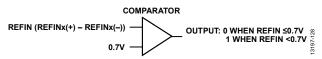

| Reference Detect Level                         | 0.7                    |                                   | 1                     | V        | REF_DET_ERR bit active if V <sub>REF</sub> < 0.7 V                                                               |

| AINM/AINP Overvoltage Detect Level             | $AV_{DD} + 0.04$       |                                   |                       | V        |                                                                                                                  |

| AINM/AINP Undervoltage Detect Level            |                        |                                   | $AV_{SS} - 0.04$      | V        |                                                                                                                  |

| INTERNAL/EXTERNAL CLOCK                        |                        |                                   |                       |          |                                                                                                                  |

| Internal Clock                                 |                        |                                   |                       |          |                                                                                                                  |

| Frequency                                      | 614.4 - 5%             | 614.4                             | 614.4 + 5%            | kHz      |                                                                                                                  |

| Duty Cycle                                     |                        | 50:50                             |                       | %        |                                                                                                                  |

| External Clock                                 |                        |                                   |                       |          |                                                                                                                  |

| Frequency                                      |                        | 2.4576                            |                       | MHz      | Internal divide by 4                                                                                             |

| Duty Cycle Range                               |                        | 45:55 to 55:45                    |                       | %        |                                                                                                                  |

| LOGIC INPUTS <sup>2</sup>                      |                        |                                   |                       |          |                                                                                                                  |

| Input Voltage                                  |                        |                                   |                       |          |                                                                                                                  |

| Low, $V_{INL}$                                 |                        |                                   | $0.3 \times IOV_{DD}$ | V        | $1.65 \text{ V} \le \text{IOV}_{\text{DD}} < 1.9 \text{ V}$                                                      |

|                                                |                        |                                   | 0.35 ×                | V        | $1.9 \text{ V} \leq \text{IOV}_{\text{DD}} < 2.3 \text{ V}$                                                      |

|                                                |                        |                                   | $IOV_{DD}$            | ***      | 224 2104 2264                                                                                                    |

| TT: 1 X/                                       | 0.7 1011               |                                   | 0.7                   | V        | $2.3 \text{ V} \leq \text{IOV}_{\text{DD}} \leq 3.6 \text{ V}$                                                   |

| High, $V_{INH}$                                | $0.7 \times IOV_{DD}$  |                                   |                       | V        | $1.65 \text{ V} \le \text{IOV}_{\text{DD}} < 1.9 \text{ V}$                                                      |

|                                                | $0.65 \times IOV_{DD}$ |                                   |                       | V        | $1.9 \text{ V} \leq \text{IOV}_{\text{DD}} < 2.3 \text{ V}$                                                      |

|                                                | 1.7                    |                                   |                       | V        | $2.3 \text{ V} \le \text{IOV}_{DD} < 2.7 \text{ V}$                                                              |

|                                                | 2                      |                                   |                       | V        | $2.7 \text{ V} \le \text{IOV}_{DD} \le 2.7 \text{ V}$<br>$2.7 \text{ V} \le \text{IOV}_{DD} \le 3.6 \text{ V}$   |

| Hysteresis                                     | 0.2                    |                                   | 0.6                   | V        | $1.65 \text{ V} \le \text{IOV}_{DD} \le 3.6 \text{ V}$<br>$1.65 \text{ V} \le \text{IOV}_{DD} \le 3.6 \text{ V}$ |

| Input Currents                                 | -1                     |                                   | +1                    |          | $V_{IN} = IOV_{DD}$ or GND                                                                                       |

| Input Capacitance                              | 1                      | 10                                | 1 1                   | μA<br>pF | $V_{IN} = IOV_{DD}$ or GND All digital inputs                                                                    |

| піриі Сараспансе                               |                        | 10                                |                       | hr.      | An uignai inpuis                                                                                                 |

Rev. D - 9/93 -

| Parameter <sup>1</sup>                                       | Min                      | Тур           | Max              | Unit | Test Conditions/Comments                                                                    |

|--------------------------------------------------------------|--------------------------|---------------|------------------|------|---------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS (INCLUDING CLK)                                |                          |               |                  |      |                                                                                             |

| Output Voltage <sup>2</sup>                                  |                          |               |                  |      |                                                                                             |

| High, V <sub>OH</sub>                                        | IOV <sub>DD</sub> - 0.35 |               |                  | V    | $I_{SOURCE} = 100 \ \mu A$                                                                  |

| Low, $V_{OL}$                                                |                          |               | 0.4              | V    | $I_{SINK} = 100 \mu A$                                                                      |

| Floating State Leakage Current                               | -1                       |               | +1               | μΑ   |                                                                                             |

| Floating State Output Capacitance                            |                          | 10            |                  | pF   |                                                                                             |

| Data Output Coding                                           |                          | Offset binary |                  |      |                                                                                             |

| SYSTEM CALIBRATION <sup>2</sup>                              |                          | -             |                  |      |                                                                                             |

| Calibration Limit                                            |                          |               |                  |      |                                                                                             |

| Full Scale (FS)                                              |                          |               | $1.05 \times FS$ | V    |                                                                                             |

| Zero Scale                                                   | $-1.05 \times FS$        |               |                  | V    |                                                                                             |

| Input Span                                                   | $0.8 \times FS$          |               | $2.1 \times FS$  | V    |                                                                                             |

| POWER SUPPLY VOLTAGES FOR ALL POWER MODES                    |                          |               |                  |      |                                                                                             |

| $AV_{DD}$ to $AV_{SS}$                                       |                          |               |                  |      |                                                                                             |

| Low Power Mode                                               | 2.7                      |               | 3.6              | V    |                                                                                             |

| Mid Power Mode                                               | 2.7                      |               | 3.6              | V    |                                                                                             |

| Full Power Mode                                              | 2.9                      |               | 3.6              | V    |                                                                                             |

| IOV <sub>DD</sub> to GND                                     | 1.65                     |               | 3.6              | V    |                                                                                             |

| AV <sub>SS</sub> to GND                                      | -1.8                     |               | 0                | V    |                                                                                             |

| IOV <sub>DD</sub> to AV <sub>SS</sub>                        |                          |               | 5.4              | V    |                                                                                             |

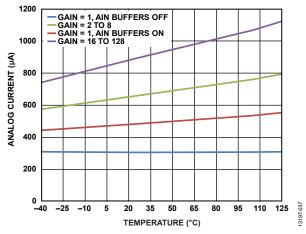

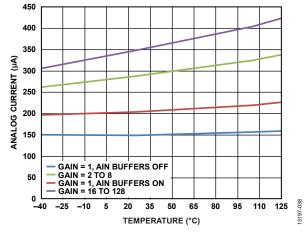

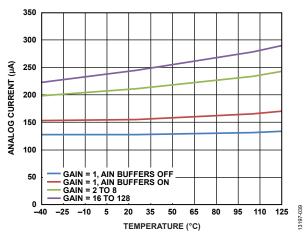

| POWER SUPPLY CURRENTS <sup>11, 13</sup>                      |                          |               |                  |      |                                                                                             |

| I <sub>AVDD</sub> , External Reference                       |                          |               |                  |      |                                                                                             |

| Low Power Mode                                               |                          |               |                  |      |                                                                                             |

| $Gain = 1^2$                                                 |                          | 125           | 140              | μA   | All buffers off                                                                             |

| Gain = $1 I_{AVDD}$ Increase per AINx Buffer <sup>2</sup>    |                          | 15            | 25               | μA   |                                                                                             |

| Gain = 2 to 8                                                |                          | 205           | 250              | μA   |                                                                                             |

| Gain = 16 to 128                                             |                          | 235           | 300              | μA   |                                                                                             |

| I <sub>AVDD</sub> Increase per Reference Buffer <sup>2</sup> |                          | 10            | 20               | μA   | All gains                                                                                   |

| Mid Power Mode                                               |                          |               |                  | '    |                                                                                             |

| $Gain = 1^2$                                                 |                          | 150           | 170              | μА   | All buffers off                                                                             |

| Gain = $1 I_{AVDD}$ Increase per AINx Buffer <sup>2</sup>    |                          | 30            | 40               | μΑ   |                                                                                             |

| Gain = $2 \text{ to } 8$                                     |                          | 275           | 345              | μA   |                                                                                             |

| Gain = 16 to 128                                             |                          | 330           | 430              | μA   |                                                                                             |

| I <sub>AVDD</sub> Increase per Reference Buffer <sup>2</sup> |                          | 20            | 30               | μA   | All gains                                                                                   |

| Full Power Mode                                              |                          |               |                  | '    |                                                                                             |

| $Gain = 1^2$                                                 |                          | 315           | 350              | μА   | All buffers off                                                                             |

| Gain = $1 I_{AVDD}$ Increase per AINx Buffer <sup>2</sup>    |                          | 90            | 135              | μA   |                                                                                             |

| Gain = 2  to  8                                              |                          | 660           | 830              | μA   |                                                                                             |

| Gain = $16$ to $128$                                         |                          | 875           | 1200             | μA   |                                                                                             |

| I <sub>AVDD</sub> Increase per Reference Buffer <sup>2</sup> |                          | 85            | 120              | μA   | All gains                                                                                   |

| I <sub>AVDD</sub> Increase                                   |                          |               |                  |      |                                                                                             |

| Due to Internal Reference <sup>2</sup>                       |                          | 50            | 70               | μА   | Independent of power mode; the reference buffers are not required when using this reference |

| Due to V <sub>BIAS</sub> <sup>2</sup>                        |                          | 15            | 20               | μΑ   | Independent of power mode                                                                   |

| Due to Diagnostics <sup>2</sup>                              |                          | 4             | 5                | μA   |                                                                                             |

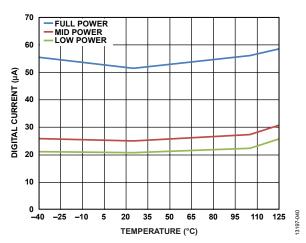

| $I_{IOVDD}$                                                  |                          |               |                  |      |                                                                                             |

| Low Power Mode                                               |                          | 20            | 35               | μΑ   |                                                                                             |

| Mid Power Mode                                               |                          | 25            | 40               | μA   |                                                                                             |

| Full Power Mode                                              |                          | 55            | 80               | μA   |                                                                                             |

Rev. D - 10/93 -

| Parameter <sup>1</sup>            | Min | Тур | Max | Unit | Test Conditions/Comments  |

|-----------------------------------|-----|-----|-----|------|---------------------------|

| POWER-DOWN CURRENTS <sup>13</sup> |     |     |     |      | Independent of power mode |

| Standby Current                   |     |     |     |      |                           |

| $I_{AVDD}$                        |     | 7   | 15  | μΑ   | LDOs on only              |

| $I_{IOVDD}$                       |     | 8   | 20  | μΑ   |                           |

| Power-Down Current                |     |     |     |      |                           |

| $I_{AVDD}$                        |     | 1   | 3   | μΑ   |                           |

| $I_{IOVDD}$                       |     | 1   | 2   | μΑ   |                           |

<sup>&</sup>lt;sup>1</sup> 温度範囲 = -40 °C ∼ +125 °C

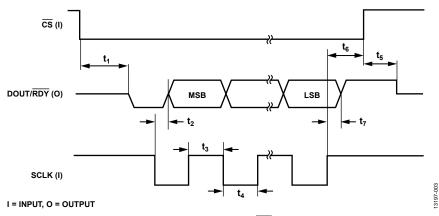

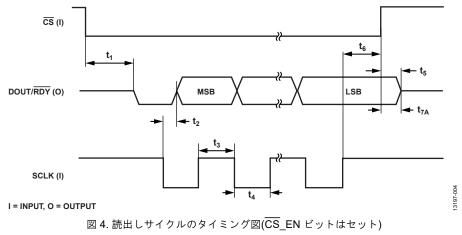

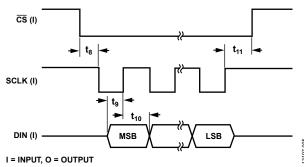

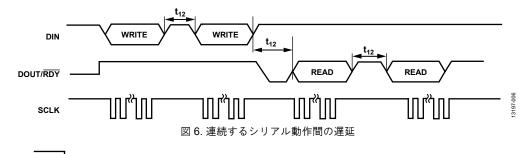

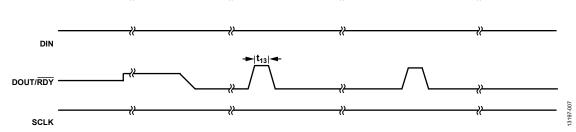

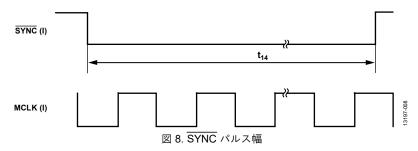

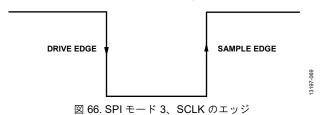

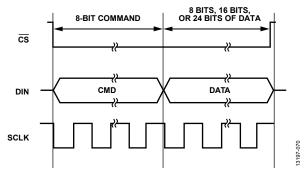

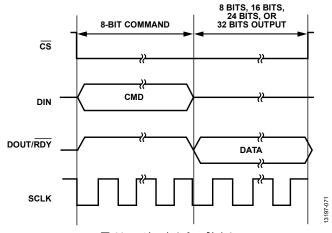

### タイミング特性

特に指定のない限り、 $AV_{DD}$  = 2.9 V ~3.6 V (通常消費電力モード)、2.7~V ~ 3.6 V (中消費電力および低消費電力モード)、 $IOV_{DD}$  = 1.65 V ~ 3.6 V、 $AV_{SS}$  = DGND = 0 V、入力ロジック 0 = 0 V、入力ロジック 1 =  $IOV_{DD}$  です。

表 4.

| Parameter <sup>1, 2</sup> | Min Typ             | Max | Unit | Test Conditions/Comments                                                                        |

|---------------------------|---------------------|-----|------|-------------------------------------------------------------------------------------------------|

| t <sub>3</sub>            | 100                 |     | ns   | SCLK high pulse width                                                                           |

| $t_4$                     | 100                 |     | ns   | SCLK low pulse width                                                                            |

| $t_{12}$                  |                     |     |      | Delay between consecutive read/write                                                            |

|                           |                     |     |      | operations                                                                                      |

|                           | 3/MCLK <sup>3</sup> |     | ns   | Full power mode                                                                                 |

|                           | 12/MCLK             |     | ns   | Mid power mode                                                                                  |

|                           | 24/MCLK             |     | ns   | Low power mode                                                                                  |

| $t_{13}$                  |                     |     | μs   | DOUT/RDY high time if DOUT/RDY is                                                               |

|                           |                     |     |      | low and the next conversion is available                                                        |

|                           | 6                   |     | μs   | Full power mode                                                                                 |

|                           | 25                  |     | μs   | Mid power mode                                                                                  |

|                           | 50                  |     | μs   | Low power mode                                                                                  |

| $t_{14}$                  |                     |     |      | SYNC low pulse width                                                                            |

|                           | 3/MCLK              |     | ns   | Full power mode                                                                                 |

|                           | 12/MCLK             |     | ns   | Mid power mode                                                                                  |

|                           | 24/MCLK             |     | ns   | Low power mode                                                                                  |

| READ OPERATION            |                     |     |      |                                                                                                 |

| $t_1$                     | 0                   | 80  | ns   | CS falling edge to DOUT/RDY active time                                                         |

| $t_2^4$                   | 0                   | 80  | ns   | SCLK active edge <sup>5</sup> to data valid delay                                               |

| t5 <sup>6, 7</sup>        | 10                  | 80  | ns   | Bus relinquish time after CS inactive edge                                                      |