# ANALOG 2 ppm/°C リファレンス、SPIインターフェース 内蔵の16/12ビット・デュアル nanoDAC+

## AD5689R/AD5687R

#### 特長

高い相対精度(INL): 16 ビットで最大±2 LSB 2 ppm/°C (typ)の低ドリフト 2.5 V リファレンスを内蔵 小型パッケージ: 3 mm x 3 mm の 16 ピン LFCSP

TUE: FSR の最大±0.1% オフセット誤差:最大±1.5 mV ゲイン誤差: FSR の最大±0.1%

高い駆動能力: 20 mA、電源レールから 0.5 V ユーザー設定可能なゲイン: 1 または 2 (GAIN ピン)

ゼロスケールまたはミッドスケールへのリセット(RSTSEL ピン)

1.8 V ロジックに互換

リードバックまたはデイジーチェーン付きの 50 MHz SPI

低グリッチ: 0.5 nV-sec

強固な 4 kV HBM 定格と 1.5 kV FICDM ESD 定格

低消費電力: 3 V で 3.3 mW 2.7~5.5 V 電源で動作 温度範囲: -40°C~+105°C

#### アプリケーション

光トランシーバ 基地局用パワー・アンプ プロセス制御(PLC I/O カード) 工業用オートメーション データ・アクイジション・システム

#### 概要

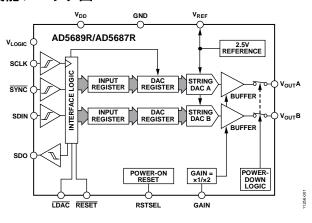

nanoDAC+TMファミリーに属する AD5689R/AD5687R は、低消費電 力 16/12 ビットのバッファ付き電圧出力デュアル DAC です。この デバイスは、2.5 Vの2ppm/℃リファレンス電圧(デフォルトでイ ネーブル)、2.5 V (ゲイン=1)または5 V (ゲイン=2)のフルスケー ル出力を選択するゲイン選択ピンを内蔵しています。デバイスは 2.7 V~5.5 V の単電源で動作し、デザインにより単調性が保証さ れ、ゲイン誤差は 0.1% FSR 以下でオフセット誤差性能は 1.5 mV です。両デバイスは、3 mm × 3 mm LFCSP パッケージまたは TSSOPパッケージを採用しています。

また、AD5689R/AD5687Rはパワーオン・リセット回路とRSTSEL ピンも内蔵しています。このRSTSEL ピンを使うと、DAC 出力が ゼロスケールまたはミッドスケールでパワーアップし、有効な書 込みが行われるまでその状態を維持させることができます。各デ バイスは、チャンネルごとのパワーダウン機能を内蔵しています。 この機能はパワーダウン・モードのデバイス消費電流を 3 V で 4 μAへ削減します。

AD5689R/AD5687Rは、最大 50 MHz のクロック・レートで動作す る、多機能なシリアル・ペリフェラル・インターフェース(SPI)を 採用し、両デバイスは 1.8 V/3 V/5 V ロジック用の V<sub>LOGIC</sub> ピンを内 蔵しています。

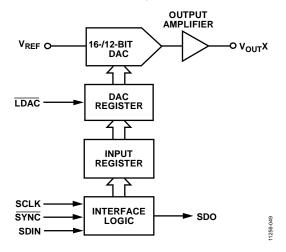

#### 機能ブロック図

図 1.

表 1.デュアル nanoDAC+ デバイス

| Interface | Reference | 16-Bit  | 12-Bit  |

|-----------|-----------|---------|---------|

| SPI       | Internal  | AD5689R | AD5687R |

|           | External  | AD5689  | AD5687  |

| $I^2C$    | Internal  | N/A     | AD5697R |

|           | External  | N/A     | N/A     |

#### 製品のハイライト

高い相対精度(INL)。

AD5689R (16 ビット): 最大±2 LSB AD5687R (12 ビット): 最大±1 LSB

低ドリフトの 2.5 V リファレンス電圧を内蔵。

温度係数: 2 ppm/°C (typ) 温度係数: 5 ppm/°C (max)

2種類のパッケージ・オプション。

3 mm×3 mm の 16 ピン LFCSP

16ピン TSSOP

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセス社の特許または特許の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセス社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料はREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

©2013 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 雷話 03(5402)8200

大阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

## 目次

| 特長1                        |

|----------------------------|

| アプリケーション1                  |

| 機能ブロック図1                   |

| 概要1                        |

| 製品のハイライト1                  |

| 改訂履歴2                      |

| 仕様                         |

| AC 特性5                     |

| タイミング特性6                   |

| デイジーチェーンおよびリードバックのタイミング特性7 |

| 絶対最大定格9                    |

| ESD の注意                    |

| ピン配置およびピン機能説明10            |

| 代表的な性能特性11                 |

| 用語17                       |

| 動作原理19                     |

| D/A コンバータ19                |

| 伝達関数19                     |

| DAC アーキテクチャ19              |

| シリアル・インターフェース20            |

| スタンドアロン動作21                |

| 青込コマントと史材コマント                        | 21     |

|--------------------------------------|--------|

| デイジーチェーン動作                           | 21     |

| リードバック動作                             | 22     |

| パワーダウン動作                             | 22     |

| DAC のロード(ハードウェア LDAC ピン)             | 23     |

| LDAC マスク・レジスタ                        | 23     |

| ハードウェア・リセット(RESET)                   | 24     |

| リセット選択ピン(RSTSEL)                     | 24     |

| 内蔵リファレンスのセットアップ                      | 24     |

| ハンダ加熱リフロー                            | 24     |

| 長時間温度ドリフト                            | 24     |

| 熱ヒステリシス                              | 25     |

| アプリケーション情報                           | 26     |

| マイクロプロセッサ・インターフェース                   | 26     |

| AD5689R/AD5687R と ADSP-BF531 とのインターフ | /ェース26 |

| AD5689R/AD5687R と SPORT とのインターフェー    | ス26    |

| レイアウトのガイドライン                         | 26     |

| 電流絶縁型インターフェース                        | 26     |

| 外形寸法                                 | 27     |

| ナーダー・ガイド                             | 28     |

#### 改訂履歴

2/13—Revision 0: Initial Version

仕様

特に指定がない限り、 $V_{DD}$  = 2.7  $V\sim$ 5.5 V; 1.8  $V\leq V_{LOGIC}\leq$ 5.5 V; すべての仕様は  $T_{MIN}\sim T_{MAX}$  で規定。  $R_L$  = 2  $k\Omega$ ;  $C_L$  = 200 pF。

表 2.

|                                                      |        | A Grade    | ,1                       |        | B Grade <sup>1</sup> |                          |            |                                                                                                           |

|------------------------------------------------------|--------|------------|--------------------------|--------|----------------------|--------------------------|------------|-----------------------------------------------------------------------------------------------------------|

| Parameter                                            | Min    | Typ        | Max                      | Min    | Typ                  | Max                      | Unit       | Test Conditions/Comments                                                                                  |

| STATIC PERFORMANCE <sup>2</sup>                      |        |            |                          |        |                      |                          |            |                                                                                                           |

| AD5689R                                              |        |            |                          |        |                      |                          |            |                                                                                                           |

| Resolution                                           | 16     |            |                          | 16     |                      |                          | Bits       |                                                                                                           |

| Relative Accuracy                                    |        | ±2         | ±8                       |        | ±1                   | ±2                       | LSB        | Gain = 2                                                                                                  |

|                                                      |        | ±2         | ±8                       |        | ±1                   | ±3                       |            | Gain = 1                                                                                                  |

| Differential                                         |        |            | ±1                       |        |                      | ±1                       | LSB        | Guaranteed monotonic by design                                                                            |

| Nonlinearity AD5687R                                 |        |            |                          |        |                      |                          |            |                                                                                                           |

| Resolution                                           | 12     |            |                          | 12     |                      |                          | Bits       |                                                                                                           |

| Relative Accuracy                                    |        | $\pm 0.12$ | ±2                       |        | ±0.12                | ±1                       | LSB        |                                                                                                           |

| Differential Nonlinearity                            |        |            | ±1                       |        |                      | ±1                       | LSB        | Guaranteed monotonic by design                                                                            |

| Zero-Code Error                                      |        | 0.4        | 4                        |        | 0.4                  | 1.5                      | mV         | All 0s loaded to DAC register                                                                             |

| Offset Error                                         |        | +0.1       | <u>±</u> 4               |        | +0.1                 | ±1.5                     | mV         |                                                                                                           |

| Full-Scale Error                                     |        | +0.01      | ±0.2                     |        | +0.01                | ±0.1                     | % of FSR   | All 1s loaded to DAC register                                                                             |

| Gain Error                                           |        | $\pm 0.02$ | ±0.2                     |        | ±0.02                | ±0.1                     | % of FSR   |                                                                                                           |

| Total Unadjusted Error                               |        | ±0.01      | ±0.25                    |        | ±0.01                | ±0.1                     | % of FSR   | External reference; gain = 2; TSSOP                                                                       |

|                                                      |        |            | ±0.25                    |        |                      | ±0.2                     | % of FSR   | Internal reference; gain = 1; TSSOP                                                                       |

| Offset Error Drift <sup>3</sup>                      |        | ±1         |                          |        | ±1                   |                          | μV/°C      |                                                                                                           |

| Gain Temperature                                     |        | ±1         |                          |        | ±1                   |                          | ppm        | Of FSR/°C                                                                                                 |

| Coefficient <sup>3</sup>                             |        |            |                          |        |                      |                          |            |                                                                                                           |

| DC Power Supply Rejection<br>Ratio <sup>3</sup>      |        | 0.15       |                          |        | 0.15                 |                          | mV/V       | DAC code = midscale;<br>$V_{DD} = 5 \text{ V} \pm 10\%$                                                   |

| DC Crosstalk <sup>3</sup>                            |        |            |                          |        |                      |                          |            |                                                                                                           |

|                                                      |        | ±2         |                          |        | ±2                   |                          | μV         | Due to single channel, full-scale output change                                                           |

|                                                      |        | ±3         |                          |        | ±3                   |                          | $\mu V/mA$ | Due to load current change                                                                                |

|                                                      |        | ±2         |                          |        | ±2                   |                          | μV         | Due to powering down (per channel)                                                                        |

| OUTPUT CHARACTERISTICS <sup>3</sup>                  |        |            |                          |        |                      |                          |            |                                                                                                           |

| Output Voltage Range                                 | 0      |            | $V_{\text{REF}}$         | 0      |                      | $V_{\text{REF}}$         | V          | Gain = 1                                                                                                  |

|                                                      | 0      |            | $2\times V_{\text{REF}}$ | 0      |                      | $2\times V_{\text{REF}}$ | V          | Gain = 2, see Figure32                                                                                    |

| Capacitive Load Stability                            |        | 2          |                          |        | 2                    |                          | nF         | $R_L = \infty$                                                                                            |

|                                                      |        | 10         |                          |        | 10                   |                          | nF         | $R_L = 1 \text{ k}\Omega$                                                                                 |

| Resistive Load <sup>4</sup>                          | 1      |            |                          | 1      |                      |                          | kΩ         |                                                                                                           |

| Load Regulation                                      |        | 80         |                          |        | 80                   |                          | $\mu V/mA$ | $ \begin{array}{l} 5~V \pm 10\%,  DAC \; code = midscale; \\ -30~mA \leq I_{OUT} \leq 30~mA \end{array} $ |

|                                                      |        | 80         |                          |        | 80                   |                          | $\mu V/mA$ | $\begin{array}{l} 3~V \pm 10\%, DAC~code = midscale;\\ -20~mA \leq I_{OUT} \leq 20~mA \end{array}$        |

| Short-Circuit Current <sup>5</sup>                   |        | 40         |                          |        | 40                   |                          | mA         |                                                                                                           |

| Load Impedance at Rails <sup>6</sup>                 |        | 25         |                          |        | 25                   |                          | Ω          | See Figure 32                                                                                             |

| Power-Up Time                                        |        | 2.5        |                          |        | 2.5                  |                          | μs         | Coming out of power-down mode; $V_{DD} = 5 \text{ V}$                                                     |

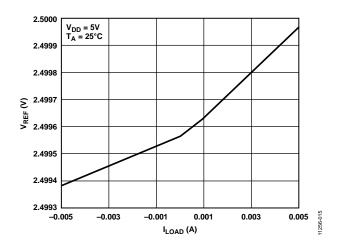

| REFERENCE OUTPUT                                     |        |            |                          |        |                      |                          |            |                                                                                                           |

| Output Voltage <sup>7</sup>                          | 2.4975 |            | 2.5025                   | 2.4975 |                      | 2.5025                   | V          | At ambient                                                                                                |

| Reference Temperature<br>Coefficient <sup>8, 9</sup> |        | 5          | 20                       |        | 2                    | 5                        | ppm/°C     | See the Terminology section                                                                               |

| Output Impedance <sup>3</sup>                        |        | 0.04       |                          |        | 0.04                 |                          | Ω          |                                                                                                           |

| Output Voltage Noise <sup>3</sup>                    |        | 12         |                          |        | 12                   |                          | μV p-p     | 0.1 Hz to 10 Hz                                                                                           |

| Output Voltage Noise<br>Density <sup>3</sup>         |        | 240        |                          |        | 240                  |                          | nV/√Hz     | At ambient; $f = 10 \text{ kHz}$ , $C_L = 10 \text{ nF}$                                                  |

| Load Regulation Sourcing <sup>3</sup>                |        | 20         |                          |        | 20                   |                          | μV/mA      | At ambient                                                                                                |

| Load Regulation Sinking <sup>3</sup>                 |        | 40         |                          |        | 40                   |                          | μV/mA      | At ambient                                                                                                |

| Output Current Load<br>Capability <sup>3</sup>       |        | ±5         |                          |        | ±5                   |                          | mA         | $V_{DD} \ge 3 \text{ V}$                                                                                  |

| Line Regulation <sup>3</sup>                         |        | 100        |                          |        | 100                  |                          | $\mu V/V$  | At ambient                                                                                                |

Rev. **0** - 3/28 -

|                                        |                        | A Grad | e <sup>1</sup>         |                        | B Grade | 1                      |      |                                                                                |

|----------------------------------------|------------------------|--------|------------------------|------------------------|---------|------------------------|------|--------------------------------------------------------------------------------|

| Parameter                              | Min                    | Typ    | Max                    | Min                    | Тур     | Max                    | Unit | Test Conditions/Comments                                                       |

| Long-Term Stability/Drift <sup>3</sup> |                        | 12     |                        |                        | 12      |                        | ppm  | After 1000 hours at 125°C                                                      |

| Thermal Hysteresis <sup>3</sup>        |                        | 125    |                        |                        | 125     |                        | ppm  | First cycle                                                                    |

|                                        |                        | 25     |                        |                        | 25      |                        | ppm  | Additional cycles                                                              |

| LOGIC INPUTS <sup>3</sup>              |                        |        |                        |                        |         |                        |      |                                                                                |

| Input Current                          |                        |        | ±2                     |                        |         | ±2                     | μΑ   | Per pin                                                                        |

| Input Low Voltage (V <sub>INL</sub> )  |                        |        | $0.3 \times V_{LOGIC}$ |                        |         | $0.3 \times V_{LOGIC}$ | V    |                                                                                |

| Input High Voltage (V <sub>INH</sub> ) | $0.7 \times V_{LOGIC}$ |        |                        | $0.7 \times V_{LOGIC}$ |         |                        | V    |                                                                                |

| Pin Capacitance                        |                        | 2      |                        |                        | 2       |                        | pF   |                                                                                |

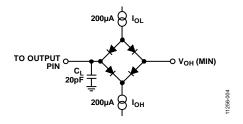

| LOGIC OUTPUTS (SDO) <sup>3</sup>       |                        |        |                        |                        |         |                        |      |                                                                                |

| Output Low Voltage (V <sub>OL</sub> )  |                        |        | 0.4                    |                        |         | 0.4                    | V    | $I_{SINK} = 200 \mu A$                                                         |

| Output High Voltage (V <sub>OH</sub> ) | $V_{LOGIC} - 0.4$      |        |                        | $V_{LOGIC} - 0.4$      |         |                        | V    | $I_{SOURCE} = 200  \mu A$                                                      |

| Floating State Output<br>Capacitance   |                        | 4      |                        |                        | 4       |                        | pF   |                                                                                |

| POWER REQUIREMENTS                     |                        |        |                        |                        |         |                        |      |                                                                                |

| $V_{LOGIC}$                            | 1.8                    |        | 5.5                    | 1.8                    |         | 5.5                    | V    |                                                                                |

| $I_{LOGIC}$                            |                        |        | 3                      |                        |         | 3                      | μΑ   |                                                                                |

| $ m V_{DD}$                            | 2.7                    |        | 5.5                    | 2.7                    |         | 5.5                    | V    | Gain = 1                                                                       |

| $ m V_{DD}$                            | $V_{REF} + 1.5$        |        | 5.5                    | $V_{REF} + 1.5$        |         | 5.5                    | V    | Gain = 2                                                                       |

| $I_{\mathrm{DD}}$                      |                        |        |                        |                        |         |                        |      | $V_{IH} = V_{DD}, V_{IL} = GND,$<br>$V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$ |

| Normal Mode <sup>10</sup>              |                        | 0.59   | 0.7                    |                        | 0.59    | 0.7                    | mA   | Internal reference off                                                         |

|                                        |                        | 1.1    | 1.3                    |                        | 1.1     | 1.3                    | mA   | Internal reference on, at full scale                                           |

| All Power-Down Modes <sup>11</sup>     |                        | 1      | 4                      |                        | 1       | 4                      | μΑ   | −40°C to +85°C                                                                 |

|                                        |                        |        | 6                      |                        |         | 6                      | μΑ   | −40°C to +105°C                                                                |

<sup>&</sup>lt;sup>1</sup> 温度範囲 (A および B グレード): −40°C~+105°C。

<sup>&</sup>lt;sup>2</sup> 特に指定がない限り、DC 仕様は出力無負荷でテスト。 上側デッドバンド = 10 mV で、これは  $V_{REF} = V_{DD}$  かつゲイン = 1 の場合、または  $V_{REF}/2 = V_{DD}$  かつゲイン = 2 の場合にのみ存在します。 直線性は、縮小コード範囲 256~65,280 (AD5689R)、12~4080 (AD5687R)を使って計算。

<sup>&</sup>lt;sup>3</sup> デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

<sup>&</sup>lt;sup>4</sup> チャンネル A の出力電流は最大 30 mA です。 同様に、チャンネル B は、ジャンクション温度 110℃ までで最大 30 mA の出力電流を持つことができます。

$<sup>^5</sup>$   $V_{DD} = 5$   $V_{DD} = 5$   $V_{CD} =$

$<sup>^6</sup>$  いずれかの電源レールから負荷電流を取り出すとき、その電源レールに対する出力電圧のヘッドルームは、出力デバイスのチャンネル抵抗  $25\,\Omega$  (typ)により制限されます。 例えば、 $1\,\mathrm{mA}$  のシンク電流の場合、最小出力電圧 =  $25\,\Omega \times 1\,\mathrm{mA}$  =  $25\,\mathrm{mV}$  となります (図  $32\,$  参照)。

<sup>&</sup>lt;sup>7</sup> 前処理ハンダ・リフローでの初期精度は±750 μV です。出力電圧は前処理でのドリフトの影響を含みます。 内蔵リファレンスのセットアップのセクションを参照してください。

<sup>&</sup>lt;sup>8</sup> リファレンス電圧は2点の温度で調整/テストし、キャラクタライゼーションは-40°C $\sim$ +105°C で行います。

<sup>9</sup> リファレンス電圧の温度係数はボックス法に準拠して計算します。 詳細については、用語のセクションを参照してください。

$<sup>^{10}</sup>$  インターフェースは非アクティブ状態。 両 DAC はアクティブ状態。 DAC 出力は無負荷。

<sup>11</sup> 両 DAC はパワーダウン。

#### AC 特性

特に指定がない限り、 $V_{DD}$  = 2.7  $V\sim5.5$  V;  $R_L$  = 2  $k\Omega$  (GND  $\sim$ 接続);  $C_L$  = 200 pF (GND  $\sim$ 接続); 1.8  $V \leq V_{LOGIC} \leq 5.5$  V; すべての仕様は  $T_{MIN}\sim T_{MAX}$ で規定。デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

表 3.

| Parameter <sup>1</sup>                       | Min | Тур  | Max | Unit           | Test Conditions/Comments <sup>2</sup>                                               |

|----------------------------------------------|-----|------|-----|----------------|-------------------------------------------------------------------------------------|

| Output Voltage Settling Time                 |     |      |     |                |                                                                                     |

| AD5689R                                      |     | 5    | 8   | μs             | <sup>1</sup> / <sub>4</sub> to <sup>3</sup> / <sub>4</sub> scale settling to ±2 LSB |

| AD5687R                                      |     | 5    | 7   | μs             | <sup>1</sup> / <sub>4</sub> to <sup>3</sup> / <sub>4</sub> scale settling to ±2 LSB |

| Slew Rate                                    |     | 0.8  |     | V/µs           |                                                                                     |

| Digital-to-Analog Glitch Impulse             |     | 0.5  |     | nV-sec         | 1 LSB change around major carry                                                     |

| Digital Feedthrough                          |     | 0.13 |     | nV-sec         |                                                                                     |

| Digital Crosstalk                            |     | 0.1  |     | nV-sec         |                                                                                     |

| Analog Crosstalk                             |     | 0.2  |     | nV-sec         |                                                                                     |

| DAC-to-DAC Crosstalk                         |     | 0.3  |     | nV-sec         |                                                                                     |

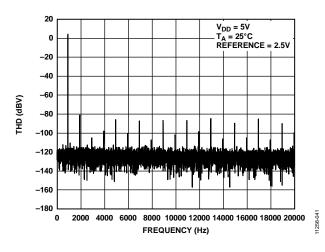

| Total Harmonic Distortion (THD) <sup>3</sup> |     | -80  |     | dB             | At ambient, BW = 20 kHz, $V_{DD} = 5 \text{ V}$ , $f_{OUT} = 1 \text{ kHz}$         |

| Output Noise Spectral Density (NSD)          |     | 300  |     | $nV/\sqrt{Hz}$ | DAC code = midscale, 10 kHz; gain = 2                                               |

| Output Noise                                 |     | 6    |     | μV p-p         | 0.1 Hz to 10 Hz                                                                     |

| Signal-to-Noise Ratio (SNR)                  |     | 90   |     | dB             | At ambient, BW = 20 kHz, $V_{DD} = 5 \text{ V}$ , $f_{OUT} = 1 \text{ kHz}$         |

| Spurious Free Dynamic Range (SFDR)           |     | 83   |     | dB             | At ambient, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz                          |

| Signal-to-Noise-and-Distortion Ratio (SINAD) |     | 80   |     | dB             | At ambient, BW = 20 kHz, $V_{DD} = 5 \text{ V}$ , $f_{OUT} = 1 \text{ kHz}$         |

<sup>1</sup>用語のセクションを参照してください。

$<sup>^2</sup>$  温度範囲 (typ)は、25°C で-40°C~+105°C です。

³デジタル的に発生した1kHzの正弦波。

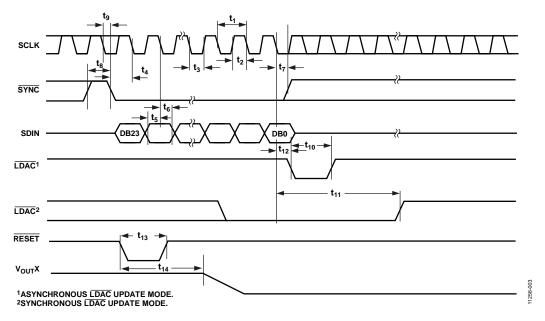

#### タイミング特性

すべての入力信号は  $t_R=t_F=1$  ns/V ( $V_{DD}$ の 10%から 90%)で規定し、電圧レベル( $V_{IL}+V_{IH}$ )/2 からの時間とします。図 2 参照。特に指定がない限り、 $V_{DD}=2.7$  V $\sim$ 5.5 V; 1.8 V $\leq$ V $_{LOGIC}\leq$ 5.5 V;  $V_{REF}=2.5$  V。すべての仕様は  $T_{MIN}\sim T_{MAX}$ で規定。

表 4.

|                        | $1.8 \text{ V} \leq \text{V}_{\text{LOGIC}} < 2.7 \text{ V} \qquad 2.7 \text{ V} \leq \text{V}_{\text{LOGIC}} \leq 5.5 \text{ V}$ |     | V <sub>LOGIC</sub> ≤ 5.5 V |     |      |                                                                                                                                                            |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter <sup>1</sup> | Min                                                                                                                               | Max | Min                        | Max | Unit | Description                                                                                                                                                |

| $t_1$                  | 33                                                                                                                                |     | 20                         |     | ns   | SCLK cycle time                                                                                                                                            |

| $t_2$                  | 16                                                                                                                                |     | 10                         |     | ns   | SCLK high time                                                                                                                                             |

| $t_3$                  | 16                                                                                                                                |     | 10                         |     | ns   | SCLK low time                                                                                                                                              |

| $t_4$                  | 15                                                                                                                                |     | 10                         |     | ns   | SYNC to SCLK falling edge setup time                                                                                                                       |

| $t_5$                  | 5                                                                                                                                 |     | 5                          |     | ns   | Data setup time                                                                                                                                            |

| $t_6$                  | 5                                                                                                                                 |     | 5                          |     | ns   | Data hold time                                                                                                                                             |

| $\mathbf{t}_7$         | 15                                                                                                                                |     | 10                         |     | ns   | SCLK falling edge to SYNC rising edge                                                                                                                      |

| t <sub>8</sub>         | 20                                                                                                                                |     | 20                         |     | ns   | Minimum SYNC high time (update single channel or both channels)                                                                                            |

| t <sub>9</sub>         | 16                                                                                                                                |     | 10                         |     | ns   | SYNC falling edge to SCLK fall ignore                                                                                                                      |

| $t_{10}$               | 25                                                                                                                                |     | 15                         |     | ns   | LDAC pulse width low                                                                                                                                       |

| t <sub>11</sub>        | 30                                                                                                                                |     | 20                         |     | ns   | SCLK falling edge to LDAC rising edge                                                                                                                      |

| $t_{12}$               | 20                                                                                                                                |     | 20                         |     | ns   | SCLK falling edge to LDAC falling edge                                                                                                                     |

| $t_{13}$               | 30                                                                                                                                |     | 30                         |     | ns   | RESET minimum pulse width low                                                                                                                              |

| t <sub>14</sub>        | 30                                                                                                                                |     | 30                         |     | ns   | RESET pulse activation time                                                                                                                                |

| Power-Up Time          | 4.5                                                                                                                               |     | 4.5                        |     | μs   | Time that is required to exit power-down and enter normal mode of operation; 24 <sup>th</sup> clock edge to 90% of DAC midscale value with output unloaded |

$<sup>^{1}</sup>$   $V_{DD}$  = 2.7  $V \sim 5.5$  V、2.7  $V \leq V_{LOGIC} \leq V_{DD}$  での最大 SCLK 周波数は 50 MHz。 デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

図 2.シリアル書込み動作

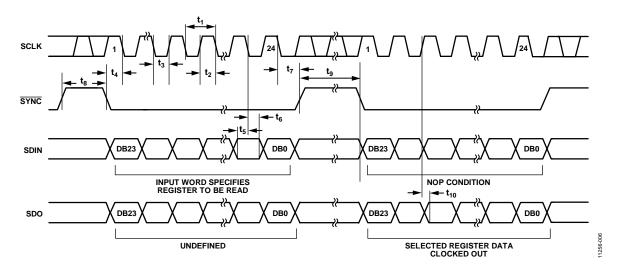

### デイジーチェーンおよびリードバックのタイミング特性

すべての入力信号は  $t_R=t_F=1$  ns/V ( $V_{DD}$ の 10%から 90%)で規定し、電圧レベル( $V_{IL}+V_{IH}$ )/2 からの時間とします。図 4 と図 5 参照。特に指定がない限り、 $V_{DD}=2.7$  V  $\sim 5.5$  V; 1.8 V  $\leq$  V $_{LOGIC} \leq$  5.5 V;  $V_{REF}=2.5$  V。すべての仕様は  $T_{MIN}\sim T_{MAX}$  で規定。  $V_{DD}=2.7$  V  $\sim 5.5$  V。

#### 表 5.

|                        | 1.8 V ≤ V <sub>LOGIC</sub> < 2.7 V | $2.7 \text{ V} \leq V_{\text{LOGIC}} \leq 5.5 \text{ V}$ |      |                                       |

|------------------------|------------------------------------|----------------------------------------------------------|------|---------------------------------------|

| Parameter <sup>1</sup> | Min Max                            | Min Max                                                  | Unit | Description                           |

| $t_1$                  | 66                                 | 40                                                       | ns   | SCLK cycle time                       |

| $t_2$                  | 33                                 | 20                                                       | ns   | SCLK high time                        |

| $t_3$                  | 33                                 | 20                                                       | ns   | SCLK low time                         |

| $t_4$                  | 33                                 | 20                                                       | ns   | SYNC to SCLK falling edge             |

| $t_5$                  | 5                                  | 5                                                        | ns   | Data setup time                       |

| $t_6$                  | 5                                  | 5                                                        | ns   | Data hold time                        |

| $\mathbf{t}_7$         | 15                                 | 10                                                       | ns   | SCLK falling edge to SYNC rising edge |

| $t_8$                  | 60                                 | 30                                                       | ns   | Minimum SYNC high time                |

| t <sub>9</sub>         | 60                                 | 30                                                       | ns   | Minimum SYNC high time                |

| $t_{10}$               | 36                                 | 25                                                       | ns   | SDO data valid from SCLK rising edge  |

| $t_{11}^{5}$           | 15                                 | 10                                                       | ns   | SCLK falling edge to SYNC rising edge |

| $t_{12}^{5}$           | 15                                 | 10                                                       | ns   | SYNC rising edge to SCLK rising edge  |

$<sup>^{1}</sup>$   $V_{DD}$  = 2.7  $V \sim 5.5$  V、1.8  $V \leq V_{LOGIC} \leq V_{DD}$  で、最大 SCLK 周波数は 25 MHz または 15 MHz。 デザインとキャラクタライゼーションにより保証しますが、出荷テストは行いません。

#### 回路およびタイミング図

図 3.デジタル出力(SDO)タイミング仕様の負荷回路

図 4.デイジーチェーンのタイミング図

図 5.リードバック・タイミング図

## 絶対最大定格

特に指定のない限り、 $T_A = 25$  °C。

#### 表 6.

| Parameter                                                                    | Rating                                               |

|------------------------------------------------------------------------------|------------------------------------------------------|

| V <sub>DD</sub> to GND                                                       | -0.3 V to +7 V                                       |

| V <sub>LOGIC</sub> to GND                                                    | −0.3 V to +7 V                                       |

| V <sub>OUT</sub> to GND                                                      | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$           |

| $V_{REF}$ to GND                                                             | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$           |

| Digital Input Voltage to GND                                                 | $-0.3 \text{ V to V}_{\text{LOGIC}} + 0.3 \text{ V}$ |

| Operating Temperature Range                                                  | −40°C to +105°C                                      |

| Storage Temperature Range                                                    | −65°C to +150°C                                      |

| Junction Temperature                                                         | 125°C                                                |

| 16-Lead TSSOP, $\theta_{JA}$ Thermal Impedance, 0<br>Airflow (4-Layer Board) | 112.6°C/W                                            |

| 16-Lead LFCSP, $\theta_{JA}$ Thermal Impedance, 0<br>Airflow (4-Layer Board) | 70°C/W                                               |

| Reflow Soldering Peak Temperature, Pb Free (J-STD-020)                       | 260°C                                                |

| $ESD^1$                                                                      | 4 kV                                                 |

| FICDM                                                                        | 1.5 kV                                               |

<sup>&</sup>lt;sup>1</sup> 人体モデル (HBM)分類。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久 的な損傷を与えることがあります。この規定はストレス定格の規 定のみを目的とするものであり、この仕様の動作のセクションに 記載する規定値以上でのデバイス動作を定めたものではありませ ん。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼 性に影響を与えます。

#### ESD の注意

ESD (静電放電)の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

Rev. **0** — 9/28 —

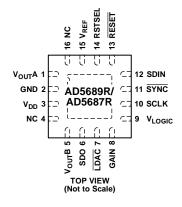

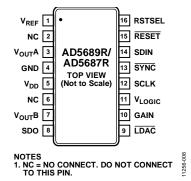

## ピン配置およびピン機能説明

NOTES

1. THE EXPOSED PAD MUST BE TIED TO GND.

2. NC = NO CONNECT. DO NOT CONNECT TO THIS PIN.

図 6.16 ピン LFCSP のピン配置

図 7.16 ピン TSSOP のピン配置

#### 表 7.ピン機能の説明

| <br>ピン番号 |       |                    |                                                                                                                                                                                                                                                                                |

|----------|-------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LFCSP    | TSSOP | 記号                 | 説明                                                                                                                                                                                                                                                                             |

| 1        | 3     | V <sub>OUT</sub> A | DAC A からのアナログ電圧出力。出力アンプはレール to レールの動作を行います。                                                                                                                                                                                                                                    |

| 2        | 4     | GND                | AD5689R/AD5687Rの全回路に対するグラウンド基準。                                                                                                                                                                                                                                                |

| 3        | 5     | $V_{ m DD}$        | 電源入力。AD5689R/AD5687R は 2.7 V~5.5 V で動作できます。電源は $10\mu\text{F}$ のコンデンサと $0.1\mu\text{F}$ のコンデンサの並列接続により GND ヘデカップリングしてください。                                                                                                                                                     |

| 4        | 6     | NC                 | 未接続。このピンは接続しないでください。                                                                                                                                                                                                                                                           |

| 5        | 7     | $V_{OUT}B$         | DAC B のアナログ電圧出力。出力アンプはレール to レールの動作を行います。                                                                                                                                                                                                                                      |

| 6        | 8     | SDO                | シリアル・データ出力。SDO は複数の AD5689R/AD5687R デバイスのデイジーチェーン接続に、またはリードバックに使用することができます。シリアル・データは SCLK の立上がりエッジで転送され、クロックの立下がりエッジで有効になります。                                                                                                                                                  |

| 7        | 9     | LDAC               | LDAC は、非同期と同期の2つのモードで動作することができます。入力レジスタに新しいデータがある場合、このピンにロー・レベルのパルスを入力すると、一方または両方のDAC レジスタを更新することができます。両DAC 出力を同時に更新することができます。あるいは、このピンをロー・レベルに固定することができます。                                                                                                                    |

| 8        | 10    | GAIN               | ゲイン選択ピン。このピンを GND に接続すると、両 DAC 出力の振幅は $0$ $V \sim V_{REF}$ になります。このピンを $V_{LOGIC}$ に接続すると、両 DAC 出力の振幅は $0$ $V \sim 2 \times V_{REF}$ になります。                                                                                                                                    |

| 9        | 11    | $V_{LOGIC}$        | デジタル電源。電圧範囲は 1.8 V~5.5 V。                                                                                                                                                                                                                                                      |

| 10       | 12    | SCLK               | シリアル・クロック入力。データは、シリアル・クロック入力の立下がりエッジでシフトレジスタに入力されます。データは最大50 MHzのレートで転送できます。                                                                                                                                                                                                   |

| 11       | 13    | SYNC               | アクティブ・ローのコントロール入力。これは、入力データに対するフレーム同期信号です。 SYNCがロー・レベルになると、データは次の 24 個のクロックの立下がりエッジで転送されます。                                                                                                                                                                                    |

| 12       | 14    | SDIN               | シリアル・データ入力。このデバイスは、24 ビットの入力シフトレジスタを内蔵しています。データは、<br>シリアル・クロック入力の立下がりエッジでレジスタに入力されます。                                                                                                                                                                                          |

| 13       | 15    | RESET              | 非同期リセット入力。 $\overline{\text{RESET}}$ 入力は、立下がりエッジ検出です。 $\overline{\text{RESET}}$ がロー・レベルのときは、すべての $\overline{\text{LDAC}}$ パルスが無視されます。 $\overline{\text{RESET}}$ がロー・レベルになると、入力レジスタと $\overline{\text{DAC}}$ レジスタが $\overline{\text{RSTSEL}}$ ピンの状態に応じてゼロスケールまたはミッドスケールで更新されます。 |

| 14       | 16    | RSTSEL             | パワーオン・リセット選択ピン。このピンを GND に接続すると、両 DAC はゼロスケールでパワーアップします。このピンを $V_{\text{LOGIC}}$ に接続すると、両 DAC はミッドスケールでパワーアップします。                                                                                                                                                              |

| 15       | 1     | V <sub>REF</sub>   | リファレンス電圧。AD5689R/AD5687Rは共通のリファレンス・ピンを持っています。内蔵リファレンス電圧を使用する場合、このピンがリファレンス出力ピンになります。外付けリファレンスを使用する場合は、このピンはリファレンス入力ピンになります。このピンは、デフォルトでリファレンス出力になります。                                                                                                                          |

| 16       | 2     | NC                 | 未接続。このピンは接続しないでください。                                                                                                                                                                                                                                                           |

| 17       | N/A   | EPAD               | エクスポーズド・パッド。エクスポーズド・パッドは GND に接続する必要があります。                                                                                                                                                                                                                                     |

Rev. **0** — 10/28 —

## 代表的な性能特性

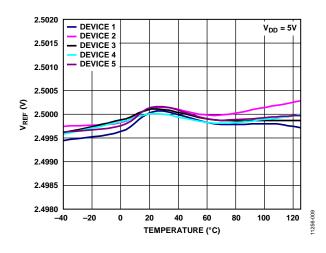

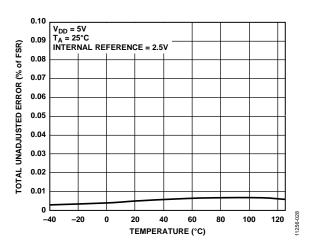

図 8.内蔵リファレンス電圧の温度特性(グレード B)

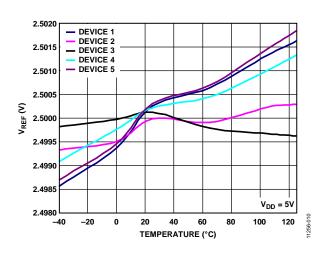

図 9.内蔵リファレンス電圧の温度特性(グレード A)

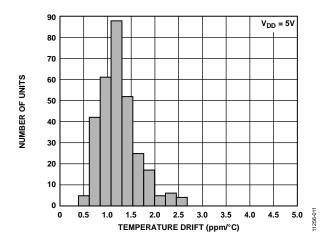

図 10.リファレンス出力温度ドリフトのヒストグラム

図 11.リファレンスの長時間安定性/ドリフト

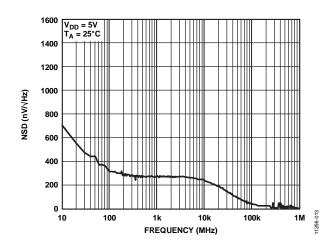

図 12.内蔵リファレンス・ノイズ・スペクトル密度の周波数特性

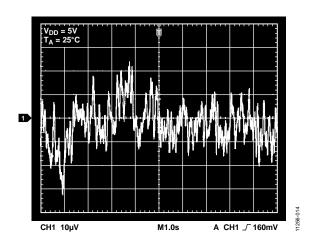

図 13.内蔵リファレンスのノイズ、0.1 Hz~10 Hz

Rev. **0** — 11/28 —

図 14.負荷電流対内蔵リファレンス電圧

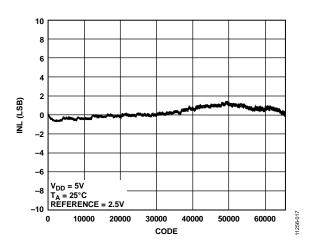

図 15.AD5689R のコード対積分非直線性(INL)

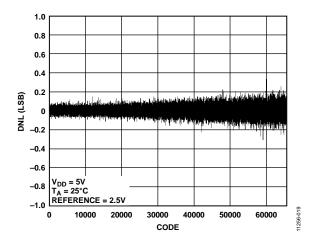

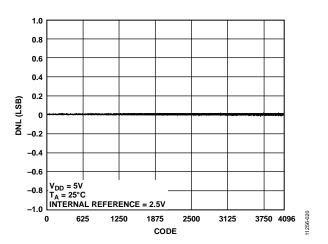

図 16.AD5689R のコード対微分非直線性 (DNL)

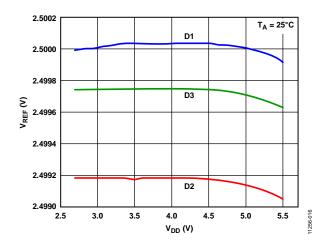

図 17.電源電圧対内蔵リファレンス電圧

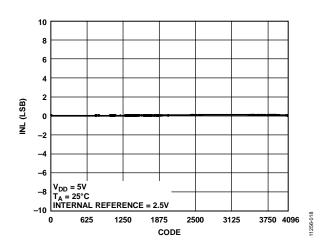

図 18.AD5687R のコード対 INL

図 19.AD5687R のコード対 DNL

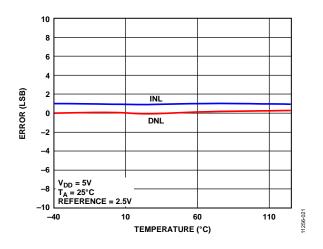

図 20.INL 誤差と DNL 誤差の温度特性

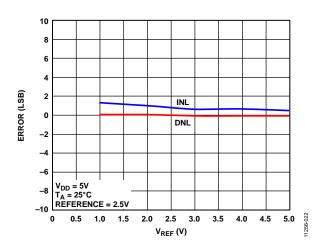

図 21.V<sub>REF</sub>対 INL 誤差および DNL 誤差

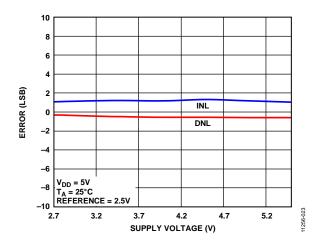

図 22.電源電圧対 INL 誤差および DNL 誤差

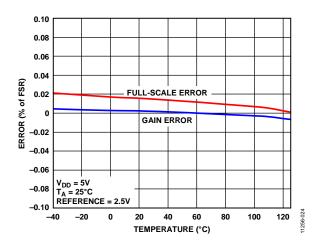

図 23.ゲイン誤差とフルスケール誤差の温度特性

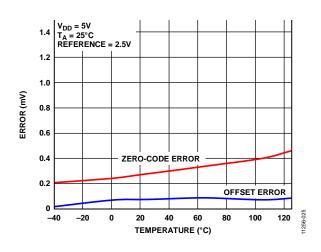

図 24.ゼロ・コード誤差とオフセット誤差の温度特性

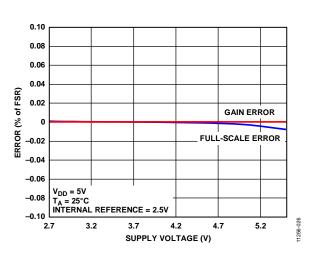

図 25.電源対ゲイン誤差およびフルスケール誤差

Rev. **0** — 13/28 —

データシート

## AD5689R/AD5687R

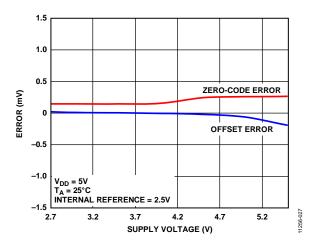

図 26.電源電圧対ゼロ・コード誤差およびオフセット誤差

図 27.総合未調整誤差(TUE)の温度特性

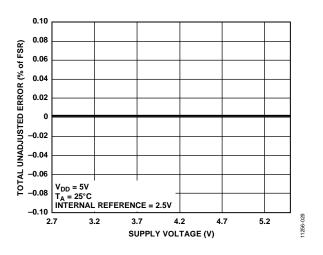

図 28.電源対 TUE、ゲイン= 1

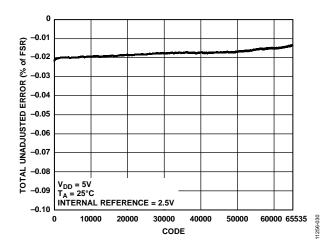

図 29.コード対 TUE

図 30.外付けリファレンス電圧  $V_{DD} = 5 V$  での  $I_{DD}$  ヒストグラム

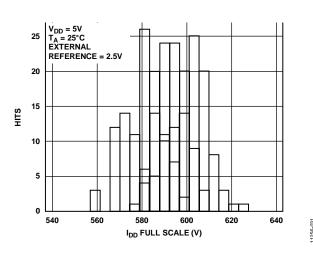

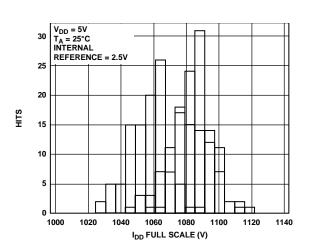

図 31.内蔵リファレンス電圧での  $I_{DD}$  ヒストグラム  $V_{REF} = 2.5 \ V$ 、ゲイン= 2

Rev. **0** — 14/28 —

11256-032

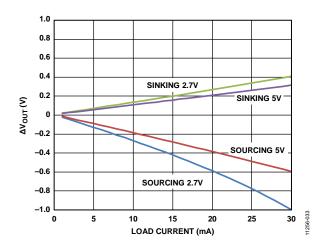

図 32.負荷電流対ヘッドルーム/フットルーム

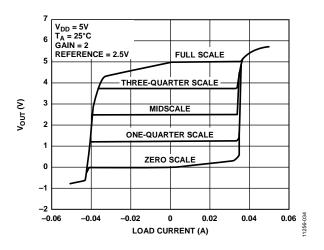

図 33.5 V でのソース能力とシンク能力、ゲイン = 2

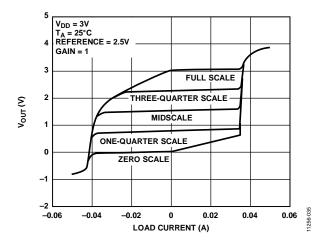

図 34.3 V でのソース能力とシンク能力、ゲイン = 1

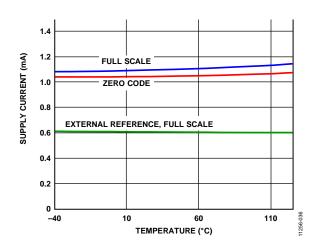

図 35.電源電流の温度特性

図 36.デジタルからアナログへのグリッチ・インパルス

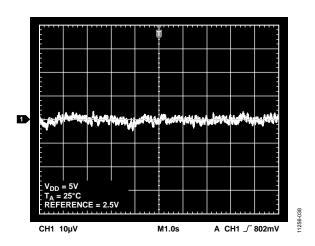

図 37.0.1 Hz~10 Hz での出力ノイズ・プロット 外付けリファレンス電圧

Rev. **0** — 15/28 —

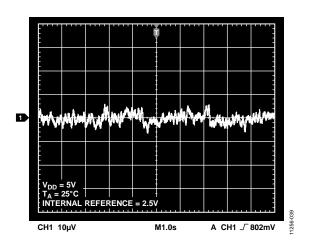

図 38.0.1 Hz~10 Hz 出力ノイズ・プロット 2.5 V 内蔵リファレンス電圧

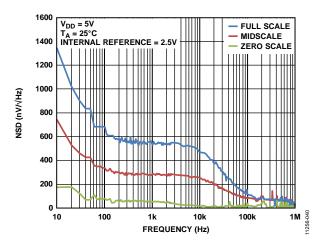

図 39.ノイズ・スペクトル密度(NSD)

図 40.全高調波歪み、1 kHz

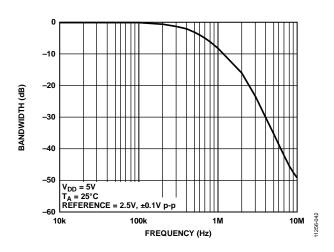

図 41.乗算帯域幅、外付けリファレンス電圧= 2.5 V ±0.1 V p-p、10 kHz~10 MHz

Rev. **0** — 16/28 —

## 用語

#### 相対精度または積分非直線性(INL)

DACの場合、相対精度すなわち積分非直線性は、DAC伝達関数の上下両端を結ぶ直線からの最大乖離(LSB 数で表示)を表します。 図 15と図 18 にコード対 INL (typ) を示します。

#### 微分非直線性(DNL)

微分非直線性(DNL)は、隣接する 2 つのコードの間における測定された変化と理論的な 1 LSB 変化との差をいいます。最大 $\pm 1$  LSB の微分非直線性の規定により、単調性が保証されます。この DAC はデザインにより単調性を保証しています。図 16 と図 19 にコード対 DNL (typ) を示します。

#### ゼロ・コード誤差

ゼロ・コード誤差は、ゼロ・コード(0x0000)を DAC レジスタにロードしたときの出力誤差として測定されます。 理論的には、出力が 0V である必要があります。ゼロ・コード誤差はこのデバイスでは常に正です。これは、DAC と出力アンプのオフセット誤差の組み合わせによって DAC 出力が 0V より低くなることができないためです。ゼロ・コード誤差は mV で表します。ゼロ・コード誤差の温度特性を図 24 に示します。

#### フルスケール誤差

フルスケール誤差は、フルスケール・コード(0xFFFF)を DAC レジスタにロードしたときの出力誤差として測定されます。理論的には出力は  $V_{DD}-1$  LSB である必要があります。フルスケール誤差はフルスケール範囲のパーセント値(FSR 0%)で表します。フルスケール誤差の温度特性を図 23 に示します。

#### ゲイン誤差

ゲイン誤差は DAC のスパン誤差を表します。理論 DAC 伝達特性の傾きからの変位を表し、FSR の%で表示されます。

#### オフセット誤差ドリフト

オフセット誤差ドリフトは、温度変化によるオフセット誤差の変化を表し、 $\mu V/^{\circ}C$ で表されます。

#### ゲイン温度係数

ゲイン温度係数は、温度変化に対するゲイン誤差の変化を表し、 $FSR/^{\circ}C$ のppmで表されます。

#### オフセット誤差

オフセット誤差は、伝達関数の直線領域での $V_{OUT}$ (実測値)と $V_{OUT}$ (理論)の差を表し、mVで表示されます。オフセット誤差は、デバイスのDACレジスタにコード 512をロードして測定されています。この誤差は正または負になります。

#### DC 電源除去比(PSRR)

PSRR は、電源電圧変化の DAC 出力に対する影響を表します。 PSRR は、DAC フルスケール出力での、 $V_{OUT}$ 変化の  $V_{DD}$ 変化に対する比です。これは mV/V で測定されます。  $V_{REF}$ を 2V に維持して、 $V_{DD}$ を $\pm 10\%$ 変化させます。

#### 出力電圧セトリング・タイム

これは、1/4フルスケール入力から3/4フルスケール入力への変化に対して、DAC出力が所定のレベルまでに安定するために要する時間であり、SYNCの立上がりエッジから測定されます。

#### デジタルからアナログへのグリッチ・インパルス

デジタルからアナログへのグリッチ・インパルスは、DAC レジスタ内の入力コードが変化したときに、アナログ出力に混入するインパルスを表します。通常、nV-sec で表すグリッチの面積として規定され、主要キャリ変化時に(0x7FFFから 0x8000)、デジタル入力コードが 1LSB だけ変化したときに測定されます(図 36 参照)。

#### デジタル・フィードスルー

デジタル・フィードスルーは、DAC 出力の更新が行われていないときに、DAC のデジタル入力から DAC のアナログ出力に注入されるインパルスを表します。nV-sec で規定され、データ・バス上でのフルスケール・コード変化時、すなわち全ビット0から全ビット1への変化、またはその逆の変化のときに測定されます。

#### リファレンス・フィードスルー

DAC 出力に変化がない時の DAC 出力における信号振幅のリファレンス入力に対する比であり、dB で表されます。

#### ノイズ・スペクトル密度(NSD)

NSD は、内部で発生されたランダム・ノイズの大きさを表します。 ランダム・ノイズは、スペクトル密度(nV/\Hz)としてキャラクタ ライズされます。DACにミッドスケールを入力し、出力のノイズ を測定して、nV/\Hzで表します。ノイズ・スペクトル密度のプロ ットを図 39に示します。

#### DC クロストーク

別の DAC 出力での変化に起因する 1 つの DAC の出力レベルでの DC 変化。1 つのミッドスケールに維持した DAC をモニタしながら、別の DAC 上でのフルスケール出力変化(またはソフト・パワーダウンとパワーアップ)を使って測定し、 $\mu$ V で表されます。

負荷電流変化に起因する DC クロストークは、1 つの DAC の負荷電流変化がミッドスケールに設定された別の DAC へ与える影響を表し、 $\mu$ V/mA で表わされます。

#### デジタル・クロストーク

1つのDACの入力レジスタにおけるフルスケール・コード変化 (全ビット 0 から全ビット 1 への変化、およびその逆変化)から、 ミッドスケール・レベルにある別のDACの出力に混入したグリ ッチ・インパルスを表し、スタンドアロン・モードで測定し、nVsec で表されます。

#### アナログ・クロストーク

DACの出力変化に起因して、別のDAC出力に混入するグリッチ・インパルスを表し、入力レジスタの1つにフルスケール・コード変化(全ビット0から全ビット1への変化、およびその逆の変化)をロードして測定します。次に、ソフトウェアLDACを実効して、デジタル・コードが変化しないDACの出力をモニタします。グリッチの面積はnV-secで表示します。

#### DAC 間クロストーク

デジタル・コードの変化とそれに続く DACのアナログ出力変化に起因して、別の DAC 出力に混入するグリッチ・インパルス。書込コマンドと更新コマンドを使って、DACの1つにフルスケール・コード変化(全ビット0から全ビット1への変化、およびその逆変化)をロードして、この間にミッドスケールにある別の DAC 出力をモニタすることにより測定します。グリッチのエネルギーは nV-sec で表示します。

#### 乗算帯域幅

DAC内のアンプは有限な帯域幅を持っています。乗算帯域幅はこれを表します。入力された基準正弦波(DACにフルスケール・コードをロード)は、出力に現われます。乗算帯域幅は、出力振幅が入力より3dB小さくなる周波数で表します。

#### 全高調波歪み(THD)

THD は、理論正弦波と DAC を使ったために減衰したその正弦波との差を表します。 DAC に対してリファレンスとして正弦波を使ったときに、DAC 出力に現われる高調波が THD になります。 dB 値で表示します。

#### リファレンス電圧の 温度係数

温度変化に対するリファレンス出力電圧の変化を意味し、リファレンス TC はボックス法を使って計算されます。この方法では、与えられた温度範囲でのリファレンス出力の最大変化として TC を定義し、次式のように ppm/℃で表わします。

$$TC = \left[ \frac{V_{REFmax} - V_{REFmin}}{V_{REFnom} \times TempRange} \right] \times 10^{6}$$

こって

$V_{REFmax}$ は全温度範囲で測定した最大リファレンス出力。  $V_{REFmin}$ は全温度範囲で測定した最小リファレンス出力。

$V_{REFnom}$ は公称リファレンス出力電圧 2.5  $V_{\circ}$

TempRange は規定の温度範囲(-40°C~+105°C)。

Rev. **0** — 18/28 —

## 動作原理

#### D/A コンバータ

AD5689R/AD5687Rは、リファレンス電圧内蔵の 16/12 ビット、シリアル入力、デュアル電圧出力 DAC です。これらのデバイスは 2.7 V~5.5 V の電源電圧で動作します。データは、3 線式シリアル・インターフェースを使用して 24 ビット・ワード・フォーマットで AD5689R/AD5687R へ書込まれます。 デバイスは、パワーオン・リセット回路を内蔵しており、この回路により、パワーアップ時に DAC 出力を既知出力状態に維持することができます。 AD5689R/AD5687Rは、消費電流を 4  $\mu$ A まで減少させるソフトウェア・パワーダウン・モードも持っています。

#### 伝達関数

内蔵リファレンスはデフォルトでオンになっています。外付けリファレンスを使うときは、非リファレンス・オプションのみが使用できます。DACへの入力コーディングはストレート・バイナリを使っているため、外付けリファレンスを使う場合、理論出力電圧は次式で与えられます。

$$V_{OUT} = V_{REF} \times Gain \left[ \frac{D}{2^N} \right]$$

ここで、

Gain は、出力アンプのゲインで、デフォルトで 1 に設定されます。この値は、ゲイン選択ピンを使って $\times$ 1 または $\times$ 2 に設定することができます。GAIN ピンを GND に接続すると、両 DAC 出力の振幅は 0  $V \sim V_{REF}$  になります。GAIN ピンを  $V_{LOGIC}$  に接続すると、両 DAC 出力の振幅は 0  $V \sim 2 \times V_{REF}$  になります。

Dは DAC レジスタにロードされるバイナリ・コードの 10 進数表示です。 12 ビット・デバイスの場合  $0\sim4,095$ 、16 ビット・デバイスの場合  $0\sim65,535$  になります。

Nは、DAC の分解能です。

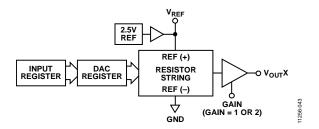

#### DAC アーキテクチャ

DAC アーキテクチャは、ストリング DAC とそれに続く出力アンプから構成されています。図 42 に、DAC アーキテクチャのブロック図を示します。

図 42. DAC 1 チャンネルあたりのアーキテクチャのブロック図

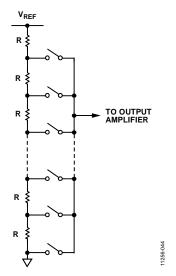

抵抗ストリング構造を図 43 に示します。各値が R の抵抗ストリングから構成されています。DAC レジスタにロードされるコードにより、ストリングのどのノードから電圧を分割して出力アンプへ供給するかが指定されます。

スイッチの内の 1 つが閉じてストリングがアンプに接続されて、電圧が取り出されます。抵抗のストリングであるため、単調整が保証されます。

図 43.抵抗ストリング構造

#### 内蔵リファレンス

AD5689R/AD5687Rの内蔵リファレンスはパワーアップ時にオンになりますが、コントロール・レジスタへの書込みによりディスエーブルすることができます。詳細については、内蔵リファレンスのセットアップのセクションを参照してください。

AD5689R/AD5687R は 2.5 V、2 ppm/°Cのリファレンス電圧を内蔵し、GAIN ピンの状態に応じてフルスケール出力 2.5 V または 5 V になります。デバイスの内蔵リファレンス電圧は  $V_{REF}$  ピンに出力されます。このバッファ付きリファレンス電圧は、最大 10~mA の外部負荷を駆動することができます。

#### 出カアンプ

出力バッファアンプは、出力でレール to レール電圧を発生することができ、0 V $\sim$ V<sub>DD</sub> の出力範囲になります。実際の範囲は、 $V_{REF}$  の値、GAIN ピン、オフセット誤差、ゲイン誤差に依存します。次のように、GAIN ピンで出力のゲインを選択します。

- GAIN ピンを GND に接続すると、両 DAC の出力ゲインは 1 で、出力範囲は  $0 \, V \sim V_{REF}$  になります。

- GAIN ピンを  $V_{LOGIC}$  に接続すると、両 DAC の出力ゲインは 2 で、出力範囲は  $0 \, V \sim 2 \times V_{REF}$  になります。

これらのアンプは、GND  $\land$  接続した  $1 \text{ k}\Omega$  と 2 nF の並列接続負荷を駆動することができます。スルーレートは  $0.8 \text{ V/\mu}$ s であり、1/4 スケールから 3/4 スケールまでのセトリング・タイムは 5 us です。

#### シリアル・インターフェース

AD5689R/AD5687Rは、SPI、QSPI™、MICROWIRE®の各インターフェース規格や太部分の DSP と互換性のある 3 線式シリアル・インターフェース(SYNC、SCLK、SDIN)を内蔵しています。図 2 に、代表的な書込みシーケンスのタイミング図を示します。AD5689R/AD5687Rには SDO ピンがあります。このピンを使うと、複数のデバイスをデイジーチェーン接続することができます(ディジーチェーン動作のセクション参照)。あるいはリードバックに使うことができます。

#### 入力シフトレジスタ

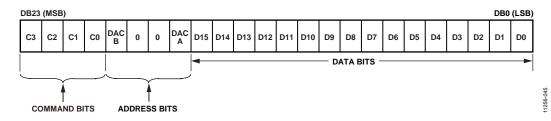

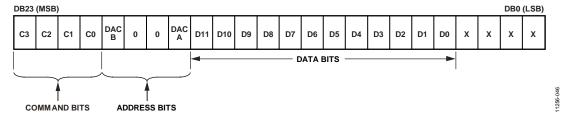

AD5689R/AD5687R の入力シフトレジスタは 24 ビット幅で、データは MSB ファースト (DB23)でロードされます。先頭の 4 ビットはコマンド・ビット C3~C0 です(表 9 参照)。その後ろに、DAC B と DAC A から構成される 4 ビットの DAC アドレス・ビットと、0 に設定された 2 ビットの don't care ビットが続きます(表 8 参照)。入力シフトレジスタの最後は、データワードです。

このデータワードは、16 ビットまたは 12 ビットの入力コード、その後ろに、AD5689Rでは 0 個の don't care ビットが、AD5687Rでは 4 個の don't care ビットが、それぞれ続きます(それぞれ図 44 と図 45 を参照)。これらのデータビットは、SCLK の 24 個の立下がりエッジで入力シフトレジスタへ転送され、SYNCの立上がりエッジで更新されます。

コマンドは、選択したアドレス・ビットに応じて、個別 DAC チャンネル、または両 DAC チャンネルに対して実行することができます。

表 8.アドレス・コマンド

|       | Addres | s (n) |       |                      |

|-------|--------|-------|-------|----------------------|

| DAC B | 0      | 0     | DAC A | Selected DAC Channel |

| 0     | 0      | 0     | 1     | DAC A                |

| 1     | 0      | 0     | 0     | DAC B                |

| 1     | 0      | 0     | 1     | DAC A and DAC B      |

表 9.コマンドの定義

|    | Co | mmand |    |                                                         |

|----|----|-------|----|---------------------------------------------------------|

| С3 | C2 | C1    | C0 | Description                                             |

| 0  | 0  | 0     | 0  | No operation                                            |

| 0  | 0  | 0     | 1  | Write to Input Register n (dependent on LDAC)           |

| 0  | 0  | 1     | 0  | Update DAC Register n with contents of Input Register n |

| 0  | 0  | 1     | 1  | Write to and update DAC Channel n                       |

| 0  | 1  | 0     | 0  | Power down/power up DAC                                 |

| 0  | 1  | 0     | 1  | Hardware LDAC mask register                             |

| 0  | 1  | 1     | 0  | Software reset (power-on reset)                         |

| 0  | 1  | 1     | 1  | Internal reference setup register                       |

| 1  | 0  | 0     | 0  | Set up DCEN register (daisy-chain enable)               |

| 1  | 0  | 0     | 1  | Set up readback register (readback enable)              |

| 1  | 0  | 1     | 0  | Reserved                                                |

|    |    |       |    | Reserved                                                |

| 1  | 1  | 1     | 1  | Reserved                                                |

図 44.AD5689R の入力シフトレジスタ値

図 45.AD5687R の入力シフトレジスタ値

#### スタンドアロン動作

SYNCラインをロー・レベルにすると、書込みシーケンスが開始 されます。SDIN ラインからのデータは、SCLK の立下がりエッジ で 24 ビット入力シフトレジスタに入力されます。24 個のデータ ビットの最後を入力した後に、SYNCをハイ・レベルにします。 その後で設定された機能、すなわち DAC レジスタ値の LDACに依 存した変更および/または動作モード変更が実行されます。24番 目のクロックの前で SYNCがハイ・レベルになると、有効なフレ ームで無効なデータが DAC にロードされたと見なされま す。SYNCの立下がりエッジで次の書込みシーケンスを確実に開 始できるようにするため、次の書込みシーケンスの前に SYNCを 最小 20 ns 間 (シングル・チャンネル、図 2 の ts参照)ハイ・レベル にする必要があります。デバイスをさらに低消費電力動作させる ため、書込みシーケンスの間に SYNCを電源レールにアイドルさ せる必要があります。SYNCラインは SCLK の 24 個の立下がりエ ッジ間ロー・レベルに維持され、DAC は SYNCの立上がりエッジ で更新されます。

データがTドレス指定された DAC の入力レジスタへ転送された ときに、 $\overline{SYNC}$ ラインがハイ・レベルの間に  $\overline{LDAC}$ をロー・レベルにすると、両 DAC レジスタと両出力を更新することができます。

#### 書込コマンドと更新コマンド

#### 入力レジスタ n への書込(LDACに依存)

コマンド 0001 を使うと、各  $\underline{DAC}$  の専用入力レジスタへ個別に書込みを行うことができます。 $\underline{LDAC}$  がロー・レベルのとき、入力レジスタはトランスペアレントになります( $\underline{LDAC}$ マスク・レジスタから制御されていない場合)。

#### 入力レジスタ n の値による DAC レジスタ n の更新

コマンド 0010 は、選択した入力レジスタ値を DAC レジスタ/出力へロードして DAC 出力を直接更新します。

#### DAC チャンネル n への書込と更新(LDAC 非依存)

コマンド 0011 を使うと、DAC レジスタへ書込みを行なって、DAC 出力を直接更新することができます。

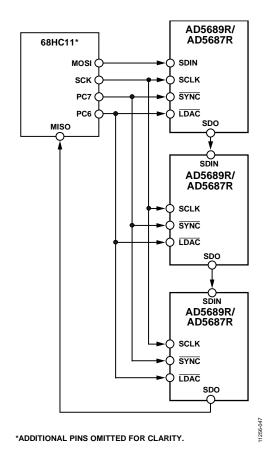

#### デイジーチェーン動作

複数の DAC を使うシステムでは、SDO ピンを使って複数のデバイスをデイジーチェーン接続することができます。SDO は、ソフトウェアからディジーチェイン・イネーブル(DCEN)コマンドを実行してイネーブルします。コマンド 1000 は、この DCEN 機能として予約されています(表 9 参照)。デイジーチェーン・モードは、DCEN レジスタのビット(DB0)をセットしてイネーブルします。デフォルト設定はスタンドアロン・モードで、DB0 (LSB) = 0 になっています。表 10 に、ビットの状態とデバイスの動作モードとの対応を示します。

表 10.デイジーチェーン・イネーブル(DCEN)レジスタ

| DB0 (LSB) | Description               |

|-----------|---------------------------|

| 0         | Standalone mode (default) |

| 1         | DCEN mode                 |

図 46.複数の AD5689R/AD5687R デバイスのディジーチェイン接続

SYNCがロー・レベルのとき、SCLK ピンは連続的に入力シフトレ ジスタに接続されます。24 個を超えるクロック・パルスが入力さ れると、データは入力シフトレジスタからはみ出して、SDO ピン に出力されます。データは SCLK の立上がりエッジで出力され、 SCLK の立下がりエッジで有効になります。このラインをチェー ン内の次の DAC の SDIN 入力に接続すると、デイジーチェーン・ インターフェースが構成されます。システム内の各 DAC は、24 個のクロック・パルスを必要とします。したがって、必要な合計 クロック・サイクル数は 24×N になります。ここで、N は<u>更新</u>さ れる合計デバイス数です。24 の整数倍でないクロックで SYNCが ハイ・レベルになると、有効なフレームと無効なデータが DAC にロードされたものと見なされます。すべてのデバイスに対する シリアル転送が完了したら、SYNCをハイ・レベルにします。こ の動作により、デイジーチェーン内にある各デバイス内の入力デ ータがラッチされて、入力シフトレジスタにさらにデータが入力 されるのを防止します。シリアル・クロックとしては、連続クロ ックまたはゲーティド・クロックが可能です。正しいクロック・ サイクル数間、SYNCをロー・レベルに維持することが可能な場 合にのみ、連続 SCLK ソースを使用することができます。ゲーテ ィド・クロック・モードでは、所定数のクロック・サイクルを含 むバースト・クロックを使い、最終クロックの後に SYNCをハ イ・レベルにしてデータをラッチする必要があります。

Rev. 0

#### リードバック動作

リードバック・モードは、ソフトウェアからリードバック・コマ ンドを実行して開始します。コントロール・レジスタのデイジー チェーン・モード・ディスエーブル・ビットを使って SDO 出力を ディスエーブルすると、再度ディスエーブルされた後に、読出し 動作の間自動的にイネーブルされます。 コマンド 1001 はリードバ ック機能に予約されています。このコマンドは、アドレス・ビッ ト DAC B または DAC A の選択に対応して、読出し対象レジスタ を選択します。リードバックでは 1 個の DAC レジスタだけが選 択可能であることに注意してください。 残りの 3 個のアドレス・ ビット(2 ビットの don't care ビットを含む)はロジック 0 に設定する 必要があります。書込みシーケンス内の残りのデータビットは無 視されます。複数のアドレス・ビットを選択した場合、またはア ドレス・ビットを選択しない場合、デフォルトで DAC チャンネ ルAがリードバックされます。次のSPIへの書込み時にSDOに出 力されるデータに、前にアドレス指定したレジスタのデータが含 まれています。

例えば、チャンネル A の DAC レジスタをリードバックするときは、次のシーケンスを使うことができます。

- 1. 0x900000 をAD5689R/AD5687R 入力レジスタへ書込みます。 この動作により、デバイスが読出しモードに設定され、チャンネル A の DAC レジスタが選択されます。\_データビット DB15~DB0 は無視されることに注意してください。

- 2. この書込み動作の後に、NOP 条件 0x000000 を書込む 2つ目 の書込みを行います。この書込みで、レジスタからのデータ が SDO ラインへ出力されます。DB23~DB20 には未定義データが格納され、最後の 16 ビットに DAC レジスタ値の DB19~DB4 が格納されます。

#### パワーダウン動作

AD5689R/AD5687R には 3 種類のパワーダウン・モードがあります。コマンド 0100 はパワーダウン機能を制御します (表 9 参照)。これらのパワーダウン・モードは、入力シフトレジスタの 8 ビット(ビット DB7〜ビット DB0)を設定することにより、ソフトウェアから設定することができます。各 DAC チャンネルに対応した 2 ビットがあります。表 11 に、2 ビットの状態とデバイスの動作モードとの対応を示します。

対応するビットをセットすることにより、DAC (DAC B または DAC A の一方または両方)を選択したモードにパワーダウンさせることができます。パワーダウン/パワーアップ動作時の入力シフトレジスタ値については表 12 を参照してください。

表 11.動作モード

| Operating Mode               | PDx1 | PDx0 |

|------------------------------|------|------|

| Normal Operation Mode        | 0    | 0    |

| Power-Down Modes             |      |      |

| $1 \text{ k}\Omega$ to GND   | 0    | 1    |

| $100 \text{ k}\Omega$ to GND | 1    | 0    |

| Three-State                  | 1    | 1    |

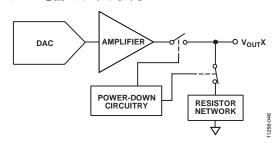

入力シフトレジスタのビット PDx1 とビット PDx0 (x は選択したチャンネル)を 0 に設定すると、デバイスは通常の消費電力(5 V で 4 mA)で通常動作しますが、AD5689R/AD5687Rの3つのパワーダウン・モードでは、電源電流は 5 V で 4  $\mu$ Aに減少します。電源電流が減少するだけでなく、出力ステージも内部でアンプ出力から既知値の抵抗回路へ切り替えられます。この切り替えは、デバイスの出力インピーダンスが既知であると同時にデバイスがパワーダウン・モードになるという利点を持っています。3 種類のパワーダウン・オプションは次の通りです。

- 出力が内部で  $1 k\Omega$  の抵抗を介して GND に接続されます。

- 出力が内部で  $100 \text{ k}\Omega$  の抵抗を介して GND に接続されます。

- 出力がオープンになります(スリー・ステート)。

出力ステージを図47に示します。

図 47.パワーダウン時の出力ステージ

パワーダウン・モードのときは、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、およびその他の関係するリニア回路はシャットダウンされます。ただし、DAC レジスタ値はパワーダウン・モードで影響を受けないため、デバイスのパワーダウン・モード中でも DAC レジスタを更新することができます。パワーダウンから抜け出すために要する時間は、 $V_{DD}=5~V~c~4.5~\mu s~(typ)$ です。消費電流をさらに減らすときは、内蔵リファレンスをパワーオフさせることができます(内蔵リファレンスのセットアップのセクション参照)。

表 12.パワーダウン/パワーアップ動作の 24 ビット入力シフトレジスタ値  $^1$

| DB23<br>(MSB) | DB22                    | DB21 | DB20 | DB19 to DB16 | DB15 to DB8  | DB7  | DB6             | DB5 | DB4  | DB3 | DB2  | DB1  | DB0<br>(LSB)    |

|---------------|-------------------------|------|------|--------------|--------------|------|-----------------|-----|------|-----|------|------|-----------------|

| 0             | 1                       | 0    | 0    | X            | X            | PDB1 | PDB0            | 1   | 1    | 1   | 1    | PDA1 | PDA0            |

| C             | Command bits (C3 to C0) |      |      | Address bits | ; don't care |      | -down,<br>DAC B | Set | to 1 | Set | to 1 |      | -down,<br>DAC A |

<sup>1</sup> X = don't care.

#### DAC のロード (ハードウェアLDACピン)

AD5689R/AD5687R のDAC は、入力レジスタと DAC レジスタの 2 つのレジスタ・バンクで構成されているダブルバッファ化されたインターフェースを内蔵しています。入力レジスタの任意の組み合わせへ書込みを行うことができます。 DAC レジスタの更新は、LDACピンから制御されます。

図 48.1 個の DAC についての入力ロード回路の簡略化した図

#### DAC の瞬時更新(LDACをロー・レベルに維持)

コマンド 0001 を使ってデータを入力レジスタへ入力する間  $\overline{\text{LDAC}}$  をロー・レベルに維持します。アドレス指定された入力レジスタ と DAC レジスタが  $\overline{\text{SYNC}}$ の立上がりエッジで更新されて、出力が変化を開始します(表 14 と表 15 参照)。

#### DAC の遅延更新 (LDACへ立下がりパルスを入力)

コマンド 0001 を使ってデータを入力  $\underline{\nu y}$ スタへ入力するとき  $\underline{LDAC}$ をハイ・レベルに維持します。 $\underline{SYNC}$ をハイ・レベルにした後に  $\underline{LDAC}$ をロー・レベルにすることにより、両  $\underline{DAC}$ 出力が非同期で更新されます。更新は、 $\underline{LDAC}$ の立下がりエッジで行われるようになります。

#### LDAC マスク・レジスタ

コマンド 0101 は、アドレス・ビットを無視させるソフトウェア  $\overline{\text{LDAC}}$  マスク機能用に予約されています。コマンド 0101 を使って DAC へ書込を行うと、4 ビットの  $\overline{\text{LDAC}}$  マスク・レジスタ (DB3~DB0)がロードされます。各チャンネルのデフォルト値は 0、すなわち  $\overline{\text{LDAC}}$  ピンはノーマル動作になります。選択したビットを 1 に設定すると、ハードウェア  $\overline{\text{LDAC}}$  ピンの状態に無関係に、この DAC  $\underline{\text{F}}$  ヤンネルは  $\overline{\text{LDAC}}$  ピンに対応させてチャンネルを選択するアプリケーションで役立ちます。

この  $\overline{\text{LDAC}}$ マスク・レジスタを使うと、ハードウェア  $\overline{\text{LDAC}}$ ピン を柔軟に制御することができます(表 13 参照)。ある  $\overline{\text{DAC}}$  チャンネルに対して  $\overline{\text{LDAC}}$ ビット( $\overline{\text{DB3}}$ 、 $\overline{\text{DB0}}$ )を  $\overline{\text{0}}$  に設定することは、このチャンネルの更新がハードウェア  $\overline{\text{LDAC}}$ ピンから制御されることを意味します。

#### 表 13.LDAC 上書きの定義

| Load LDA                | C Register     |                                                                                                                 |

|-------------------------|----------------|-----------------------------------------------------------------------------------------------------------------|

| LDAC Bits<br>(DB3, DB0) | LDAC Pin       | LDAC Operation                                                                                                  |

| 0                       | 1 or 0         | Determined by the LDAC pin.                                                                                     |

| 1                       | X <sup>1</sup> | DA <u>C</u> channels update and override the <u>LDAC</u> pin. DAC channels see the <u>LDAC</u> pin as set to 1. |

$<sup>^{1}</sup>$  X = don't care

表 14. LDAC 動作に対する 24 ビット入力シフトレジスタ値 <sup>1</sup>

| DB23<br>(MSB)                        | DB22 | DB21 | DB20 | DB19         | DB18 | DB17       | DB16        | DB15 to DB4 | DB3            | DB2        | DB1 | DB0<br>(LSB) |

|--------------------------------------|------|------|------|--------------|------|------------|-------------|-------------|----------------|------------|-----|--------------|

| 0                                    | 0    | 0    | 1    | X            | X    | X          | X           | X           | DAC B          | 0          | 0   | DAC A        |

| Command bits (C3 to C0) Address bits |      |      |      | s, don't car | re   | Don't care | Setting the | LDAC bit to | 1 overrides th | e LDAC pin |     |              |

<sup>1</sup> X = don't care

#### 表 15.書込コマンドと LDAC ピンの真理値表 <sup>1</sup>

| Command | Description                            | Hardware LDAC Pin State | Input Register Contents | DAC Register Contents                |  |  |

|---------|----------------------------------------|-------------------------|-------------------------|--------------------------------------|--|--|

| 0001    | Write to Input Register n (dependent   | $V_{LOGIC}$             | Data update             | No change (no update)                |  |  |

|         | on LDAC)                               | GND <sup>2</sup>        | Data update             | Data update                          |  |  |

| 0010    | Update DAC Register n with contents of | $V_{LOGIC}$             | No change               | Updated with input register contents |  |  |

|         | Input Register n                       | GND                     | No change               | Updated with input register contents |  |  |

| 0011    | Write to and update DAC Channel n      | $V_{LOGIC}$             | Data update             | Data update                          |  |  |

|         |                                        | GND                     | Data update             | Data update                          |  |  |

$<sup>^1</sup>$  ハードウェア $\overline{\text{LDAC}}$ ピンのハイ・レベルからロー・レベルへの変化により、常に DAC レジスタ値が、 $\overline{\text{LDAC}}$ マスク・レジスタでマスクされていないチャンネルの入力 レジスタ値で更新されます。

$<sup>^{2}\</sup>overline{\text{LDAC}}$ をロー・レベルに固定すると、 $\overline{\text{LDAC}}$ マスク・ビットは無視されます。

#### ハードウェア・リセット(RESET)

RESET はアクティブ・ローのリセットで、出力をゼロスケールまたはミッドスケールへクリアできるようにします。クリア・コード値は、パワーオン・リセット・セレクト・ピン(RSTSEL)を使って選択することができます。 動作を完了するためには、RESETを最小時間ロー・レベルに維持する必要があります(図 2 参照)。RESET信号がハイ・レベルに戻っても、新しい値が設定されるまで出力はクリア値を維持します。RESETピンがロー・レベルの間、出力は新しい値で更新できません。これらのデバイスには、DACをパワーオン・リセット・コードにリセットする、ソフトウェアからのリセット機能もあります。コマンド 0110 は、このソフトウェア・リセット機能に割り当てられています(表 9 参照)。パワーオン・リセット時の  $\overline{\text{LDAC}}$ または  $\overline{\text{RESET}}$ の動作はすべて無視されます。

#### リセット選択ピン(RSTSEL)

AD5689R/AD5687R は、パワーアップ時に出力電圧を制御するパワーオン・リセット回路を内蔵しています。RSTSEL ピンをロー・レベル(GND)に接続すると、出力はゼロスケールでパワーアップします。これは DAC のリニア領域外であることに注意してください。RSTSEL ピンをハイ・レベル( $V_{LOGIC}$ )に接続すると、 $V_{OUT}X$  はミッドスケールでパワーアップします。出力はこのレベルでパワーアップを維持し、有効な書込みシーケンスが実行されるまでこの状態が維持されます。

#### 内蔵リファレンスのセットアップ

コマンド 0111 は、この内蔵リファレンスの設定に予約されています (表 9 参照)。内蔵リファレンスはパワーアップ時にデフォルトでオンになっています。電源電流を減少させるときは、ソフトウェアから設定可能なビット DBO をセットすることにより、このリファレンスをターンオフさせることができます(表 17 参照)。表 16 に、ビットの状態と対応するデバイスの動作モードを示します。

表 16.リファレンス・セットアップ・レジスタ

| Internal Reference<br>Setup Register (DB0) | Action                 |

|--------------------------------------------|------------------------|

| 0                                          | Reference on (default) |

| 1                                          | Reference off          |

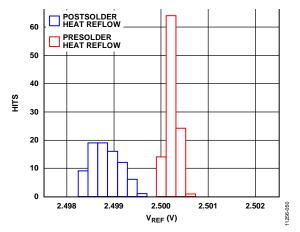

#### ハンダ加熱リフロー

すべての IC リファレンス電圧回路と同様に、リファレンス値がハンダ処理でシフトすることがあります。アナログ・デバイセズは、デバイスをボードへハンダ付けする影響を模倣する、プリコンディションと呼ばれる信頼性テストを実施しています。表 2 の出力電圧仕様には、この信頼性テストの影響が含まれます。

図 49 に、この信頼性テスト(プリコンディション)で測定したハンダ加熱リフロー(SHR)の影響を示します。

図 49.SHR でのリファレンス電圧シフト

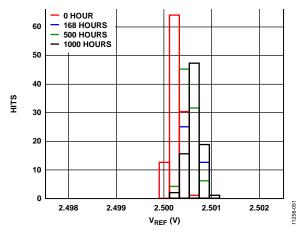

#### 長時間温度ドリフト

図 50 に、150°C の寿命テストにおける 1000 時間後の  $V_{\text{REF}}$ 値変化を示します。

図 50.1000 時間でのリファレンス電圧ドリフト

表 17.内蔵リファレンス・セットアップ・コマンドに対する 24 ビット入力シフトレジスタ値 1

| DB23<br>(MSB)           | DB22 | DB21 | DB20 | DB19                    | DB18 | DB17 | DB16 | DB15 to DB1 | DB0 (LSB)                |

|-------------------------|------|------|------|-------------------------|------|------|------|-------------|--------------------------|

| 0                       | 1    | 1    | 1    | X                       | X    | X    | X    | X           | 1 or 0                   |

| Command bits (C3 to C0) |      |      |      | Address bits (A3 to A0) |      |      |      | Don't care  | Reference setup register |

<sup>1</sup> X = don't care

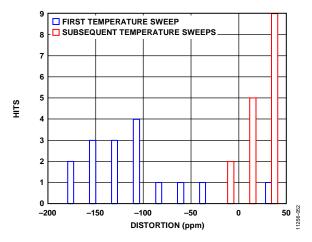

#### 熱ヒステリシス

熱ヒステリシスは、周囲温度→低温→高温→周囲温度で温度変化させた場合にリファレンス電圧に発生する電圧差です。

熱ヒステリシス・データを図 51 に示します。このデータは、周囲温度 $\rightarrow$ 40°C $\rightarrow$ +105°C $\rightarrow$ 周囲温度で温度変化させて測定したものです。そこで、 $V_{REF}$ の変化分を 2 つの周囲温度の間で測定し、図 51 に青で示します。同じ温度変化と測定を直ちに繰り返し、その結果を図 51 に赤で示します。

図 51.熱ヒステリシス

Rev. **0** — 25/28 —

## アプリケーション情報

#### マイクロプロセッサ・インターフェース

マイクロプロセッサと AD5689R/AD5687R とのインターフェースは、マイクロコントローラと DSP プロセッサに対して互換性を持つ標準プロトコルを使うシリアル・バスを使って行います。この通信チャンネルには、クロック信号、データ信号、同期信号から構成される 3 線式または 4 線式のインターフェースが必要です。各デバイスでは、24 ビットのデータ・ワードを使用し、SYNCの立上がりエッジでデータが有効である必要があります。

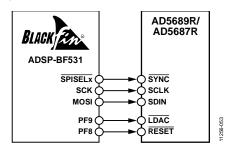

## AD5689R/AD5687R と ADSP-BF531 とのインターフェース

AD5689R/AD5687R の SPI インターフェースは、業界標準の DSP とマイクロコントローラに容易に接続できるようにデザインされています。図 52 に、AD5689R/AD5687R とアナログ・デバイセズの Blackfin® DSP との接続方法を示します。Blackfin は、AD5689R/AD5687R の SPI ピンへ直接接続できる SPI ポートを内蔵しています。

図 52.ADSP-BF531 と AD5689R/AD5687R とのインターフェース

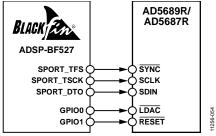

#### AD5689R/AD5687R とSPORT とのインターフェ ース

アナログ・デバイセズの ADSP-BF527 は、1 個の SPORT シリアル・ポートを内蔵しています。図 53 に、1 個の SPORT インターフェースを使って、AD5689R/AD5687R を制御する方法を示します。

図 53.SPORT と AD5689R/AD5687R とのインターフェース

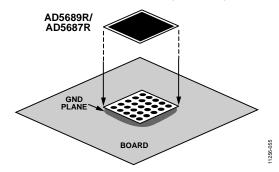

#### レイアウトのガイドライン

高精度が重要となる回路では、電源とグラウンド・リターンのレイアウトを注意深く行うことが、定格性能の保証に役立ちます。 AD5689R/ AD5687R を実装する PCB は、AD5689R/AD5687R をアナログ・プレーン上に配置するようにデザインする必要があります。

AD5689R/AD5687R に対しては、 $10 \mu F \ \ \, 0.1 \mu F$  の並列接続により十分な電源バイパスをパッケージのできるだけ近くに、理想的にはデバイスに直接に、接続する必要があります。 $10 \mu F$  コンデンサはタンタルのビーズ型を使います。 $0.1 \mu F$  のコンデンサは、高周波でグラウンドに対する低インピーダンス・パスを提供する

セラミック型のような実効直列抵抗(ESR)が小さく、かつ実効直列インダクタンス(ESI)が小さいものを使って、内部ロジックのスイッチングに起因する過渡電流を処理する必要があります。

1 枚のボード上に多くのデバイスを実装するシステムでは、ヒート・シンク能力を設けて電力の消費を容易にすることが有効であることがあります。

AD5689RまたはAD5687Rには、デバイスの底にエクスポーズド・パッドが設けてあります。このパッドをデバイスのGNDへ接続してください。最適性能を得るためには、マザーボードのデザインに特別な注意を払って、パッケージを実装してください。熱的性能、電気的性能、ボード・レベルの性能を強化するため、パッケージ底面のエクスポーズド・パッドは対応する PCB のサーマル・ランド・パッドにハンダ付けしてください。PCB ランド・パッド領域にサーマル・ビアを配置するようにデザインしてさらに熱放散を強化してください。

自然なヒート・シンク効果を提供するため、デバイス上の GND プレーンを大きくすることができます(図 54参照)。

図 54.パッドとボードの接続

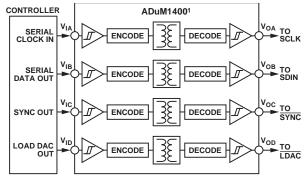

#### 電流絶縁型インターフェース

多くのプロセス制御アプリケーションでは、コントローラと被制御対象のユニットとの間にアイソレーション障壁を設けて、危険な同相モード電圧から制御回路を保護してアイソレーションすることが必要です。アナログ・デバイセズの iCoupler®製品ファミリーは、2.5~kV を超える電圧アイソレーションを提供します。AD5689R/AD5687R はシリアル・ローディング方式を採用しているため、インターフェース・ライン数が最小になっているので、絶縁インターフェース向けに最適です。図 55~c に、ADuM1400 を使用して構成した、AD5689R/AD5687R への 4~f キャンネル絶縁型インターフェースを示します。詳細については、www.analog.com/icouplersをご覧ください。

図 55.絶縁型インターフェース

<sup>1</sup>ADDITIONAL PINS OMITTED FOR CLARITY.

1256-056

## 外形寸法

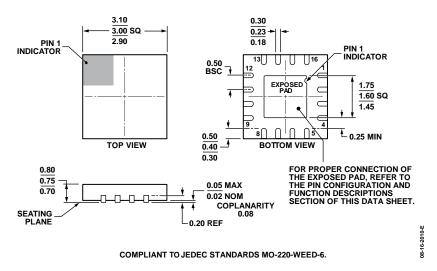

図 56.16 ピン・リードフレーム・チップ・スケール・パッケージ[LFCSP\_WQ] 3 mm x 3 mm ボディ、極薄クワッド (CP-16-22) 寸法: mm

COMPLIANT TO JEDEC STANDARDS MO-153-AB

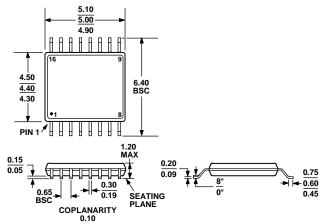

図 57.16 ピン薄型シュリンク・スモール・アウトライン・パッケージ[TSSOP] (RU-16) 寸法: mm

Rev. **0** — 27/28 —

## オーダー・ガイド

| Model <sup>1</sup> | Resolution | Temperature<br>Range | Accuracy   | Reference<br>Tempco<br>(ppm/°C) | Package<br>Description | Package<br>Option | Branding |

|--------------------|------------|----------------------|------------|---------------------------------|------------------------|-------------------|----------|

| AD5689RACPZ-RL7    | 16 Bits    | -40°C to +105°C      | ±8 LSB INL | ±5 (typ)                        | 16-Lead LFCSP_WQ       | CP-16-22          | DLU      |

| AD5689RBCPZ-RL7    | 16 Bits    | −40°C to +105°C      | ±2 LSB INL | ±5 (max)                        | 16-Lead LFCSP_WQ       | CP-16-22          | DL2      |

| AD5689RARUZ        | 16 Bits    | −40°C to +105°C      | ±8 LSB INL | ±5 (typ)                        | 16-Lead TSSOP          | RU-16             |          |

| AD5689RARUZ-RL7    | 16 Bits    | −40°C to +105°C      | ±8 LSB INL | ±5 (typ)                        | 16-Lead TSSOP          | RU-16             |          |

| AD5689RBRUZ        | 16 Bits    | -40°C to +105°C      | ±2 LSB INL | ±5 (max)                        | 16-Lead TSSOP          | RU-16             |          |

| AD5689RBRUZ-RL7    | 16 Bits    | −40°C to +105°C      | ±2 LSB INL | ±5 (max)                        | 16-Lead TSSOP          | RU-16             |          |

| EVAL-AD5689RSDZ    |            |                      |            |                                 | Evaluation Board       |                   |          |

| AD5687RBCPZ-RL7    | 12 Bits    | −40°C to +105°C      | ±1 LSB INL | ±5 (max)                        | 16-Lead LFCSP_WQ       | CP-16-22          | DL1      |

| AD5687RBRUZ        | 12 Bits    | −40°C to +105°C      | ±1 LSB INL | ±5 (max)                        | 16-Lead TSSOP          | RU-16             |          |

| AD5687RBRUZ-RL7    | 12 Bits    | −40°C to +105°C      | ±1 LSB INL | ±5 (max)                        | 16-Lead TSSOP          | RU-16             |          |

| EVAL-AD5687RSDZ    |            |                      |            |                                 | Evaluation Board       |                   |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS 準拠製品。