# **AN-793** アプリケーション・ノート

# iCoupler $^{\circ}$ アイソレータ製品のESD/ラッチアップに関する考慮事項

著者: Rich Ghiorse

# はじめに

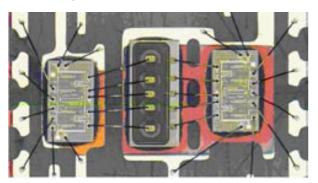

アナログ・デバイセズのiCoupler製品は、集積度、性能、消費 電力特性に優れた、フォトカプラに代わる絶縁ソリューション を提供します。iCoupler絶縁チャンネルは、CMOS入力および 出力回路とチップ・スケールのトランスで構成されています (図1を参照)。iCouplerはCMOS技術を採用しているため、シ ステム・レベルの静電気放電 (ESD) やサージ電圧、高速トラ ンジェント、またはその他の過電圧状態が発生すると、フォト カプラよりもラッチアップまたはESDによる損傷を受けやすく なっています。

図1. ADuM140xクワッド・アイソレータ

このアプリケーション・ノートは、これらの問題を解決するた めの指針を示します。システム・レベルの各種のテスト設定を 例にとり、性能に悪影響を及ぼす可能性のあるメカニズムにつ いて説明します。またその例に対して推奨するソリューション を紹介します。

アナログ・デバイセズは2005年後半、大部分のiCoupler製品に ついて、ラッチアップと電気的過大ストレス(EOS)に対する 耐性を強化したモデルを発売する予定です。この新しい製品 ファミリーADuM3xxxシリーズは、既存のADuM1xxxシリー ズ製品とピン互換で、同一の性能仕様となっています。 ADuM3xxxシリーズのリリース後も、ADuM1xxxシリーズは 引き続き販売する予定です。

# 部品かシステムか

簡単に言えば、部品とは相互配線された単一の集積化デバイス であり、システムとは相互配線された複数の部品からなる非集 積化デバイスです。ほとんどの場合、部品とシステムは明確に 区別できます。しかし、部品テストとシステム・テストの区別 はそれほど明確ではありません。さらに、システム・レベルの テストでデバイスがどのように動作するかを部品の仕様から直 接予想できない場合もあります。ESDテストがその例です。

ESD、サージ、バースト、高速トランジェントは、エレクトロ ニクス・アプリケーションにおいては避けられないものです。 これらの事象においては一般的に、高電圧で持続時間の短いス パイクがデバイスに対して直接または間接に加わります。これ は、人間の接触、ACラインの摂動、雷撃、システム・グラウ ンド間の同相電圧差などのように、デバイスと実環境の現象と の相互作用が原因で発生します。

部品レベルのESDテストは、部品をシステムにアセンブリする 前やアセンブリ時に作業者や自動アセンブリ装置が行うハンド リングに対してデバイスのESD耐性を判断するには非常に役立 ちます。しかし、システム・レベルのESD事象が発生したとき の内部デバイスのESD耐性を判断するには、部品レベルのESD データはあまり役に立ちません。これには、以下の2つの理由 があります。

- システム・レベルと部品レベルのESDテストは、その目的が 異なります。部品レベルのテストは、一般的に部品のハンド リングとアセンブリ時の条件下におけるESD耐性を判断する ことを目的としています。システム・レベルのテストは、-般的にシステムの動作時の条件下におけるESD耐性を判断す ることを目的としています。

- システム・レベルのテスト時に部品に適用される条件が、実 装されるボード/モジュール/システムの設計に応じて大き く変わる場合があります。たとえば、システム・グラウンド と部品グラウンド間の誘導性のパターン配線が長いと、テス ト時より大きな電圧トランジェントが部品上に印加されます。

REV. 0

アナログ・デバイセズ株式会社

ADuM140xクワッド・アイソレータのESDテスト結果を表Iにまとめています。これによれば、iCouplerを使用できるのは、ESD耐圧の定格値が4kVよりも低いシステムに限られるということになります。しかし実際には、IEC 61000-4-2規格に準拠した15kV ESDレベルのシステムで、iCouplerがごく一般的に使用されています。

こうしたずれが生じる原因はテストの方法にあります。部品レベルのテストでは、電源が投入されていない状態にあるデバイスのピンまたはボディに対してESD事象を直接印加します。これに対しシステム・レベルのテストでは、外部のESD事象に接する可能性のあるシステム内部のさまざまな箇所に対してESD事象を加えることが求められています。さらに、部品レベルとシステム・レベルのテストで使用する信号波形も異なります。

表I. ADuM140xのESDテスト結果

| ESDモデル                         | 最初の<br>合格電圧(V) | 最初の<br>不合格電圧(V) |

|--------------------------------|----------------|-----------------|

| 人体モデル<br>フィールド誘導電荷<br>デバイス・モデル | 3,500<br>1,500 | 4,000<br>2,000  |

| マシン・モデル                        | 200            | 400             |

アナログ・デバイセズのESDテストに関する詳細は、『アナログ・デバイセズ信頼性 ハンドブック』を参照してください。

システムの内部で使用するiCouplerの性能を正確に予測するには、システム・テストの特性を理解したうえで、これらのテストが部品レベルでのiCouplerにどのように影響しているかを評価する必要があります。表IIは、iCouplerのアプリケーションで使用する一般的なシステム・レベルのテストを示します。これらのテストの事例をいくつか後述します。

表II. iCouplerのアプリケーションで使用する一般的なシステム・レベルのテスト

| テスト規格        | 目的         | テスト電圧<br>(Vrms) <sup>1</sup> |

|--------------|------------|------------------------------|

| IEC61000-4-2 | ESD        | 2,000~15,000                 |

| IEC61000-4-4 | 高速トランジェント/ | 500~4,000                    |

|              | バースト       |                              |

| IEC61000-4-5 | サージ        | 500~4,000                    |

<sup>&</sup>lt;sup>1</sup> IEC 61000-4テストには、コンプライアンス・レベルが含まれます。上の表に記載するテスト電圧は、レベル1 (最小)からレベル4 (最大)までのコンプライアンス電圧レンジです。

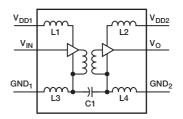

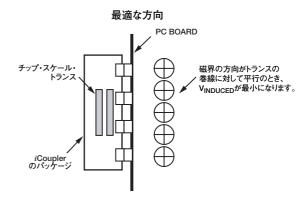

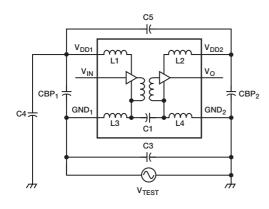

システム・テスト性能を解析するためのiCouplerモデルシステム・レベルのテストの影響を理解するために役立つiCouplerの回路モデルを図2に示します。インダクタL1、L2、L3、L4は主にパッケージ・ピンとボンディング・ワイヤを、コンデンサC1は絶縁パリア間の浮遊容量を考慮したものです。インダクタンス値は約0.2nHです。容量値はiCouplerチャンネルあたり約0.3pFです。

図2. システム設計の解析に役立つiCouplerモデル

# CMOSデバイスのラッチアップ

CMOSプロセスでは本来、シリコン制御整流器(SCR)として構成される寄生のPNPおよびNPNトランジスタを使用します。ラッチアップとは、この寄生SCRがトリガされるときの状態です。これによって $V_{DD}$ とグラウンド間に低い抵抗値が発生し、その後大きい電流が引き込まれ、これがデバイスを通過します。この過大な電流レベルによって、EOSによるデバイスの損傷が生じる場合があります。

ラッチアップによって発生する損傷は、デバイスの完全な破壊からパラメータ性能の劣化までさまざまです。さらに厄介なのは潜在的な障害で、後になってシステムの動作に悪影響を及ぼしかねません。ラッチアップ全般の問題の対処法を扱った「Winning the Battle Against Latch-Up in CMOS Switches」(CMOSスイッチのラッチアップの問題を解決する手法)という優れた論文が、『Analog Dialog35-05』(2001年発行)に掲載されています。この記事ではCMOSスイッチに関する問題を取り上げていますが、その内容はiCouplerを含むすべてのCMOSデバイスにおおむね適用できます。

iCouplerを使用するすべてのアプリケーションでは、 $V_{DD}$ とグラウンド間の電源ノイズを最小限に抑えるために、バイパス用のセラミック・コンデンサを外付けすることを特に推奨します。これらのコンデンサの容量は $0.01\sim0.1\mu$ Fとし、可能な限りiCouplerデバイスに近い位置に実装してください。アプリケーションによっては、十分なバイパス処理を行った場合でもラッチアップの問題が発生することがあります。このような場合、さらに $200\Omega$ の抵抗を $V_{DD}$ と直列に接続すると、良好な結果を得られます。この方法によって、5V電源アプリケーションでは電源電流がラッチアップ・トリガ電流を下回る25mAまでに制限されます。ただし、消費する電源電流によっては、この直列抵抗によってiCouplerの電源電圧が許容レベル以下になることがあります。高い電源電流が要求される高速データレートの動作時に、このような問題が最も発生しやすくなります。

一般的にラッチアップを引き起こすメカニズムは、デバイスの 絶対最大定格を超える過電圧状態です(大部分のiCoupler製品 では7.0V超または-0.5V未満の電圧)。iCouplerをシステムに 組み込んで実装すると、過電圧の発生源がはっきりしないこと もあります。しかし十分に理解すれば、通常は過電圧状態を管 理することができます。

# IEC 61000-4-2 ESDテスト

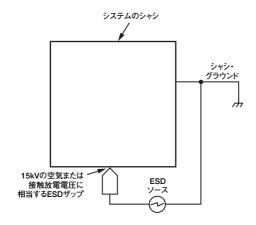

IEC 61000-4-2 ESDテスト設定のブロック図を図3に示します。このテストでは、ESD接触または空気放電電圧を、システム・シャシ上のさまざまなポイントに印加します。これによって、iCouplerにラッチアップの問題を引き起こす可能性のあるいくつかのメカニズムが発生します。iCouplerのグラウンドを経由した注入電流や、システムのシャシまたはプリント配線基板のパターン配線を流れるESD電流からの誘導性結合などがその例です。

図3. IEC 61000-4-2 ESDテスト

## ESD注入電流

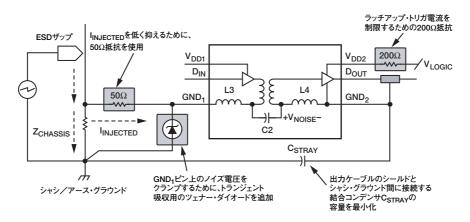

ラッチアップを引き起こす可能性があるメカニズムとしてまず 考えられるのは、過大なESD電流がiCouplerのグラウンドに注 入される場合です。図4は、iCouplerをフローティング出力と して使用する場合の回路図を示しています(フローティング入 力構成でも同様のメカニズムが存在する可能性があります)。 この例では、シャシ・インピーダンス $Z_{CHASSIS}$ がESD放電中に注入電流を発生させます。この電流はL3、C2、L4、 $C_{STRAY}$ からなるループ内に流れ込みます。 $C_{STRAY}$ は、出力ケーブルのシールドとシャシ・グラウンド間に接続したコンデンサです。 $C_{STRAY}$ の容量を大きくすると、それに応じて注入電流が大きくなり、その結果としてL4を通過する内部ノイズ電圧が発生します。この電圧にともなって $GND_2$ がその絶対最大定格値を超えると、ラッチアップが発生すると考えられます。

電流注入の問題に対しては、以下のような措置を講じることを 推奨します。

- グラウンド間のシャシ・インピーダンスを可能な限り低く抑えます。

- クロス絶縁バリア容量のC<sub>STRAY</sub>を最小限に抑えます。

- 可能であれば、ラッチアップ・トリガ電流を制限するために  $200\Omega$ の抵抗を $V_{DD2}$ と直列に接続します。

- ・ シャシのグラウンドと $GND_1$ との間に $50\Omega$ の抵抗を接続します。これによって注入電流( $I_{INIECTED}$ )が低減され、最終的にノイズ電圧( $V_{NOISE}$ )が低下します。

- 接続部とシャシのグラウンド間にトランジェント吸収用の ツェナー・ダイオードを接続します。これによりノイズ電圧 がツェナー電圧以下のレベルにクランプされます。

#### ESD電流からの誘導性結合

iCouplerのプリント配線基板またはシステムのシャシに存在するESD電流から誘導性結合が発生する可能性も考慮する必要があります。ほとんどのアプリケーションでは、外部の磁界からiCouplerトランス上で誘導性ピックアップが生じることは、問題ではありません。しかしIEC 61000-4-2 ESDテストでは、まれにこのような現象が確認されています。この問題はきわめて簡単に解決できます。

図4. ESD注入電流メカニズムと推奨のソリューション

REV. 0 — 3 —

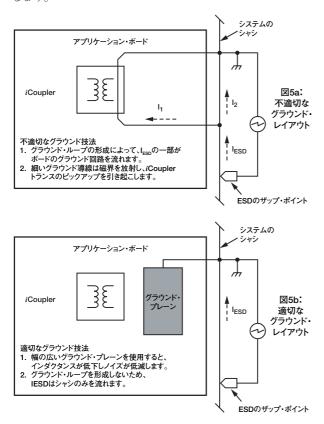

図5は、ESDテストのセットアップと、ESD事象によって発生する $I_{ESD}$ および $I_1$ 電流の経路を図示しています。これらの電流は非常に大きくなることがあり、アプリケーションのプリント配線基板とシャシ上に大きい磁界を誘導します。放射された磁界からの誘導性ピックアップを最小限に抑えるには、グラウンド・パターン配線の配置とその外面形状、グラウンド回路の接続、ボードの場所、シャシ内部の方向のすべてが重要な要素となります。

図5aは不適切なレイアウトの例で、iCouplerの近くで細いグラウンド・パターン配線を使用しています。グラウンド・ループによって $I_{ESD}$ の一部が $I_i$ としてボードのグラウンド回路を流れることもわかります。配線がiCouplerに近接し、パターン配線幅が狭いと、誘導される磁界のレベルは増加します。磁界が高いレベルに達すると、上述のようにiCouplerのラッチアップが起きます。図5bは適切なレイアウトの例で、iCouplerから十分に離れた幅の広いグラウンド・プレーンと、 $I_{ESD}$ がボードのグラウンド回路に流れ込むことを防止するシングル・ポイントのグラウンドを使用しています。グラウンド回路を設計するときは、常に電流経路を考慮に入れるとよいでしょう。

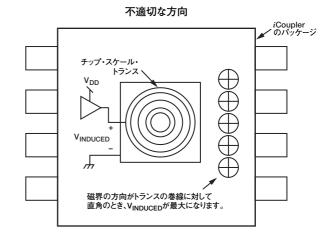

システムのシャシを設計するときは、シャシ・グラウンド接続のインピーダンスを最小限に抑えることが重要です。また、シャシのエッジから可能な限り離れた位置にプリント回路基板を実装し、図6に示すように、放射されるいずれの磁界に対しても*i*Couplerが平行となる方向にボードを配置するとよいでしょう。

図5. ボードのグラウンド回路の適切な例と不適切な例

図6. 外部磁界とiCouplerトランスの相互作用

誘導性結合を解決するには、以下の方法を推奨します。

- グラウンド・ループができないようにグラウンド・システム を設計します。

- 個々の細いパターン配線ではなく、グラウンド・プレーンを 使用します。

- プリント配線基板をシャシのエッジから離れた位置に配置します。

- 可能であれば、図6に示すように*i*Couplerが外部の磁界に対して平行になるような方向に実装します。

# IEC 61000-4-5サージ・テスト

IEC 61000-4-5規格に準拠したサージ・テストも、工業および 計装アプリケーションで実施されるシステム・レベルのテスト として一般的です。図7は、iCouplerのサージ・テスト構成回路およびこれに関連するバイパス・コンデンサと浮遊容量を示します。 $V_{TEST}$ は、アース・グラウンドとボードのローカル・グラウンドであるGND」との間に現れるサージ・テスト電圧です。このテストの一般的なテスト電圧は、最大4kVです。図7に示すように、絶縁バリア間に過度の浮遊容量が存在すると、 $V_{DDI}$ の電圧がその絶対最大定格値を超えるレベルまで駆動され、iCouplerの損傷が発生する可能性があります。

図7. *i*CouplerのIEC 61000-4-5サージ・テスト・セットアップ回路

図8は、解析を容易にするために簡略化した回路図です。この回路図ではリード・インダクタンスのわずかな影響を無視し、 $C_{STRAY}$ を1つの演算要素として扱っています(式1)。

図8. 図7の等価回路簡略図

図8を使用し、インダクタンスを無視すると、 $C_{STRAY}$ を次式で表すことができます。

$$C_{STRAY} = C4 + \frac{C_{BP2} \times C5}{C_{BP2} + C5} \tag{1}$$

結合電圧の $V_X$ は、以下に示す簡単なコンデンサ除算式を用いて求めます。

$$V_{X} = V_{TEST} \times \frac{C_{STRAY}}{C_{STRAY} + C_{BPI}}$$

(2)

式2より、 $C_{BPI}$ と比較して $C_{STRAY}$ を小さくすると、 $V_X$ が最小になることが分かります。たとえば、テスト電圧を4kV、バイパス・コンデンサの容量を $0.01\mu$ Fとすると、浮遊容量が10pFと適当であっても、4Vの結合された $V_{DDI}$ 電圧が生成されます。

通常の電源電圧に加えてこの電圧が印加されると、ラッチアップを誘発します。このような状況のときは、結合電圧を十分に安全な値である0.4Vに低減するために、バイパス・コンデンサ  $C_{BPI}$ の容量を $0.1\mu F$ まで高くしてください。最善の結果を得るためには、以下の事項に従ってください。

- *i*Couplerのフローティング・グラウンドとシステム・グラウンド間の容量を最小限に抑えます。

- 十分に大きい容量の高品質セラミック・バイパス・コンデン サを使用して適切なバイパス処理を施し、*i*Couplerの電源ピンに誘導される電圧を可能な限り低く抑えます。

- $V_{DD1}$ と $V_{DD2}$ でノイズ・スパイクが発生しないようにします。

- 可能であれば、 $V_{DDI}$ と直列に $200\Omega$ の抵抗を追加し、寄生のSCRトリガ電流を制限します。

- $V_{\mathrm{DDI}}$ 間にトランジェント吸収用ツェナー・ダイオードを使用します。

# IEC 61000-4-4高速トランジェントおよびバースト・ テスト例

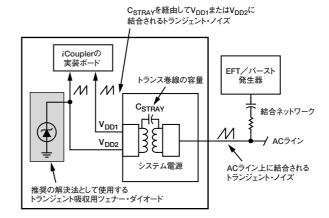

IEC 61000-4-4規格に準拠した高速トランジェントやバーストのテストも、適切な設計プラクティスを順守していないと問題を生じることがあるシステム・レベルのテストです。このテストでは、高電圧の高速エッジ信号をシステムのAC電源上に結合します。

図9. IEC 61000-4-4高速トランジェント/バースト・テスト・ セットアップ回路

図9は、高速トランジェント・テスト・セットアップの回路簡略図です。ここで問題となる主要なメカニズムは、システム電源トランスの巻線間の容量です。この浮遊容量は、AC電源から発生する高速のトランジェント信号をiCouplerの電源ピンに結合させる可能性があります。iCouplerの電源に印加された電圧が十分に高いレベルであれば、これが電源電圧の最大定格値を上回り、そのためにラッチアップが発生することが考えられます。

この場合、問題の発生を予防するには以下の方法が最適です。

- 巻線間の容量が低い電源を使用します。

- 適切なバイパス処理を施して、電源ノイズを最小限に抑えます。

- iCouplerの電源間にツェナー・ダイオードのクランプ回路を 使用して、ノイズ電圧をクランプします。

REV. 0 — 5 —

# ESD耐性を強化した新しいiCoupler

過酷なESDアプリケーションにおけるiCouplerの使用に一層対応するために、アナログ・デバイセズでは新しいiCoupler製品ラインを発売する予定です。ADuM3xxxシリーズでは、回路設計とレイアウトの改良により、ESD事象に対するiCouplerの耐性を強化しました。この新しい製品ファミリーは、既存のADuM1xxxシリーズ製品とピンおよび仕様の互換性を備えています。すでに実装されている数多くのアプリケーションで、標準タイプのiCoupler製品が良好な性能を発揮しています。したがって、ESD耐性を強化したADuM3xxxシリーズのリリース後も、標準タイプのADuM1xxxシリーズを引き続き販売する予定です。

ADuM3xxxシリーズの部品番号は標準タイプと同じですが、鉛フリー・モデルのみの販売となります。表IIIは、2つの製品ファミリーの部品番号例を示します。

表III. 標準タイプ/ESD耐性強化タイプ各種iCoupler製品の 部品番号例

| 標準タイプ        | ESD耐性強化タイプ   |

|--------------|--------------|

| ADuM1100ARWZ | ADuM3100ARWZ |

| ADuM1201ARWZ | ADuM3201ARWZ |

| ADuM1301BRWZ | ADuM3301BRWZ |

| ADuM1402CRWZ | ADuM3402CRWZ |

# ADuM3xxxシリーズiCouplerの内部

ESD耐性を強化するために、ADuM3xxxシリーズiCouplerにはいくつかの設計改良を行っています。具体的には、以下のような改良点があります。

- すべての入出力インターフェースにESD保護セルをつけています。

- 幅の広い形状およびビアと平行のラインを使用して、主要な 金属パターン配線の抵抗値を低減します。

- PMOSとNMOSの各デバイス間のガードおよび絶縁技法を採用して、CMOSデバイス固有のSCRの影響を最小限に抑えます。

- 金属パターン配線に45°のコーナーを使用して、電界濃度の 高いエリアをなくしています。

- 各電源ピンとそれに対応するグラウンド間の大きいESDクランプによって、電源ピンの過電圧を防止します。

# 結論

このアプリケーション・ノートに従えば、システム・レベルでのiCouplerのアプリケーションの設計はうまくいくはずです。iCouplerについて紹介した一体化要素の回路モデルを利用すれば、システム・レベルのテストに関する問題を予測できます。このモデルを利用し、さらに各種のシステム・テストを十分に理解したうえで、本書で推奨する予防的な技法を採用すれば、設計上の問題を防ぐことができます。コスト、システム設計、またはその他の理由で本書の推奨事項を実施できない場合は、新しいADuM3xxxシリーズのiCouplerを使用することで、ESD/ラッチアップの問題を解決できます。