### ADF4xxx PLLシンセサイザ・ファミリーでのロック検出

著者: Peadar Forbes、Ian Collins

#### はじめに

このアプリケーション・ノートでは、ADF4xxxインテジャーNPLLシンセサイザ・ファミリー、ADF4360-xフェーズ・ロック・ループ (PLL) シンセサイザおよび電圧制御発振器 (VCO)集積化ファミリーについて説明します (このアプリケーション・ノートで説明するADF4xxx製品の詳細については、付録を参照してください)。各製品では、アナログ・ロック検出(ALD)とデジタル・ロック検出(DLD)という、2つのロック検出方式を使用できます。アプリケーションによって、それぞれに利点と欠点があります。このアプリケーション・ノートの目的は、2つのオプションについて説明し、使用するロック検出方式をユーザ自身が判断できるようにすることです。

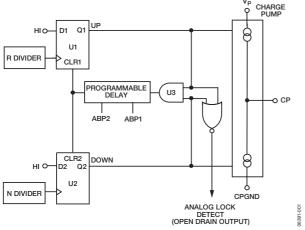

PLLがロックされているかどうかを判断するために、ALDと DLDでは、位相周波数検出器(PFD)入力における位相誤差を 使用します。図1は、PFDとチャージ・ポンプ・ブロックを示します。

図1. ADF4xxx PLLシンセサイザ・ファミリーのPFDと チャージ・ポンプ

#### デジタル・ロック検出

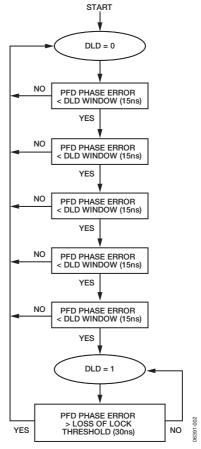

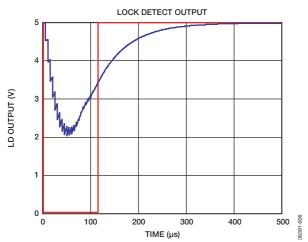

デジタル・ロック検出では、PLLのロック状態を示すCMOSロジック・ハイ、またはアンロック状態を示すロジック・ローを出力します。図2はDLDの状態図を示します。図3は簡略回路図を示します。機能としては、PFD入力において位相誤差を測定し、15ns位相誤差のウィンドウを使用してPLLのロック・ステータスを判断します。

PFD入力における位相誤差が、5つ以上の連続したサイクルで15nsウィンドウ内にあれば、PLLはロック状態と見なされ、ロジック・ハイが出力されます。

それ以降のPFDサイクルで、位相誤差がロックの喪失スレッショールド(30ns)の外側にドリフトすると、非ロック状態、つまりロジック・ローが示されます。PLL製品によっては、ウィンドウは $\mathbf{R}_{\text{SET}}$ 抵抗によって設定されることもあります(「デジタル・ロック検出 —  $\mathbf{R}_{\text{SET}}$ への依存」を参照)。15nsウィンドウと30nsウィンドウは、4.7k $\Omega$ の $\mathbf{R}_{\text{SET}}$ 抵抗用です。

図2. デジタル・ロック検出の状態図 (この場合、ロック検出 精度 (LDP) は5)

REV. 0

アナログ・デバイセズ株式会社

本 社/〒105-6891

東京都港区海岸1-16-1 ニューピア竹芝サウスタワービル 電話02 (5402) 8200

電話03 (5402) 8200

大阪営業所/ 〒532-0003 大阪府大阪市淀川区宮原3-5-36 新大阪MTビル2号 電話06(6350)6868

# **AN-873**

# 目次

| はじめに1        | デジタル・ロック検出 — Rest への依存6 |

|--------------|-------------------------|

| デジタル・ロック検出1  | 551                     |

| アナログ・ロック検出3  |                         |

| 一般的な性能3      |                         |

| PFD周波数 対 性能4 |                         |

| リーク電流4       |                         |

| サイクル・スリップ5   |                         |

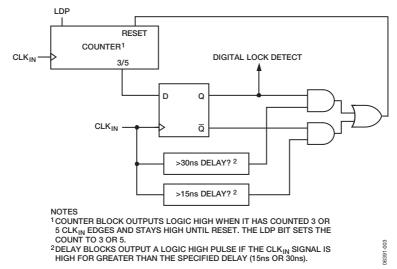

図3. デジタル・ロック検出用の簡略回路図 (CLK<sub>IN</sub>はアナログ・ロック検出信号)

ロックが表示されるまでにカウントされるサイクル数は、Rカウンタ・ラッチのロック検出精度(LDP)ビットによって設定されます。3サイクルまたは5サイクルを選択できます。

## アナログ・ロック検出

アナログ・ロック検出(ALD)信号は、PFDからチャージ・ポンプへのアップ/ダウン信号のNORです(図1を参照)。

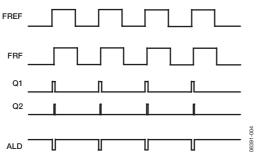

図4に示すように、PLLがロック状態のとき、PFD入力におけるエッジはほぼ同相です。この場合、PFD出力はQ1とQ2という非常に短いパルスから構成されます。これらの論理NORにより、立下がりパルスを持つハイレベル信号が生成されます。立下がりパルスの継続時間は、Rカウンタ・ラッチで設定されたアンチバックラッシュ・パルス幅の継続時間と同じです。図4は、ロックされたPLLのタイミング図とALDからの対応する出力を示します。

図4. ロック状態のPLLのタイミング図:リファレンス信号、 分割されたRF信号、Q1とQ2(PFDからチャージ・ポン プへのアップ/ダウン・パルス)、およびALD信号(Q1 とQ2のNOR)を示します

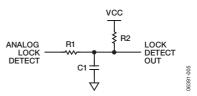

立下がりパルスを除去するために、この信号にはチップ外部でのフィルタリングが必要です。図5に示すように、このフィルタはアナログ・デュアル時定数フィルタです。アナログ・ロック検出信号はオープン・ドレイン出力です。

Q1とQ2のNORがハイレベルのとき、コンデンサC1はR2を通じて充電します。これがローレベルのとき、C1はR1を通じて放電します。正確なフィルタ設計により、ロック検出出力でPLLのロック・ステータスを正しく表現できます。ADIsimPLLTMは、フィルタの設計を支援します(www.analog.com/pllを参照)。

図5. R1、R2、C1によるアナログ・ロック検出のオフチップ・フィルタリング(アナログ・ロック検出はオープン・ドレイン出力です)

#### 一般的な性能

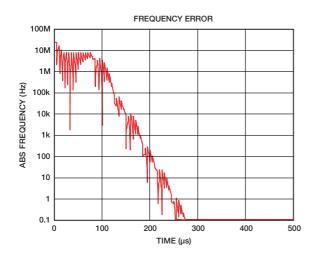

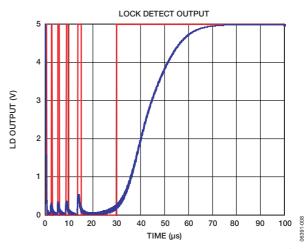

デジタル・ロック検出信号がロックを表示してから、PLLは最終的な周波数と位相にセトリングします。その理由は、5つを超える連続したサイクルにわたって位相誤差が<15nsとなった後で、最終的な周波数と位相がセトリングするためです。図6は、35MHzの周波数ジャンプに対する周波数誤差のシミュレーションと、対応するALD(青)およびDLD(赤)信号を示します。PLLは300 $\mu$ s未満でロックされます。その前に、DLDは約150 $\mu$ sにわたってハイレベルになります。一方、アナログ・ロック検出は、ALDの出力がフィルタリングされるため、最終的な周波数と位相が安定した後に、安定したハイレベルに到達します。

REV. 0 — 3 —

図6. 35MHzの周波数ジャンプに対する周波数誤差と、対応 するALD(青)およびDLD(赤)信号

逆に、アンロック状態が発生すると、ほとんど即座にDLDはローレベルになります。ALDがローレベルに変化するには、若干の時間を要することがあります。

#### PFD周波数 対 性能

高いPFD周波数(>15MHz)では、デジタル・ロック検出の精度が低下します。その理由は、PFD周波数の周期がロックのチェックに使用される15nsウィンドウに近づき始めるからです。たとえば、25MHzのPFD周波数では、周期は40nsとなります。このような場合、デジタル・ロック検出の精度が損なわれます。アンロック状態において、アンロック周波数が希望する周波数に近づくと、PFDでの位相誤差が15nsウィンドウに出入りするようになり、DLD信号はハイレベルとローレベルのパルスになります。

あるいは、電圧制御水晶発振器(VCXO)が使用された場合、アンロック信号とREFIN周波数との位相があまり違わないこともあります。その理由は、VCXOの周波数範囲がきわめて狭いからです。たとえば、50MHzのPFDを使用した場合、周期は20nsになります。PLLはロック状態にあり、ロックされた信号によりロジック・ハイが出力されます。

REFIN周波数を増やすと、VCXOは、VCXOの最大周波数 (たとえば、50MHz+1ppm) に達するまで周波数を追跡し、それ以上はリファレンス信号を追跡できません。PLLはもはやロック状態にありません。しかし、2つの信号の周期は20nsを超えるため、デジタル・ロック検出には30nsを超える位相誤差はなく、デジタル・ロック検出信号はロジック・ハイを表示し続けます。

アナログ・ロック検出の精度は、高いPFD周波数においてはこれほど低下しません。しかし、ALDからの立下がりパルスの幅がPFD周期全体に占める割合が高まるため、ハイレベル信号の電圧レベルは若干減少することがあります。立下がりパルスの継続時間は、Rカウンタ・ラッチで設定されたアンチバックラッシュ・パルス幅の継続時間と同じです。したがって、高いPFD周波数では小さなパルス幅が望ましいといえます。

同様にアンロック状態では、立上がりパルスが目立つようになり、ロック検出信号のアンロック電圧を上げるように機能しますが、信号レベルをCMOSのハイレベル/ローレベルから外れるほど上下変動させることはできません。このため、PFD周波数が15MHzを超える場合は、アナログ・ロック検出を推奨します。

低いPFD周波数ではリーク電流の影響が大きくなります。次に、リーク電流と、ALD/DLD性能に対する影響について説明します。

#### リーク電流

ループ・フィルタに入出力するリーク電流は、ALDとDLDの性能に影響を与えることがあります。リーク電流には、チャージ・ポンプ、VCO同調ポート、ループ・フィルタ・コンデンサを通じての漏れ、あるいはアクティブ・ループ・フィルタのバイアス電流など、多くの発生源が考えられます。VCO同調電圧を一定に保持し、PLLをロック状態に保持するには、PFDとチャージ・ポンプが各PFDサイクルで失われた電荷を元に戻すように機能する必要があります。そのために、PLLはPFD入力に位相誤差を設定します。これによって、チャージ・ポンプのターンオン時間が十分に確保され、各PFDサイクルで失われた電荷を元に戻すことができます。低いPFD周波数ではリーク電流の与える影響が大きくなります。なぜなら、チャージ・ポンプがスリーステート状態になる時間が十分に確保されることで、リーク電流が増えるためです。

リーク電流によって発生するPFD入力での位相誤差(秒単位)は、およそ次のようになります。

$$Phase\ Error = \frac{Leakage\ Current}{I_{CP}} \times I_{PFD} \eqno(1)$$

ここで、

$I_{CP}$ はチャージ・ポンプ電流です。

$t_{PFD}$ はPFD周波数の周期です。

—4— REV. 0

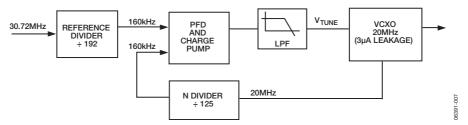

図7. 30.72MHzリファレンスから20MHzを生成するPLL

アプリケーションとして、30.72 MHzのリファレンスから 20 MHzのクロックを生成する例を考えてみます。30.72 MHzを 192で除算して160 kHzが得られます。これがPFDに供給されます。続いて、125が乗算されて20 MHzの出力周波数が得られます。 $3\mu A$ の最大リーク電流を持つ20 MHzのVCXOは、同調可能発振器です。図7はPLLのブロック図を示します。

式1を使用して、PFD入力での位相誤差を計算すると、次のようになります。

Phase Error =

$$\frac{3\mu A}{1mA} \times 6.25\mu s = 18.75ns$$

このアプリケーションでデジタル・ロック検出が使用された場合、PFD入力における18.75nsの位相誤差は、15nsウィンドウを外れます。したがって、たとえPLLがロック状態でも、DLDはハイレベルになりません。しかし式1から、 $I_{CP}$ が増加すると位相誤差が減ることがわかります。したがって、 $I_{CP}$ が4倍に増加すると、位相誤差が4.7nsまで下がってDLDウィンドウの中に戻り、DLDは再び機能します。しかし、いつでもチャージ・ポンプ電流を増やせるとは限りません。なぜなら、ループ・フィルタのコンデンサ・サイズが過大になることがあるためです。

リーク電流があると、アナログ・ロック検出の信頼性が高くなります。しかし、ロック状態ではリーク電流によってPFD入力での位相誤差が増加するため、立下がりパルスが長くなります。ALDのロック電圧レベルをハイレベルに保持するには、これらのパルスのフィルタリングを強化する必要があります。ALDフィルタ(図5)では、立下がりパルス区間でコンデンサC1の放電を遅くするために、抵抗R1を増やしてください。同様に、抵抗R2を減らせばハイ・パルス区間でのC1の充電を速めることができます。これらの値を変更する影響や、リーク電流下でのALD電圧レベルへの影響については、ADIsimPLLでシミュレートできます。

#### サイクル・スリップ

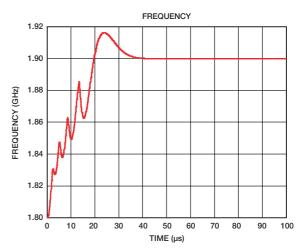

PFD入力での位相誤差がPLLの訂正能力を超えて蓄積すると、PLL内でサイクル・スリップが発生します。これらの検出は、チャージ・ポンプにより同調電圧を間違った方向に瞬間的に駆動させたときのセトリング過渡応答で特性を歪めることによって行うことができます(図8を参照)。フラクショナルNシンセサイザではさらに一般的ですが、PFD周波数がループ帯域幅よりずっと大きくなると、インテジャーNシンセサイザでもサイクル・スリップが発生することがあります(一般に、PFD:ループ帯域幅の比が100:1を超えると、サイクル・スリップが発生します)。

サイクル・スリップの周りでは、PFD入力での誤差が何サイクルにもわたってロック検出ウィンドウを下回るほど低下することがあるため、デジタル・ロック検出信号がアサートされます。PFDでの誤差がロックの喪失スレッショールドを超えるまでは、DLDはハイレベルを維持します。多くのサイクル・スリップを持つセトリング・トランジェントでは、これが何度も発生して、周波数が最終的にセトリングするまで、DLDがハイとローのパルスを出力することがあります。この場合は、DLDはロックの喪失検出回路としてのみ信頼できます。慎重に設計されたフィルタを使用すれば、サイクル・スリップが存在する状況下で、ロック・インジケータとしてのアナログ・ロック検出の信頼性を高めることができます。

図8. セトリング・トランジェント時のサイクル・スリップと、 対応するDLD(赤) およびALD(青) 出力(セトリング・ トランジェント時にDLDはハイとローのパルスを出力)

REV. 0 — 5 —

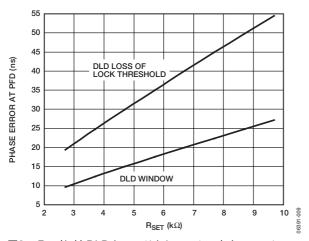

# デジタル・ロック検出 — R<sub>SET</sub>への依存

デジタル・ロック検出でロックのチェックに使用されるタイミング・ウィンドウは、公称値で15nsです。しかし、ADF41xx、ADF42xx、ADF4001/ADF4002のシンセサイザでは、このウィンドウは $R_{SET}$ 値によって決定されます。図9は、DLDウィンドウが $R_{SET}$ の値とともに増加することを示します。4.7k $\Omega$ の $R_{SET}$ に対して、公称値は15nsです。ロックの喪失スレッショールドも、 $R_{SET}$ 値とともに増加します。DLDがハイレベルになった後、DLDがローレベルになるには、PFDでの位相誤差がロックの喪失スレッショールドを1 PFDサイクルにわたって超える必要があります。この公称値は、4.7k $\Omega$ の $R_{SET}$ の場合で30nsです。

図9.  $R_{SET}$ 値 対 DLDウィンドウとロックの喪失スレッショールド。 $R_{SET}$ の許容範囲は $2.7\sim10$ k $\Omega$ です。これらのウィンドウは、図に示す公称値の10%だけ変化できます。

デジタル・ロック検出ウィンドウを制御する機能は、アプリケーションによっては利点と見なすことができます。図7に示す例では、リーク電流によってデジタル・ロック検出が使用できなくなり、 $R_{SET}$ を4.7k $\Omega$ から10k $\Omega$ に変更すると、DLDウィンドウは約28nsまで増加します。これによって、18.75nsの最大位相誤差はDLDウィンドウ内に戻り、DLDが再び機能します。なお、 $R_{SET}$ の変更によって、チャージ・ポンプ電流値も変化します。 $R_{SET}$ が変更されてもチャージ・ポンプ電流値を一定に保持するには、チャージ・ポンプ電流の設定を変更してください。これによって、ループのダイナミック特性が変化しないことが保証されます。

高いPFD周波数が使用されるアプリケーションでは、 $R_{SET}$ の値を減らすことができます。これには、DLDウィンドウを減らしてPFD周期全体に占める割合を減らすことで、DLD精度を高める効果があります。

ADF4360-xでは、 $R_{SET}$ 値とは無関係に、DLDウィンドウとロックの喪失スレッショールドがそれぞれ15nsと30nsに固定されます。

# デジタル・ロック検出 — アンチバックラッシュ・パルス幅への依存

アンチバックラッシュ・パルス幅がデジタル・ロック検出の動作に与える影響は小さなものです。これは多くのアプリケーションでは無視できますが、極端な場合は考慮が必要なこともあります。

図3から、DLDはアナログ・ロック検出信号を使用してロックをチェックします。アナログ・ロック検出では、常に立下がりパルスはアンチバックラッシュ・パルス幅と等しくなります。リーク電流によってPFD入力に生じる位相誤差は、このパルスによって増加します。DLD回路側から見たPFD位相誤差を計算する際には、このことを考慮に入れてください。

たとえば、PFD入力にリーク電流によって生じた10nsの位相誤差があり、ABPWが1.3nsに設定されている場合、DLD回路側から見た合計位相誤差は11.3nsです。

#### 結論

このアプリケーション・ノートでは、ALDとDLDの利点と欠点を説明しました。DLDはそのデジタル的な特性により、PLLがロック状態にあるかどうかについて、明確なイエス/ノーの判断をくだす必要があります。特定の状況のもとでは、このアプリケーション・ノートで説明するように、DLDは誤差の影響を受けやすくなります。特定のアプリケーションにおいてDLDが正確であるかどうかを判断するには、PFD周波数とリーク電流に注意することが必要です。

フィルタリングの後、ALDでは、PLLのロック・ステータスを単なる0/1以外の方法でも表現できるようになります。出力電圧レベルでは、ロック・ステータスをさらに正確に表現できます。しかし、フィルタを慎重に設計する必要があり、アプリケーションによっては、出力電圧レベルの立上がり/立下がり時間が問題となることもあります。

#### 付録

以下に、このアプリケーション・ノートで取り上げた製品番号の一覧を示します。

| , .     |                                                                                                 |                                                                                                                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADF41xx | ADF42xxx                                                                                        | ADF43xx-x                                                                                                                                                                                                          |

| ADF4106 | ADF4206                                                                                         | ADF4360-x                                                                                                                                                                                                          |

| ADF4107 | ADF4207                                                                                         |                                                                                                                                                                                                                    |

| ADF4108 | ADF4208                                                                                         |                                                                                                                                                                                                                    |

| ADF4110 | ADF4210                                                                                         |                                                                                                                                                                                                                    |

| ADF4111 | ADF4211                                                                                         |                                                                                                                                                                                                                    |

| ADF4112 | ADF4212                                                                                         |                                                                                                                                                                                                                    |

| ADF4113 | ADF4212L                                                                                        |                                                                                                                                                                                                                    |

| ADF4116 | ADF4213                                                                                         |                                                                                                                                                                                                                    |

| ADF4117 | ADF4216                                                                                         |                                                                                                                                                                                                                    |

| ADF4118 | ADF4217                                                                                         |                                                                                                                                                                                                                    |

|         | ADF4218                                                                                         |                                                                                                                                                                                                                    |

|         | ADF4218L                                                                                        |                                                                                                                                                                                                                    |

|         | ADF4219L                                                                                        |                                                                                                                                                                                                                    |

|         | ADF4106<br>ADF4107<br>ADF4108<br>ADF4110<br>ADF4111<br>ADF4112<br>ADF4113<br>ADF4116<br>ADF4117 | ADF4106 ADF4206<br>ADF4107 ADF4207<br>ADF4108 ADF4208<br>ADF4110 ADF4210<br>ADF4111 ADF4211<br>ADF4112 ADF4212<br>ADF4113 ADF4212L<br>ADF4116 ADF4213<br>ADF4117 ADF4216<br>ADF4118 ADF4217<br>ADF4218<br>ADF4218L |