# ちょっと変わった設計の問題を解決する計装アンプ Scott Wurcer、Walt Jung 著

計装アンプはこれまでトランスデューサの

コンディショニング用にのみ使用されるデバイスと考えられていましたが、 ほかのさまざまなアプリケーションでもその特長を利用することで性能向上が図れます。

これまで計装アンプは、真の差動入力とシングルエンド出力を 備えたゲイン・ブロックを必要とする、トランスデューサの信号 コンディショニング・アプリケーションに使用されてきました。 しかし、歪みゲージや熱電対アンプなどのセンサー・ベースの回 路に適した計装アンプの性能特性は、従来とは異なる数多くのア

ナログ信号プロセッシング・アプリケーションにも力を発揮しま す。この記事の回路に示すような低価格の最新型モノリシック計 装アンプは、アナログ回路の基本的なビルディング・ブロックと してオペアンプよりも優れているということさえ珍しくありませ

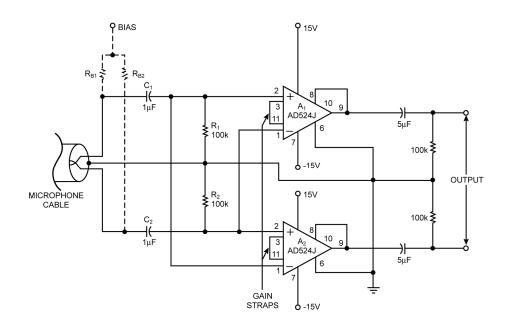

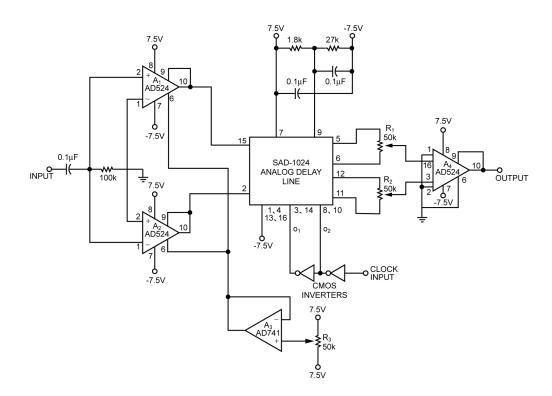

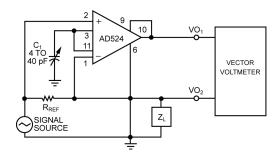

図 1. アクティブ・トランス・マイクロフォン・プリアンプ:2個の計装アンプを使ってノイズを低減します。この回路では、計装アンプの出力 信号が直線的に増加し、ノイズは2の平方根によって増加します。このため、シングルエンド設計よりも 3dB 優れたノイズ性能が得られま す。

## 計装アンプのさまざまな用途

IC 計装アンプの利点は、複数の内蔵オペアンプを使用することで、平衡反転/非反転入力、高い同相ノイズ除去比(CMRR)、プログラマブルなフロントエンド・ゲイン(下の枠内記事「1個のオペアンプより優れた3個のオペアンプ」を参照)を提供できることです。高性能なデバイスは、低い入力ノイズ電圧で広帯域幅と安定した DC 特性を備えていますが、これらは大部分のモノリシック・オペアンプでは両立しない特性です。このため、非反転ゲイン段のような単純なアプリケーションの場合、計装アンプのほうがオペアンプより優れた性能を発揮することがよくあります(枠内記事の「オペアンプとしての計装アンプ」を参照)。

### マイク・プリアンプの簡素化

しかし、最も興味深い計装アンプの用途は、オペアンプではふつうは解決できないような性能上の問題がある回路に関わる場合です。たとえば、マイクロフォン用プリアンプは、低ノイズと高CMRRの両方の特性を持つアクティブ段が必要なため、従来のオペアンプには難しい条件が求められます。計装アンプは2つの差動入力、低ノイズの入力段を提供し、ゲインを簡単に設定できるため、マイク・プリアンプの設計を大幅に簡素化できます。

#### 1個のオペアンプより優れた3個のオペアンプ

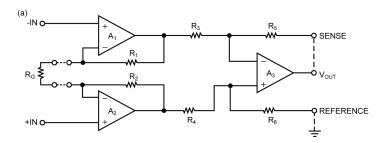

計装アンプは、一般に差動入力段が 2 つ、出力バッファが 1 つの 3 個のオペアンプで構成されています(図(a))。入力アンプに接続された内部帰還抵抗によって、1 個の抵抗( $R_G$ )で全体のゲインを設定できます。ユニティ・ゲインの出力構成とすると、全体のゲインは( $(R_1 + R_2)/R_G$ )+1 になります。センス入力とリファレンス入力により、出力ゲインのスケーリングとオフセットが可能です。

この記事の回路に使用されているアナログ・デバイセズのモノリシック計装アンプAD524とAD624(図(b))には、従来

の 3 オペアンプ回路と同じゲイン特性がありますが、さらに新しい機能もいくつかあります。入力アンプ $A_1$ 、 $A_2$ の前段に接続されたトランジスタ・プリアンプ  $(Q_1$ 、 $Q_2$ )などがそうです。この構成では、入力ゲイン帯域幅積がトランジスタのトランスコンダクタンスに依存するため、従

来の計装アンプよりゲイン帯域幅が大きくなります。トランジスタ・プリアンプによって、計装アンプの全体的なゲインも増大するため、クローズド・ループ誤差が小さくなります。

代表的な計装アンプは 3 個のオペアンプで構成されています(a)。入力アンプの周辺の内部帰還抵抗によって 1 個の抵抗で全回路のゲインを設定します。この記事の回路に使用されているモノリシック計装アンプ(b)は、回路の帯域幅を拡大し、クローズド・ループ歪みを低減するトランジスタ・プリアンプを備えています。

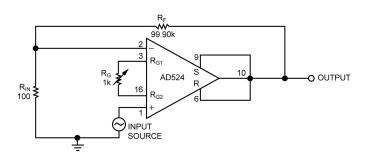

図 2. この電流モード・ミキサで複数の電流を加算します。この回路 は計装アンプの反転/非反転入力の周辺のローカルな帰還を 使って、信号の加算と減算をします。

図1に、アナログ・デバイセズのモノリシック計装アンプAD524Jを2の使用したプリアンプを示します。この回路は、参考文献1に記載されているクロス入力のスタック・アンプに似ており、平衡入力/平衡出力型のアクティブ・トランスとして機能します。この差動出力構成では、シングルエンド設計に比べてS/N比が3dB改善します。2アンプ構成では、単一アンプの回路に比べ2倍の信号電圧を生成し、発生するノイズは√2倍になるためです。プリアンプの差動出力構成は、非オーディオ関連のアプリケーションにも適合します。たとえば、信号経路の後段の計装アンプに給電する汎用アクティブ・トランスとしても使用できます。

アプリケーションの柔軟性を最大限高めるために、計装アンプのプログラマブル・フロントエンドは、回路全体で 20、200、または 2000 のゲインを設定できます。ゲインを 20 に設定した場合、プリアンプの出力振幅は 40V p-p、CMRR は 80dB、20kHz 帯域幅でのノイズは  $0.6\mu V$ rms、高調波歪みは 0.01%未満になります。

プリアンプの入力は、コンデンサ  $C_1$ 、 $C_2$ 経由で信号源のマイクロフォンに AC 結合されます。抵抗  $R_1$ 、 $R_2$ は、計装アンプの入力バイアス電流のリターン・パスとして機能します。結合コンデンサは、数ボルトまでの電圧レベルに対しては AC/DC 過負荷保護機能がありますが、入力過渡電圧がかなり大きくなる可能性があるため(特にマイクのケーブルの接続/切断時)、アンプを十分に保護しておく必要があります。 AD524 は 36V まで完全に保護されていますが、ほかの計装アンプの場合は必要に応じて結合コンデンサに  $1k\Omega$  以上の保護抵抗を直列に接続する必要があります。ただし、入力抵抗にはノイズが伴うので注意してください。 $1k\Omega$  の抵抗で  $4nV/\sqrt{Hz}$  相当の入力ノイズが発生し、実効値として計装アンプの入力ノイズに加算されます(この回路の AD524 の場合は  $4.7nV/\sqrt{Hz}$ )。

マイク・プリアンプを作製するときは、結合コンデンサと関連する入力回路を必ずシールドしてください。また、ハム混入を最

小限に抑えるために、平衡型ツイスト・ペア入力ケーブルを使用 してください。

### 電流加算器によるオーディオ信号の合成

図2に、オーディオ周波数信号を処理する別の計装アンプのアプリケーションを示します。ここでは、計装アンプをベースにした電流加算器が任意の数の入力波形をリニアに合成し、それぞれの信号の符号を個別に選択できるようにしています。加算器には各ディスクリート入力の個別のゲイン設定があり、ユニティを上回る値にすることも、ユニティ未満の値にすることもできます。

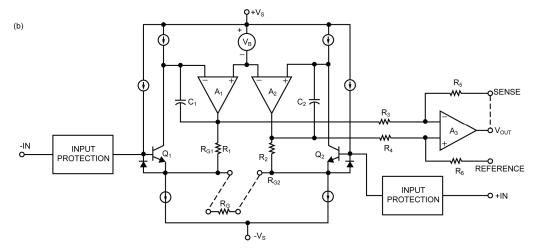

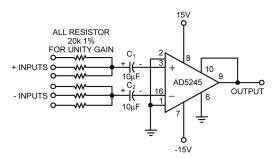

合成された信号が両極性になるように、計装アンプの各入力段にあるローカルな帰還回路を利用します。アンプの入力トランジスタにはローカルなエミッタ帰還回路があるため、トランジスタのベース(1番ピンと 2番ピン)がグラウンドに接続されているときに、エミッタ(3番ピンと 16番ピン)に入力された合計電流から正比例する出力電圧が生成されます。AD524 は  $20k\Omega$  の帰還抵抗を内蔵しているため、 $20k\Omega$  の入力抵抗を使用することでユニティ・ゲインが得られます。

図 2の回路の 16 番ピンは非反転入力になり、3 番ピンは反転ノードとして動作します。この 2 つのピンを個別に使用してシングルエンド電流信号を合成するか、または一緒に使用して差動入力を代数的に結合することができます。内部的に帰還接続が行われるため、各入力のダイナミック・インピーダンスは 1kHz未満の周波数で  $1\Omega$ 未満であり、各信号チャンネル間のクロストークは低い値になります。たとえば、 $20k\Omega$ の入力抵抗(ユニティ・ゲイン)では、チャンネル間のクロストークは入力レベルより 86dB低いレベルになります。

入力トランジスタの接地ベースによってエミッタ電圧がグラウンドより  $1\times V_{BE}$  低いレベルになるため、入力結合コンデンサを使って低オフセットにする必要があります。これらのコンデンサの値を選択するときは、対象周波数におけるそのリアクタンスが入力抵抗値に比べて低くなるようにしてください。そうしないとゲイン誤差が発生します。

計装アンプの入力ノイズは小さいため、20kHz 帯域幅における加算器の S/N 比は IV 入力を基準にして 90dB を上回ります。さらに、全高調波歪みは全オーディオ範囲で 0.01%未満になります。ただし、ゲイン精度は入力抵抗と計装アンプの内部帰還素子との間のマッチングに依存します。AD524 の帰還抵抗の許容誤差は 20%であるため、ユニティ・ゲインに設定された回路では、補償が無い場合のゲイン誤差が、最大で±1.6dB になる可能性があります。入力抵抗にトリミング用のポテンショメータを使用すれば、このような誤差を除去することができますが、チャンネル間のゲイン・マッチングは内部許容誤差に影響されることはありません。すべての入力が共通のノードに供給されるため、ゲイン・マッチングは入力抵抗の許容誤差にのみ依存します。

また、DAC内にあるようなアナログ・スイッチなどの、電流モード・アナログ・スイッチ付きの加算器も使用することができます。このようなアプリケーションでは、デバイスの $V_{BE}$ に等しい正の電圧に入力トランジスタのベースを接続し、回路全体でCDC結合を保持できます。その場合、エミッタはグラウンドに接続します。

### バケット・ブリゲードのバッファ処理

計装アンプの真の差動特性は、アナログ遅延ラインを内蔵した 回路にも有効であることがわかります。このような回路でクロッ クのフィードスルーや歪みを最小限に抑えるために、デュアル CCD バケット・ブリゲード・レジスタ(Reticon 社の SAD-1024 な ど)では、それぞれ個別のクロック入力がある、個別にアドレス 指定ができる 2 個の遅延ラインを持っています。しかし、CCD デ バイスの差動機能をフルに利用するには、優れた平衡入力を持ったバッファ・アンプが必要になります。

図 3に、差動入力/差動出力構成でSAD-1024 512x2 CCDレジスタを使用する遅延回路を示します。回路の入力アンプに使用する2個のAD524は、シングルエンドの入力信号を遅延回路の2つの入力を駆動する差動レベルに変換します。CCDレジスタの出力に接続された3個目の計装アンプは、遅延差動信号をシングルエンド波形に変換します。

遅延ラインのクロック入力は、バッファ処理済みのコンプリメンタリ・クロック信号を供給する1対のCMOSインバータが駆動します。ナイキストのサンプリング条件を満たすために、クロック・レートは最大周波数の少なくとも2倍にする必要があります。外部VCOと分周器からクロックを生成できます。

図3. アナログ遅延回路は、CCD 遅延ラインの両半分を使用します。計装アンプは差動回路動作を続けるため、ノイズとクロック・フィードスルーが最小限に抑えられます。

### 内部帰還によって簡素化する回路の設計

クロック・ノイズを最小限に抑えるために、遅延ラインの各出力は2つの信号で構成されます。ポテンショメータ $R_1$ 、 $R_2$ を使用すれば、これらの信号の電流を平衡させて、クロック・ノイズ除去を最大化することができます。差動の電流合成出力構成でクロック・フィードスルーをさらに除去すれば、全S/N比は70dBというシングルエンド設計では達成できないレベルになります。

図示されているように、回路の入力アンプはユニティ・ゲインになっていますが、ゲイン値は 1000 まで設定することができます。  $A_3$  とこれに関連する回路によって、入力段をバイアスして遅延ラインの高調波歪みを最小限に抑えることができます。回路をトリミングする場合は、 $R_3$ でバイアス・レベルを調整し、1V rms の入力信号で歪みが最小になるようにします。正しく調整し、150kHzのクロックを入力すると、通常、回路の動作時の全高調波歪みは0.2%になります。

#### 歪みの測定

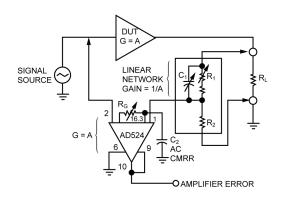

計装アンプの差動特性をさらに利用して、歪み測定装置の分解能を高めることができます。代表的な歪み計は、信号の基本波を $80\sim100 \mathrm{dB}$ 除去して、測定制限値を $0.01\sim0.001\%$ とします。しかし、計装アンプを使用して被試験デバイス(DUT)の出力を事前にゼロ化することで(図 4)、歪み計の測定機能を基本振幅より $140 \mathrm{dB}$ 低いレベルまで拡張できます。これで、最小0.00001%の歪みの測定が可能となります。

事前ゼロ化には、測定の分解能が向上する以外にもいくつか利点があります。その一つは、計装アンプが DUT 出力から来る信号源の入力を引き算するため、試験発振器の誤差が測定処理中にキャンセルされるという点です。このため、ほとんどの発振器では対応できないような低レベルの歪みが測定可能になります。

また、事前ゼロ化により、高分解能試験に使用する歪み計に通常課せられるダイナミック・レンジの条件を緩和することができます。歪み計は基本波ではなく信号誤差のみを処理するため、アナライザは十分なダイナミック・レンジさえあれば計装アンプの残留出力の誤差を監視できます。さらにノッチ・フィルタリングではなく減算によって試験信号をキャンセルするため、相互混変調試験やその他の高調波解析に複雑な波形を利用できます。

図 4の回路では、被試験アンプが負荷抵抗 $R_L$ を駆動します。ゲインが 1/Aの線形ネットワークは(A=アンプのゲイン)、 $R_L$ 間の電圧をゼロ化用のアンプの 1 つの入力に供給します。もう 1 つの計装アンプの入力はリファレンス・ポートとなり、DUTの入力信号に接続します。計装アンプのゲインは $R_G$ 経由でAに設定され、ゼロ化回路の誤差出力レベルはDUTの出力信号の振幅を基準にしています。

図 4. 事前ゼロ化回路で歪み測定の分解能を改善。被試験デバイス (DUT) の出力と計装アンプの入力の間の線形ネットワークが、 DUT のゲインと周波数特性を補償します。事前ゼロ化回路によって、計装アンプの出力から発生する誤差信号だけを処理すればよくなるため、歪みアナライザのダイナミック・レンジ条件が緩和されます。

アッテネータ・ネットワークの調整は、ゼロ化回路の測定セットアップ手順の中で最も難しい作業です。最初の最も簡単なステップは、1/Aと同量の DC減衰を得るために  $R_1$ を調整することです。次に、オシロスコープのプローブの補償と同じ方法で、補償コンデンサ  $C_1$ をトリミングします。時定数  $R_1C_1$ は、DUT O-3dB 帯域幅に対応している必要があります。そうでないと、計装アンプで高周波信号成分を完全に除去することができません。

減衰器を作製するときは、 $R_1$ と  $R_2$ を非リアクティブにし、 $R_1$ と  $R_2$ の熱/電圧の非直線性係数を小さくして DUT 誤差がマスキングされないようにします。また、 $R_1/C_1$  調整を何回か繰り返して最適なゼロ化を行います。

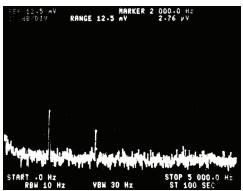

計測器を使って計装アンプの出力を表示する場合は、DUTとアッテネータ・ネットワーク間の正確な位相トラッキングが必要になります。位相誤差が1°の場合は、除去率はわずか35dBに制限されます。しかし、スペクトル・アナライザに給電する場合は、残留基本波によってアナライザのフロントエンドが過負荷にならない限り、位相トラッキング条件を緩和できます。図5aに、正しいゼロ化処理の結果を示すスペクトル・アナライザのディスプレイを示します。基本波は、試験信号の3Vrms以下の106dBレベルで表示されています。したがって、試験信号より120dB低いレベルでも2次高調波がはっきりと示されています。

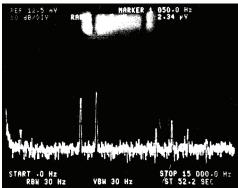

図 5bに、事前ゼロ化を行った相互変調試験の結果を示します。この測定では、5kHzと 6kHzの信号をDUTに同時に入力します。アナライザは 1kHzと 11kHzの和と差のビート周波数、それに 10kHzと 12kHzの 2 次高調波成分を明確に表示します。計装アンプは試験信号のほんの一部分を除いてすべてをキャンセルするため、高調波成分や相互変調成分が試験信号レベルより 100dB以上低いレベルであっても、ダイナミック・レンジの制限されたFFTアナライザを使用して出力波形のスペクトル・データを再現できます。

同じような差動アンプを使用する方法で複素インピーダンスを 測定できます。計装アンプによっては1個のコンデンサでトリミン グできるほど超高周波の CMRR 特性を備えたものがあり、時間的 に大きく変動する要素が含まれたライン上で電流を検出するアプ リケーションに適しています。

(a)

(b)

図 5. 図 4の事前ゼロ化回路の動作を示す高調波スペクトルです。図 (a) は、高調波歪み試験です。基本波が-106dBまで事前にゼロ 化され、DUTの出力レベルより 120dB低い 2 次高調波をはっき りと示すことができます。図 (b) は相互変調試験を示しています。この試験では、DUTが 5kHzと 6kHzの試験信号を処理します。ディスプレイには 1kHzと 11kHzの相互変調成分、それに 10kHzと 12kHzの 2 次高調波が表示されています。

図 6. インピーダンスを測定する電流モニタです。リファレンス抵抗間の電圧降下を増幅することで、ベクトル電圧計によって ZLの振幅と位相を検出することができます。

たとえば、図 6の電流モニタでは、低インピーダンスのサイン波信号源がリファレンス抵抗  $(R_{REF})$  と計装アンプの1個の入力に信号を供給します。 $R_{REF}$  は高精度の非リアクティブ抵抗であり、被試験ネットワーク  $(Z_L)$  に比べて低インピーダンスです。計装アンプの出力は、 $R_{REF}$  両端の電圧にその段のゲインを乗算した値に等しく、その結果  $Z_L$  を通る電流に比例しています。回路をトリミングして最小の誤差(最大のCMRR)にするには、 $R_{REF}$  を短絡させ、 $C_1$  を調整して回路の出力を最小限に抑えます。

図 6の回路を使って複素インピーダンスを測定する場合は、ベクトル電圧計を計装アンプの出力と $Z_L$ に接続します。ベクトル・モニタは $V_L$ ÷ $I_L$ の大きさと角度を測定して、 $R_L$ = $(V_L/I_L)$ cos $\theta$ および $X_L$ = $(V_L/I_L)$ sin $\theta$ を計算します。

# 計装アンプによるフォノ・プリアンプの 改善

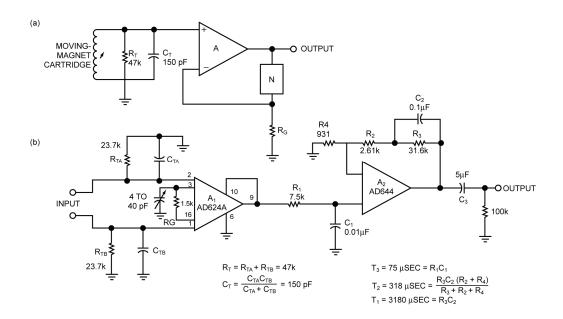

計装アンプの高CMRRは、フォノ・カートリッジ・プリアンプにも効果的です。一般に、MM型フォノ・ピックアップ(ステレオ・システムで最もよく使用されているカートリッジ)用のプリアンプでは、帰還ループ内のRIAAイコライゼーション・ネットワーク(N)とともにオペアンプを使用します(図 7a)。これらの回路はかなり単純で、1個のアクティブ・デバイスのみを使用しますが、使用するオペアンプには厳しい性能条件が課せられます。20Hz~20kHzの低レベルの信号を処理し、1kHzで40dBのゲインを提供するには、従来のフォノ・プリアンプに使用するオペアンプではユニティ・ゲインで高速かつ低ノイズを実現しなければなりません。また、複雑な帰還ネットワークを駆動するには、高い周波数で低出カインピーダンスである必要があります。最も重大な点は、シングルエンド回路では低周波のハム・ノイズをうまく除去できないことです。

### 事前ゼロ化回路によって向上する測定分解能

これに対し、別の方法によりフォノ・プリアンプ(図 7b)では、計装アンプの差動特性と低入力ノイズという特長を活かし、優れたS/N特性とイコライゼーションに依存しないゲイン制御が可能になります。この回路のAD624 計装アンプ( $A_1$ )は、MM型カートリッジ平衡出力を、イコライゼーションと残りの処理に最適なシングルエンド増幅電圧に変換します。

2個の終端抵抗( $R_{TA}$ 、 $R_{TB}$ )が DC 入力負荷( $47k\Omega$  typ)を提供し、1 対のコンデンサ( $C_{TA}$ 、 $C_{TB}$ )によってカートリッジのダンピングを行います(大部分のカートリッジは 150pF で十分です)。 差動ネットワークは、ハムを最大限除去するために信号バランスを維持し、カートリッジを正しく終端します。計装アンプのゲイン端子に接続された  $4\sim40pF$  のトリマまたは 15pF の固定のコンデンサにより、高周波 CMRR が高くなります。 $C_{TA}/C_{TB}$  の比を調整することによって、回路の高周波同相性能をさらに改善することができます。

$A_1$ 入力電流の大部分は  $R_{TA}$ と  $R_{TB}$ を流れるため、計装アンプのオフセット電流だけがカートリッジを流れます。また、AD624 のオフセット電流値はつねに 35nA 以内で、通常は 10nA に過ぎないため、入力電流に起因するオフセット誤差は計装アンプの  $250\mu$ V の入力オフセット・レベルに比べると無視できる程度になります。

部品を最大限自由に選択できるように、図 7bの設計では 2 つの 回路段でRIAAイコライゼーションを行います。 $A_1$  と出力バッファ  $A_2$  間の受動ネットワーク( $R_1$  と $C_1$ )により、75 $\mu$ sのデエンファシスが得られます。応答の 318~3180 $\mu$ sの成分は、 $A_2$ の帰還ループで生成されます。このスプリット・ネットワーク技術を使用することで、すべてのイコライゼーション要素を完全にバッファすることができます。 $A_1$  と $A_2$  間のシングル・ネットワークで 3 つのRIAA時定数をすべて一まとめにするイコライゼーション方式もありますが(参考文献 2)、このようにするとスプリット・イコライゼーションよりも出力ノイズがかなり増大します。

#### オペアンプとしての計装アンプ

モノリシック計装アンプの性能が向上 するにつれて、面白い逆転現象が起きて います。計装アンプはオペアンプで構成 されていますが、それ自体をオペアンプ としても使用できます。たとえば、右下 の図に示す高精度計装アンプ・ベースの オペアンプを考えてみましょう。この回 路では、センス抵抗とリファレンス抵抗 を出力端子に接続し、計装アンプの出力 段アンプを Howland 電流ポンプとして構 成しています(EDN、1月20日号、85頁)。 電流ポンプのコンダクタンスは非常に高 いため、出力アンプはかなり大きなゲイ ンで動作します。このゲインは CMRR に よってしか制限されず、一般に 80dB にな ります。

計装アンプをベースにしたオペアンプの全ゲインは、入力アンプを出力バッファに接続していると、80dBを上回ります。たとえば、入力ゲインを 100 に固定すると、オペアンプ構成のAD524で5×106(134dB typ)のオープン・ループ・ゲインが得られます。

図の回路の場合、オペアンプのクローズド・ループ・ゲインは 1000 になり、-3dB 帯域幅は 56kHz になります。したがって、アンプのゲイン帯域幅積は 56MHz になります。このような広帯域幅と、計装アンプの低ノイズや高安定性によって、従

来のICオペアンプでは通常達成できないような性能を実現できます。従来のオペアンプに勝るもう一つの利点は、回路のダンピング特性が1個の抵抗(R<sub>G</sub>)の設定だけによる点です。

このような計装アンプ・ベースのオペアンプは、広帯域幅で 100,000 までのクローズド・ループ・ゲインを必要とするアプリケーションに効果的です。たとえ

ば、AD524は、入力アンプのゲインが1000 に設定されている場合、ゲイン帯域幅積が1GHz になります。計装アンプ・ベースのオペアンプは高ゲイン時に最も有効です。フロントエンド・フェーズが過剰になると、非常に低いクローズド・ループ・ゲインのときに安定性が損なわれます。

計装アンプは、センス抵抗とリファレンス抵抗が回路の出力に接続されているときにオペアンプとして機能します。デュアル帰還構成では、計装アンプの出力アンプを Howland 電流ポンプとして構成することで、高オープン・ループ・ゲインのオペアンプを実現できます。

図 7. 従来のフォノ・プリアンプ (a) は、オペアンプの帰還ループ内で 1 個の RIAA イコライゼーション・ネットワーク (N) を使用します。このような回路は非常にシンプルですが、オペアンプ性能に過度の要求を課します。これより優れた回路 (b) では、カートリッジ出力をバッファする計装アンプを使用します。計装アンプの高 CMRR によって、ハム除去率は 100dB になります。

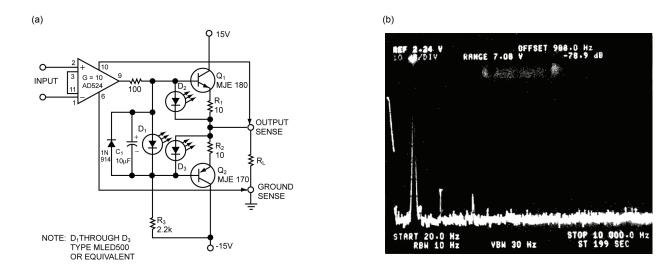

図 8. 計装アンプの帰還ループ内にある出力バッファは、高電流を駆動することができます(a)。写真(b)はバッファの低歪みを示しています。 スペクトルは、 $100\Omega$  負荷を駆動する 7V rms バッファ出力の高調波成分を示しています。

図 7bの回路では、 $A_1$ が高ゲインで動作するとノイズが最小になり、 $A_1$ のゲインが相対的に小さくなると過負荷耐性が最大になります。したがって、入力段のゲインを選択して、この2つの対立する特性の間で最適なバランスをとる必要があります。一般には、 $A_1$ のゲインがほぼ20になると最良のバランスが得られます。そのあと、 $A_2$ がネットワークの残りのゲインを提供しなければなりません。図 7bの設計では、 $A_1$ はゲイン 28で動作し、 $A_2$ はDCゲインが38になります。したがって、全DCゲインは1064または約60dBとなります。

一般に、フォノ・プリアンプの DC ゲインは次式で表すことができます。

$$G_{DC} = (1 + 40k/R_G)(1 + (R_2 + R_3)/R_4)$$

RIAA でイコライズされた 1kHz ゲインは次の式で表すことができます。

$$G_{1k} = 0.101G_{DC}$$

定数 0.101 は、RIAAイコライゼーション規格に定められた 1kHz時のゲインとDC間の比を表します。図 7bの回路では、1kHzのゲインは約 40dBになります。 $R_G$ の値を調整すれば、イコライゼーション特性に影響を与えずに回路のゲインを変更できます。また、 $R_1$ ~ $R_3$ 、 $C_1$  および $C_2$  に適切な値を選択することによって回路の応答を変更し、たとえば、テープ・ヘッドのアプリケーションに適合させることができます。

図示されているように、40dBの中帯域ゲインで、フォノ・プリアンプは基準出力 IV に対して 80dBの S/N 比を提供します。低周波 CMRR は 100dB (min) です。イコライゼーション・ネットワークのすべての抵抗を金属皮膜タイプにし、すべてのコンデンサにポリスチレンまたはポリプロピレン誘導体のものを使用すると、最大の応答精度と安定性が得られます。

多くの場合、計装アンプは規定の精度を完全に維持した状態で 5mA を超える出力電流を提供しなければなりません。大部分の IC 計装アンプは 5mA の電流を  $2k\Omega$  の負荷に駆動するよう仕様規定されていますが、その  $100\Omega$  (typ) のオープン・ループ出力インピーダンスによって高電流動作が制限されます。しかし、ユニティ・ゲイン・バッファを計装アンプの帰還ループ内に配置することで、回路の駆動上の制約を解消できます。

図 8aに、 $150\Omega$ の低負荷インピーダンスを駆動し、75mAの出力電流を提供する出力バッファ付き計装アンプ回路を示します。この回路は、LED  $D_1$  によって順方向バイアスされる 3A/40Vのコンプルメンタリ・パワー・トランジスタ( $Q_1$ 、 $Q_2$ )を使用しています。 $D_1$  のバイアス電圧によって、 $R_1$   $\ge R_2$  はそれぞれ約 140mV電圧降下し、図に示した部品の値で出力静止電流は約 15mAになります。15mA のバイアス・レベルで十分に出力段のクロスオーバー歪みを防止できます。ほかの 2 個のLED ( $D_2$ 、 $D_3$ ) は電圧クランプとして機能し、 $Q_1$  および $Q_2$ を通る電流を約 100mAに制限します。これらのLEDは、過負荷状態を表示する機能も備えています。

図 8aの回路を作製するときに、いくつかの注意が必要です。まず、最大の直線性を得るために、 $R_3$ を選択して $A_1$ の出力段でクラスAの動作が行われるようにします。また、内部回路ノードからの出力電圧ではなく出力端子からの電圧を検出する必要があります。さらに、負荷の共通端子を負荷の電源接続を介してグラウンドに接続します。そうしないと、負荷電流によって回路のアナログ・グラウンドに障害が生じることがあります。最後に、高周波発振を防止するために、バイパス・コンデンサを出力トランジスタのコレクタのできるだけ近くに配置してください。

### 参考文献

- 1 Wurcer, S A、Kitchen, C 共著「Stacked amplifiers lower noise」EDN、 1982 年 10 月 13 日 184 頁

- 2 Jung, W著「Topology considerations for RIAA phono preamplifiers」 67th Audio Engineering Society Convention、1982年11月、Reprint No 1719

- 3 Wurcer, S A、Counts, L W 共著「A programmable instrumentation amplifier for 12-bit-resolution systems」IEEE Journal of Solid State Circuits, Vol SC-17, No 6、1982 年 12 月 1102∼1111 頁

- 4 Jung, W 著『Audio IC Op Amp Applications (second edition)』 Howard W Sams and Co Inc, Indianapolis, IN、1978 年