# AN-244 アプリケーション・ノート

**AN-244**

## IC計装アンプのユーザ・ガイド

Jeffrey R. Riskin著

#### はじめに

計装アンプについて解説するときは、これはオペアンプではないという説明から始めるのが一般的です。これは十分な知識を備えたユーザにはわかりきったことであり、説明としてぎこちないのですが、このような手法は必然的で、おそらく必要なのでしょう。エンジニアがシグナル・コンディショニング・ゲイン・ブロックを必要とするとき、最初に頭に浮かぶのは、現在市販されている各種の低価格ICオペアンプが、ほぼ完璧にフレキシビリティを備えているということです。オペアンプは特定のゲイン・ブロックを構成する要素としては十分に対応しますが、要求レベルの高いアプリケーションでオペアンプ回路を使用する場合には、多くの高価な追加回路要素、特殊化された製造や試験計測器に加えて、これらのすべてを運用する高度な技術力を備えたスタッフが必要になることがあります。このアプリケーション・ノートの目的は、計装アンプが、いつどこで最適に利用できるか、そしてフレキシビリティに優れたオペアンプより優れた利点として、どのような特性が備わっているかを解説することです。

#### 計装アンプとは?

計装アンプは、高精度計測には不利な環境での動作に最適化された高精度の差動電圧ゲイン・デバイスです。実際の信号は、理想からかけ離れています。つまり、物理学の法則に従って、温度変動や電気的ノイズが発生し、さらに電流が離れた場所からリード線の抵抗を通過することで電圧降下が発生します。その上、実際のトランスデューサのほとんどはゼロの出力インピーダンス特性を備えることがなく、しかも0~10Vの電圧範囲に正確に対応しているわけではありません。電気的干渉(ノイズ)の誘導、漏れ、結合は常に、ある程度は存在します。つまり、最良の「料理本」でも、塩加減が必要とされるわけです。

計装アンプは、有用な信号のアクイジションが難しいときに使用されることを目的としています。信号源インピーダンスが高くて不平衡か、高いか、不平衡なので、計装アンプは非常に高い入力インピーダンスを備える必要があります。バイアス電流とオフセット電流が低く、比較的安定しているので、信号源インピーダンスは一定である必要はありません。平衡の差動入力が備わっているため、信号源は計装アンプの出力負荷のリファレンスとは関係なく、任意の適切なレベルを基準とします。入力平衡の目安である同相ノイズ除去が非常に高いので、リモート・センサー・アプリケーション特有のノイズのピックアップとグラウンド降下は、最小限に抑えられます。

温度や電源電圧の変動などの変化する条件下でも重要なパラメータの特性が高く、良好に維持されるように注意が払われています。最後に、計装アンプの性能にとって重要な部品はすべてデバイスに内蔵されています(ゲイン設定用の1つの抵抗または抵抗ペアを除く)。ICメーカーは仕様の最適化、特性評価、および保証を行います。ユーザは、各自で高精度のアプリケーション部品を用意したり、設計上の専門知識を持たなくても、一定の性能が得られます。

計装アンプの精度は、フレキシビリティを犠牲にして提供されます。 計装アンプのメーカーは電圧を増幅するという1つの明確なタスクに 努力を集中することで、その性能を最適化します。計装アンプは集 積化、微分、整流など、電圧ゲイン以外の機能の実行を目的とはして いません。これらのタスクは計装アンプでも実行可能ですが、オペ アンプに委ねるのがベストです。

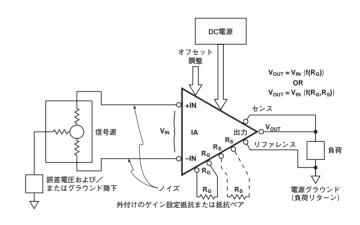

計装アンプを使用する場合、ユーザはその内部構造を詳細に理解する必要はありません。図1の基本的な計装アンプの機能図を参考にすれば、多くのアプリケーションで役立つ情報が得られます。

図1. 基本的な計装アンプの機能図

図に示す2つの入力により、「フローティング」信号源との直接的なインターフェースが可能になります。真に差動の計装アンプは、自身の入力間の電圧差のみを検出します。つまり、ノイズやグラウンド・ラインの電圧降下などの同相信号(両方の入力に存在する信号)はすべて、増幅が行われる前に入力で減算され、キャンセルされます。\*

<sup>\*</sup> 非常に高いコモン・モード電圧を含むか、または完全なガルバニック絶縁が要求されるアプリケーションでは、アイソレーション・アンブを使用してください。アナログ・デバイセズでは、シングルおよびマルチチャンネルのアイソレーション・アンブを豊富に製造しています。

1つの抵抗または抵抗ペアを使用して、計装アンプを必要なゲインにプログラミングします。あるゲインに必要な抵抗の値を計算するための伝達関数やゲイン式がICメーカーから提供されます。抵抗について特別な要求がある場合には、これもICメーカーから詳細に説明されます。

出力はシングルエンドで、計測装置で一般的に見られるグラウンド 基準の負荷を駆動するように設計されています。負荷リファレンス は電源リターンに対して共通ですが、グラウンド処理システム全体 について細心の配慮を払う必要があります(後述)。

当然ですが、計装アンプには電源を供給する必要があります。オペアンプと同様に、通常は規定の範囲内で変動することがある差動平衡電圧です。

大部分の計装アンプには、オフセット電圧(両方の入力がグラウンド接続されたときに出力側で発生するDC誤差電圧)を調整する何らかの手段が用意されています。この調整は通常、外部ポテンショメータの設定を変更することで行います。センスとリファレンスの端子によって出力電圧のリモート・センシングが可能になり、IR降下とグラウンド降下の影響が最小限に抑えられます。低電流で近接負荷を駆動する場合、センス端子を出力に直接接続し、リファレンス端子を電源コモン(グラウンド)に接続できます。センスおよびリファレンス端子のその他の使用法については、本アプリケーション・ノートの「計装アンプの応用」で説明します。

### 計装アンプの内部

計装アンプの設計には多くの方法がありますが、大部分は2つのカテゴリのどちらか1つに分類できます。最も一般的なのは、相互に接続された複数個のオペアンプと1つの高精度抵抗ネットワークで構成する方法です。この技法は、実際のほとんどの設計で部品数が最小限に抑えられるモジュールおよびハイブリッド型の計装アンプで広く採用されています。

もう1つのカテゴリは、オペアンプではなく、差動回路や制御された 電流源および反射器などの基本的な能動回路素子を採用する設計 方法です。この方法は不必要な機能や冗長機能をすべて排除し、 能動デバイス(トランジスタ)の数を最小にすると同時に、高精度抵 抗マッチングへの依存度を低減する傾向があります。この技法は、 チップ・サイズとコストが反比例するモノリシック計装アンプの設計 に一般的に採用されています。適切な高精度ICオペアンプを容易 に入手できるようになったのは最近なので、一部の旧型のモジュー ル計装アンプでも、この技法が採用されています。高ゲイン時に非 直線性が低く抑えられるので、もっと新型のモジュール計装アンプ でもこの技法を採用しています。ただし、低ゲイン時には直線性が ある程度劣化します。

#### オペアンプで構成する計装アンプ

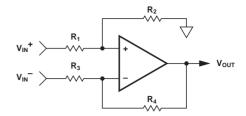

オペアンプで差動ゲイン・ブロックを構成する最も簡単な(そして手を加えていない)方式を、図2に示します。

$$V_{OUT} = V_{IN}^{+} \left(\frac{R_2}{R_1 + R_2}\right) \left(\frac{R_3 + R_4}{R_3}\right) - V_{IN}^{-} \left(\frac{R_4}{R_3}\right)$$

図2. 差動入力電圧ゲイン・ブロック (簡単な構成の減算器)

この回路では、 $V_{OUT}$ を求める数式を重ね合わせによって導き出すことが可能です。

$V_{IN}^+(V_{IN}^-$ はグラウンドに接続)の出力は、以下で求められます。

$$V_{O_1} = V_{IN}^+ \left(\frac{R_2}{R_1 + R_2}\right) \left(\frac{R_3 + R_4}{R_3}\right) \tag{1}$$

$V_{IN}^{-}(V_{IN}^{+}$ はグラウンドに接続)の出力は、以下で求められます。

$$V_{O_2} = -V_{IN}^- \left(\frac{R_4}{R_3}\right) \tag{2}$$

重ね合わせによって、以下になります。

$$V_{O} = V_{O_{1}} + V_{O_{2}}$$

$$= V_{IN}^{+} \left( \frac{R_{2}}{R_{1} + R_{2}} \right) \left( \frac{R_{3} + R_{4}}{R_{3}} \right) - V_{IN}^{-} \left( \frac{R_{4}}{R_{3}} \right)$$

(3)

$R_2 = R_4$ 、 $R_1 = R_3$ の場合:

$$V_{O} = (V_{IN}^{+} - V_{IN}^{-}) \frac{R_{4}}{R_{3}}$$

(4)

これにより、簡単な差動電圧アンプを構成しました。ただし、入力インピーダンスは低く、不平衡です。これに加えて、良好な同相ノイズ除去性能を維持するために、全4個の抵抗の比を慎重にマッチングする必要があります。

$$\begin{split} V_{OUT\ CM} &= V_{OUT\ for}\ V_{IN}^{}^{} = V_{IN}^{}^{} \\ &= V_{IN}\left[\left(\frac{R_2}{R_1 + R_2}\right)\!\left(\!\frac{R_3 + R_4}{R_3}\right) - \left(\!\frac{R_4}{R_3}\right)\right] \end{split} \tag{5}$$

ゲイン1を得る場合、全部の抵抗の値を等しくする必要があります。 4個の抵抗の1個に0.1%のミスマッチがある場合には、以下になります。

$$\begin{split} R_1 &= R_3 = R_4 = R \\ R_2 &= 0.999R \\ V_{O CM} &= V_{IN} \left[ \left( \frac{0.999R}{1.999R} \right) \left( \frac{2R}{R} \right) - \left( \frac{R}{R} \right) \right] \\ &= 0.0005 V_{IN} \end{split} \tag{6}$$

(信号源抵抗値が低くなくて、平衡でない場合には、ゲインとCMR がさらに劣化する点に注意してください)

通常の価格の標準的な抵抗器を用いた場合、たいした性能の改善 は期待できません。また、いくつかの大きい欠点を考えれば、この 構成が真の計装アンプの設計に使用されないのは当然です。

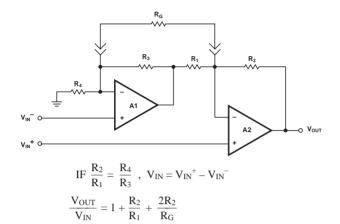

図3に示した2個のアンプによる構成手法は、図2の単純な減算器に内在する弱点のいくつかを解消します。

図3. 「2個のアンプ」構成の計装アンプ

入力抵抗値が高いので、平衡でない、ほぼゼロ $\Omega$ の出力インピーダンスをもつ信号源が得られます。さらに、1つの抵抗をスイッチするだけでゲインを変更できるため、初期トリミングが完了した時点でCMRが一定に維持されます(CMRは依然として4個の抵抗の比のマッチングに依存します)。この設計の主な欠点は、コモン・モード電圧入力範囲がゲインの関数であることから、非常に劣化する可能性がある点です。図3を参照すると、A1では、 $(R_3+R_4)/R_4$ の抵抗比で同相信号が増幅されることになります。これはA1の飽和を引き起こすので、所定の差動信号を増幅するための「ヘッドルーム」がまったく確保されません。いくつかのモジュールやハイブリッド製品には、この回路構成は最適ではないのに、構成が簡単という理由で採用されています。

オペアンプで構成する計装アンプでは最も一般的な手法を、図4に示します。

図4. 「クラシック」な3個のオペアンプ構成の計装アンプ この回路の伝達関数は、重ね合わせで計算できます。

V<sub>IN</sub><sup>+</sup> = 0の場合

$$V_a = V_{IN}^- \left( \frac{R_1 + R_G}{R_G} \right) \tag{7}$$

$$V_b = V_{IN}^- \left(\frac{R_1^{'}}{R_G}\right) \tag{8}$$

V<sub>IN</sub>-=0の場合

$$V_a = V_{IN}^+ \left(\frac{R_1}{R_G}\right) \tag{9}$$

$$V_b = V_{IN}^+ \left( \frac{R_1' + R_G}{R_G} \right) \tag{10}$$

$$V_{a} = V_{IN}^{-} \left( \frac{R_{1} + R_{G}}{R_{G}} \right) - V_{IN}^{+} \left( \frac{R_{1}}{R_{2}} \right)$$

(11)

$$V_{OUT} = -\left(\frac{R_3}{R_2}\right)V_a + V_b \left(\frac{R_3'}{R_2' + R_3'}\right) \left(\frac{R_3 + R_2}{R_2}\right) \tag{13}$$

もしR<sub>3</sub> = R<sub>3</sub>′, R<sub>2</sub> = R<sub>2</sub>′, およびR<sub>1</sub> = R<sub>1</sub>′なら

$$V_{OUT} = (V_b - V_a) \left(\frac{R_3}{R_2}\right) \tag{14}$$

VbとVaに代入を行い、計算すると、

$$V_{OUT} = (V_{IN}^{+} - V_{IN}^{-}) \left( \frac{2R_1}{R_G} + 1 \right) \left( \frac{R_3}{R_2} \right)$$

(15)

この回路構成では、ゲイン精度とCMRは $R_2$ 、 $R_2$ 、 $R_3$ 、 $R_3$ つ抵抗比マッチングに依然として依存します。ただし、CMRは $R_1$ と $R_1$ つのマッチングに依存しないことがわかります。

$$V_{CM \ OUT} = (V_a - V_b) = V_{IN}^+ \left(\frac{R_1 + R_G}{R_G}\right) - V_{IN}^- \left(\frac{R_{I}^-}{R_G}\right) - V_{IN}^- \left(\frac{R_1 + R_G}{R_G}\right) + V_{IN}^+ \left(\frac{R_1}{R_G}\right)$$

(16)

しかし $V_{CM IN} = V_{IN}^+ = V_{IN}^-$ であるため

$$V_{\text{CM OUT}} = V_{\text{CM IN}} \left[ \frac{R_1' + R_G}{R_G} - \frac{R_1'}{R_G} - \frac{R_1 + R_G}{R_G} + \frac{R_1}{R_G} \right]$$

(17)

$$= V_{\text{CM IN}} \left[ \frac{R_1'}{R_G} - \frac{R_1'}{R_G} + 1 - \frac{R_1}{R_G} + \frac{R_1}{R_G} - 1 \right]$$

(18)

$$= V_{\text{CM IN}} \left[ 0 \right]$$

$$= 0$$

したがって少なくとも理論上は、同相誤差信号を増加させることなく、ユーザは必要な数のフロントエンド・ゲイン  $(R_G$ によって決定)を設定できます。このため、非常に有用な特性として、理論上CMRRはゲインに正比例して増加します。さらに、コモン・モード電圧が $R_G$ 間を通過しないため、同相信号はゲインに関係なく1倍の増幅のみが行われるので、コモン・モード電流が流れ込みません(正常に動作しているオペアンプの入力端子間には、大きい電位差がありません)。これは、ゲインに関係なく大きい同相信号が処理できることを意味します。

最後に、この回路構成は対称なので、入力アンプの1次的な同相誤差源がトラッキングしたとして、出力段の減算器によって完全にキャンセルされる傾向があります。これらの特長により、この計装用アンプ設計技法が広く利用されています。

この種の計装アンプでは、FETまたはバイポーラ入力のオペアンプが使用されます。FET入力デバイスはバイアス電流が非常に低いので、信号源インピーダンスが非常に高い場合に適しています。ただし、FET入力オペアンプは形状に関連しないミスマッチがあるため、一般にCMRがバイポーラ・オペアンプより劣ります。(すなわち、FETのマッチングは製造プロセスによって大きく左右されますが、バイポーラ・トランジスタのマッチングはプロセスの影響をそれほど受けません)。これは、入力電圧が大きいとき、直線性およびCMRの劣化として現れます。さらに、このようなミスマッチは、一般的に入力オフセット電圧ドリフトを増加させます。このような理由から、アナログ・デバイセズの計装アンプにはバイポーラ入力段が採用されており、バイアス電流は多少高くなりますが、低入力オフセット電圧ドリフトとともに、高い直線性とCMRを達成しています。技術が進めば、FET入力の計装アンプの実現性が高くなるでしょう。

#### 専用設計の計装アンプ

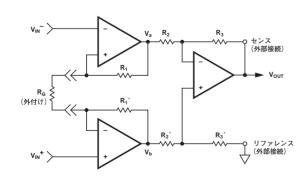

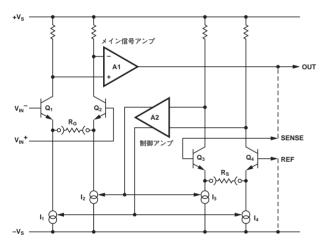

計装アンプ設計の2番目のカテゴリは、モノリシックIC回路の利点である、能動デバイスの数が最小限に抑えられています。基本的な回路図を図5に示します。

図5. 代表的なIC計装アンプの基本回路図

フォワード・ゲイン動作は、電流ゲイン (トランスコンダクタンス) が  $1/R_G$  (アンペア/ボルト)の入力差動段 $Q_1$ と $Q_2$ および、入力段のコレクタ電流の差をセンシングするメイン信号アンプ $A_1$ によって行われます。出力が再びセンスに接続されると(リファレンスはグラウンドに接続)、差動段 $Q_3$ と $Q_4$ がトランスコンダクタンス $1/R_S$  (アンペア/ボルト)のフィードバック誤差センシング・アンプとして動作します。 $A_2$ は、その段のコレクタ電流の不平衡をセンシングします。

差動電圧が入力に印加されると、 $Q_1$ と $Q_2$ のコレクタ電流は $(V_{IN}^+ - V_{IN}^-)/R_G$ だけ不平衡になる傾向があります。これは $A_1$ によってセンシングされ、 $A_1$ はセンスとリファレンス間の誤差電圧を生成します。これに応じて、 $Q_3$ と $Q_4$ のコレクタ電流が $(V_{SENSE} - V_{REF})/R_S$ だけ不平衡になります。この不平衡は $A_2$ によってセンシングされ、 $A_2$ は $Q_3$ と $Q_4$ のコレクタ電流が等化されるように $I_3$ と $I_4$ を調整します( $I_4 - I_3 = (V_S - V_R)/R_S$ )。 $A_2$ は同時に $I_1$ と $I_2$ も調整し、 $I_1 - I_2 = I_4 - I_3$ が設定されます。以下のとき、平衡状態に達します。

$$\frac{V_S - V_R}{(I_4 - I_3) R_S} = \frac{V_1 - V_2}{(I_1 - I_2) R_G}$$

(19)

$$\frac{V_S - V_R}{V_L - V_2} = \frac{V_{OUT}}{V_{DL}} = f^* ?$$

(20)

および $I_4-I_3=I_1-I_2$ とすると、

ゲイン=

$$\frac{R_{SCALE}}{R_{GAIN}}$$

(21)

慎重な抵抗マッチング条件が、慎重な能動デバイス間マッチング条件に変わることが、この解析から明らかです。IC技術では、これは高精度の写真技術と細心の注意を払った設計レイアウト、および高度に制御されたプロセス技術によって可能になります。その結果、高性能と低コストのトレードオフを最適に解決できます。

### 計装アンプの仕様

どのような電子部品でもこれを正しく利用するには、その仕様を完全に理解することが必要です。すなわち、ユーザが各仕様の意味を明確に把握していなければ、データシートの仕様表の数値はほとんど価値がありません。ここでは、標準的な計装アンプの仕様表について検討します。個々の仕様について、測定方法、およびどのような誤差が回路の性能全体に影響を及ぼすのかを解説します。場合によっては、ある仕様が特定のアプリケーションにまったく関係しないことがあります。このタイプでは、もっと一般的な状況を説明します。

仕様表の一番上には、「特に指定のない限り、記載の仕様は@ $V_S=\pm15V$ 、 $R_L=2k\Omega$ 、および $T_A=+25$ ℃時の代表値です」という記述があります。これは、これらの条件がデバイスのテストに適用される通常の動作条件であることを示しています。これらの条件から逸脱すると、性能が劣化(または改善)する場合があります。「通常」の条件からの逸脱が大きな影響を及ぼす可能性があるときには(温度の変動など)、通常は仕様に明記されます。上記の記述は、特に指定のない限り、数値はすべて代表値であることも指摘しています。「代表値」とは、この数値がICメーカーの特性評価プロセスでの平均値であることを意味しますが、個々のデバイスによって異なる場合があります。

詳細に説明していない仕様は自明であり、電子測定の基本的な知識だけで十分です。これらの仕様は、計装アンプのみに適用されるものではありません。

#### ゲイン

これらの仕様は、デバイスの伝達関数に関係します。

ゲイン式:

$$G = 1 + \frac{2(10^5)}{R_G}$$

(22)

あるゲインの $R_G$ を選択するときには、以下の式から $R_G$ の値を求めます。

(単位

$$\Omega$$

) :  $R_G = \frac{200,000}{G-1}$  (23)

例:

G=1 :  $R_G=\infty$  (オープン回路)

$\begin{array}{ll} G\!=\!10 & :R_G\!=\!22,\!222\,\Omega \\ G\!=\!100 & :R_G\!=\!2020.2\,\Omega \\ G\!=\!1000 & :R_G\!=\!200.20\,\Omega \end{array}$

200MΩの漏れ抵抗は0.1%のゲイン誤差を引き起こすので、高精度 ゲイン1を実現するには、当然のことですが、非常にクリーンなPCボードを用意する必要があります。

#### ゲイン範囲

仕様で1~1000のゲイン範囲が規定されているデバイスは、もっと高いゲインで動作する可能性がありますが(実際に動作するでしょうが)、メーカーでは性能レベルを保証していません。実際にはノイズとドリフトの面から、このデバイスでゲインを高くすることは、実際的ではありません。

#### ゲイン式誤差

この仕様の数値は、ゲイン式からの最大偏差を表します。ユーザはゲイン(ユニティ以上)を調整するか、任意の回路を設計して補償を行うことが可能です。データが最終的にデジタル信号に変換され、「インテリジェント・システム」(マイクロプロセッサなど)に送られる場合には、リファレンスを測定し、定数で乗算することによって、ゲイン誤差を補正できます。

#### 非直線性

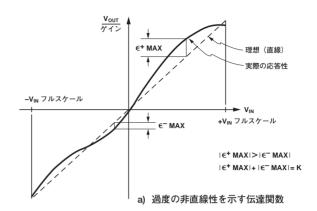

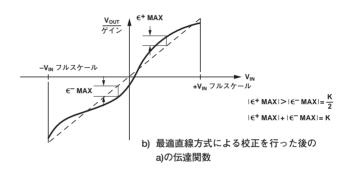

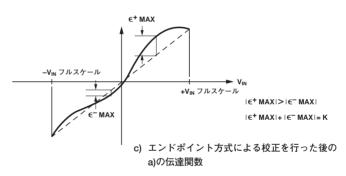

非直線性は、出力対入力のプロット上の直線からの偏差として定義 されます。図6aには、過度の非直線性を備えるデバイスの伝達関 数を示しています。この誤差の大きさは、以下の式で求めることが できます。

混乱のもとですが、この偏差を規定する基準は任意の直線または特定の直線のどちらでも可能です。高精度測定デバイスの性能に関連する、この理想的な直線を規定する方法として、2つの方式が一般的に利用されています。

非直線性仕様の「最適直線(ベスト・ストレート・ライン)」法では、正と負のピーク偏差を測定し、この正と負の最大誤差が等しくなるように、(ゲインとオフセットの調整により)デバイスの伝達関数の勾配を調整します。この方法は最適な仕様を規定できますが、正と負の最大偏差を確定するには出力信号範囲全体を調べなければならないという点で、実際の利用には困難を伴います。最適直線校正の結果を図6bの伝達関数で表しています。

非直線性を規定する「エンドポイント」法では、出力範囲の上限および下限値でオフセットとゲイン、またはどちらかを校正することが必要です。これは最適直線方式よりも非常に容易ですが、非直線性誤差が最適直線方式で規定される数値の2倍になることがあります。この最悪ケースは、伝達関数が一方向のみに「曲げられた」ときに発生します。エンドポイント校正の結果を図6cに示します。

計装アンプなどの大半のリニア・デバイスは、最適直線での直線性で仕様規定されます。アプリケーションで誤差見積りの評価を行う際には、この点を考慮に入れる必要があります。

非直線性の規定にどの方式を利用するかに関係なく、非直線性誤差は低減できません。すなわち、これらの誤差は一定でもなければ、入力または出力電圧にも比例しません。さらに、調整によって低く抑えることもできません。

図6. 非直線性伝達関数

#### ゲイン対温度

これらの数値は、温度の関数としてゲイン式からの偏差の最大値と代表値を表します。インテリジェント・システムでは、「オート・ゲイン」サイクル(リファレンスを測定し、再正規化を実行)によってこれを補正できます。

#### セトリング時間

セトリング時間とは、出力電圧がその最終値に近づき、一定の許容誤差の範囲内におさまるまでに必要な時間として定義されます。通常、これは高速のフルスケール入力ステップに対して規定され、出力スルー時間が含まれます。セトリング時間全体にはいくつかの要素が影響するので、0.1%への高速セトリングが0.01%に対して必ずしも比例的に高速セトリングするとは限りません。これに加えて、セトリング時間は必ずしもゲインの関数になるとは限りません。影響要因として、スルーレートの制限、アンダーダンピング(リンギング)、熱勾配(「長いテール」)などが挙げられます。

#### 雷圧オフセット

電圧オフセット仕様は、計装アンプの長所を表すものと考えられることが、よくあります。初期オフセットはゼロに調整できますが、オフセット電圧のシフトによって誤差が発生することがあります。インテリジェント・システムでは、オートゼロ・サイクルによってこの誤差を補正できますが、多くの小信号、高ゲインのアプリケーションは補正機能を備えていません。

電圧オフセット・ドリフトの2つの成分から構成されます。入力オフセットとオフセット・ドリフトの2つの成分から構成されます。入力オフセットは、ゲインと直接比例するオフセット成分です。すなわち、G=100のときに出力で測定される入力オフセットは、G=1のときより100倍高くなります。出力オフセットはゲインと無関係です。ゲインが低いときには入力オフセット・ドリフトが支配的で、ゲインが高いときには入力オフセット・ドリフトが支配的になります。したがって、出力オフセット電圧ドリフトは通常G=1(入力の影響が小さい)のときのドリフトとして規定され、これに対して入力オフセット電圧ドリフトは高ゲイン(出力オフセットの影響を無視できる)時のドリフト仕様として規定されます。入力に関係するすべての数値は入力換算(RTI)値として規定され、出力に及ぶ影響が「ゲイン倍」大きくなります。電圧オフセット対電源の仕様も複数のゲイン設定で規定され、同様にRTIです。

#### 入力バイアス電流

入力バイアス電流とは、DCアンプの入力トランジスタをバイアスするのに必要な電流です。FET入力デバイスのバイアス電流は比較的低く抑えられていますが、入力バイアス電流は温度の上昇に応じて大幅に増加し、11℃上昇するごとに約2倍に増加します。バイアス電流は電圧オフセットの発生源と考えられるので(信号源抵抗値によって乗算されるとき)、バイアス電流の大きさよりも、バイアス電流の変化のほうが懸念材料になります。入力オフセット電流は、2つの入力バイアス電流の差です。

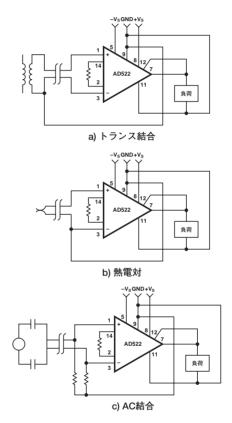

計装アンプは差動入力を備えていますが、バイアス電流のリターン経路を確保する必要があります。これを用意しないと、バイアス電流によって浮遊容量が発生し、出力が制御不能の状態でドリフトするか、または飽和する原因になります。したがって、トランスや熱電対などの「フローティング」入力信号源、およびAC結合の信号源を増幅するときは、各入力とグラウンド間にDC経路を用意することが必要です。

#### 同相ノイズ除去

同相ノイズ除去とは、両方の入力の変化量が等しいときの出力電圧変化の測定値です。一般的にこの仕様は、フルスケールの入力電圧変化および指定信号源の不平衡に対して規定されます。「同相ノイズ除去比」(CMR)は比を表し、「同相ノイズ除去」(CMR)はその比の対数を表します。たとえば、10,000のCMRRは80dBのCMRに相当します。

ほとんどの計装アンプでは、CMRRはゲインの増加に応じて大きくなります。その理由は、大半の設計では同相信号を増幅しないフロントエンド構成回路が使用されるためです。CMRR仕様の標準は出力の実測値(RTO)であるため、同相の出力信号のゲインがまったく設定されないときの差動信号に対するゲインによって、ゲインの増加に伴うCMRRが改善されます。このことは、同相出力誤差信号がゲインに応じて大きくならないことを意味しますが、ゲインの減少に応じて小さくなることを意味するわけではありません。しかし、ゲインが高く設

定されると、アンプの帯域幅が減少します。差動入力段に位相シフトの差があると同相誤差として現れるので、高ゲイン時に、CMRRは周波数依存度が高くなります。

#### 誤差の見積り解析

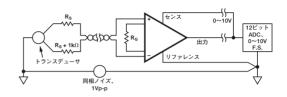

計装アンプの仕様がどのような方法で適用されるかを例証するために、不平衡トランスデューサの出力の増幅にAD522を必要とする代表的なケースについて検討します。

図7. 計装アンプの代表的なアプリケーション

図7に、離れた場所の計装アンプに $0\sim1$ Vの信号を供給する $1k\Omega$ 不平衡の差動トランスデューサを示します。計装アンプからの出力は、入力電圧範囲が $0\sim10$ Vの12ビットA/Dコンバータ(ADC)に送られます。グラウンド・リターンには1Vp-p( $0\sim10$ Hz)のノイズが乗っており、これは計装アンプの入力で同相信号として現れます。動作温度範囲は $-25\sim+85$ ℃で、校正は+25℃時に実行されます。

A/Dコンバータの分解能を完全に利用するには、入力信号を10倍増幅しなければなりません。G=10のゲイン式から、 $R_G$ は $22.22k\Omega$ の値が得られます。

初期誤差は、初期校正によって無視できる量まで低減できる誤差として定義されます。低減可能な誤差には、初期誤差に加えて、通常の動作時に発生するその他の誤差も含まれますが、これらの誤差は「インテリジェント」システムによって補正できます。たとえば、ゲインまたはオフセットの変動は、2つの既知の電圧(たとえば、高精度リファレンスとグラウンド)を測定することによって、オートゼロ/オートゲイン・サイクル中に測定できます。これは、コンピュータやプロセッサ制御装置で一般的な方法です。

低減不能の誤差とは、初期校正時または使用時に容易に補正できない誤差です。高精度リファレンス・アレイを採用すると、直線性はソフトウェアによって補正できるという意見もありますが、大部分のアプリケーションではこれは厄介であり、非現実的です。

トータル誤差が約5540ppm、つまり0.55%のとき、初期校正を実行すると、この数値は $2210\sim3330$ ppm=0.33%分だけ低減されます。このうち3000ppmをゲイン・ドリフトが占める点に注意してください。

多くのアプリケーションでは、微分直線性と分解能が最重要とされます。数値の変化が変数の絶対値よりも重視される場合にも、これが当てはまります。このようなアプリケーションでは、低減不能誤差(57.8ppm=0.006%)のみが重要です。さらに、A/D変換出力をモニタするインテリジェント・プロセッサがシステムに搭載されている場合には、オートゲイン/オートゼロ・サイクルを追加すると低減可能な誤差がすべて除去され、初期校正を実行する必要性がありません。この方法でも、誤差が0.006%に低減されます。

上の例では、微分直線性と分解能を考慮すると13ビットのA/Dコンバータを使用するのが正当です。ダイナミック・レンジは84dB(14ビット)を超えます。絶対精度は、校正およびシステムの相互作用能力に依存します。つまり、分解能(0.006%)ほど高くなることもあれば、初期精度(0.55%)ほど低くなることもあります。

#### 計装アンプの応用

#### 一般的な留意事項

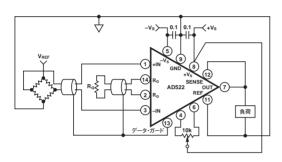

計装アンプのような高精度でゲインの高いデバイスを使用する際には、事前に特定の措置を講じる必要があります。言うまでもありませんが、クリーンなレイアウトの適用、配線を可能な限り短くすること、およびグラウンド処理方法を慎重に検討することが賢明です。図8に示す計装アンプの相互接続方式はよく練られています。

図8. AD522の相互接続

計装アンプの設計がよければ、電源変動の影響は低く抑えられます。たとえば、AD522はG=1000で電源電圧変動1%につき、わずか0.2  $\mu$  VのRTIオフセット変化特性を備えます。しかし、周波数が高くなると、内部容量が信号経路に乗る電源ノイズを増加させるので、この除去能力は劣化します。 $0.1 \mu$  Fのセラミック・ディスク・コンデンサを計装アンプに可能な限り近接させて接続する方法で電源をバイバスすることによって、この影響を最小限に抑えることが可能です。比較的低い周波数変動に対しては、もっと容量の大きいタンタル・コンデンサが効果的ですが、高性能の計装アンプはこうした低速な変動の大部分を除去する能力を備えています。

オフセット調整用のポテンショメータは通常、高ゲイン差動入力段の 平衡に影響します。ポテンショメータへの配線を短くすると、ノイズの 影響を受けやすいピンへのノイズの注入が最小化できます。

ゲイン設定抵抗R<sub>G</sub>は、ゲイン・スイッチングの目的で、離れた場所に 実装されます。良好に設計された計装アンプはこれをある程度許容 できますが、浮遊容量と配線インダクタンスによって、デバイスの周波 数補償に悪影響が及ぶことがあります。場合によっては、ちょうど計 装アンプのR<sub>G</sub>端子にRCを直列に接続してゼロ補償を追加し、浮遊 インダクタンスと浮遊容量によって発生するLCの共振を補正すること が必要になります。このリード補償によって安定性が増しますが、周 波数応答曲線のハイエンドでピークが発生します。残念ながら、この 補償は個々のアプリケーションに依存しており、一般的に経験に基づ いて決定されます。

大半の計装アンプは「センス」と「リファレンス」の出力を備えています。これにはいくつかの興味深い使用法がありますが(後述)、最も基本的なアプリケーションは負荷のリモート・センシングです。これは本質

的にIR降下を計装アンプの「ループ内部」で発生させるので、リモート負荷と大きい負荷、またはどちらかの負荷を駆動する場合、あるいは負荷グラウンドが電源リターンにしっかりと固定されていない場合に非常に役立ちます。

グラウンディングの詳細は、A.P. Brokaw著のアプリケーション・ノート「デカップリング、グラウンド等に関するICアンプ・ユーザ・ガイド」("An IC Amplifier User's Guide to Decoupling, Grounds, etc.")を参照してください。計装アンプで留意すべき主な点は、すべての信号および電源リターンが最終的には1つの直接的または間接的な共通点を持つ必要があることです。計装アンプの入力を直接結合するには、入力アンプのバイアス電流用の信号グラウンド・リターンを用意する必要があります。この直接接続を図8に示します。「フローティング」信号源またはAC結合を使用する場合には、図9に示すような間接的なリターンを設ける必要があります。

図9. 「フローティング」トランスデューサ用の 間接的なグラウンド・リターン

リモート・トランスデューサからの信号がシールド・ケーブルを経由して計装アンプに送信されることが、よくあります。これはノイズのピックアップを少なくするのに役立ちますが、ケーブルで配分されたRCが原因となって、これらの伝送線で差動位相シフトが発生することがあります。AC同相信号が存在するときには、位相シフトによって同相ノイズ除去が低下します。シールド・ケーブル端にリモートRGを接続した場合も、同じ影響が出ます。シールドが同相信号によって駆動される場合には、ケーブル容量を「ブートストラップ」すると、同相信号に対して容量が実質的にゼロに抑えられます。AD522のデータ・ガード出力は入力信号の同相成分を供給するので、これを使用して同軸入力ケーブルのシールドを駆動し、AC CMRを高くすることが可能です。この接続を図8に示しています。データ・ガードを使用しない場合は、開放のままにしてください。

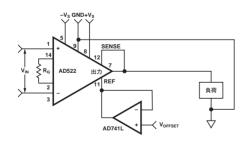

図10. 電流ブースタ出力

#### ブースト出力

前項では、負荷のリモート・センシングにセンス端子を使用する方法を説明しました。この端子のもう1つの使用方法を図10に示します。

一般的にIC計装アンプの仕様は、2k Ω負荷に対する±10Vの全出力振幅範囲について規定されています。しかし、一部のアプリケーションではもっと大きい負荷に対して、より高い電流を駆動しなければならない場合があります。図10には、高電流ブースタを計装アンプの「ループ内部」に接続し、全体の性能を大きく劣化させずに、必要な電流ブーストを実行する方法を示しています。計装アンプの出力アンプのループ・ゲインによって、バッファの非直線性、オフセットおよびゲイン誤差が最小限に抑えられます。バッファのオフセット・ドリフトも同様に低減されます。

#### オフセット負荷

リファレンス端子を使用し、出力を最大±10Vまでオフセットできます。 これは、負荷が「フローティング」の場合、またはシステムの他の回路部 とグラウンドを共有しない場合に役立ちます。さらに、高精度オフセットを注入する、直接的な手段にもなります。

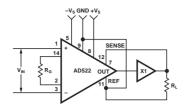

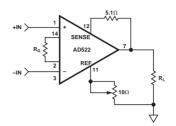

リファレンス・ピンの使用法については、2つの注意事項があります。図4に示すように計装アンプが3個のオペアンプで構成されている場合には(AD522と同様)、リファレンス端子にかかるインピーダンスはほとんどゼロに維持する必要があります。リファレンス端子からグラウンドへの抵抗の値が大きいと、非反転信号経路のケインが増加し、そのため計装アンプの同相ノイズ除去が大幅に劣化することが明らかです。図11に示すように、オペアンプを使用して低インピーダンスのリファレンス電圧を設定することが可能です。このアンプの入力オフセット電圧特性は、計装アンプのオフセット電圧性能に直接的に影響します。

図11. 出力オフセット用にリファレンス端子を 使用する方法

もう1つの注意事項はもっと明確です。計装アンプの出力電圧範囲は明確に規定されています。つまり、その範囲の大部分がリファレンス端子のオフセットで使用されると、信号用に残される範囲はほとんどありません。すなわち、オフセットと信号の合計は、計装アンプの仕様出力電圧範囲を上回ることはできません。

#### CMRの調整

リファレンス端子の抵抗値を有効に活用できます。図12に示す回路では、CMRが一時的に改善されます。

低周波数の20Vp-pの入力信号を両方の入力に加えながら、ポテンショメータで出力のゼロ調整を行います。多くのケースでは、この調整で長期ベースの改善は行われません。その理由は、デバイスの同相ノイズ除去は(外部動作に関係なくドリフトする)内部部品の長期安定性によって決定されるためです。

図12. 同相ノイズ除去の調整

#### 電流制御

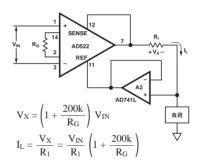

図13に示すように、センスとリファレンスの端子を利用して、計装アンプを電圧/電流コンバータに変えることが可能です。

図13. 電圧/電流コンバータ

電流設定抵抗の「ロー」サイドにリファレンスを設定することによって、出力電流は入力電圧、ゲイン、およびその抵抗の値の関数として定義できます。バッファ・アンプA2の入力には微小な電流だけが要求されるので、強制電流ILの大部分は負荷を流れます。A2のオフセットおよびドリフト仕様を計装アンプの出力オフセットおよびドリフト仕様に追加する必要があります。

#### 結論

上述のような特性をもつことから、計装アンプは重要な製品としての地位を固めつつあります。計装アンプは特殊なオペアンプではないという序文の主張が明らかになったはずです。オペアンプに比べて柔軟性には欠けますが、そのアプリケーションは無限の可能性を秘めています。計装アンプは、主にその仕様によって高精度のリニア・デバイスとされているので、その利点を活用するには、仕様を十分に理解する必要があります。長年にわたり高精度計測アプリケーション向けの部品を販売しているアナログ・デバイセズでは、モジュール、ハイブリッド、およびモノリシックICの計装アンプ製品を幅広く取り揃えており、それぞれ特定のアプリケーション向けに最適化されています。このアプリケーション・ノートが問題点を明確にするのを助け、アプリケーションに適したデバイスの選択に役立つことを希望しています。