# アプリケーション・ノート

# DC〜500MHz の アプリケーションでの AD834 の使用: RMS から DC への変換、電圧制御アンプ、 およびビデオ・スイッチ

著者: Mark Elbert および Barrie Gilbert

#### はじめに

AD834 は汎用性の高い 800MHz の帯域幅を備える 4 象限アナログ乗算器です。帯域幅 60MHz の 2 象限乗算器 AD539、帯域幅 10MHz の 4 象限乗算器 AD734、あるいは 1MHz の帯域幅を備える業界標準の 4 象限乗算器 AD534 と比較しても、最速の演算能力を備えています。モノシリック構造と高速演算性能が特長のAD834 は、従来、アナログ乗算器では不可能とされていた周波数帯域における、平衡変調/復調、電力測定、ゲイン制御、およびビデオ・スイッチングなどの HF アプリケーションに最適です。

AD834 は、精度を犠牲にすることなく速度を達成しています。 すべてのアナログ・デバイセズの乗算器と同様、製造時にレー ザー・トリミングを使用して、入力/出力オフセットをゼロに して高精度なスケーリングを実現しています。代表的なアプリ ケーションにおける全体的な静的誤差を±0.5%未満に保持する ことができます。

AD834 は、商用、工業用、および軍用温度範囲の、8 ピンのプラスチック DIP、SOIC、およびセラミックパッケージで提供され、 $\pm 5V$  の電源で動作します。

AD834 を使用するときの最大の留意点は、電流モードの出力段に関するものです。帯域幅を最大限確保するために、AD834 の出力はオープン・コレクタを用いた 1 対の差動電流の形態をとります。より標準的なグラウンド・リファレンスの電圧出力を必要とする場合には、この点が障壁となります。したがって、今回のアプリケーション・ノートでは、このような差動電流をシングルサイドのグラウンド・リファレンス電圧へと正確に変換する方法について説明します。

こうしたアプリケーションの適用事例としては、広帯域の平均2乗検出器、RMS/DCコンバータ、2つの広帯域電圧制御アンプ、高速ビデオ・スイッチ、およびトランス結合出力回路などがあります。今回取り上げたアプリケーションは、完全動作が確認済みのソリューションであり、多くの事例において、重要な部品の推奨供給元が記載されています。

#### AD834の概要

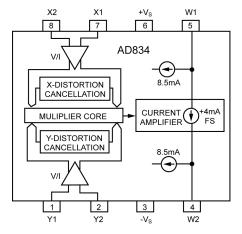

AD834(図 1 にブロック回路図を示す)は、アナログ・デバイセズの高精度アナログ信号処理領域における継続的な努力の結晶です。この製品においては、20 年にわたるアナログ乗算器の製造で培った経験が特に反映されています。製品は、レーザー・トリミングされた薄膜抵抗器を使用した、3GHエピタキシャル・バイポーラ・トランジスタ・プロセスで構築されています。微妙な細部に配慮することで、超低歪みと超低ノイズを達成しています。図 2 は、簡略ながら少し詳細にした回路図を示しています。

図 1. AD834 のブロック図

X と Y の入力は、 $285\Omega$  のトランス抵抗と約  $25k\Omega$  の小信号入力抵抗を備えた電圧/電流(V/I)コンバータに印加されます。入力電圧のフル・スケールはどちらの入力についても $\pm IV$  です。入力バイアス電流は通常、 $45\mu A$  です。したがって、オペアンプの場合と同様、オフセット電圧を最小限に抑えるために、差動ペアの両方の入力に現れる DC 抵抗は等しくなければなりません。入力端の抵抗器も高周波発振のリスクを最小限に抑えています。V/I コンバータのコモンモード範囲は、推奨電源電圧を使用して、 $\pm 1.2V$ です。この範囲内で、差動入力は、f<100kHzについて控えめに規定された 70dB の同相ノイズ除去を示します。V/I コンバータ内の偶数次歪みは本質的に低くなりますが、歪み除去回路を搭載することで、奇数次の非線形性は通常 $\pm 0.05\%$ に低減されます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属 します。※日本語資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

© Analog Devices, Inc. All rights reserved.

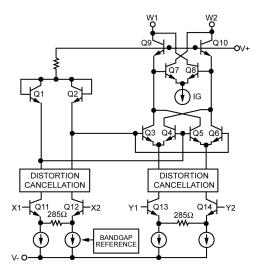

図 2. AD834 の簡略回路図

「乗算器コア」は、よく知られたトランスリニア回路です。トランスリニアの原理(参考文献 1)は、ベース・エミッタ電圧  $(V_{BE})$  とバイポーラ・トランジスタのコレクタ電流  $(I_{C})$  との間の正確な対数関係を利用しています。トランスリニア回路の入力と出力の信号は常に電流形態です。内部ノードにおける電圧スイングはきわめて小さく、このため寄生接合容量の充電/放電が必要でなくなります(これは帯域幅減少やスルーレート制限の一般的な要因となります)。このようにトランスリニア乗算器セルは本質的に高速であり、またモノシリック形態で実装することも可能です。ただし、慎重に設計しなければ、歪みが生じるおそれがあります。

この歪みは主としてエミッタ・エリアのミスマッチやコア・トランスミッタ内のオーム抵抗によって生じます(参考文献 2)。図 2 に示すように、チャンネルの命名では従来の規則を使用しています。Xチャンネルは、上記の影響を受けやすくなるものの、Y信号経路は基本的に線形となります(Q3~Q6 の 4 つの出力デバイスが、コモン/ベース段やカスコードのように多くの箇所で動作しています)。したがって、最小予想歪みを要求する信号は常にY5 チャンネルで取り扱うようにしてください。たとえば、平衡変調器のアプリケーションでは、Y入力のベースバンド信号とX入力にキャリア(ローカル発振器の電圧)を加える必要があります。

コアからの出力は、1 ペアの差動電流の形態になっています。現在、これらの電流のスケーリングは、通例、V/I コンバータが X 入力で使用していたバイアス電流を調整することによって制御され、これによってダイオード接続トランジスタ Q1 と Q2 内の電流も決定されます。

古典的な電圧出力乗算器では、抵抗器の避けられないミスマッ

チを吸収するために必要となる調整範囲は狭いため、このスケーリング係数をトリミングするという方法を受け入れることが可能です。しかし、AD834 では、伝達関数に、 $V_X$  と  $V_Y$  の 2つの入力電圧、スケーリング電圧(バンド・ギャップ・リファレンス回路で生成され、正確な値(ここでは IV と想定)にトリミングされる)、および出力電流  $I_W$  が含まれています。

$$I_{W} = \frac{V_{X}V_{Y}}{1V} \times \frac{I}{R} \tag{1}$$

この式では、抵抗 R の値が、出力電流のキャリブレーションを決定します。製造上の問題から、薄膜抵抗器には初期のバラツキによって、 $\pm 20\%$ ほどの誤差が生じる場合があります。スケール係数をトリミングするという一般的な対処法では、他の面での妥協が必要になってしまいます(たとえば、X入力の V/I コンバータで利用可能な信号範囲の縮小など)。

このため、AD834 は、コアの後に「ギルバート・セル」(参考文献 3)を配置して、必要となる R の実効値の調整ができるようにしています。実際には、電流  $I_G$  のトリミングを用いてこのセルの電流ゲインを変動させることで、これを実現しています。  $I_G$  トリム後の R の実効値は  $250\Omega$  であり、両方の入力がフル・スケールの $\pm IV$  のとき、フル・スケールの出力電流 $\pm 4mA$  になります。標準電流ゲインは 1.6 です。このタイプのアンプは非常に高速で、またコア出力をバッファリングするため、乗算器の全体的な帯域は、直接的にコア出力を使用して得られる帯域よりも実際には広くなります。

コアからのバイアス電流とゲイン設定電流  $I_G$  は、かなり大きな永続電流(通常 8.5mA) となり、出力 W1 と W2 (ピン 4 とピン 5) に流れ込みます。「差動」出力のみが厳密に $\pm 4mA$  に規定されます。

出力電流は、さまざまな方法で変換して電圧に戻すことができます。最も簡単な方法では、正電源に接続された負荷抵抗器を使用する方法がありますが、この方法では、(2 つの) 差動出力をシングルサイドの電圧に変換することはできません。

AD834 を正しく動作させるには、出力ピン (4 と 5) を V+以上 にプルアップして Q7~Q10 の飽和を防ぐ必要があります。別個 の電源を用意せずにこれを実行するには、ここに含まれるいく つかの回路で、AD834 の正電源ピン (6) と直列に電圧降下抵抗器を使用します。この場合、デカップリング目的に用いるよりも大きな値の抵抗が必要になります。

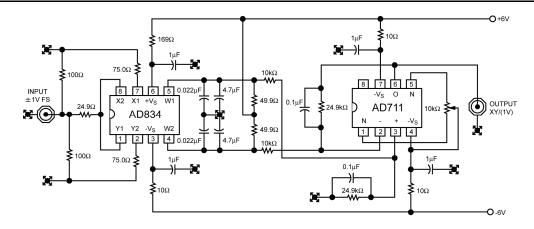

この降下抵抗器を加えることで、ピン 6 の電圧が低下し、出力トランジスタのバイアスに十分なマージンを確保できます。たとえば、図 3 の平均 2 乗回路では、 $169\Omega$ の降下抵抗器を流れる11mAの無信号時消費電流によって 1.86Vのヘッドルームが生まれます。ピン 3 の負電源と直列のデカップリング抵抗器は、単に電源をデカップリングするためにのみ実装されているため、わずか  $10\Omega$ です。

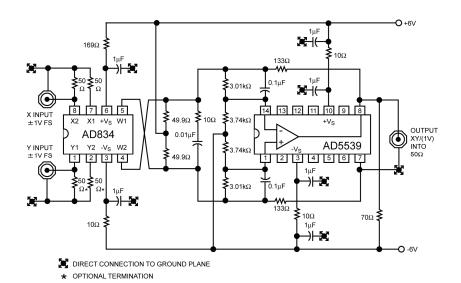

図 3. DC~500MHz の平均 2 乗回路

ただし、このアプリケーション・ノートでは、より効果的に出力を取り込む方法を重点的に取り上げています。たとえば、AD834 の出力は、十分にキャリブレーションされているため、2 つ以上の AD834 をただ並列に接続するだけで正確に加算することができますが、今回のアプリケーション・ノートでは、こうした事例も RMS アプリケーションに関する解説の中で取り上げられています。

### 平均2乗検出器

まず、平均 2 乗検出器 (図 3) の説明から始めましょう。この検出器の出力は入力電力に比例したDC電圧です。この回路では、キャリブレーション済みの信号発生器とDC電圧計を組み合わせるだけでAD834 の超高速性能を発揮することができます。

$$A (\sin \omega t)^2 = A^2 (1 - \cos 2 \omega t)/2$$

(2)

AD834 への入力が、このような正弦波である場合、瞬間出力電流(式1を使用)は、単純に

$$I_W = 2A^2 (1 - \cos 2\omega t) \, \text{mA}$$

(3)

となり、最大振幅が 1V の正弦波の場合、その平均値は 2mA となります。

したがって、AD834 のピン 4 とピン 5 の両端で測定したフル・スケール差動電圧は、 $2mA \times (50\Omega + 50\Omega)$ すなわち 200mV となります。この平均値は、 $4.7\mu F$  と  $0.022\mu F$  (AVX 製品番号 SR505E475MMAA および SR505a223JAA) の並列コンデンサとともに約 650Hz の-3dB 周波数を備えた  $50\Omega$  のコレクタ負荷抵抗器で構成されたローパス・フィルタによって得られます。

2 つのコンデンサが並列に使用されているのは、4.7μF コンデンサが、小型ながら損失の多い Z5U 誘電体を使用する一方、22μFコンデンサの方は、最大周波数で良好なフィルタリング性能を

発揮する高 Q NPO 誘電体を使用しているからです。 $4.7\mu$ F コンデンサは、-20%~+80%の許容誤差に対応しているため、-3dB 周波数は正確ではなく、また通常、その必要もありません。-3dB 周波数が 65Hz となるように設定された AD711 オペアンプの帰還抵抗器と並列に接続されたコンデンサによってさらなるフィルタリングが実行されます。

回路の平均化能力には限界があるため、低周波入力には若干のリップルが生じます。ここに示す回路では、1kHzの入力によって平均2乗プラス-42dB2kHzリップルが生成されます。100kHz入力では、リップルはわずか-80dBです。出力は帯域が制限されているため、コモンモード電圧範囲の広い一般的な低速オペアンプを使用することができ、レベル・シフトの必要性がなくなります。アンプの差動ゲインの設定によって、スケール係数を調整することができます。

図 3 の回路のフル・スケール・ゲインは、次のようにして算出します。平均出力電流は 1V (ピーク) 正弦波入力に対して $\pm 2$ mAで、各  $50\Omega$ の出力負荷抵抗器の両端に $\pm 100$ mVの電圧すなわち 200mVの差動電圧が生成されます。アンプは、2.5 の差動ゲインに対応して設定されており(ソース抵抗を上回る帰還抵抗)、1VのRMS入力に対して 0.5VDC出力の電流ゲインを生じます。

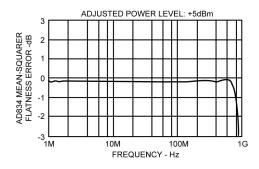

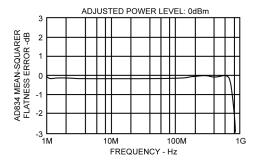

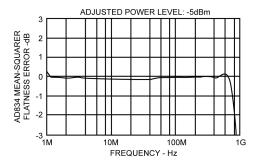

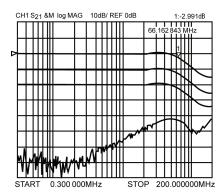

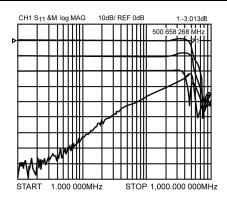

この回路の帯域幅は、パッケージのキャパシタンスとインダクタンスによって制限されます。8 ピンのサーディップでは、乗算器の応答は、パッケージの共振があるため通常 500MHzから上昇を始め、減衰前の 800MHzにてピークに達します。入力端の 24.9Ω抵抗器によって共振が弱められ、800MHzに対して本質的にフラットな応答出力が生成されます(表面実装のAD834では、パッケージのインダクタンスは異なります)。図 4 では、図 5 で示した試験構成を使用し、3 種類の電力レベルでの周波数に対する結果を示しています。

ハイ・インピーダンス入力と直列につながれた  $24.9\Omega$ を無視すると、図 3 の平均 2 乗回路に対する入力抵抗は  $50\Omega$ になります。フル・スケールの入力範囲は $\pm 1V$ となるため、 $50\Omega$ の入力負荷による測定可能な最大電力は、正弦波入力を想定した場合、10mW(20dBm)となります。

図 4. 入力電力レベルが-5dBm、0dBm、および+5dBm の場合の 平均 2 乗回路の周波数応答

より広い入力レンジを確保するには、入力端の  $50\Omega$  の直列抵抗を用いた分圧器によって、適正な終端抵抗を維持しながら、AD834 に現れる電圧を低減します。たとえば、グラウンドに接続された  $5\Omega$  抵抗器と直列の  $45\Omega$  抵抗器に入力信号を印加した場合、分圧器の中間ノードから AD834 の入力を取り出すことで、 $50\Omega$   $(45\Omega+5\Omega)$  の終端抵抗を維持しながら、入力信号は  $20\mathrm{dB}$  減衰します。

低電力信号の検知は、DC オフセットとオペアンプの同相ノイズ除去によって制限されます。たとえば、 $50\Omega$  両端の 22.4 mV RMS に相当する-20 dBm の信号によって、オペアンプに 1 mV のオフセットがあるだけで、4.5 %の誤差を生じます。AD834 の X チャンネルのオフセットがわずか 2 mV の場合、10 %の誤差が生じる可能性があります。

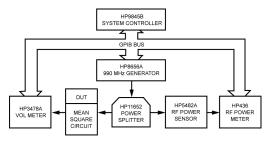

図5. 試験の構成

#### RMS/DCコンバータ

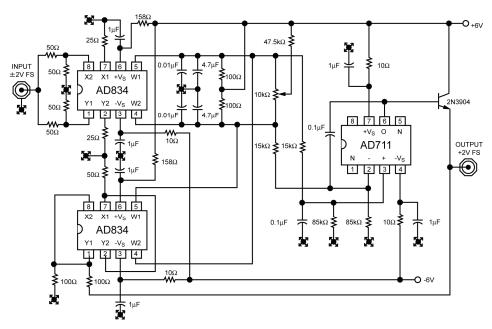

2乗平均平方根 (RMS) 回路 (図 6) は、上述の平均 2乗検出回路およびその後の平方根回路と大差はありません。周波数応答は、フロント・エンドのスクエアラと出力フィルタによって決まります。平均 2 乗の説明で示したように、スクエアラは、500MHzを十分に超えて機能する一方で、下位の-3dBの周波数応答は 340Hzです( $100\Omega$ および  $4.7\mu$ F)。入力端の抵抗分割器ネットワークによって、フル・スケールの入力電圧が $\pm 2V$ ピークとなるよう設定されています。

平方根機能は、AD711 オペアンプの帰還ループ内にある AD834 の 2 乗演算回路によって実行されます。2N3904 トランジスタは、バッファとして機能します。バッファリングされた出力と、平方根セクションで使用される AD834 の X と Y のチャンネル入力の間の抵抗分割器ネットワーク(2 つの  $100\Omega$ )により、出力スケーリングが $\pm 2V$  のフル・スケールとなるように設定されます。

2 つの AD834 の出力は、電流差分されています。 AD843 は高精度なレーザー・トリミング法で微細化加工された出力信号経路を備えており、正確な出力の差分と加算を得ることが可能になります。 AD711 は、2 つの AD843 間の信号電流の差を強制的にゼロにします。ゼロ化によって生じる誤差はいずれも、2 つの $100\Omega$  のプルアップ抵抗の両端に電圧を生成します

$15k\Omega$ 、 $85k\Omega$ 、および  $0.1\mu F$  のネットワークによる追加のフィルタリングとレベル・シフトを経た後の残留誤差は、AD711 のオープン・ループのフル・ゲインによって増幅されます。増幅された誤差信号によって、帰還ループ内の AD834 の出力がAD834 の平均 2 乗化出力と一致するよう補正されます。RMS 回路の出力が回路入力の平均 2 乗の平方根と等しい場合は、誤差=ゼロとされます。以上が RMS 機能です。

小信号レベルでの回路の精度は、不可避的に発生するオフセット電圧に左右されます。平均 2 乗機能に 1 mv の誤差をともなう公称値 0 V を入力すると、 $1 \mu \text{V}$  の出力誤差が生成されます。同じ入力誤差を平方根回路に通した場合は、31.6 mV の出力誤差が生成されます。

図 6. DC~500MHz RMS/DC コンバータ

## DC結合VCAアプリケーション

AD834 の DC 動作が収まらない場合には、ある種のレベル・シフト (パッシブまたはアクティブのいずれか)を採用する必要があります。ほとんどの場合、高速オペアンプのコモンモード範囲は不十分であるからです。以下のアプリケーションでは、広帯域電圧制御アンプの実装においてアクティブおよびパッシブのレベル・シフト回路を使用しています。

# パッシブ・レベル・シフトを使用 した DC~60MHz 電圧制御アンプ

図 7 は、パッシブ・ネットワークをレベル・シフタとして用いた回路図を示しています。ここで選択されたオペアンプはAD5539です。

図 7. パッシブ・レベル・シフトを使用した DC $\sim$ 60MHz 電圧制御アンプ

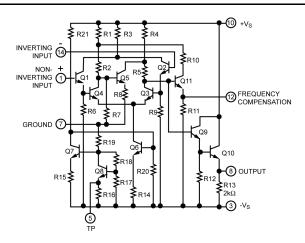

図 8. AD5539 オペアンプの簡略回路図

AD5539 は、AD834 と同じプロセスで製造されており、クローズド・ループの高ゲインにて 2GHzのゲイン帯域幅積を実現しています。AD5539 は、他のほとんどのオペアンプとは異なり、グラウンド・ピンとすべてがNPNの出力段を備え、「クラスA」で動作して製品の高速性(図 8 を参照)を実現しています。詳しく測定すると、出力ノードと入力の間、およびこれらの電圧とグラウンドの間の「ヘッドルーム」は限られていることが分かります。こうした事実やAD5539 の高速性、あるいはこの製品に特有のいくつかの特性を考えると、この製品を使用する際には特別な配慮が必要となります。

最初に、クラス A の出力段による影響について考えてみましょう。ほとんどのオペアンプでは、負荷に対して出力の「プルアップ」および「プルダウン」の両方が可能ですが、NPN エミッタ・フォロワ出力段はプルアップだけが可能です。AD5539は、 $2k\Omega$  の内部プルダウン抵抗(R11)を備えており、2 または3 ミリアンペアのみ供給できます。汎用の高速乗算器は、最小予想負荷抵抗  $50\Omega$  を駆動しながら、少なくとも $\pm 1V$  のスイングが必要です。この出力レベルでは、負荷電流は $\pm 20mA$  となり、したがって、外付けのプルダウン抵抗器によってこの負荷電流を供給する必要があります。実際には、プルダウン電流は、これを大幅に上回るため、慎重な配慮が必要となります。

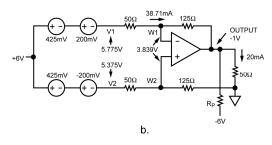

図 9 は、計算の方法を示しています。 425 m Vの電圧源は  $\Gamma_{IB}R_{C}$ 」で表され、AD834 の 8.5 m Aの永続電流に負荷抵抗器 $R_{C}$  (ここでは  $50 \Omega$ に設定)を乗じたものです。図 9 (a) の 200 m V の電圧源は、フル・スケール出力電流が +4 m A のとき、  $\Gamma_{Iw}R_{C}$ 」の発生源となります。ここから、V1-5.375 とV2-5.775 Vを計算します。

次に、W2 端での電圧を計算します。理想的なオペアンプに流れる入力電流はゼロであるため、W2 に負荷はなく、電圧は単純に V2 に減衰率 125/(125+50)を乗じた値、すなわち 4.125V となります。理想的なオペアンプに流れる入力電圧がゼロのため、W1 は同じ電圧となり、上側の  $50\Omega$  の抵抗器に流れる電流を計算すると、(5.375-4.125)/50mA すなわち 25mA となります。繰り返しますが、オペアンプの入力端には本質的に電流が存在しないため、25mA の電流はすべて  $125\Omega$  の帰還抵抗器に流れ込み、その両端で 3.125V の電圧降下をもたらします。最後に、W1 端の電圧 (4.125V) からこの電圧降下を減算して出力を計算します。つまり、出力は+1V となります。

この時点で、やや驚くべき結果が生じています。すなわち、負荷に対しては 20mA の電流が流れる一方で、帰還抵抗器にはそれよりも大きな 25mA という電流が流れているのです! こうした珍しい現象が起きるのは、スケーリング係数を目標値にまで低減するためにはきわめて低い値の帰還抵抗器が必要となるからであり、また、W1 と W2 の出力に正しいバイアスをかけるためには AD834 の出力端に比較的高い電圧をかける必要があるからです。このように、負荷に 20mA を供給する場合、プルダウン抵抗  $R_p$  には少なくとも 5mA を供給して AD5539 の出力エミッタ・フォロワにバイアスをかける必要があります。 AD834 の出力電流が反転すると状況はさらに深刻になります。  $50\Omega$  の負荷に 20mA をシンクさせる必要が生じ、帰還抵抗器両端の電圧はさらに高くなるからです。

この状況を 図 9 (b) に示します。計算は先ほどとまったく同じで、帰還抵抗器を流れる電流は 39.7mAであることがわかります。このため $R_p$ は、帰還経路において 20mAの負荷電流に加えて 40mA程度の追加電流を供給する必要があり、この時、両端の電圧は 5Vとなります。このため $R_p$  = 83 $\Omega$ が必要となります。実際には、この値を若干低くして、スルーレートによって立ち下がり時間が制限されるのを防ぐ必要があります。また、高負荷状態の下で限定されたAD5539 のゲインを補うため、帰還抵抗器は 125 $\Omega$ から 133 $\Omega$ に増やします。50 $\Omega$ の負荷、70 $\Omega$ のプルダウン、および約 150 $\Omega$ の実効帰還抵抗器の並列和を計算した場合、アンプに対する実際の負荷はわずか 24 $\Omega$ となります!

AD5539 は、5 より大きな非補償ゲインで安定しますが、この回路の AD5539 は、3 をわずかに超えるゲインで動作しています。 $50\Omega$  の負荷を駆動する場合は、オープン・ループ・ゲインに見合った  $0.01\mu F$  と  $10\Omega$  のネットワークで補償することで安定に動作します。より大きなインピーダンス負荷に対しては、 $10\Omega$  よりも低い補償抵抗器を用いるほうが良いでしょう。

図 9. プルダウン抵抗の値を計算する等価回路

レベル・シフト・ネットワークは、AD5539 の入力に対するノード W1 と W2 の間にあり(その平均電圧は約+4V)、グラウンドの近くに配置する必要があります。以下に示した値の場合、オペアンプの入力は、わずかにグラウンドを下回って設定されます(約 $-460 \mathrm{mV}$ )。このネットワークは、低周波オープン・ループ・ゲインを半減するため、AD5539 の入力端にオフセット電圧が存在する場合に、DC の精度に若干の影響を及ぼします。出力オフセットが重要になる場合には、 $3.74 \mathrm{k}\Omega$  の抵抗器と直列に  $500\Omega$  のポテンショメータを挿入し、そのスライダを $-6\mathrm{V}$  に設定する必要があります。これで X と Y の入力をゼロに設定した状態でゼロ出力用に調整されます。

また、AD834 の「内部」ピン X1 と Y2 を接地することで、HF (高周波) フィードスルーを最小限に抑えています。結果として生じる X 入力での位相反転は、W1 と W2 を入れ替えることによって修正できます。

図 10 は、X入力とY入力に加える入力パルスを+1Vに設定した状態でのパルス応答を示しており、立ち上がり時間が 6nsであることがわかります。

図 10. DC~60MHz 電圧制御アンプのパルス応答

図 11 は、+1V、316mV、+100mV、および 0VのY入力に対する HP8753Bネットワーク・アナライザ上での一連の周波数応答を 示しています。0Vの場合、Y入力は、入力オフセットがゼロに なるように調整されています。高周波フィードスルーは、フル・スケールの-65dB (f < 3MHz) を下回ることに留意してく ださい。

図 11. DC~60MHz 電圧制御アンプの周波数応答

# アクティブ・レベル・シフトを 使用したDC〜480MHz電圧制御 アンプ

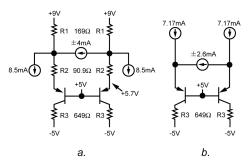

図 12 (a) は、コモン・ベース段またはカスコードにPNPトランジスタを使用したアクティブ・レベル・シフタを示しています。ここで、AD834は、3つの理想的な電流源(2つは 8.5mAバイアス電流用で、1つは $\pm 4$ mA差動信号電流用)によってモデル化されています。トランジスタのベースを $\pm 5$ Vに固定し、エミッタの電位が 5.7Vで安定するように設定すると、信号が存在しないときのR1とR2の抵抗器の両端の電圧は 3.3Vになります。図 12 (b) は、等価回路を示しています。

図 12. アクティブ・レベル・シフトを使用した AD834 の出力段

信号の定電流源がゼロになるときのエミッタに流れる電流を算出することで、7.17mA の等価 DC バイアス電流が求まります。AC ドメインでは、信号の定電流源によって、R1 と R2 の両方がロー・インピーダンス・ノードに固定されています。詳しく考察を加えることで、元の信号電流は、次式から算出されることが分かります。

$$\pm 2.6 \text{mA} = \pm 4 \text{mA} \times \frac{\text{R1}}{\text{R1} + \text{R2}} \tag{4}$$

AD834 の出力は、インピーダンスが非常に高く、等価直列抵抗は無視することができます。カスコードのエミッタに流れ込む 7.17mA の電流は、良好な  $\alpha$  と R3 両端の電圧を想定した場合、すべてカスコードのコレクタから送出されます。

$$4.65V = 7.17mA \times 649\Omega \tag{5}$$

オペアンプの入力は、グラウンドを 350mV 下回り、広帯域アンプのコモンモードにおける電圧の範囲内に収まります。

スプリアスによるポールが生成されない場合、カスコードとして設定されたトランジスタの帯域幅は、トランジスタのユニティ・ゲイン周波数帯域( $f_r$ )と一致します。トランジスタのエミッタ・ベースの寄生容量に対して並列和が大きすぎたり、トランジスタのコレクタ・ベースの寄生容量に対して R3 が大きすぎるような R1 および R2 を選択すると、回路の周波数応答劣化の原因となる不要なポールが発生します。

図 13. アクティブ・レベル・シフトを使用した DC~480MHz 電圧制御アンプ

アクティブ PNP のレベル・シフタを使用するときのもう 1 つの落とし穴として考えられるのが、カスコードのエミッタで生じる発振です。バイポーラ接合トランジスタのエミッタの入力インピーダンスは、ゲイン帯域幅積( $f_T$ )に近づいた周波数において誘導性を帯び、一方 AD834 の出力は、容量性を帯びます。システムの高帯域幅が原因となって、これらのインピーダンスによって発振を生じる可能性があります。

このような発振を防ぐため、図 12 のエミッタは、R2 によって AD834 の出力から分離されています。これにより、式 4 にある とおり、信号が減衰(ゲイン制御)されている間は、発振を防ぐことができます。図中の 2N3906 は、共振や発振を生じることのない広帯域のレベル・シフトに対応していますが、他のトランジスタを使用するときには、慎重な取り扱いが必要です。

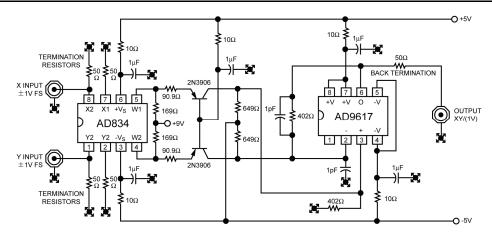

図 13 に示すとおり、カスコードのコレクタにおける信号電流は、 差動電流/電圧コンバータの構成で広帯域アンプに供給されま す。この構成は、オペアンプ駆動の電流/電圧コンバータとよ く似ており、通常、D/Aコンバータを増大する電流出力に追従 します。

AD9617 は、電流/電圧コンバータを駆動するのに最良の選択肢です。AD9617 は、第 2 世代のトランスインピーダンス・アンプ (電流帰還アンプまたは TZ アンプとしても知られています) であり、十分な相補出力段を備え(この点で AD5539 とは異なります)、 $400\Omega$  の帰還抵抗器を使用できるように最適化されています。

AD9617 の入力は、カスコードのコレクタと直結されています。オペアンプは、入力ノード間に仮想の短絡を生成し、すべての信号電流が強制的に帰還経路を流れるようにします。コンバータの差動トランス抵抗は  $400\Omega$  です。望ましいスケーリングは、上述の R1 と R2 の減衰ネットワークによって達成することができます。AD9617 の出力端における回路のフル・スケール・ゲイン(X=Y=1V)は、次式で計算できます。

$$2 \times 2.6 \text{mA} \times 400 \Omega = 2.08 \text{V} \tag{6}$$

反転終端抵抗器の後は 1.04V となります。実際の回路では、フル・スケール・ゲインはユニティにより近くなります。

図 14 は、+1Vに設定されたX入力とY入力に加えられるフル・スケールのステップ応答(-1V $\sim+1$ V)を示しています。若干のオーバーシュートを示しつつも(リンギングはない)、立ち上がり時間が 2nsを下回る回路性能を実証しています。出力のスルーレートは 500V/ $\mu$ sを超えています。

図 14. 広帯域 VCA のステップ応答

図 15 は、+1V、316mV、+100mV、および 0VのY入力に対する HP8753Bネットワーク・アナライザ上での一連の周波数応答を 示しています。Y入力は、実際には、入力オフセットがゼロに なるように調整されています。回路に 500MHzの小信号帯域幅 (0dBmの入力電力レベルにて) があることに留意してください。この帯域幅は、反転ノード端の 2 つの 1pFコンデンサによるも のと考えられます。高周波フィードスルーは、フル・スケール の-80dB (f < 2MHz) を下回ります。

Application Note AN-212

図 15. 広帯域 VCA の周波数応答

### AD834をビデオ・スイッチに応用

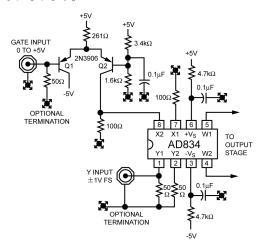

Xチャンネルにゲート制御として 0Vまたは+1Vを加え、Yチャンネルにビデオ信号を加えると、AD834 は、高速ビデオ・スイッチとして機能します。図 16 は、この概念を示しており、ECLスイッチのまわりに高速電流スイッチング回路を配置しています。電流は、入力電圧に応じてQ1 またはQ2 のいずれかを流れます。電流スイッチングにより、確定済みのレベル(+1V とグラウンド)への高速でクリーンなスイッチングが可能となり、ゲート入力をオーバードライブまたはアンダードライブできるようになります。

図 16. 高速ビデオ・スイッチとして機能する AD834

AD834 は、ゲート回路入力端でゲート入力が+1V から+2V に上昇するとスイッチがオンになります。1V 未満では、Q1 が、 $216\Omega$  の抵抗器から流れるほぼすべての電流を吸収します。したがって、2N3906 トランジスタは、オフ状態になります。この状態で、X2 入力からグラウンド間の  $100\Omega$  抵抗器は Y チャンネルを正確に遮断し、出力への Y チャンネルのフィードスルーの測定値は-50dB です。Q2 のベースを 1.6V に保持した状態では、トランジスタのエミッタの電位は 2.35V です。 $261\Omega$  抵抗器から流れる安定した 10.2mA の電流(マイナスのベース電流)により、ハイレベルのゲート入力とは関係なく、X2 入力端の  $100\Omega$  抵抗器の両端に+1V が生成されます。

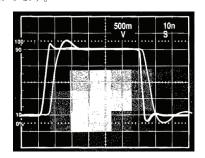

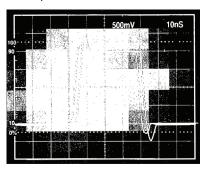

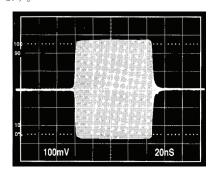

図 17 は、200MHz信号をゲーティングする、立ち上がり時間が

1.5nsのパルスのスコープ写真を示しています。得られるエンベロープの立ち上がり時間は 2.7nsで、立ち下がり時間は 3.0nsです。切り替えられた信号はかなり遅延する場合がありますが、3.5nsのエンベロープ立ち上がり時間を維持するためには、AD834 からの出力段は 100MHzより大きな帯域幅を備えている必要があります。

図 17. ビデオ・スイッチの立ち上がり時間

### 出力のAC結合方法

多くのアプリケーションで、出力端の DC 成分は切り捨てられてしまう可能性があります。このような場合、広帯域バッファを用いることで、簡単に AD834 の出力を AC 結合することができます。下記の回路では、AC 結合されたパッシブ出力回路にシンプルなトランスとバランを配置しています。

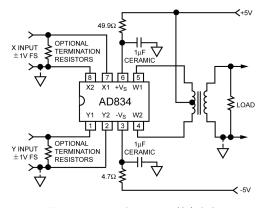

### トランス結合出力

図 18 では、センター・タップ出力トランスを使用しています。この出力トランスは、出力W1 とW2 において必要となるDC負荷状態を実現し、適切な巻数比を選択することによって、目標の負荷インピーダンスに一致するように設計されています。トランス設計の個々の選択は、全面的にアプリケーションに依存しています。トランスは入力においても使用される場合があります。センター・タップ・トランスは、平衡信号で入力を駆動することによって、高周波歪みを削減し、またHFフィードスルーを低減することができます。適合するセンター・タップ・トランスとしては、Coilcraft WB2010PCがあり、メーカーの仕様では、0.04MHz~250MHzの帯域で動作します。

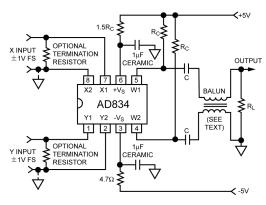

図 18. AD834 とトランス結合出力

# バラン結合出力

図 19 は、DCオフセットを取り除くためのブロッキング・コンデンサとバランを使用した回路を示しています。バランは、特別な効果を目的とした一種のトランスであり、差動(平衡)信号をシングルサイド(不平衡)の出力に変換するものです。バランは、短い伝送線をトロイダル・フェライト・コアに巻き付けたもので、平衡("bal"anced)出力を不平衡("un"-balanced)出力に変換します(これがバラン"bal-un"という用語の由来です)。

図 19. AD834 とバラン結合出力

使用する記号は、トランスの場合と同じですが、動作モードはまったく異なります。第一に、この場合、負荷はラインの特性インピーダンスと等しくする必要があります。ただし、ラインの長さが短い場合には、さほど気にする必要はありません。ラインを反転終端するためにコレクタの負荷抵抗器  $R_c$  を置く場合もありますが、これも、電気的に長いラインを使用する場合にのみ必要となります。ほとんどの場合、DC 条件が許す限り  $R_c$  の値を大きくして、負荷に対する電力の損失を最小限に抑えます。ラインには、小型の同軸ケーブルまたはツイスト・ペアが使用できます。

バランの帯域幅の上限は、伝送ラインの品質のみが決定要因になることに留意する必要があります。したがって、通常は乗算器の帯域幅を超えることになります。これは、磁気コア内の磁

束として信号が伝達されるため、コアの損失と漏れインダクタンスの影響を受ける、従来のトランスの場合とは異なります。 帯域幅の下限は、全体として、ラインの直列インダクタンスと 負荷抵抗によって決まります(ただしブロッキング・コンデンサ C が十分に大きい場合)。実際には、バランは、トランスよりもかなり広い帯域幅に対して優れた差動/シングルサイド変換を実現できます。

#### 実装

これらの回路を製作するには、高度な高周波技術が要求されま す。文中の回路図は、推奨される適切なレイアウトを示してい ます。今回のアプリケーション・ブリーフで取り上げたすべて の回路において、グラウンド・プレーンの設置が必須となりま す。PCB の部品側の面をできる限り広く覆う必要がありますが、 IC の真下や個々のピンの周囲まで覆う必要はありません。ソ ケットは、ピンの容量やインピーダンスを増大することになる ため、使わないようにしてください。ソケットが必要な場合は、 AMPの製品番号 6-330808-3 など専用のピン・ソケットを使用し てください。このようなソケットは、モールドされたソケッ ト・アセンブリに比べてはるかに浮遊リアクタンスが少なくな ります。各電源トレースは、メインのデカップリング・コンデ ンサに加えて、0.1μF の低インダクタンス・セラミック・コンデ ンサを用いて、IC にてデカップリングしてください。すべての リード長は可能な限り短くします。リード長が 1 インチより長 い場合は、ストリップライン手法を使用する必要があります。

### 参考文献

(参考文献 1) Barrie Gilbert 著『Translinear Circuits: A Proposed Classification』 Electronic Letters、Vol.11, No.6、pp.126-127.

(参考文献 2) Barrie Gilbert 著『A Precise Four-Quadrant Multiplier with Subnanosecond Response』 Journal of Solid State Circuits、Vol. SC-3, No.4、pp.365-373.

(参考文献 3) Barrie Gilbert 著『A New Wideband Amplifier Technique』 Journal of Solid-State Circuits、Vol. SC-3, No.4、pp.353-365.