# AN-1549

## アプリケーション・ノート

#### ADuCM4050 内蔵 ADC の性能を最適化

#### はじめに

生体信号のモニタリング、温度センシング、イメージングなどのアプリケーションでは、通常、高ダイナミック・レンジで高分解能の A/D コンバータ (ADC) が必要となりますが、これによりコストが上昇し、消費電力が増大します。

このアプリケーション・ノートでは、ADuCM4050 システムに内蔵された 12 ビット ADC の性能を最適化する際の、オーバーサンプリングと平均化の技術およびサンプリング・クロックと電圧リファレンスの選択による影響について説明します。また、ADuCM4050 の ADC から取得されたサンプルをオーバーサンプリングおよび平均化する技術を実行する、プログラミング・フローとアプリケーション例についても説明します。

#### ADuCM4050 について

ADuCM4050 マイクロコントローラ・ユニット(MCU)は、処理、制御、および接続を目的とする超低消費電力の統合化されたミックスド・シグナル・マイクロコントローラ・システムです。この MCU システムは、ARM® Cortex-M4F プロセッサをベースにしています。また、この MCU には ADC サブシステムと共に、デジタル・ペリフェラル、内蔵のスタティック・ランダム・アクセス・メモリ(SRAM)とフラッシュ・メモリ、およびクロッキング、リセット、パワー・マネージメントの機能を実現するアナログ・サブシステムが集約されています。

ADuCM4050 MCU はダイナミックおよびソフトウェア制御のクロック・ゲーティングや電力ゲーティングなど、複数の電力モードや機能を集約し、極めて低いダイナミック電力と休止電力をサポートしています。

ADuCM4050 の全仕様は、ADuCM4050 のデータシートに記載されています。

#### ADC の最適化

ADuCM4050 マイクロコントローラは、最大 1.8MSPS まで動作可能な高速、マルチチャンネルの 12 ビット ADC を内蔵しています。ADC コントローラは、一連の変換を行いながら、専用のダイレクト・メモリ・アクセス(DMA)チャンネルを使用してデータをシステムに転送するように設定できます。この設定により、プロセッサは(デバイス全体の消費電力を最小限に抑える)FlexiTMモードになり、他のタスクを実行できます。

ADC の性能は、オーバーサンプリングと平均化、電圧リファレンスの選択、サンプリング・クロックの選択、および消費電力の観点から向上させることができます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本語配数の商標および登録商標は、それぞれの所有 者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2018 Analog Devices, Inc. All rights reserved.

Rev. **0**

本 社/〒105-6891

東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F電話 03 (5402) 8200

大 阪営業所/〒532-0003

大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F電話 06 (6350) 6868

名古屋営業所/〒451-6038

8 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 40F 電話 052 (569) 6300

## 目次

| 1 |

|---|

| 1 |

| 1 |

| 2 |

| 3 |

| 3 |

| 2 |

| 2 |

| 4 |

| 2 |

| 4 |

| 4 |

|   |

| サンプリング・クロックの選択       | 6    |

|----------------------|------|

| サンプリング・クロック源の選択      | 6    |

| 電力の最適化               | 7    |

| リファレンス・バッファの低消費電力モード | 7    |

| Flexi モード            | 7    |

| 高電力降圧                | 7    |

| オーバーサンプリングと平均化技術の実装  | 8    |

| プログラミング・フロー          | 8    |

| アプリケーション例の概要         | 11   |

| 結果                   | . 12 |

| 参考文献                 | 13   |

#### 改訂履歴

7/2018—Revision 0: Initial Version

## オーバーサンプリングと平均化

オーバーサンプリングは、内蔵 12 ビット ADC をアプリケーションにおいて効率的に使用するための 1 つの技法です。

ADuCM4050マイクロコントローラの ADC サブシステムには、ハードウェア・コントローラでオーバーサンプリングと平均化の技法を実行するオプションがあるため、MCUで専用のソフトウェアを実行する必要はありません。この結果、ADC サブシステムでは、アルゴリズムを計算する際のプロセッサのオーバーヘッドと消費電力を低減できます。オーバーサンプリングの概念のセクションでは、オーバーサンプリングと平均化の手法を使用した ADC の性能向上について考察します。

#### オーバーサンプリングの概念

オーバーサンプリングは、ナイキスト周波数  $f_{s/2}$  よりも周波数 の高い入力信号をサンプリングするプロセスです。ここで、 $f_{s}$  はサンプリング周波数です。

入力信号を  $M \times fs$  でサンプリングして、M 個のサンプルを平均 すると 1 つのサンプルが得られます。係数 M は、オーバーサンプリング係数と呼ばれています。

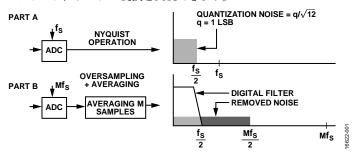

図1の Part Aに示すように、ナイキスト帯域(DC〜 $f_s/2$ )内に量子化ノイズが一様に分布する理想的な n ビット ADC を検討してみましょう。図1の Part B に示すように、入力信号をこの ADC を使用してはるかに高いサンプリング・レート( $Mf_s$ )でサンプリングすると、ノイズは  $DC \sim Mf_s/2$  の広い帯域幅にわたって分布します。M 個のサンプルごとの平均化処理はデジタル・フィルタとして機能するため、入力信号の帯域幅に影響を与えずに広帯域ノイズの大部分を除去することができます。次式に示すように、この処理を行うと、S/N 比(SNR)はデシベル単位で増加します。

$$S/N \not = 6.02N + 1.76 + 10\log_{10}M$$

(1)

ここで、Nは理想的なADCの有効ビット数(ENOB)です。

このようにして、低分解能の ADC を使用した場合でも高分解能のアナログ/デジタル変換を実現できます。

図 1. 周波数領域でのオーバーサンプリングと平均化の効果

この技術を適用すると、信号帯域外のノイズが除去され、ダイナミック・レンジが  $10\log_{10}M$  だけ増加し、ENOB が $\sqrt{M}$  だけ増加します。ここで、M はオーバーサンプリング係数です。

一般に、サンプリング周波数が倍増するごとに、S/N比は3dB増加し、ENOBは0.5ビット向上します。

例えば、理想的な場合では、4つの 12 ビット ADC のサンプルを 平均化すると、ENOB は 1 ビット増加し、ダイナミック・レン ジは 6dB 向上します。

一般に、ADCでは量子化ノイズ、熱ノイズ、ADCの非直線性による歪み、および、クロックやリファレンスをはじめとする様々な要素による何らかの外部ノイズが発生します。これらのノイズが原因で、性能の実測値は理論値ほど高くはなりません。50kSPSのときにノイズ・フリー・ビットが 10.5 の 12 ビットADCを検討してみましょう。入力信号で隣接する 2 つのサンプルを平均化すると、有効なサンプリング周波数が 25kSPSに減少し、ノイズ・フリー・ビットが 11 ビットに増加します。更に、隣接する 4 つのサンプルを平均化すると、有効なサンプリング・レートは 12.5kSPS に減少し、ノイズ・フリー・ビットは12.5 ビットに増加します。

隣接するサンプルを平均化すると、信号内に存在する無相関ノイズだけが減少するので、ADC のノイズ・フロアが減少し、S/N 比が向上します。ただし、積分非直線性 (INL) は変わりません。したがって、この技術を使用すれば ADC のダイナミック・レンジを効果的に向上させることができますが、その代わりに全体的な出力サンプリング・レートを上げたり、デジタル・ハードウェアを付加したりする必要があります。

ADC で観測されるノイズが量子化ノイズだけの場合は、平均化を行っても性能は向上しません。この場合、ディザとして知られている少量の白色ノイズを入力に加えて平均化を行うと、容易に高い分解能を得ることができます。加えるノイズは入力信号と無相関である必要があり、変換出力がランダムにトグルされるように振幅は十分に大きくなければなりません。入力に上記のディザが加えられた場合、変換されるサンプルのヒストグラムはガウス分布に従います。これらのサンプルの平均化処理はローパス・フィルタとして機能し、ノイズがフィルタリングされて、S/N比が増加します。

十分なノイズが入力に加えられ、オーバーサンプリング値が平均化された場合でも、ノイズ・フリー・ビットは理論値ほど高くならないことがあります。この制限は、コンバータの全高調波歪み(THD)が原因です。

Rev. 0 - 3/13 -

### リファレンス電圧の選択

ADC の性能において、リファレンス電圧を適切に選択することは重要な要素です。

ADuCM4050 マイクロコントローラはリファレンス・バッファを内蔵しており、このバッファは内蔵バンドギャップ・リファレンスを使用して、リファレンス電圧として 2.50V または 1.25V を生成できます。バッテリ電圧( $V_{BAT}$ )または外部電圧もリファレンスとして選択できます。これらの設定値(リファレンス電圧)は、同時には選択できません。内部バッファと  $V_{BAT}$ の両方をリファレンス・ソースとして選択すると、内部リファレス・バッファがディスエーブルになり、 $V_{BAT}$  がリファレンス電圧として選択されます。

#### 内部リファレンス電圧

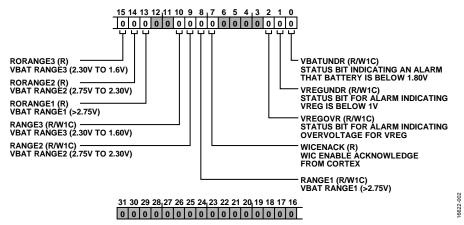

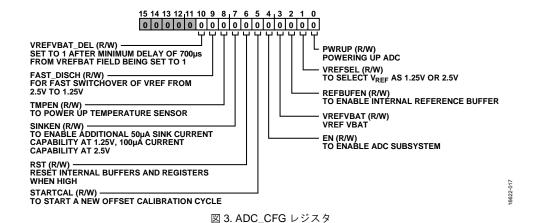

電源 モニタ・ステータス・レジスタ(図 2 に示す PMG\_PSM\_STAT)によって指定されるバッテリ範囲に基づいて、ADC 設定レジスタのリファレンス(図 3 に示す ADC\_CFG レジスタの VREFSEL ビット)として 2.5V または 1.25V を選択できます。

バッテリ電圧が 2.75V を上回る場合は、2.5V または 1.25V を内部 ADC リファレンスとして選択します。バッテリ電圧が 2.75V を下回る場合は、1.25V をリファレンスとして選択します。

#### 内部リファレンス・バッファの高速放電

ADuCM4050 MCU では、高いリファレンス電圧から低いリファレンス電圧への高速切替えが可能です。ADC 設定レジスタの高速放電ビットをイネーブルにする(ADC\_CFG レジスタのFAST\_DISCH ビットを 1 に設定する)ことによって、この切替えを実行できます。

下記の切替えを行うとき、高速放電をイネーブルにできます。

- 2.5Vから1.25V

- V<sub>BAT</sub>から 1.25V

- V<sub>BAT</sub>から 2.5V (V<sub>BAT</sub> > 2.5V の場合)

例えば、室温で 2.5V から 1.25V に切り替えると、切替え時間が 2% (45ms から 0.9ms に) 減少します。

#### 外部リファレンス電圧

外部リファレンス電圧を選択するには、ADC 設定レジスタの内部リファレンス・イネーブル・ビット(ADC\_CFG レジスタのREFBUFEN ビット)を 0 に設定することによって、内部リファレンス・バッファをディスエーブルにします。外部リファレンス電圧は、バッテリ電圧を上回ってはいけません。

外部リファレンス・ソースは、VREFP\_ADC ピンに接続する必要があります。内部バッファを使用している間は、VREFP\_ADC ピンをフロート状態にする必要があります。ADCの性能を向上させるためには、外部リファレンス・ソースをノイズ・フリーにする必要があります。

#### VBAT をリファレンス電圧として使用可能

ADuCM4050 MCU は、内部リファレンスを  $V_{BAT}$ に切り替える特別な機能を備えています。この機能により、ADC は  $V_{BAT}$ 電源を電圧リファレンスとして使用できるため、外部ソースを  $V_{REFP\_ADC}$  ピンに追加接続する必要がなく、また、電源ピンから  $V_{REFP\_ADC}$  ピンまでのボード上のワイヤ接続も必要ありません。

$V_{BAT}$  の使用時に  $VREFP\_ADC$  をイネーブルにするには、 $ADC\_CFG$  レジスタの VREFVBAT ビットを 1 に設定します。最低  $700\mu s$  待ち、その後  $VREFVBAT\_DEL$  ビットを 1 に設定します。内部リファレンスを  $V_{BAT}$ に正常に切り替えるには、少なくとも  $700\mu s$  の遅延が必要です。

#### PCB の推奨事項

GND\_VREFADC ピンの近くに 4.7μF と 0.1μF のコンデンサを並列に接続して、VREFP\_ADC ピンをデカップリングすることを推奨します。更に、このピンを ADuCM4050 の GND\_DIG、GND\_ANA、および露出パッドに接続する必要があります。これらのデカップリング部品から最大限の性能を発揮させるには、これらのコンデンサをデバイスのできるだけ近くに(理想的にはデバイスのすぐ隣に)配置する必要があります。

図 2. PMG\_PSM\_STAT レジスタ

Rev. 0 - 4/13 -

0 - 5/13 -

Rev. 0

## サンプリング・クロックの選択

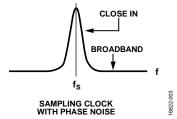

サンプリング・クロックのジッタに関する特性によって、ADC の性能が決まります。最適なサンプリング・クロックの選択は、アプリケーションの選定に基づいた重要事項です。ジッタとはクロック・エッジの位置が変動することであり、この変動によってサンプリング時間の誤差が発生します。サンプリング・エッジにこうした変動があると、サンプルの間隔が一定でなくなり、コンバータのノイズ性能が低下します。

コンバータのノイズ性能の低下を観測することによって、クロック・ジッタを推定できます。次式を用いることで、ジッタに起因する S/N 比の限界を算出します。

S/N

$$\bowtie = -20\log \left(2\pi f_{IN} t_{JITTER (RMS)}\right) dB$$

(2)

ここで、

finは入力周波数です。

t<sub>JITTER (RMS)</sub> はサンプリング・クロックの rms ジッタです。

サンプリング・レートが 154kSPS の理想的な 12 ビット ADC では、クロック・ジッタの条件は、入力周波数が 70kHz の場合に約 412ps になるのに対して、入力周波数が 300Hz の場合に約 105ns になります。

図4に示すように、クロック・ジッタを観測する従来の方法は、クロック・ジッタのスペクトルを解析することによって行われていました。図4では、サンプリング・クロックにジッタが存在するので、理想的なインパルス応答が広がって、スペクトル漏れが発生しています。エネルギーの大部分は目的の周波数の近くに分布し(近接ノイズとして知られている)、同時に広帯域にも広がっています(高帯域ノイズとして知られている)。近接位相ノイズにより、基本波信号が多数の周波数ビンに広がるため、全体的なスペクトル分解能が低下します。

図 4. 周波数領域のサンプリング・クロックとジッタ

サンプリング処理では、サンプリング・クロックとアナログ入力信号が乗算されます。この時間領域での乗算は、周波数領域での畳込みと等価です。このため、サンプリング・クロックのスペクトルが純粋なサイン波の入力信号スペクトルと畳み込まれると、合成されたスペクトルにはサンプリング・クロックのスペクトルからのスペクトル漏れも含まれています。この漏れにより、コンバータのノイズ性能が低下します。

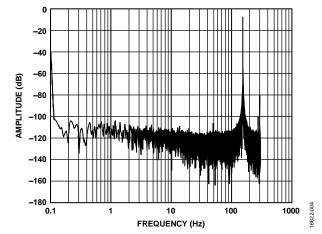

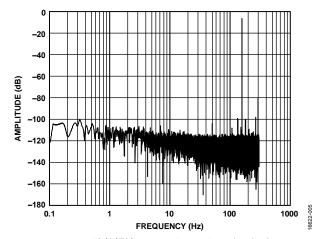

図 5 と図 6 は、クロック・ジッタが ADC サンプルのスペクトル に与える影響を示しています。16 ビットのサンプルを取得する ため、ADC はオーバーサンプリング・モードでイネーブルされ、157Hz の入力信号は 604SPS でサンプリングされています。図 5 に示すように、1 秒間に約 4ns のジッタが発生する自励発振器を

使用して入力周波数をサンプリングすると、サンプリングされた信号の S/N 比は低下します。同じセットアップにおいて、ジッタの極めて少ないクロック源(約200ps)を使用して入力信号をサンプリングすると、前の場合のスペクトルで確認できる劣化は観測されません(図6を参照)。

詳細については、AN-756 アプリケーション・ノート、サンプル 化システムに及ぼすクロック位相ノイズとジッタの影響を参照 してください。

図 5. 周波数領域で ADC クロック・ジッタが ADC サンプルに与える影響、ジッタ ≈ 4ns

図 6. 周波数領域で ADC クロック・ジッタが ADC サンプルに与える影響、ジッタ ≈ 200ps

#### サンプリング・クロック源の選択

この MCU ではサンプリング・クロック源として、内部の26MHz発振器、または外部の26MHz水晶発振器を選択できます。詳細については、ADuCM4050パワー・マネージメント搭載の超低消費電力ARM Cortex-M4F MCUハードウェア・リファレンスを参照してください。

Rev. 0 - 6/13 -

### 電力の最適化

ADC が内蔵された MCU を使用するシステムや、多くの外部センサーとインターフェースするシステムを検討する場合、ADuCM4050 MCUの低消費電力機能を使用すると、ADC サブシステムが被る全体的なノイズを低減できるため、ADC の性能を向上させることができます。また、低消費電力オプションを有効にすると、MCU の消費電力を最適化することもできます。リファレンス・バッファの低消費電力モード、Flexi モード、および高電力降圧の各セクションでは、ADuCM4050 マイクロコントローラに備えられている様々な機能について説明します。

#### リファレンス・バッファの低消費電力モード

ADCのサンプリング・レートが 100kSPS 未満のとき、内部リファレンス・バッファは、低消費電力モードで動作できます。低消費電力モードでは、バッファの電流消費が通常動作モードよりも約 100μA 少なくなります。低消費電力モード・レジスタ(ADC\_CFG1 レジスタ)にあるリファレンス・バッファのRBUFLP ビット・フィールドを 1 に設定することによって、低消費電力モードを有効にします。

#### Flexi モード

ADC が複数のサンプルを変換している間、DMA をイネーブルにしてサンプルを ADC の出力バッファからメモリに転送します。この間、ARM Cortex-M4F コアを Flexi モードにしたり、その他の機能のために使用したりでき、全体的な消費電力を減らすことができます。

Flexi モードでは、コアがスリープしている間でも、ペリフェラルと DMAにはクロックが供給されます。このため、ペリフェラルとメモリの間だけでなく、あるメモリ位置から別のメモリ位置にも DMA 転送を続行できます。 ADC が変換している間、MCU におけるこの低消費電力モードでもノイズ・フリー環境を確保できます。

#### 高電力降圧

高電力降圧(HP降圧)は、 $V_{BAT}$ レベルに基づいてデバイス全体の消費電流を低減できる容量性の降圧コンバータです。バッテリ電圧が 2.8V を上回る場合、デバイスの消費電流は約 50%減少します。

Rev. 0 - 7/13 -

## オーバーサンプリングと平均化技術の実装

#### プログラミング・フロー

以下の手順において、1 つのチャンネルで複数の変換を平均化 する方法について説明します。

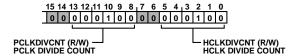

次式に規定されるように、クロック・コントロール・レジスタ (CLKG\_CLK\_CTL1 レジスタの ACLKDIVCNT ビット)でADC クロック分周器を設定し、ADC クロック (ACLK)を規定します。

$$ACLK = \frac{RootClock}{ACLKDIV}$$

(3)

ここで、 $Root\ Clock\$ はルート・クロック周波数(26MHz)であり、高周波発振器、高周波水晶発振器、フェーズ・ロック・ループ(PLL)、または外部の汎用入出力(GPIO)クロック源から供給できます。デフォルトでは、ルート・クロックは HFOSC です。必ず  $ACLK \leq PCLK$  かつ  $ACLK \leq HCLK$  となるようにしてください。ACLK に設定する最高周波数は、26MHz でなければなりません。

31 30 29 28,27 26 25 24,23 22 21 20,19 18 17 16

ACLKDIVCNT (R/W) - ACLK DIVIDE COUNT

図 7. CLKG\_CLK\_CTL1 レジスタ

6622

ADC のサンプリング・レートは、ACLK に基づいて内部で計算されます。ここで、アクイジション・フェーズではADC\_CNV\_TIME レジスタの SAMPTIME ビット + 1ACLK サイクルかかり、変換フェーズでは逐次比較によって13ACLK サイクルかかります。変換フェーズは、アクイジション・フェーズの終了時に開始されます。次式を使用して、サンプリング・レートを計算します。

ADC Sampling Rate =

$$\frac{Root \, Clock \div ACLKDIV}{\left(\left(14 + Sampling \, Time\right) \times Oversampling \, Factor\right)} \tag{4}$$

オーバーサンプリング係数によって、オーバーサンプリングおよび平均化されるサンプル数が決まります。オーバーサンプリング係数として、1~256の値が設定できます。

ADC のサンプル間に遅延時間を設ける場合は、式 5 を使用してサンプリング・レートを計算します。

Delay Time は、1未満の値にすることができないことに注意してください。

ADC 設定レジスタのパワーアップ ADC ビット (ADC\_CFG レジスタの PWRUP ビット)を1に設定して、ADCをパワーアップします(図3を参照)。

3. ADC パワーアップ時間レジスタの待機ビット・フィールド (ADC\_PWRUP レジスタの WAIT ビット・フィールド) に、526を CLKG\_CLK\_CTL1 レジスタの PCLKDIVCNT ビットで割った値を設定します。

図 8.ADC PWRUP レジスタ

ADC を正常に動作させるには、パワーアップ待機時間が必要です。CLKG\_CLK\_CTL1 レジスタの PCLKDIVCNT ビットが 1 の場合、ADC に必要な最大パワーアップ待機時間は526 クロック・サイクルです。

- 4. ADC\_CFG レジスタの VREFSEL ビットを使用して、内部の 1.25V または 2.5V のリファレンス・バッファをリファレンス電圧として選択します。

- ADC\_CFG レジスタの REFBUFEN ビットを 1 に設定することによって、内部リファレンス・バッファをイネーブルにします。

- 6. ADC\_CFG1 レジスタの RBUFLP ビットを 1 に設定すること によって、リファレンス・バッファにおける低消費電力モードを有効にします。

図 9. ADC CFG1 レジスタ図

- 7. ADC\_CFG レジスタの EN ビットを 1 に設定することによって、ADC サブシステムをイネーブルにします。

- 8. 3.5ms 以上待機します。この待機時間は、内部リファレンス・バッファが設定されたリファレンス・バッファ電圧レベル (1.25Vまたは2.5V) に達するために必要です。3.5ms 待機するために汎用 (GP) タイマーの1つを使用することができます。この待機期間中、デバイスを Flexi モードにすると、システム電力を節約でき、また、GP タイマーの割込みによってデバイスはウェイクアップできます。

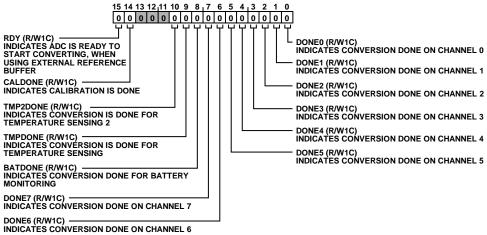

- 9. ADC ステータス・レジスタ上のビット(ADC\_STAT レジス タの RDY ビット)で ADC が変換を開始するための準備状 態を確認します。このビットが 1 の場合、ADC は変換を開 始する準備が整っています。

- 10. このビットに 1 を書き込むと、ADC\_STAT レジスタの RDY ビット(図 11 を参照)をクリアできます。

- ADC\_CFG レジスタの STARTCAL ビットを 1 に設定して、 キャリブレーション・サイクルを開始します(図 3 を参 照)。

- 12. ADC\_STAT レジスタの CALDONE ビットを確認します。このビットがアサートされている場合は、このビットに 1 を書き込んでクリアします(図 11 を参照)。

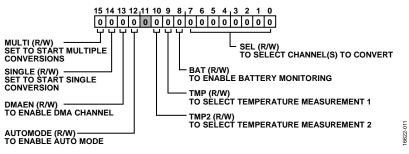

- 13. ADC変換設定レジスタ (ADC\_CNV\_CFG レジスタ) の SEL ビット (図 12 を参照) を設定して、変換を行うチャンネル を選択します。例えば、これらのビットに 1 を書き込むと、 チャンネル 0 が選択されます。

ADC Sampling Rate =  $\frac{Root\ Clock \div ACLKDIV}{\left(\left(14 + Sampling\ Time\right) \times Oversampling\ Factor\right) + \left(Delay\ Time + 2\right)}$

(5)

Rev. 0 - 8/13 -

図 11. ADC\_STAT レジスタ図

図 12. ADC\_CVN\_CFG レジスタ図

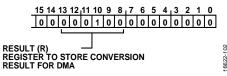

図 13. ADC\_DMA\_OUT レジスタ図

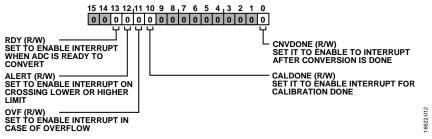

- 14. 変換が完了したとき、ADC 割込みイネーブル・レジスタ (ADC\_IRQ\_EN レジスタ) の CNVDONE ビットを 1 に設定し、割込み機能を有効にします(図 14 を参照)。

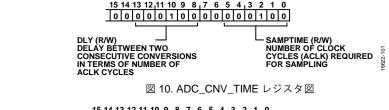

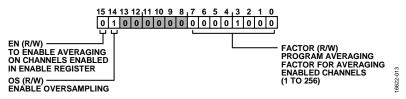

- 15. ADC 平均化設定レジスタ (ADC\_AVG\_CFG) の OS ビット と EN ビットを 1 に設定して、オーバーサンプリングと平均 化を有効にします (図 15 を参照)。

- 16. ADC 平均化設定レジスタ(ADC\_AVG\_CFG)の FACTOR ビット・フィールドでオーバーサンプリングと平均化の係数 (M) を設定します。表 1 は、特定の分解能が必要な場合にプログラムしなければならない要素の一覧表です。

- 17. ADC\_CNV\_CFG レジスタの SINGLE ビットを 1 に設定して、 シングル変換を開始します(図 12 を参照)。

- 18. ADC\_IRQ\_EN レジスタの CNVDONE ビットが 1 に設定されている場合は、変換完了割込みが発生します。変換完了割込みが発生した場合は、対応するチャンネルの ADC\_STAT レジスタの変換完了ビット (ADC\_STAT レジスタの DONEO ビットなど) を確認します。

6622-010

- 19. 対応するチャンネルの変換結果レジスタ(ADC\_CH0\_OUT など)から変換出力を読み出します。

- ADC\_STAT レジスタの変換完了ビットに 1 を書き込んでクリアします(例えば、DONE0 ビットに 1 を書き込む)。

- 21. オーバーサンプリングおよび平均化された複数のサンプルを取得するには、手順1~15を繰り返します。

Rev. 0 – 9/13 –

- 22. 以下のように DMA の設定を行います。

- 変換数が 10 の場合は、DMA カウント = 9 (DMA カウント = 変換数 1) になります。

- ソース・アドレスは、ADC\_DMA\_OUT レジスタのア ドレスです(図13を参照)。

- ソース・サイズはハーフ・ワードです。

- DMAのディスティネーション・アドレスをSRAMメモリ・ロケーション・アドレスに設定して、変換結果を保存します。

- ディスティネーション・アドレス内に必要なインクリメントをプログラムします。

- 23. ADC 変換設定レジスタ(ADC\_CNV\_CFG レジスタ)の DMAEN ビットを 1 に設定して、DMA をイネーブルにします。

- 24. ADC 変換設定レジスタ(ADC\_CNV\_CFG レジスタ)の MULTI ビットを1 に設定して、変換を開始します。

- 25. DMA\_DONE 割込みが発生したときに、MULTI ビットをクリアして、割込みサービス・ルーチンでこの後の変換を無効にします(図 16 を参照)。

図 14. ADC IRQ EN レジスタ図

図 15. ADC\_AVG\_CFG レジスタ図

表 1. 分解能を向上させるためのオーバーサンプリングと平均化の係数

| Resolution Required | Oversampling and Averaging Factor (M) | Number of Samples Used for Averaging |

|---------------------|---------------------------------------|--------------------------------------|

| 13-Bit              | 0x02                                  | 4                                    |

| 14-Bit              | 0x08                                  | 16                                   |

| 15-Bit              | 0x20                                  | 64                                   |

| 16-Bit              | 0x80                                  | 256                                  |

Rev. 0 - 10/13 -

## アプリケーション例の概要

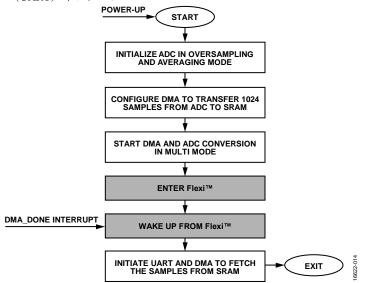

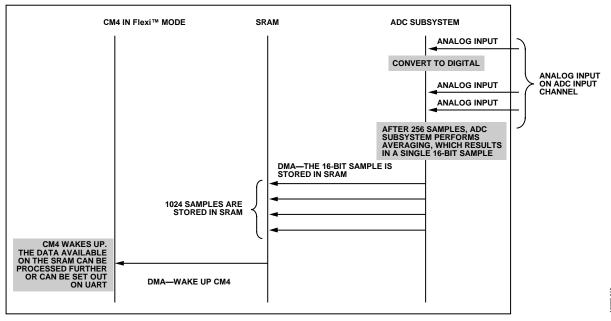

このセクションでは、電力最適化モードで ADC のオーバーサンプリングと平均化を実行するアプリケーション・シーケンスについて説明します。

この例では、ADC はオーバーサンプリングと平均化モードでイネーブルされています。オーバーサンプリング係数 (M) を 256 に設定して、16 ビットのサンプルを取得します。DMAには、16 ビットのサンプル 1024 個を取得して SRAM のロケーションに保存するように設定します。その後、サンプルはユニバーサル非同期レシーバー/トランスミッタ (UART) インターフェース

によって取得されます。ADC 変換と DMA 転送の間、コアは Flexi モードになります。

図 16 に、マルチ変換モードでのオーバーサンプリングのアプリケーション・フローを示します。

図 17 にアプリケーション・シーケンスを示します。

図 16. マルチ変換モードでのオーバーサンプリングのアプリケーション・フロー

図 17. アプリケーション・シーケンス

Rev. 0 - 11/13 -

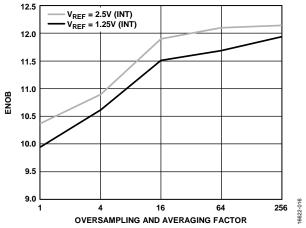

### 結果

図 18 はオーバーサンプリングと平均化の係数に対する有効ビット数 (ENOB) をグラフ化したもので、ADC 性能の測定値を示しています。この ADC は理想的ではないため、ENOB は式 1 の S/N比に基づいて計算しています。S/N比は、周波数が 157Hz のサイン波信号を信号発生器から ADC チャンネル 0 に入力することによって得ています。

オーバーサンプリング係数 (M) ごとにスループットが常に 604SPSになるように、ADCのクロック周波数を調整しています。

図 18. オーバーサンプリングと平均化の係数に対する ENOB

Rev. 0 - 12/13 -

## 参考文献

Brannon, Brad. AN-756 アプリケーション・ノート: サンプル化システムに及ぼすクロック位相ノイズとジッタの影響、Analog Devices, 2004.

Kester, Walt. 『ADC の入力ノイズ:良いノイズと悪いノイズと厄介なノイズ 良いノイズとはノイズ・ゼロのこと?』 Analog Dialogue Vol. 40, February 2006.

Kester, Walt. 2005. The Data Conversion Handbook. Analog Devices.

Reeder, Rob, Wayne Green, and Robert Shillito. 『A/D コンバータのクロックの最適化 試験工学的な観点』 Analog Dialogue Vol. 42, February 2008.

Rev. 0 - 13/13 -