# アプリケーション・ノート

## コンポーネント・プロセッサの非標準ビデオ・フォーマット 著者: Witold Kaczurba

#### 概要

このアプリケーション・ノートの目的は、PRIM\_MODE[3:0]と VID\_STD[3:0]でカバーされていない HD、PS、グラフィックス標準を処理するようにコンポーネント・プロセッサ(CP)コアを設定する際の支援を行うことです。例えば、720p/50 Hz や 1080i/50 Hz のような、VID\_STD[3:0]ではサポートされていないその他の SMPTE HD 標準をサポートするように CP を設定することができます。MAC 13 や MAC 16 のようなグラフィックス標準は、CP を正しく設定すればサポートできる RGB 非標準グラフィックス・フォーマットの例です。

ADV7401/ADV7403 の標準動作では、PRIM\_MODE[3:0]コントロールと VID\_STD[3:0]コントロールを使って、一般的な HD、PS、SD、RGB のグラフィックス・フォーマットを処理するように CP を設定します(プライマリ・モードとビデオ標準の選択の詳細 については、ADV7401/ADV7403 ハードウェア・マニュアル「Integrated Multiformat SDTV/HDTV Video Decoder and RGB Graphics Digitizer」をご覧ください。この資料にはサポートしているモードが記載してあります)。

このアプリケーション・ノートでは、非標準ビデオ・フォーマットを処理するように CP を設定する方法について次のステップで説明します。

- 1. 該当する PRIM MODE[3:0]/VID STD[3:0]の選択

- 2. ラッチ・クロックの設定

- 3. PLL DIV RATIO[11:0]の設定

- 4. FR LL[10:0]の設定

これらの各ステップは、それぞれ 非標準フォーマットに対する PRIM\_MODE[3:0]/VID\_STD[3:0]の選、ラッチ・クロック、ピク セル・クロックの発生、フリー・ラン・モードの設定の各セク ションで説明します。実施例のセクションには、例を示します。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語データシートは REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2009 Analog Devices, Inc. All rights reserved.

# 目次

| 概要                                              | 1 |

|-------------------------------------------------|---|

| <b>CP</b> コアの設定                                 | 3 |

| 非標準フォーマットに対する<br>PRIM_MODE[3:0]/VID_STD[3:0]の選択 | 3 |

| ラッチ・クロック                                        | 3 |

| ピクセル・クロックの発生                                    | 3 |

| フリー・ラン・モードの設定                                   | 4 |

| 宇協例                                             | 5 |

|    | 例 1: 720P、50 HZ                                      | 5 |

|----|------------------------------------------------------|---|

|    | 例 2: MAC 16                                          | 6 |

|    | 例 3: SXGA、75 HZ<br>(サブサンプル・ピクセル・クロック= 108 MHZ)       | 7 |

|    | 例 4: VESA 1360×768、60.015 HZ (ピクセル・クロック= 85.<br>MHZ) |   |

| 12 | 台書車佰                                                 | C |

## CPコアの設定

### 非標準フォーマットに対する PRIM\_MODE[3:0]/VID\_STD[3:0]の選択

PRIM\_MODE[3:0]とVID\_STD[3:0]を最も似ている標準に設定することにより、非標準動作を行うようにCPを設定することができます。表 2 に、非標準フォーマット用にPRIM\_MODE[3:0]とVID\_STD[3:0]を設定する例を示します。解像度とピクセル・クロック周波数が最も一致するように設定することが基本です。

#### ラッチ・クロック

ラッチ・クロックは、サンプリングを制御するADCの内部パラメータです。推奨ラッチ・クロック設定値は、表 1 に従って設定することができます。

表 1.ラッチ・クロックの設定値

| LATCH_CLK[3:0] | Pixel Clock (MHz) |

|----------------|-------------------|

| 0001           | 13.5 to 54        |

| 0010           | 55 to 100         |

| 0101           | 108               |

| 0110           | 135               |

#### ピクセル・クロックの発生

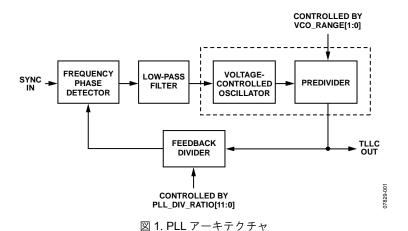

ADV7401/ADV7403 では、PLLを使って着信Hsyncからピクセル・クロック(TLLC)を発生しています。非標準ビデオ・フォーマットの場合、PLLを手動で設定して任意周波数のピクセル・クロックを発生することができます。これは、PLL帰還分周器ブロックを設定することにより行います(図 1 参照)。

先ず、 $PLL_DIV_MAN_EN$  に 1 を設定して、PLL ブロックの手動設定をイネーブルする必要があります。次に、非標準モードに対して所望ピクセル・クロックを得るように $PLL_DIV_RATIO[11:0]$ を設定します。

PLL\_DIV\_RATIO[11:0]のこの値を計算するときは、2 つの方法を使用することができます。非標準フォーマットについての情報に基づいてこれらの方法の1つを選択する必要があります。

方法 1 は、ピクセル・クロック周波数を着信 Hsync 周波数で除算する式 1 で表されます。この式は、PLL で逓倍を行って着信Hsync からピクセル・クロックを発生することを示しています。

$$PLL\_DIV\_RATIO[11:0] = \frac{f_{PIXELCLOCK}}{f_{HSYNC}} \tag{1}$$

方法 2 は、PLL\_DIV\_RATIO[11:0]がライン周期あたりの輝度信号サンプル・ピクセル数に常に一致するという規則に基づいています。

表 2.非標準フォーマットに対する PRIM MODE[3:0]/VID STD[3:0]設定の例

| N           | onstandard Vide | o Format          | ADV7401/ADV7403 CP Default Configurations |              |            |             |                   |

|-------------|-----------------|-------------------|-------------------------------------------|--------------|------------|-------------|-------------------|

| Format      | Resolution      | Pixel Clock (MHz) | PRIM_MODE[3:0]                            | VID_STD[3:0] | Format     | Resolution  | Pixel Clock (MHz) |

| VGA 70      | 640 × 480       | 28.561            | 0010                                      | 1001         | VGA 72     | 640 × 480   | 31.515            |

| WVGA60      | 852 × 480       | 34.000            | 0010                                      | 0000         | SVGA 56    | 800 × 600   | 36.00             |

| MAC 13      | 640 × 480       | 30.240            | 0010                                      | 1001         | VGA 72     | 640 × 480   | 31.515            |

| MAC 21      | 1152 × 870      | 100.00            | 0010                                      | 1111         | XGA 85     | 1024 × 768  | 94.5              |

| 1080i/50 Hz | 1920 × 1080     | 74.25             | 0001                                      | 1100         | HD 1080/60 | 1920 × 1080 | 74.25             |

Rev. 0 - 3/9 -

#### VCO\_RANGE[1:0]とPLL\_QPUMP[2:0]の手動設定

VCO\_RANGE[1:0] と PLL\_QPUMP[2:0]は、 PLLが安定なTLLCを発生するように設定する必要があります。 VCO範囲とPLLチャージ・ポンプの推奨設定値は、表 3 と 表 4 に従って設定することができます。

表 3.非標準ビデオ・フォーマット VCO 範囲の設定値

| VCO_RANGE[1:0] | Pixel Clock (MHz) |

|----------------|-------------------|

| 00             | 13.5 to 29        |

| 01             | 30 to 44          |

| 10             | 45 to 89          |

| 11             | 90 to 140         |

表 4.非標準ビデオ・フォーマット PLL の設定値

| Charge Pump Current, PLL_QPUMP[2:0] | Pixel Clock (MHz) |

|-------------------------------------|-------------------|

| 001                                 | <22               |

| 011                                 | ≥22               |

| 100                                 | ≥31               |

| 101                                 | ≥42               |

| 011                                 | ≥45               |

| 100                                 | ≥48               |

| 101                                 | ≥58               |

| 100                                 | ≥90               |

| 101                                 | ≥95               |

| 110                                 | ≥136              |

| 111                                 | ≥205              |

VCO\_RANGE[1:0]の設定値は、VCO\_RANGE\_MAN が 1 に設定された場合にのみアクティブになります。該当する VCO 範囲は、PRIM\_MODE[3:0]と VID\_STD[3:0]によりサポートされるすべての標準に対して自動的に選択されます。

#### 入力ビデオのサブサンプリング

PLL 分周比を調節することにより入力ビデオをサブサンプルすることができます。この機能を使うと、水平解像度(ラインあたりの輝度信号サンプル数)は低くなるが、垂直解像度(フレームあたりのライン数)は同じである標準フォーマットを CP に処理させることができます。折り返し歪みを防止するために、着信ビデオ信号の帯域制限に注意する必要があります。

また、サブサンプリング機能を使うと、CP は ADV7401/ADV7403 の仕様より高い解像度とピクセル・クロックを持つビデオ・フォーマットも処理することができます。例え

ば、60~Hz の UXGA  $(1600 \times 1200)$ のピクセル・クロックは 162~MHz ですが、これは ADC の最大サンプル・レートより高くなります。PLL を使って着信 Hsync から 108~MHz クロックを発生することにより、CP で 1200~ライン解像度を処理することができます。これより低いピクセル・クロックでは水平解像度が低くなり、トータル・ラインあたりの輝度信号サンプル数(S/TL) がフル帯域幅信号での 1600~から 1440~ 低下します。

#### フリー・ラン・モードの設定

ADV7401/ADV7403 のフリー・ラン機能は、CP コアがアンロック状態になったときブルー・スクリーン出力を表示できるようにします。CP では、ライン長の測定値を使ってフリー・ラン状態になるタイミングを決定しています。CP は VID\_STD[3:0]を使って予測ライン長を決定します。CP を手動で設定して、非標準フォーマットに対する異なるライン長を予測させる必要があります。

FR\_LL (フリー・ラン・ライン長)パラメータは、ビデオ・フォーマットの理論ライン長内での水晶クロック・サイクル数です。 CP はこのパラメータを使って、入力フォーマットが変わった場合または入力がなくなった場合に、ライン長が変化したタイミングを検出します。このパラメータは通常、VID\_STD[3:0]とPRIM MODE[3:0]からデコードされます。

測定ライン長が 32 クロック・サイクル(このスレッショールドは CP\_F\_RUN\_TH[2:0]に設定)だけ FR\_LL[11:0]から異なると、CPコアはアンロック状態になり、フリー・ラン・モードに入ります。 CP を非標準ビデオ用に設定するときは、FR\_LL[11:0]を手動で設定する必要があります。これにより、CP は該当する VID\_STD[3:0]に対応するデフォルト・ライン長を無視することができるようになります。

FR\_LL[11:0]の手動パラメータを計算するときは、ライン周期を27 MHz クロック周期(27 MHz 水晶の場合)または 28.6363 MHz クロック周期(28.6363 MHz 水晶の場合)で除算します(式 2 参照)。この式の分子は Hysnc 周期から直接計算することができます。あるいは、ラインあたりの輝度信号ピクセル周期合計数を使って、これにピクセル・クロック周期を乗算して計算することができます。

$$FR\_LL[11:0] = \frac{t_{LINE \, PERIOD}}{t_{XTAL \, MHZ}} \tag{2}$$

ここで、 $t_{XTAL\_MHZ} = t_{27 \ MHZ}$  (27 MHz 水晶の場合)または  $t_{XTAL\_MHZ} = t_{28.6363MHZ}$  (28.6363 MHz 水晶の場合)。

Rev. 0 — 4/9 —

# 実施例

#### 例 1: 720p、50 Hz

1. PRIM\_MODE[3:0]と VID\_STD[3:0]を最も似ている標準に設定します。

PRIM\_MODE[3:0] = 0001b VID\_STD[3:0] = 1010b

この設定は、最も似ている非標準フォーマットのピクセル・クロック周波数と解像度に基づきます。

2. ラッチ・クロックを設定します。74.25 MHzについては表1 を参照してください。

$LATCH\_CLK[3:0] = 0010b$

3. PLL\_DIV\_RATIO[11:0]を設定します。この標準のHsync周波数についての情報がないため式1を使用できません。トータル・ラインあたりの輝度信号サンプル周期数は1980であるため、方法2を使ってPLL\_DIV\_RATIO[11:0]に1980を設

##CP 720p YPrPb 1X1##

:720p/50 YPrPb In 1X1 30Bit 444 Out:

42 05 01 ; PRIM\_MODE = 0001b COMP

42 06 0A ; VID\_STD = 1010b for 720P 1x1

42 3A 20 ; set latch clock settings to 010b

42 3B 80 ; External Bias Enable

42 3C 5D ; PLL\_QPUMP to 101b

42 6B C2; 30-bit 4:4:4 output

42 87 E7 ; Man set PLL\_DIV\_RATIO 1980

42 88 BC ; Man set PLL\_DIV\_RATIO 1980

42~8A~DO ; VCO Range to 10b

42 8F 02 ; Set  $FR_LL = 720$

42 90 D0 ; Set  $FR_LL = 720$

End

定します(ピクセル・クロックの発生のセクション参照)。

PLL\_DIV\_MAN\_EN = 1b

$PLL_DIV_RATIO[11:0] = 1980_{dec} = 0x7BC$

PLL\_QPUMP[2:0]に 101bを、VCO\_RANGE[1:0]に 10bを、それぞれ設定します(表 3 と 表 4 を参照)。

4. 式 2 を使って FR\_LL[11:0]を計算します。 t<sub>LINE PERIOD</sub> = (1980 × 1/74.25 MHz) = 26.667 μs

$t_{27 \text{ MHz}} = 37.037 \text{ ns}$ FR\_LL[11:0] =  $720_{dec} = 0x2D0$

これらの新しいレジスタ設定値と標準設定値を組み合わせると、ADV7401/ADV7403 (デバイス・アドレス 0x42) 720p/50 Hz に対する次の  $\rm I^2C$  書込みが得られます。

表 5.ビデオ信号タイミング—720p、50 Hz

| System       | Luma Samples per | Active Lines per Frame | Frame Rate | Sampling        | Luma Sample Periods per | Total Lines per |

|--------------|------------------|------------------------|------------|-----------------|-------------------------|-----------------|

| Nomenclature | Active Line      |                        | (Hz)       | Frequency (MHz) | Total Line              | Frame           |

| 1280 × 720   | 1280             | 720                    | 50         | 74.25           | 1980                    | 750             |

Rev. 0 -5/9 —

## AN-0978

#### 例 2: MAC 16

1. PRIM\_MODE[3:0]と VID\_STD[3:0]を最も似ている標準に設定します。

PRIM\_MODE[3:0] = 0010b VID STD[3:0] = 0100b

この設定は、最も似ている非標準フォーマットのピクセル・クロック周波数と解像度に基づきます。

ラッチ・クロックを設定します。55,000 MHzについては表1 を参照してください。

LATCH CLK[3:0] = 0010

3. PLL\_DIV\_RATIO[11:0]を設定します。式1を使い、Hsync周 波数=49.107 kHzとピクセル・クロック=55.000 MHzから、 次が得られます。 PLL\_DIV\_MAN\_EN = 1b

$PLL_DIV_RATIO[11:0] = 1120_{dec} = 0x460$

PLL\_QPUMP[2:0]に 100bを、VCO\_RANGE[1:0]に 10bを、それぞれ設定します(表 3 と 表 4 を参照)。

4. 式2を使ってFR\_LL[11:0]を計算します。

$t_{LINE\ PERIOD} = (1/49.107\ kHz) = 20.36\ \mu s$

$t_{27 \text{ MHz}} = 37.037 \text{ ns}$

$FR_LL[11:0] = 550_{dec} = 0x226$

これらの新しいレジスタ設定値と標準設定値を組み合わせると、ADV7401/ADV7403 (デバイス・アドレス 0x42) MAC 16 に対する次の  $1^2$ C 書込みが得られます。

##CP RGB Graphics Special Modes##

:832 x 624 \_@ 75.087Hz MAC 16 PIXEL CLOCK 55.00 MHz:

42 04 75; enable max drive strength

42 05 02 ; PRIM\_MODE = 0010b for GR

42 06 04 ; VID\_STD = 0100b for 800x600 @ 85; closest available standard.

42 OE OF ; enable max drive strength Clock & Syncs

42 3A 20; set latch clock settings to 010b

42 3B 80 ; External Bias Enable

42 3C 5C; PLL\_QPUMP to 100b

42 6A 00 ; DLL Phase Adjust

42 6B 82; Enable DE output, swap Pr& Pb

42 73 90 ; Set man\_gain

42 7B 1C ; TURN OFF EAV & SAV CODES

42 87 E4 ; PLL\_Div\_Ratio to 1120

42 88 60 ; PLL\_Div\_Ratio to 1120

42 8A D0 ; VCO Range to 10b

$42 \ 8F \ 02 \ ; \ FR\_LL = 550$

$42\ 90\ 26$ ; FR\_LL = 550

End

#### 表 6.ビデオ信号タイミング-MAC 16

| System       | Luma Samples per | Active Lines | Frame Rate (Hz) | Sampling        | Luma Sample Periods | Total Lines |

|--------------|------------------|--------------|-----------------|-----------------|---------------------|-------------|

| Nomenclature | Active Line      | per Frame    |                 | Frequency (MHz) | per Total Line      | per Frame   |

| 832 × 624    | 832              | 624          | 75.087          | 55.000          | 1120                | 654         |

Rev. 0 -6/9 —

## AN-0978

PLL\_QPUMP[2:0]に 101bを、VCO\_RANGE[1:0]に 11bを、そ

サブサンプル・ビデオ・データでは 1350 S/TL、標準フォ ーマットでは 1688 S/TLであることに注意してください。

これらの新しいレジスタ設定値と標準設定値を組み合わせると、 ADV7401/ADV7403 (デバイス・アドレス 0x42) 75 Hz の SXGA

れぞれ設定します(表3と表4を参照)。

式 2 を使って FR LL[11:0]を計算します。

$t_{LINE\ PERIOD} = (1/79.976\ kHz) = 12.503\ \mu s$

$FR_LL[11:0] = 338_{dec} = 0x152$

に対する次の I<sup>2</sup>C 書込みが得られます。

$t_{27 \text{ MHz}} = 37.037 \text{ ns}$

## 例 3: SXGA、75 Hz (サブサンプル・ピクセル・ クロック= 108 MHz)

PRIM\_MODE[3:0]と VID\_STD[3:0]を 75 Hz の SXGA 標準に 設定します。

PRIM MODE[3:0] = 0010b $VID_STD[3:0] = 0101b$

この設定は、最も似ている非標準フォーマットのピクセ ル・クロック周波数と解像度に基づきます。

ラッチ・クロックを設定します。108 MHz (サブサンプリン グ・ピクセル・クロック)については表1を参照してくだ さい。

LATCH CLK[3:0] = 0010b

標準フォーマット(135 MHz)では、ラッチ・クロックは LATCH\_CLK[3:0] = 0110 であることに注意してください。

PLL\_DIV\_RATIO[11:0]を設定して、必要とされるサブサン プリング・ピクセル・クロックを発生させます。式1を使 い、Hsync周波数=79.976 kHzとピクセル・クロック=108 MHzから、次が得られます。

PLL DIV MAN EN = 1b

$PLL_DIV_RATIO[11:0] = 1351_{dec} = 0x547$

##CP RGB Graphics MEI Special Modes##

:1280x1024 \_@ 75.025Hz SubSamp. 108MHz Out through DAC:

42 05 02 ; PRIM\_MODE = 0010b for GR

42 06 05 ; VID\_STD = 0101b for 1280x1024 @ 75

42 37 00 ; Invert PCLK

42 3A 21; set latch clock settings to 010b, Power Down ADC3

42 3B 80 ; Enable External Bias

42 3C 5D; PLL\_QPUMP to 101b

42 6A 00 ; DLL Phase Adjust

42 6B C2; sets CPOP\_SEL to 0010b 30 Bit Output Pr/Pb pins swapped.

42 73 90 ; Set man\_gain

42 7B 1C ; TURN OFF EAV & SAV CODES

42 87 E5 ; PLL\_Div\_Ratio to 1350

42 88 47 ; PLL\_Div\_Ratio to 1350

42 8A F0; VCO Range to 11b

42 8F 01 ; FR\_LL = 338

$42\ 90\ 52$ ; FR\_LL = 338

42 B3 FE ; STDI Tweak

42 F4 3F; Max Drive Strength

## 表 7.ビデオ信号タイミング—SXGA、75 Hz (サブサンプル)

| System<br>Nomenclature | Luma Samples per<br>Active Line | Active Lines<br>per Frame | Frame Rate (Hz) | Sampling Frequency<br>(MHz) | Luma Sample Periods<br>per Total Line | Horizontal<br>Frequency<br>(kHz) |

|------------------------|---------------------------------|---------------------------|-----------------|-----------------------------|---------------------------------------|----------------------------------|

| 1280 × 1024            | 1280                            | 1024                      | 75              | 135 (108 <sup>1</sup> )     | 1688 (1350)                           | 79.976                           |

<sup>&</sup>lt;sup>1</sup>サブサンプルされたビデオ・データ・フォーマット。

Rev. 0 -7/9 -

## AN-0978

## 例 4: VESA 1360 × 768、60.015 Hz (ピクセル・ クロック= 85.5 MHz)

PRIM\_MODE[3:0]と VID\_STD[3:0]を 75 Hz の 1024 × 768 標準に設定します。

PRIM\_MODE[3:0] = 0010b VID\_STD[3:0] = 1110b

この設定は、最も似ている非標準フォーマットのピクセル・クロック周波数と解像度に基づきます。

2. ラッチ・クロックを設定します。85.5 MHzについては表1を参照してください。

LATCH\_CLK[3:0] = 0010b B PLL DIV RATIO[11:0]を設定し

3. PLL\_DIV\_RATIO[11:0]を設定して、必要とされるサンプリング・ピクセル・クロックを発生させます。式1を使い、

Hsync周波数=47.712 kHzとピクセル・クロック=85.5 MHzから、次が得られます。

PLL DIV MAN EN = 1b

$PLL_DIV_RATIO[11:0] = 1792_{dec} = 0x700$

PLL\_QPUMP[2:0]に 101bを、VCO\_RANGE[1:0]に 10bを、それぞれ設定します(表 3 と 表 4 を参照)。

4. 式2を使って FR LL[11:0]を計算します。

$t_{LINE\ PERIOD} = (1/47.712\ kHz) = 20.959\ \mu s$

$t_{27 \text{ MHz}} = 37.037 \text{ ns}$

$FR_LL[11:0] = 566_{dec} = 0x236$

これらの新しいレジスタ設定値と標準設定値を組み合わせると、ADV7401/ADV7403 (デバイス・アドレス 0x42) 60 Hz の  $1360 \times 768$  に対する次の  $I^2$ C 書込みが得られます。

##CP RGB Graphics Special Modes##

:1360×768 \_@ 60.015Hz, 85.500MHz Out through DAC:

42 05 02 ; PRIM\_MODE = 0010b for GR

42 06 0E; VID\_STD = 1110b for 1024x768 @ 75

42 3A 21; set latch clock settings to 010b, Power Down ADC3

42 3B 80 ; Enable External Bias

42 3C 5D ; PLL\_QPUMP to 101b

42 6A 00 ; DLL Phase Adjust

42 6B 82; Enable DE output, swap Pr Pb

42 73 90 ; Set man\_gain

42 7B 14; AV CODES DISABLE, TURN OFF EAV and SAV CODES

42 87 E7 ; PLL\_Div\_Ratio to 1792

42 88 00 ; PLL\_Div\_Ratio to 1792

42~8A~E0 ; VCO Range to 10b

$42 \ 8F \ 02 \ ; FR\_LL = 566$

42 90 36 ; FR\_LL = 566

42 F4 3F; Max Drive Strength

End

#### 表 8.ビデオ信号タイミング—1360 × 768、50 Hz

| System       | Luma Samples per | Active Lines | Frame Rate (Hz) | Sampling        | Luma Sample Periods | Horizontal      |

|--------------|------------------|--------------|-----------------|-----------------|---------------------|-----------------|

| Nomenclature | Active Line      | per Frame    |                 | Frequency (MHz) | per Total Line      | Frequency (kHz) |

| 1360 × 768   | 1360             | 768          | 60.015          | 85.5            | 1792                | 47.712          |

Rev. 0 -8/9 -

# 考慮事項

DAC 出力の設定中に  $AV\_CODE\_EN[1]$ をイネーブルすると、出力に垂直ラインが表示されることがあります。これを回避するためには、DAC 出力を使う場合、 $AV\_CODE\_EN[1]$ をターンオフする必要があります。

PRIM\_MODE[3:0] の 指定 に 従い、 VBI の 位置 に 応 じて AV\_BLANK\_EN[3]によりビデオがブランクにされるため、新しい設定ではこれが機能しないことがあります。この場合には、 AV BLANK EN ビットをディスエーブルしてください。

デコーダとバックエンドとの間で PCLK 極性が不適切であることにより出力でノイズが発生することがあります(ADV7401 と ADV7403 のハードウェア・マニュアル「Integrated Multiformat SDTV/HDTV Video Decoder and RGB Graphics Digitizer」を参照してください)。 PCLK[0]を使って、PCLK 信号を反転させて、ノイズを防止することができます。

42 37 00 ; Invert PCLK

CP フリー・ラン・スレッショールド(CP\_F\_RUN\_TH[2:0])を変更すると、無効な出力が発生することがあります。この値はデフォルトで0x54に設定されています。

EMC とクロストークのため、出力ドライバの駆動強度を調節することが必要になります。DR\_STR\_S[1:0]により、同期信号、HS、VS、FIELD の駆動強度が設定されます。DR\_STR\_C[1:0]により、クロック信号出力ドライバの出力強度が設定されます。DR\_STR[1:0]により、データ出力ドライバの駆動強度が設定されます。

推奨値を表9に示します。

表 9.駆動強度の設定値

| DR_STR_S[1:0] | DR_STR_C[1:0] | DR_STR[1:0] | Pixel Clock (MHz) |

|---------------|---------------|-------------|-------------------|

| 01            | 01            | 01          | <54               |

| 10            | 10            | 10          | <110              |

| 11            | 11            | 11          | >110              |

©2009 Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。

Rev. 0 -9/9 -