# アプリケーション・ノート

AN-2555

## 真のバイポーラ入力、完全差動出力の ADC ドライバ設計

#### はじめに

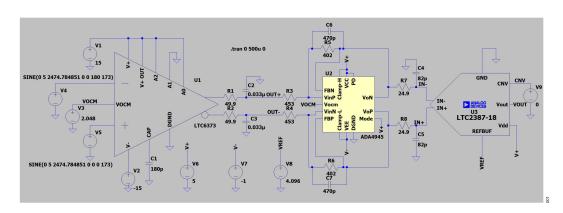

データ・アクイジションや汎用の試験装置および計測装置で用いられる高精度シグナル・チェーンは、広い範囲の入力レベルに対応できることが必要です。シグナル・チェーンでは、シグナルが ADC に適切な入力範囲に収まるようにするために、高入力インピーダンスを提供すること、ゲインと減衰のどちらにも対応すること、コモンモード・レベルを調整することなどが必要になる場合もあります。図 1 に示す回路図は、2 段のシグナル・コンディショニングを表したもので、 $\pm 10$ V の差動バイポーラ信号を、ADC に必要な 2.048V のコモンモード・レベルを持つ $\pm 4.096$ V の完全差動信号にスケーリングしレベル・シフトします。設計目標は、ADC のノイズ性能と歪み性能を低下させることなく、このコンディショニングを実現することです。入出力

の振幅電圧のヘッドルームを確保するために、通常、ADC ドライバには ADC の入力範囲を超える電源電圧が必要です。ドライバは通常、初段の出力電圧にスケーリングとシフトを施し、ADC の入力電圧範囲に合わせます(すなわち、例えば、真のバイポーラ差動信号をグラウンドから  $V_{REF}$ までの振幅の差動信号に変換します)。

図1の回路図は、LTspice®で作成したものです。これは、スイッチング・レギュレータ回路、リニア回路、シグナル・チェーン回路のシミュレーションを容易にするための各種強化機能およびモデルを備えた、高性能 SPICE III シミュレータであり、また、回路図キャプチャおよび波形ビューアでもあります。図 1 に示したデバイスの詳細については、LTC6373、ADA4945-1、LTC2387-18 データシートを参照してください。

図 1. バイポーラ入力、完全差動出力 ADC ドライバの LTspice 回路図

analog.com.jp Rev. 0 | 1 of 7

### 目次

| はじめに1  | 設計手順4      |

|--------|------------|

| 主要設計仕様 | 設計シミュレーション |

| 設計の説明4 | 測定結果       |

| 設計のコツ4 | 設計デバイス(    |

#### 改訂履歴

5/2023—Revision 0: Initial Version

analog.com.jp Rev. 0 | 2 of 7

#### 主要設計仕様

$\pm 10$ V の真のバイポーラ入力信号範囲に対する主要設計仕様を、表 1 に示します。 $\pm 10$ V ピークの差動サイン波に対し、この回路は $\pm 4.096$ V の差動出力信号を出力します。

表 1. 設計目標の主要仕様

| Parameter                                      | Value            |

|------------------------------------------------|------------------|

| Input Differential                             | ±10 V            |

| Output Differential                            | ±4.096 V         |

| Output Common-Mode Voltage (V <sub>OCM</sub> ) | 2.048 V          |

| +V <sub>S</sub> /-V <sub>s</sub> Supplies      | ±15 V, +5 V/-1 V |

| ADC Fully Differential                         | 18 bits          |

| Reference Voltage (V <sub>REF</sub> )          | 4.096 V          |

| Input Frequency Range                          | 0 kHz to 100 kHz |

| Total Harmonic Distortion (THD)                | -117 dB          |

| Single-to-Noise Ratio (SNR)                    | 95.7 dB          |

analog.com.jp Rev. 0 | 3 of 7

#### 設計の説明

この回路は、入力インピーダンスが非常に高く、シングルエン ドと差動のどちらに対しても広い範囲の入力電圧を駆動するよ う調整できる ADC ドライバ回路です。回路の出力信号は、アク イジション時間が 30ns 未満の ADC を駆動できます。しかも、 最高のノイズ性能と歪み性能を維持しながらこれを実現します。 図 1 の回路は、入力段にプログラマブル・ゲイン計装アンプ LTC6373、2 段目の ADC ドライバに完全差動アンプ (FDA) ADA4945-1、更に 18 ビット 15MSPS の ADC である LTC2387-18 を用いて構成されています。また、LTC6373 の出力と ADA4945-1 の入力の間にはノイズ低減用の100kHzフィルタがあ り、ADA4945-1 の出力と LTC2387-18 の入力の間にはグリッチ 抑制/ノイズ除去フィルタがあります。LTC6373 は、ゲインが 0.5、出力コモンモード電圧が 2.048V の、差動入力差動出力アン プとして構成されています。また、ADA4945-1 は、ゲインが 0.8 の減衰差動入力差動出力ドライバとして構成されています。 ADA4945-1は、LTC2387-18の入力範囲に対応できるよう、出力 コモンモード電圧が2.048Vに設定されています。LTC2387-18の 各入力の入力信号範囲は0V~4.096Vであるため、4.096Vの内部 リファレンスを用いた場合、差動入力信号範囲は±4.096V とな ります。

#### 設計のコツ

これより広い、あるいは狭い信号範囲が必要な場合、LTC6373 のゲインと  $R_F/R_G$  の比を変更できます。例えば、 $\pm 100 \text{mV}$  の信号範囲が必要な場合、 $R_G$  は元の値のままとしながら  $R_F$  を増加することができます。次の式を用いると  $R_F$  を再計算できます。

$$R_F = (V_{OUT}/V_{IN}) \times R_G \tag{1}$$

ここで、

$$V_{OUT} = ADC_{IN} + (MAX) - ADC_{IN} - (MIN)$$

(2)

$$V_{IN} = V_{IN}(MAX) - V_{IN}(MIN) \tag{3}$$

ADA4945-1 の方が利得帯域幅が大きいので、LTC6373 ではなく こちらのゲインを増加することを推奨します。

R5、C6、R6、C7 で構成されるフィルタにより、ADA4945-1 の 帯域幅は減少します。帯域幅が狭くなると、LTC2387-18 の入力 ノイズが低減します。C6 と C7 の値は、SNR の改善が終わるま で値を徐々に増加させることで、実験的に求まります。

抵抗 R7 および R8 とコンデンサ C4 および C5 で構成されるフィルタは、ADC 入力がバッファされていない場合に、この入力によって生じるサンプリング・グリッチから ADA4945-1 の出力を分離します。このフィルタは、ADC 入力に供給される信号の帯域幅を制限し、ADC 入力に表れるノイズを低減する効果があります。

ドライバと ADC の間のフィルタにセトリングする時間がない場合は、ゲイン誤差が発生します。アプリケーションによっては小さなゲイン誤差なら許容できるかもしれませんが、セトリングできない場合には歪みも生じ、これは回避する必要があります。高精度 ADC ドライバ・ツールを用いるとフィルタのセトリングをチェックし、回路の S/N 比と THD 性能を推定することができます。

#### 設計手順

#### 初期条件および前提事項

LTC6373 の電源は±15V、ADA4945-1 の電源は+5V/-1V に設定されています。入力範囲は20V p-p (±10V)、出力範囲は8.192V p-p (ADC への入力)を前提としています。アナログ・フロント・エンド (AFE) に分配される合計ゲインは次のとおりです。

$$G_{TOTAL} = 8.192 \text{ V p-p/}20 \text{ V p-p} = 0.4096 \text{ V/V}$$

(4)

部品の許容誤差とコモンモードのわずかな変動に対応するための若干のヘッドルームを考慮し、合計ゲインの目標値は 0.4V/V に設定します。LTC6373 には、{0.25、0.5、1、2、...、16}のゲイン値のいずれかを選択できます。どちらの段のゲインも 1 未満となるように選択すると、ADA4945-1 で電源範囲の値を小さくでき、各段のノイズ・ゲインを下げることができます。LTC6373 のゲインを 0.5 に設定すると ADA4945-1 のゲインは 0.8 となります。

LTC6373 および ADA4945-1 のどちらのコモンモードも 2.048V に 設定します。

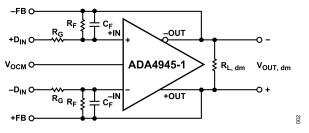

図 2. ADA4945-1 の回路の定義

- ADC (LTC2387-18) に対し、フルスケール入力を±4.096V、 VREFを 4.096V、±VFSを±4.096V に設定します。

- 2. ドライバ・アンプ (ADA4945-1) の V<sub>OCM</sub>を設定します。

$V_{OCM}$  は 4.096V/2 = 2.048V にバイアスします。これがデータシートの出力コモンモード条件を満たすかどうかを確認します。

$$(-V_S + 0.4) \le V_{OCM} \le (+V_S - 1.4 \text{ V})$$

このアプリケーションでは、

$$-V_S = -1 \text{ V}, +V_S = 5 \text{ V}, V_{OCM} = 2.048 \text{ V}$$

$(-1+0.4) \le V_{OCM} \le (5-1.4 \text{ V})$

$(-0.6) \le 2.048 \text{ V} \le (3.6 \text{ V})$

$V_{OCM}$  は許容範囲内に収まっています。 $V_{OCM}$  は LTC2387-18 の  $V_{OCM}$  ピンによって供給されます。

3. 入力アンプ (LTC6373) の入力制限値と出力制限値を設定します。

ゲインが 0.5 に設定されているため、出力振幅は次のようになります。

$\pm 10V/2 = \pm 5V$

出力振幅は、

analog.com.jp Rev. 0 | 4 of 7

$V_{OCM} \pm 5 \text{ V/2}$

$$V_{OUT_{max}} = + D_{IN} = 2.048 \text{ V} + 5 \text{ V}/2$$

= 2.048 V + 2.5 V = 4.548 V

$$V_{OUT_{min}} = -D_{IN} = 2.048 \text{ V} - 5 \text{ V}/2$$

= 2.048 V - 2.5 V = -0.452 V

信号の極性が反転している場合、 $\pm D_{IN}$  の値は単にこれを反転したもの (0.452V、-4.548V)になります。

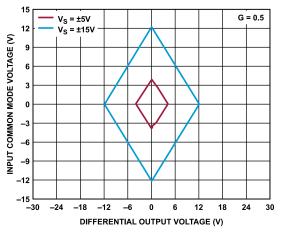

図 3 に、ゲインが 0.5 の場合の LTC6373 について、入力振幅 と出力振幅の各制限値を示します。 $V_S = \pm 15V$  のグラフを見ると、入力コモンモード電圧が 2.048V、出力差動電圧振幅が $\pm 4.548V$  の場合、このアプリケーションは LTC6373 で容易に実現できることがわかります。しかし、 $\pm 5V$  の電源を用いた場合は、LTC6373 はその差動出力電圧範囲外で動作する可能性があります。LTC6373 の全ゲインに対するコモンモード電圧範囲と差動出力電圧の関係を示すグラフは、データシートに記載されています。

LTC6373 の  $V_{OCM}$  も、別のバイアス・ポイントを生成する必要がないよう、LTC2387-18 の  $V_{OCM}$  ピンを用いて 2.048V に設定します。

図 3. 入力コモンモード電圧範囲と差動出力電圧の関係

4. アンプのゲインは次のように設定します。

$$Gain = V_{OUTdm pp} / V_{INdm pp}$$

(5)

このアプリケーションでは、

$$Gain = 8 V_{P-P}/(0.5 \times 20 V) = 0.8 V/V$$

ノイズを最大限に抑えるために、ADA4945-1 のデータシートでは、ユニティゲインのセットアップでは  $R_F$ および  $R_G$ を 499 $\Omega$  とすることを推奨しています。この例の場合では、 $R_G$  は目的のゲインに合わせて  $402\Omega$  にスケーリングします。  $R_G$  は  $49.9\Omega$  と  $453\Omega$  の抵抗で構成できます。 THD が S/N 比より も重要となる場合は、 $R_G$  を  $2k\Omega$ 、 $R_F$  を  $1.62k\Omega$  とすれば、S/N 比は 4dB 悪化しますが、THD を 3dB 改善できる可能性 があります。

5. ドライバ・アンプ (ADA4945-1) の出力振幅を設定します。 ドライバ・アンプの振幅は  $V_{OCM}$  を中心とする差動出力であるため、 $+V_{FS}$  が印加されている場合、オペアンプ出力は  $-V_{FS}$  に反転した電圧となります。実際の最大範囲が回路ゲインによって 4V に制限されている場合でも、 $V_{REF}$  (4.096V) をこの範囲に対し用います。ADA4945-1 の出力は、このア

プリケーションの場合、 $0.0V \sim 4.096V$  の範囲で振動できる 必要があります。

$$V_{OUTdm} = V_{+OUT} - V_{-OUT} \tag{6}$$

$V_{OUTdm} = +V_{FS} \, \mathcal{C} \mathcal{L}$

$$V_{+OUT} = V_{OCM} + V_{OUTdm}/2$$

$$V_{+OUT} = 2.048 \text{ V} + 4.096 \text{ V}/2 = 4.096 \text{ V}$$

$$V_{-OUT} = V_{OCM} - V_{OUTdm}/2$$

$$V_{-OUT} = 2.048 \text{ V} - 4.096 \text{ V}/2 = 0.0$$

$$V$$

(7)

**6.** ドライバ・アンプ (ADA4945-1) の出力電圧振幅が電源レールに対するデータシートの条件に合うかどうかを調べます。

1kΩ 負荷時の ADA4945-1 データシートに従い、

$$(-V_S + 0.1 \text{ V}) \le V_{OUT} \le (+V_S - 0.1 \text{ V})$$

(8)

このアプリケーションでは、

$$V_{+OUT\_min} = 0 \text{ V}, \quad V_{+OUT\_max} = 4.096 \text{ V}$$

$$-V_{S\_min} = V_{+OUT\_min} - 0.1 \text{ V}$$

$$-V_{S\_min} = 0 \text{ V} - 0.1 \text{ V} = -0.1 \text{ V}$$

$$+V_{S\_min} = V_{+OUT\_max} + 0.1 \text{ V}$$

$$+V_{S\_MIN} = 4.096 \text{ V} + 0.1 \text{ V} = 4.196 \text{ V}$$

(9)

7. ドライバ・アンプ (ADA4945-1) の入力振幅を設定します。

$V_{OUTdm}$ =+ $V_{FS}$ の場合、入力コモンモード電圧は次のように計算できます。

$$\begin{split} V_{OUTdm} &= 4.096 \text{ V}, \ +D_{IN} = 4.548 \text{ V}, \ -D_{IN} = -0.452 \text{ V}, \\ V_{OUT+} &= 4.096 \text{ V}, \ V_{OUT-} = 0.0 \text{ V} \\ V_{+IN} &= +D_{IN}(R_F(R_F + R_G)) + V_{-OUT}(R_G/(R_F + R_G)) \\ V_{+IN} &= +4.548(402/(402 + 503)) + 0.0 \text{ V}(503/(402 + 503)) = 2.02 \text{ V} \\ V_{-IN} &= -D_{IN}(R_F/R_F + R_G)) + V_{+OUT}(R_G/(R_F + R_G)) \\ V_{-IN} &= -0.452(402/(402 + 503)) + 4.096 \text{ V}(503/(402 + 503)) = 2.07 \text{ V} \end{split}$$

$V_{OUTdm} = -V_{FS}$  の場合、入力コモンモード電圧は次のように計算できます。

$$\begin{split} V_{OUTdm} &= -4.096 \text{ V}, \ +D_{IN} = -0.452 \text{ V}, \ -D_{IN} = +4.548 \\ \text{V}, \ V_{OUT+} &= 0.0 \text{ V}, \ V_{OUT-} = 4.096 \text{ V} \\ V_{+IN} &= +D_{IN}(R_F(R_F + R_G)) + V_{-OUT}(R_G/(R_F + R_G)) \\ V_{+IN} &= -0.452(402/(402 + 503)) + 4.096 \text{ V}(503/(402 + 503)) = 2.07 \text{ V} \\ V_{-IN} &= -D_{IN}(R_F/R_F + R_G)) + V_{+OUT}(R_G/(R_F + R_G)) \\ V_{-IN} &= 4.548(402/(402 + 503)) + 0 \text{ V}(503/(402 + 503)) \\ &= 2.07 \text{ V} \end{split}$$

ADA4945-1 の入力は、このアプリケーションの場合、 $2.02V \sim 2.07V$  の範囲で振動できる必要があります。

8. ドライバ・アンプ (ADA4945-1) の入力コモンモード電圧を チェックします。

ADA4945-1 のデータシートに従い、

$$-V_S \le V_{CM} \le (+V_S - 1.3 \text{ V}) -1 \text{ V} \le 2.048 \text{ V} \le 3.7 \text{ V}$$

(12)

analog.com.jp Rev. 0 | 5 of 7

データシートの条件は満たされています。 このアプリケーションでは、

$$V_{+IN\_min} \le V_{CM} \le V_{+IN\_max}$$

2.03 V \le 2.048 V \le 2.07 V (13)

アプリケーションの条件は満たされています。

#### 設計シミュレーション

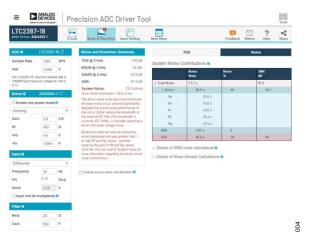

高精度 ADC ドライバ・ツールは、ドライバ・アンプと RC フィルタの選択が ADC シグナル・チェーンの全体性能に及ぼす影響を技術者が手早く確定できる、専用のシミュレーション環境を提供します。

図 4 に示す高精度 ADC ドライバ・ツールを用いると、セトリング時間、ノイズ、THD 性能が推定できます。現在のところ、高精度 ADC ドライバ・ツールでは LTC6373 を回路図に追加することができません。そのため、LTC2387-18 を駆動する ADA4945-1 の性能のみをシミュレーションできます。ドライバ・ツールによれば、最低電源電圧は+4.6V および-0.5V です。また、選択したドライバでは全体的なノイズ性能が大きく低下することをこのツールは警告しています。 $R_F$ および $R_G$ がドライバのノイズの最大要因です。ドライバ・ツールでは、ここで示すアプリケーションのように、 $R_F$ の両端をつなぐコンデンサを追加できません。これらのコンデンサによりドライバ・ノイズは低減されます。設計目標とシミュレーション結果の比較を表 2 に示します。

表 2. 設計目標とシミュレーションの比較

| Parameter | Design Goal | Simulation |

|-----------|-------------|------------|

| SNR       | 95.7 dB     | 91.9 dB    |

| THD       | −117 dB     | −116 dB    |

図 4. 高精度 ADC ドライバ・ツール:ノイズと THD の結果

#### 測定結果

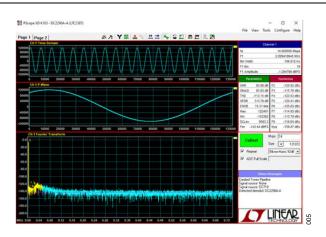

図 5 に示すように、ADC の S/N 比性能を測定した値は ADA4945-1 のデータシートに記載された代表的仕様値である-95.7dB より 0.4dB 低下し、THD 性能はデータシートの代表的仕様値である-117dB より 3.8dB 低下しました。

図 5. 図 1 の回路の実測性能

設計目標と測定結果の比較を表 3 に示します。THD 性能は、ADA4945-1 の  $R_G$ を  $2k\Omega$ に、 $R_F$ を  $1.62k\Omega$  に増加することで、最大 3dB 改善できる可能性があります。ADC ドライバ・ツールによると、この増加により S/N 比は 4dB 悪化します。THD と S/N 比のどちらを重視するかはユーザによって異なります。取得したデータはすべて 14MSPS のデータ・レートです。15MSPS にすると、ADC のアクイジション時間が短くなるため、THD は大きく低下します。

表 3. 設計目標と測定値の比較

| Parameter | Design Goal | Measured  |

|-----------|-------------|-----------|

| SNR       | 95.7 dB     | 95.3 dB   |

| THD       | −117 dB     | −113.2 dB |

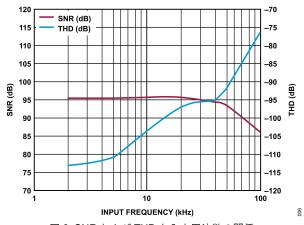

図 6 に示すように、入力周波数が 15kHz を超えると THD は -100dB を超えます。入力周波数が 90kHz を超えると S/N 比は 90dB未満となります。このデータは25℃で取得したものです。温度がこれより低い場合も高い場合も、性能はこれよりも早く低下します。回路処理を変更すると、性能が低下し始める電圧も変化する可能性があります。

図 6. SNR および THD と入力周波数の関係

#### 設計デバイス

表 4. オペアンプ-ADA4945-1

| 2007                         |       |

|------------------------------|-------|

| Parameter                    | Value |

| Input Offset Voltage Maximum | 50 μV |

analog.com.jp Rev. 0 | 6 of 7

#### 表 4. オペアンプ-ADA4945-1 (続き)

| Parameter                               | Value    |

|-----------------------------------------|----------|

| Bias Current Maximum                    | -2.5 μA  |

| Gain Bandwidth Product Typical          | 145 MHz  |

| Noise Voltage Typical                   | 5 nV/√Hz |

| Quiescent Current per Amplifier Typical | 180 μΑ   |

| Supply Voltage Span Minimum/Maximum     | 3 V/10 V |

#### 表 5. オペアンプ-LTC6373

| Parameter                               | Value       |

|-----------------------------------------|-------------|

| Input Offset Voltage Maximum            | 464 μV      |

| Bias Current Maximum                    | 0.0005 μΑ   |

| Gain Bandwidth Product Typical          | 7 MHz       |

| Noise Voltage Typical                   | 26.4 nV/√Hz |

| Quiescent Current per Amplifier Typical | 4.4 mA      |

| Supply Voltage Span Minimum/Maximum     | 9 V/36 V    |

#### 表 6. ADC-LTC2387-18

| Parameter                                                                      | Value              |

|--------------------------------------------------------------------------------|--------------------|

| Resolution                                                                     | 20 bits            |

| Sampling Frequency Maximum                                                     | 1 MSPS             |

| Input Type (Single-Ended or Differential)                                      | Fully differential |

| $V_{IN}$ Span $V_{MIN}/V_{MAX}$                                                | 5 V                |

| SNR Typical                                                                    | 104 dB             |

| THD Typical                                                                    | -125 dB            |

| Data Interface (I <sup>2</sup> C, Serial Peripheral Interface (SPI), Parallel) | SPI                |

©2023 Analog Devices, Inc. All rights reserved.

・ イン 〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 10F 電話 03(5402)8200

大 阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F 電話 06 (6350) 6868

名古屋営業所/〒451-6038 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F 電話 052 (569) 6300