# AN-1316 アプリケーション・ノート

## フライバック、SEPIC、Čuk の組み合わせによる IGBT モーター・ドライブ用の 複数の絶縁バイアス・レールの生成

#### Bob Zwicker 著

#### はじめに

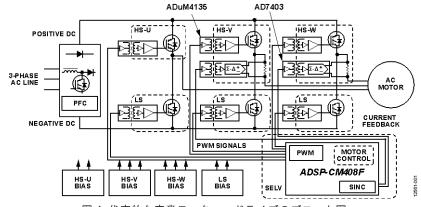

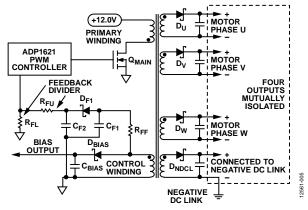

先進のモーター・ドライブは、3 相、絶縁型ゲート・バイポーラ・トランジスタ(IGBT)ベースのインバータを採用し、400 V dc ~800 V dc の DC 電圧で動作します。このような高電圧は、3 相整流器ブリッジ・フィルタの組み合わせ、または力率補正ブースト整流器から直接供給します。これにより、3 相 AC 入力から高電圧が生成されます(図1を参照)。

IGBT は、凡そ 10 kHz のパルス幅変調 (PWM) の出力を 3 つの モーター相に与え、メインのパワースイッチとして機能します。、 インダクション・モーターと永久磁石モーターは、巻線のインダ クタンスが高く、この PWM で生成されたサイン波に近い低周波 の電流波形で駆動されます。小型モーターで使用される一部の IGBT は、ADuM4223 などのゲート・ドライバによって提供され るユニポーラ (例: 0 V  $\sim$  15 V) 電圧で動作しますが、大型シス テムでは、ADuM4135などのゲート・ドライバによって、バイポー ラ  $(-7.5 \text{ V} \, \text{と} + 15 \text{ V} \, \text{など})$  電圧で駆動されることがあります。負 のターンオフ電圧により、コレクタ-エミッタ電圧 (VcE) の急激 な上昇(正側の高いdV/dt)によって誘発されるIGBTのターンオ ン時のスプリアスを回避できます。この高い dV/dt は、他デバイ スの通常のターンオンによって発生します。(上側デバイスのター ンオンが下側デバイスの望ましくないターンオンを誘導したり、 その逆が発生することもあります)。6個のゲート・ドライバに は、これらの+15Vおよび-7.5Vのバイアス電圧を供給するため の電源が必要です。

図1の例で、3つのモーター相のうち、2つにシャント抵抗が直列接続され、モーター相の電流を計測する AD7403 絶縁型  $\Sigma$ - $\Delta$  モジュレータが抵抗の両端に接続されています。 (3番目の相は

推測できるため、電流は2つの相でのみ計測します)。これら2つの  $\Sigma$ - $\Delta$  モジュレータは、5 V で駆動します。

3つのハイサイド (HS) IGBT のドライバ・バイアス電圧は、各モーター相を基準にしています。つまり、3つのハイサイド・ドライバ (3つのモーター相に接続された) は、それぞれ独自の絶縁されたバイアス領域 (HS-U、HS-V、HS-W) を備えています。また、3つのローサイド (LS) ドライバはすべて負の DC 電圧を基準にしているため、もう1つのバイアス領域 (LS) を共有します。表1に、一般的なモーター・ドライブのバイアス領域 (ドメイン)、および含まれている電源(バイアス・レール)の要件を示します。

表 1. モーター・インバータ電源要件

| Inverter Circuit                             | Domains                 | Voltages (V) | Voltage Rails |

|----------------------------------------------|-------------------------|--------------|---------------|

| Three Low-Side<br>IGBTs                      | LS                      | +15, -7.5    | 2             |

| Three High-Side<br>IGBTs                     | HS-U, HS-<br>V,<br>HS-W | +15, -7.5    | 6             |

| Two High-Side $\Sigma$ - $\Delta$ Modulators | HS-V, HS-<br>W          | +5           | 2             |

| Total                                        | 4                       |              | 10            |

表1の計算ではレールの合計数は10個ですが、合計数はモーター・ドライブの設計によって変わるので、このアプリケーション・ノートでは重要性を持ちません。値が異なる場合でも、これらの電源供給する技法に影響を与えません。これは、このアプリケーション・ノートの主題は、その技法になります。

図 1. 代表的な産業モーター・ドライブのブロック図

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって 生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示 的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本語配数の商標誌とび登録商標は、それぞれの所有 者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2016 Analog Devices, Inc. All rights reserved.

Rev. **0**

アナログ・デバイセズ株式会社

本 社/〒105-6891

| 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル 電話 03(5402)8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

# 目次

| はじめに                        | 1   |

|-----------------------------|-----|

| 改訂履歴                        | 2   |

| バイアス電圧に関する基本的な制約            | 3   |

| 絶縁                          | 3   |

| ドウェル                        | 3   |

| 電圧レギュレーション                  | 3   |

| バイアス電圧の生成方法                 | 4   |

| フライバック・コンバータの適用によるモーター・ドライフ | ブ・バ |

| イアスの生成                      | 5   |

| 1次側からのフライバック・コンバー?              | タ出力の検出6 |

|---------------------------------|---------|

| フライバック、SEPIC、Čuk トポロジの          | り組み合わせ7 |

| 回路の理論とトポロジの比較について               | 10      |

| 複合フライバック、SEPIC、および Čul<br>る考慮事項 |         |

| 結論                              |         |

#### 改訂履歴

11/15—Revision 0:初版

#### バイアス電圧に関する基本的な制約

これらのバイアス・レールを供給する方法では、いくつかの基本的な要件を考慮する必要があります。

#### 絶縁

ミッドエンド/ハイエンドのモーター・ドライブでは、プロセッ サは通常、最適な性能を得られるように安全超低電圧 (SELV) の 電力領域で動作します。一般的なオーディオ機器やPCのポート に供給される電力と同様、これらの電圧および電流レベルは十分 に低いため、危険ではありません。偶発的な人的接触に対して注 意する必要もないので、セーフティー・アイソレーションを実装 せずに、プロセッサ・ヒューマン・インターフェースが簡単に行 えます。ただし、IGBT とモーター相は、通常、数百ボルト以上 で互いに関係を持った信号で、SELV 電力領域に関係します。こ のため、IGBT ゲート、ドライバ出力、およびそれらを駆動する バイアス電圧はすべて危険な電圧領域です。IGBT ゲート電圧領 域とそれらの駆動源となる SELV 電力領域の間にセーフティー・ アイソレーションが必要で、領域自体の間に機能的絶縁も必要に なります。バイアス電源トランスには、絶縁された出力巻線、お よび絶縁された各電力領域用に少なくとも2つの接続端子が必要 です。

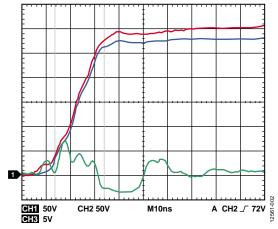

電圧の絶対値に加え、モーター相のコモンモード・スルー・レート(電圧の変化率または dV/dt)を考慮する必要があります。図 2 に、デモ・ボードの IGBT で駆動されるモーター相のスイッチング波形を示します。この測定のスルー・レートは  $11\ V/ns$  です。バイアス電圧は、コモンモード電圧のこのスルー(変化)に追従する必要がありますが、コモンモード電圧のスルーによって妨害されてはいけません。

図2で、チャンネル1はハイサイドIGBTのエミッタ、チャンネル、2はゲートです。このIGBTがオンになると、正の負荷電流がエミッタから出力されます。チャンネル1のカーソル測定値に基づいて判断すると、dV/dtは11 V/nsです。

図 2. モーター相電圧波形

#### ドウェル機能

モーター・ドライブ・アルゴリズムによっては、ある状態(高電 圧出力または低電圧出力など)でモーター相を比較的長い時間に わたって安定させる必要があります。特に、一部の空間ベクトル 変調方式により、モーター相が数ミリ秒またはそれ以上にわたっ てハイ状態になることがあります。ドライバをバイアスする一部 の方法(ブートストラップなど)は、これらの変調方式と互換性 がありません。

#### 電圧レギュレーション

電圧レギュレーションは、絶縁型電圧コンバータでそれほど要件の厳しくない性能基準の1つです。ゲート・ドライバへの出力電圧は、約10:1の負荷電流範囲にわたって $\pm 3$ %  $\sim \pm 5$ % に維持する必要があります。これは比較的低い精度です。 $\Sigma$ - $\Delta$  モジュレータへの5 V 出力は、 $\pm 1$ % の電圧レギュレーションが必要で、これは ADP7118、ADP7102、ADP7104 などの低ドロップアウト (LDO) レギュレータで実現できます。

#### バイアス電圧の生成方法

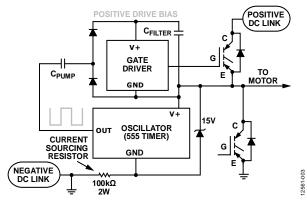

抵抗から電力を供給する抵抗供給チャージ・ポンプは、モーター相を基準としたバイアス電圧を発生させる、低コストな方法の1つです。図3の例では、チャージ・ポンプが正の単ーレールを生成します。基本的なモーター・ドライブではこれで十分ですが、消費電力が大きくなるので効率が非常に悪くなります。レールの数や電流が増えると、この損失は許容できなくなります。

図 3. 抵抗供給チャージ・ポンプ

抵抗供給チャージ・ポンプは、非効率であるにもかかわらず、一 般的に使用されています。

抵抗供給チャージ・ポンプのメリットは、次のとおりです。

- 2つのトランス・ピンから複数の電圧を出力

- 部品コストが低い

- 負荷レギュレーションの性能が高い

- 電圧設定の柔軟性が高い

- ブートストラップのデューティ・サイクル制限を回避

抵抗供給チャージ・ポンプのデメリットは次のとおりです。

- 効率が非常に低い

- 出力電流能力が低い

- 下部 IGBT がオンの場合、電力伝送なし

15 V のみが必要な場合、ローサイドの IGBT に対して 15 V を供給すること自体に問題はなく、ローサイドの IGBT を長時間にわ

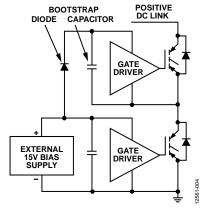

たって使用してもオフになることはありません。ブートストラップ (図4を参照)は、ローサイド・ドライバのバイアス電流を使用 してハイサイド・ドライバを駆動する最適な方法になる場合も あります。

図 4. ブートストラップ

ブートストラップは幅広く使用されていて、特に降圧 DC/DC 電圧変換で使用されます。これらは、ブートストラップが十分な性能を実現できるアプリケーションで推奨されます。

ブートストラップのメリットは、次のとおりです。

- 複数のトランス出力巻線の使用を回避

- 低コスト

- 効率が高い

ブートストラップのデメリットは、次のとおりです。

- ブートストラップ・コンデンサを再充電するには、ローサイドの IGBT を頻繁にオンにする必要がある。空間ベクトル変調と互換性のない可能性がある。

- 負バイアス・レールの作成が困難になる

- チャージ・ポンプの性質上、出力電流が制限される

トランスベースの技法は、チャージ・ポンプ方式とブートストラップ方式の制限を回避するうえで最も有力な方法です。

## フライバック・コンバータの適用によるモーター・バイアスの生成

トランスの漏れインダクタンスを低く抑える低消費電力の絶縁型 コンバータの場合、フライバック方式が最も一般的で経済的な方法です。

しかしながら、市販のフライバック電源の多くは、2次側の誤差アンプから1次側PWMコントローラへの帰還にフォトカプラを使用しますが、この方法には2つの問題があります。

1つ目は、フライバック・コンバータのメイン出力を2次側の電圧センシングに利用すると、センシングされたメイン出力では優れた電圧レギュレーション(1%)を実現できますが、モーターに与えられている他の絶縁された10個の出力も悪影響を受けます。通常、この影響はクロス・レギュレーションと呼ばれます。

代わりに、いくつかの2次側出力の組み合わせに重みを付けて、レギュレーションを実施することもできます。ただし、これらの出力全体が、同じ絶縁領域内に収まる必要があります。これらのセンシングされた出力で構成される負荷の組み合わせに生じる変動も、他の絶縁領域にあるスレーブ出力に悪影響を与えます。ある領域に含まれる複数の出力を検出しても、スレーブ領域やセン

シングを行っていない領域のクロス・レギュレーションは改善されません。

2つ目は、フォトトランジスタのベースの容量と高ゲインにより、フォトカプラが高コモンモードでのdV/dtの悪影響を受けやすくなることです。 図2 は、モーター相を駆動している IGBT エミッタでの実際のdV/dtを示しています。11 V/ns という値は、多くのフォトカプラに干渉する可能性が高いと考えられます。フォトカプラは、ADuM3190 などの高性能デバイスと置き換えることができ、絶縁型電源で一般的に使用されるフォトカプラと2次側リファレンスの両方を置き換えることが出来ます。絶縁バリアをまたいで結合するには、内蔵の超小形トランスを使用します。この製品は11 V/ns というコモンモード・スルー・レートの影響を受けません。

モーターのゲート・バイアス電源コンバータに複数の絶縁された出力が存在する場合、2次側の電圧検出にメリットはありません。

#### 1 次側からのフライバック・コンバータ出力の検出

もう1つのオプションとして、1次側の巻線からトランスの出力電圧をセンシングする方法があります。1次側センシングフライバック・コンバータは、シンプルで優れた出力電圧レギュレーションを実現します。2次側センシングコンバータでは、メイン出力は厳密にレギュレーションされますが、スレーブ(検出されない)出力はセンシングされた出力の負荷によって変動します。1次側センシングコンバータでは、センシングされた出力の負荷が固定され、非常に低い値になる可能性もあります。その場合、検出された出力の負荷によってスレーブ出力が変動することはありません。このため、1次側の電圧センシングを利用して電圧レギュレーションを実施する方が全体的に優れた結果を得られる可能性もあります。範囲の広い負荷電流に対して、±3%(概算)の誤差で負荷レギュレーションを実施することは、代表的なモーター制御ゲート・ドライブ・バイアス電力を含む、さまざまな目的にとって有効です。

個別の出力電圧は、トランス巻線の巻数を変えることで変更できます。帰還回路を変更するか、制御巻線の巻数を変更して、すべての出力電圧を巻数に比例する形で変更することもできます。

1次側の電圧センシングでは、2次側リファレンスと絶縁帰還も不要になります。通常、単純で低コストな設計になり、部品数の削減とプリント基板 (PCB) の小型化が可能になります。この技法は、絶縁バリアをまたぐコモンモードでの dV/dt に対して優れた耐性のあることが実証されています。

図5に、絶縁された1次側センシングフライバック電圧コンバータのトポロジを示します。

図 5.1 次側の電圧センシングを行う絶縁型 フライバック・コンバータ(複数出力)の簡略回路図

$Q_{MAIN}$ がオフになると、絶縁された出力によって実現されるのと同じ電圧/巻数が、制御巻線によって実現されます(図5のトランスの右側)。

$R_{FF}$  (100 $\Omega$  ~ 500 $\Omega$ ) と  $C_{FI}$  (50 pF ~ 300 pF) は、 $D_{FI}$  のアノードの AC 入力波形から立ち上がりエッジ電圧スパイクを抑制するローパス・フィルタを形成します。このスパイクは  $Q_{MAIN}$  のターンオフと同じで、複雑なトランス漏れインダクタンスの関数です。 $D_{FI}$  の出力の負荷が非常に小さい場合、このスパイクは  $D_{FI}$  によって整流され、抑制しないとコンバータ電圧レギュレーションが大幅に低下します。 $D_{FI}$  の整流された出力には、 $C_{F2}$  によって DC フィルタが適用されます。

$C_{FI}$  の反復的な充電は損失の原因となります。このため、 $C_{FI}$  の値を最小にする必要があります。最小の  $C_{FI}$  で、必要なローパス・フィルタ時間定数を達成するには、 $R_{FF}$  の値を最大にする必要があります(この時定数の最適な値は、トランスによって異なりますが、通常は  $10\,\mathrm{ns}\sim100\,\mathrm{ns}$  の範囲に収まります)。ただし、 $C_{FF}$  と連携して AC ローパス・フィルタを形成することが  $R_{FF}$  の唯一の目的です。  $R_{FF}$  の DC 電圧降下は誤差の要因であり、最小限に抑える必要があります。この DC 電圧降下を最小にするには、可能な限り高いインピーダンスが得られるように  $R_{FU}$  と  $R_{FL}$  を選択する必要があります。ただし、 $ADP1621\,PWM$  コントローラ IC の FB ピン入力のバイアス電流に合わせてインピーダンスを整合させます。ここで、 $R_{FU}$  と  $R_{FL}$  は帰還分圧器を形成します。これらの抵抗は、制御巻線と連携して機能し、出力電圧を設定する役割を果たします。

$D_{FI}$ には、適切な定格電圧を備えた小信号 (定格電流  $10 \, \text{mA} \sim 200 \, \text{mA}$ ) ショットキー・ダイオードを使用する必要があります。

DC フィルタリングに使用する  $C_{F2}$  の値も考慮する必要があります。 $C_{F2}$  を過度に大きくすると、追加された極が帰還ループ通過帯域に移動し、安定性を損なう原因となります。帰還ループの位相マージンに悪影響を与えないようにするには、 $C_{F2}$  を可能な限り小さくして、DC フィルタリングという目的に整合させる必要があります。代表値は  $10\,nF$  です。

図5の設計には、 $12 V \sim 48 V$ の入力で駆動しているときに最高の効率を得られるように、動作バイアス電流をコントローラ IC に供給するための  $D_{BIAS}$  と  $C_{BIAS}$  (これらはオプション) も組み込まれています。この場合、効率的な 5 V の 1 次側バイアス・レールは使用できません。2 つの機能を実行するように  $D_{BIAS}$  から帰還を取り出すことはできますが、 $D_{BIAS}$  と  $D_{FI}$  ( $D_{FI}$  に最小負荷)を分離すると、最高の電圧レギュレーションを実現できます。

## フライバック、SEPIC、ČUK 方式の組み合わせ

以降のセクションでは、フライバック・コンバータの出力方式について説明してから、SEPIC およびČuk(チューク、セルビア語 Чук≒英語 Chuk)出力回路について説明します。これらの事項は、このアプリケーション・ノートの主題です。

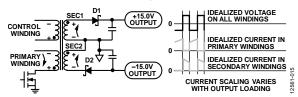

図6に、フライバック・トランスから2つの出力を生成するうえで最も一般的な方法を示します。シンプルかつ効率的で、各巻線の巻数に基づいて独立した出力電圧を設定できます。

この方法では、出力ごとに1本のトランス・ピンとコモン接続用に1本のトランス・ピンが必要になります。この要件は、大量の出力を生成する場合にデメリットとなります。

図 6. フライバック・トランスから複数の出力電圧を生成する 簡単な方法

この方法のメリットは、次のとおりです。

- 効率が非常に高い

- 部品コストと部品数を削減

- 負荷レギュレーションの性能が非常に高い

- 電圧設定の柔軟性が高い

- 負電圧または正電圧の生成が容易

この方法のデメリットは、出力電圧ごとに1本のトランス・ピン とコモン・ポイント用に1本のピンが必要になることです。

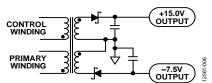

図7に、異なるトレードオフへの手法を示します。絶縁された出力領域でのみトランス・ピンを2本使用します。リニア方法または消費型の方法を使用してレールを分割します。この方法を使用するとレギュレーションを適切に実施できますが、アプリケーション領域は低出力電流に制限されます。この方法は、このアプリケーション・ノートで説明しているフライバック出力回路アーキテクチャの中で最も効率が低いのですが、1つのフライバック出力巻線から複数のモーター・ドライブ・バイアス電圧を生成できます。

図 7. 消費型のレール分割

必要な最大出力電流と最小ツェナー・バイアス電流は、常に D1 から R1 に流す必要があります。

消費型のレール分割方法のメリットは、次のとおりです。

- 2つのトランス・ピンから複数の電圧を出力

- 部品コストが低い

- 負荷レギュレーションの性能が高い

- 電圧設定の柔軟性が高い

消費型のレール分割方法のデメリットは、次のとおりです。

- 効率が低い

- 出力電流能力が低い

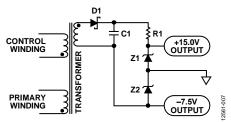

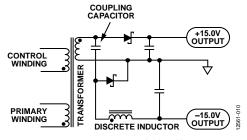

出力巻線の間にカップリング・コンデンサを追加すると(図8を参照)、同じ巻数で同じ電圧を生成する2つのDC出力間の電圧トラッキングが向上します。カップリング・コンデンサは、トランスの漏れインダクタンスの影響を効果的に解消するため、クロス・レギュレーションの性能が向上します。追加したカップリングがフライバック出力レギュレーションに与えるメリットを実証するため、図9にPQ3230コア・トランスを使用した36Wのオフライン・フライバック・コンバータでの実験したテスト結果を示します。

図 8. SEPIC および Čuk フライバックの変更

図8に示す変更を加えた回路は、図6の回路をベースにしています。両方の巻線の両端がトランスのピンに接続されています。負の整流器を巻線の反対側の端に移動し、出力巻線の間にカップリング・コンデンサを追加しました。ここでは、両方の出力巻線を同じ巻数にする必要があります。

図8の変更のメリットは、次のとおりです。

- 効率が高い

- 部品コストが低い

- 領域内でのクロス・レギュレーション性能が最高

図8の変更のデメリットは、次のとおりです。

- 各領域の出力ごとに2つのトランス・ピンが必要

- 出力電圧の大きさが互いに一致する必要がある

表 2. バイアス電源負荷のテスト条件

| Load Combination | +12 V Output (A) | -12 V Output (A) |

|------------------|------------------|------------------|

| 1                | 0.01             | 0.50             |

| 2                | 0.01             | 0.02             |

| 3                | 0.10             | 0.02             |

| 4                | 0.10             | 0.01             |

| 5                | 0.20             | 0.01             |

| 6                | 0.50             | 0.02             |

| 7                | 0.50             | 0.01             |

| 8                | 1.00             | 0.01             |

| 9                | 2.00             | 0.02             |

| 10               | 2.00             | 0.01             |

| 11               | 3.00             | 0.02             |

| 12               | 3.00             | 0.01             |

図 9. 出力巻線の間にカップリング・コンデンサがある場合とない場合のデュアル出力フライバック電源のテスト・データ

図9に、36 W ± 12 V の出力フライバック・オフライン電源から得られたテスト・データを示します。出力整流回路のアーキテクチャは、図6とほぼ同じです。このため、同じように動作し、カップリング・コンデンサの効果を示す定性値が存在します。500 mA、-12 V の出力には、SS2PH10 出力整流器を使用しています。一方、3 A、+12 V の出力には、SS5P10 出力整流器を使用しています。これらの出力には、同じ負荷電流の組み合わせを使用して、カップリング・コンデンサが接続されている場合と接続されていない場合の両方について測定しました。表2 と図9 では、カップリング・コンデンサがない場合に増加する負の出力に従って結果を示しています。帰還ループは+12 V 出力のレギュレーションを厳密に実施します。このため、テスト中の変動は無視できます。

コンデンサが接続されていない場合、測定された-12Vレギュレーション帯域は $-12.8V \pm 13.7\%$ でした。

コンデンサが接続されている場合、-12 V レギュレーション帯域は $-12.2 V \pm 3.6\%$ でした。

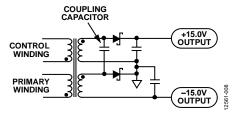

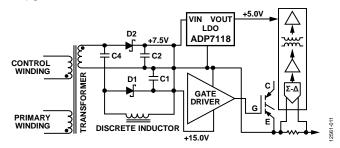

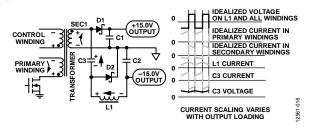

設計の次のステップでは、1つ以上の外部(ディスクリートまたは結合)インダクタを使用して、1つ以上のトランス出力巻線を置き換えます(図 10 を参照)。

図 10.1 つのトランス巻線を使用した デュアル出力フライバック電源

図 10 に示す変更を加えた回路は、図 8 の回路をベースにしていて、1 つのトランス巻線をディスクリート・インダクタで置き換えています。-15 V 出力は、Čuk 出力です。

図10の変更のメリットは、次のとおりです。

- 効率が高い

- 部品コストが低い

- 負荷レギュレーションの性能が高い

- 1つのトランス巻き線から2つのピンで複数の電圧を出力

図10の変更のデメリットは、次のとおりです。

- 追加のディスクリート・インダクタが必要

- 同じ電圧を出力する必要がある

この変更は、図6の回路と同様の性能を発揮しますが、1つの絶縁された領域で2つの出力を生成するのに必要なトランス・ピンの数を削減できます(合計2つ)。

図 11 に、トランスの巻線から 7.5 V を出力するモーター・ドライブ・アプリケーションを示します。コモン・ポイントは、負側に接続されています。このため、整流されたトランス出力は 7.5 V と 15 V になります。 7.5 V で LDO レギュレータを駆動して 5 V レールを生成し、15 V でユニポーラ・ゲート・ドライバを駆動します。

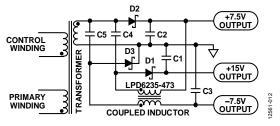

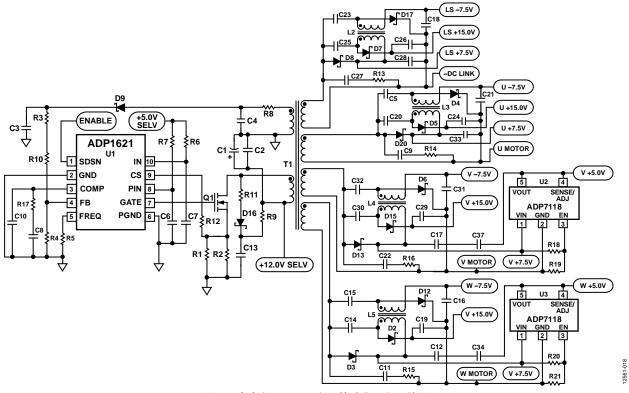

これら2つの出力は制限されていません。図12に示す回路では、2つの巻線を結合したインダクタ(Coilcraft LPD6235-473)を使用しています。3つの等しく整流された出力を直列接続して-7.5 V、+7.5 V、+15 Vを生成します。これは、図18に示す複数出力フライバック・コンバータ設計全体で使用されているアーキテクチャです。

図 11. 絶縁型ゲート・ドライブ用に 15 V、絶縁型モジュレータ 用に 5 V をサポートしているデュアル出力電源

図 11 の設計は図9 とほぼ同じですが、デモ・ボードで 7.5 V と 15 V を生成します。 7.5 V は 5 V 出力 LDO レギュレータに電力を供給して A/D コンバータを駆動します。

図 12. 絶縁型ゲート・ドライブ用に 15 V と 7.5 V、 絶縁型モジュレータ用に 7.5 V をサポートしている トリプル出力電源

## アプリケーション・ノート

図 12 の設計は図 10 とほぼ同じですが、結合インダクタを使用して、1 つのトランス巻線から3 つの出力レールを生成しています。 +15 V 電源レールはゲート・ターンオン・ドライブ用で、+7.5 V レールは+5 V LDO レギュレータに電力を供給します。-7.5 V レールはゲート・ターンオフ・ドライブ用です。

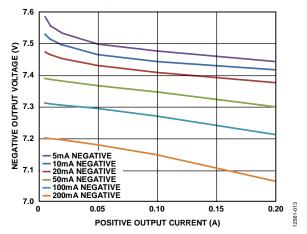

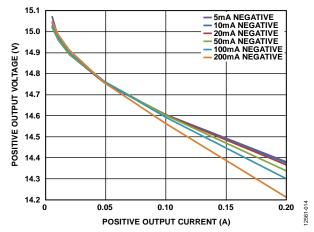

図 12 のバイアス・コンバータの負荷およびクロス・レギュレーションを +15 V 出力と -7.5 V 出力で、5 mA  $\sim$  200 mA の負荷範囲にわたって測定しました。図 13 と図 14 に、計算した結果のグラフを示します。これらの結果は、この方式が少なくとも 40:1 の負荷電流範囲にわたって、許容誤差の小さい出力電圧を維持できることを示しています。

図 13. -7.5 V 出力が測定された出力電圧レギュレーションと -7.5 V / +15 V で変化する負荷電流の関係(図 12 の回路)

図 14. +15 V 出力が測定された出力電圧レギュレーションと -7.5 V /+15 V で変化する負荷電流の関係(図 12 の回路)

表 3. 図 14 に示すバイアス・コンバータの負荷レギュレーションの測定値

| Output<br>(V) | Tested Current Range (mA) | Center Point (V) | Tolerance<br>(%) |

|---------------|---------------------------|------------------|------------------|

| +15           | 5 to 200                  | 14.64            | ±3.0             |

| -7.5          | 5 to 200                  | 7.326            | ±3.6             |

### 回路の理論と方式の比較について

フライバック、SEPIC、Čuk コンバータはいずれも、バック・コンバータまたはブースト・コンバータです。入力電圧の両端の巻線を切り替えて磁気コアにエネルギーを格納し、出力の両端にある同じ巻線または別の巻線を切り替えてエネルギーを提供することで、電力を変換します。(バック、ブースト、および他の方式は重要な点が異なり、通常は複数の出力に適していません)。これらはすべて同じ基本動作モードになっているため、電圧とデューティ・サイクルは、インダクタ両端の電圧・秒のバランスおよびコンデンサを流れる充電バランスに基づいています。巻数比を求めた後で適用される動作の式は同じです。多様なバック方式またはブースト方式の基本ブロックをさまざまな方法で組み合わせて、幅広い電流範囲にわたって優れたトラッキング性能を示す、比例した電圧を出力できます。

バック-ブースト・コンバータの連続導通モード (CCM) と不連続導通モード (DCM) 動作に関する式を以下に示します。

CCM 電圧変換の式は、次のとおりです。

$$V_{OUT} = \frac{D \times V_{IN}}{1 - D}$$

ここでDは、デューティ・サイクル。

DCM 合計出力電力(ワット)の式は、次のとおりです。

$$P_{OUT} = \frac{(D \times V_{IN})^2}{2 \times L \times f}$$

ここで、

f は周波数。

Lは並列インダクタンス (H) の合計。

DCM 電圧を抵抗負荷に変換する式は、次のとおりです。

$$V_{OUT} = \frac{D \times V_{IN} \times R^{0.5}}{(2 \times L \times f)^{0.5}}$$

ここでRは負荷抵抗( $\Omega$ )。

これらの SEPIC および Čuk 関連の設計で、カップリング・コンデンサは周波数 AC 電流を切り替える短絡インダクタンスを発生します。前述の式では、トランスと出力インダクタが並列になっていることを考慮してください。結合インダクタ(巻数の同じコアを有する複数の巻線)で、並列(相接続)になっている巻線またはすべての巻線のインダクタンスは同じです。通常は、結合インダクタについて公表されているインダクタンス値です。

図10、図11、図12に示すように、複数のインダクタまたはトランスを並列接続した場合(DC 結合またはAC 結合)、有効インダクタンス値は、次に示す並列接続された複数のインダクタの式によって決まります。

$$L_{p} = \frac{1}{(1/L_{1}) + (1/L_{2}) + ... + (1/L_{n})}$$

フライバック・トランスでは、コアの磁束はすべての巻線をリン クし、すべての巻線で「巻数あたりの電圧」が常に同じになりま す。このため、ある巻線によって生成された電圧を監視することで、いくつかの出力を調整できます。漏れインダクタンスは、1つの巻線において直列で動作するインダクタンスで、他の巻線とは共有されません。巻線をデカップリングし、フライバック・トランスの設計で最小化されます。これに対して、結合インダクタは、漏れインダクタンスが最小になるように設計したり、特定の漏れインダクタンスになるように設計したりできます。漏れインダクタンスが最小になるように設計された結合インダクタは、フライバック・トランスとして正常に機能します。漏れインダクタンスが最小になるように設計されていない結合インダクタは正常に機能しません。

巻線の合計インダクタンス Lは、相互インダクタンス Lm と漏れインダクタンス L°の合計です。

$$L = L_M + L^{\sigma}$$

巻線の相互インダクタンス  $L_M$  は、合計インダクタンス L と結合係数 k の積になります。

$$L_M = L \times k$$

通常、トランスには1次巻線と2次巻線の間にセーフティー・アイソレーションを備えていますが、結合インダクタにはセーフティー・アイソレーションがありません。ただし、例外もあります。

SEPIC コンバータと Čuk コンバータは、良好な磁気結合またはわずかな磁気結合のある結合インダクタ、または、磁気結合のないディスクリート・インダクタを使用できます。エネルギーの伝達は、カップリング・コンデンサに依存します。コンデンサに結合された巻線間の電圧スケーリングは、巻線の漏れインダクタンスによる大幅な影響を受けません。ただし、正しく動作させるには、連続電流または準連続電流を維持し、カップリング・コンデンサがAC電圧波形を駆動できるように、結合インダクタに漏れインダクタンスを組み込む必要があります。漏れインダクタンスが小さい場合、帰還ループのユニティ・ゲイン・クロスオーバーを大幅に下回る LC 共振周波数を得るには、コンデンサのサイズを大きくすることが必要になる場合があります。ディスクリート・インダクタの代わりに、結合インダクタを使用する主なメリットは、部品コストと PCB スペースを削減できることにあります。

このアプリケーション・ノートの例では、フライバック・トランスが絶縁を実現します。巻数比は1:1です(他の比率も使用できます)。あらゆるフライバックと同様、1次巻線と2次巻線の間に小さい漏れインダクタンスが必要になります。ただし、複数の出力を1つの絶縁された領域にリンクする SEPIC または Čuk カップリングの場合、電流の波形と領域内の電圧クロス・レギュレーションの条件は SEPIC コンバータや Čuk コンバータと同様になります。

## 複合フライバック、SEPIC、および ČUK コンバータの設計に関する 考慮事項

まず、フライバック・コンバータの設計について説明します。巻線の出力電圧 (例: 7.5 V または 15 V) を決定し、出力電力の合計から出力電流を求めます。

例えば、電流および電力の要件が表 4 に示す値の場合、単一出力の場合と同じようにトランスを設計できます。 1.5 W/7.5 V = 200 mA.

表 4. 領域の電力要件

| Output Rail | Volts          | Amps           | Watts |

|-------------|----------------|----------------|-------|

| V1          | +7.5           | +0.05          | 0.375 |

| V2          | +15            | +0.06          | 0.9   |

| V3          | -7.5           | -0.03          | 0.225 |

| Total       | Not applicable | Not applicable | 1.5   |

動作周波数は、トランス、インダクタ、およびセラミック・コンデンサのサイズに関連があります。通常、サイズが小さくなるに伴い、動作周波数は高くなります。ただし、200 kHz ~ 400 kHz を超える周波数ではトランスの漏れインダクタンスにより、損失が増加し、電圧レギュレーションが低下します。

実用的な最小漏れインダクタンスは、常にトランスの設計周波数に反比例して増減するわけではありません。通常、漏れインダクタンスに保存されるエネルギーは $L \times F/2$ であり、浪費されるだけです。電力はエネルギー  $\times$  周波数であるため、漏れインダクタンスによる電力損失は周波数に比例して増減します。

電力レベルと周波数の他に、トランスのピン配置と安全間隙が、最小のトランス・サイズを決定する要因となります。Rubadueの多層テフロンセーフティー・アイソレーションワイヤを使用して容易に手巻きできるようにPQ2625を選択しました。この設計は200kHzで動作します。

トランスと電源コンバータの設計に関する注意事項を以下に示します。

• 図 13、図 14、表 3 の波形の例で、これらの図に示すデューティ・サイクルは約 56%です。このような高いデューティ・サイクル(50% 近辺または 50%以上)で安定した CCM 動作を確保するには、傾き補償を増やす必要があります。傾き補償とは、電流モード PWM コントローラ IC によって使用される電流ランプに電圧ランプを追加したものです。通常、デューティ・サイクルが 45% 未満の場合、傾き補償はほとんど必要ないため、制御が容易になります。デューティ・サイクルが 20%~45%の場合が最も簡単になります。例として示している回路(入力 12 V、出力 7.5 V、ショットキー・ダイオード、巻数比 1:1)は、約 40%のデューティ・サイクルで動作します。

・ ショットキー出力整流器、連続導通モード (CCM) を備え、サイズと電力が最適化されたフライバック・トランスが最高の効率を発揮します。トランスの温度が高い場合にコアの飽和を防止できるように、ピーク負荷および最小入力電圧時のピーク・トランス磁束密度は0.2 T~0.22 T未満に抑える必要があります。ACピーク to ピーク磁束密度は、可能な限り高くする必要がありますが、許容されるコア損失によって制限されます。このため、このアプリケーション・ノートでの設計は、0.05 T~0.07 T (200 kHz 時、Ferroxcube 3F3 フェライト)のACピーク to ピーク磁束密度制限に基づいています。

PQ2625 コアを使用した例において、最小サイズは重要な要件ではありません。このトランスは手作業で簡単に作成できるように、低い漏れインダクタンスと合理的なコア損失で、十分な沿面距離と間隙を得られるように設計しました。電力レベルで一般的に必要とされるサイズよりもコアが大幅に大きくなることがトレードオフです。1次側、2次側、および出力巻線の巻数は、わずか4です。このようなわずかな巻数では、CCM に必要なインダクタンスを得ることはできません。このため、ポリエステル・フィルムを切断して作成した厚いスペーサ(0.001 インチ、0.025 mm)でコア・アセンブリに間隙を設けました。どの巻線でも、達成されたインダクタンスは約28  $\mu$ Hでした。コンバータは、通常の限界まで負荷がかかると、不連続導通モード(DCM)で動作します。巻数を増やすことで目的のインダクタンスが大幅に増えるため、トレードオフが悪化します。

図 15. デュアル出力フライバック・コンバータ、 トランスの巻線の電流と電圧

図 15 に示す複数出力フライバック・コンバータでは、トランスの合計アンペア-巻数を連続的に変化させることができます。ただし、波形の忠実度と電圧レギュレーションを維持するには、個別巻線の電流を瞬時に変化させる必要があります。トランス巻線での漏れインダクタンスを低くすることが重要です。この例では、トランスの巻数比は1:1:1:1で、理想ダイオードと12 V dc 入力を使用しています。

通常のフライバック方式の場合、すべての巻線が1つの磁気コアを共有し、コア磁束が合計アンペア×巻数の積に比例し、磁路のリラクタンスの逆数に従って増減します。独立したインダクタを使用する場合、独立した(共有されていない)コアが形成されます。カップリング・コンデンサは、トランスの巻線とインダクタの間を流れるあらゆる DC 電流をブロックするため、AC 電流のみが2つの磁気部品の間を通過します。コンデンサの値は十分に大きく、AC 電流によってコンデンサの両端に発生するリップル電圧は非常に小さいです。コンデンサがAC 短絡経路として機能し、回路動作の単純な分析でリップル電圧は無視できます。

図 15 に示す通常のフライバック方式の例で、トランジスタがオンのときにトランス出力巻線に電流は流れません。フライバックと Čuk コンバータを組み合わせたトランス(またはその他の方式) には当てはまりません。これは、出力巻線がカップリング・コンデンサを通じて L1 やその他のあらゆるインダクタを駆動する必要があるためです。結果として、トランス出力巻線の波形には、出力ダイオード電流とインダクタ磁化電流の両方の成分が含まれます。1 次巻線電流の波形は、通常のフライバックの場合と同様になり、インダクタンスはすべての磁気構造を並列で組み合わせたものになります。図 12 の例で、トランスのインダクタンスは約 28  $\mu$ H です。Coilcraft LPD6235 結合インダクタも同様に動作し、トランスのインダクタンスは並列等価値の 17.5  $\mu$ H に等しくなります。

図 16. デュアル出力フライバック・コンバータ、トランス巻線 の電流と電圧、単一 2 次トポロジ

図16に示す複合フライバック-Čukコンバータでは、低い漏れインダクタンスは効率的にエネルギーを伝達するために重要ですが、1つの電圧領域の出力間のクロス・レギュレーションにはほとんど影響を与えません。ダイオードD2電流の重要なAC成分は、インダクタL1ではなく、コンデンサC3を流れます。重要な浮遊インダクタンスは、D1とC1の経路、およびC3とD2の経路を通じて計測した値です。PCBレイアウトを慎重に行うことで、この浮遊インダクタンスは、通常のフライバック方式で使用されるトランスで発生する最小漏れインダクタンスよりも大幅に低くなります。

インダクタンス、コア損失、DC抵抗、および飽和電流に基づいて外部インダクタを選択します。通常、50kHz~100kHzの周波数でインダクタのピークtoピーク・リップル電流が定格飽和電流に近づいた場合、過剰なコア損失が発生します。可能であれば、Coilcraftなどのインダクタ・メーカーが提供しているコア損失計

算ツールを使用します。特定のサイズで高いインダクタンスを発生するワイヤの巻数を増やすと、リップル電流とコア損失が減少しますが、DC飽和電流が減少し、DC抵抗が増加します。

図 10 で、L1 の DC 電流は、-15 V の電圧に対応する出力電流です。図 11 で、DC インダクタ電流は、+15 V の電圧に対応する出力電流です。

図 12 で、結合インダクタの一方の側は +15 V に対応する電流を出力し、もう一方の側は -7.5 V に対応する電流を出力します。DC コア励起を決定するには、これら 2 つの値を追加します。これはコモンモード・チョークではありません。

Coilcraft と Cooper は、シングル・ソースとなる小型の結合インダクタ (Coilcraft LPD6235 など) を提供しています。12 mm の角形の結合インダクタは、Pulse、Wurth、Cooper、Coilcraft などのメーカー間で互換性のあるフットプリントになっています。

まず、サイクリック充電(IOUT/スイッチング周波数に等しい)に対して平均充電量が大きくなるように、カップリング・コンデンサの値を選択する必要があります。次に、充電量/容量を計算してからリップル電圧を求めます。この電圧は、DC電圧の数ペーセント(最大5%)を超えてはいけません。セラミック・コンデンサは、印加電圧とハンダ付け後の時間経過により、大量の容量を失います。このため、セラミック容量の定格について慎重に考慮してください。(村田製作所では、これらの係数をグラフ化するオンライン・ツールを提供しています)。この印加電圧による容量損失は、小型パッケージの  $\mathbf{C} \times \mathbf{V}$  定格が高いデバイスで特に当てはまります。出力コンデンサとカップリング・コンデンサに同じコンデンサ定格を使用すると便利です。

12561-017

図 17. ボビン・エクステンダによる プロトタイプ・フライバック・トランス

図 17 に、PQ2625 3F3 とボビン・エクステンダを使用し、10 mm の沿面距離を備えたトランスを示します。これが、図 18 に示すコンバータで使用したトランスです。

図 18. 完全なコンバータの簡略化した回路図

表 5. 完全なコンバータの部品表

| Item | Reference Designator | Value        | Description             |  |

|------|----------------------|--------------|-------------------------|--|

| 1    | C1                   | 100 μF       | Nichicon UCL1C101MCL6GS |  |

| 2    | C2                   | 1.00E-05     | 16 V, X5R, 1206         |  |

| 3    | C3                   | 10 nF        | 50 V, X7R, 0603         |  |

| 4    | C4                   | 100 pF       | 50 V, NP0, 0603         |  |

| 5    | C5                   | 2.2 μF       | 0805, X5R, 25 V         |  |

| 6    | C6                   | 1.0 μF       | 16 V, X5R, 0603         |  |

| 7    | C7                   | 1.0 μF       | 16 V, X5R, 0603         |  |

| 8    | C8                   | 10 nF        | 50 V, X7R, 0603         |  |

| 9    | C9                   | 100 pF       | 50 V, NP0, 0603         |  |

| 10   | C10                  | Do not place | Do not place            |  |

| 11   | C11                  | 100 pF       | 50 V, NP0, 0603         |  |

| 12   | C12                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 13   | C13                  | 100 nF       | 50 V, X7R, 0603         |  |

| 14   | C14                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 15   | C15                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 16   | C16                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 17   | C17                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 18   | C18                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 19   | C19                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 20   | C20                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 21   | C21                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 22   | C22                  | 100 pF       | 50 V, NP0, 0603         |  |

| 23   | C23                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 24   | C24                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 25   | C25                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 26   | C26                  | 2.2 μF       | 0805, X5R, 25 V         |  |

| 27   | C27                  | 100 pF       | 50 V, NP0, 0603         |  |

# アプリケーション・ノート

| Item     | Reference Designator | Value                       | Description             |

|----------|----------------------|-----------------------------|-------------------------|

| 28       | C28                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 29       | C29                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 30       | C30                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 31       | C31                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 32       | C32                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 33       | C33                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 34       | C34                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 35       | C37                  | 2.2 μF                      | 0805, X5R, 25 V         |

| 36       | D2                   | MBR0560                     | Micro Commercial        |

| 37       | D3                   | MBR0560                     | Micro Commercial        |

| 38       | D4                   | MBR0560                     | Micro Commercial        |

| 39       | D5                   | MBR0560                     | Micro Commercial        |

| 40       | D6                   | MBR0560                     | Micro Commercial        |

| 41       | D7                   | MBR0560                     | Micro Commercial        |

| 42       | D8                   | MBR0560                     | Micro Commercial        |

| 43       | D9                   | LL101A                      | Vishay                  |

| 44       | D12                  | MBR0560                     | Micro Commercial        |

| 45       | D13                  | MBR0560                     | Micro Commercial        |

| 46       | D15                  | MBR0560                     | Micro Commercial        |

| 47       | D16                  | LL103A                      | Vishay                  |

| 48       | D17                  | MBR0560                     | Micro Commercial        |

| 49       | D20                  | MBR0560                     | Micro Commercial        |

| 50       | L2                   | LPD6235-473                 | Coilcraft               |

| 51       | L3                   | LPD6235-473                 | Coilcraft               |

| 52       | L4                   | LPD6235-473                 | Coilcraft               |

| 53       | L5                   | LPD6235-473                 | Coilcraft               |

| 54       | Q1                   | IRLML0060                   | International rectifier |

| 55       | R1                   | Do not place                | Do not place            |

| 56       | R2                   | $0.033 \Omega, 5\%$         | 0805, Susumu            |

| 57       | R3                   | 499 kΩ, 1%                  | 0603<br>0603            |

| 58       | R4                   | 100 kΩ, 1%                  | 0603                    |

| 59       | R5                   | 100 kΩ, 1%                  | 0603                    |

| 60       | R6                   | 10 Ω, 1%                    | 0603                    |

| 61       | R7                   | 10 Ω, 1%                    | 0603                    |

| 62       | R8                   | 357 Ω, 1%                   | 1206                    |

| 63       | R9                   | 619 Ω, 1%                   | 1206                    |

| 64       | R10                  | 2.00E+04                    | 1206                    |

| 65       | R11                  | 8.2 Ω, 5%                   | 1206                    |

| 66       | R12                  | 200 Ω, 1%                   | 0603                    |

| 67       | R13                  | Do not place                | 1206                    |

| 68       | R14                  | Do not place                | 1206                    |

| 69       | R15                  | Do not place                | 1206                    |

| 70       | R16                  | Do not place                | 1206                    |

| 71       | R17                  | 4.99 kΩ, 1%                 | 0603                    |

| 72       | R18                  | $35.7 \text{ k}\Omega$ , 1% | 0603                    |

| 73       | R19                  | 10 kΩ, 1%                   | 0603                    |

| 74       | R20                  | 35.7 kΩ, 1%                 | 0603                    |

| 75       | R21                  | 10 kΩ, 1%                   | 0603                    |

| 76       | T1                   | Transformer                 | Described in text       |

| 77       | U1                   | ADP1621ARMZ                 | 10-pin MSOP             |

| 78       | U2                   | ADP7118AUJZ-5.0             | 5-pin TSOT              |

| 79<br>79 | U3                   | ADP7118AUJZ-5.0             | 5-pin TSOT              |

| 17       | US                   | ADI /110AUJZ-3.0            | J-pin 15O1              |

#### 結論

このアプリケーション・ノートでは、産業用モーター・ドライブのハイサイド/ローサイド・ゲート・ドライブおよび電流検出IC用に絶縁されたバイアス電源を生成する方法について説明しました。チャージ・ポンプやブートストラップ電源などのメリットと制限事項についても取り上げました。また、トランス絶縁の方式は、効率、柔軟性、および安全バリアに関して明白なメリットをもたらすことについても説明しました。フライバック方式は、これらのバイアス電源の複数の出力特性に最適です。ただし、複数の出力または消費型のレール分割のあるゲート・ドライバ・バイアス電源向けのフライバック・コンバータ・ソリューションは、高いトランス・ピン使用率と低い効率による制限を受けます。さらに、代表的な2次検出レギュレーション手法では、不十分なクロス・レギュレーションによる問題の影響を受けます。そこで、これらの制限事項を軽減するソリューションを提案しました。1

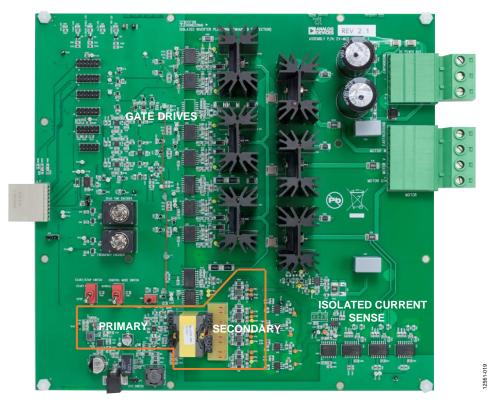

次側検出を使用することで、クロス・レギュレーション全体を大幅に向上できます。巻線の間に2次側カップリング容量を追加して、レギュレーションを大幅に向上させます。トランスの巻線をディスクリート・インダクタまたは結合インダクタと交換すれば、トランスのピン配置に関する要件を軽減できます。クロス・レギュレーションの結果を示し、結合インダクタ出力タイプの完全な回路図と部品表を提供しました。ディスクリート・インダクタ・バージョンも最大800 VのDC バスで実行される完全な3相インバータ・プラットフォームとして実装しました。

図 19 に、EV-MCS-ISOINV-Z 絶縁インバータ・プラットフォームにおけるバイアス回路の写真を示します。このプラットフォームは、アナログ・デバイセズの Web サイト (www.analog.com/EVAL-ISO-INVERTER-MC) から注文できます。

図 19.3 相モーター制御インバータ、バイアス電源付き