# アプリケーション・ノート

AN-1248

### SPI インターフェイス

著者: Miguel Usach

#### はじめに

SPIバス・インターフェイスは、用途の広い構成で比較的高い送信レートが可能であるため、同期データ伝送に広く採用されています。

SPIは事実上の業界標準になっていますが、公式に規定されたものではありません。1つの部品を最大限活用することができるため、これを利点と見なすことがありますが、異なる部品間の相互接続は複雑になってしまいます。

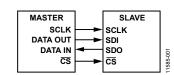

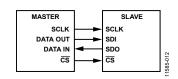

SPIバスは単方向の4本の線から構成されています。これらの線の名称は、部品間で、更に同じ製品範囲内でさえ、異なることがあります。

- インターフェイス・イネーブル: CS、SYNC、ENABLEなど

- データ入力: SDI、MISO (マスタ用)、MOSI (スレーブ用) など

- データ出力: SDO、MISO (スレーブ用)、MOSI (マスタ用) など

- クロック:SCLK、CLK、SCKなど

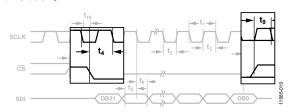

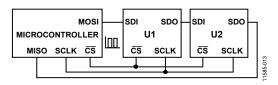

図 1 に示すように、各ピンの信号方向について混乱のないように規則に則った名前を定義することから始めることが重要です。

3 本の線しか使用しないこともあります。例えば、DAC ではデータのリードバックが不要な場合があり、ADC ではマスタからのデータの送信が不要の場合があります。これらの場合、接続は3線式インターフェイスとして定義することができます。

#### マスタースレーブ間の互換性

最初のステップは、マスタ-スレーブ間接続の互換性を確保することです。SPIインターフェイスは公式な仕様でないため、マスタからスレーブへのデータ、または逆向きのデータがそれぞれの仕様を満たすことが重要です。

データはクロックに同期していますが、 $\overline{CS}$ は同期または非同期のことがあるため、 $\overline{SPI}$ は完全な同期インターフェイスではありません。

完全な同期インターフェイスでは、エッジはサンプリング・エッジと駆動エッジに分けられます。駆動エッジでは、データをバス上で更新できます。サンプリング・エッジでは、SDI/DATA IN ピンのデータが読みこまれます(サンプルされます)。

実用的な点から、バス上のデータはサンプリング・エッジ以外 の任意のタイミングで更新することができます。

SPI インターフェイスでは、4 つの送信モードを定義しています。マスタ側は 4 つのすべてのモードをサポートできる必要がありますが、マスタが特定のモードと互換性を持たないこともあるため、これを事前に確認しておく必要があります。SPIモードの相互接続のセクションで説明するように、これはインバータの使用により解決することができます。

大部分の部品では、スレーブ動作でのモード設定はできず、1つの動作モードでのみ動作します。ただし、最大 2 つのモードで動作するものもあります。

図 1. SPI の基本的な接続

# アプリケーション・ノート

## AN-1248

## 目次

| はじめに1               | バス上のデータが更新されるタイミングは? |

|---------------------|----------------------|

| マスタ–スレーブ間の互換性1      | その他の考慮すべき事項は?        |

| 改訂履歴2               | <b>SPI</b> モードの相互接続  |

| スレーブ側で使用される伝送モードは?3 | 接続                   |

### 改訂履歴

| 9/15–Rev. 0 to Rev. A                       |   |

|---------------------------------------------|---|

| Changes to SPI Mode Interconnection Section | 6 |

7/13-Revision 0: Initial Version

#### スレーブ側で使用される伝送モードは?

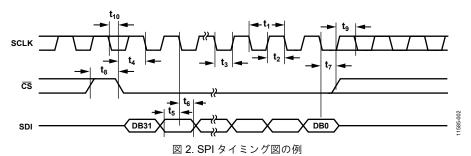

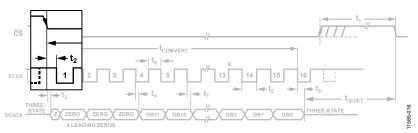

図 2 に示すように、タイミング図では、複数のラインと名称を使用しています。

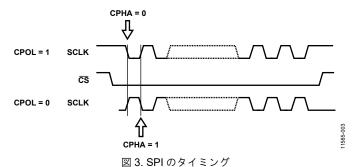

モードは、データ伝送が開始される( $\overline{\text{CS}}$ をロー・レベルにする)ときの SCLK レベル(場合により極性(CPOL)と呼ばれる)と、サンプリング・エッジ(位相(CPHA)と呼ばれる)によって決定されます(図 3 参照)。位相は極性に対する相対的なもので絶対値でないことに注意してください。SPIモードを表 1に示します。

表 1. SPI のモード

| Mode  | Polarity (CPOL) | Phase (CPHA) |

|-------|-----------------|--------------|

| 0     | <b>∳</b> /∖_    | <u>_</u>     |

| 1     | <b>∳</b> /∖_    | l d          |

| <br>2 | <b>₽\</b>       | 7            |

| 3     | <b>Ā</b>        |              |

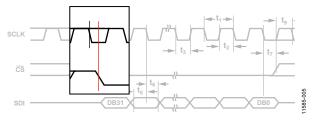

これらのモードを定義することは比較的容易です。図 4 に示すように、 $\overline{CS}$ の立下がりエッジと SCLK を結ぶ線が存在します(図 4 参照)。

図 4. 極性モード

この図のケースでは、SCLK はハイ・レベルまたはロー・レベルであることができ、制約はありません。

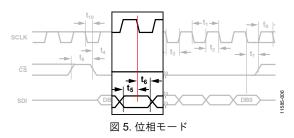

次に SDI の図には、セットアップとホールドの 2 つのタイミングで囲まれる区間が必要です。2 つのタイミングは、バス上にデータが存在し有効でなければならない、サンプル・エッジの前後の時間を意味し、両タイミングはサンプリング・エッジを基準タイミングとして使用します(図 5 参照)。

この例では、サンプル・エッジは立下がりエッジです。

以上と表1から、スレーブ・デバイスはモード1およびモード2に対応できます。

#### バス上のデータが更新されるタイミングは?

SDO を使って、データをスレーブからマスタへ転送、あるいはマスタからスレーブへ転送します。データは何時でも更新できますが、特に2つの方法が採用されています。

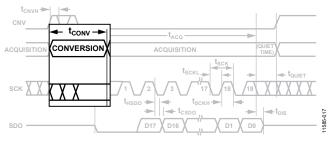

1つ目の方法は、駆動エッジで SDO/DATA OUT ピンを更新する方法です(図 7 参照)。

もう 1 つの方法は、サンプリング・エッジの数ナノ秒後に SDO/DATA OUT ピンを更新する方法です(図 8 参照)。

2 つの方法にはそれぞれに技術的な理由がありますが、トレードオフを理解することが重要です。

マスタでは最初の方法が使われます。これは SDO ドライバが高速の切り替えをサポートするように設計されているためです。

スレーブではマスタに比べて駆動能力の低い SDO ドライバを内蔵しているため、使用する方法はデータ転送レートに依存します。

SDO 信号を駆動エッジで更新する場合、信号はサンプリング・エッジの数ナノ秒前に安定している必要があるため、ピンは信号の更新にクロック周期の1/2以下の時間しか使うことができません。

正しいリードバックをサポートするためには、サンプリング・エッジの前に信号が確実に安定するようにするため SCLK を減らす必要があります。

この例では、最大変化時間を36nsとしています。

SCLK 立上がりエッジから SDO データ有効 までの時間 t<sub>9</sub> 36ns

これは、最大サイクル時間が 36ns + マスタ・セットアップ時間 (10ns と仮定) = 46 ns となるため、リードバックの最大 SCLK 周波数は約 10MHz となることを意味します。

サンプリング・エッジの数ナノ秒後にピンを更新する場合、 SCLK 周波数を低下させずにリードバックを可能にするように バス上で信号の安定な値を確保するには、スレーブは SCLK の ほぼ全周期を必要とします。

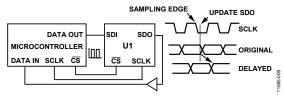

主なトレードオフは、マスタ側が低速の場合にあります。これは、サンプリング・エッジの後の数ナノ秒しかピン上にデータが安定していないため、マスタのホールド時間の制限に反する危険性があるからです。この問題は、ホールド時間が 15 ns 以上に大きくなると発生します。この場合、DATAIN ピンの新しいデータを必要なだけ遅延させるロジック・ゲートを使うことが推奨されます(図 6 参照)。

図 6. イネーブル時間

幾つかのゲート技術と NOR ゲートの伝搬遅延(代表値)を表2に示します。

表 2. ゲート技術と伝搬遅延

| 技術  | 伝搬遅延  |

|-----|-------|

| AHC | 4.4ns |

| HC  | 9ns   |

| HCT | 11ns  |

図 7. SDO 駆動エッジでの更新

図 8. 遅延 SDO 更新

#### その他の考慮すべき事項は?

#### イネーブル時間

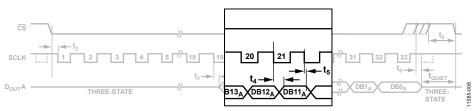

イネーブル時間は、SPI インターフェイスをイネーブルして データの受信または送信を可能にする速さを決定します。これ は一般にSCLKサンプリング・エッジと呼ばれます(図9参照)。

#### ディスエーブル時間

ディスエーブル時間は、SPI をディスエーブルして新しく発生するサンプリング・エッジの変化を無視する速さを決定します(② 9 参照)。

図 9. イネーブル時間とディスエーブル時間

#### 変換開始信号としてのCS

いくつかの ADC では、ピン数を減らすためや、小型パッケージへの組み込み、あるいは単に配線の複雑さを減らすために、1本のピンを複数の機能で共用しています。

$\overline{\text{CS}}$ を使って内部で変換開始信号を発生させる場合、2 つの方法があります。

#### 1つ目の方法

SCLK 信号を内部クロックとして使用するため、連続的な SCLK が必要です。この場合、SCLK の周波数は最大値と最小値の間に制限されます(表 3 参照)。

表 3. SCLK 周波数制限の例

| パラメータ | 最小値  | 最大値 | 単位  | 説明       |

|-------|------|-----|-----|----------|

| fsclk | 0.01 | 20  | MHz | SCLK 周波数 |

下に説明するイネーブル時間に似たタイミングの制約が、図 10 のようにあります。さもないと、マスタがサンプリング・エッジを正しく発生できず、あるいは変換が失敗します。

図 10. 変換時の連続 SCLK

#### 2つ目の方法

この例ではデバイスは変換クロックを内蔵しています。この場合、LSB ビット変換へのデジタル・フィードスルーの影響を小さくするため、SCLK パルスを発生しないことが推奨されます(図 11 参照)。

図 11. 変換時に静かな SCLK

SPIインターフェイスを FPGA ではなくハードウェアで構成する場合、SCLK ピンと $\overline{CS}$ ピンを正確に制御することは不可能です。この場合は、GPIO を $\overline{CS}$ として使用して、 $\overline{CS}$ と SCLK の関係を正確に制御することが推奨されます。

#### 変換レディ・ピンとしての SDO

ADC によっては、SDO が 2 つの機能を持っています。これは一般に SDO/ $\overline{RDY}$ と表されています。SDO ピンが $\overline{CS}$ によりディスエーブルされ、変換が完了するまで高インピーダンスを維持します。変換が完了したとき、このピンはロー・レベルになって、変換の終了を表示します。

#### SPI モードの相互接続

コントローラをスレーブが使用する特定の SPI モードに設定できないため、または同じ SPI モードですべてのデバイスを動作させる必要があるため(すなわちデイジーチェーン・モード)、モードを外部から変更しなくてはならないことがあります。

次の2つのケースを考えます。

モードが相補的 (MODE1 = MODE3 または MODE0 = MODE2) の場合

SCLK ラインにインバータ・ゲートを使用すると、問題は解決されます。

• モードが相補的でない場合 この場合の解決策は少し複雑になります。インバータとフ リップフロップを使用するため、タイミング問題が生ずるの でこれを回避することが推奨されます。

#### 接続

SPI インターフェイスでは、1 個または複数のスレーブをマスタから制御する様々な接続が可能です。

#### スタンドアロン接続

この構成では、1個のスレーブと1個のマスタのみが存在します (図 12 参照)。

図 12. スタンドアロン構成

#### デイジーチェーン接続

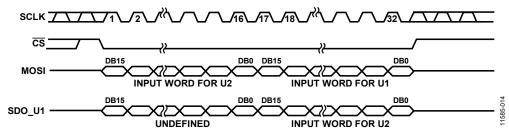

この構成では、1個のマスタと直列に接続された複数のスレーブが存在します(図13参照)。

図 13. デイジーチェーン構成

この構成の主な利点は、必要な接続ライン数が少なくなることです。

このモードで動作させる場合、後続デバイス間のライン伝搬遅延のため、クロック周期を大きくする必要が生じる可能性があります。更に、所要クロックは U1 と U2 の和であるため、クロック数を増やす必要があります。

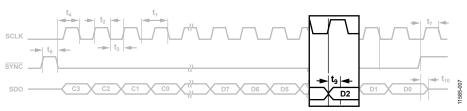

デイジーチェーン構成での代表的な送信を図14に示します。先頭のデータ・ワードは接続されたマスタから最も遠いスレーブに、最終のデータ・ワードは最も間近のスレーブに、それぞれ割り当てられます。

デイジーチェーン・モードに設定できるデバイスがありますが、 デフォルトでは、デバイスはスタンドアロン・モードでパワー アップします。すなわち、そのままでは SDO ピンはデータを出 力しません。

この場合、このデバイスをチェーンの先頭に置いて、デバイスに直接書込みを行ってデイジーチェーン・モードをイネーブルすることが推奨されます。モードをイネーブルする前には SDO は高インピーダンスであるため、SDO ピンにプルアップ (またはプルダウン) 抵抗を接続して、チェーン内の 2 番目のデバイスへ転送されるデータを制御することを推奨します。

SDO ピンを複数の機能 SDO/RDYに使用する場合、同じ問題が生じます。プルアップ抵抗を接続して、電気的問題を回避し、RDY機能の使用を続けることが推奨されます。

図 14. デイジーチェーンのタイミング図

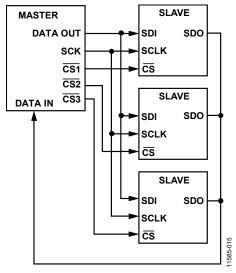

#### 並列構成

この構成では、1個のマスタと並列に接続された複数のスレーブが存在します(図15参照)。

図 15. 並列構成

この構成では、SCLK と SDI がすべてのデバイス内で共用されます。回路(またはパターン)の寄生容量があるため、クロック周期を単体の場合より少し大きくすることが推奨されます。

この構成での注意として、例えばデバイスをデイジーチェーン・モードに構成した場合のように、幾つかのデバイスでは SYNCと同期して SDO をディスエーブルすることはできません。

この場合は、電気的問題を回避するため、SDO ピンをバスに接続しないことが推奨されます。あるいは、SDO ピンをディスエーブルできる場合、直列抵抗を SDO ピンに接続して、最初の送信の電気的問題を最小限に抑え、開始時に SDO ピンをディスエーブルします。

注: