# アナログ電子回路技術ノート

# フォトダイオード・アンプ(電流電圧変換)の周波数特性を考える(前編)

OP アンプを高速なものに変えても周波数特性が思ったほど伸びない理由は

著者: 石井 聡

### はじめに

フォトダイオード・アンプ(電流電圧変換)回路は、簡単そうでとても奥の深い回路です。その考察とか解析で最初にひっかかるところが、周波数特性とノイズ特性ではないでしょうか。実験とかシミュレーションしていただくと分かるのですが、周波数特性を伸ばそうと、高速OPアンプに変更しても、思ったほど特性が改善しないのです。「なぜだ?」と思うところではないでしょうか。ノイズ特性もどう考えていいか、壁にぶち当たるのではと思います(この技術ノートでは解説しませんが)。

今回はその周波数特性の考え方について、前回までの技術ノートで示したブロック線図の考え方を活用して、解きほどいていきたいと思います。

## 社会人駆け出しのころに抱いた疑問は 30 年以上 の時空を超えて

いろいろなところで私の若い(初級)の頃の話題として申し上げる話しなのですが、私は社会人駆け出しのころ、フォトダイオード・アンプの設計をしていました。「設計」だなんて高尚なものではなく、実際はフォトダイオード増幅回路の基板を作っていた程度だったかもしれません。そのときに感じていたフォトダイオード・アンプへの疑問が3つありました。

- ① なんだか思ったほど周波数特性が伸びていないような気がする

- ② フォトダイオード・アンプは電流を電圧に変換する回路だが、この周波数特性はどのように考えるのか

- ③ なんだか出力波形がノイズっぽいような気がする

現場で設計していたこの頃は知恵もなく、ましてやなんとなく、ぼんやりと感じていただけでした。そしてこれらをどのように理論的に考え、どのように解決していけばよいか、そのとっかかりさえも見つけることができませんでした。なにせ「電流を電圧に変換する」回路ですから、初級レベルには及びもしない話しだったものです。図 1 は当時購入した OP アンプの参考書です [1]。これを読んでかなり勉強した記憶があります…。

以降、RF(高周波)の設計を長いことおこない(またここでは PLL についての疑問が出てきたのですが)、アナログ・デバイセズに入社後に、この若いころに疑問に思っていたことを解析してみようと思いました。それこそ「解析に没頭」できるような時間的余裕もありませんでしたが、各種の書籍やアプリケーション・ノートを見たり、横道にそれたり、中断したり、試行錯誤をしながら、少しずつの合間時間を活用して、上記①~③について考えをまとめていきました。アナログ・デバイセズの生活でも結局、この技術ノートとしてまとめられるレベルには数年がかかったかもしれません…。また PLL についての疑問も自己解決することができました。PLL は大学 4 年時の研究テーマでもありましたから、さらに昔からの疑問でもありました。

図 1. 駆け出しのころに勉強した参考書 [1]

### さらに疑問を増幅するシミュレーション結果

アナログ・デバイセズの生活でのとある日、とあるセミナ資料を作ろうと SPICE シミュレーションを行いました。少し前の話しなので LTspice ではなく、当時の公式シミュレータ ADIsimPE (現在でも ADIsimPE は公式です)を用いていました。そのときに進めた検討経過を、まずは以降でLTspiceを用いて再現してみます。

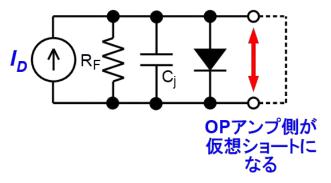

フォトダイオードから得られる電流を電流電圧変換して取り出すフォトダイオード・アンプを作る場合、回路は図 2 のように端子間が仮想ショート状態で動作します。またこのときフォトダイオードは、電流源と、無視できるほどの並列高抵抗( $G\Omega$ 以上)と、ダイオードとしてのPN接合容量 $C_j$ でモデル化できます。これも同図中に示してあります。

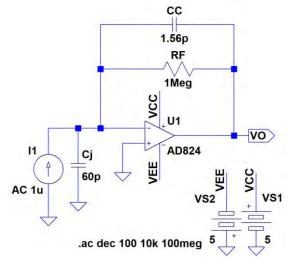

LTspice のシミュレーション回路図を図 3 に示します。OP アンプはJFET 入力 OP アンプ AD824 を使用しています。AD824 をご紹介しておきましょう。

アナログ・デバイセズ株式会社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。 ©2020 Analog Devices, Inc. All rights reserved.

Rev. 0

本 社/〒105

社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

電話 03(5402)8200

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 電話 06 (6350) 6868

AD824 オペアンプ、クワッド、単電源動作、レール to レール出力、低消費電力、FET 入力

https://www.analog.com/jp/AD824

#### 【概要】

AD824 は、レール to レール出力を特長とした FET 入力の 単電源動作クワッド・オペアンプです。FET 入力とレール to レール出力という2つの特長を備えているので、低入力 電流が第一条件となる低電圧アプリケーションで幅広く使 用できます。

AD824 は単電源 3V から両電源±15V までの動作が保証されています。AD824AR-3V は 3V でパラメータ性能が保証されています。

アナログ・デバイセズの CB プロセスで製造し、独自の入力段を備えているため、入力電圧範囲を負電源電位以下や正電源電位に安全に拡張することができ、位相反転やラッチアップ現象がまったく生じません。電源の 15mV までの出力電圧振幅が可能で、350pF までの容量性負荷を発振なしで駆動できます。

AD824 は GB 積 2 MHz です。フォトダイオードの PN 接合容量 $C_j$  を 60pF とし、安定性を増加させるため、帰還抵抗に並列に小容量の安定化容量 $C_C$  (補償容量) 1.56pF を接続してあります。な

図 2. フォトダイオード・アンプは端子間が 仮想ショート状態で動作する

図 3. GB 積 2MHz の AD824 を用いた LTspice の シミュレーション回路図

図 4. 図 3 の AD824 でのシミュレーション結果

おこの容量は、次回の技術ノートで「ブートストラップによる 高速化」の説明をする都合から、位相余裕を 40° 程度と若干少 なめにして、周波数特性のピーキングが出るように、ピーキン グが 3 dB になるように設定してあります。

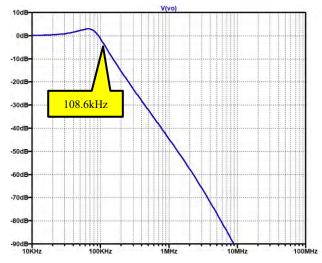

図 3 の周波数特性をシミュレーションした結果を図 4 に示します。-3dB カットオフ周波数は 108.6 kHz となっています。

### 高速な OP アンプに変えてみる

続いてフォトダイオード・アンプの周波数特性を向上させるべく、OPアンプをより高速な JFET 入力 OPアンプ AD8066 に交換してみます。AD8066 もご紹介しておきましょう!

AD8066 ローコスト・ビデオ・アンプ

https://www.analog.com/jp/AD8066

### 【概要】

AD8065/AD8066 FastFETTM アンプは、きわめて高性能で使いやすい FET 入力を備えた電圧フィードバック・アンプです。AD8065 はシングル・アンプで、AD8066 はデュアル・アンプです。この FastFETアンプは、アナログ・デバイセズ独自の XFCB プロセスにより、超低雑音の動作  $(7.0nV/\sqrt{Hz}\ E)$  ときわめて高い入力インピーダンスを実現しています。

AD8065/AD8066は、5~24Vの広い電源電圧範囲、単一電源で動作可能な能力、および145MHzの帯域幅を備え、さまざまなアプリケーションで機能するように設計されています。汎用性をさらに向上するため、アンプには、レールtoレール出力も備わっています。

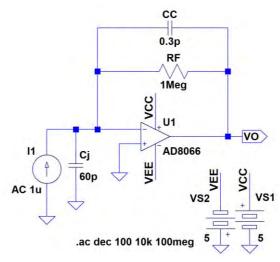

AD8066のGB積は65MHzであり、AD824の35倍のGB積です。 これで同様に周波数特性をシミュレーションしてみます。回路 図を図5に示します。なお安定化容量 $C_C$ は AD824のケースと同 じ位相余裕になるように修正してあります(0.3pF)。

### 思ったように周波数特性が伸びない…

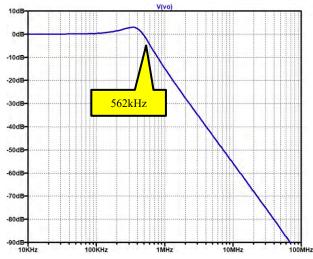

シミュレーション結果を図6に示します。より高速なOPアンプAD8066に変えても、思ったように周波数特性が伸びません…。 -3dB カットオフ周波数は562 kHzで、AD824の108.6 kHz から5 倍程度しか変わっていません。35 倍のGB 積のOPアンプに交換すれば、相応の周波数特性が得られるはずですが、これは何故なのでしょうか…。

Rev. **0** -2/7 -

図 5. GB 積 65MHz の AD8066 を用いた LTspice の シミュレーション回路図

図 6. 図 5 の AD8066 でのシミュレーション結果

この理由は、実はフォトダイオードの接合容量 $C_j$ が周波数特性を大きく低下させる支配的要因だからなのです。このなりたちをこの技術ノートのゴールとして説明を進めて参りましょう。

# まず電流電圧変換回路の周波数特性検討モデルを 考えてみる

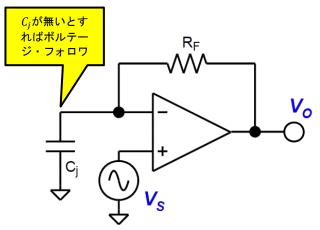

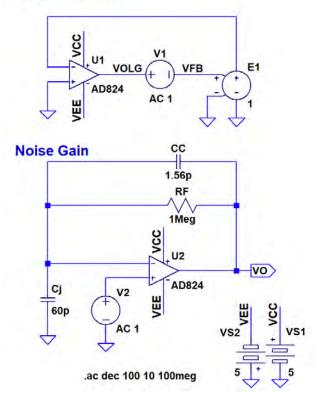

周波数特性を検討するために、図3や図5の回路をノイズ・ゲインを得る回路に書き換えたものを図7に示します。

一般的に OP アンプ増幅回路の周波数特性は、その回路のノイズ・ゲインで決まります。この回路でのノイズ・ゲインを求めるには、同図のように図 3 や図 5 の電流源を取り去り(もし電圧源だったら取り去ったのちにそこをショートし)、非反転入力端子に信号源を挿入し、その信号源から出力に現れる信号増幅率として定義します。

もしこの回路で PN 接合容量 $C_j$ がないとすれば、電流電圧変換回路のノイズ・ゲインはボルテージ・フォロワと同じになります。端的な見方をすると「電流電圧変換回路の増幅率周波数特性はボルテージ・フォロワと同じ」とも言えます。しかし残念ながら PN 接合容量 $C_i$ が存在していることから、これがノイズ・ゲイ

ンつまり電流電圧変換回路の増幅率周波数特性に影響を与えて しまいます。

さて、この回路の周波数特性はどうなるでしょうか。ステップ・バイ・ステップで考えていきましょう。

## フォトダイオード・アンプのブロック線図を描い てみる

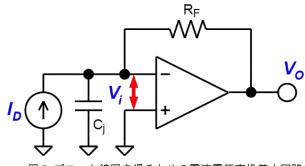

図 3 や図 5 の回路をより理論的に検討してみましょう。これまでのふたつの技術ノート TNJ-062 [2]と TNJ-063 [3]で示したように、この回路をブロック線図で考えてみます。図 3 や図 5 を書き換えた図 8 の回路を 2 条件に分けて、それぞれを「重ね合わせの理」を用いて合成する手順により、ブロック線図を得てみます。なおこの検討では安定化容量 $C_C$ は無視しています。

# 電圧源・電流源がひとつだけ有効な状態でそれぞれ計算する

まず図8の出力電圧Voを

$$V_0 = 0$$

とします。入力電流(フォトダイオードの電流)を $I_D$ 、OP アンプの反転入力端子の電圧(端子間電圧)を $V_{i1}$ とすると、

$$V_{i1} = \frac{R_F X_{Cj}}{R_F + X_{Cj}} I_D \tag{1}$$

ここで $X_{ci}$ は接合容量 $C_i$ のリアクタンス

$$X_{Cj} = \frac{1}{j2\pi f C_i} \tag{2}$$

つづいて同図のフォトダイオードの電流源Inを

$$I_D = 0$$

図 7. 電流電圧変換回路のノイズ・ゲインを得る回路 (周波数特性を考えるため)

図 8. ブロック線図を得るための電流電圧変換基本回路

Rev. **0** -3/7 -

# アナログ電子回路技術ノート

TNJ-064

として考えると、この条件での OP アンプの反転入力端子の電圧 (端子間電圧)  $V_{12}$ は

$$V_{i2} = \frac{X_{Cj}}{R_F + X_{Cj}} V_0 \tag{3}$$

となります。

#### 重ね合わせの理を用いる

重ね合わせの理により、本来の反転入力端子の電圧(端子間電圧) $V_i$ を得ると

$$V_i = V_{i1} + V_{i2} = \frac{R_F X_{Cj}}{R_F + X_{Cj}} I_D + \frac{X_{Cj}}{R_F + X_{Cj}} V_0 \tag{4}$$

OP アンプのオープン・ループ・ゲインをAとすれば

$$V_O = -AV_i \tag{5}$$

またβを帰還率とし

$$\beta = \frac{X_{Cj}}{R_F + X_{Cj}} \tag{6}$$

とすれば (なお $\beta$ はリアクタンス $X_{cj}$ を含んでいますから周波数依存性があります)、

$$-\frac{V_O}{A} - \beta V_O = \frac{R_F X_{Cj}}{R_F + X_{Cj}} I_D \tag{7}$$

この左辺は

$$-\left(\frac{1}{A} + \beta\right)V_O = -\frac{1 + A\beta}{A}V_O \tag{8}$$

となり、あらためて式(7)に戻ると、

$$-\frac{1+A\beta}{A}V_O = \frac{R_F X_{Cj}}{R_F + X_{Cj}}I_D \tag{9}$$

Voについて解くと

$$V_O = \frac{A}{1 + A\beta} \cdot \left( -\frac{R_F X_{Cj}}{R_F + X_{Cj}} I_D \right) \tag{10}$$

ただし

$$\beta = \frac{X_{Cj}}{R_F + X_{Cj}} \tag{6)再掲$$

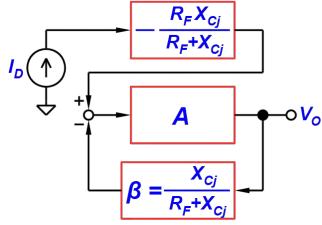

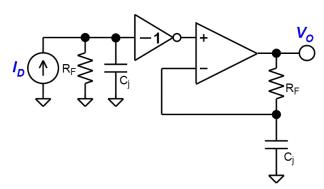

これは図 9 のようにブロック線図として表せます。電流 $I_D$ は、上側のボックスで $R_F$ と $C_J$ の並列接続で電圧に変換され、下側のボックスで帰還率 $\beta$ をもつ非反転増幅回路で電圧増幅されます。この下側のボックスのブロックの考え方は TNJ-062 [2]での説明のとおりでもありますし、一般的な帰還システムの伝達関数でもあります。さらにこの図 9 を回路図的に表してみると、図 10 のようになります。

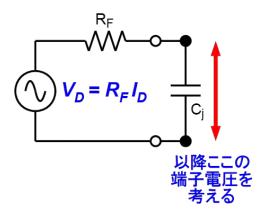

ここでノートン・テブナン変換により図  $10 \, \sigma I_D \, \mathcal{E} R_F$ は電圧源

$$V_D = R_F I_D$$

に、 $R_F$ が出力抵抗として直列接続されたモデルとして図 11 のように表すことができます。図 11 ではフォトダイオードの接合容量 $C_i$ も記載しています。そうすると $C_i$ の両端に生じる電圧 $V_{Ci}$ は

$$V_{Cj} = \frac{X_{Cj}}{R_F + X_{Cj}} V_D \tag{11}$$

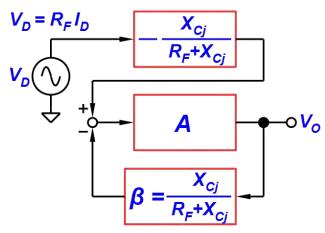

ここで右辺を「電圧」 $V_D$ としているところがポイントです。これをブロック線図で表すと、図 12 のようになり、またこれを $\beta$ を使わない式(4)の表現に戻すと

$$V_{O} = \frac{A}{1 + A \frac{X_{Cj}}{R_{F} + X_{Cj}}} \cdot \left( -\frac{X_{Cj}}{R_{F} + X_{Cj}} \right) V_{D}$$

(12)

図 9. ここまでの考えをブロック線図として表してみる

図 10. 図 9 のブロック線図を回路図的に表してみる

図 11. 図 10 の電流源を電圧源と出力抵抗に変換する

さらにA=∞とすれば

$$V_{O} = -\frac{R_{F} + X_{Cj}}{X_{Cj}} \cdot \frac{X_{Cj}}{R_{F} + X_{Cj}} V_{D} = -V_{D} = -R_{F} I_{D}$$

(13)

とはなるわけですが、発見として、 $A \neq \infty$ であれば式(12)において「ちょっと面白い」周波数特性が出来てしまうことが分かります。たとえばA = 1としてみると

$$V_O = -\frac{X_{Cj}}{R_F + X_{Cj} + X_{Cj}} V_D = -\frac{X_{Cj}}{R_F + 2X_{Cj}} V_D$$

(14)

となるのですね…。こんな条件は通常は考えられないわけですが (ブロック線図でのお遊びなので)、面白いものですね…。

Rev. **0** — 4/7 —

図 12. 図 11 のように信号源を電圧源としたときのブロック線図

# それぞれの OP アンプでのフォトダイオード・アンプの各種ゲインを求めてみる

前回までの TNJ-062, TNJ-063 は実は結構すんなり (計算でひっかからずに) 執筆できたのですが、実は今回は意外とてこずっています。計算ができないというより、うまくストーリーを組み立てられないのです…。いつもながらの「書きながら考える」、「一緒に学ぼう!」という形式なので平にご容赦をいただければと…。

つづいて OP アンプのオープン・ループ・ゲインとの関係を式で 求めていたのですが、読んでいる皆様は数式に飽きてきただろ うと思いましたので (汗)、一旦ここで LTspice のシミュレーシ ョンにより、AD824 と AD8066 のオープン・ループ・ゲインと ノイズ・ゲインを求めてみましょう。そして続いてそれぞれの ループ・ゲインを求めてみます。

### まずはオープン・ループ・ゲインとノイズ・ゲインを求め てみる

OP アンプの入力換算ノイズは非反転入力端子に存在する直列電圧源としてモデル化されます(入力換算オフセット電圧も同じしくみ)。ノイズ・ゲインは、図 7 のように非反転入力端子に信号源を挿入し、ここから出力への増幅度を求めるものです。その信号源が出力に現れる増幅率が、なるほどノイズ源からのゲイン「ノイズ・ゲイン」なのだと理解もできますし、図 7 のように信号源を挿入する行為も腹落ち感があるものと思います。

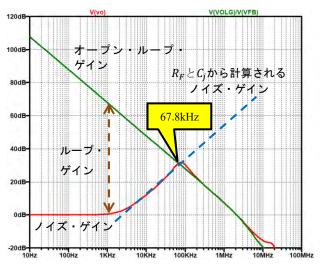

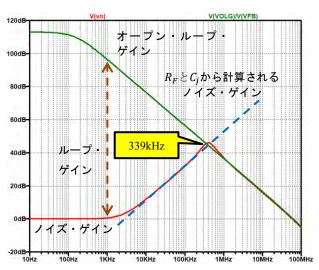

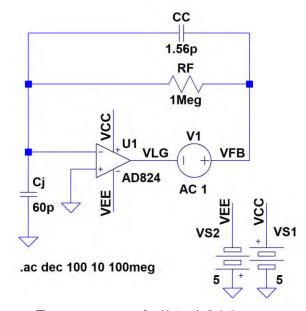

図 13 は AD824 のオープン・ループ・ゲイン(上)とノイズ・ゲイン(下)を求める LTspice シミュレーション回路です。シミュレーション結果を図 14 に示します。OP アンプを AD8066 に変えてシミュレーションした結果も図 15 に示します。

それぞれオープン・ループ・ゲインとノイズ・ゲインをプロットしています。オープン・ループ・ゲインとノイズ・ゲインが交差する周波数はそれぞれ 67.8kHz、339kHz となります。この周波数を基準として、電流電圧変換周波数特性が決まってくることになります。

### つづいてループ・ゲインを求めてみる

OP アンプのオープン・ループ・ゲインを $A_{OL}$ 、ループ・ゲインを $A_{LG}$ 、回路の帰還率を $\beta$ とすると

$$A_{LG} = A_{OL} \cdot \beta \tag{15}$$

また $\beta$ はノイズ・ゲイン $A_{NG}$ の逆数

$$A_{NG} = \frac{1}{\beta} \tag{16}$$

### **Open Loop Gain**

図 13. AD824 のオープン・ループ・ゲイン(上)とノイズ・ゲイン(下)を求める LTspice シミュレーション回路

図 14. 図 13 の AD824 の回路で得られたオープン・ループ・ゲインとノイズ・ゲイン(この差がループ・ゲインになる)

となりますから、対数で表現すれば

$$\log_{10} A_{LG} = \log_{10} A_{OL} + \log_{10} \beta \tag{17}$$

$$\log_{10} A_{LG} = \log_{10} A_{OL} - \log_{10} A_{NG} \tag{18}$$

と表すことができます。これらから図 14 と図 15 それぞれの二 つのカーブの「差」がループ・ゲインになることも理解できます。図 14 と図 15 それぞれにも、ループ・ゲインに相当する矢印(ゲインの幅)を表記してあります。

Rev. **0** -5/7 -

図 15. 図 13 の回路を AD8066 に変えて得られたオープン・ルー プ・ゲインとノイズ・ゲイン

実際に LTspice でそれぞれの OP アンプのループ・ゲインをシミュレーションしてみましょう。図 16 はこのシミュレーション回路(OP アンプは AD824)です。

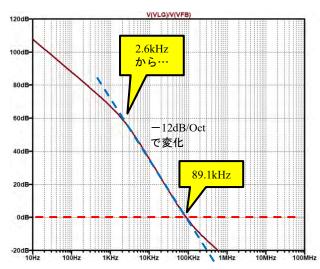

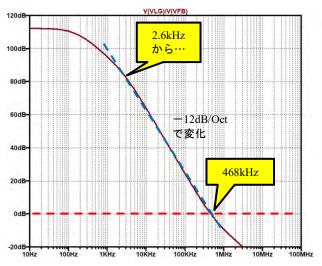

ループ・ゲインのシミュレーション結果を AD824 のケースを図 17 に、AD8066 のケースを図 18 に示します。ループ・ゲインが 0dB となるクロスオーバ周波数は AD824 では 89.1kHz、AD8066 では 468kHz となっていることが分かります。

図 14 と図 15 でオープン・ループ・ゲインとノイズ・ゲインが 交差する周波数はそれぞれ  $67.8 \mathrm{kHz}$ 、339 $\mathrm{kHz}$  でしたから、これ と同じ比率になっています。またそれぞれの  $\mathrm{OP}$  アンプでフォト ダイオード・アンプを構成したときの $-3 \mathrm{dB}$  カットオフ周波数は  $108.6 \mathrm{kHz}$ 、 $562 \mathrm{kHz}$  でしたから、こことも相関が取れていることも分かります。

### ノイズ・ゲインが低い周波数で上昇している

図 17 と図 18 を改めてみてみると、どちらも 2.6kHz あたりでー6dB の変化から-12dB の変化に屈曲していることが分かります。これはこの低い周波数において、ノイズ・ゲインが上昇することが理由です。このことを考えてみましょう。

このフォトダイオード・アンプにおける帰還率は

$$\beta = \frac{X_{Cj}}{R_F + X_{Cj}} = \frac{\frac{1}{j2\pi f C_j}}{R_F + \frac{1}{j2\pi f C_j}} = \frac{1}{1 + j2\pi f C_j R_F}$$

(19)

となり、ノイズ・ゲインは、

$$A_{NG} = \frac{1}{\beta} = 1 + j2\pi f C_j R_F \tag{20}$$

であり、 $C_i$ と $R_F$ でできるカットオフ周波数特性 $f_c$

波数特性が制限されることになるわけです。

$$f_C = \frac{1}{2\pi R_F C_i} \tag{21}$$

を超えると(ここまでの例では $f_c = 2.6 \text{kHz}$ )、ノイズ・ゲインが 1 (0dB) から+6dB/Oct で上昇を始めることになるわけです。 その結果、図 17 や図 18 のようにループ・ゲインについてもカットオフ周波数特性 $f_c$ を超えると-12 dB/Oct で低下を始め。周

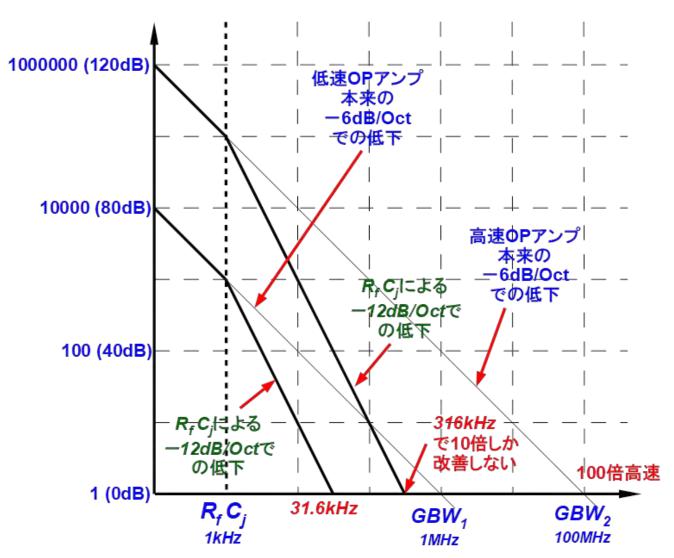

# これで高速な OP アンプに変えても周波数特性が 伸びない理由が分かる

これから分かることは、高速な OP アンプを用いたとしても、 $C_j$  と  $R_F$  でできるカットオフ周波数特性  $f_c$  (ここまでの例では  $f_c$  = 2.6kHz)により、ループ・ゲインが-12 dB/Oct で低下を始め、本来の(1 次遅れ系の)-6 dB/Oct よりも低下が急になり、より高速な OP アンプに変えても、思ったように周波数特性が伸びないということが分かります。

このようすを具体的に図示すると、図 19 のようなループ・ゲイン特性として表すことができます。 $C_j$ と $R_F$ でできるカットオフ周波数は $f_c=1$ kHzにしてあります。ここから分かることは、GB積  $GBW_1=1$ MHzのOPアンプからGB積  $GBW_2=100$ MHzの 100 倍も高速なOPアンプに変えても、改善率は

$$\sqrt{\frac{GBW_2}{GBW_1}} = \sqrt{\frac{100}{1}} = 10$$

(22)

で10倍までにしかならないのですね。

図 16. AD824 のループ・ゲインを求める LTspice シミュレーション回路

図 17. 図 16 の AD824 の回路で得られたループ・ゲイン

図 18. 図 16 の回路を AD8066 に変えて得られたループ・ゲイン

### 一旦まとめ

### 参考文献

[1] 玉村 俊雄; OP アンプ IC 活用ノウハウ, CQ 出版社(現在はオンデマンド版として復刻)

[2] 石井 聡; ロック線図で考える OP アンプ DC サーボ回路の低域 カットオフ周波数(前編), 回路設計 WEB ラボ, TNJ-062, アナログ・デバイセズ

[3] 石井 聡; ロック線図で考える OP アンプ DC サーボ回路の低域 カットオフ周波数(後編), 回路設計 WEB ラボ, TNJ-063, アナロ グ・デバイセズ

図 19. 高速な OP アンプに変えても周波数特性が伸びない理由をループ・ゲインで考える

Rev. **0** - 7/7 -