# SPICE vs. IBIS: 回路シミュレーションの目的に 即したモデルを選択する

著者: May Anne Porley、アプリケーション・エンジニア Jermaine Lim-Abrogueña、システム・インテグレーション・エンジニア Mar Christian Lacida、プロダクト・アプリケーション・エンジニア

プロトタイピングの分野では、回路シミュレーションがより一 般的に利用されるようになりました。その結果、広範なアプリ ケーション分野においてシミュレーション用のモデルはより重 要な要素となりました。その中でも、SPICEモデルとIBISモデ ルは非常に代表的なものだと言えます。これらのシミュレー ション・モデルを活用すれば、プリント回路基板を開発する際、 プロトタイピングの段階でコストの削減を図ることができま す。本稿では、まずSPICEモデルとIBISモデルの比較を行い、 その違いを明らかにします。続いて、プリント回路基板を製作 する前に実施される検証が重要な理由について説明します。更 に、ユース・ケースごとに各種のサンプルを示しながら、回路 設計における両モデルの使い分けについて解説します。なお、 SPICE シミュレータである「LTspice®」やプリント基板用の検 証ツールである「HyperLynx®」など、よく使われるシミュレー ション・ツールについても解説を加えことにします。

#### はじめに

デジタル技術は急速な進化を遂げています。電子機器のメーカー がこのデジタル化の流れに応えるためには、新たな技術の導入 が不可欠です。その具体的な例となるコンポーネントやツール の開発も絶えず進められています。シミュレーションの世界で言 えば、様々な種類のモデルが提供されるようになりました。そ うしたモデルは、プリント回路基板を開発する際、設計したシス テムの機能を確認したり、検証を行ったりすることを目的として 利用されます。つまり、基板の製作に進む前の段階で、設計に 問題がないかどうかを確認するということです。その際に使用さ れる代表的なシミュレーション・モデルは2つ存在します。それ がSPICEモデルとIBISモデルです。いずれも本質的に動作モデル (behavioral model) として位置づけられます。ただ、それらを どのように使い分けるべきなのかは、シミュレーションの目的に よって異なります。

# シミュレーション・モデルがもたらすメリット

一般に、シミュレーション・モデルは、プロトタイピングの前の 段階で、設計した回路のシミュレーションを実施する際に使用 します。ただ、IBISモデルやSPICEモデルを使用して単にシミュ レーションを実施すればそれでよいというわけではありません。 シミュレーションの目的は、信号の完全性に関するあらゆる問題 を検出し、設計した回路の性能を確認することです。そうした問 題は、配線パターンを含めて、設計した基板の特性に起因してい ることが少なくありません。ただ、コンポーネントの機能のレベ ルで単純な問題が生じていることもあります。

IBISモデルは、コンポーネントのクランプ動作や駆動能力を表現 するために使用されます。それだけでなく、デジタルI/O(入出 力) バッファのインピーダンスも表現されます。つまり、デジタ ル系のドライバやレシーバーの入出力インピーダンスなどが網羅 されるいうことです。ただ、それらの情報はモデルに直接記述さ れているわけではありません。コンポーネントの動作を表す電圧 と電流のデータに暗黙的に含まれています。クロストークや反射 といった信号の完全性の問題を解決する上では、バッファのイン ピーダンスが鍵になります。そのため、シミュレーションを実施 する際には、それらの値が明確になっていることが重要です。な お、クロストークとは、ある配線パターンを伝わる信号が別の配 線パターンを伝わる信号に結合して発生する干渉のことです。一 方の反射は、基板を製作する前の段階で、信号の完全性につい てシミュレーションを実施すると遭遇する非常に一般的な問題で す。反射の問題は、入力バッファまたは出力バッファのインピー ダンスと配線パターンの特性インピーダンスの間にミスマッチが ある場合に発生します。機器に入力された信号は、配線パターン に沿って伝わり、一切の干渉を受けることなく配線パターンの他 端に到達するのが理想です。しかし、実際にはそのようにはなり ません。インピーダンス・ミスマッチによって、信号の完全性に 影響が及ぶからです。

そうすると、伝送線路に沿って伝搬する信号の一部が他端に到達し、その信号の一部が反射成分として元の場所に戻ってきます。この問題への代表的な対処策は、バッファに終端を施すことです。これについては、IBISモデルのインピーダンス機能を活用すると便利です。つまり、IBISモデルを使用したシミュレーションにより、終端に適用する直列抵抗またはシャント抵抗の値を計算します。それによって、ピンと伝送線路のインピーダンスをマッチングさせるということです。その結果、信号の反射という問題を解消できます。

SPICEモデルを使用すれば、回路の詳細な動作を予測することができます。このことは、時間とコストの有効活用に役立ちます。プロトタイプを製作する前に、起こり得る問題を確認/検討/解決し、回路の性能向上を図れるからです。SPICEモデルによるシミュレーションは、主にコストと時間の面でメリットをもたらします。コストと時間のかかるプロトタイプの修正作業や、コンポーネントの再発注、ハンダ付けのやり直しにつながる可能性のある回路の誤りを早い段階で検出することが可能になるからです。最近のシミュレーション・モデルは更なる進化を遂げており、コンポーネントの性能をより正確に模擬できるようになりました。シミュレーションであれば、様々なコンポーネントを即座に交換しながら回路の設計について詳細な評価を実施できます。また、回路のプロトタイピングに多くの時間を費やしたり、プロトタイプに誤りがあった場合にハンダ付けをやり直したりする必要もなくなります。

# SPICE モデルとは何か?

SPICEというのは、Simulation Program with Integrated Circuit Emphasisの頭文字をとったものです。その実体は、汎用の回路シミュレータだと説明することができます。SPICEシミュレータには、回路素子(トランジスタ、抵抗、コンデンサなど)とそれらの接続について記述したテキスト・ベースのネット・リストを受け渡します。すると、同シミュレータは節点解析を使用して数式を生成し、それらを解く処理を実行します。SPICEモデルというのは、テキスト・ベースの動作モデルのことです。このモデルを使用することで、SPICEシミュレータは様々な条件下のデバイスの動作を数学的に予測します。

# IBISモデルとは何か?

IBISは、Input/Output Buffer Information Specificationの頭文字をとったものです。IBISモデルは、デバイスのデジタル入出力バッファのアナログ的な動作を表現するためのものです。この動作モデルは、プレーンなASCIIテキスト形式のデータとして記述されます。具体的には、デジタル・バッファ内のコンポーネントの電圧と電流の関係 (V-I) が記述されます。また、出力バッファまたはI/Oバッファのスイッチング特性を表す記述も盛り込まれます。このスイッチング特性は、時間の経過と電圧の関係 (V-t)の形で表現されます。IBISモデルには、V-I/V-tについて記述した表形式のデータが盛り込まれます。このようなモデルを使用することにより、基板を製作する前に信号の完全性を解析することが

できます。IBISモデルには、リバース・エンジニアリングの対象となり得るデバイスの内部情報は含まれません。つまり、ブラックボックス・モデルのようなものであり、機密情報は一切開示されないことを特徴とします。

#### モデルとは、どのようなものなのか?

上述したように、IBISモデルとSPICEモデルはいずれもテキスト・ベースの動作モデルです(図1)。単純なテキスト・ファイルとして提供されるので、Windowsの「メモ帳」のようなシンプルなツールによって内容を表示することも可能です。ただ、より検討を行いやすくするためには専用のツールを使用した方がよいでしょう。IBISモデルについては、「Cadence Model Integrity」やSiemensのHyperLynxを使って表示することをお勧めします。一方、SPICEモデルについては、SPICEシミュレータを使うことで、そのファイルを読み込んだり開いたりすることができます。代表的なSPICEシミュレータとしては、LTspice、NIの「Multisim™」、「OrCAD® PSpice®」などが挙げられます。

図1. SPICEモデル(左)とIBISモデル(右)。 SPICEモデルのファイル(拡張子は.cir)はLTspiceによって 開いています。IBISモデルのファイル(拡張子は.ibs)は HyperLynxによって開いています。

SPICEモデルとIBISモデルは、どちらも実行可能ファイルではありません。あくまでも、モデルの内容をテキスト・ベースで記述しただけのものです。いずれのモデルも、主に次の3つの部分で構成されています。

- ▶ ヘッダ・ファイル:モデル、デバイス、改訂履歴、モデルに固有の特記事項、モデル化の対象であるデバイスのメーカー/ブランドに関する簡単な説明や一般的な情報を提供します。

- ▶ モデル名/タイトル:通常は、デバイス名、ピンの構成、ピンとバッファのマッピングに関する情報を記述します。SPICEでは、「.subckt ADGxx < ピンの構成 >」という行を記述します。ここで「ADGxx」はモデル名です。一方、IBISでは、「[Component] ADGxx」という記述を使用します。

- ▶ モデルの構造: モデルの詳細をテキスト・ベースで表現します。 SPICE モデルは、デバイスの各パラメータを表す様々なブロックで構成されます。それには、コンデンサ、抵抗、ダイオード、電圧源、電流源といったプリミティブ・コンポーネントや、ネイティブ・コンポーネントで構成されるピンの機能などが含まれます。一方、IBIS モデルは、各デジタル I/O バッファをモデル化した V-I/V-t のデータ・テーブル (表) で構成されます。

### どこで入手すればよいのか?

ほとんどの場合、SPICEモデルとIBISモデルは、各半導体メーカーのウェブ・ページで提供されています。多くの半導体メーカーは、自社の製品に対応するシミュレーション・モデルを開発しています。そして、モデルに含まれる内容や、モデルの精度、サポートに関するメンテナンスを行っています。図2に示したのは、アナログ・デバイセズのウェブサイトの例です。数多くの製品に対応するSPICEモデルとIBISモデルを提供していることがわかります。

また、多くのSPICEシミュレータは、SPICEモデルのライブラリを備えています。そのライブラリには、数多くの製品のモデルが格納されています。図3に示したのは、LTspiceが備えるスイッチのライブラリの例です。ご覧のように、アナログ・デバイセズのほとんどのスイッチ製品が網羅されています。シミュレーションを滞りなく行うためには、広範なSPICEモデルを網羅するライブラリが用意されたシミュレータを選択するべきでしょう。

図 2. アナログ・デバイセズのウェブ・ページの例。 数多くの製品のSPICEモデル(左)と IBISモデル(右)を提供しています。

図 3. LTspiceのライブラリの例。 数多くのSPICEモデルが用意されています。

#### シンボル用のファイル

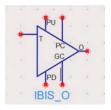

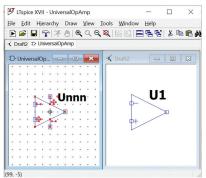

シミュレータでSPICEモデルとIBISモデルを使用するには、どちらにもシンボルと呼ばれる付随的なファイルが必要です。通常、IBISモデルはテキスト・ベースで表現したデータの形で提供されます。EDA (Electronic Design Automation) ツールを使用してシミュレーションを実施するためには、他のコンポーネントが接続されるコンポーネントのシンボル内にそのIBISモデルを配置する必要があります。IBISモデルと同様に、SPICEモデルについてもシンボル用のファイルを用意しなければなりません。通常、そのファイル(拡張子は.asy)はドット・シンボルの形式です。そのファイルを、SPICEシミュレータのライブラリにインストールする必要があります。モデルとシンボルの両方のファイルをライブラリに追加/設定すれば、回路シミュレーションでそのモデルを使用できるようになります。図4と図5に示したのは、IBISモデルとSPICEモデルに対応するシンボルの例です。

図 4. IBIS モデルのシンボル。 HyperLynx(左)と Advanced Design System(右)で 出力バッファを表示しています。

図5. SPICE モデルのシンボル。LTspice の回路シミュレーションで 使用される3ピンの単純なオペアンプの例を示しました。 (右) はテンプレート、(左) はその等価シンボルです。

通常、メーカーはIBISとSPICEのシンボル・ファイルは提供していません。ただ、ほとんどのシミュレータには、シンボルのテンプレートが用意されています。これを、ピンの配置/数やデバイスの種類に応じて使用することができます。また、SPICEについては、シミュレータによって機能の詳細は異なりますが、シンボル・ファイルを自動生成することも可能です。

# SPICEとIBISの比較

続いて、SPICEモデルとIBISモデルとでは何が違うのか両者の比較を通して説明することにしましょう。

#### SPICEモデルの詳細

一般に、SPICEモデルは、ピンの配置、ピンの構成、機能、その 他の動作を含むコンポーネントの振る舞いを再現します。それら のモデルには標準的なアーキテクチャが用意されているわけでは ありません。SPICEモデルを使用することにより、ピンの機能を 含めてコンポーネントに期待される動作性能を正確に再現する アーキテクチャを構築することになります。SPICEモデルは、抵 抗やコンデンサなどの受動部品、ダイオード、トランジスタなど で構成されます。適切な設計を行えば、対象とするコンポーネン トの動作を再現可能なモデルを構築できます。但し、その際には 留意すべきことがあります。コンポーネントの動作を正確に再現 するためには、SPICEモデルに複雑な回路を盛り込まなければな りません。ただ、あまりにも複雑すぎると、シミュレーションの 実行速度が低下してしまいます。例えば、抵抗のような受動部品 のSPICEモデルであれば、1行のテキスト・データとして記述で きるでしょう。しかし、より複雑な回路やサブサーキットの場合、 その記述は数百行にも達する可能性があります。

先述したように、SPICEモデルはテキスト・エディタのようなツールによって開くことができます。ただ、最近のSPICEシミュレータは、等価回路図を描画することで非常に簡単に回路解析を実施できるようになっています。図6に示したのは、3つのオペアンプから成る状態変数フィルタの例です。このような回路図を描くことにより、回路で使用する素子とその接続を記述したテキスト・ベースのネット・リストが生成されます。

SPICEモデルについては、対象とするデバイスのデータシートに記述された仕様/機能に近い性能を提供することが期待されます。例えば、スイッチのSPICEモデルにはオン抵抗やタイミングなどのパラメータを用意する必要があります。それに対し、オペアンプのモデルにはゲイン帯域幅や入力オフセットといったパラメータが必要です。通常、SPICEモデルでは、データシートに記載されている代表値、最小値、最大値を網羅する形で機能や仕様が記述されます。

図6.3つのオペアンプから成る状態変数フィルタ。 右に示したのがそのSPICEモデルです。

#### IBISモデルの詳細

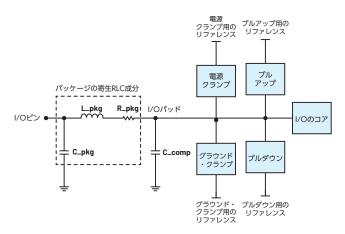

一般に、IBISモデルは、デジタルI/Oバッファを表現する標準的なアーキテクチャに従って記述されます。そのアーキテクチャは、図7に示すようなものです。各コンポーネントのデジタル・バッファについて記述するためには、IBISの仕様で定義されているキーワードを使用します。V-Iルックアップ・データ・テーブルとV-tルックアップ・データ・テーブルは、各キーワードの下に記述します。

図7. IBISで使用されるアーキテクチャ。 標準的なI/Oバッファに対応しています。

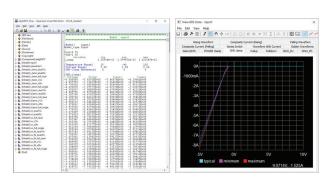

図8(左)は、IBISモデルに記述されたV-Iルックアップ・テーブ ルの例です。一方、同図(右)には、HyperLynxを使用してこの V-Iルックアップ・テーブルを波形としてプロットしたものを示し ました。通常、このテーブルには、 $-V_{DD} \sim V_{DD} \times 2$ の電圧範囲で 測定した電流の値が記述されます。また、3つの条件(標準コー ナー、スロー・コーナー、ファスト・コーナー) におけるコンポー ネントの電流値(動作)が示されます。それらの条件は、デバイ スのプロセス・コーナー、動作電圧、動作温度を考慮して設定さ れています。例えば、デジタル系のレシーバーにおいてクランプ を実現する保護用コンポーネントの動作は、V-Iルックアップ・ テーブルと、キーワード[Power clamp]、[GND clamp]を使 用して記述します。また、I/Oバッファの駆動能力はキーワード [Pullup]、[Pulldown]を使用して記述します。これら4種のキー ワードを使用した記述はモデル内で独立して存在することになり ます。信号の完全性をシミュレーションするには、受信モードと 駆動モードの両方が必要です。

図8. スイッチ製品 (ADG5401F) のV-Iデータ (左)。 IBISのキーワードの下に記述しています。 (右) はHyperLynxを使用して プロットしたV-Iカーブです。

一方、V-tテーブルはデジタル系のドライバのスイッチング特性 を表します。具体的には、負荷がVppとグラウンドを基準として いる場合に、ある状態から別の状態に遷移するときの動作を表 すデータが記述されます。そのテーブルは、キーワード[Rising\_ Waveform]、[Falling\_Waveform]を使用して記述します。また、 キーワード[Ramp]の下には、I/Oバッファのスルー・レートが 記述されます。スルー・レートの電圧については、遷移エッジに おける振幅の20%から80%が対象になります。これらの波形/ ランプのデータは、ドライバのコンポーネントが時間に対してど の程度高速にターン・オン/ターン・オフするのかを表します。

上記のキーワードを使用した記述は、モデル内で独立した形で存 在することになります。シミュレーションで使用する場合、EDA ツールはそれらV-IデータとV-tデータを組み合わせます。それ により、動作領域に基づいてバッファのモデルを構築します。構 築されたモデルを使用し、基板上の信号の完全性についてシミュ レーションやタイミング解析を行います。

また、IBISモデルには、デバイスのピンやパッケージの寄生RLC 成分の値、各I/Oバッファのバッファ容量C\_compの値も含まれ ています。C\_compはパッドからバッファを見た場合の容量であ り、パッケージの容量は含まれていません。

IBISモデルで使用する V-I/V-t データ・テーブルやキーワードの 詳細については、「IBISモデルの開発方法【Part 1】 IBISモデル の開発が設計の成功に不可欠な理由」をご覧ください。

#### 代表的なシミュレーション・ツール

SPICEシミュレータとIBISシミュレータとしては、様々な製品が 標準的に使用されています。技術者向けのものもあれば、教育向 けのものもあります。なかには、高速システムやアナログ・シス テム、ミックスド・シグナル・システムなど、ほとんどの回路に 対応可能なシミュレータも存在します。通常、SPICEシミュレー タは、回路の接続/ノードに基づいて節点方程式を生成し、各 ノードにおける電流値と電圧値を算出します。一方、IBISシミュ レータでは、モデル内に記述されたV-I/V-tルックアップ・デー タ・テーブルを参照して信号の出力動作を予測します。以下、よ く使用されているシミュレータをいくつかピックアップして紹介 することにします。

#### 代表的なIBISシミュレータ

ここでは、代表的なIBISシミュレータを2つ紹介しておきます。

- ▶ Siemens の HyperLynx: この EDA ツールは、高速回路の設 計における信号の完全性や電源の完全性の解析、電気的な設 計ルールのチェック、電磁モデリングなどに使用されます。ま た、HyperLynx を使用すれば、IBIS モデルの表示、編集、シミュ レーションを実施することができます。

- ▶ Keysight Technologies の ADS (Advanced Design System): 周波数領域/時間領域での回路シミュレーション、 回路図の設計とレイアウト、設計ルールのチェック、電磁界シ ミュレーションなど、様々な設計プロセスで使用可能な EDA ツールです。ADS は IBIS モデルを使用するシミュレーション にもよく使用されています。

#### 代表的なSPICEシミュレータ

続いて、代表的なSPICEシミュレータを3つ紹介します。

- ▶ アナログ・デバイセズの LTspice®: 高性能の SPICE シミュ レータです。回路図のキャプチャ用のグラフィカルなインター フェースを備えていることが特徴の1つです。回路図中の ノードにプローブを当てれば、LTspice が内蔵する波形ビュー ワによってシミュレーション結果を表示することができま す。LTspice の GUI(Graphical User Interface)は、回路 図の入力に必要なキーボード入力とマウスの操作を統計的に 分析した結果に基づいて設計されています。そのため、他の SPICE シミュレータと比較して、よりインタラクティブな操作 が実現されています。LTspice のライブラリには、シグナル・ チェーン製品を含むアナログ・デバイセズのほとんどの製品 の SPICE モデルが含まれています。それだけでなく、数多く の受動部品の SPICE モデルも用意されています。

- ▶ NI Multisim: Multisim を使用すれば、電子回路の動作を即 座に視覚化、解析することができます。回路図を扱うための インタラクティブな環境が用意されていることも特徴の1つ です。加えて、仮想的なオシロスコープ、デジタル・マルチメー タなど、様々な装置に対応する機能を備えています。そのため、 標準的な実験/評価環境で体験するのと似たような形で回路 のシミュレーションを実施できます。

- ▶ OrCAD PSpice Designer:回路図の入力、ネイティブなアナ ログ対応機能、ミックスド・シグナル機能、解析エンジンが統 合されたツールです。回路のシミュレーションと検証に対応す る完全なソリューションだと言えます。簡単な回路のプロトタ イピング、複雑なシステムの設計、あるいはコンポーネントの 歩留まりや信頼性の検証などにも対応できます。そうしたあら ゆる作業に対し、極めて高い性能の回路シミュレーション機能 を提供します。基板のレイアウトや製作に移行する前の段階 で、回路、コンポーネント、パラメータの解析と改良を図るこ とができます。

#### IBISとSPICEの使用例

続いては、IBISモデルとSPICEモデルの使用例を紹介していきま

#### IBISモデルの使用例

先述したように、IBISモデルはテキスト・データの形で提供され ます。EDAツールを使用してシミュレーションを行う際には、他 のコンポーネントが接続されているシンボルの中にそのモデルを 取り込みます。シミュレータはモデルに記述されたデータを使用 し、特定の条件下におけるバッファの動作の解析/予測を行いま す。

SiemensのHyperLynxとKeysightのADSには、シミュレーションで使用可能なIBISモデルのシンボルが用意されています。各ツールにおいて、各シンボルは図9のように表示されます。

図9. IBIS モデルのシンボル。(左)はHyperLynxのツールバーであり、IBIS モデルをベースとするシミュレーションで使用可能なシングルエンド・バッファ、差動バッファ、IC コンポーネントのシンボルが表示されています。同様に、(右)の ADSの画面には、シミュレーションで使用可能な様々な種類のバッファのシンボルが表示されています。

HyperLynxでは、シングルエンドの入力バッファまたは出力バッファをシミュレーションする場合、図9(左)で強調表示されている最初のバッファを使用します。その中にIBISモデルをロードし、シミュレーションの対象とする特定のバッファを選択します。出力バッファのモデルが選択されたら、同ツールはその出力バッファを自動的に表示します。入力バッファのシミュレーションを実施する場合には、同ツールが自動的にシンボルを入力バッファのシンボルに変換します。

ADSの場合、Signal Integrity-IBISのパレットに様々な種類のバッファのモデルが表示されます。例えば、オープン・ドレイン出力が必要な場合、OSNKというラベルが付加されたシンボルを選択します。終端抵抗のシミュレーションを実施する場合には、Tというラベルが付加されたシンボルを使用します。シンボルの選択を誤ると、エラーが発生する可能性があるので注意してください。例えば、入力バッファが必要なのに出力バッファのシンボルを回路図に配置してしまったとします。その場合、IBISモデルが備える入力バッファのピンを確認することはできません。ADSとしては、出力バッファのピンしかシンボルにロードすることができないからです。

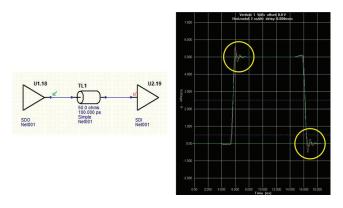

ここで、IBISモデルによるシミュレーションの目的について考えてみましょう。バッファと、伝送線路として機能する配線パターンの間には、インピーダンス・ミスマッチが存在することがあります。IBISモデルによるシミュレーションの目的の1つは、そのミスマッチに起因する望ましくない信号の振る舞いを検出することです。

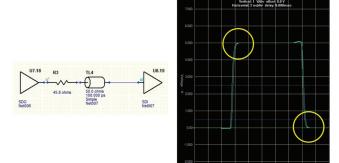

ここでは、図10(左)に示した回路を例にとります。この回路では50Ωの配線パターンを使用していますが、出力バッファは終端されていません。この回路図を基に、HyperLynxを使用してシミュレーションを実行してみます。図10(右)のシミュレーション結果を見ると、望ましくないオーバーシュートとアンダー

シュートが生じていることがわかります。ただ、この問題には、 直列の終端抵抗を追加することで対処できます。それにより、 バッファと配線パターンの間のインピーダンスをマッチングさせ るということです。そのためには、まず出力バッファのインピー ダンスを明確にする必要があります。

図10.終端されていない回路(左)。 (右)は、この回路のシミュレーション結果です。

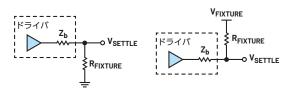

IBISモデルには、グラウンドを基準とする [Rising\_Waveform] と VDD を基準とする [Falling\_Waveform] のV-tテーブルが用意されています。これらを使用することで、バッファの出力インピーダンスを導出することができます。つまり、分圧器が構成されていることを考慮すれば、バッファのインピーダンスの値を計算できるということです。得られた値を使用すれば、モデルに追加すべき適切な終端抵抗の値も計算できます。つまり、バッファと配線パターンの間のインピーダンスをマッチングさせることが可能になるということです。インピーダンス・ミスマッチを解消し、信号に望ましくないオーバーシュートやアンダーシュートが生じないようにするためには、この手法が有効です。

図 11 に示したのは、上述した分圧器の回路図です。 $Z_b$ がバッファのインピーダンスです。そして、 $R_f$ ixture と $V_f$ ixture はモデル内にあらかじめ用意されています。 $V_{SETTLE}$ は $V_f$ tの波形がセトリングする電圧です。

図11. 分圧器を構成する回路

図12. V-tルックアップ・テーブルの抽出に使用したフィクスチャ。 IBISモデルに含まれています。(左)は立ち上がり波形、 (右)は立下がり波形に対応しています。

終端抵抗の値が決まったら、それを回路図に追加します。図13 に示したのは、終端抵抗を追加した回路図とそれに対応するシ ミュレーション結果です。この結果を見ると、オーバーシュート とアンダーシュートが改善されていることがわかります。

上述したのは、バッファのインピーダンスを計算し、インピーダ ンス・ミスマッチによる問題を解決するための手段の1つに過ぎ ません。IBISモデルに含まれるプルダウンのV-Iテーブルを使用 したり、動作点を特定するために負荷線解析を実行したりすると いった方法も考えられます。そうした方法によっても、出力イン ピーダンスと直列終端抵抗の値を導出することができます。

図13. 終端抵抗を追加した回路(左) (右) は、この回路のシミュレーション結果です。

#### SPICEモデルの使用例

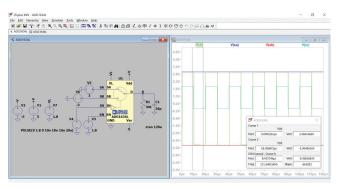

図14に示したのは、SPICEシミュレーションによって過渡解析を 行う例です。ここでは、アナログ・スイッチ「ADG1634LIをシ ミュレーションの対象とし、その性能を評価します。シミュレー ション結果を時間領域でプロットすることで、同スイッチの機能 やタイミングについて確認することができます。過渡解析は、指 定された期間におけるコンポーネントの動作の予測を可能にしま す。SPICEモデルを使えば、DC解析やAC解析など、様々な解 析手法によってシミュレーションを実施できます。DC解析では、 ある範囲のDC入力値に基づいて回路の電圧と電流が計算されま す。AC解析を実施すれば、回路の特定のノードにおける信号の 振幅と位相を確認できます。AC解析は、周波数領域で回路の動 作を確認したい場合に役立ちます。

図14. SPICEシミュレーションの例。 ADG1634Lのモデルを使用しています。

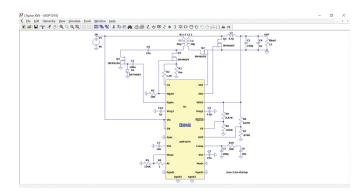

SPICEでは、より複雑な回路も扱えます。例えば、図15のよう に設計した回路の性能をシミュレーションによって確認すること が可能です。

図15. シミュレーションの対象とする複雑な回路。 LTspice を使えば、アクティブ・クランプ回路を備える フォワード・コンバータのシミュレーションも実行できます。

#### SPICEとIBISの使い分け

ここまで、SPICEモデルとIBISモデルについて詳しく説明してき ました。どちらのモデルを使用すべきなのかは、回路やシミュ レーションしたい内容によって異なります。IBISモデルを使用す べきケースとしては、以下のようなものが挙げられます。

- ▶ バッファのインピーダンス、駆動能力、立ち上がり時間、立下 がり時間など、デジタル I/O バッファの動作特性を把握した い場合

- ▶ 評価しようとしているコンポーネントが FPGA などのデジタ ル・コンポーネントである場合

- ▶ コンポーネントを配線パターンに接続した際のデジタル I/O ピンにおける信号の完全性や伝送線路で起こり得る問題を懸 念している場合

では、SPICEモデルはどのような場合に使用すべきなのでしょう か。それは、回路シミュレーションにおいて、コンポーネントの より完全な性能が必要とされるケースです。コンポーネントのア ナログ・ピン、デジタル・ピン、電源ピンの振る舞いや、回路内 の複数のコンポーネントに接続されている場合の動作応答などを 把握したい場合にはSPICEモデルを使用するのが最適です。以下 のようなケースでは、IBISモデルではなくSPICEモデルを使用す べきです。

- ▶ 回路内で使用した場合のコンポーネントの機能と動作性能を 評価したい場合

- ▶ 様々な解析手法を使って、時間領域/周波数領域のコンポー ネントの動作応答を評価したい場合

- ▶ 複雑な設計において、集中的な節点解析を必要とする場合や、 回路内の電流/電圧ノードの解析を実施したい場合

# まとめ

SPICEモデルとIBISモデルは、シミュレーション用のモデルとし て広く使われています。これらのモデルを利用することにより、 プロトタイピングの段階に移行する前(あるいはプロトタイピン グの最中) に、対象とする回路の性能を検証することができま す。それにより、コストと時間を節約することが可能になります。 SPICEモデルもIBISモデルも、その本質は動作モデルです。一般 に、SPICEモデルは、ピン配置、ピンの構成、機能、その他の動 作を含むコンポーネントの振る舞いを再現します。一方のIBISモ デルは、V-I/V-tのデータ・テーブルを用意することにより、デ バイスのI/Oの動作を再現します。これらのモデルをシミュレー タ上で利用するには、シンボル用の付随的なファイルが必要にな ります。SPICEモデルによるシミュレーションを実施すれば、ピ ンの機能や構成を踏まえた上でコンポーネントの性能を予測する ことができます。一方、IBISモデルによるシミュレーションは、 信号の完全性に関する問題を予測するために使用されることが多 いでしょう。例えば、基板上にコンポーネントを実装した際にデ ジタルI/Oピンで生じるインピーダンス・ミスマッチや、クロス トーク、反射、アンダーシュート/オーバーシュートなどについ て検証したい場合です。どちらのモデルを使用すべきなのかは、 目的に応じて異なります。基板の配線パターンにコンポーネント を接続した際、デジタルI/Oピンの信号の完全性や伝送線路で起 こり得る問題を懸念している場合には、IBISモデルの使用を強く お勧めします。一方、コンポーネントを回路内で使用する際、ア ナログ・ピン、デジタル・ピン、電源ピンの振る舞いやコンポー ネントの性能を回路シミュレーションによって検証したい場合に は、SPICEモデルを使用することをお勧めします。

# 参考資料

Gabino Alonso [LTspice活 用 へ の 第 一 歩] Analog Dialogue、Vol. 53、No. 4、2019年12月

Mike Engelhardt [SPICE Differentiation (SPICEの差別化)] LT Journal of Analog Innovation、2015年1月

Roy Leventhal [How to Use the IBIS Model (IBISモデルの使 い方) | 2014年3月

Roy Leventhal, Lynne Green [Semiconductor Modeling: For Simulating Signal, Power, and Electromagnetic Integrity (半導体のモデリング:信号、電力、電磁界インテグリティのシ ミュレーション)」Springer、2006年

Jermaine Lim、Keith Francisco-Tapan [IBISモデルの開発方 法【Part 1】 IBISモデルの開発が設計の成功に不可欠な理由」 Analog Dialogue、Vol. 55、No. 3、2021年9月

[Advanced Design System (ADS)] Wikipedia. The Free Encyclopedia、2022年5月

[HyperLynx High-Speed Design Analysis & Verification] (HyperLynxにより、高速回路の設計を解析/検証する)] Siemens

「IBIS Modeling Cookbook for IBIS Version 4.0 (IBISバージョ ン4.0のためのIBISモデリング・クックブック)」The IBIS Open Forum、2005年9月

[LTspice®: Schematic Editor (LTspice: 回路図エディタ)] **Analog Devices**

[LTspice®: Overview (LTspice: 概要)] Analog Devices

「Why IBIS? (IBISの導入に伴うメリット)」 Advanced Micro Devices. Inc.

# 著者について

May Anne Porleyは、アナログ・デバイセズ(フィリピン)のアプリケーション・エンジニアです。入社は2012年で、自動試験装置(ATE)グループに所属。スイッチ、マルチプレクサ、レベル変換器、バッファ非内蔵型のクロスポイント・スイッチなどを対象としたアプリケーション・サポートを提供しています。スイッチ/マルチプレクサ製品のSPICEモデルの開発も主導してきました。フィリピンのデラサール大学ダスマリニャス校で電子工学の学士号を取得しています。

# 著者について

Jermaine Lim-Abrogueñaは、アナログ・デバイセズのシステム・インテグレーション・エンジニアです。 2014年10月に入社しました。COSAPJC(アジア太平洋/日本/中国担当カスタマオフィス・ソリューション)のシステム・モデリング/シミュレーション・グループに所属。アナログ・デバイセズの様々な製品に対応するIBISモデルの開発などに取り組んでいます。マニラ市立大学で電子工学の学士号を取得しました。

# 著者について

Mar Christian Lacidaは、アナログ・デバイセズのアプリケーション・エンジニアです。入社は2018年で、自動試験装置(ATE)グループ(フィリピン カビテ)に所属。スイッチ/マルチプレクサ製品のアプリケーション・サポートとLTspice用のモデルの開発を担当しています。フィリピン工科大学サンタメサ校(マニラ)で電子工学の学士号を取得しました。