# フェーズド・アレイ・アンテナの パターン---- [Part 3] サイドローブとテーパリング

著者: Peter Delos、テクニカル・リード

Bob Broughton、エンジニアリング担当ディレクタ

Jon Kraft、シニア・スタッフ・フィールド・アプリケーション・エンジニア

# はじめに

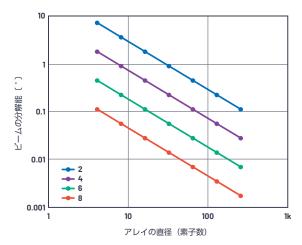

本稿は、フェーズド・アレイ・アンテナのパターンについて解説 するシリーズのPart 3です。Part 1では、フェーズド・アレイ やビーム・ステアリングの概念、アレイの利得について説明しま した。続くPart 2では、グレーティング・ローブとビーム・ス クイントの話題を取り上げました。今回は、まずアンテナのサイ ドローブとアレイに対するテーパリングの効果について考察しま す。ここで言うテーパリングとは、アンテナ全体の振幅応答に対 する各素子の寄与率を操作する処理のことです。

Part 1で示したのは、テーパリングを適用しない状態での結果で した。その場合、第1サイドローブは-13dBcに達していました。 テーパリングを実施すれば、アンテナの利得とメイン・ローブの ビーム幅はある程度犠牲になるものの、サイドローブを低減する ことが可能になります。今回は、このテーパリングについて説明 したうえで、アンテナの利得に関するいくつかの要点について詳 しく解説します。

## 矩形関数とsinc関数の相互変換

電気/電子工学の分野では、ある領域の矩形関数を別の領域の sinc関数に変換するという処理がよく用いられます。最も一般的 に行われるのは、時間領域の矩形パルスを基にsinc関数のスペク トル成分を生成するという処理です。逆に、広帯域のアプリケー ションでは、その広い帯域にわたる成分を時間領域の狭いパルス に変換するという処理がよく行われます。フェーズド・アレイ・ アンテナは、これと同様の処理を実行します。つまり、アンテナ の平面軸に沿った矩形の重み付けに応じ、sinc関数に従ったパ ターンを放射します。

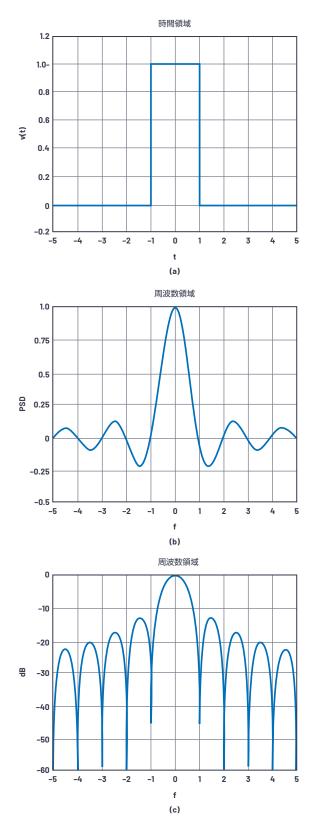

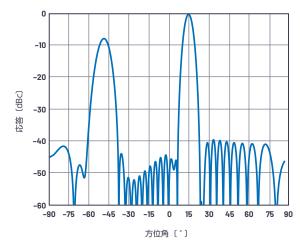

この処理を伴うアプリケーションでは、sinc関数のサイドローブ が問題になります。上述したように、第1サイドローブが-13dBc にも達するからです (図1)。

## テーパリングの効果

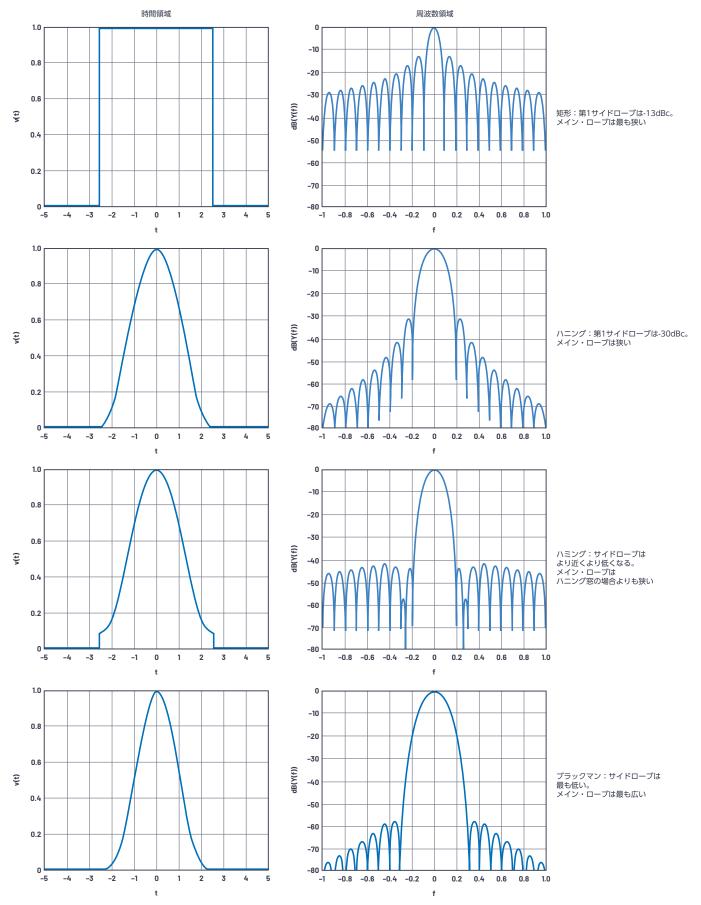

サイドローブの問題の解決策は、矩形パルスにテーパリング(重 み付け)を適用することです。これは、FFT (高速フーリエ変換) を実施する際には一般的に行われています。フェーズド・アレイ でのテーパリングは、FFTで使用される重み付け(重み関数の適 用)によく似ています。ただ、重み付けには、サイドローブが低 減される代償として、メイン・ローブが広くなるという欠点が伴 います。図2に、重み関数の例をいくつか示しました。

#### 波形とアンテナの類似性

ほとんどの技術者にとって、時間領域から周波数領域への変換 は、自然にその様子が思い浮かぶくらい日常的な処理です。しか し、初めてフェーズド・アレイに接する技術者にとって、アンテ ナ・パターンでその類似性を利用するというのは、直観的に理解 しにくいことかもしれません。そこで、ここでは、時間領域の信 号を電界領域の励起で置き換え、周波数領域の出力を空間領域で 置き換えるという手法を考えることにします(以下参照)。

#### 時間領域 → 電界領域

▶ v(t):時間の関数として表される電圧

▶ E(x):アパーチャ内の位置の関数として表される電界強度 周波数領域 → 空間領域

▶ Y(f): 周波数の関数として表されるパワー・スペクトル密度

▶ G(q):角度の関数として表されるアンテナの利得

図 1. 時間領域の矩形パルスを周波数領域の  $\sin$  関数に変換した結果。 第 1 サイドローブは -1 3 dBc に達します。

図2. 重み関数の例

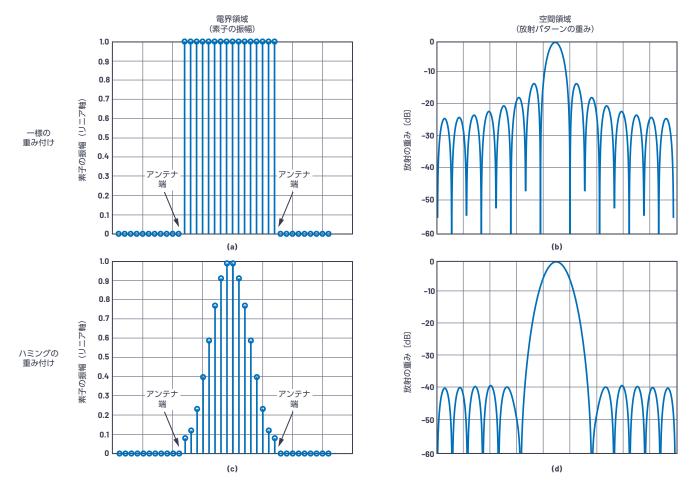

図3. 素子のテーパリングによって重み付けした結果得られる放射エネルギー。 (a) は、全素子に一様な重み付けを適用した結果です。 (b) は、それにより空間的に放射されるsinc関数を表しています。 (c) は、全素子にハミングの重み付けを適用した結果です。 (d) は、それによりメイン・ビームが広くなるという犠牲を払いつつ、サイドローブを40dBcまで抑制した結果を表しています。

図3は、上述した処理の原理を示したものです。ここでは、アレイ全体に2つの異なる重み付けを適用した場合の放射エネルギーを比較しています。図3(a)と図3(c)は、電界領域を示しています。各ドットは、N=16のアレイにおける1つの素子の振幅を表しています。アンテナの範囲外には放射エネルギーは存在せず、放射はアンテナ端から始まります。図3(a)では、電界が急激に変化していますが、図3(c)では、アンテナ端から離れるにつれて電解は徐々に増加しています。図3(b)、図3(d)からは、この特性が放射エネルギーに与える影響を見てとることができます。

次のセクションでは、アンテナ・パターンの性能に影響を及ぼす2つの誤差要因を取り上げます。1つは相互結合です。本稿では、この問題とその影響を定量化するために使用する電磁界モデリングについて認識することを目的として解説を行います。もう1つの誤差要因は、位相シフトを制御するためのビット数が有限であるために生じる量子化サイドローブです。量子化誤差についてはより詳細に解説を行い、量子化サイドローブを定量化する方法を説明することにします。

#### 相互結合による誤差

本稿で考察するすべての式とアレイ・ファクタのプロットは、素子が同一で、それぞれが同一の放射パターンを備えているという 仮定に基づいています。ただ、実際にはそうはなりません。その 理由の1つは、相互結合が存在することです。つまり、隣接する素子間に結合が生じることによって影響が生じます。アレイ内で 広い間隔を取っている場合と間隔が狭い場合とでは、1つの素子の放射性能は大きく異なる可能性があります。また、アレイ端の素子とアレイの中央の素子とでは、周囲の環境が異なります。更に、ビーム・ステアリングが実行されると、素子間の相互結合にも変化が生じます。これらすべての影響により、アンテナの設計者が考慮すべき様々な誤差が生じます。したがって、そうした条件下における放射の影響を評価するためには、電磁界シミュレータが使用されます。ただ、シミュレータを使用したとしても、多くの労力を費やさなければならないことに変わりはありません。

# ビーム角の分解能と量子化サイドローブ

フェーズド・アレイ・アンテナにおいては、機能面でもう1つの問題が発生する可能性があります。その問題は、ビーム・ステアリングに使用する時間遅延ユニット(位相シフタ)の分解能が有限であることから生じます。通常、この処理は、離散時間(または位相)のステップでデジタル的に制御されます。では、ビーム品質の目標を達成するために必要な分解能やビット数は、どのようにして決めるのでしょうか。

誤解されがちですが、ビーム角の分解能は位相シフタの分解能と同等ではありません。これらの関係は、以下の式 (Part 2で式 (2) として示しました)で表されます。

$$\theta = \sin^{-1} \frac{\Delta \Phi \lambda}{2\pi d} \tag{1}$$

この式において、アレイの幅Dを素子の間隔dに代入すると、アレイ全体の位相シフトを表すことができます。次に、位相シフタの $\Phi$ LSBを $\Delta$  $\Phi$ に代入します。すると、ビーム角の分解能を概算することができます。半波長の間隔を空けたN素子のリニア・アレイの場合、ビーム角の分解能は以下の式で示されます。

$$\theta_{RES} \propto \sin^{-1} \frac{\Phi LSB}{N\pi}$$

(2)

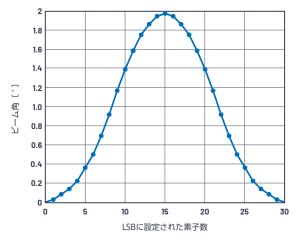

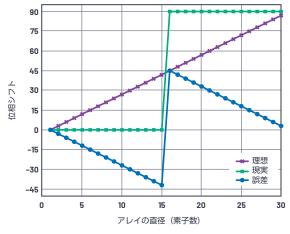

これにより、ボアサイトから離れた位置におけるビーム角の分解能を求められます。アレイの半数の位相シフトがゼロで、残りの半数の位相シフトが位相シフタのLSBである場合のビーム角に相当します。位相のLSBに設定されているアレイが半数より少ない場合には、より小さい角度を実現することが可能です。図4は、2ビットの位相シフタを使用した場合に、30素子のアレイのビーム角がどのようになるのかを表しています。アレイの左から右へ向かって、素子が徐々に位相のLSBに切り替わっていきます。ビーム角は、半数の素子のシフト量がLSBに設定されるまで増加し、すべての素子がLSBになるとゼロに戻ります。これは、ビーム角がアレイ全体の位相差によって変化するということを意味しています。この特性のピークはθRESであることに注意してください。

図4.30素子のリニア・アレイのビーム角と LSBに設定された素子数の関係

図5は、アレイの直径の関数(素子の間隔は $\lambda/2$ )として $\theta_{RES}$ をプロットしたものです。位相シフタの分解能を2~8の範囲 で変化させています。これを見れば、LSBが90°という非常に粗 い2ビットの位相シフタを使用した場合でも、アレイが30素子 であれば、1°の分解能を達成できるということがわかります。 間隔が $\lambda/2$ 、30素子のアレイについてPart 1の式(10)を解 くと、メイン・ローブのビーム幅は約3.3°になります。この結果 は、このような非常に粗い位相シフタでも十分な分解能が得ら れるということを示唆しています。では、より高い分解能の位 相シフタを使用すると、どのような結果が得られるのでしょう か。先述したように、時間に基づいてサンプリングを行うシステ ム(A/Dコンバータ)と空間に基づいてサンプリングを実施す るシステム(フェーズド・アレイ・アンテナ)には類似性があり ます。A/Dコンバータの分解能を高めると、量子化に伴うノイ ズ・フロアは低くなります。それと同様に、位相シフタ/時間シ フタの分解能を高めれば、量子化サイドローブ・レベル(QSLL: Quantization Sidelobe Levels) を低減することができます。

図5. ビーム角の分解能とアレイのサイズの関係。位相シフタの分解能を2ビットから8ビットの範囲で変化させた結果を示しています。

図6は、30素子のリニア・アレイにおける位相シフタの設定と位相誤差の関係を示したものです。2ビットの位相シフタを使用すると仮定し、ビームの分解能は角度  $\theta_{RES}$ に設定しています。また、アレイの半分は位相シフトをゼロとし、残りの半分は90°LSBに設定しています。理想的な位相シフトと量子化された現実の位相シフトの差(誤差)は、鋸歯状に現れることに注目してください。

図6. アレイの直径と位相シフトの関係

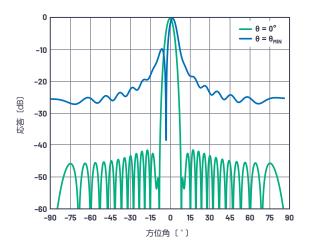

同一のアンテナを0°とビーム分解能の角度にステアリングした場合、アンテナ・パターンは図7のようになります。位相シフタの量子化誤差により、パターンに非常に大きな劣化が生じていることに注目してください。

図7. 量子化サイドローブを伴うアンテナ・パターン。 最小ビーム角に設定した場合の結果を示しています。

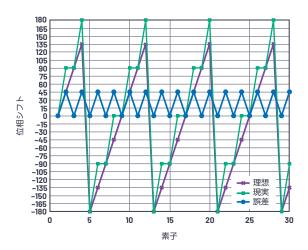

最も厳しい条件(以下、ワーストケース)の量子化サイドローブは、アパーチャ全体で最大の量子化誤差が生じる場合に発生します。つまり、誤差が1つおきにゼロとLSB/2になる場合です。これは、アパーチャ全体で生じうる最大の量子化誤差の大きさと最大の誤差が生じる周期を表しています。図8に、素子数が30、位相シフトが2ビットの条件下で生じる誤差について示しました。

図8. ワーストケースの量子化サイドローブ (位相シフトが2ビットの場合)

この状況は、以下の式に示すように、予想どおりのビーム角で発生しています。

$$\theta_{MAX\,QSLL} = \sin^{-1} \frac{\pm n}{2BITS} \tag{3}$$

ここで、nはビット数であり2未満の奇数となります。2ビットのシステムの場合、この条件は水平線間で $\pm$ 14.5°と $\pm$ 48.6°の計4回満たされます。図9に、n=1、q=14.5°の場合のアンテナ・パターンを示しました。-50°で-7.5dBというかなり大きな量子化サイドローブが発生している点に注目してください。

図9. ワーストケースにおける量子化サイドローブ(位相シフトが2ビット、nが1、素子数が30の場合)

量子化誤差が連続してゼロとLSB/2になる特別なケースを除けば、ビーム角のrms誤差はアパーチャ全体に広がって低く抑えられます。実際、式(3)として示したnが偶数の場合の角度の計算式では、量子化誤差はゼロになります。位相シフタの分解能を変えて最大の量子化サイドローブの相対レベルをプロットすると、興味深いパターンが現れます。

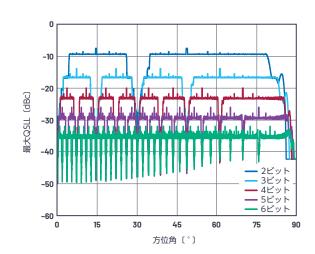

図10は、100素子のリニア・アレイについて、ワーストケースにおけるQSLLがどのようになるのか示したものです。ハミング窓によるテーパリングを適用していることから、量子化サイドローブは、先ほど示した従来の窓関数を適用した場合のサイドローブとは明確に異なります。

30°において量子化誤差がすべてゼロになっている点に注目してください。これは、sin30° = 0.5であることによるものです。n ビットの位相シフタを使用した場合のワーストケースのビーム角については、nがより高い分解能のどのような値であっても、量子化誤差がゼロになることに注目してください。1ビットの分解能あたりQSLLが6dB改善していることに加え、ここで説明したワーストケースのサイドローブに対するビーム角も確認することができます。

図10. ワーストケースにおける量子化サイドローブとビーム角の関係。 位相シフタの分解能を2ビットから6ビットまで変化させています。

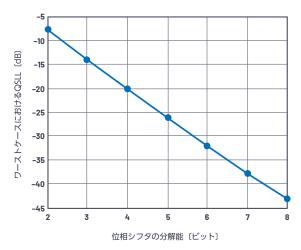

図11に、最大のQSLLと位相シフタの分解能の関係を示しまし た。分解能は2ビットから8ビットまでの間で変化させています。 次式のとおり、よく知られているA/Dコンバータの量子化ノイズ の法則と同様の結果が得られています。

$$QSLL \alpha 20 \log_{10} 2^{-BITS}$$

(4)

つまり、分解能の1ビットは約6dBに相当します。2ビットの場 合、QSLLは約-7.5dBです。A/Dコンバータでランダムな信号を サンプリングする場合は12dBなので、それよりも高くなります。 この差異は、周期的に発生する鋸歯状の誤差がアパーチャ全体で サンプリングされ、空間高調波が同相で加算された結果だと考え られます。QSLLは、アパーチャ・サイズの関数にはならないこ とに注意してください。

図11. ワーストケースにおける QSLL と 位相シフタの分解能の関係

#### まとめ

最後に、アンテナ技術者がビーム幅とサイドローブに関連して直 面するいくつかの課題についてまとめておきましょう。

▶ 角度分解能を高めるためには狭いビームが必要です。狭いビー ムを実現するためには大きなアパーチャが必要であり、多くの 素子を用意しなければなりません。更に、ボアサイトから離れ るとビームが広がるので、走査角度が増加すると、ビーム幅 を維持するために素子を追加する必要が生じます。

- ▶ 素子を追加するのではなく、素子の間隔を広げることでアン テナ全体の面積を増やすことも可能なのではないかと思われ るかもしれません。そうすればビームは狭くなるでしょうが、 残念ながら、素子が等間隔に配置されている場合には、グレー ティング・ローブが生じてしまいます。意図的に素子パターン をランダム化した非周期的なアレイを使用しつつ、走査角度 を小さくすることで、グレーティング・ローブの問題を最小限 に抑えながら、拡大したアンテナの面積を有効に活用すること ができます。

- ▶ サイドローブの問題は、アレイの利得を端に向かってテーパリ ングすることで軽減することができます。しかし、テーパリン グはビーム幅が広がるという犠牲を伴うので、再び素子数を 増やす必要が生じます。位相シフタの分解能によっては、量 子化サイドローブが生じる可能性があるので、そのこともアン テナの設計に織り込む必要があります。位相シフタを使って実 装したアンテナでは、ビーム・スクイント現象の影響で周波数 に依存してビーム角がシフトし、高い角度分解能で利用できる 帯域幅が制限されます。

フェーズド・アレイ・アンテナのパターンについて解説した本シ リーズは以上で終了です。Part 1では、ビーム・ステアリング、 アレイ・ファクタ、アンテナの利得について説明しました。続く Part 2では、グレーティング・ローブとビーム・スクイントの問 題について解説しました。今回のPart 3では、テーパリングと量 子化誤差について考察を加えました。本シリーズは、電磁気学や 放射素子の設計に精通したアンテナ設計技術者ではなく、フェー ズド・アレイの採用を検討している隣接領域の技術者を対象とし ています。そのため、アンテナ・パターン全体の性能に影響を及 ぼす要因について、直感的に理解できるよう配慮しました。本稿 の内容を今後の設計にぜひお役立てください。

# 参考資料

Constantine A. Balanis [Antenna Theory: Analysis and Design. Third edition (アンテナの理論:分析と設計 第3版)」 Wilev、2005年

Robert J. Mailloux [Phased Array Antenna Handbook. Second edition (フェーズド・アレイ・アンテナ・ハンドブック 第2版)」Artech House、2005年

Robert M. O'Donnell [Radar Systems Engineering: Introduction (レーダー・システム・エンジニアリング: 概要)」 IEEE、2012年6月

Merrill Skolnik 「Radar Handbook, third edition (レーダー・ ハンドブック 第3版)」McGraw Hill、2008年

## 著者について

Peter Delos (peter.delos@analog.com) は、アナログ・デバイセズ(米国ノースカロライナ州グリーンズボロ)の航空宇宙/防衛グループに所属するテクニカル・リードです。1990年にバージニア工科大学で電気工学の学士号を、2004年にニュージャージー工科大学で電気工学の修士号を取得。エレクトロニクス業界で25年以上にわたって経験を積み上げてきました。そのうちのほとんどの期間は、アーキテクチャのレベル、プリント基板のレベル、ICのレベルで先進的なRF/アナログ・システムの設計に携わっていました。現在は、フェーズド・アレイ・アプリケーション用の高性能レシーバー、波形発生器、シンセサイザの小型化を図るための設計に注力しています。

## 著者について

Bob Broughton (bob.broughton@analog.com) は、アナログ・デバイセズの航空宇宙/防衛事業部門に所属するエンジニアリング担当ディレクタです。1993年に入社し、プロダクト・エンジニアとIC設計エンジニアの業務を経験しました。アナログ・デバイセズに入社する前は、RaytheonにRF設計エンジニアとして、Peregrine SemiconductorにRF IC設計者として勤務していました。1984年にウェスト・バージニア大学で電気工学の学士号を取得しています。

## 著者について

Jon Kraft (jon.kraft@analog.com) は、アナログ・デバイセズのシニア・スタッフ・フィールド・アプリケーション・エンジニアです。コロラド州を拠点とし、ソフトウェア無線と航空宇宙用フェーズド・アレイ・レーダーを担当しています。勤続年数は13年です。ローズ・ハルマン工科大学で電気工学の学士号、アリゾナ州立大学で電気工学の修士号を取得。9件の特許を保有しており(それらのうち6件はアナログ・デバイセズで取得)、現在も1件を申請中です。