# ppmレベルの精度のオペアンプ回路は 実現できるのか?

著者: Barry Harvey

産業分野や医療分野では、より精度が高く、より高速な製品が求 められ続けています。アナログICの業界は、速度に対する要件 には概して対応できています。しかし、精度に対する要件につい ては、後れをとっている状態にあります。現在では、1ppmの精 度を達成するリニアA/Dコンバータ (ADC) が一般的になりつ つあります。そのため、システム全体についても、1ppmの精度 を求める動きが進んでいます。本稿では、まずシステムの構成要 素であるオペアンプの精度の限界を示します。続いて、1ppmの 精度を達成できる可能性のある数少ないオペアンプ製品を取り上 げ、適切な選択を行う方法を説明します。更に、既存のオペアン プが抱える限界を踏まえつつ、アプリケーション全体としての精 度を改善する方法を紹介します。

より詳しく言うと、精度は正確度 (accuracy) と精度 (precision) に分けられます。正確度は、真の値に対してどれくらい近い値で あるかということを表します。一方の精度は、複数回の測定結果 におけるばらつきを表します。本稿では、ノイズ、オフセット、 ゲイン誤差、非直線性など、システムの限界を表すあらゆる測定 値を対象とし、正確度の意味で精度という用語を使用することに します。

いくつかの指標で見ると、誤差がppmのレベルに抑えられてい るオペアンプICは、数多く存在します。しかし、すべての誤差が ppmレベルのオペアンプICは存在しません。例えば、チョッパ・ アンプであれば、オフセット電圧、DCの直線性、低周波ノイズ は、ppmのレベルに抑えられます。しかし、入力バイアス電流と 周波数に対する直線性についてはそうはなりません。一方、バイ ポーラのオペアンプは、広帯域ノイズが小さく、直線性も良好で す。しかし、入力電流によって回路内で誤差が生じるおそれがあ ります(本稿では、回路内の動作についてもアプリケーションと いう用語で表現することにします)。MOSのオペアンプは、バイ アス電流については優れた性能を発揮します。しかし、低周波ノ イズと直線性の面で問題があることが少なくありません。

本稿では、伝達関数における1ppmの非直線性が、-120dBcの 高調波歪みとほぼ等価であると見なすことにします。

# 精度が ppm のレベルに達しないアンプ

まずは、直線性が高いとは言えないタイプのオペアンプを取り上 げます。最も直線性に劣るのは、いわゆるビデオ・アンプやライ ン・ドライバ・アンプです。これら広帯域対応のアンプは、DC 精度が高くありません。オフセットは数mV、バイアス電流は1  $\mu$ A~50 $\mu$ Aのレベルです。また1/fノイズが高いものが多い ことも特徴の1つです。予測されるDC精度は0.3%~0.1%です が、AC歪みは-55dBc~-90dBcにも達する可能性があります (直線性は2000ppm~30ppm)。

次に挙げるのは、「OP07」のような昔ながらの設計を採用したオ ペアンプです。ゲイン、CMRR (同相ノイズ除去比)、PSRR (電 源電圧変動除去比)が高く、オフセットとノイズもまずまずです。 しかし、特に負荷が1kΩより重くなると、歪みを-100dBc以下 に抑えることができません。

また、新旧にかかわらず、安価なアンプは負荷が10k Ωより重く なると、せいぜい-100dBc程度までしか歪みを抑えられません。

一方、オーディオ・アンプに相当するオペアンプ製品の場合、か なり安価であるのにもかかわらず、歪み性能が非常に高いものが あります。但し、オフセットと1/fノイズを抑えるようには設計 されていないため、それらの性能は良好ではありません。また、 この種のアンプも、おそらく10kHzを超える領域では、高い歪み 性能を発揮することはできないはずです。

MHzレベルの信号に直線的に対応できるオペアンプがあります。 通常はバイポーラ構造で実現されており、入力バイアス電流が多 く、1/fノイズが大きくなります。-80dBc~-100dBc程度の性 能が求められる用途向けの製品であり、ppmのレベルの性能を 得ようとするのは現実的ではありません。

電流帰還アンプは、どれだけ帯域が広く、どれだけスルー・レー トが高くても、高い直線性はおろか、それなりの精度さえも得ら れません。その入力段には誤差源が遍在していることに加え、ゲ イン、入力性能、PSRRもあまり良好ではないからです。また、 電流帰還アンプでは、セトリング時間が長くなる原因となる温度 ドリフトも発生します。

一般に、最新の汎用オペアンプは1mVのオフセット、数μVの 1/fノイズを実現します。歪み性能も-100dBcほどに達しますが、 負荷が重い場合には、そこまでの性能は得られないことがほとん どです。

## オペアンプの誤差源

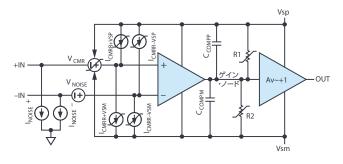

図1は、オペアンプの簡略化されたブロック図に、ACとDCの 誤差源を追加したものです。単極アンプと、出力向けにバッファ されるゲイン・ノードを駆動する入力gm段で構成されています。 実際のオペアンプは様々な構成で実現されますが、この図に示した誤差源は、それらすべての構造に当てはまります。

図1. オペアンプのブロック図。様々な誤差源を描き加えています。

### 入力ノイズ

入力電圧ノイズ $V_{NOISE}$ を周波数軸で見ると、広帯域ノイズの成分と 1/f ノイズの成分が存在することがわかります。システムで使用しているオペアンプのノイズの振幅が、システムのLSB と同等かそれ以上に達する場合には、信号を正確に測定することはできません。例えば、広帯域ノイズが  $6nV/\sqrt{Hz}$ で、システムの帯域幅が 100kHzである場合、入力ノイズは  $1.9 \mu Vrms$ です。このノイズはフィルタで抑えることができます。例えば、帯域幅を 1kHzに下げると、ノイズは  $0.19 \mu Vrms$ (ピーク  $1 \mu V$ P-p)に低下します。ローパス・フィルタを使うことにより、ノイズの振幅を抑えることができます。

一方、1/f ノイズは周波数が低い領域に発生します。そのため、フィルタで除去したり平均化したりするのが困難です。1/f ノイズは、0.1Hz  $\sim$  10Hz の帯域に生成されるピーク1to ピークの電圧 ノイズです。ほとんどのオペアンプでは、低周波領域のノイズは  $1 \mu V P$ -1 P0~1 P0 1 P0

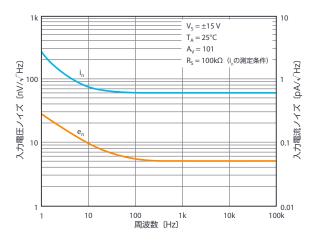

図2に、高精度のオペアンプIC [LT1468] の電流ノイズと電圧 ノイズを示しました。

図2.LT1468の入力電圧ノイズと入力電流ノイズ

図1の入力部には、バイアス電流に起因するノイズ $I_{NOISE}$ +と $I_{NOISE}$  (以下、2つをまとめて $I_{NOISE}$ と表記します)が存在します。これらにも、広帯域ノイズの成分と1/f ノイズの成分の両方が含まれます。 $I_{NOISE}$  により、アプリケーションで使用する抵抗(以下、アプリケーション抵抗)の値との乗算で決まる電圧ノイズが生成され、入力電圧ノイズが更に大きくなります。一般に、これら2つの電流ノイズは互いに非相関であり、等価な入力抵抗によって打ち消されることなく、RMS形式で加算されます。かなり高い確率で、 $I_{NOISE}$  とアプリケーション抵抗の値との乗算値は、1/f ノイズの領域において入力電圧ノイズ $V_{NOISE}$  よりも大きくなります。

# コモン・モード除去比(CMRR)と オフセット誤差

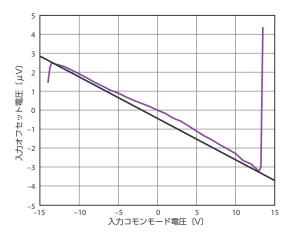

次に取り上げる誤差源はV<sub>CMRR</sub>です。これは、両方の電源レール を基準とする入力レベル (いわゆるコモンモード電圧 V cm) に応 じてオフセット電圧が変化するというCMRRの仕様に対応する 現象です。図2で使用している記号において、矢印は電源からの 作用を表します。また、セグメント化されたラインは、可変だが 線形ではない可能性があるということを表しています。CMRRが 信号に与える主な影響としては、線形の要素がゲイン誤差と区 別できなくなるということが挙げられます。なお、非線形の要素 は歪みになります。図3に示したのは、高精度のオペアンプIC [LT6018] のCMRR特性です。紫色の曲線がCMRRを表してい ます。黒い直線は、CMRRの曲線が過負荷の状態へと逸れていく 手前の点を結んだものです。この直線の傾きから、CMRR性能と して133dBという値が得られます。CMRRの曲線は、30Vにわ たる完全な直線に対して、わずか 0.5 μ V しか逸脱していません。 つまり、1ppm未満の入力精度を軽々と達成しています。なお、 他のオペアンプICでは、CMRRの曲線がこれよりもはるかに大 きく湾曲する可能性があります。

図3. LT6018の入力オフセット電圧とV<sub>CM</sub>の関係

ここでは、オフセット電圧 $V_{OS}$ はCMRRと一括りにして扱います。一般に、チョッパ・アンプの入力オフセット電圧は $10 \mu V$ 未満です。2Vp-p~10Vp-pの標準的な信号に対し、誤差はほぼ数ppmと見なすことができます。最高の精度を誇るADCであっても、オフセット電圧は最大で $100 \mu V$ ほどに達します。したがって、オペアンプのオフセット電圧がもたらす影響は、さほど大きくありません。また、いずれにせよ、システムではオートゼロの処理を実行する必要があります。入力信号のコモンモード・レベルに関連するのは、入力バイアス電流と、電源に伴うその変化である $I_{CMRR}$ です。

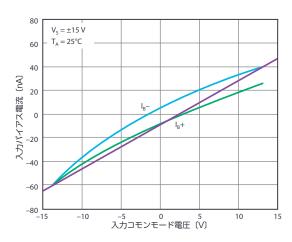

図1に示したように、 $I_{CMRR}$ は 4つに細分化されます。記号の折れ線は、バイアス電流が電圧に応じて可変であり、線形でない可能性があるということを表しています。2つの入力のバイアス電流とレベルへの依存度は異なる可能性があります。また、各入力は、両方の電源に応じて独立して変化します。 $I_{CMRR}$ (合算することによりバイアス電流が決まります)により、アプリケーション抵抗の値との乗算で決まる電圧ノイズが生成され、回路全体のオフセット電圧が増加します。図4は、LT1468のバイアス電流とV<sub>CM</sub>の関係を表したものです( $I_{CMR}$ の仕様)。追加されている紫色の直線の傾きは約8nA/Vです。アプリケーション抵抗が1k  $\Omega$ ならば8  $\mu$  V/V となり、ppm レベルの精度が得られることがわかります。直線からの逸脱は約15nAであり、アプリケーション抵抗が1k  $\Omega$ であれば誤差は26Vに対して15  $\mu$  Vで、非直線性は0.6ppmとなります。

図 4. LT1468の入力バイアス電流と V<sub>CM</sub>の関係

# 入力段の歪み

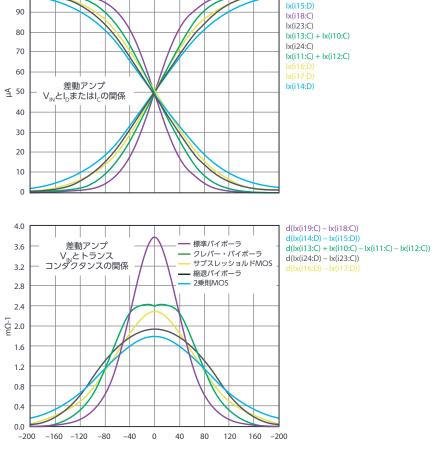

図1に示した入力段は、一般的には、トランジスタの差動ペアによって構成されたトランスコンダクタとして実現されます。図5 (上)のグラフは、様々な種類の差動アンプにおける差動入力電圧とコレクタ電流またはドレイン電流の関係を表しています。これは、以下の各トランジスタを対象とし、テール電流が100  $\mu$  A という条件でシミュレーションを実施した結果です。

- ▶ 標準的なバイポーラ・トランジスタ・ペア(以下、標準バイポーラ)

- ▶ トランスリニア回路(以下、クレバー・バイポーラ)

- ▶ サブスレッショルド領域で動作する(非常に大きい)MOS 差動トランジスタ・ペア(以下、サブスレッショルド MOS)

- ▶ エミッタ抵抗付きのバイポーラ・トランジスタ・ペア(以下、縮退バイポーラ)

- ▶ サブスレッショルド領域外にあり2乗則で動作する小さな MOSトランジスタ・ペア(以下、2乗則MOS)

より多くの情報を得るためには、図5(下)に示したトランスコンダクタンス $g_m$ と入力電圧 $V_{IN}$ の関係を確認する必要があります。 $g_m$ とは、入力電圧に対する出力電流の変化量のことです。ここでは、シミュレータとして「LTspice®」を使用して計算を行っています。 [d()] として示している式は、 $[d()/d(V_{INP})]$  と数学的に等価です。 $g_m$ のグラフは平坦になりませんが、これは周波数軸におけるオペアンプの歪みの基本的な性質に影響を及ぼします。

図5. 様々な差動アンプのシミュレーション結果。(上) は入力電圧と出力電流の関係、 (下) は入力電圧とトランスコンダクタンスの関係を表しています。

出力バッファのゲインがほぼユニティであると仮定すると、DCにおいて、オペアンプのオープンループ電圧ゲインは、およそgm(R1¦¦R2)となります。R1とR2は、信号パス上にある様々なトランジスタの出力インピーダンスで、それぞれ正負の電源レールに接続されています。オペアンプのゲインが制約を受ける基本的な理由はここにあります。R1とR2は線形であるという保証はなく、無負荷の状態における歪みや非直線性の原因になります。直線性の問題だけでなく、ppmのレベルでゲインの精度を得るには、100万近く、あるいはそれ以上のゲインが必要です。

標準バイポーラのグラフを見ると、トランスコンダクタンスの値は最も大きいものの、入力が0Vからずれると急速に低下しています。ゲインまたは $g_m$ が一定であることが直線性を得るための基本的な要件なので、この特性には問題があります。一方、オペアンプの電圧ゲインが非常に高く、出力が数V変化するのに、差動入力は数 $\mu$ Vしか変化しないということには何ら問題はありません。そこで追加されるのが $C_{COMP}$ です。

$C_{COMP}$ (図1の $C_{COMPP}$ と $C_{COMPM}$ の並列構造)は、一定の周波数範囲にわたって $g_m$ の出力電流の大部分を吸収します。これにより、オペアンプのゲイン帯域幅積(GB積、GBW)が決まります。周波数fにおけるオペアンプのオープンループ・ゲインはGBW/fとなります。fがGBW/10、クローズドループ・ゲインが1、オペアンプの出力が1VP-pである場合、入力間の電位差は100mVp-pとなります。平衡状態から見て $\pm 50mV$ ということです。図5のグラフによると、標準バイポーラでは、 $\pm 50mV$ でゲインが半分になるので、大きな歪みが生じます。それに対し、クレバー・バイポーラのゲインは13%しか低下しません。サブスレッショルドMOSでは26%、縮退バイポーラでは12%、2乗則MOSでは15%低下します。

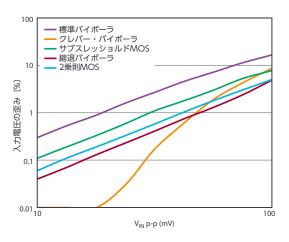

図6は、入力電圧の振幅と入力段の歪みの関係を表したものです。これは、(ノイズ・ゲインと乗算した形で)アプリケーション回路の出力に現れます。出力の歪みはこれ以上になる可能性がありますが、これ以下になることはありません。

図6. 入力段における差動入力電圧と全高調波歪みの関係

クレバー・バイポーラを除く各差動アンプでは、入力電圧の2乗に比例する歪みが生じます。ユニティ・ゲインのアプリケーションでは、入力の歪みがそのまま出力の歪みに影響を及ぼします。これが、多くのオペアンプにおける支配的な歪み源になります。

ここで、バイポーラ入力を備えるユニティ・ゲイン・バッファを考えます。ピークtoピークの出力電圧を $V_{OUT}$ とすると、入力差動信号は次のようになります。

$$f_{SIGNAL} \times \frac{V_{OUT}}{GRW}$$

(1)

ここで、以下のような仮定を行います。

%Distortion<sub>INPUT</sub> =

$$0.3\% \times \left(\frac{V_{IN} p-p}{10 \text{ mV}}\right)^2$$

(2)

%Distortion<sub>OUTPUT</sub> =

$$G_{NOISE} \times$$

%Distortion<sub>INPUT</sub> =

$$0.3\% \times \left(\frac{V_{OUT}, p-p \times f_{SIGNAL}}{10 \text{ mV} \times \text{GBW}}\right)^{2}$$

(3)

ここで、G<sub>NOISE</sub>は、アプリケーションにおけるノイズ・ゲインです。

1ppmの非直線性は、-120dBcの高調波歪み (0.0001%) とほぼ等価です。バイポーラの入力段を備えるオペアンプを使用し、GB積が15MHz、バッファとしての出力が5Vp-pになる状況を考えます。その場合、式 (2) から、1ppmのレベルの直線性が得られる最大周波数はわずか548Hzとなります。ただ、このオペアンプを使用した場合、少なくとも低い周波数領域では、それだけの直線性が得られると言うこともできます。当然のことながら、オペアンプ回路によってゲインを得る場合には、ノイズ・ゲインが増加し、-120dBcを達成できる周波数はより低くなります。

-120dBc を達成する最大周波数は、入力段がサブスレッショルド MOS である場合に866Hz、2乗則MOS である場合に1342Hz、縮退バイポーラである場合に1500Hzとなります。クレバー・バイポーラの場合、このような歪みの予測方法は適用できないので、データシートで推定値を確認する必要があります。

出力の歪みは、以下に示すより簡単な式を使って求めることもできます。

%Distortion<sub>OUTPUT</sub> =

$$K \times G_{NOISE} \times \left(\frac{V_{OUT}, p-p \times f_{SIGNAL}}{GBW}\right)^{2}$$

(4)

ここで、Kは、オペアンプICのデータシートに記載されている歪み性能のグラフから得ることができます。

余談になりますが、レールtoレールの入力段を備えるオペアンプICは、数多く提供されています。ほとんどの製品は、2つの独立した入力段を備えており、入力コモンモード範囲の途中で一方から他方へのハンドオフ(引き継ぎ)を行うことにより、レールtoレール入力を実現しています。このハンドオフによってオフセット電圧が変化し、バイアス電流、ノイズ、更には帯域幅までもが変動する可能性があります。また、このハンドオフは出力におけるスイッチング・トランジェントの原因にもなります。信号がクロスオーバー領域を横切ることがある場合、この種のアンプを使用して高い歪み性能を得ることはできません。ただ、反転アプリケーションであれば、良好な結果が得られる可能性があります。

ここで、スルーエンハンスド・アンプ(Slew-enhanced Amplifier)について触れておきます。この種のアンプでは、差動入力が大きい場合、電流が不足することはありません。差動入力が小さい場合には、その入力振幅と同程度の変化がgmに生じます。歪みを抑えるには、やはり対象とする周波数において大きなループ・ゲインが必要になります。

本稿では、ppmのレベルの歪みを求めているので、スルー・レートの上限近くでオペアンプを動作させることは想定しません。したがって、スルー・レートは、対象とする周波数におけるppmレベルの直線性に対して重要なパラメータとはなりません。重要なのはGB積だけです。

オープンループ・ゲインについては、単極補償の設計を前提として説明しました。もちろん、すべてのオペアンプがこの方法で補償されるわけではありません。一般に、オープンループ・ゲインは、データシートのグラフから得られます。式中のGBW/( $G_{NOISE}$  ×  $f_{SIGNAL}$ )は、対象とする周波数におけるオープンループ・ゲインです。

#### ゲイン・ノードの誤差

次に取り上げるのは、図1のR1とR2です。これらの抵抗と入力部の $g_m$ から、オペアンプのオープンループのDCゲインは $g_m$ × (R1¦¦R2)となります。図1において、両抵抗は、値が可変で非線形であることを表す取り消し線付きの記号で描かれています。両抵抗の非直線性は、無負荷の状態におけるオペアンプの歪みとして現れます。また、R1は正の電源に対するDCのPSRR (PSRR+)という形で回路に影響を及ぼします。その大きさは $g_m$ × R1とほぼ等しくなります。同様に、R2は、負の電源に関するPSRR-に関連づけられます。PSRRの大きさは、オープンループ・ゲインとほぼ同じになることに注意してください。 $C_{COMPP}$ と $C_{COMPM}$ には、R1、R2と同じように、電源の信号が印加されます。それらにより、周波数に対するPSRR+とPSRR-が決まります。

ゲインが 10<sup>6</sup> よりかなり小さいオペアンプでも、直線性が高いことはあり得ます。ただ、ゲインがそのレベルであった場合、ゲインの精度には限界があります。

電源端子は歪みの原因になる可能性があります。出力段が重い負 荷を駆動している場合、負荷に対する電流は、一方の電源から流 れます。周波数軸で見たとき、遠くにある電源にレギュレーショ ン能力がほとんどなく、オペアンプのバイパス・コンデンサが事 実上の電源として働くケースがあります。その場合、電源電流 は、バイパス・コンデンサを介して減少します。この電源電流の 減少は、等価直列抵抗 (ESR)、等価直列インダクタンス (ESL)、 リアクタンスに依存し、電源に乱れを引き起こします。オペアン プの出力がAB級である場合、出力電流波形の半分だけが電源に 変調を加え、偶数次の高調波歪みが生成されます。オペアンプの PSRRは、一定の周波数範囲において電源の乱れの影響を低減す る能力を表す指標です。例えば、50mVp-pの電源変動が観測さ れる状態で、PSRRによって5μVp-p未満の入力の乱れによる影 響を抑えたい場合には、対象となる信号の周波数において80dB のPSRRが必要です。PSRR(f)をAvol(f)と近似すると、GB積が 15MHzのオペアンプでは、1500Hz以下の周波数において十分 なPSRRが得られます。

## 出力段の歪み

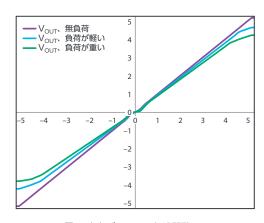

最後に取り上げる要素は図1の出力段です。ここでは、出力段は バッファであると仮定します。標準的な出力段の伝達関数は、図 7のようになります。

図7. 出力バッファの伝達関数。 負荷を変化させた場合の特性を示しています。

負荷の違いに応じて、出力段では4種類の誤差が生じます。1つ目の誤差源はクリッピングです。ここでは、出力段の公称ゲインは1で、完全なレールtoレール出力ではないと仮定します。この回路の出力は、無負荷の状態でも各電源レールから100mVほどのところでクリッピングします。出力は負荷が重くなる(負荷の抵抗値が小さくなる)に従い、より電源レールから遠い電圧でクリッピングするようになります。クリッピングが生じるということは、歪みが大きくなるということです。それを防ぐには、出力振幅を小さくする必要があります。

2つ目の誤差源はゲインの圧縮です。これは、動作限界付近の信号に対して伝達関数の湾曲として現れます。圧縮は、負荷の増大に伴ってだんだん条件の緩い電圧で生じるようになります。クリッピングと同様に、圧縮が生じると、ppmレベルの歪みを達成するのは不可能になります。

圧縮は出力段の能力が低く、必要な電流を出力するのが精いっぱいであることに起因して発生します。オペアンプから得られる線形で圧縮が生じない最大の出力電流は、出力短絡電流のわずか35%程度です。これは確かな経験則として言えることです。

3つ目の顕著な誤差源(歪み源)は、0Vの入力電圧付近にある クロスオーバー領域です。無負荷の状態では、クロスオーバー領域の問題は目立たないかもしれません。しかし、負荷が重くなる と、図7の緑色の曲線のように、問題が顕著になります。クロスオーバー歪みを除去するには、十分な電源電流が必要になります。

4つ目の歪み源は、上記の3つよりも気づきにくい性質のものです。オペアンプ回路には、正の電圧と電流を出力する部分と、負の信号を出力する部分があります。特に負荷が存在する場合には、両者のゲインは同じであるとは限りません。図7を見ると、負荷が存在する場合には、負の信号のゲインの方が低いことがわかります。

上記のすべての歪みは、ループ・ゲインが高ければ抑えられます。出力段の歪みが3%の場合、-120dBcのレベルを達成するには、3万のループ・ゲインが必要です。当然のことながら、そのレベルが得られるのは、周波数がGBW/(30000×G<sub>NOISE</sub>以下の場合です。この値は、GB積が15MHzのアンプの場合で1kHz程度になります。

出力段の一部の歪みは周波数に依存します。オープンループ・ゲインが高ければ出力段の歪みは抑えられますが、同ゲインは周波数が高くなるほど低下します。出力の歪みが周波数に対して一定である場合もありますが、ゲインが低下すると、出力の歪みも周波数に比例して大きくなります。それとは別に、入力の歪みに起因して、トータルの出力歪みは周波数が高くなるほど増大します。その場合、おそらくクローズドループにおけるトータルの出力歪みを、入力の歪みが支配するようになります。言い換えると、出力段で発生する歪みの寄与分は、取るに足らないものになります。

例えば、出力段の歪みが周波数に比例して変化するとします。その場合、ループ・ゲインが低下すると、周波数の2乗に比例する更なる出力歪みが生成されます。これは、入力歪みと区別できない形で追加されます。

消費電力の少ないオペアンプでは、出力段の自己消費電流も少なく抑えられています。これは、電流が不足気味な状況だと言うことができます。このようなオペアンプでは、入力段よりも出力段が出力歪みの支配的な要因になる可能性があります。低歪みのオペアンプを構成するには、少なくとも2mA程度の電源電流が必要だと言えるでしょう。

## ppmレベルの精度に必要な仕様

実用的なレベルシフト、減衰/増幅、アクティブ・フィルタを実現するオペアンプ回路で、 $1k\Omega$ の負荷、 $\pm 5V$ の信号を処理するケースを考えます。この条件下で1ppmの直線性を達成するためには、オペアンプは、表1に示すような基本的な要件を満たす必要があります。

表 1. ppm レベルの精度を得るために必要なオペアンプの仕様

| 仕様                                              | 値                               | 説明                                                                 |  |  |

|-------------------------------------------------|---------------------------------|--------------------------------------------------------------------|--|--|

| V <sub>NOISE</sub>                              | < 6nV/√ Hz                      | 広帯域の入力電圧ノイズ                                                        |  |  |

| V <sub>NOISE</sub> (0.1Hz~10Hz)                 | < 1ppm、<br>ピークtoピーク値、<br>フルスケール | 低周波域の入力電圧ノイズ                                                       |  |  |

| I <sub>NOISE</sub>                              | < 6pA/√ <del>Hz</del>           | 広帯域の入力電流ノイズ                                                        |  |  |

| I <sub>NOISE</sub> (0.1Hz~10Hz)                 | < 10nA、<br>ピークtoピーク値、<br>フルスケール | 低周波域の入力電流ノイズ                                                       |  |  |

| V <sub>os</sub>                                 | < 200µV                         | 入力オフセット電圧。通常<br>はデジタルで補正される                                        |  |  |

| CMRR                                            | > 100dB                         | 入力同相ノイズ除去比。<br>ゲイン誤差は10ppm未満                                       |  |  |

| CMRRの直線性                                        | > 120dB                         | CMRR性能の湾曲具合                                                        |  |  |

| I <sub>BIAS</sub>                               | < 200nA                         | 入力バイアス電流。<br>1kΩの抵抗値を乗じた<br>値はV <sub>os</sub> 未満                   |  |  |

| $I_{\rm BIAS}$ vs. $V_{\rm CM}$ $(I_{\rm CMR})$ | < 10nA/V                        | 1kΩの抵抗値を乗じた値<br>は10ppmのゲイン<br>誤差未満                                 |  |  |

| I <sub>BIAS</sub> vs. V <sub>CM</sub> の直線性      | < 1nA~5nA                       | 1kΩの抵抗値を乗じた値<br>は1ppm(フルスケール)                                      |  |  |

| PSRR                                            | > 90dB<br>(一部の帯域で)              | 電源電圧変動除去比。 $50 \text{mV}$ の電源変動に $対し、V_{\odot}$ のずれは $1.6\mu V$ 未満 |  |  |

| GB積                                             | > 1000× [信号<br>帯域幅]             | ゲイン帯域幅積。<br>歪みを抑えるためには<br>高いGB積が必要                                 |  |  |

| 線形出力電流                                          | > 15mA                          | 歪みを抑えるためには<br>高い値が必要<br>(出力短絡電流の35%)                               |  |  |

| DC V <sub>os</sub> vs. V <sub>out</sub><br>の直線性 | < 1ppmの非直線性                     | DCの直線性が低ければ、<br>ACの直線性も得られない                                       |  |  |

オペアンプの性能に限界があることから、ppmレベルの精度を 達成するのは容易ではありません。では、どのようにすれば、こ の状況を改善できるのでしょうか。

まず行うべきことは、アプリケーション抵抗のトータルのノイズ よりも入力ノイズ電圧が小さいオペアンプを選択することです。 アプリケーション抵抗のノイズは、回路全体のインピーダンスを 下げることにより抑えることができます。もちろん、アプリケーションのインピーダンスを下げると、信号のやり取りに伴う電流 が増加すると共に、負荷に起因する歪みが大きくなる可能性があります。 ただ、どのような場合でも、オペアンプ段の出力ノイズ を、それが駆動する段の入力ノイズよりもはるかに低いレベルまで引き下げる必要はありません。

電流ノイズは、アプリケーションのインピーダンス値との乗算で決まる電圧ノイズを生成します。MOSベースの入力部は、電流ノイズが非常に小さいという点で魅力的です。しかし、バイポーラ・ベースの入力部よりも1/f電圧ノイズが高くなる傾向があります。バイポーラ・ベースの入力部では、pA/√Hzレベルの電流ノイズが生じ、アプリケーション全体のノイズに少なからず影響を及ぼします。一方で、1/f電流ノイズは、アプリケーションにおいて、オペアンプ全体としての1/f電圧ノイズよりも大きな電圧ノイズを生成する可能性があります。

一般的な経験則として、アプリケーションのインピーダンスをオペアンプの $V_{NOISE}/I_{NOISE}$ よりも低くし、 $I_{BIAS}$ によって支配されるアプリケーション・レベルのノイズを防ぐということが行われています。バイポーラ・ベースのオペアンプでは、 $V_{NOISE}$ が低いほど $I_{NOISE}$ が高くなります。

# オペアンプの性能を引き出す方法

#### 入力誤差の低減

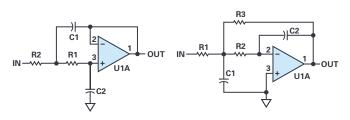

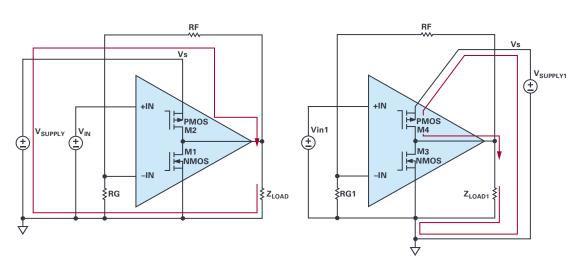

卓越したCMRR性能を備えるオペアンプを選択するというのは1つの手ですが、基本的な考え方として、非反転回路ではなく反転回路としてオペアンプを使用することが推奨されます。反転回路において、グラウンドなどのリファレンスを基準とする入力は、CMRR誤差を全く生成しないからです。ただ、すべてのアプリケーション回路を反転構成にできるわけではありません。また、負の方向への信号の変化に対応するための負電源が使用できないケースもよくあります。図8に、2極のサレンキー・フィルタを非反転構成と反転構成で実装した例を示しました。

図8. サレンキー型のアクティブ・フィルタ。 (左) は非反転構成、(右) は反転構成で実現しています。

両方の入力にアプリケーション抵抗を配置し、各入力のバイアス電流が適切なリアクタンスによって出力誤差として相殺されるようにします。そうすれば、 $I_{CMR}$ 誤差を相殺できます。例えば、アンプのゲインが 10、フィードバック抵抗が 900  $\Omega$ 、グラウンドに接続する抵抗が 100  $\Omega$ である場合、非反転入力ピンに 90  $\Omega$ の直列抵抗を接続すれば、出力において全く同じ大きさのバイアス電流を相殺することが可能です。バイポーラをベースとするほとんどのオペアンプでは、バイアス電流は高い精度で一致します。そのため、一般的な 1% 精度の抵抗ではなく、0.1% 精度の抵抗を選択すれば、 $I_{CMR}$  を最大限に除去できます。図8に示した回路の場合、補償用の抵抗は、各反転入力に直列に配置します。その

際には、補償用の抵抗をバイパスするパスを設ける必要があるかもしれません。また、残念ながら、入力部に抵抗を追加すると、 ノイズに対する影響は大きくなります。

反転増幅回路では、信号がスイッチング・ポイントを横切らない 状態でレールtoレール入力のオペアンプを使用することができ ます。電源とコモンモード入力レベルをバイアスし、スイッチン グ・ポイントの電圧を回避するようにすれば、その状態を作るこ とが可能です。

#### 電源に関する考察

出力電流は、ローカルの電源電圧に変調を生じさせます。ただ、 電源は変動するものの、入力に対してはPSRRの効果が働きます。 その状態の入力によって、ループを流れる出力信号が生成されま す。ローカルの電源に $1\mu$ Fのバイパス・コンデンサを付加して いる場合、1kHzにおけるインピーダンスは159Ωです。つまり、 電源までのラインと電源自体のインピーダンスの合計と比べては るかに小さくなります。そのため、ローカルのバイパス・コンデ ンサは、10kHz以下では実質的に何の効果ももたらしません。 1kHzでは、リモートの電源がレギュレーションの制御を担いま す。1kHzにおいて、オペアンプのPSRRは90dB程度です。一方、 オペアンプの電源端子から流れる電流の大部分は、信号の偶数次 高調波に依存して発生します。これらのことを考慮し、120dBc の目標を達成するには、出力から電源までのゲインを30dB未満 にする必要があります。ゲインを30dBにするには、電源のイン ピーダンスが負荷のインピーダンスの1/30よりも小さくなけれ ばなりません。例えば、負荷が500Ωであるとしたら、電源のイ ンピーダンスは17Ω未満でなければならないということです。 これは実現可能な数字ですが、電源とオペアンプの間に、直列の アイソレーション抵抗やインダクタを配置することができなくな ります。10kHzでは更に条件が厳しくなります。PSRRは90dB から70dBに低下し、電源のインピーダンスも1.7Ωまで低下し ます。この条件に対応するのは不可能ではありませんが、容易で はありません。ローカルのバイパス・コンデンサとして値の大き いものを使用すれば、問題は緩和されます。

プリント回路基板のレイアウトの観点からは、図9に示すように、 出力における電流ループの流れを確認することが重要です。

図9. 負荷と電源の電流ループ

図9(左)の回路図では、電源から負荷に対して流れ込んだ正の電源電流がグラウンドを通って負荷に再び戻ってきます。この場合、グラウンドのパス全体を通して電圧降下が生じる可能性があります。例えば、偶数次の高調波に依存する電源電流は、信号源から出力まで、また帰還分圧器から出力または入力のグラウンドまでの電圧を降下させます。このような電圧の変動が生じてしまっては、グラウンドの意味をなしません。図9(右)は、電源に関するより良いルーティング方法を示したものです。こちらでは、電源電流が入力ノードと帰還ノードを通らないようにルーティングされています。

100kHzを超える高い周波数では、電源ラインの磁気放射が歪み源になる可能性があります。偶数次の高調波に依存する電源電流は、入力または帰還回路に対して磁気結合します。その結果、周波数に依存して歪みが著しく増大します。このような周波数への依存性に対応するためには、慎重なレイアウトが不可欠です。オペアンプ製品の中には、標準的なものとは異なるピン配列を採用しているものがあります。例えば、電源ピンを入力ピンから遠ざけた製品や、磁気的な作用を避けるために入力側に出力端子を配置した製品などが存在します。

#### 負荷が支配的な要因となる歪みの低減

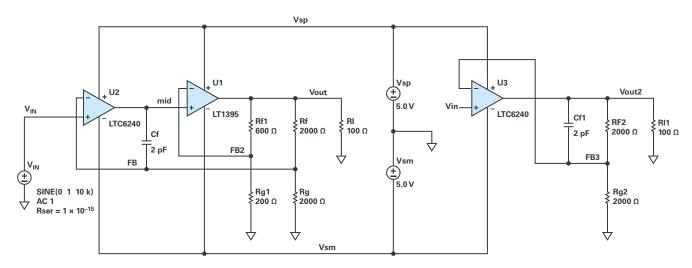

多くの場合、負荷が重くなると、オペアンプの出力段が支配的な 歪み源になります。この問題は、いくつかの手段によって改善す ることができます。その1つは、複合アンプを使用することです。 図10に示すように、1つのオペアンプで出力を駆動し、別のオペ アンプでそれを制御します。 図10の回路図を使用して、LTspiceによるシミュレーションを実施しました。「LTC6240」と「LT1395」の両オペアンプICには、歪み特性を反映したマクロモデルが用意されています。マクロモデルの多くは、歪みに全く対応していません。対応しているとしても、シミュレーションで得られる値は不正確であることが少なくありません。両オペアンプについては、マクロモデルのテキストを参照し、かなり適切に歪みがモデル化されていることを確認済みです。

図10の右側には、LTC6240を使用して構成したゲインが2の 増幅回路が配置されています。これにより、100Ωの負荷を駆動 します。100Ωというのは、同ICにとっては厳しい条件です。 図10の左側には、もう1つのLTC6240とLT1395を使って入力 用の複合アンプを構成しています。広帯域に対応する電流帰還 アンプにより、スタンドアロン・アンプ (LTC6240を使用して 構成した右側の増幅回路) と同じ負荷を駆動します。この複合ア ンプは、出力用のオペアンプの歪みが既にある程度低い場合に、 一定の周波数範囲を対象とし、その歪みを入力アンプのループ・ ゲインによってさらに低減しようというものです。スタンドアロ ン・アンプと複合アンプのクローズドループ・ゲインはいずれも 2です。ただ、複合アンプでは、LT1395にもゲインを設定して いるので (Rf1とRg1によって4を設定)、制御アンプ (左側の LTC6240で構成したアンプ回路)の出力振幅を抑えることがで きます。入力に起因する歪みは、出力振幅の2乗に比例して増加 するので、制御アンプの歪みは更に抑えられます。

図 10. 歪みのシミュレーション用回路。スタンドアロン・アンプと複合アンプを対象としています。

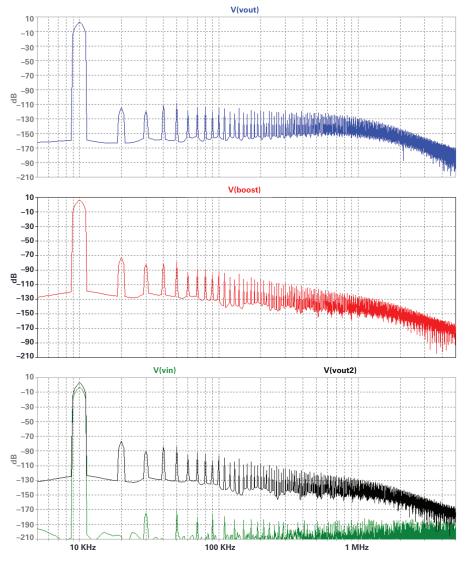

図 11. スタンドアロン・アンプと複合アンプの歪み

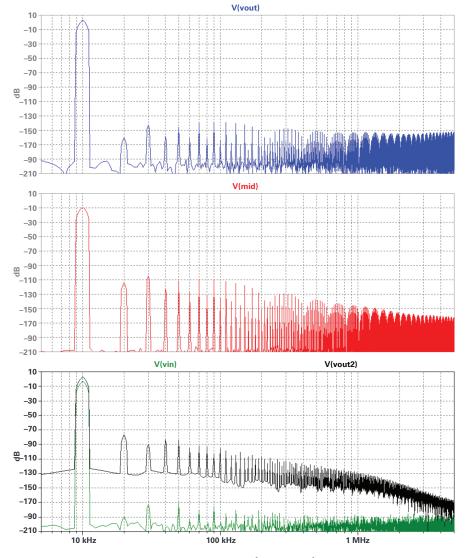

図11に示したのは、図10の回路における各信号のスペクトルです。10kHz、4Vp-pの信号を出力する場合の結果を示しています。

高調波歪みは、基本波(10kHz)のレベル(dB値)を各高調波のレベルから差し引くことによって測定しました。図11のいちばん下のグラフのとおり、入力信号の歪みは約163dBcです。したがって、信頼できるシミュレーション結果が得られるレベルにあると言えます。V(out2)は、スタンドアロン・アンプの出力です。歪みは-78dBcで、悪い値ではありません。ただ、ppmのレベルには全く達していません。

図11のいちばん上のグラフは、複合アンプの出力結果です。-135dBcという優れた歪み性能が得られています。ただ、これほどまでに良い結果を、果たして信じてもよいものなのでしょうか。図11の真ん中には、midノードにおける歪みが示されています。複合アンプの出力の歪みはほぼゼロですが、出力アンプには有限の歪みが存在します。したがって、帰還プロセスにより出力アンプの歪みの符号を反転した値がその入力(mid)に表れるはずです。midの歪みは-92dBcであり、LT1395のデータシートに

記載されたグラフと一致しています。但し、LTC6240の入力のCMRRやI<sub>CMR</sub>の特性の湾曲がマクロモデルで表現されているかどうかは疑問です。それらによって、実際の回路では歪みが増大する可能性があります。

残念ながら、歪みを含むマクロモデルはあまり作成されていません。マクロモデルのCIRファイル(拡張子はcir)のヘッダを見て、歪みをサポートしているかどうかを確認する必要があります。また、シミュレーションを実行し、歪みの結果がデータシートのグラフと一致するかどうかも確認しなければなりません。

複合アンプの補償は、少し難易度が高いケースがあります。本稿で示した例の場合、出力アンプの帯域幅が制御アンプの10倍以上あります。そのため、値の小さいコンデンサCfを追加するだけで補償できます。この補償方法では、ゲイン全体にわたる制御アンプの帯域幅がBWであるとすると、出力アンプの帯域幅を3×BW以上にする必要があります。これにより、全体の帯域幅は約BW/3に設定されます。

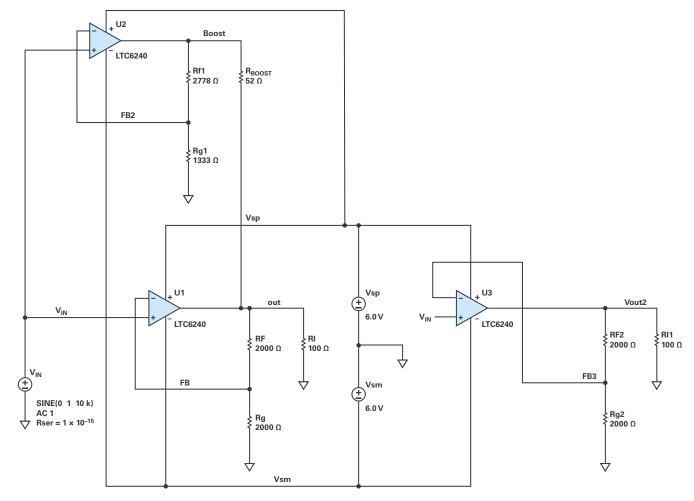

図 12. 歪みのシミュレーション用回路。スタンドアロン・アンプとブースト・アンプを対象としています。

帯域幅の縮小は、ブースト・アンプを使用する方法によって回避することができます。複合アンプほど歪みは改善されませんが、 帯域幅とセトリング時間は全く損なわれません。図12に、ブースト・アンプのシミュレーション用回路図を示します。

図12の右側は、LTC6240 (U3) を使用して構成したスタンドアロン・アンプです。左側には、2個のLTC6240 (U1、U2) で構成したブースト・アンプが配置されています。U1は、出力を制御する役割を果たします。ゲインは、スタンドアロン・アンプと同じく2です。U2で構成した出力アンプのゲインは3です。

Boost ノードにおいて、U1の出力電圧よりもU2の出力電圧の方が大きいので、出力にはU2が電流を供給します。R<sub>BOOST</sub>の値とU2のゲインは、RIへの負荷電流の96%をU2が供給するように設定されています。U1の負荷が軽減されることから、歪みが改善されます。なお、U2については、振幅の増加に対して十分な出力ヘッドルームが確保されるようにする必要があります。

LTC6240では、負荷が k  $\Omega$ のレベルになると、入力が歪みの支配的な要因になります。この例では負荷が  $100~\Omega$ なので、出力段の歪みが支配的な要因になります。

図13. スタンドアロン・アンプとブースト・アンプの歪み

図13に図12の回路のシミュレーション結果を示しました。

図10の回路と同様に、10kHzにおけるスタンドアロン・アンプの歪みは-78dBcです。ブースト・アンプの歪みは-106dBcで、複合アンプほどの性能は得られていません。それでも、スタンドアロン・アンプよりも30dBc近く良い値になっています。加えて、ブースト・アンプには帯域幅がそれほど縮小しないという利点があります。

また、歪みは $R_{BOOST}$ の値に依存する点に注意してください。同抵抗の値を $52\pm2\Omega$ に変動させると、歪みは10dBcほど悪化します。ただ、その後、同抵抗の値を $\pm10\Omega$ まで変動させても、歪みはほとんど変化しません。U1には、予想される極性の適度な負荷が必要であることがわかります。ブースト電流が理想的(負荷なし)であったり過剰であったりすると、歪みは増大します。

この回路では、U2とU1の回路で群遅延が等しく、ブースト信号が出力と同時に発生する状態が理想です。しかし、U2はゲインがU1よりも50%大きいので、クローズドループの帯域幅はU1よりも狭く、周波数軸で見てブースト出力はメインの出力よりも遅れることになります。U1の入力に並列抵抗を挿入することで、U1の帯域幅をU2と同じ広さまで縮小することができます。そ

れにより、U1とU2の回路の群遅延が等しくなり、ノイズ・ゲインも等しくなります。ただ、シミュレーション上、この方法では10kHzにおける改善は見られませんでした。遅延のバランスをとらない状態で、U1を使用した回路は最適な歪みを生成していたのです。周波数を高めてこれと同じことが起きるかどうかは、試してみなければわかりません。アンプが電流帰還型のものであれば、Rf1とRg1の値を小さくすることにより、U2の回路の帯域幅をU1の回路と同じ値まで広げることができます。

# ppmレベルの性能を備えるオペアンプ

表2と表3に、ppmのレベルに近い直線性を示すオペアンプ製品についてまとめました。

赤色の項目は、ppmレベルの歪みという基準を満たさない可能性があるパラメータです。使いやすい製品としては、「AD8597」、「ADA4807」、「ADA4898」、「LT1468」、「LT1678」、「LT6018」が挙げられます。

「AD797」、「ADA4075」、「ADA4610」、「ADA4805」、「ADA4899」、「LTC6228」は、入力部が原因で対処が必要になりますが(非反転アプリケーションで問題が生じる可能性があります)、良好な歪み性能を得ることができます。

表 2. ppm レベルに近い直線性を示すオペアンプ製品の主な仕様

| 品番      | V <sub>NOISE</sub><br>nV/√Hz | V <sub>NOISE</sub><br>(0.1Hz~10Hz)<br>μV p-p | I <sub>NOISE</sub><br>pA/√Hz | I <sub>NOISE</sub><br>(0.1Hz~10Hz)<br>pA p-p | V <sub>os</sub><br>μV (max) | CMRR dB<br>(min) | CMRR<br>の非直線性<br>µV/V | I <sub>BIAS</sub><br>nA (max) |

|---------|------------------------------|----------------------------------------------|------------------------------|----------------------------------------------|-----------------------------|------------------|-----------------------|-------------------------------|

| AD797   | 0.9                          | 0.05                                         | 2                            | 220                                          | 60~180                      | 110~114          |                       | 2000または3000                   |

| AD8597  | 1.1                          | 0.08                                         | 2.4                          | 190                                          | 120                         | 105              | 0.1                   | 200                           |

| ADA4075 | 2.8                          | 0.06                                         | 1.2                          | 60                                           | 1000                        | 106              | 1.5                   | 100~150                       |

| ADA4610 | 7.3                          | 0.45                                         | 非常に小さい                       |                                              | 800~1800                    | 96               |                       | 0.025~1500<br>(高温)            |

| ADA4805 | 5.2                          | 0.1                                          | 0.7                          | 140                                          | 125                         | 103              |                       | 800                           |

| ADA4807 | 3.1                          | 1.6                                          | 0.7                          | 370                                          | 125                         | 103              | 0.2                   | 800                           |

| ADA4898 | 0.9                          | 0.05                                         | 2.4                          | 130                                          | 125                         | 103              |                       | 400                           |

| ADA4899 | 1.0                          | 0.4                                          | 5.2                          | 4800                                         | 230                         | 98               |                       | 1000                          |

| LT1468  | 5                            | 0.3                                          | 0.6                          | 3                                            | 150~400                     | 96               |                       | 10、40                         |

| LT1678  | 3.9                          | 0.09                                         | 0.7                          | 26                                           | 350                         | 96               |                       | 35                            |

| LT6018  | 1.2                          | 0.03                                         | 0.75または3                     | 110または750                                    | 75~95                       | 120              | 0.02                  | 150~900                       |

| LTC6228 | 0.9                          | 0.94                                         | 6.3                          | 9000または20000                                 | 95~250                      | 94               | 0.1                   | 4000または44000                  |

# 表3. 表2の続き

| 品番      | I <sub>BIAS</sub> vs.<br>V <sub>CM</sub> nA/V | I <sub>BIAS</sub> vs. V <sub>CM</sub> の<br>非直線性pA/V | PSRR dB (min) | GBW MHz | 線形出力電流<br>mA(min) | DC V <sub>os</sub> vs.<br>V <sub>ouT</sub> の非直<br>線性 ppm | 歪み:<br>AV = 2、<br>2Vp-p出力、<br>10kHz、dBc | マクロモデルにおける<br>歪みへの対応    |

|---------|-----------------------------------------------|-----------------------------------------------------|---------------|---------|-------------------|----------------------------------------------------------|-----------------------------------------|-------------------------|

| AD797   |                                               |                                                     | 110または114     | 110     | ±30               |                                                          | -120                                    | シミュレーション・モデル<br>は楽観的すぎる |

| AD8597  | 5                                             | 0.2                                                 | 118           | 14      | ±20               |                                                          | -120未満                                  | データシートと比較               |

| ADA4075 | 2                                             | 3000                                                | 100           | 6.5     | ±15未満             |                                                          | -130未満                                  | 楽観的                     |

| ADA4610 | 非常に小さい                                        | 0.1                                                 | 100または103     | 12      | ±30未満             |                                                          | -114未満                                  | なし                      |

| ADA4805 | 2.2                                           | 4000                                                | 100           | 30      | ±30未満             | 30                                                       | -125                                    | なし                      |

| ADA4807 | 0.7                                           | 140未満                                               | 98            | 17      | ±50               |                                                          | -130未満                                  | なし                      |

| ADA4898 |                                               |                                                     | 98            | 120     | ±40               |                                                          | -120未満                                  | なし                      |

| ADA4899 |                                               |                                                     | 84            | 280     |                   |                                                          | -117                                    | なし                      |

| LT1468  | 3.5                                           | 600                                                 | 100           | 55      | ±15               |                                                          | -120未満                                  | あり                      |

| LT1678  |                                               |                                                     | 1000.7        | 10      | ±10未満             |                                                          | -120未満                                  | シミュレーション・モデル<br>は楽観的すぎる |

| LT6018  |                                               |                                                     | 128           | 12      | ±15未満             | 0.02                                                     | -115未満                                  | あり                      |

| LTC6228 | 300                                           | 28または140                                            | 95            | 800     | ±20               | 0.2                                                      | -120                                    |                         |

### まとめ

残念ながら、ppmレベルの精度を達成するオペアンプ製品を見つけるのは、非常に困難です。ppmレベルの直線性を備えるオペアンプ製品は存在しますが、アプリケーションのインピーダンスに対して歪みを生成する入力電流に注意する必要があります。アプリケーションのインピーダンスを低減することは可能ですが、それを帰還回路で駆動すると、オペアンプの入力に歪みが生

成されるおそれがあります。入力電流が少なく、変動が特に小さいオペアンプを使用すれば、アプリケーションのインピーダンスが高くても、オペアンプの最良の歪み性能を引き出すことができます。但し、そうすると、システムのノイズが大きくなります。 ppmレベルの直線性とノイズを達成するためには、オペアンプを慎重に選択すると共に、アプリケーション回路を最適化する必要があります。

#### 著者について

Barry Harvey (barry.harvey@analog.com) は、アナログ・デバイセズでアナログICの設計を担当しています。これまでに、高速オペアンプ、電圧リファレンス、ミックスド・シグナル回路、ビデオ回路、DSLライン・ドライバ、D/Aコンバータ、サンプル&ホールド・アンプ、乗算器などを設計してきました。スタンフォード大学で電気工学の修士号を取得。20件を超える特許を保有し、それと同じくらいの数の記事や論文を発表しています。趣味は、中古のテスト装置を修理すること、ギターを演奏すること、Arduino関連のプロジェクトに取り組むことです。