# ゼロIFアーキテクチャがもたらすメリット 実装面積は50%に、コストは1/3に

著者: Brad Brannon

#### はじめに

ゼロIF (ZIF) アーキテクチャは、無線通信の初期の時 代から存在するアーキテクチャです。現在では、テレ ビ、携帯電話、Bluetooth®対応機器など、民生向けのあ らゆる無線通信システムで使用されています。このよう にZIFアーキテクチャが広く普及したのは、あらゆる無 線技術の中で最もコストを削減でき、最も消費電力が少 なく、基板上の実装面積を最も小さく抑えられるからで す。これらの特質は、長年にわたり何度も実証されてき ましたが、これまでZIFアーキテクチャは、高い性能が 求められるアプリケーションには使われない傾向にあり ました。しかし、現在は無線に対する消費者の需要が高 まり、周波数帯の混雑が急速に深刻化している状況にあ ります。そのため、需要を支える無線インフラを経済的 に配備し続けるためには変化が必要になります。最新の ZIFアーキテクチャであれば、このようなニーズを満た すことができます。プロセス、設計、分割(パーティシ ョニング)、アルゴリズムの組み合わせによって、ZIF アーキテクチャが抱えるとされる多くの課題はすでに解 決されているからです。進化を遂げた新たなZIFアーキ テクチャは、性能の高い既存の無線アーキテクチャに 勝るメリットを備えています。また、画期的な性能を 達成した新たな製品が生み出されており、これまでZIF アーキテクチャの適用範囲外だった分野で、新たなアプリ ケーションが実現されています。本稿では、ZIFアーキテ クチャが備える多くのメリットについて説明します。そ のうえで、同アーキテクチャが無線設計にもたらす新た なレベルの性能について解説を加えます。

#### 無線技術者が抱える課題1

ワイヤレス対応の機器やアプリケーションに対する消費者の要求は、とどまることがありません。今日のトランシーバ設計に携わる技術者には、次々と新たな要件が提示されます。また、より広い帯域幅が絶えず求められる 状況にあります。

この数年間で、無線設計の焦点はシングルキャリアからマルチキャリアへと移行しています。いくつかの用途によって1つの周波数帯域を使い切ってしまったら、別の用途には新たに異なる帯域が割り当てられます。この

ような状況が繰り返された結果、40を超える無線周波数帯を扱わなければならないケースもあります。通信事業者は複数の帯域を保有しており、その周波数リソースについて調整を行う必要に迫られます。その結果、キャリア・アグリゲーション(CA)やマルチバンド無線が採用されるようになりました。現在では、従来よりも帯域外除去性能や放射性能に優れ、消費電力の少ない無線通信が求められています。

無線に対する需要が急速に高まる一方で、消費電力や実装面積はそれほど改善されていません。実際には、電力と面積を効率良く使って、CO2の排出量や物理的なスペースを減らすことが非常に重要です。このような目標を達成するために、無線アーキテクチャと分割について新たな視点が求められています。

# 集積の可否

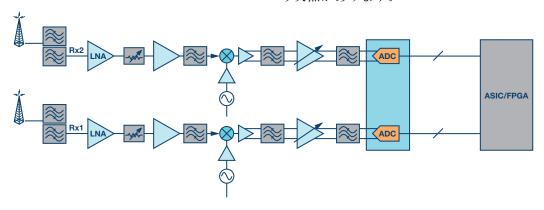

特定の設計において無線の本数を増やすには、各無線そ れぞれの占有面積を小さくする必要があります。そのた めに、従来は1つのICにできるだけ多くの回路を集積す るということが行われていました。これは、デジタル回 路の観点からは理に適った方策だと言えるでしょう。し かし、集積度を高めるためにアナログ機能を1つのICに 大量に集積するのは、必ずしも合理的なことだとは言 えません。無線用のアナログ機能の多くは、効率的に集 積することができないからです。図1に、従来のIFサン プリング・レシーバの例を示しました。IFサンプリング 部の前段には、低ノイズのゲイン段/RF選択段、周波数 変換段、IFゲイン段/選択段、検出段という4つの基本的 な回路ブロックがあります。一般に、選択段にはSAW (Surface Acoustic Wave: 弾性表面波) フィルタが使 用されます。SAWフィルタはICに集積することはでき ないので、チップの外部に配置する必要があります。ま た、RF選択段は圧電素子または機械素子で構成されます が、IFフィルタにはLC(インダクタ - コンデンサ)フィ ルタが使用される場合もあります。LCフィルタはモノリ シック構造に集積されることもありますが、その場合、 フィルタの性能(O値と挿入損失)が低下します。また、 デジタイザ (検出器) のサンプル・レートを上げなけれ ばならないことから、全体的な消費電力が増加するとい う欠点があります。

図1. 従来のIFサンプリング・レシーバ

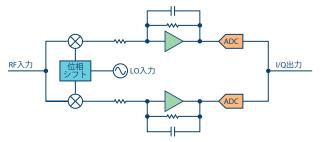

図2. 一般的なZIFサンプリング・レシーバ

通常、デジタイザ(A/Dコンバータ)は、コストと消費 電力を妥当なレベルに抑えるために、低コストのCMOS プロセスで実装します。バイポーラ・プロセスでも製 造は可能ですが、そうするとサイズが大きく、消費電 力が多くなってしまうため、目的に沿うことができま せん。したがって、デジタイザに対する適切なプロセ スはCMOSプロセスだということになります。このこと から、高性能のアンプ、特にIF段の集積は難しくなり ます。アンプはCMOSプロセスでも実現できます。しか し、CMOSプロセスは低電圧化や低消費電力化に向けて 最適化されるので、この用途のアンプに求められる性 能を引き出すのは困難です。また、A/D変換の前にはIF フィルタやアンチエイリアシング・フィルタを経由しな ければならないため、ミキサーとIFアンプをICに集積 した場合には、各段の間の信号をチップ外にルーティン グしなければならなくなります。その結果、集積によっ て得られるメリットがほぼ相殺されてしまうことになり ます。集積を行った場合、ピン数が多くなり、パッケー ジのサイズが大きくなるため、逆効果となってしまうの です。加えて、重要なアナログ信号がピンを通過する度 に劣化する恐れもあります。

集積度を高めるための最適な方法は、システムを再分割し、集積できない要素を取り除くことです。SAWフィルタをLCフィルタは効率良く集積することはできません。したがって、それらを排除するように再設計するというのが最良の選択肢です。図2に、標準的なZIFアーキをであるとです。RF信号をアル・チェーンを示した。RF信号をアルッチを完全に排除することで目標ををI/Qベース実力の必ずけん。選択段は、2つのローパス・フィルタをI/Qベース実力のようによっかがしています。損失が大きく、中性が固定されたチップ・しています。損失が大きく、ローパス特性のアクティブ・フィルタを集積することで実現するということです。従

来のIF用に使用されていたSAWフィルタやLCフィルタは、特性が固定されています(以下、固定型のフィルタと呼ぶことにします)。それに対し、ICに集積するアクティブ・フィルタは、一般的に数百kHzから数百MHzの範囲で電子的にチューニングすることが可能です。ベースバンドの帯域幅を変更できることにより、BOM(Bill of Material)リスト(部品表)を変更したり、複数の固定型IFフィルタを切り替えて使用したりすることなく、単一のデバイスによって広い範囲の帯域幅に対応することができます。

図を見ただけで直感的に理解するのは容易ではありませ んが、ZIFレシーバは、局部発振器(LO)を変更するだ けで、非常に広いRF周波数範囲に対応できます。一般 に、ZIFトランシーバは数百MHzから6GHz程度までを 連続的にカバーすることができ、非常に広い帯域幅の通 信に対応することが可能です。固定型のフィルタを使わ ないので、非常に柔軟性の高い無線通信を実現できます。 さまざまな帯域に対応可能な無線設計を行うための作業 が大幅に軽減されるか、あるいは全く不要になる可能性 もあります。ZIFを採用した設計であれば、柔軟性の高 いデジタイザとプログラマブルなベースバンド・フィル タにより、高い性能だけでなく、広範な周波数/帯域幅に 対応可能な卓越した柔軟性を提供できます。また、構成 ごとにフィルタなどのアナログ回路を最適化することな く、ほぼ一定の性能を維持できるので、真のソフトウェ ア無線(SDR:Software Defined Radio)技術であると も言えます。複数の周波数帯に対応しなければならない アプリケーションにおいてフィルタ群が不要になるため、 実装面積を大幅に削減できます。RFフィルタを完全に排 除し、苦もなく周波数帯を変更可能な完全な広帯域無線 を実現できる場合もあります。一部のデバイスを不要に したり集積したりすることで、ZIFアーキテクチャに必 要な実装面積は大きく削減され、帯域を変更する作業も 簡素化されます。それだけでなく、必要に応じてフォー ム・ファクタを変更する作業も軽減されます。

## 実装面積を抑えられる

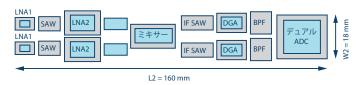

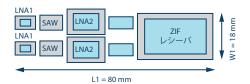

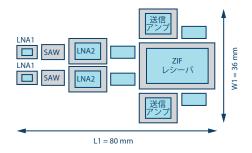

図3と図4は、IFサンプリング・アーキテクチャとZIFアーキテクチャの実装面積を比較するためのものです。合理的な実装を行った場合、2系統の受信パスの実装面積は、IFサンプリング・アーキテクチャで2880mm² (18mm×160mm)、ZIFサンプリング・アーキテクチャで1440mm² (18mm×80mm)となります。RFフィルタを排除するといったさらなる簡素化の可能性を除外しても $^2$ 、ZIFアーキテクチャでは、従来のIFサンプリング・アーキテクチャと比べて実装面積を最大50%削減できる可能性があるということです。将来的には、さらに集積化を進めることによって、実装面積をさらに半分にできる可能性もあります。

図3. 一般的なIFサンプリング回路のレイアウト

図4. 一般的なZIFサンプリング回路のレイアウト

### コストを削減できる

IFサンプリング・アーキテクチャからZIFアーキテクチ ャへ移行すると、BOMは単純に33%減少します。とは いえ、コストの分析というのは常に難しいものです。図 1と図2を詳細に比較すると、IFフィルタやアンチエイリ アシング・フィルタなどで使うディスクリート部品の多 くが排除され、ミキサーやベースバンド・アンプがICに 集積されていることがわかります。また、図を見ただけ ではわかりませんが、ZIFレシーバは従来のIFサンプリン グ・アーキテクチャにはない帯域外成分の除去性能を備 えています。そのため、外付けフィルタ全般の要件が大 幅に緩和されます。帯域外成分の除去は、ZIFアーキテク チャの2つの要素によって実現されます。1つ目はベース バンド向けのアクティブ・フィルタです。これは、帯域 内の信号の増幅と帯域外成分の除去の両方を行います。 もう1つは、I/O信号のA/D変換に使用するΣΔ型A/Dコン バータ (ΣΔ ADC) です。高いサンプル・レートに対応す るこのADCはローパス特性を示します。帯域外の成分は アクティブ・フィルタによって抑えられますが、サンプ ル・レートの高いADCを使用すれば、エイリアスのポイ ントが十分に高い周波数に移動し、外付けのアンチエイ リアシング・フィルタが不要になるという効果が得られ ます(アクティブ・フィルタによって、高周波成分が十 分に除去されるからです)。

図5. ベースバンド用のアクティブ・フィルタとADC

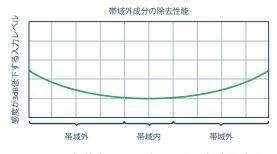

図5に示すように、ベースバンド信号にはアクティブ・フィルタが適用され、高周波成分が減衰します。続いてADCによってA/D変換が行われ、この時に $\Sigma\Delta$  ADCのローパス特性が適用されます。その総合的な効果を図6に示します。この図は、アクティブ・フィルタと $\Sigma\Delta$  ADC の相乗効果によって得られる標準的なレシーバの特性を表しています。この図には、帯域内と帯域外における標準的な3dBデセンス(感度が3dB低下する入力レベル)が示されています。帯域外の性能は、外付けのフィルタを使うことなく改善されている点に注目してください。

IFサンプリング・レシーバでこれと同等の性能を達成するためには、SAWフィルタなど、ディスクリート構成のIFフィルタにより、選択、帯域外信号の除去ス)の帯域内への折り返し(エイリアグ・アもとでも、他の不要なミキサー成分からの保護は、RFアクチャでは、他のません。例えば、ハーフIF成分は、RFフィルタとIFフィルタに対する要件を厳しくします。それだけでなく、サンプル・レートとIFの計画にそのような制約が加わることはありません。

図6. 一般的なZIF設計における帯域外成分の除去性能

アプリケーションや設計にもよりますが、このような帯域外成分の除去性能が得られることから、外付けのRFフィルタの要件が緩和されます。場合によっては、外付けのRFフィルタは不要になります。外付けのRFフィルタは、種類によっては比較的高価なものになります。それが不要になれば、コストの面で大きな効果が得られます。た、損失が大きいRFフィルタがなくなれば、RFゲイン段を排除できる可能性が生まれます。そうすると、コストだけでなく、消費電力の削減や直線性の向上といったメリットも得られます。このような利点を、再分割/集積による効果に加えて得ることができます。

繰り返しになりますが、コストの見積もりは容易な作業ではありません。製造数やベンダーとの契約にもば、ZIF た右されるからです。しかし、詳しい分析を行えば、ZIF アーキテクチャを採用することによって、必要な要集積や排除、削減が可能になります。それによります。を体的なシステム・コストを最大で1/3程度低減でコストを最大で1/3程度低減のコストを最大で1/3程度低減のコストであり、デバイスのコストではない点に注意してださい。より多くの機能をより少ないデバイスに実装するで、システム全体のコストは低下する一方で、一部のデバイスのコストは増加する可能性があります。

集積型のZIFレシーバを採用すれば、BOMコスト以外の 複数の問題を解決することができます。例えば、高い集 積度を活かしたシステムでは、デバイスの数が少なくな ります。そのため、組み立てコストが抑えられ、製造歩 留まりが高くなります。また、ディスクリート部品の数 が減れば、アライメントに要する時間が短くなります。 これらの要因から、製造コストが低下します。

また、ZIFレシーバは非常に広い帯域に対応します。そのため、帯域の変更に伴う設計コストを削減できます。IFサンプリングを採用したシステムでは、IF周波数を慎重に選択する必要があります。これに対し、ZIFを採用したシステムでは、慎重な周波数計画は必要ありません。新たな周波数帯域には、主にLOを変更することで対したのます。また、ZIF設計を採用すれば、多くのアプリケーションで外付けのRFフィルタが不要になるので、さらにコストに加えて直接コストも考慮すると、ZIF設計を採用することにより、全体的にはかなり大きなコスト削減効果が得られる可能性があります。

# 消費電力を低減できる

図1に示したアーキテクチャをそのままSoC(System on Chip)として集積しても、消費電力やコストは削減できません。消費電力を削減するには、使用するプロセスに最適化した効率的なアーキテクチャを選択する必要があります。図1に示したIFサンプリング・レシーバのようなアーキテクチャは、低コストのプロセスには適していない高~中レベルの周波数を多く扱います。そうした周波数に対応するためには、かなりの電力を消費します。一方、図2に示したZIFアーキテクチャは、対象とする周波数をDC(ベースバンド)に直接変換するので、低い周波数で動作する回路によって実装することができます。

同様に、帯域幅についても消費電力の問題が生じます。RF信号のダイレクト・サンプリングを行うアーキテクチャなどであれば、高い柔軟性が得られ、広い帯域幅に対応できます。しかし、システムで帯域幅を広げると、必ず消費電力が増加します3、4。

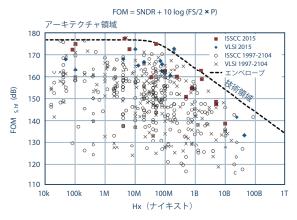

実際に帯域幅そのものが必要な場合を除き、帯域幅だけによって問題を解決しようとするのは得策ではありません。レシーバを使用するほとんどのアプリケーションでは、その方法がコスト効率に優れる解決策になることはないでしょう。長期にわたる研究結果を見ると、コンバータの進化は2つの領域で実現されていることがわかります。1つ目は技術の領域です。この領域では、ダイ

ナミック・レンジと帯域幅の観点からコア部のAC性能を意味のあるかたちで向上させてきたという歴史があります。もう1つはアーキテクチャの領域では、コア部のアーキテクチャが効率の改善に向してきたことがわかります。一般に進化してきたことがわかります。一般に進化を高速に向かって伸びていきます。通信でいたの機能は、当初は右側に向かって伸びていきます。通信でいたの場合、その性能は技術面の低でしまって担があり、ADCの効率は約10dB/10年で低にすると実別に対し、この下降曲線上では、帯域幅を2倍にするが進行に増加します。しかし、この下降曲線上では、帯域幅を2倍にするが進行といかたちで性能の進化が進むます。その結果、効率が向上し、通常は消費電力の増取るでは2倍程度に抑えられます。

図7. ADCのコア技術の性能指数4

消費電力が重視される場合、帯域幅とサンプル・レートをそのアプリケーションに対して最適化するのが消費電力を下げるための最善の策となります。 $\Sigma\Delta$  ADCを使用するZIFサンプリングは、そうしたアプリケーションに対して最適化されています。具体的な実装方法にもよりますが、ZIFレシーバであれば、消費電力はIFサンプ・アーキテクチャと比べて50%以上削減できます。また、RF信号をダイレクト・サンプリングするアーキテクチャと比べると、最大120%程度にできる可能性があります。

#### 性能の向上

無線設計には、いくつもの重要な評価指標があります。例えば、ノイズ指数(NF)や直線性(IP3、IM3)、感度の低下、選択性などがそれに当たります。そうした一般的な無線仕様以外に、重要であるにもかかわらず、ほとんどのユーザーには公開されない仕様がいくつも存在します。例えば、時間、電源、温度、プロセスの関数として表される分布/ドリフトの仕様などがあります。ZIFアーキテクチャは、そうした無線設計における主要な要件を満たします。

## 温度、電源、プロセスによるトラッキング

完全集積型のトランシーバのアーキテクチャには、適 切に設計された無線システムに対して、デバイスの整 合性が非常に高くなるというメリットがあります。適切 に設計されたデバイスであれば、使用を開始した時だけ ではなく、その後のプロセス、温度、電源、周波数の変 化に効果的にトラッキングすることができます。不整合 が存在していても、集積型の設計に一般的に組み込まれ ている信号処理の手法によって直ちにそれを補正できま す。これはICの設計方法としては非常に一般的なもので す。ただ、集積型のZIF設計については、周波数に依存 する全ての要素がチップ上に存在することになり、それ らもトラッキングの対象にできるという点が異なります。 図1に示した一般的な無線回路の場合、IFフィルタはIC に外付けされます。IFフィルタの特性は、時間、温度、 あるいはデバイスによって異なることに加え、チップ上 のどの要素とも相関性がないことから把握することがで きません。フィルタを集積することのメリットの1つは、 チップ上の部品を使って構成することから、各部品をス ケーリングしたり、互いをレシオメトリックにトラッキ ングさせたりすることで、安定した性能を維持できるこ とです。これらの要素は本来は計画的に安定化させるこ とができないものですが、その校正を簡単に実施するこ とができます。そのため、デバイスのばらつきを見積も る際、全てのデバイスに相関性のないディスクリート構 成の設計を採用した場合よりも、かなり小さくマージン を抑えることができます。

例えば、ミキサー、IFフィルタ、IFアンプ、ADCのNF に、それぞれ1dBのばらつきが存在すると想定して検討を 行うケースがあるでしょう。性能を見積もる際には、こ れらのばらつきを盛り込んで考える必要があります。し かし、集積型の設計では、重要な仕様は全て互いをトラ ッキングさせるか、校正によって整合性を確保できるよ うにするので、1dBのばらつきを持つ単一のデバイスだ と見なすことができます。そのため、シグナル・チェー ンにおけるばらつきを大幅に簡素化して考えることがで きます。このことは、設計に対して多大な効果をもたら します。相関性のない要素を含む設計の場合、ノイズが 増加する可能性を打ち消すために、システムにゲイン処 理を追加する必要が生じ、最終製品のコスト、消費電力、 直線性に影響が及びます。しかし、集積型の設計ならば、 そうした影響を回避できるのです。図2に示したような集 積型の設計では、性能の総合的なばらつきは、相関性の ない設計よりもかなり小さくなります。そのため、シス テムに必要なゲインも小さくて済みます。

# 補償に向けた高度な手法

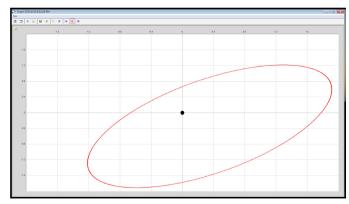

一般に、ZIFレシーバについては、以前から2つのポイントが懸念材料となっていました。ZIFレシーバでは、複素データが生成され、その実数部と虚数部がカスケード構成の2つの回路で表現されます。それにより、個々のシグナル・チェーンのゲイン、位相、オフセットを表す誤差が生成されます(図8)。

図8. ゲイン、位相、オフセットの各成分を示す直交誤差

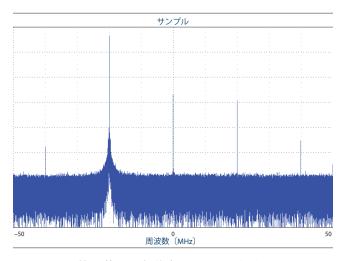

この誤差は、周波数軸で見るとイメージとして現れます。このことが、ZIFアーキテクチャの採用が進まなかった一般的な理由となっています。しかし、集積型の設計では、アナログ回路の最適化とデジタル回路による補正によって、この誤差を容易に制御できます。図9に、補正前の一般的な複素データの状態を示しました。これを見ると、LOリーク(とDCオフセット)、イメージ(直交誤差)の両方が現れています。

図9. 補正前の一般的なLOリークとイメージ

#### LOリークの制御

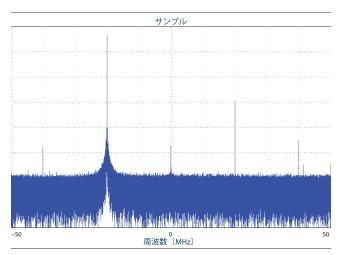

LOリークは、I/Qの信号パスにDCオフセットの増加というかたちで現れます。これは、LOがRF信号のパスに直接カップリングし、そのまま出力にダウンコンバートされることによって生じます。その結果、ミキサー積がDCオフセットとしてシグナル・チェーンの残余DCオフセットに追加されます。適切なZIFアーキテクチャであれば、使用を開始した時だけでなく、時間、温度、電源、プロセスの変化に伴って自動的にトラッキングを行い、それらの誤差を補正することができます。結果として、図10に示すように-90dBFSを上回る性能を達成できます。

図10. 一般的なLOリークの制御手法を適用した結果

# **QEC**

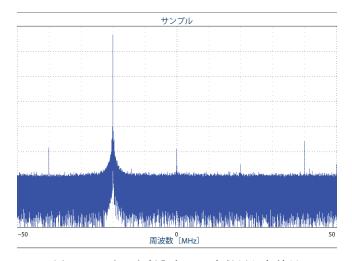

一般に、イメージによって性能が損なわれることを防ぐ方法としては、QEC(直交誤差補正)の機能が利用されます。図11は、その補正の効果を示したものです。この例では、ほとんどの無線アプリケーションにおいて十分なレベルである-105dBc以下にイメージが抑えられています。LOリーク制御とQECの両方にトラッキングを採用することで、時間の経過に伴う性能の変化に応じて常に最新の補正が加えられます。それにより、最適な性能を維持できることが保証されます。

図11. LOリーク制御とQECを併用した結果

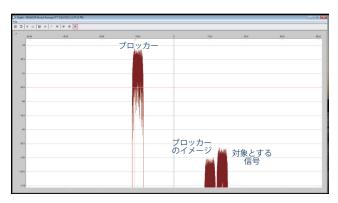

無線システムにおいて、直交誤差とLOフィードスルーは 重要な項目です。誤差が大きいと、大きなブレーのう 可能性があります。図12の例では、大きなブロッカーの イメージが15MHzに、対象とする信号の中心が20MHz にあります。対象とする信号の中心が20MHz にあります。対象とする信号の中心が20MHz にあります。対象とする信号の中心が20MHz にあります。対象とする信号の中心が20mHz にあります。対象とする信号の中心が20mHz にあります。となるには不し、復調時に誤差が 生じる恐れがあります。LTEやW-CDMAなどのシステムは、このようなイメージをある程度まではありません。 全は、このようなイメージをある程度まではありません。 それでも、完全な耐性を持つというわけとのイメージ除去 とれてもれば、その要件を容易に満たし、維持する とができます。

図12. 信号を妨害するイメージの例

#### ZIFに対応するAD9371

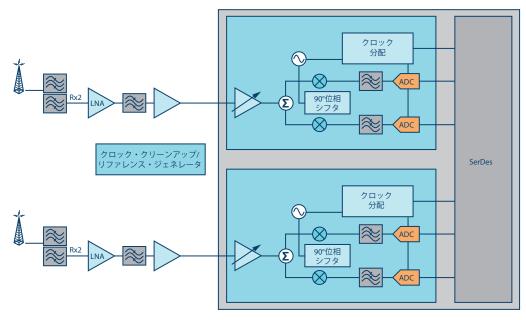

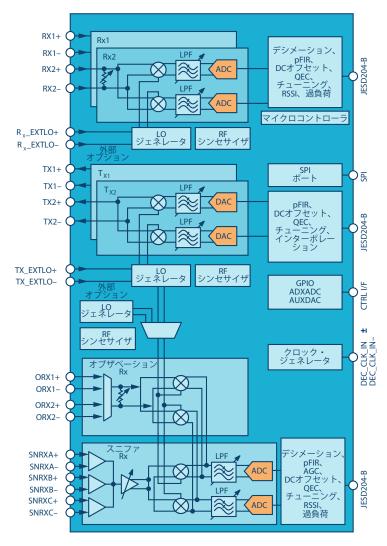

ZIFトランシーバの典型的な例として、アナログ・デバイセズ(ADI)の「AD9371」を取り上げます。このICは、図13に示すように、デュアル対応の送受信機能などを非常に高いレベルで集積しています。例えば、オブザベーション・レシーバやスニファ・レシーバ、AGC(自動ゲイン制御)機能、DCオフセット補正(LOリーク制御)機能、QECといった機能を備えています。対応する周波数帯は、300MHz~6GHzと広範です。各トランスミッタは20MHz~100MHzの合成帯域幅に対応し、各レシーバは5MHz~100MHzに対応します。3G/4Gの用途を主なターゲットとしていますが、6GHzまでの汎用無線やソフトウェア無線の用途に対しても理想的な製品となっています。

AD9371は、先述した周波数に依存する全てのデバイスを備えているうえに、全ての校正機能とアライメント機能を有しています。パッケージは12mm×12mmのBGAです。図4に示した受信機能だけでなく、送信機能も備える非常にコンパクトなデュアルトランシーバ回路が、単一のパッケージ内に収められています(図14)。帯域幅はどうするのか、どの機能を有効にするのかといった具体的な構成にもよりますが、AD9371の標準的な消費電力は、LOリークとイメージを抑えるためのデジタル機能を含めてわずか4.86Wです。

図13. 集積度の高いZIFトランシーバ「AD9371」

図14. 一般的なZIFトランシーバのレイアウト

#### AD9371の主要な性能

以下に、AD9371の主要な性能についてまとめます。

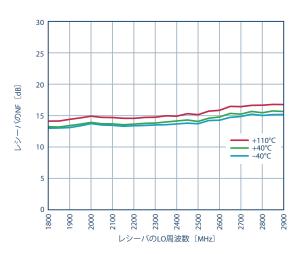

#### ●ノイズ指数

図15と図16は、AD9371の標準的なNF特性を示したものです。図15は、RF帯で広範に周波数掃引した結果です。その範囲全体にわたってNFが比較的一定に保たれることがわかります。このICの入力部は減衰器として働き、NFは1dBごとに1dB増加します。最悪の場合のNFが、減衰がない状態で16dBであると想定し、外部のゲインばら

つきに応じて約4dBまでの減衰を許容すると、トータルのNFとしては20dBという値をとり得ることになります。外付けのLNA (0.8dB) で24dB以上のゲインを与えれば、システムのNFは2dBになります。

図15. AD9371のNF (減衰量が0dB、帯域幅が40MHzの場合)

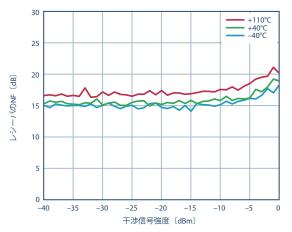

図16は、AD9371の入力を基準とした帯域外ブロッカーの関数としてNFを示したものです。外部のゲインが24dBであるとし、このICの入力が0dBmであるとすると、アンテナのコネクタ部では-24dBmということになります。AD9371の影響のみを考えた場合、集積化されたレシーバで3dB増加すると全体的なNFは約1dB増加します。

図16. AD9371のNFと帯域外信号強度の関係

# ●イメージ除去

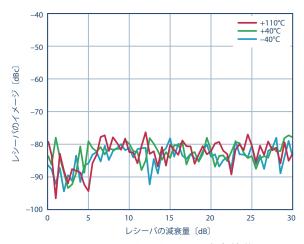

LOリークと同様に、レシーバのイメージ除去性能は、図17に示した情報から見積もることができます。アンテナの標準入力レベルが-40dBmである場合、イメージはそれよりも80dB小さく、アンテナのポートでは-120dBmであると見積もることができます。

図17. レシーバのイメージ除去性能

#### まとめ

従来、ZIFアーキテクチャは高い性能が必要とされないアプリケーションだけで使われてきました。AD9371のような新しい製品は、その状況を一変させるだけの性能を備えています。IFサンプリング・レジーバに匹敵する性能を達成しているだけでなく、無線立るという一歩路によって堅牢なアーキテクチャを構成すること製造しています。これ低減することがでなく、導入後の運用コストも低減することがでするといます。コストを削減するために、無線とステムの実はありません。ユーザーは、無線システムースを集中させることができます。

## 参考文献

- 「この部分の内容は、主にレシーバを対象として記述されているが、トランスミッタにも当てはまる。トランスミッタについては、10年以上前からZIFアーキテクチャが高性能のアーキテクチャとして採用されている。

- <sup>2</sup> ここで分析したように、一般的なZIFレシーバでは、送 信パス全体も同じパッケージ内に含まれている (AD9371)。

- <sup>3</sup> R. H. Walde「Analog-to-Digital Converter Survey and Analysis(ADCの調査と分析)」IEEE Journal on Selected Areas in Communications、4月1999年

- <sup>4</sup> Boris Murmann「ADC Performance Survey 1997-2015(ADCの性能調査1997年~2015年)」Stanford University, 2015年

#### 著者:

Brad Brannon (brad.brannon@analog.com) は、ノースカロライナ州立大学を卒業後、32年間にわたってアナログ・デバイセズに勤務しています。これまで設計、テスト、アプリケーション、システム・エンジニアリングを担当してきました。ADC/DACのクロッキング、無線設計、ADCのテストなど、さまざまなテーマで多数の記事やアプリケーション・ノートを執筆しています。現在は、4G/5Gの受信アーキテクチャのシステム・エンジニアリングを担当しています。