# StudentZone — 2017 年 8 月 Virtual Evalの活用法 -ADC に関する設計を仮想的にスタートする

著者::Christoph Kämmerer

Share on (1) (f) (in)

#### はじめに

これまでに A/D コンバータ(ADC)を使ったことはあ りますか。マルチプレクサや PGA、バッファ、シグマ・ デルタ (ΣΔ) コンバータ、リファレンス電圧、電源で構 成される複雑なシステムは手に負えないと感じたり、ど こから手を着ければよいものかと悩んだりはしていませ んか。そのようなときに役立つのが「Virtual Eval」で す。ADC のアナログ入力、PGA のゲイン、電圧リファ レンスの値、あるいは電源電圧の値を変更しつつ、ステ ップ応答や周波数応答 H(f)、変換結果のヒストグラム への影響などを把握することができます。

本稿では、アナログ・デバイセズの ADC「AD7124-8」 を例にとり、仮想評価ボードの使い方を解説します。

#### なぜ仮想化という手法を使うのか?

個々のアプリケーション向けに設計した回路の性能は、選 択した部品に応じて決まります。各部品の性能に関する情 報やヒントは、データシートを見れば確認することができ ます。ただ、各種の回路から成る設計全体の特性を詳し く評価するために、通常は評価ボードを使用することに なります。それによって、ADC、アンプ、インシュレ タなどの部品のテストを行うということです。しかし、

評価ボードを使う方法には大きな欠点があります。それ は、実際に評価ボードを購入し、計測器に接続しなけれ ば評価できないということです。また、最適な設定を見 いだすためにさまざまなボードでテストを行うプロセス には、特に時間とコストがかかります。このような複雑 さを回避できるようにするために、アナログ・デバイセ ズは、設計者がシミュレーションによって ADC や D/A コンバータ (DAC) の評価を行えるようにするためのオ ンライン・ツールを開発しました。それが Virtual Eval です。このツールを使えば、物的コストが不要になりま す。また、設計を行う際、部品の選択に費やす時間を削 減することができます。

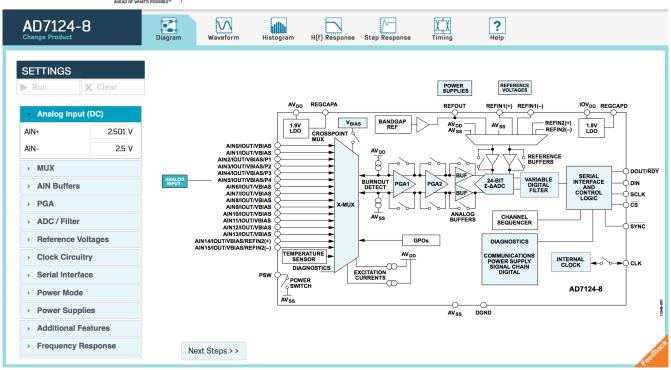

Virtual Eval 向けには、アナログ・デバイセズの ADC/ DAC に関する最新かつ包括的なデータベースが用意され ています。同ツールを使用すれば、ADC/DAC の各動作環 境について正確にシミュレーションすることができます。 同時に、さまざまなシナリオや境界条件でのテストを実施 することも可能です。図 1 に示すように、同ツールには さまざまな機能が用意されています。ここでは、分解能 が 24 ビットの ΣΔ ADC 「AD7124」を例にとることにし ます。同 IC は、ケーブルの接続やショートなどを検出す る診断用の拡張機能をオプションとして備えています。

**ANALOG**DEVICES Virtual Eval Tool

図 1. Virtual Eval 上に表示された AD7124 のブロック図

**Analog Dialogue 51-08** 1

Power Mode

Additional Feature

1.0018 mV

b.

図 2. 入力信号の波形(a)と入力信号に対応するヒストグラム(b)

図 3. ステップ関数 (a) とタイミング図 (b)

Virtual Eval では、最初のステップとして ADC 全体のブロック図を確認することができます。図中で内部の各モジュールをクリックすれば、個々のシミュレーションのシナリオに合うようにパラメータを変更できます。設定が可能なモジュールとしては、入力アンプや各種スイッチが挙げられます。また、画面左側の「SETTINGS」には、利用可能なオプションが表示されます。AD7124の場合、フィルタの設定(Sinc 4 + Sinc 1 または Sinc 4)、内部クロック、電圧リファレンスなども設定の対象にります。変換レートやタイミングの校正も可能です。

a.

Power Mode

Additional Features

Next Stens >>

パラメータの設定を行ったら、ADC の特性が視覚化され、それを基に評価を行うことができます。まず、入力波形を表示できます(図 2 (a))。また、入力信号に対して FFT を適用することが可能です。ADC の統計的なデータと精度はヒストグラム(図 2 (b))によって確認できます。

Virtual Eval では、信号の周波数応答とステップ関数を表示することも可能です(図 3 (a))。一般に、ADCはナイキスト定理を満たせるように選択されます。スステップ関数を利用することにより、安全を確保を算出することができます。ステップ関数の立上りは、ADC がまます。ステップ関数の立上りは、ADC がます。とができます。ステップ関数の立上りは、ADC がます。変換レートが不十分であれば、データは失われる過で変換レートが不十分であれば、データは失われる過に伴うなりのタイミング図は、AD7124 の時間の経過に伴う応答を表しています。消費を表高めた場合など、さまざまなシーションを実施することが可能です。

#### まとめ

ADC/DAC 用のシミュレーション・ツールである Virtual Eval は、異なる条件やシナリオに基づいてさまざまな製品のシミュレーションを実施する手段を提供します。これを利用すれば、コストを削減しつつ、製品の選択に必要者時間を大幅に短縮することができます。つまり、設計者は評価用ボードを購入したり、コストのかかるテストを実にしたりすることなく、適切な製品を選択できるということです。ADC を選択したら、すぐに Virtual Eval のヘルプ・ページ上でデータシートや詳細な情報を確認することができます。近い将来、データベースは拡張され、ADC/DAC を内蔵した AMR(異方性磁気抵抗)センサーなどの集積化モジュールも網羅されるようになります。

### 今月の問題

PGA のゲインが 128 に設定され、差動入力電圧が  $0.1\ V$  に設定されているとき、AD7124-4 には何が起きるでしょうか。ヒントは、差動入力とはどのようなものなのか考えてみることです。なお、リファレンス電圧は  $2.5\ V$ 、アナログ電源は  $3.3\ V$ 、I/O 電源は  $2.7\ V$  であるとします(それ以外はすべて標準的な設定)。

各自で計算を行ってみたうえで、Virtual Eval でシミュレーションを実施してみてください。

この問題の答えは Student Zone で確認できます。

2 Analog Dialogue 51-08

## Christoph Kämmerer

## 著者:

Christoph Kämmerer (christoph.kaemmerer@analog.com) は、アナログ・デバイセズのフィールド・アプリケーション・エンジニアです。2015年2月から当社に勤務しています。2014年にドイツエアランゲンにあるフリードリヒ・アレクサンダー大学で物理学の修士号を取得しました。同校を卒業後、リムリックにあるアナログ・デバイセズのプロセス開発部門でインターンとして勤務しました。2016年12月に研修プログラムを修了し、現在はフィールド・アプリケーション・エンジニアとして新たなアプリケーションに取り組んでいます。

Analog Dialogue 51-08