# アナログ・デバイセズに寄せられた珍問/難問集 Issue 148 新たなゲート駆動手法により、大電力アンプの 高速オン/オフを実現

著者: Peter Delos/Jarrett Liner

# 質問:

200 ナノ秒以内でオン/オフすることが可能な大電力ア ンプは実現できるでしょうか。

#### 回答:

パルス・レーダーのアプリケーションでは、送信動作から 受信動作へ遷移する際、大電力アンプ (HPA: High Power Amplifier) を高速にターンオン、ターンオフする必要が あります。一般に、遷移時間の目標は1マイクロ秒未満 といった値に設定されます。従来、この目標はドレイン を制御することによって実現されてきました。ドレイン の制御による大電流のスイッチングには、28 V ~ 50 V の電圧が必要になります。この制御は既知の手法によって実現できます。ただし、実装面積が大きくなるととも に回路がより複雑になります。最新のフェーズド・アレ イ・アンテナを開発するケースでは、SWaP(サイズ、重 量、消費電力)を最小限に抑えることが要求されます。 この目標を達成しつつ、HPA のスイッチングをドレイン 制御で実現することに伴う複雑さを排除することが求め られています。

本稿では、HPA の高速ターンオン/オフを実現するため の別の方法を紹介します。ドレイン制御によってスイッ チングを実現する回路を排除し、ゲートをパルスで駆動 するシンプルかつユニークな回路です。スイッチングに 要する時間は 200 ナノ秒未満に抑えられるので、1 マイ クロ秒という目標に対して十分なマージンを確保できま す。また、その回路は3つの付加機能も備えています。1 つは、デバイス間のばらつきに対処するためのバイアスの プログラム機能です。もう 1 つは、ゲート電圧の予期せ

ぬ上昇から HPA を保護するゲート・クランプ機能です。 最後の 1 つは、パルスの立上がり時間を最適化するため にオーバーシュートを補償する機能です。

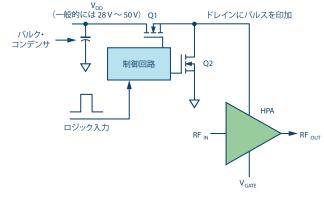

## 一般的なドレイン制御回路

図 1 に、ドレインの制御によって HPA をターンオン/ オフする回路を示しました。HPA には直列に接続された FET を介して高い電圧が印加されます。制御用の回路で は、その FET をオンにするために、論理レベルのパルス をより高い電圧に変換します。

この構成が複雑になる原因としては、以下のような事柄 が挙げられます。

- ▶ 大電流のスイッチングにあたっては、バルク・コンデ ンサから HPA のドレイン・ピンまでのパスにおいて インダクタンスを小さく抑える必要があります。

- ▶ ターンオフが行われる際、ドレインの容量には電荷が 保持されるので、別の放電パスが必要になります。こ れは 図 1 に Q2 として示した FET を追加すること で実現します。それに伴い、制御回路には、Q1 と Q2 が同時にイネーブルにならないようにするという制約 が加わります。

- ▶ 多くの場合、直列に接続される FET としては N チャ ンネルのデバイスが使用されます。このことから、タ ーンオンを実現するために、HPAのドレイン電圧より 高い電圧を生成する制御回路が必要になります。

この制御回路の設計手法はすでに確立されています。し かし、フェーズド・アレイ・システムでは、さらなる集 積度の向上と SWaP の削減が求められます。また、複雑 さの排除も必要です。ドレイン制御回路の全体を不要に することが求められていると言うこともできます。

図 1. HPA のオン/オフに使用されてきたドレイン制御回路

**Analog Dialogue 51-12**

## 従来の課題を解決するゲート駆動回路

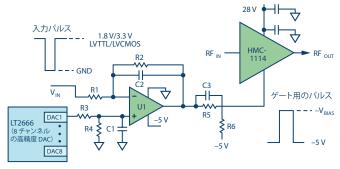

ゲート駆動回路の目的は、ロジック信号を、GaN ベースの HPA のゲートを制御するための適切な信号に変としてすることです。適切なバインを設定するためにです。適切なが、さらに低い負の電圧によっては、イスをターンオフさせます。つまでは、その回路で成るでは、で、大田で変換する必要があります。また、その回路によって、ゲート容量に対応しなければなりません。

ゲート用のバイアス設定については 2 つの懸念があります。1 つは、バイアス電圧のわずかな増加によって HPA の電流が大幅に増加する可能性があることです。このられます。加えて、損傷を防ぐためにクランプ機構を設けることが必要になります。もう 1 つの懸念は、発見に、おいることが必要になります。このばらつきるようにするために、ゲートのバイアスをプログラムできるようによりの機能をシステム内に追加することが必要になります。

図 2. HPA 用のゲート駆動回路。 図 1 の手法が抱える課題を解決します。

図 2 に示した回路では、上述したすべての事柄への対応が図られています。オペアンプ U1 は、負の単一電源を使用します。高精度の D/A コンバータ (DAC) である「LT2666」は、U1 の非反転入力ピンに印加するリファレンス電圧を設定するために使用しています。ロジック入力がハイの時、オペアンプの出力は負の電源レールにクランプされます。入力がローになると、オペアンプの出力

は、抵抗値と DAC の設定によって決まる小さな負の値に 近づきます。U1 を負電源で動作させているのは、ロジッ ク入力がロー(グラウンドのレベル)になった時に HPA をターンオンするためです。このようにした理由は、ロー・レベルではハイ・レベルよりも電圧値のばらつきが 小さく抑えられるからです。レール to レールのオペアン プとしては、高いスルー・レートとアプリケーションに対 して適切な出力電流値を達成できるものを選択します。

各部品の値の決定には、次のような事柄がかかわります。

- ▶ 抵抗 R1、R2 によって、オペアンプのゲインを設定します。

- ▶ DAC の設定と抵抗 R3、R4 によって、オペアンプの 非反転入力ピンに入力するリファレンス電圧が決まり ます。コンデンサ C1 と R3 の値は、それらによって 構成されるローパス・フィルタのノイズの条件に応じ て決められます。

- ▶ 抵抗 R5、R6 によって、重要なクランプ機能が実現されます。オペアンプ U1 の電源ピンはグラウンドに接続されており、それが U1 の出力の最大値になります。R5 と R6 は、-5 V の電源電圧を分圧する役割を果たします。

- ▶ R5 は好ましくない影響が生じる原因になります。その影響とは、ゲートの容量と組み合わせられることによって、パルスに対する応答が遅くなることです。これについては、コンデンサ C3 を加えて急峻なパルスを得ることで補償します。

- ▶ コンデンサ C2 の値は小さく設定します。オペアンプ の出力パルスの立上がりエッジに生じるオーバーシュートを制限したいからです。

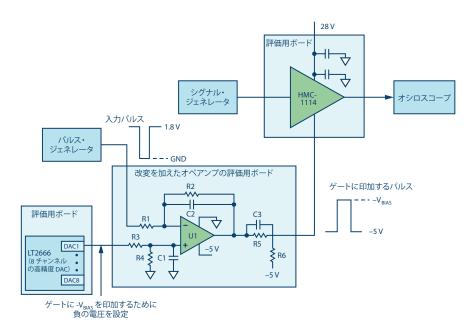

#### 評価結果

図3に示したのは、図2の回路を評価するためのシステム構成です。高精度のDAC、オペアンプ、HPAの各評価用ボードを組み合わせています。パルス・ジェネレータは、1.8 Vのロジック信号を生成するために使用します。また、シグナル・ジェネレータは常に動作させておきます。この状態でHPAをターンオン/オフし、RF信号の測定を行います。そのために、そのRF周波数よりも広い入力帯域幅を備えるオシロスコープを使用します。

図 3. 評価用のシステム構成

表 1 に、評価に使用した部品の値/品番をまとめました。

表 1. 使用した部品の値/品番

| 部品  | 値/品番    |

|-----|---------|

| U1  | LT1803  |

| R1  | 1       |

| R2  | 2.7     |

| R3  | 1       |

| R4  | 5       |

| R5  | 2.2     |

| R6  | 3       |

| C1  | 0.47 µF |

| C2  | 10 pF   |

| C3  | 180 pF  |

| DAC | LTC2666 |

| HPA | HMC1114 |

ターンオンにかかる時間を測定した結果を図 4 に示しました。時間軸の 1 目盛りは 500 ナノ秒です。つまり、RF 信号の立上がり時間は、200 ナノ秒未満に抑えられています。ゲートに印加されるパルスが立上がり始める位置から、RF 信号の立上がりエッジにおける最後の位置まから、BF 信号の立上がります。1 マイクロ秒につまでの時間(ターンオン時間)は約 300 ナノ砂です。り、送信から受信への遷移時間を 1 マイクロ秒に抑えたいシステムにおいて、十分なマージンが確保できるということです。

図 4. HPA のターンオン時間の測定結果

図 5. HPA のターンオフ時間の測定結果

一方、図5に示したのは、ターンオフ時間の測定結果です。時間軸の1目盛りは図4と同じく500ナノ秒です。立下がり時間は立上がり時間よりもさらに短くなります。こちらも200ナノ秒を十分に下回っています。送信から受信への遷移時間として1マイクロ秒を割り当てているシステムにおいて、かなり大きなマージンが得られます。

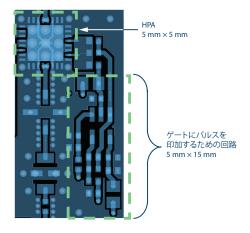

#### レイアウトの例

図6に、典型的なレイアウトの例を示しました。オペアンプのゲートにパルスを印加する回路は、HPAの入力につながるRFパスの隣に配置しています。高精度のDACは示していませんが、制御部に配置し、複数の送信チャンネルに入力信号を供給することになるはずです。このレイアウトを見ると、必要なスペースは最小限に抑えられていることがわかります。つまり、図2の回路は実用的なレベルのスペース/コストでプリント基板上のRF送信回路の部分に加えられるということです。

図 6. レイアウトの例

Analog Dialogue 51-12 3

## まとめ

本稿では、HPA を高速にターンオン/オフするための回路を紹介しました。HPA のゲートにパルスを印加することでそれを実現します。併せて、その評価結果も示しました。

この回路には次のような特徴があります。

- ▶ 200 ナノ秒未満の遷移時間

- ▶ あらゆるロジック入力形式に対応可能

- ▶ デバイス間のばらつきに対応するためにバイアスをプログラムすることが可能

- ▶ 最大ゲート電圧にクランプする保護機構

- ▶ 立上がり時間/オーバーシュートの補償機構

- ▶ 高密度のフェーズド・アレイ・アプリケーションに対応可能なサイズ

高度な電子システムでは、集積化が進んでいることもあり、実装面積の削減が継続的に求められます。本稿で紹介した回路(ないしは、これを少し改変したもの)は、HPAの高速オン/オフに広く採用されていくと考えられます。特に、遷移時間の短縮が求められるフェーズド・アレイ・アプリケーションでは、この種の回路が普及することになるでしょう。

# 著者:

Peter Delos (peter.delos@analog.com) は、アナログ・デバイセズの航空宇宙/防衛グループ(ノースカロライナ州グリーンズボロ)に所属するテクニカル・リードです。1990 年にバージニア工科大学で電気工学の学士号、2004 年にニュージャージー工科大学で電気工学の修士号を取得しています。1990 ~ 1997 年には、米海軍原子力プログラムの業務に携わりました。ここで、海軍原子力学校の幹部向けプログラムを修了し、海軍の潜水艦施設ではインストラクタとして、コネチカット州グロトンではシーウルフ級の潜水艦上でリード電気フィールド・エンジニアとして勤務しました。

1997年には、ニュージャージー州ムアズタウンの Lockheed Martin 社に入社し、複数のレーダーや EW (電子戦) プログラム用の受信器/励振器、シンセサイザの開発に携わりました。ここで経験した事柄は、アーキテクチャの定義、詳細設計、ラピッド・プロトタイピング、製造カバレッジ、フィールドへの配備、多くの工学的規律の調整など多岐にわたります。その後、この業務は、フェーズド・アレイ向け受信器/励振器の電子回路を、集中型のアーキテクチャからアレイ上のデジタル・ビームフォーミング・システムへと移行する取り組みに発展しました。

2016 年に現職に就きました。アーキテクチャ、プリント基板、IC という異なるレベルで、RF システムの設計に約 20 年にわたって携わってきました。

#### Peter Delos

この著者が執筆した他の技術文書 DACの位相ノイズ性能を改善、極めて精度の高い DDS アプリケーシ

ョンを実現可能に Analog Dialogue 51-08

Jarrett Liner (jarret.liner@analog.com) は、アナログ・デバイセズの航空宇宙/防衛グループに所属する RF システム・アプリケーション・エンジニアです。ノースカロライナ州グリーンズボロで勤務しています。RF に対応するシステムとコンポーネントの設計について豊富な経験を有しています。

以前は、アプリケーション・エンジニアとして航空宇宙/防衛分野向けに GaN on SiC のアンプを担当していました。RFIC、WLAN 向けパワー・アンプ、フロントエンド・モジュールの設計とテストには 13 年間携わっています。また、エレクトロニクス技術者として米海軍で 6 年間働いていました。ノースカロライナ州グリーンズボロにあるノースカロライナ農業工科州立大学で 2004 年に電気工学の学士号を取得しています。

研究所で回路ソリューションのシミュレーションやデータ収集を行っている以外は、マウンテンバイクに乗ったり、ジムでサイクル・クラスの指導を担当したり、ランニングしたり、庭で 4 人の子供たちを追いかけたり、といった具合に過ごしています。

## Jarett Liner

この著者が執筆した 他の技術文書 DAC の位相ノイズ性能 を改善、極めて精度の 高い DDS アプリケーションを実現可能に

Analog Dialogue 51-08

4 Analog Dialogue 51-12