In Chapter 3-1, the design and testing of logarithmic devices have been discussed and explained in some detail. This chapter will consider the various tradeoffs a designer is confronted with when applying a log device with a predetermined reference. The specifications of log modules, which were listed in Chapter 3-1, will be discussed in greater depth here, in the context of the manner in which they affect performance in an application.

#### SELECTING THE APPROPRIATE LOG DEVICE

There are many options available to the designer. These range from performing one's own design — from the ground up — using the most appropriate approach (linear approximations, diodes, monolithic-dual transistors, or other components characterized by logarithmic transfer characteristics) to purchasing one of the several types of log module available on the market today. Available standard devices, with guaranteed performance, range from modules containing a simple transistor-pair packaged with a temperature-compensating resistor network to complete logamplifiers containing op amps, a reference-current source, and all the necessary temperature- and frequency-compensating components.

# THE BASIC LOGARITHMIC ELEMENT

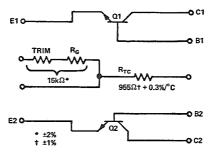

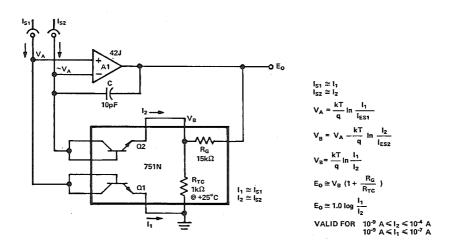

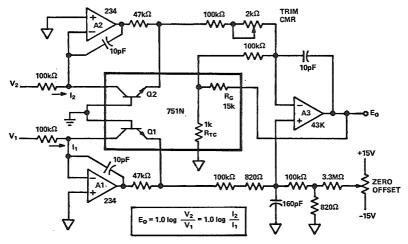

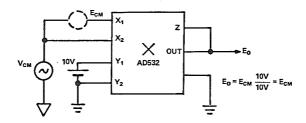

The simplest module available for temperature-compensated log circuits is the basic log element. A schematic of the Analog Devices Model 751 is shown in Figure 1.

Figure 1. Schematic diagram of 751N basic log element

At first glance, one may think that this is too trivial a module to consider for purchase; it contains only two transistors and three resistors. Superficially, this is true, but it is also true (though less obvious) that an essential characteristic of such a device is its isothermal environment. Also, despite the many advantages of monolithic dual transistors, a matched discrete-transistor pair is better-suited to the purpose of the device. Since the log element is the heart of a circuit that provides a logarithmic output, a thorough understanding of these two points is essential to successful design.

The transistors used in Model 751 are discrete transistors especially selected for log characteristics and carefully matched. There is a subtle, but important, advantage for discrete transistors: the combination of base spreading resistance and contact resistance, which can be lumped together and considered as a small resistor in series with the emitter, is the major cause of log conformity error at current levels from  $100\mu A$  to 1mA. The discrete transistors used in the 751 have a much lower value of series resistance, hence three to ten times better performance at these levels (without compensation circuitry) than do available high- $\beta$  monolithic pairs.

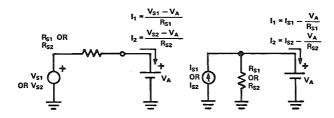

In order to capitalize on this advantage (as well as the temperature-tracking capability of matched transistors), it is imperative that the two transistors be located in an isothermal environment. At constant current, the  $V_{be}$  of a transistor has a temperature-coefficient of approximately -2mV/°C. If the junctions are

allowed to be as little as  $0.5^{\circ}$ C apart, the corresponding voltage difference is 1 mV, which corresponds to an input-current change of 4% (If  $1 \text{mV} = k\text{T/q} 1\text{n}(1+\lambda) = 26\text{mV} 1\text{n}(1+\lambda)$ , then  $\lambda = 0.04$ ). If errors from this source are to be held at less than 0.5%, the junctions must be held within  $130\mu\text{V}$ , or  $0.06^{\circ}$ C, under all conditions of ambient or internally-generated temperature change.

To obtain an isothermal environment, conductive epoxy and "heat clips" are used, and particular attention is paid to the layout. This environment is also essentially isothermal as regards the temperature-compensating resistor. To appreciate this advantage, one need only consider the effect of a small amount of air circulation over similar components sitting on an open circuit board. Although the compensation resistor may be precisely trimmed to eliminate the temperature-dependence of the scale factor, its effect can be nullified (and even detrimental) for differences greater than 1°C. These points are illustrated in Figure 2.

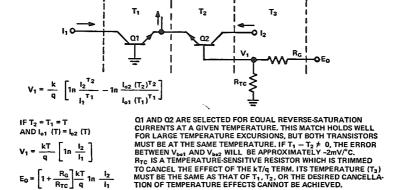

Figure 2.Importance of an isothermal environment for the basic log element.

# When to Apply the Basic Log Element

The simplest of all log modules, it contains only the log transistors, calibrated temperature-compensating resistors, and the isothermal environment necessary for reliable and predictable log operation. By itself, the basic log element can perform no useful function, but when coupled with two or three op amps, a reference-current source, and frequency compensation, a complete log amplifier can be built.

The basic log element should be considered primarily for special-purpose designs, calling for considerable design flexibility, e.g., physical form, current ranges, choice of reference or gains, etc. Though allowing considerable freedom for the circuit designer, it requires the greatest amount of care in the external wiring, circuit layout, and choice of components, to obtain best results.

The designer must take especial pains to obtain the best compromise of speed and dynamic stability. Familiarity with the stability considerations in Chapter 3-1, especially Figures 5 through 7 in that chapter, is essential. The *Log Circuits* Application Note<sup>1</sup> will also be of value.

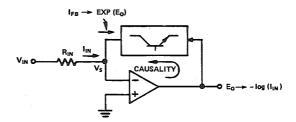

### THE LOG TRANSCONDUCTOR

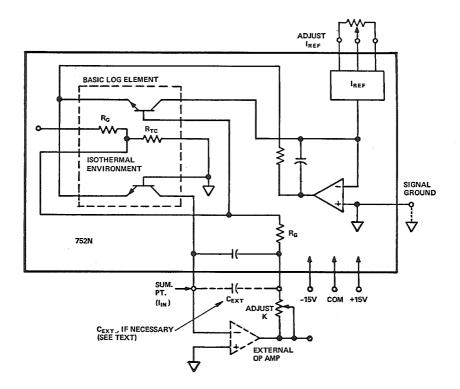

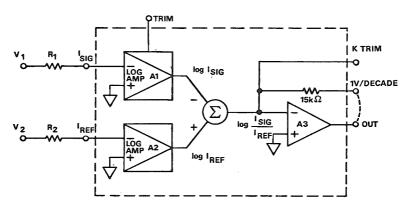

This term describes a device that combines a log element, reference-current source, op amp for the reference transistor, and the related frequency-compensation components. Figure 3 shows the basic circuitry of a log transconductor (Model 752) and its relationship to the basic log element (751).

Besides offering a completely-tested circuit, the log transconductor eliminates a number of application problems relating to stabilization: it is dynamically stable at all rated levels of input current.

To complete the log amplifier circuit, the designer needs only to provide an external operational amplifier and the two trim

<sup>1&</sup>quot;Design of Temperature-Compensated Log Circuits Employing Transistors and Operational Amplifiers," by W. Borlase and E. David, Analog Devices, Inc., March, 1969.

Figure 3. Functional diagram of a log transconductor and its relationship to the basic log element.

adjustments for  $I_{ref}$  and the scale factor, K. When currents beyond the specified range of the log transconductor are to be "logged," it may be necessary to add capacitance (10-20pF) in the feedback circuit of the external amplifier (Figure 3) for stability, at the cost of reduced bandwidth.

It should be noted that Figure 3 is a functional diagram of the 752 transconductor. For a wholly-packaged circuit, a separate basic log module is not used; in many cases a monolithic dual transistor is used to obtain improved temperature-tracking. To overcome the series-resistance problem mentioned above, a feedback compensation circuit is used internally to reduce the series resistance.

When to Apply the Log Transconductor

Log transconductors are used in preference to basic log modules when it is desired to use an essentially-complete packaged circuit with guaranteed performance instead of a collection of parts; yet, on the other hand, the designer wishes to optimize the price/performance mix by choosing the most appropriate operational amplifier to fit his needs.

The major error terms associated with log amplifier circuits (that are readily controllable) are the offset voltage and bias current of the operational amplifier. By choosing an amplifier to fit a specific application, the designer may, in most cases, effectively eliminate amplifier-caused errors at a given level of voltage or current. For example, when the logarithm of a low-level current is to be computed, the Model 42K amplifier may be used because of its 100fA bias-current specification.

If 100fA is compared to the lowest-level of signal current specified for the 752, 1nA, it can be seen to represent an error of 0.01%. If one starts by choosing this low value of bias current, its contribution to error could be completely ignored, despite the characteristic doubling/ $10^{\circ}$ C of FET-input-amplifier bias current. At 65° C, the bias current would have increased by a factor of  $2^{4} = 16$ , which is still insignificant compared to the other errors.

If the input signal is a voltage, the external op amp would be chosen for minimal offset voltage and drift. For ultimate low-level performance, "spikeless" chopper-stabilized amplifiers are perhaps the best choice; but one should also consider such low-drift chopperless types as the 184L and the AD504M, and especially, the 52K ( $I_b = 2pA$ ,  $\Delta E_{os}/\Delta T = 1\mu V/^{o}C$ ).

When economy is of prime concern, the log transconductor and a low-cost IC op amp can be the best answer. To achieve good performance when using a low-cost (modest-performance) amplifier, the input signal should be scaled so that its geometric mean falls in the center (i.e., geometric mean) of the range determined by the log transconductor's upper limit and 100x the bias voltage or offset current of the amplifier. With this approach, excellent

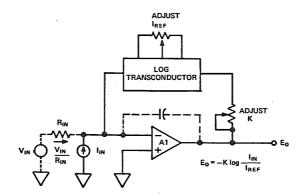

results can be obtained over a limited range. Figure 4 shows how the log transconductor is connected with an external op amp. Table 1 provides a brief selection guide.

Figure 4. Application of log transconductor. If the input signal is a current, connect it directly to the summing junction, as shown. If the input signal is a voltage, connect it to the summing junction through a resistance as shown by the dashed lines. Note that RIM includes the source resistance of VIM.

TABLE 1. SELECTION CRITERIA FOR A1 (FIGURE 4)

| INPUT SIGNAL                                                  | SELECT A1 FOR      | RECOMMENDED OP-AMP TYPE                                                          |  |

|---------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------|--|

| VOLTAGE                                                       | LOW OFFSET VOLTAGE | CHOPPER (234)<br>CHOPPERLESS LOW-<br>DRIFT (184L, 504M, 52K)                     |  |

| CURRENT                                                       | LOW BIAS CURRENT   | ELECTROMETER (42K)                                                               |  |

| VOLTAGE OR CURRENT: PERFORMANCE PERFORMANCE PERFORMANCE RANGE |                    | LOW-COST BIPOLAR OR<br>FET, I.C. OR MODULE:<br>AD301A, AD540,<br>MODEL 40, AD308 |  |

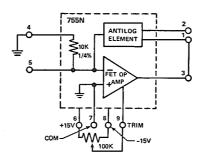

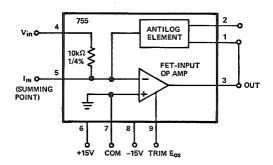

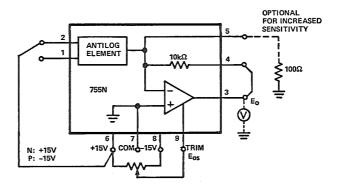

# THE COMPLETE LOG AMPLIFIER

The complete log amplifier contains a log transconductor, all the necessary trim circuitry, and a high-quality FET-input op amp. This is the most convenient type of log module, since the designer has only to connect power (usually ±15V @ ±10mA), input and

output leads. All the necessary frequency-stabilization and trimming have been performed by the manufacturer.

When to Apply the Complete Log Amplifier (and When Not to)

The complete log amplifier is the starting point for all new log-circuit designs. By freeing himself from the problems of designing, building, and trimming a log amplifier, the designer has more time available to deal with the problems involved in the instrument, apparatus, or system that led to the use of a log amplifier.

Performance of the complete log amplifier is adequate to deal with a wide range of input currents and voltages; and the fixed choices of reference  $(10\mu\text{A}, 100\text{mV})$  and scale factor (2/3, 1, 2) provide convenient scaling, which can be modified for the system by external gains and biases.

If wider ranges of current or voltage, greatly-different local scaling, or paired operations (such as the use of 752P and 752N in hyperbolic-sine operations), are necessary, then the need for the flexibility inherent in the log transconductor (or basic log devices) will become apparent (see Page 102).

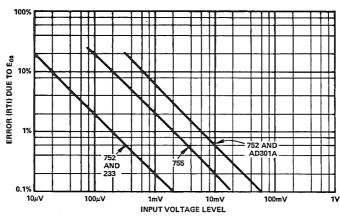

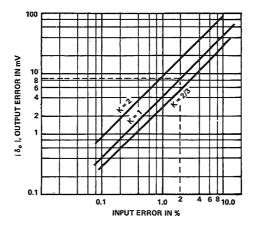

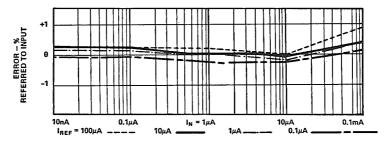

Figure 5. Effect of offset on dynamic range in terms of error vs. input level. Errors are for +2°C temperature change. Greater temperature changes move curves up proportionally (e.g., 755 at 10mV has 0.2% change for 2°, 2% for 20°).

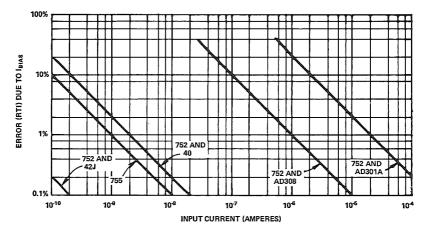

As an aid to determining the performance tradeoffs between the complete log amplifier (755) and the log transconductor-plus-external amplifier, the graphs of Figures 5 and 6 will be found helpful. They show the error as a function of input-voltage and current levels for the 755 and for the 752 with-external-op-amps of several types. The voltage error used in the plots is that caused by a 2°C variation from an initially-zeroed condition. The current error is essentially that caused by the amplifier's bias current.

Figure 6. Effect of op-amp bias current on dynamic range in terms of error vs. input level, for various combinations of op amps and log transconductors

# Selecting the Best Log Device for the Application

Table 2 provides general guidelines as to the choice of approach. The choice will be determined by the designer's principal objective: best performance, lowest cost, easiest-to-apply.

If cost is the criterion, then the basic log element may be the answer, but the saving is somewhat marginal; the designer must honestly evaluate the cost of designing, assembling, and testing the finished device. If the design is to be used in quantity, costs of drawings, parts inventorying, and production engineering must also be anticipated.

TABLE 2. SUMMARY OF SALIENT FEATURES OF CONSTANT-REFERENCE LOG MODULES (SUMMER, 1973)

| Log<br>Module                      | Description Contents and Applications                                                                                   | Advantages                                                                                                   | Disadvantages                                                                                                          |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Basic Log<br>Element<br>Model 751  | (2 Matched Log Transistors<br>Scaling and Temperature-<br>Compensating Resistors<br>For Special-purpose log.<br>designs | Lowest Cost<br>Greatest Flexibility                                                                          | Most Complex to Apply Requires at least 2 external op amps plus dynamic stabilization in conventional log application. |

| Log<br>Transconductor<br>Model 752 | {Basic Log Element<br>Reference-current source<br>To optimize operation at<br>low levels                                | Best performance obtainable through op amp choice                                                            | Requires external op<br>amp, gain trim<br>I <sub>REF</sub> trim                                                        |

| Log<br>Amplifier<br>Model 755      | (Log Transconductor<br>\FET-Input Op Amp  The initial choice for all fixed-reference log applications.                  | Easiest to apply. Meets specs with no trimming or exter- nal components. Best performance over a wide range. | Op amp is optimized for most (but not all) applications                                                                |

To optimize performance for a specific application, the log transconductor and a high-performance op amp selected for the application can offer the best performance.

The easiest log module to apply is the complete log amplifier. Except for the extremely low end of the signal range, the log amplifier offers performance equal to or better than that of any of the other choices.

While the generalities given above are helpful in selecting the best log device for the application, the proper choice can be made only when specific information regarding signal level, source impedance, and acceptable error has been developed.

Once this is known, the limitations on dynamic range caused by the input parameters of the op amp associated with the log modules can be determined.

#### STEP RESPONSE

The dynamic parameters of log modules are highly dependent on signal level, as Chapter 3-1 has demonstrated. Perhaps the most useful parameter to discuss in detail is the step response, since the response to a step of a given magnitude is usually a matter of

prime concern. The time required for the output to change (or "slew") from one level to another is dependent on the magnitudes of the input currents and on the direction, i.e., whether the current is increasing or decreasing.

Slewing rate of a log transistor's base-emitter voltage can be explained in terms of the effects of current level on the transistor's base-charging capacitance ( $C_b$ ), transconductance ( $g_m$ ), and incremental space-charge-layer capacitance ( $C_{je}$ ). Base-charging capacitance,  $C_b$  is defined as

$$C_b = \tau_F g_m = \tau_F \frac{q}{kT} |I_c|$$

(1)

where  $\tau_F$  is the average charge-replacement time in the base and  $I_c$  is the collector current.

Transconductance,  $g_m$ , and — in turn —  $C_b$  are proportional to  $I_c$ , provided that the base current is much greater than the reverse saturation current. This condition is met for all log modules operated within the specified range.

The capacitance of the transistor hybrid  $\Pi$  model,  $C_{\Pi}$ , directly controls the common-emitter current gain at high frequencies. It is equivalent to

$$C_{II} \equiv C_{je} + C_{b} \tag{2}$$

which, from (1), may be written as

$$C_{\Pi} \equiv C_{je} + \tau_{F} \frac{q}{kT} |I_{c}| \qquad (3)$$

The dependence of  $\omega_t$ , the frequency at which current-gain is unity, on  $C_\Pi$  is

$$\frac{1}{\omega_{\rm T}} \equiv \frac{C_{\rm II} + C_{\mu}}{g_{\rm m}} \tag{4}$$

where  $C_{\mu}$  is the feedback capacitance of the hybrid model.

Substituting (2) and  $g_m = \frac{q}{kT} |I_c|$  into (4),

$$\frac{1}{\omega_{\rm T}} = (C_{\rm je} + \tau_{\rm F} \frac{\rm q}{\rm kT} |I_{\rm c}| + C_{\mu}) \left[ \frac{\rm kT}{\rm q|I_{\rm c}|} \right]$$

(5)

$$= \tau_{\rm F} + (C_{\rm je} + C_{\mu}) \left[ \frac{kT}{q|I_{\rm c}|} \right]$$

(6)

Although base-charging capacitance,  $C_b$ , is directly proportional to collector current, its effect on  $\omega_t$  is nullified by the proportionality of  $g_m$  to collector current.

The net effect of these expressions is to show that the admittances of  $C_{je}$  and  $C_{\mu}$  are controlled by collector current; an increase in collector current results in greater bandwidth and faster slewing rate.

The above discussion relates only to the effect of the signal level on speed through its effect on the parameters of the log transistor. In a practical situation, there are many other factors that influence the speed of response of the circuit. The most important of these factors in log modules are the added feedback capacitance for stabilization, the stray capacitance at the amplifier input, and the bandwidth of the amplifier.

With proper stabilization circuitry, the amplifier and its stabilizing feedback capacitor should restrict speed only at the high end of the allowable input range. Stray capacitances modify the values of  $C_{je}$ ,  $C_{\mu}$ , and  $\tau_{F}$  in the expression defining  $\omega_{t}$ . The stray capacitance from summing junction to common is a constant that modifies  $\tau_{F}$ . Stray capacitance from collector to base is feedback capacitance and affects  $C_{\mu}$ .

Table 3 lists response times for steps of differing magnitude and current level for the 755 log amplifier. By comparing them with the equation for the radian period  $1/\omega_t$ , it is clear that the predicted linear relationship does exist at the lower levels, with a limit determined by the feedback capacitance and strays at the higher levels. In this region  $(1\mu\text{A to }1\text{mA})$ , other considerations, such as the bandwidth of the amplifier and the size of the stabilizing capacitor, dominate the response, and further improve-

TABLE 3. RESPONSE TIME (755) FROM 10 TO 90%

| I <sub>IN</sub> INCREASING |             | IN DECREASING  |       |

|----------------------------|-------------|----------------|-------|

| I <sub>IN</sub>            | TIME        | I <sub>M</sub> | TIME  |

| 1nA -> 10nA                | 1ms         | 10nA>> 1nA     | 4.5ms |

| 10nA → 100nA               | 100µs       | 100nA-> 10nA   | 400µs |

| 100nA-► 1μA                | <b>7</b> μs | 1μA —▶ 100nA   | 30µs  |

| 1μA —▶ 1mA                 | 4µs         | 1mA —> 1μA     | 7μs   |

ments in response time become marginal. Even if an external amplifier having near-infinite gain and requiring no stabilization capacitor were used, the improvements in slew rate would be slight.  $C_{je}$  and  $C_{\mu}$  are not quite constant, as assumed, but increase with signal level for currents of  $0.1\,\mathrm{mA}$  and more).

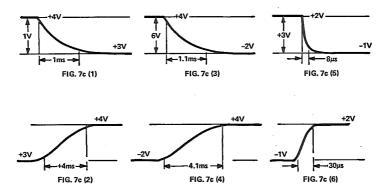

If steps of current are applied to the log module in the direction of increasing magnitude, a faster slew rate will be achieved than for steps in the direction of decreasing magnitude. Since the time to charge or discharge a capacitor is dependent on the available current, it is to be expected that steps which increase quiescent current will have a faster slewing rate and a shorter final exponential "tail." Because of the decreased time constant at high current levels, responses that end at higher levels will be completed faster than those ending at lower levels, even though the latter start faster than the former in traversing a given current range.

For changes over combinations of the ranges listed in Table 3, the response time will be determined by the final value of current. For example, in traversing the entire range of 1 nA to 1 mA, the total time will be dictated by the final value of 1 mA, resulting in a total response time of about  $6\mu\text{s}$ . Conversely, when slewing from 1 mA to 1 nA, the final value is 1 nA, and the total response time will correspond approximately to that for 1 nA, or 4.5 ms.

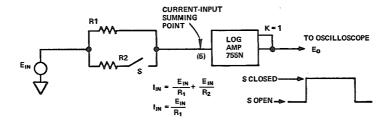

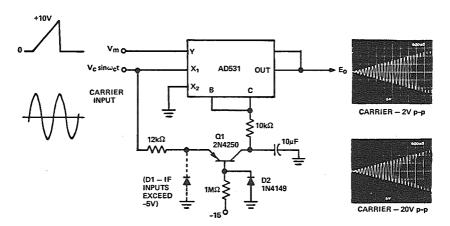

The dependence of slew rate on signal level will cause varying degrees of distortion for input square waves at various signal levels. Shown in Figure 7 are several input signals and the corresponding outputs from the log amplifier. By the choice of  $V_{\rm IN}$ , R1, and R2, and the position of electronic switch S1, the various input signals are readily obtainable. Alternatively, the square-wave-plus-bias of Figure 20, Chapter 3-1, may be used.

a) Test setup for measuring response time (10% - 90%)

| R <sub>1</sub> | R <sub>2</sub>                                                           | S Operation                                                     | Magnitude<br>Change                                                                                                                                          | Output<br>Waveform<br>Fig. 7c ( )                                                                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\Omega$ M001  | $11M\Omega$                                                              | CLOSED                                                          | 1nA → 10nA                                                                                                                                                   | 7c (1)                                                                                                                                                                                                                                                                 |

| $\Omega$ M001  | 11M $\Omega$                                                             | OPEN                                                            | 10nA <del>&gt;</del> 1nA                                                                                                                                     | 7c (2)                                                                                                                                                                                                                                                                 |

| $\Omega$ M001  | $100\Omega$                                                              | CLOSED                                                          | 1nA —→1mA                                                                                                                                                    | 7c (3)                                                                                                                                                                                                                                                                 |

| $100M\Omega$   | $\Omega$ 001                                                             | OPEN                                                            | 1mA → 1nA                                                                                                                                                    | 7c (4)                                                                                                                                                                                                                                                                 |

| 1M $\Omega$    | 1kΩ                                                                      | CLOSED                                                          | 0.1µA → 100µA                                                                                                                                                | 7c (5)                                                                                                                                                                                                                                                                 |

| $1M\Omega$     | 1kΩ                                                                      | OPEN                                                            | 100µA→0.1µA                                                                                                                                                  | 7c (6)                                                                                                                                                                                                                                                                 |

|                | $\Omega$ M00M $\Omega$ M0001 $\Omega$ M0001 $\Omega$ M0001 $\Omega$ M001 | 100MΩ 11MΩ<br>100MΩ 11MΩ<br>100MΩ 100Ω<br>100MΩ 100Ω<br>1MΩ 1kΩ | $100 M \Omega$ $11 M \Omega$ CLOSED $100 M \Omega$ $11 M \Omega$ OPEN $100 M \Omega$ CLOSED $100 M \Omega$ OPEN $100 M \Omega$ OPEN $10 M \Omega$ 1kΩ CLOSED | R <sub>1</sub> R <sub>2</sub> S Operation Change<br>100MΩ 11MΩ CLOSED 1nA $\rightarrow$ 10nA<br>100MΩ 11MΩ OPEN 10nA $\rightarrow$ 1nA<br>100MΩ 100Ω CLOSED 1nA $\rightarrow$ 1mA<br>100MΩ 100Ω OPEN 1mA $\rightarrow$ 1nA<br>1MΩ 1kΩ CLOSED 0.1μA $\rightarrow$ 100μA |

## b) Table of input values

c) Responses (10% - 90%)

Figure 7. Response time (10% — 90%) for steps of various magnitudes and polarities

### ANOTHER LOOK AT SPECIFICATIONS OF LOG DEVICES.

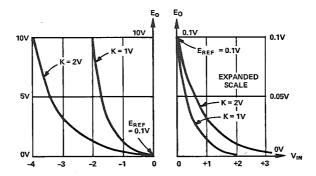

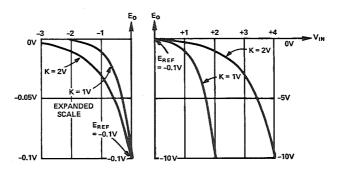

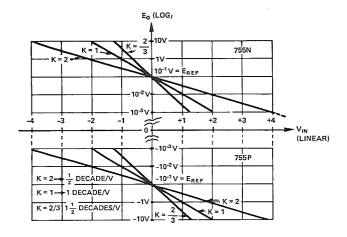

The transfer equation for a log module is

$$E_o = -K \log \frac{I_{IN}}{I_{REF}} \text{ or } -K \log \frac{V_{IN}}{E_{REF}}$$

(7)

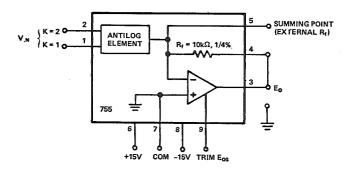

$I_{REF}$  is a dimensional constant necessitated by the fact that logarithms exist only for pure numbers (the expression log  $I_{IN}$  by itself would imply a reference current of 1A). When  $I_{IN} = I_{REF}$ , the logarithm of the ratio is zero.  $I_{REF}$  for practical devices can be chosen as one or the other extreme of the range of  $I_{IN}$ , or it may be approximately in the middle of the range (geometric mean).  $I_{REF}$  for Model 755 and similar devices is  $10\mu A$ , which corresponds to 0.1V for  $E_{REF}$ , the geometric mean between 1mV and 10V, hence mid-scale. Since the logarithm is real only for positive arguments, the input and reference must be of the same polarity, i.e., if  $V_{IN}$  is negative,  $V_{REF}$  must also be negative.

The gain, or scale factor, K is also a dimensional constant (volts). The typical log amplifier (755) can be connected for K = 1, K = 2, or K = 2/3. -K = -1 gives an output decrease of 1 volt for each 10X increase in the input ratio. K  $\log_{10}$  (ratio) can also be interpreted in terms of other logarithmic bases (B), according to the relationship,  $E_0 = -K' \log_B$  (ratio), where

$$K' = K \log_{10}B$$

(8)

For  $K = 1$ , BASE (B)  $K'$

100 2.0

10 1.0

8 0.903

5 0.699

3.16 0.50

$\epsilon$  0.434

2 0.301

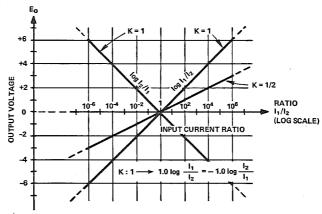

K'is the output change corresponding to an input ratio change, B.

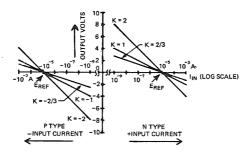

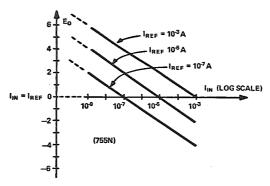

The 755 and 752 modules are really families having devices of both polarities. 755N and 752N utilize NPN transistors (751N); 755P and 752P utilize PNP transistors (751P). When used for log operations, the "N" versions accept positive voltage or current, and K is positive (that is, the output becomes less positive or more negative as the input becomes more positive — the characteristic response of any circuit involving an inverting operational amplifier); the P versions accept negative voltage or current for logarithmic operation, and K is negative (that is, the output becomes less negative, or more positive, as the input becomes more negative — again, an inverting response). The output voltage of both devices is plotted against current input (log scale) in Figure 8. All three inherent values of the scale factor, K, are shown.

Figure 8. Plot of output voltage vs. input current for model 755

#### INTERPRETING LOG-DEVICE TERMS

Log Conformity Error: Log conformity error is the difference between the actual output voltage and the output voltage predicted by the log-transfer equation. A plot of output vs. input, when plotted on semilog paper (linear output scale, log input scale), should be a straight line. Any deviation from this straight line is log conformity error; in this sense, it is analogous to linearity error for linear devices. For most log amplifiers, the best

linearity is obtained in the middle 4 decades (10nA to  $100\mu$ A). In this range, for 755, log-conformity error is  $\pm 0.5\%$  referred to the input (RTI) or 2.17mV referred to the output (RTO) for |K| = 1. To obtain best results, the input data, if possible, should be centered within this range.

Log conformity error is the one irreducible error of the log amplifier. It appears as an error in the log operation and cannot be compensated-for with internal circuitry.

Offset Voltage  $(E_{os})$ : The offset voltage of the log module is the offset voltage of the internal amplifier. This voltage acts as though it were a small dc offset voltage in series with the input terminals. For voltage-logging operations, best performance is obtained with the offset voltage trimmed.

Since  $E_{os}$  appears in series with  $V_{IN}$ , the effect of  $E_{os}$  depends on the level of  $V_{IN}$ . Referred to the input, the error contribution of  $E_{os}$  is

% RTI =

$$(E_{os}/V_{in})$$

100% (9)

Determining the output error corresponding to a given RTI error is straightforward. For example, for a RTI error of  $\frac{1}{2}\%$ , (1± 0.005), the respective values of the logarithm are 0.002166 (1.005) and -0.002177 (0.995), or about  $\pm 0.0022$ . Multiplying by K = 1V yields an output error of  $\pm 2.2$ mV for an input error of  $\pm \frac{1}{2}\%$ .

An alternative method of determining RTO errors from RTI (or vice versa) is to use an abbreviated table, such as Table 4,\* with linear interpolation, if necessary.

<sup>\*</sup>Note: Table 4 differs from the table in the Specifications section of Chapter 3-1; in the latter table, the errors are based on low-side error (e.g.,  $1-0.1\% \rightarrow 0.999$ ), hence give greater errors referred to the output. In table 4 on this page, the errors are based on high-side error ( $1 + 0.1\% \rightarrow 1.001$ ), hence give greater errors referred to the input. While not significantly different, worst-case error computations should take into account the more-important error from the standpoint of the application.

| % Error<br>Referred to | Millivolt Error<br>Referred to Output $(\delta_n)$ |        |         |

|------------------------|----------------------------------------------------|--------|---------|

| Input $(\delta_i)$     | K=1                                                | K = 2  | K = 2/3 |

| 0.1%                   | 0.43mV                                             | 0.87mV | 0.29mV  |

| 0.5                    | 2.17                                               | 4.33   | 1.44    |

| 1.0                    | 4.32                                               | 8.64   | 2.88    |

| 3.0                    | 12.84                                              | 25.67  | 8.56    |

| 4.0                    | 17.03                                              | 34.07  | 11.36   |

| 5.0                    | 21.19                                              | 42.38  | 14.13   |

| 10.0                   | 41.39                                              | 82.79  | 27.60   |

This table gives representative examples of input errors and the corresponding error at the output for common values of K. For a given output error, the input error can be computed by linear interpolation. The curves may also be helpful in obtaining approximate error conversions instantly. Example shown: 2% error ≅ 8.5mV.

Table 4. Error conversion:  $|\delta_0| = K \log_{10} (1 + \delta_i/100)$

For example, to determine the RTI error equivalent to 14mV out for K = 1, the nearest value to 14mV is 12.84mV, at 3.0%. To this should be added (4.0-3.0) (14-12.84)/(17.03-12.84)=0.28, for a total error of 3.3% RTI.

Offset Current  $(I_{os})$ : The offset current,  $I_{os}$ , of the log amplifier is the bias current of the internal amplifier. This parameter can be a significant source of error when processing signals in the nanoampere region. For this reason, it is important to select a log amplifier having bias current much less than the smallest signal to be processed. Error contribution of  $I_{os}$  is:

$$\% \text{ RTI} = (I_{os}/I_{IN}) 100\%$$

(10)

Reference Current  $(I_{REF})$ :  $I_{REF}$  is the internally-generated current source to which all input currents are compared. Tolerance errors in  $I_{REF}$  appear as a dc offset at the output. Other offsets appearing at the output cannot be differentiated from the effects of  $I_{REF}$  error. This is easily demonstrated by considering the transfer equation with an added offset

$$E_o = -K \log \frac{I_{IN}}{I_{REF} (1 \pm P/100)} \pm E_1$$

(11)

where P represents the percent tolerance in  $I_{\text{REF}}$  and  $E_1$  is the output offset.

This equation can be rewritten

$$E_o = -K \log \frac{I_{IN}}{I_{REF}} + K \log (1 \pm P/100) \pm E_1$$

(12)

Since both the second and the third terms on the right-hand side of (12) are constants, they can be combined to form a constant  $E_2$ :

$$E_o = -K \log \frac{I_{IN}}{I_{P,E,E}} \pm E_2$$

(13)

Table 4 can be used, as before, to determine the RTI equivalent of the combined offset,  $E_2$ , and this new tolerance (P') can be part of the error in  $I_{R.E.F}$ :

$$E_o = -K \log \frac{I_{IN}}{I_{RFF} (1 \pm P / 100)}$$

(14)

The specified tolerance for  $I_{R\,E\,F}$  of log amplifiers includes dc output offset errors, since they are inseparable from the effects of  $I_{R\,E\,F}$ .

The effect of  $I_{R\,E\,F}$  tolerance errors can be compensated for by adding a constant at the output or in a stage following the output, or by trimming the input scale factor ahead of the log amplifier.

Reference Voltage  $(E_{REF})$ :  $E_{REF}$  is the effective internally-generated voltage to which all input voltages are compared. It is related to  $I_{REF}$  through the equation,

$$E_{REF} = I_{REF} R_{IN}$$

(15)

where  $R_{\rm IN}$  is the total input-circuit resistance, including the input resistor, the signal source resistance, and any other appreciable series resistance. Virtually all the tolerance in  $E_{\rm R\,E\,F}$  is due to  $I_{\rm R\,E\,F}$ , provided  $R_{\rm IN}$  is made up of stable precision resistors. Consequently, variations in  $I_{\rm R\,E\,F}$  cause a shift in  $E_{\rm R\,E\,F}$ .

The effects of  $E_{REF}$  tolerance errors are compensated for in the same manner as the similar effects of  $I_{REF}$ .

Scale Factor (K): Scale factor is the voltage change at the output for a decade (i.e., 10:1) change at the input. Scale-factor error is equivalent to a change in gain, or slope, and is specified in percent of the nominal value. An external adjustment may be performed to fine-trim the scale factor (usually preset) or it may be locally adjusted to a value that is several times the initial value by adding series resistance at the feedback terminal. It can also be manipulated by adjusting the gain of a stage following the log amplifier. (Its effect is the same as that of manipulation of the exponent of the log-amplifier input.)

### ADJUSTING THE PARAMETERS OF LOG DEVICES

Adjusting  $E_{os}$ : The amplifier's offset voltage may be adjusted to near-zero by a very simple but unconventional procedure. Most users of op amps are accustomed to "zeroing" an op amp's offset voltage by adjusting for a zero-volt output. For log modules, this is not applicable, since a zero output corresponds to the log of 1  $(I_{IN} = I_{REF})$ , and log (0) is not defined.

There is, however, a quite convenient method of adjusting  $E_{os}$  without disturbing the log circuit arrangement (except for grounding the input). The method is shown in Figure 9, and, while specifically applied to the 755, it is applicable to all log amplifiers. Under the conditions shown in Figure 9, the output is

$$E_o = -K \log \frac{V_{IN} - E_{os}}{E_{REF}}$$

(16)

Figure 9. Trimming EOS

Since the input terminal is grounded through the  $10k\Omega$  resistor,  $V_{\rm IN}$  = 0. The equation for output voltage then becomes

$$E_o = -K \log \frac{-E_{os}}{E_{REF}}$$

(17)

Remembering that the log is undefined for zero, assume a practical limitation on  $E_{os}$ , and then calculate  $E_o$ : Since the change in  $E_{os}$  with temperature for a good FET amplifier is in the range of  $20\mu V/^o C$ , it is reasonable to assume that adjustment of  $E_{os}$  to  $10\mu V$  would be reasonable.

Using this value of  $E_{os}$  and the value of K and  $E_{REF}$  specified for the log amplifier, the output can be calculated. For Model 755N, as shown in Figure 9, the output is

$$E_o = -1V \log \left[ \frac{-\pm 10\mu V}{100mV} \right] = 4V$$

, for  $E_{os} = -10\mu V$  (18)

The amplifier's offset voltage can therefore be adjusted to within  $10\mu V$  by adjusting for a +4V output (for 755P, the output would be -4V). By adjusting for a higher output voltage, one can adjust the offset to a still smaller value. Care should be taken to ensure that the amplifier's output voltage specification is not exceeded, since this may lead to a false offset indication.

A volt-ohmmeter is all that is required to monitor the output, since the signal level of 4V is high, and impedances are low. If an oscilloscope is used to monitor the output, high noise levels will be

observed when performing this adjustment. This is to be expected, since the sensitivity is extremely high: for the next decade, (5V - 4V) out/(10 $\mu$ V - 1 $\mu$ V) in = 111,000, gain for input noise. The open-loop gain of the amplifier may, in some cases, limit the closeness with which zero input may be approached, beyond 4V out. For 755P, the output is adjusted to < 4V.

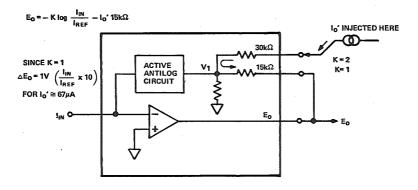

Reference-Current Adjustment: A shift of reference current results in a dc offset at the output. By adding a dc voltage to the output, one may change the reference current to the desired value. This can be accomplished in the amplifier stages following the log amplifier or by injecting a current into an unused scale-factor-feedback terminal. In the latter case, the impedance of the scale-factor terminal being used must be known. The current inserted into the unused terminal, multiplied by the resistance in series with the used terminal determines the amount of offset change. This point is illustrated in Figure 10.

Figure 10. Adjusting I<sub>REF</sub> by inserting current into unused scale-factor terminal. Since V<sub>1</sub> is determined by input only, I<sub>O</sub>' must flow out through  $15k\Omega$  resistor, biasing E<sub>O</sub> by  $(15k\Omega)$  (I<sub>O</sub>'). If I<sub>O</sub>'  $\cong$ 67 $\mu$ A at terminal 2, I<sub>REF</sub> is, in effect, divided by 10.

It should be noted that shifting  $I_{REF}$  has no effect on the output other than changing the value of input at which zero output is obtained (Figure 11).

Figure 11. Output vs. input (log scale) as a function of I REF

Reference-Voltage Adjustment: The reference voltage is defined in (15). Provided that  $R_{\rm IN}$  is constant over the range of operation, the effects of changes of  $E_{\rm R\,E\,F}$  are the same as for those of  $I_{\rm R\,E\,F}$ , and the adjustment technique is exactly the same.

Scale-Factor Adjustment: Scale-factor may be adjusted by changing the total resistance between the output and the dummy summing junction shown in Figure 10. By adding resistance in series with one of the scale-factor terminals, the scale-factor may be increased from its nominal value. In general, the total resistance required to obtain any value of scale factor is

$$R_{T} = K R_{1} \tag{19}$$

where  $R_1$  is the resistance of the resistor at the 1V/decade scale-factor terminal and K is the desired scale factor.

Example: To achieve a 5V/decade scale factor for a log amp having a  $15k\Omega$  input resistor at the 1V/decade terminal, calculate the external resistance required  $(R_T-R_1)$  or  $(R_T-R_2)$ .

$$R_T = (5)(15k\Omega) = 75k\Omega \tag{20}$$

The total resistance required is thus  $75k\Omega$ . If one uses the 1V/decade terminal, the external resistance required is  $(75-15)k\Omega = 60k\Omega$ . Alternatively, one might use the 2V/decade terminal, and connect an external resistance of  $(75-30)k\Omega = 45k\Omega$ .

#### **APPLICATIONS**

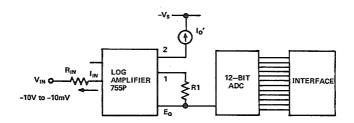

#### LOG OF VOLTAGE - DATA-COMPRESSION EXAMPLE

One of the more-interesting applications of a log module is in data compression. Suppose it is desirable to introduce a signal to a computer or data link, maintaining an accuracy within 1% of the signal throughout the range.

The conventional approach might be to select an A/D converter having sufficient resolution to meet the accuracy requirement. If the input range were 1V to 10V, the dynamic range would be from 1% of 1V to 10V, or 1000:1. To obtain this resolution, a 10-bit converter might be used,\* and 1 LSB (least-significant bit) would represent 1% of the smallest signal. If the range were increased to 10mV to 10V, the converter would require a resolution of 1% of 10mV to 10V, or 1:100,000. To even approach this resolution, a 16-bit converter would be barely sufficient.\* An economical alternative, maintaining the required 1%-of-signal accuracy error is to use a log module over a 3-decade range for data compression, and a 12-bit A/D converter. The proposed scheme is shown in Figure 12.

Figure 12. Data compression, using a log amplifier

In order to convert the log output to a unipolar signal, an external current source will be used to shift the reference current. To achieve the proper scale-factor, or gain, an external resistor, R1,

has been added in series with the K=1 output. The input resistance value,  $R_{\rm IN}$ , will be chosen for the range of best log conformity, and connected at the current input, pin 5.

The first step in applying the log amplifier is to select the proper polarity. Since the input voltage is negative (-10mV to -10V), the P-type log amplifier is required. A Model 755P complete log amplifier is chosen, in order to minimize the design effort.

Choosing  $R_{IN}$ : After selecting the log amplifier, the region of best log conformity is noted, and an attempt is made to shift operation to those decades. For Model 755, the best log conformity is 0.5%, specified for the range from 10nA to 100 $\mu$ A.  $R_{IN}$  is selected, for use at the current input, to provide the highest input current desired (100 $\mu$ A) at the highest input voltage magnitude (10V).

$$R_{IN} = 10V/100\mu A = 100k\Omega$$

(21)

The lowest value of input current expected is  $10\text{mV}/100\text{k}\Omega = 100\text{nA}$ . The input-current range is therefore well within the range of 0.5% log conformity.

Adjusting K: To determine the best value of K for the application, the input requirements of the following stage must be considered. If we assume the 12-bit converter to have an input range of 0 to +5V, K can be calculated. The total output voltage required is 5V, and the input range spans 3 decades. Therefore, K must be 5/3V.

From the data sheet for the log amplifier selected (755P), a value of  $15k\Omega$  is given as the input resistance of the 1V/decade terminal. The total resistance required for K = 5/3V is

$$R_{T} = (5/3)(15k\Omega) = 25k\Omega \tag{22}$$

A nominal  $10k\Omega$  is required in series with the K = -1 terminal. To allow for tolerance of the internal resistor, a  $10k\Omega$  10-turn pot in series with a  $5k\Omega$  resistor is adopted as R1.

Shifting  $I_{REF}$ . Since  $I_{REF}$  determines the point at which a zero output will be obtained, and since a zero output is desired for the smallest input current to be processed, it is this value of current, 100nA, that  $I_{REF}$  will be shifted to.

The transfer curves for the 755P (Figure 8) show that a -2V output would be obtained for 100nA input at K = -1V. Since this is the current level for which a zero-volt output is desired, the current  $I_0$  injected into the unused scale-factor terminal must shift the output in the positive direction. Referring to Figure 10, one can see that a polarity inversion occurs between the unused scale-factor terminal and the output. To cause a shift in the positive direction, the current to be injected must be negative, i.e., derived from a negative voltage.

The amount of current to be injected can be calculated by Ohm's Law, using the total resistance of the scale-factor terminal connected to 1, the output, and the amount of voltage to be shifted.

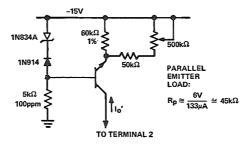

$$I = \frac{2K}{R_T} = \frac{2 \times 5/3}{25k\Omega} = 133\mu A \tag{23}$$

A resistor to the negative supply (of value  $15V/133\mu A = 30k\Omega$ ) can be used to obtain this current, but shifts in the offset voltage

Figure 13. Constant-current source to shift reference current  $(I_0)' = 133\mu$ ) in circuit of Figure 12.

at the dummy summing junction (Figure 10) of 60 mV/decade can cause significant errors. For example, if  $I_{REF}$  were adjusted at  $100 \text{nA} \ I_{IN}$ , a shift of 180 mV would occur as the input increased to  $100 \mu \text{A}$  (3 decades @ 60 mV/decade), resulting in a shift of offset current of  $(180 \text{mV/15V}) \times 100 = 1.2\%$ .

Therefore, a rudimentary current source, shown in Figure 13, is used.

#### Trim Procedure

1.  $E_{os}$ : The first step in the trim procedure is to adjust  $E_{os}$  of the log amp to nearly zero volts. As mentioned earlier, this can be accomplished by leaving pin 5 open (or  $V_{IN}$  disconnected), and grounding pin 4. The trim pots for  $I_{REF}$  and the scale factor should be set to midrange, in order to reduce interaction. R2 would then be adjusted for

$$E_o = -K \log(10\mu V/E_{REF})$$

= (5/3) log (10\mu V)/(100nA × 10k\Omega)

= -10/3 V (24)

Adjusting for any voltage between -10/3V and -5V will insure that  $E_{os}$  has been adjusted to within  $10\mu V$ .

- 2.  $I_{REF}$ : After  $E_{os}$  has been adjusted,  $I_{REF}$  can be adjusted by applying a value of input that will cause  $I_{REF}$  to flow into the log amplifier. To accomplish this, set  $V_{IN}$  to 10 mV and adjust the reference-current source for zero volts out of the log amplifier.

- 3. K: To adjust K, the input signal should be increased to its maximum value of -10V. R1 is then adjusted for 5V output.

- 4. Because some interaction among the adjustments cannot be avoided, all adjustments should be repeated at least once, and in the same order as initially performed,  $E_{os}$ ,  $I_{REF}$ , K.

## Error Analysis

| Parameter                               | Error      | Comment                                                                                                                                                                      |

|-----------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E <sub>REF</sub>                        | ≅ 0        | Initial error is trimmed to zero                                                                                                                                             |

| E <sub>REF</sub> Drift                  | 0.5% RTI   | $\pm 0.1\%$ /°C x 5°C = 0.5%                                                                                                                                                 |

| Log Conformity                          | 0.5% RTI   | Input was scaled to within range of $\pm 0.5\%$ log conformity                                                                                                               |

| Eos                                     | <b>≅</b> 0 | Initial error trimmed to zero                                                                                                                                                |

| E <sub>os</sub> Drift                   | 0.75% RTI  | ( $\pm$ 15 $\mu$ V/ $^{O}$ C $\times$ 5) / 10mV worst-case condition; occurs only for smallest input signal (7.5 $\mu$ V/10mV) (100%) = 0.75%                                |

| I <sub>os</sub> , I <sub>os</sub> Drift | <b>≅</b> 0 | Negligible contribution<br>(10 pA/100 nA) (100%) = 0.01%                                                                                                                     |

| K                                       | ≅0         | Initial error trimmed to zero                                                                                                                                                |

| K Drift                                 | ±10mV RTO  | $\pm 5^{\circ}$ C × 0.04%/ $^{\circ}$ C × K log (V <sub>IN</sub> /E <sub>REF</sub> )<br>= $\pm (3 - 0.33)$ mv log (V <sub>IN</sub> /0.01V) = 10mV @<br>V <sub>IN</sub> = 10V |

Total error, referred to input, at constant temperature: ±0.5%.

Total error, RTI, over the temperature range, assuming a worst-case condition that all errors are additive:

$$(\pm 0.5 \pm 0.5 \pm 0.75)\%$$

RTI + 10mV RTO

Converting 10mV RTO to an RTI term by Table 4 yields 1.4%.

Total error RTI over the 10°C temperature range is 3.15% (1.74% root-sum-squares).

A/D converter error: If the total converter error is kept to 1LSB = 1/4096F.S., the equivalent log-amplifier output error is 5/4096 = 1.22mV. From Table 4, this is equivalent to 0.28%, referred to the input, at any level.

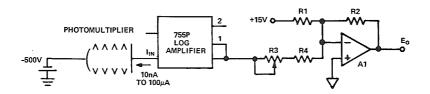

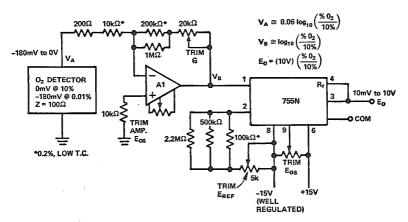

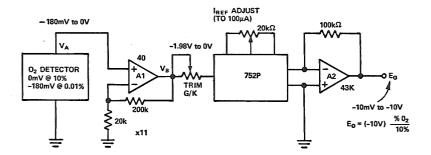

# LOG OF CURRENT - PHOTOMULTIPLIER EXAMPLE

In this example, the output current of a photomultiplier tube is to be applied to a log amplifier, as shown in Figure 14.

Figure 14. Log of current - photomultiplier input

Since the input is a current source, there is no need to perform the offset-voltage adjustment. This can be verified by determining the source resistance that will produce 0.5% error RTI at the lowest level:  $R_S = 500\mu V/(0.005 \times 10 nA) = 10 M\Omega$ , easily achievable with a photomultiplier.

The output of the 755P will be as predicted by the transfer curve (Figure 8). Level shifting, in this case, is accomplished by adding an offset to A1 *via* R1, and gain is trimmed by a small resistor R3 in series with R4.

For 0 to -10V output, the gain of A1 is 10/4, or 2.5, since 4V is the entire output range of the log module when spanning 4 decades at 1V/decade. The ratio of  $R_2$  to  $(R_3 + R_4)$  is then 2.5:1.

At the low end of the range (10nA), the corresponding output voltage is -3V. At the output of A1, it is amplified to (-3)(-2.5) = 7.5. In order to offset it to zero at the output of A1, R1 must have the value, determined by the gain equation

$$+15V(-R_2/R_1) = -7.5V$$

$$R_1 = 2R_2$$

(25)

If R2 is selected to be  $25k\Omega$ ,

$R_1 = 50k\Omega$   $R_3 = 10k\Omega$  pot  $R_4 = 5k\Omega$

# Error Analysis @ ±10° C Temperature Range

| Parameter                               | Error | Comment                                                                                                                                              |

|-----------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| IREF                                    | ≅0    | Trimmed to zero by R1                                                                                                                                |

| IREF Drift                              | ±1%   | $\pm 0.1\%$ /°C × 10°C = $\pm 1\%$                                                                                                                   |

| Log Conformity                          | ±0.5% | Not trimmable                                                                                                                                        |

| E <sub>os</sub> , E <sub>os</sub> Drift | ≅0    | Can neglect when equivalent (Thevenin) voltage is much greater than $\mathbf{E}_{\mathrm{OS}}$                                                       |

| Ios                                     | <0.1% | Worst case at lowest input current (10 nA/10 pA) (100%)                                                                                              |

| l <sub>os</sub> Drift                   | <0.1% | Additional 10pA due to I <sub>OS</sub> doubling per 10 <sup>o</sup> C increase                                                                       |

| κ                                       | ≅0    | Initial error of 10mV trimmed to zero by R3                                                                                                          |

| K Drift                                 | 12mV  | $\pm 10^{\circ}$ C × 0.04%/°C × K log (I <sub>IN</sub> /10 $\mu$ A)<br>= 4mV log (I <sub>IN</sub> /10 $\mu$ A), worst-case at I <sub>IN</sub> = 10nA |

Total error, referred to input, at constant temperature: ±0.6%.

Total error, RTI over the temperature range:

1.7% + 12mV RTO = 4.5% RTI. Referred to the output by Table 4, 4.5% RTI is equivalent to 19.3mV, or less than 1/2% of F.S.

The logarithm is a mathematical function. When it is employed to describe the behavior of a physical entity, its argument must be dimensionless. Accordingly, practical logarithmic devices always compute the log of a ratio of two voltages or currents; the numerator is termed the "signal," the denominator the "reference."

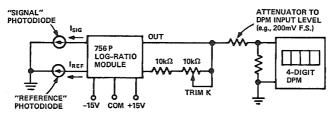

The distinction between "log" devices and "log-ratio" devices is practical, not semantic. It is determined by the requirements of the application on the "reference," and the consequent effects on the circuit design and external connections. If the reference is more-or-less fixed and considered a constant, the subject is a "log" device. If the reference is controlled by an external signal, or is simply considered to be freely variable, a different circuit design is usually employed, and it is called a "log-ratio" circuit. It is to the latter group of applications that this chapter is devoted.

A typical commercially-available log-ratio circuit (Model 756) has its performance defined over a range of 4 decades of signal current and 3 decades of reference current, or a total range of ratio of  $10^7$ :1. While it is convenient to use and by no means expensive, the user can often find it a more practical matter to design a log ratio circuit to meet a set of *specific* needs with the aid of the basic log element (751). Log-ratio circuitry is somewhat simpler to deal with than log circuitry, because a separately-generated reference current is unnecessary.

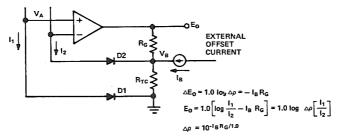

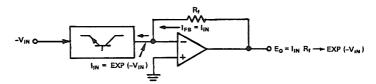

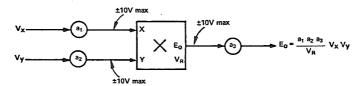

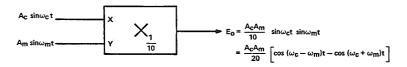

Figure 1 shows the simplest temperature-compensated log-ratio circuit, driven by two current sources,  $I_{s1}$  and  $I_{s2}$ . Since the

operational amplifier maintains its inputs at essentially the same potential,  $V_A$ , the two log-diode-connected transistors are essentially in series-opposing, and the sum of their voltage drops, proportional to the log of their current ratio, appears at the tap of the voltage divider,  $V_B$ . If  $I_{s2}$  can be kept low enough so that it does not significantly load the voltage divider,

$$E_{o} \cong \left[1 + \frac{R_{G}}{R_{TC}}\right] \frac{kT}{q} \ln \left[\frac{I_{s1}}{I_{s2}}\right]$$

(1)

The divider incorporates a temperature-sensitive resistor,  $R_{TC}$ , which is designed to compensate for the temperature variation of kT/q. The resistance values of  $R_G$  and  $R_{TC}$  are chosen and trimmed to make

$$\left[1 + \frac{R_G}{R_{TC}}\right] \frac{kT}{q} \ln(10) \approx 1.00V \tag{2}$$

Therefore,

$$E_o \cong 1 \cdot \log \left[ \frac{I_{s1}}{I_{s2}} \right]$$

(1V/decade) (3)

independently of temperature.

Figure 1. Simple temperature-compensated log-ratio circuit

## **VOLTAGE vs. CURRENT: INPUT-LOADING EFFECTS**

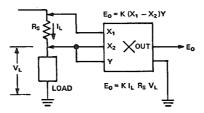

Since the basic log elements convert linear current to log voltage, inputs in the form of current from ideal current sources having "infinite" source resistance can be used with any of the circuits to be discussed here. If the input signal is a voltage, it must first be converted to a current. This is, of course, an inherent feature of circuits that employ inverting operational amplifiers operating at zero common-mode potential.\* A precise value of series resistance will determine the current scaling. However, in the simple circuit of Figure 1, employing a differential-input operational amplifier, a voltage source and its series resistor "look into"  $V_A$ . At the negative input terminal,  $V_A$  is a variable common-mode voltage; at the positive input terminal, it is a nonlinear load resistance. If the input voltages are  $V_{s1}$  and  $V_{s2}$ , in series with resistances  $R_{s1}$  and  $R_{s2}$ , then (Figure 2a)

$$\log \frac{I_1}{I_2} = \log \left[ \frac{V_{s1} - V_A}{V_{s2} - V_A} \cdot \frac{R_{s2}}{R_{s1}} \right]$$

(4)

If the inputs are imperfect current sources, having non-infinite internal resistances, the effect is similar. The log ratio of the actual input currents is

$$\log \frac{I_1}{I_2} = \log \frac{I_{s1} - V_A/R_{s1}}{I_{s2} - V_A/R_{s2}}$$

(5)

$V_A$  is an implicit function of  $I_{s1}$ ,  $R_{s1}$ ,  $V_A$ , and the reverse-saturation current of D1,  $I_{ES1}$

$$V_A \cong \frac{kT}{q} \ln \frac{I_1}{I_{ES1}} = \frac{kT}{q} \ln \frac{I_{s1} - V_A/R_{s1}}{I_{ES1}}$$

(6)

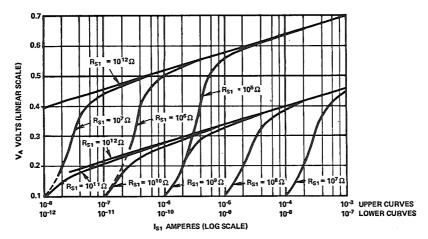

While  $V_A$  cannot be determined explicitly, it can be plotted as a function of  $I_{s1}$  for various values of  $R_{s1}$  (Figure 2b). The plot is based on the assumption that  $I_{ES1}$  at 25°C is about  $2 \times 10^{-1.5}$  A, a realistic value for the best log transistors. For higher values of  $I_{ES1}$  or temperature, the plotted value of  $V_A$  is high, i.e., conservative, by about 60 mV/decade of  $I_{ES}$  and 2 mV/°C. Quite often,  $V_A$  is simply assumed to be about 0.6V; however, for

<sup>\*</sup>See Fig. 8, this Chapter, and Fig. 9 in Chapter 3-1.

low-current operations, this figure could be conservative by a factor of 2 or more.

The output error attributable to  $V_A$  and finite source resistance is a term that adds to (3), approximately

$$1 \cdot \log \left[ \frac{1 - V_A / R_{S1} I_{S1}}{1 - V_A / R_{S2} I_{S2}} \right] \tag{7}$$

The difference between the term inside the brackets and 1.00 is the ratio-error (%/100) contribution, referred to the input. The relationship between input and output errors can be seen in Table 4, Chapter 4-1 (K = 1).

Figure 2a. Input current as a function of source voltage or current, source resistance, and  $V_A$ . Amplifier bias current and circuit leakage current are considered negligible here.

Figure 2b.  $V_A$  as a function of input current for various values of source resistance, assuming that  $I_{ES}\cong 2\times 10^{-15}$  A @ +25°C

It has been assumed that  $I_2$  does not load the feedback voltage divider. To investigate the validity of this assumption, note that

$$E_o = V_B + R_G \left(\frac{V_B}{R_{TC}} - I_2\right) = V_B \left(1 + \frac{R_G}{R_{TC}}\right) - I_2 R_G$$

(8)

The error,  $I_2R_G$ , if  $I_2=1\mu A$ , is (for  $R_G\cong 15k\Omega$ ) 15 mV, or about 4% referred to the input. For 1% error, RTI, the output error is 4.3mV, corresponding to a maximum  $I_2$  of 290nA, for this circuit.

Because the properties of current sources may be affected by voltage, it is important, in such circuits as Figure 1, to ensure that the "compliance voltage" of the current inputs is greater than  $V_A$ , and that  $V_A$  does not seriously affect the parameters of the current source.

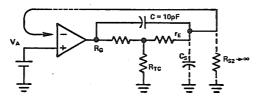

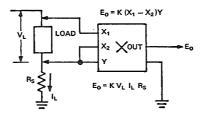

#### RESPONSE AND STABILITY

Since the transistors are connected as diodes, D2 is a passive feedback element, with a resistance =  $r_E \approx (40I_2)^{-1}$ . The 10pF feedback capacitance should be quite adequate to compensate for input strays (Figure 3).

Figure 3. Dynamic model of log-ratio circuit

The effective net resistance of the feedback divider (output to summing point) is

$$R_{eff} = R_G + r_E \left( 1 + \frac{R_G}{R_{TC}} \right) \cong R_G + \frac{16}{40I_2}$$

(9)

For this circuit, because of the accuracy requirement implied by (8),  $I_2$  is likely to be less than  $1\mu A$ , hence  $R_{eff} \cong (2.5I_2)^{-1}$ , and the small-signal time-constant,  $R_{eff}C = C/(2.5I_2)$ . For example, if C = 10 pF and we are considering small-signal variations of  $I_2$  in the neighborhood of 100 nA,  $\tau = 40 \mu s$ ,  $\omega = 25 kr/s \rightarrow 4 kHz$ .

For small changes in  $I_1$ , which may be considered to be changes in  $V_A/r_E$  ( $I_{s\,2}$  fixed and having negligible admittance), the output will immediately change by  $V_A$  (1 +  $C_s/C$ ), then continue on to the final value with the same exponential time-constant as discussed above.

For transdiode applications, if feedback to the amplifier's positive input can be considered negligible, the stability considerations are quite similar to those discussed in Chapter 3-1 (Equations 10 to 16 and Figures 5, 6, and 7 are quite relevant). For stability explorations, the open-loop gain of the amplifier may be considered to be reduced by  $(1 + R_G/R_{TC})$ , thus lowering its Bodé plot by 20 log 16 = 24.1 dB, and  $R_E$  is, in effect, the parallel combination of  $R_G$  and  $R_{TC} \cong 940\Omega$ .

#### APPLICATION CONSIDERATIONS

Thus far, there have been a number of tacit assumptions: that the diode-connected log elements are matched and are isothermal with each other and with the compensation resistors, that the diodes operate in the range for which  $h_{\rm F\,E}$  is sufficiently large and the bulk resistance sufficiently small to cause negligible errors, and that the amplifier's offset voltage, bias current, and common-mode errors are negligible. We shall now look more closely at the amplifier requirements, at various elements of log-ratio-circuit performance specifications, and at a number of alternatives to the circuit of Figure 1.

### CHOOSING THE OP AMP

In low-current operation, the time constants involved are significantly longer than amplifier time constants and preclude the possibility of operation at high frequency. The bandwidth restrictions on the choice of op amp are therefore minimal, unless log operation is confined to high current levels.

Bias current is the primary specification for all log applications involving current-input signals. The op amp's bias current is added to the input signal (±) and flows through the log element. Errors can be stated directly as percentage of input.

% error RTI due to

$$I_{BIAS} = 100\% (I_b/I_s)$$

(10)

For log voltage ratio applications, the input signal is converted to a current by the input resistor. The resulting current should be the value of  $I_s$  that is compared with  $I_b$  in (10).

Offset voltage is of little importance in log current-ratio applications if the current signals are "true current sources." The effect of offset voltage  $(E_{0.5})$  for either current or voltage applications is

% error RTI due to

$$E_{os} = 100\% (E_{os}/V_s)$$

(11)

For voltage applications,  $V_s$  is the voltage signal to be logged. For current applications,  $V_s$  is the equivalent open-circuit voltage source corresponding to  $I_sR_s$ . If  $E_{os}$  is not very much smaller than the smallest value of  $V_s$  for which a stated accuracy level is desired, it can be a significant source of error and should be trimmed to zero. (Also, in such applications, the amplifier should be chosen for low thermal drift, as noted below.)

Offset-voltage drift is important for those applications in which the current input is not provided by an ideal current source. To determine the required amplifier-offset specification, the temperature range, the allowable % error over the temperature range, and the lowest voltage for which that % error must be maintained are decided upon. The maximum allowable amplifier offset temperature-coefficient is

$$E_{os}T.C. = \frac{V_{min} \delta_{max}}{\Delta T 100}$$

(12)

where V<sub>min</sub> is the lowest input voltage

$\delta_{max}\,$  is the largest allowable % error at  $V_{min}$

$\Delta T$  is the change of temperature from the temperature at which  $E_{o\,s}$  was trimmed to zero.

For example, an input range of 10mV to 10V is to be applied to one terminal of a log-ratio device (assuming that the common-mode voltage is zero), and it is necessary the  $E_{os}$  contribute no more than 1% error over the range  $20^{\circ}\text{C}$  to  $40^{\circ}\text{C}$ .  $E_{os}$  might be

trimmed to zero at mid-range (30°C). Then the required offset temperature coefficient would be

$$E_{os}T.C. = \frac{0.01 \times 1}{\pm 10^{\circ} \times 100} = 10 \mu V/^{\circ}C$$

(13)

The same procedure would be followed to determine  $I_{\rm b}$  and  $E_{\rm os}$  requirements for the second input terminal.

Output-current rating, as with all op amp circuits, would be selected for the capability of supplying the maximum requirements of the load, in addition to the requirements of the feedback circuitry (usually negligible).

#### OTHER CONSIDERATIONS

Dynamic Range: The dynamic range of the circuitry used in a given application is determined by the logarithmic resolution of the device used as a log element, the dynamic range of the input signal, restrictions caused by characteristics of the specific circuit configuration and the devices used in it, and the desired accuracy level. A typical basic log element, such as Model 751N, can be used over a range of 100pA to 1mA with less than 2% error; over limited ranges, better accuracy can be obtained. For the circuit of Figure 1, dynamic range was limited primarily by the common-mode range for voltage sources and source resistance for current sources, at the low end, and by  $I_2R_G$  at the high end. Moresophisticated circuits are available, as will be shown in a later section, in which the characteristics of the log element are the primary limit to the dynamic range, assuming proper op-amp selection and care in circuiting.

Polarity of the Input Signal and of the Log Device: All log elements are restricted to inputs of a single polarity (but the outputs can be bipolar, with zero occurring at unity current ratio). By definition of the logarithm, the log of zero and the log of a negative number do not have real values. This means that for a given design, the input currents must both be of the same polarity, and of such polarity that the diodes are conducting in the forward direction, i.e., the most favorable direction for log behavior. Of course, input signals may be conditioned in preceding stages,

except in the case of extremely low currents, for which immediate conversion may be desirable.

If a transistor is diode-connected, either an N (NPN) or P (PNP) log element may be used, since the transistor is connected as a reversible two-terminal device. (In such cases, direct input currents of either polarity may be applied, and properly dealt-with in post-conversion conditioning.) In general, log-transistor connections (transdiode and follower) are not reversible, and polarity must be specified as "P" type for applications requiring PNP transistors (751P) and "N" type (751N) for applications requiring NPN transistors.

Temperature Range: Nearly all of today's commercially-available logarithmic modules, whether basic log elements, log transconductors, log amplifiers, or log-ratio modules, are temperature-compensated. Specially selected resistors ( $R_{TC}$  in the circuits discussed above), having resistance that increases predictably with temperature, are used to reduce the temperature-dependence of the log equation, (kT/q) ln (ratio), from 0.3%/°C to 0.04%/°C. Although this is an order-of-magnitude reduction of error, there can still be considerable contribution of scale-factor error if large temperature excursions are to be encountered. The offset voltage and bias current of op amps can also contribute significant error over wide temperature ranges. Of concern for measurements at very low currents, high temperatures may increase  $I_{ES}$  by several orders of magnitude; though the log transistors may still track, their log-conformity errors will be considerably increased.

For these reasons, the user of log devices who seeks high-accuracy wide-range operation is urged to limit ambient temperature variations to the vicinity of  $\pm 10^{\circ}$ C. An analysis illustrating the effects of temperature in a typical application, involving the voltage/current log module Model 756, is given at the end of this chapter.

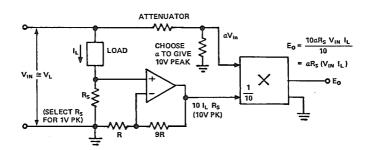

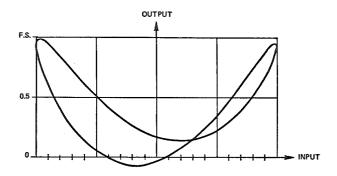

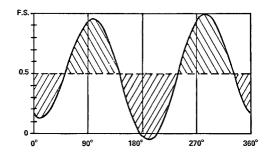

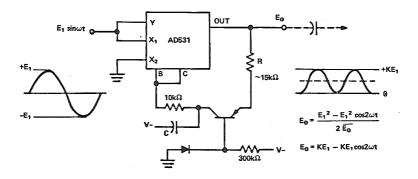

Output Polarity: The output voltage of the log-ratio circuit can be either positive, negative, or bipolar, depending on the ratio  $I_1/I_2$ , and whether or not offsets are added at the output. Figure 4 shows the output as a function of the ratio of input currents for

two different scale factors. For any given application, only a portion of the entire 14-decade (potential) range would be used. By determining the range of expected input signals and computing their ratios, one can use Figure 4 to predict the expected output-voltage range.  $I_1$  and  $I_2$  may be assigned arbitrarily, to match device performance to current range, but polarity should be observed.

Figure 4. Output of ideal log-ratio circuit vs. input ratio, showing effect of exchanging numerator and denominator

If for any reason\* it is necessary to change the effective input scaling, so that the zero-output point occurs at a ratio other than unity, but the input signals themselves are unavailable for scaling, the output can be offset by applying a current to the junction of  $R_{\rm G}$  and  $R_{\rm TC}$ , as shown in Figure 5. As noted earlier (Chapter 4-1), the voltage at this point  $(V_{\rm B})$  is determined by the <code>inputs</code>. Therefore, any current added must flow through  $R_{\rm G}$ , offsetting the output by  $I_{\rm B}R_{\rm G}$ .

Since  $V_B$  is a function of the input ratio (60mV per decadechange), the offsetting current source in Figure 5 should have high-enough source impedance to be unaffected by variations of  $V_B$ .

<sup>\*</sup>Examples include: locating 0 at the middle or extremities of the range, and measuring deviations of equipment from a fixed gain or attenuation, e.g., determining by how many "dB", an actual gain differs from a nominal gain of 100X.

Figure 5. Offsetting the output to shift the zero output (unity ratio) coordinate. The output shift,  $\triangle E_0$ , corresponds to the input ratio multiple  $\triangle \rho$  (K = 1.0).

If the signal is to be processed beyond the log-ratio amplifier, it may be better and easier to simply add a constant voltage or current at an op-amp summing junction in a succeeding stage.

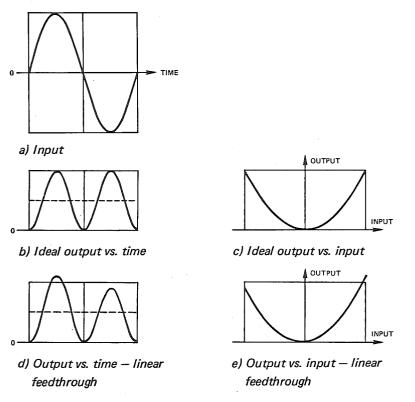

Log Conformity is the specification of logarithmic devices that is akin to linearity in linear devices. Log-conformity error is the difference between the theoretical value of the logarithm of a ratio and the actual value that appears at the output of a log-ratio circuit after initial zeroing at unity-ratio, and scale-factor adjustment (either by end-point or best-straight-line\* method).

Log conformity is basically limited by degradation of transistor gain at low current levels and by base-spreading resistance at high current levels. The form of connection affects the gain at low current levels; for example, diode-connected log transistors have a useful log range that is limited to about 1nA at the low end. If the log devices are used as transistors ("transdiode") rather than as diodes (base and collector tied together), additional decades of performance are available at the low end.

Base-spreading resistance, for log transistors, is a small resistance of a few ohms that appears in series with the emitter. For an emitter current of 1mA and 1 $\Omega$  of series resistance, an error of 1mV will be obtained. The feedback attenuator will cause it to be magnified by  $(1 + R_G/R_{TC})$  at the output. For 1V/decade operation, a 16mV error will be obtained for every ohm of

<sup>\*</sup>But "best straight line" implies the ability to measure log conformity a priori. Although "best straight line," usually specified, gives a 2X tighter specification, "end point" is easier to measure, since it is more easily located

base-spreading resistance. Referred to the input ratio, this is an error approaching  $4\%/\Omega$ . This source of error can be reduced to a satisfactory level with most of the transistor types used for log operations by restricting input signals to about  $100\mu$ A maximum.

Log Voltage-Ratio: Much that has been said about log currentratio is also pertinent to log voltage-ratio as well. The only additional consideration for voltage applications is the means of converting voltage to the current needed by the log element. If the summing junctions of input amplifiers are available, the problem is trivial, for all that is required is to attach a resistor from the voltage source to the summing junction.

The input current I<sub>IN</sub> is then

$$I_{IN} = \frac{V_{IN} - E_{os}}{R_{IN}} \tag{14}$$

The initial amplifier  $E_{os}$  should be trimmed to zero, and the amplifier chosen should have low  $E_{os}$  drift over the temperature range of concern.

As noted earlier, there are a number of circuit configurations that do not permit voltage to be easily and accurately converted to a current. These configurations are referred to as log current-ratio designs. Fortunately, many of the natural phenomena, for which log-ratio measurements are desired, are measured by transducers that provide current outputs. It is important that the designer assure himself that such transducers have sufficient "compliance voltage" to behave as ideal current sources in the presence of voltages of the order of 0.6-0.7V ( $V_A$  in Figure 1).

### **EXAMPLES OF LOG-RATIO CONFIGURATIONS**

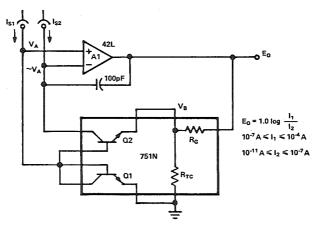

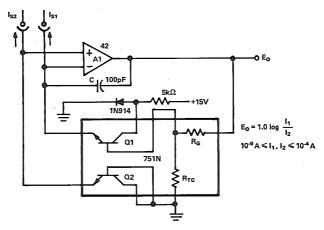

The circuit of Figure 6 is similar to that of Figure 1, but Q2 is connected as a "transdiode" rather than as a diode, extending its range at the low end. Currents from a few picoamperes to about  $0.3\mu\text{A}$  may be converted with good accuracy.

Since  $I_{s1}$  must furnish the base current for Q2, while maintaining the base voltage at  $V_A$ , the range of  $I_{s1}$  is restricted at the low

end. For example, if  $h_{FE2} = 150$  at  $I_{s2} = 0.3\mu A$ , then  $I_{s1}$  must furnish 2nA of base current to Q2. Even if this is the maximum base current that must be supplied, over the expected range of  $I_{s2}$ , it is evident that  $I_{s1}$  must always be greater than 400nA to ensure that the contribution of this source of error will be less than 0.5%.

Figure 6. Modification of the circuit of Figure 1 to extend the range of  $I_{S2}$  at the low end

The amplifier is of the Model 42 family, with bias current considerably less than the smallest signal to be processed.

Even though the dynamic range of  $I_{s2}$  has been increased at the low end, the restriction on  $I_{s2}$  for currents higher than  $0.3\mu A$  still persists, because of the error caused by the flow of  $I_2$  through  $R_G$ .

If a follower-connected op amp is used to unload  $V_A$  and drive the base of Q2, the current swing of  $I_{s1}$  at the low end can be greatly extended.