# SECTION IX NON-LINEAR CIRCUIT APPLICATIONS

- Introduction to Dynamic Range Compression

- Voltage Controlled Amplifiers (VCAs):

Structures, Using Analog Multipliers

to Build VCAs, The X-Amp, AD600,

AD602 Applications

- Logarithmic Amplifiers:

Classifications, Scaling, Translinear

Log Amps, Progressive-Compression

Log Amps, The AD640 Log Amp,

Log Amps Based on Bipolar

Differential Stages

- Using the AD834 in DC to 500MHz

Applications: RMS-to-DC Conversion,

Voltage-Controlled Amplifiers, and Video

Switches

- Video VCAs and Keyers Using the AD834 and AD811

AMPLIFIER APPLICATIONS GUIDE

### **SECTION IX**

# NON-LINEAR CIRCUIT APPLICATIONS Barrie Gilbert, Bob Clarke

#### 9.1 Introduction To Dynamic Range Compression

In real-world signal-processing systems the signal of interest often exhibits a wide range of amplitudes. Familiar examples are: radio and radar receivers, where the dynamic range of an electromagnetic signal may be as high as 120 dB; analytical instruments such as gas chromatographs, where the output current of a photodetector may vary from picoamps to milliamps; sonar and ultrasound systems, where the attenuation of an acoustic signal varies rapidly with the path length; and so on. In terms of the signal voltage,

where *lgt* here, and throughout this section, means  $log_{10}$ , or "logarithm to base 10". Note that in a *linear-impedance* system, power is proportional to the voltage (or current) squared. Therefore, a 10,000:1 *voltage* ratio – that is, an 80 dB dynamic range – corresponds to a 100,000,000:1 *power* ratio. Accordingly:

Dynamic range (dB) =

$$10 lgt$$

Largest signal power

Smallest signal power

We have chosen to use voltage ratios throughout this section because the majority of signal-processing circuits respond to purely voltage-mode signals, and occasionally operate on purely current-mode signals. Of course, at any branch in a real circuit there are both voltage- and current-mode components of the signal, hence finite power. On the other hand, the miniscule power "consumed" at the gate input of an MOS amplifier is not a very good indicator of the available dynamic range. This is because the voltage noise at this node of the circuit might be quite high, from microvolts to millivolts depending on the noise bandwidth and allowing for the possibility of 1/f noise, while the largest signal voltage might only be a volt or two. Power ratios are more useful in fixed-impedance systems, such as RF amplifiers operating between a resistively-matched source and load, usually  $50~\Omega$ .

At this point, we should differentiate between the dynamic range of the *signal* and that of the processing *system*:

#### AMPLIFIER APPLICATIONS GUIDE

| Signal dynamic range (dB) = 20 lgt | Largest actual signal voltage      |

|------------------------------------|------------------------------------|

|                                    | Smallest actual signal voltage     |

| System dynamic range (dB) = 20 lgt | Largest permissible signal voltage |

|                                    | Smallest detectable signal voltage |

We are solely concerned in this Section with the *system* dynamic range, in particular, with methods for maximizing this range, preferably matching or somewhat exceeding that of the signal. We will present the theoretical foundations as well as fully-tested practical circuits for dealing with many commonly-encountered situations in which signals of unusually wide dynamic range must be compressed to a more manageable level.

In dealing with such signals the need invariably arises for amplifiers which, on the one hand, can provide high gain with low noise levels when the signal is weak, in order to drive high-level processing circuits (such as A/D converters) while, on the other hand, being able to cope with large signals with minimum degradation. This Section also provides guidelines in the selection of suitable amplifiers for use in wide dynamic range systems.

### DYNAMIC RANGE DEFINITIONS

| Dynamic range (dB) = 20 lgt               | Large                | st signal voltage                  |

|-------------------------------------------|----------------------|------------------------------------|

|                                           | Small                | est signal voltage                 |

| Dynamic range (dB) = $10 lgt$ -           | Largest signal power |                                    |

|                                           | Small                | est signal power                   |

| Signal dynamic range (dB) = 20 lgt        |                      | Largest actual signal voltage      |

|                                           |                      | Smallest actual signal voltage     |

| System dynamic range (dB) = 20 <i>lgt</i> |                      | Largest permissible signal voltage |

|                                           |                      | Smallest detectable signal voltage |

Figure 9.1.1

#### 9.1.1 NOISE LIMITATIONS

The dynamic range of all signal-processing systems is limited by random noise, which sets a fundamental bound on the smallest signal that can be detected or otherwise utilized with adequate signal-to-noise ratio (SNR). This noise may be generated by numerous mechanisms, including those associated with the source itself (e.g., antenna, photomultiplier, piezoelectric transducer, etc.) as well as by the active and passive devices in the amplifier.

Noise cannot be discussed without reference to bandwidth, which will be unavoidably limited by the type of amplifier(s) used. Deliberate filtering is often included in a signal-processing channel to reduce noise, as well as to improve the separation of wanted from unwanted signals. This may take the form of band-pass, low-pass or high-pass functions, or combinations of these, depending on the situation. Nonlinear filtering may also be used, for example, in order to minimize the disturbance of the signal path in the presence of impulsive noise. In some case, adaptive filtering is effective: a "lock-in amplifier" seeks a periodic (and often extremely weak) component in a noisy signal and automatically tunes a narrow-band filter to track its frequency (Reference 9.1.1). A key element of such a system is a synchronous detector.

The noise powers of uncorrelated sources add, so noise voltages (or currents) must be added using a root-sum-of-squares (RSS) calculation. This leads to some rather startling consequences. Suppose a system has a major voltage noise source of magnitude  $E_a$  and several minor noise sources which RSS sum to a magnitude of  $E_b$ . Then, for the major source to contribute almost 90 % of the total system noise,  $E_a$  needs to be only twice  $E_b$ . When  $E_a/E_b = 5$ , fully 98 % of the noise is due to  $E_a$ .

It follows that the overall noise performance of a practical system can benefit greatly by (1) minimizing the input-referred noise of the first stage and (2) using the highest possible gain in this stage. However, the second of these objectives is frequently unrealizable in systems that must handle signals of large dynamic range, because the high gain would then preclude distortion-free operation at maximum signal levels.

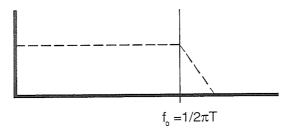

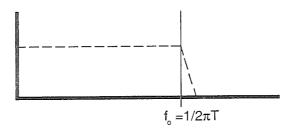

Noise is frequently specified in terms of "noise spectral density", or NSD. This term reflects the fact that the total noise power is directly proportional to the system's noise bandwidth,  $B_N$  (in Hertz). The NSD is therefore usually of interest in specifying a channel's *input-noise* limitations. Note that the noise bandwidth is not, in general, equal to the –3dB bandwidth.  $B_N$  can be viewed as the bandwidth of an equivalent system with a "brick-wall" cessation of response at that frequency. A system with a single-pole low-pass corner at  $f_0 = 1/2\pi T$  has a  $B_N$  equal to  $\pi f_0/2$ , or 1.57 $f_0$ , while for two such real-pole low-pass sections in cascade  $B_N$  is  $\pi f_0/4$ . (See Figure 9.1.2).

### FILTER NOISE BANDWIDTHS

Single-Pole Low-Pass Filter:  $B_N = \pi f/2 = 1.57 f_o$

Two Single-Pole Low-Pass Filter sections in cascade:  $B_N = \pi f/4 = 0.785 f_o$

Figure 9.1.2

The total NSD will have both voltage- and current-components. We will use the symbol SE to refer to the *voltage* noise spectral density and the symbol SI to refer to the *current* noise spectral density. Since the noise power is proportional to the square of either the voltage or current, SE and SI have the dimensions of Volts per Root-Hertz and Amps per Root-Hertz, respectively. Noise signals are usually small, and therefore nonlinear effects are often negligible; in such circumstances, it is permissible to use superposition methods to evaluate each contributing source independently, followed by an RSS calculation to calculate the total noise. A notable exception is the logarithmic amplifier, where even very small noise voltages at the input can cause later stages in the amplifier to be in heavy limiting. Special approaches to both noise analysis and noise specification are required in such cases.

#### 9.1.1.1 NOISE GENERATORS

We will only briefly review some of the most basic aspects of noise generation. The topic is well-covered in many fine standard texts; see, for example, Reference 9.1.2. The thermal (Johnson) noise voltage of an ideal resistor has an open-circuit magnitude of

$$S_E = (4kTR)^{0.5}$$

Eq. 9.1.1

where T is the absolute temperature in Kelvins, k is Boltzmann's constant (1.38 X  $10^{-23}$  Joules/Kelvin) and R is the resistance in Ohms. This evaluates to 0.129 nV/ $\sqrt{\text{Hz}}$  per root-ohm at

a temperature of 300 K (about 27 °C). We will refer to this constant as the standard temperature ohm-normalized noise-spectral density, and assign it the symbol  $S_{\Omega}$ .

## A 100 $\Omega$ resistor generates $10S\Omega$ or 1.29 nV/ $\sqrt{\text{Hz}}$ at T = 300 K.

It is sometimes more useful to consider the resistor to be noise-free and then represent the noise as an equivalent current-source in shunt with it; of course, this has the same value as the short-circuit current-noise,  $S_I = (4kT/R)^{0.5}$ .

Some real resistors exhibit excess noise, which is a function of the current flowing in the resistor. This occurs whenever there are grain boundaries in the resistive material. Monolithic diffused and thin-film resistors do not have significant excess noise. The contact-related artifacts which were troublesome in thin-film resistors many years ago are nowadays eliminated through the use of one or more intermediate conductive layers.

The incremental channel resistance of a junction-FET or strongly-inverted MOS transistor behaves as a simple ohmic resistance, as far as noise is concerned, but has a value of 3/2gm. The transconductance, gm, is proportional to the width-to-length (W/L) ratio of the channel and the channel current ( $I_{DS}$ ). Low-noise MOS stages demand the use of large interdigitated devices (large W) operating at high values of  $I_{DS}$ . Field-effect transistors, and in particular, MOS types, suffer from significant amounts of flicker noise. This noise increases with decreasing frequency, f, roughly with a  $1/f^{\alpha}$  form, where  $\alpha$  is often taken to be unity; thus, it is called "1/f noise". The topic is complex and even controversial (see, for example, Reference 9.1.3). However, as a guideline, 1/f noise can only be reduced by increasing the channel area, WL.

The base-emitter voltage,  $V_{BE}$ , of an ideal bipolar junction transistor (BJT) operating at a constant collector current  $I_{C}$  is not noise-free. There is unavoidable "granularity" in this current, expressed as the shot noise, which has a current noise spectral density of

$$S_{\rm I} = (2qI_{\rm c})^{0.5}$$

Eq. 9.1.2

This noise current operates on the transistor's (noiseless) incremental emitter resistance

$$re = kT/qI_c$$

Eq. 9.1.3

to generate a voltage-noise spectral density of

$$S_E = (2qI_c)^{0.5} kT/qI_c$$

=  $kT (2/q)^{0.5} (1/I_c)^{0.5}$  Eq. 9.1.4

The shot-noise-induced voltage which effective appears in series with base-emitter path is thus inversely proportional to the square-root of the collector current and totally independent of the transistor geometry or process technology.

The VBE noise for a BJT is 0.476 nV/ $\sqrt{\text{Hz}}$  per root-milliamp of Ic at T = 300 K.

It is interesting to note in passing that this noise is  $\sqrt{2}$  times *smaller* than the noise in a real resistance of the same value as re.

## NOISE GENERATORS

$$S_E = (4kTR)^{0.5}$$

Eq. 9.1.1

A 100  $\Omega$  resistor generates 10S $_{\Omega}$  or 1.29 nV/ $\sqrt{Hz}$  at T = 300 K.

$$S_1 = (2qlc)^{0.5}$$

Eq. 9.1.2

$re = kT/qlc$  Eq. 9.1.3

$S_E = (2qlc)^{0.5} kT/qlc$  Eq. 9.1.4

$= kT (2/q)^{0.5} (1/lc)^{0.5}$

The  $V_{BE}$  noise for a BJT is 0.476 nV/ $\sqrt{Hz}$  per root-milliamp of IC at T = 300 K.

$$R_N = \frac{S_E^2}{4kT}$$

Eq. 9.1.5

Figure 9.1.3

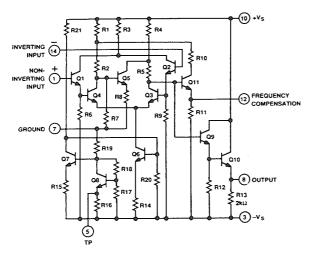

## 9.1.1.2 NOISE OF TYPICAL INPUTS STAGES

When dealing with signal sources which have relatively low resistance, the input stage should be chosen to exhibit a low value of SE. After all the noise generators have been RSS-added, the resulting SE can be expressed as an equivalent noise resistance

$$R_{N} = \frac{S_{E}^{2}}{4kT}$$

Eq. 9.1.5

An input-noise resistance of one quarter that of the source would contribute only 10% of the total noise. For bipolar input stages, the dominant noise-voltage generator is typically the base resistance, rbb'. The channel resistances of field-effect transistors used in input stages exhibit the same noise behavior as simple resistors.

#### 9.1.1.3 PRACTICAL AMPLIFIER NOISE SPECIFICATIONS

We can define the absolute lower limit of the system's dynamic range as simply being equal to its noise referred to the input, when driven from some specified source impedance, and in a specified bandwidth. This is commonly referred to as the "noise floor". A signal of the same magnitude presented to the input would result in a SNR of 0 dB, by definition. While this clearly represents the fundamental lower limit on the system dynamic range, it may be more meaningful to specify this limit in terms of some acceptable SNR, say, 20 dB. In analog channels handling digital data, this limit may be specified in terms of the maximum allowable bit-error-rate (BER).

In low-frequency applications, it is customary to specify the noise at the input of an amplifier in terms of separate voltage and noise components. The voltage noise spectral density is that noise which appears to be present at the input when this input is short-circuited. The best of contemporary op-amps exhibit values of the order of 1 to  $5nV/\sqrt{Hz}$ . The bipolar-input AD797, optimized for this specification, has an NSD of  $0.9~nV/\sqrt{Hz}$ . The generic workhorse "741", on the other hand, has a typical NSD of  $15nV/\sqrt{Hz}$  due to the use of a four-transistor input stage operating at only  $\sim 10\mu A$ . As previously noted, there is a fundamental limit to what can be achieved at any given bias level. It is quite unrealistic to expect a micropower amplifier to have a low voltage-NSD. An ideal bipolar differential pair operating at a 1  $\mu A$  cannot have a NSD lower than 30  $nV/\sqrt{Hz}$  at room temperature.

In high-frequency circuits, it is common to specify the *noise-figure* of amplifiers. Noise Figure (NF) is often computed using the formula

NF = 10

$$lgt = \frac{e_n^2 + I_n^2 R_s^2 + 4kTR_s B_N}{4kTR_s B_N}$$

Eq. 9.1.6

In the formula,  $e_n$  is the voltage noise,  $I_n$  is the current noise,  $B_N$  is the bandwidth in Hz, T is the absolute temperature in Kelvins, k is Boltzmann's constant (1.38 X 10<sup>-23</sup> Joules/Kelvin) and Rs is the source resistance in Ohms.

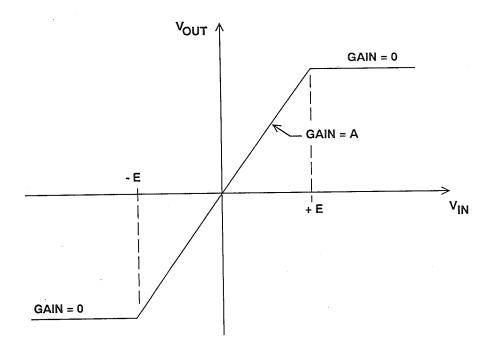

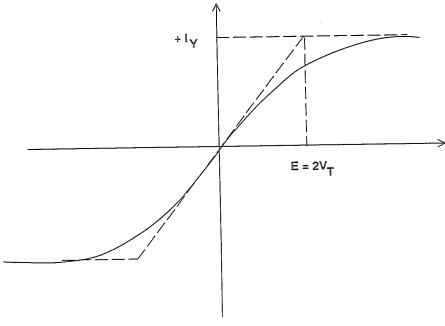

### 9.1.2 DYNAMIC-RANGE LIMITATIONS

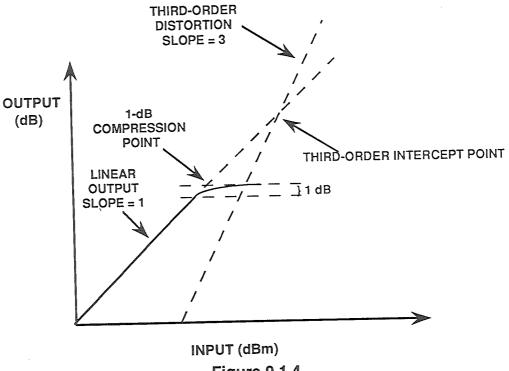

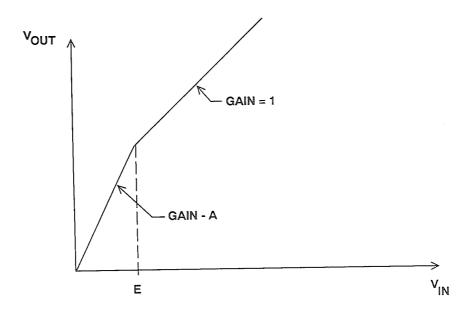

While noise limits the lower end of a system's dynamic range, performance at the upper end of the signal range is always degraded by the increasing importance of nonlinear aspects of circuit behavior. Thus, one way to specify the upper limit to the system's dynamic range is by determining the magnitude of the signal at which the total harmonic distortion reaches some maximum acceptable level, say 1 %. Alternatively, it may be specified as that signal level which causes the system's incremental gain to fall by 1 dB; this is called the I dB compression point as shown in Figure 9.1.4.

## THIRD ORDER INTERCEPT AND 1dB COMPRESSION POINT

Figure 9.1.4

The term "spurious-free dynamic range", sometimes used in this context, is a little misleading because of course the distortion of any real amplifier is always finite, and a continuous function of signal level. In systems involving frequency-translation using mixers, distortion generates spurious signal components in the intermediate (IF) output spectrum, which are usually troublesome. The term third-order intercept is often used to specify the signal-handling capacity of the mixer; this can be defined as the extrapolated single-tone input level which would generate equal fundamental and third-harmonic outputs.

In some cases (such as the gas chromatograph) it may be more appropriate to characterize the entire dynamic range in "DC" terms, limited at the low end by such things as finite offset and input bias current of the input stage, and at the upper end by the onset of unacceptable nonlinearity or even clipping. In other words, the dynamic range in these cases is that range over which the measurement accuracy is held to within defined limits (for example,  $\pm 1$  % of

reading). In such cases, flicker noise (both voltage and current), which dominates the performance of many such low-bandwidth systems, may impose a serious limitation on the available dynamic range.

From these considerations, it will be apparent that the precise method for defining the "dynamic range" of a given system clearly depends on the nature of the signal and the type of processing invoked. No single standard can be applied to adequately define the dynamic range of all systems. In fact, the central challenge of the design of a signal-processing system is ultimately that of optimizing each section so as to recover the maximum possible information (in digital systems, to achieve the lowest possible bit-error rate).

#### 9.1.3 SIGNAL COMPRESSION

In some cases, a wide dynamic range is an essential aspect of the signal, something to be preserved at all costs. This is true, for example, in the high-quality reproduction of music. However, it is often necessary to compress the signal down to a smaller range without any significant loss of information. Compression is often used in magnetic recording, where the upper end of the dynamic range is limited by tape saturation and the lower end by the granularity of the medium. In professional noise-reduction systems, compression is "undone" by precisely-matched nonlinear expansion during reproduction. Similar techniques are often used in conveying speech over noisy channels, where the performance is more likely to be measured in terms of word-intelligibility than audio fidelity. The reciprocal processes of compressing and expanding are implemented using "compandors"; many schemes have been devised to achieve this function.

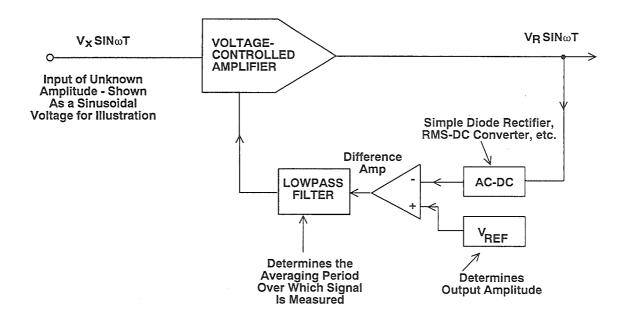

In radio systems, the received energy exhibits a large dynamic range due to the variability of the propagation path, requiring dynamic-range compression in the receiver. In this case, the wanted information is in the modulation envelope (whatever the modulation mode), not in the absolute magnitude of the carrier. For example, a 1 MHz carrier modulated at 1 kHz to a 30 % modulation depth would convey the same information whether the received carrier level is at 0 dBm or -120 dBm. Some type of automatic gain control (AGC) in the receiver is invariably utilized to restore the carrier amplitude to some normalized reference level in the presence of large input fluctuations. AGC circuits are dynamic-range compressors which respond to some metric of the signal – often its mean amplitude – acquired over an interval corresponding to many periods of the carrier. Consequently, they require time to adjust to variations in received signal level. The time required to respond to a sudden increase in signal level can be reduced by using peak detection methods, but with some loss of robustness, since impulsive noise can now activate the AGC detection circuits. Nonlinear filtering and the concept of "delayed AGC" can be useful in optimizing an AGC system. Many tradeoffs are found in practice; Figure 9.1.5. shows a basic system.

#### A TYPICAL AGC SYSTEM

Figure 9.1.5

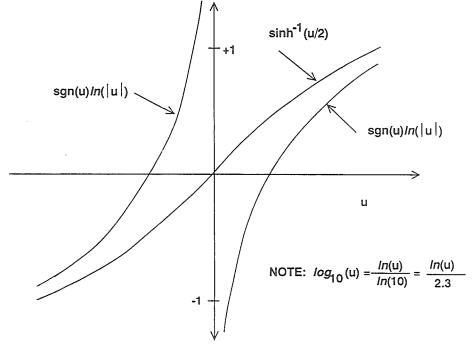

In other cases, the system is required to respond almost instantaneously to the signal. For example, the waveshape of the pulse output of a microwave radar detector must be preserved over many decades of amplitude, which requires that each value of voltage on the input waveform maps uniquely to a value of the output, with essentially the same response for signals of some arbitrarily low frequency (often DC) up to the maximum bandwidth of the channel. The most common mapping functions are the logarithm (or its near-neighbor, the inverse hyperbolic sine) and square-root.

In this section a variety of practical circuit solutions will be presented for compressing signals of large dynamic range. Because of their extensive scope, we will not discuss signal-path filtering techniques, except where they arise incidentally.

#### 9.1.4 LINEAR VS NONLINEAR COMPRESSION

We can divide dynamic range compression systems into "linear" and "nonlinear". In the first category, the gain of the amplifier(s) in the processing chain is independent of the magnitude of the signal but is arranged to vary such a way as to render the output (that is, its peak, mean or RMS value) essentially constant. The harmonic distortion is relatively low.

These systems use what are often called variable-gain amplifiers. While correct, this lacks precision, because *nonlinear* amplifiers (such as log-amps) also exhibit variable gain, but in direct response to the signal magnitude. The term voltage-controlled amplifier (VCA) is preferred in this context; it clearly describes the way in which the gain-control is implemented while allowing latitude in regard to the actual circuit means used to achieve the function. In fact, the gain may be controlled by a *current* within the circuit, but usually by conversion from a voltage at the control interface.

Analog multipliers and dividers are sometimes used as VCAs, but far more optimal circuit topologies are available.

AGC systems use one or more VCAs in conjunction with a level detector and low-pass filter (LPF), usually driven by the output. Occasionally, an analog divider will be used, in which case the input level is extracted and used as the denominator; unlike conventional (feedback) AGC systems, this approach makes use of *feedforward* control.

Any voltage-controlled amplifier may be converted to digital control by the inclusion of a DAC. There are relatively few amplifier products available which provide direct digital control, for reasons explained in the following section.

A special type of VCA is used in "swept-gain" applications. This is an amplifier whose gain is controlled without measurement of the actual signal level; instead, it utilizes the predictable magnitude of the signal as a function of time (or occasionally some other parameter). For example, in medical ultrasound systems the attenuation varies with the depth of the tissue layer being imaged. Similar circumstances arise in sonar and short-range radar.

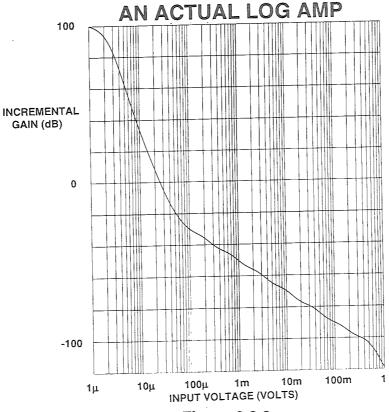

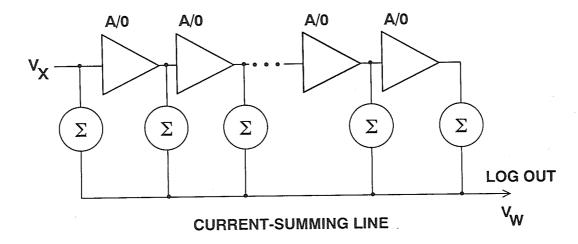

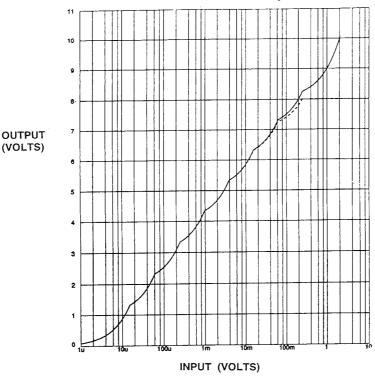

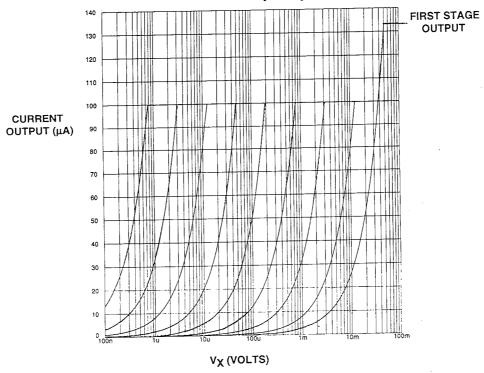

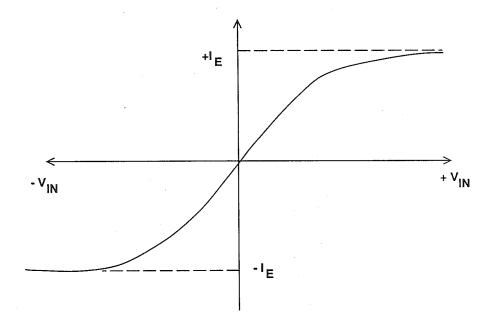

By contrast, nonlinear dynamic-range compression is used in circumstances where low harmonic distortion is not a requirement. Log-amps provide the best example of this type of compression. All types of log-amps produce a low-dynamic-range output without the need to first acquire some measure of the signal amplitude for use in controlling gain. As we shall see later, these can be basically divided into baseband and demodulating types. Baseband log-amps produce an output with minimal time delay and do not employ rectification (that is, signal detection). Demodulating log-amps provide the detection function, and produce a baseband output from a higher-frequency input; filtering is employed on the detected output only to remove the unwanted high-frequency components. In special cases, VCAs of the type used for AGC or swept-gain applications can be used for nonlinear compression; some examples will be presented. In all such cases, an A/D converter of moderate resolution (say, 8 bits) can be made to handle a signal of large dynamic range (say, 16 bits, or 96 dB) while preserving equal incremental resolution over the whole range.

#### AMPLIFIER APPLICATIONS GUIDE

### REFERENCES

- 9.1.1 See, for example, Lock-In Amplifiers: Principles and Applications by M. L. Meade, Peter Peregnius, Ltd., 1983

- 9.1.2 Low Noise Electronic Design by C. D. Motchenbacher and F. C. Fitchen, John Wiley Inc., 1973.

- 9.1.3 The MOS Transistor by Y.P. Tsividis, McGraw-Hill, Inc., 1987.

### 9.2 VOLTAGE CONTROLLED AMPLIFIERS (VCAS)

There are many ways to build voltage-controlled amplifiers. The literature goes back to the earliest days of electronics, amounting to thousands of papers and hundreds of patents. This section will review some of the most important contemporary techniques and show several practical applications.

Such digitally-controlled circuits as software-programmable-gain amplifiers or multiplying D/A converters (MDACs) provide discrete-gain steps. The Analog Devices LOGDAC<sup>TM</sup> AD7111 is a development of the MDAC approach to gain control. This special-purpose CMOS D/A converter emulates an attenuator with a range of 0 to –88.5 dB and resolution of 0.375 dB (a 4.4 % gain change per step) using an 8-bit control input.

Often, much finer gain-control is necessary, which requires the use of a larger control word. This is not of itself a basic problem: if one wished to achieve the above range of 88.5 dB with the resolution increased to 0.086 dB (a 1 % gain change per step), it would require a 10-bit word. However, important practical issues arise. In applications where the dynamic range is wide (88.5 dB corresponds to a voltage ratio of about 27,000:1), it follows that at the low end of the gain-control range the channel must process very small signals.

The complete separation of the digital control inputs from these weak signals is difficult, at both the silicon level and the board level. For example, this problem becomes severe when it is necessary to update the gain quickly – over a period of a few microseconds or less – in which case the feedthrough of rapidly-changing binary data edges ("glitching") becomes intolerable.

Furthermore, the use of MOS switches, such as those found in MDACs and their derivatives, is not conducive to low-noise, wideband design: the Johnson noise of the FET channel resistance can be reduced only by the use of large-geometry devices, and these in turn exhibit significant parasitic capacitances, leading to problems in controlling both the phase and the amplitude of the system response under all conditions, but particularly at high attenuation levels.

Consequently, in applications where (a) the signal to be compressed covers a wide dynamic range, (b) the required accuracy of the AC gain and phase response is high, and (c) the gain must be swept rapidly, digital control techniques are not attractive and in the most critical applications cannot be used at all. In these cases, a voltage-controlled amplifier (VCA) is indispensable.

It must also be remembered that there remain numerous applications where direct analog control is still the preferred approach from other considerations. For instance, it is inconvenient to distribute the control data on a wide digital bus to a large number of parallel signal-processing channels, as in an ultrasound system. It is also simpler to implement AGC systems using VCAs.

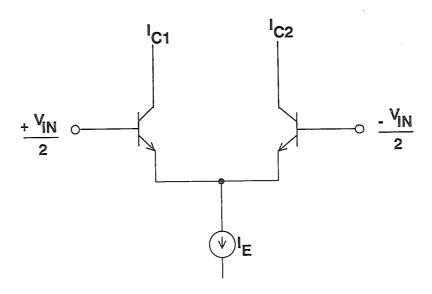

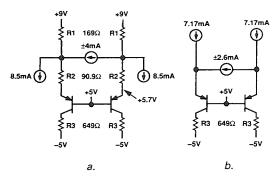

#### 9.2.1 A COMMON VCA STRUCTURE

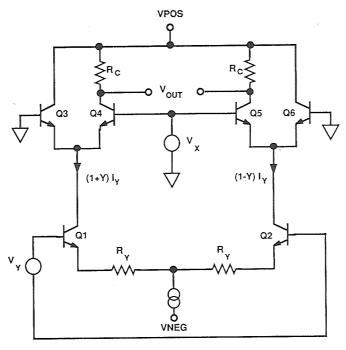

A popular approach to the design of a VCA is to use the reliable exponential relationship between collector current and base-emitter voltage in a bipolar junction transistor, through which means it is possible to achieve a gain-control range of several decades. A very widely-used circuit is shown in Figure 9.2.1. The signal voltage  $V_Y$  is first converted to a complementary pair of currents, which are here denoted as  $(1+Y)I_Y$  and  $(1-Y)I_Y$ , by a voltage-to-current (V/I) converter formed by Q1, Q2 and Ry. The "modulation index" Y has a maximum range of  $\pm 1$ ; in practice, it will have a peak value of about 0.75, to minimize distortion due to the nonlinear  $V_{BE}$  of the transistors. To a good approximation,  $Y = V_Y/I_YR_Y$  (true when  $I_YR_Y \ge 100 \ kT/q$ ).

## A COMMON VARIABLE -GAIN CELL: THE "CONTROLLED CASCODE"

Figure 9.2.1

The signal-plus-bias currents are then applied to a "current-fork", comprising Q3 through Q6, that steers some fraction,  $0 \le X \le 1$ , of the signal currents to the output load resistors, and dumps the remainder to the positive supply. These transistors also act as a cascode stage, which extends the frequency range of the amplifier; because of this feature, we will refer to this cell as a "controlled cascode".

The parameter X is determined by the gain-control voltage V<sub>X</sub>. It is readily shown that

$$X = \frac{exp(V_X/V_T)}{1 + exp(V_X/V_T)}$$

Eq. 9.2.1

where  $V_T$  is the thermal voltage kT/q, which has a value of 25.85 mV at T=300 K (about 27°C). At this temperature, X is 0.99 when  $V_X=120$  mV and 0.01 when  $V_X=-118$  mV. If the

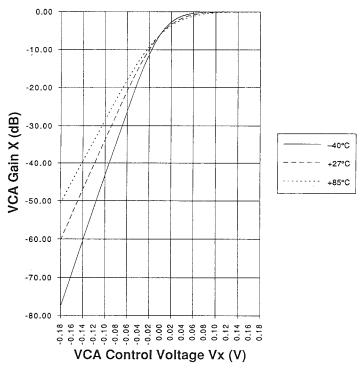

system gain is normalized to 0 dB when X = 1, the loss is 6 dB for  $V_X = 0$ ; Figure 9.2.2 shows the decibel value of gain as a function of  $V_X$  at three temperatures.

# THE DECIBEL GAIN OF THE CONTROLLED CASCODE

Figure 9.2.2

Several potential problems are immediately apparent from this graph. First, the circuit's control function is not "linear in decibels"; it approaches this condition only for very high attenuation. Second, the attenuation is a strong function of temperature; this, and the nonlinear control function, may not matter too much in closed-loop AGC systems, but both would be troublesome in "swept-gain" VCA applications, or in feed-forward AGC systems. The temperature-sensitivity can be addressed using special resistors to form an attenuator between the actual gain-control voltage and the base nodes.

Apart from these obvious weaknesses, this cell has additional problems. Notice that the lower end of the input dynamic range is fundamentally limited by the Johnson noise of Ry. If this resistor is reduced to the point where acceptable noise performance is achieved, the upper end of the dynamic range will also be reduced, due to the onset of distortion, unless very large values of bias current Iy are used.

For example, suppose we wish to achieve a short-circuited input noise spectral density of 1.5 nV/ $\sqrt{\text{Hz}}$  at 300 K (which corresponds to 15  $\mu$ V in a 100 MHz bandwidth) then Ry can be no more than 135  $\Omega$ . This assumes that Q1 and Q2 have no ohmic resistances; in practice, the rbb'

of both transistors must be subtracted from  $R_Y$  to maintain the desired total resistance. Even well-optimized monolithic transistors may have rbb' values of 15  $\Omega$ , typically requiring  $R_Y$  to be 100  $\Omega$ .

Now postulate that a maximum input of 1 V RMS must be handled with a total harmonic distortion of less than -60 dBc. (At moderate frequencies the distortion will be third-order, but there will be increasing odd- and even-order components at high frequencies.) To meet this last requirement when  $R_Y = 100~\Omega$ , it can be shown that the two currents Iy must each be at least 23 mA; using typical  $\pm 5V$  supplies, this would correspond to an expenditure of almost half a watt in just the voltage-to-current converter! Such high power consumption is unwelcome where a very large number of VCAs are used, as in ultrasound imaging applications, and would be intolerable in most battery-operated systems.

So far, we have assumed that the noise due to the second stage is negligible, but that can only be true if the controlled-cascode cell has a maximum voltage gain (when X=1) that is much greater than one. This gain is at most  $2R_C/R_Y$ . Let the noise at the input (due to  $2r_bb' + R_Y$ ) be  $E_a$ , and that in the load circuit (at best, due to  $2R_C$  alone) be  $E_b$ . The total noise at the output,  $E_{no}$ , for the maximum gain condition, where noise performance is critical, is

$$E_{no} = \{ (2R_C/R_Y)^2 E_a^2 + E_b^2 \}^{0.5}$$

Eq. 9.2.2

Referred to the input, this is equivalent to a noise of

$$E_{ni} = \frac{\{(2R_C/R_Y)^2E_a^2 + E_b^2\}^{0.5}}{2R_C/R_Y}$$

Eq. 9.2.3

Noting that  $E_a = S_\Omega (2r_bb' + R_Y)^{0.5}$  and  $E_b = S_\Omega (2R_C)^{0.5}$ , where  $S_\Omega$  is the ohm-normalized noise-spectral density (see Section 9.1.1.1) and setting  $r_bb'=0$  for simplicity and also to show the fundamental limitations more clearly, we can write

$$E_{ni} = S_{\Omega} R_{Y}^{0.5} (1 + R_{Y}/2R_{C})^{0.5}$$

Eq. 9.2.4

The first part of this expression is simply the Johnson noise of  $R_Y$ .  $E_{ni}$  is increased in direct proportion to the second factor, requiring that  $2R_C$  be much greater than  $R_Y$ . When  $R_C = 2$   $R_Y$ , the noise is increased by about 12 % or 1 dB. In our example, therefore, we might use  $R_C = 400\Omega$ . But this raises a practical problem: if a value of  $I_Y = 23$  mA were used to maintain acceptable distortion levels, the maximum voltage drop across the load resistors  $R_C$  would be nearly 15 V at full gain and full signal, requiring an inordinately high supply voltage. Further noise and distortion is generated by the base resistances and capacitances of the cascode transistors. At low gains, HF signal feedthrough occurs via the T-network formed by the  $C_{je}/r_{bb}/C_{jc}$  of these transistors, causing aberrations in the AC response.

In numerous ways this type of VCA fails to meet the exacting requirements of modern systems. Nevertheless, the approach remains appealing where some concessions to noise, distortion and gain-accuracy can be made. It is a simple cell for use in embedded applications, and provides the highest possible bandwidth for a given technology. Variable-gain amplifiers built along these lines are available for use up to about 1 GHz.

#### 9.2.2 USING ANALOG MULTIPLIER/DIVIDERS TO BUILD VCAS

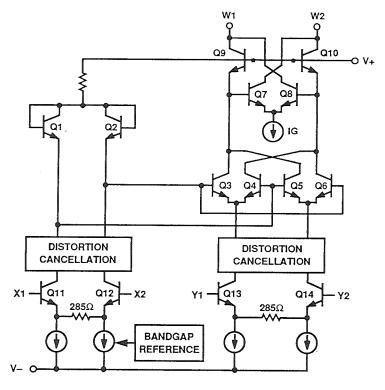

Analog multipliers and dividers can also be used in gain-control applications. These circuits are invariably based on the translinear principle, which exploits the precise proportionality of transconductance to collector current in a bipolar transistor.

Voltage-controlled amplifiers (VCAs) built from analog multipliers take one of two forms. In the first, the multiplier acts as a voltage-controlled attenuator ahead of a fixed-gain amplifier. This type of VCA is used in applications where not only a moderate maximum gain is needed but also a fairly high maximum loss. In the second, the variable attenuation is placed in the feedback path around an op amp, which in fact implements an analog divider. Analog dividers are more suitable for applications requiring high gains.

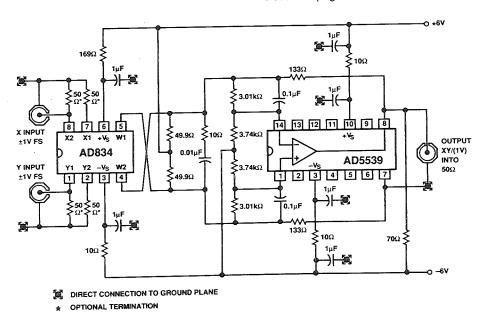

Products available from Analog Devices include the low-cost AD633, the high-accuracy AD734, and the high speed AD834 (useful to 500 MHz). These are four-quadrant multipliers. For gain-control applications, a two-quadrant circuit is more useful, such as the dual-channel AD539, which provides a signal bandwidth of about 60 MHz.

VCAs and multipliers based on the nonlinear properties of transistors inevitably exhibit various types of spurious nonlinearity, caused by non-ideal aspects of transistor behavior and the necessity for "open-loop" design. Nevertheless, with care in design and the use of distortion-nulling laser-trimming techniques in manufacturing, exceptionally low levels can be achieved. For example, the AD734 Multiplier/Divider exhibits nonlinearities of only 0.02 % from either the X- or Y-input, and provides a gain-bandwidth product of 200 MHz in its two-quadrant divider mode, implemented by direct control of the denominator voltage (rather than by putting a multiplier in a feedback path) over a 1000:1 range (10 mV to 10V).

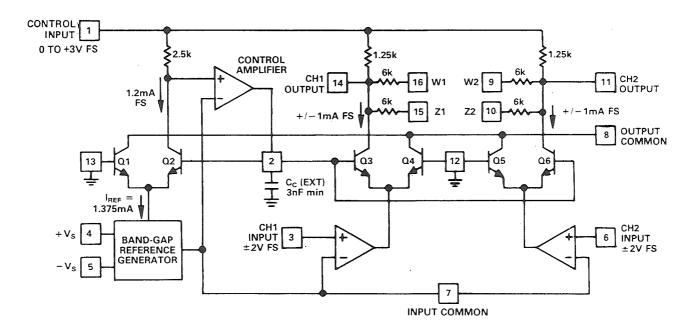

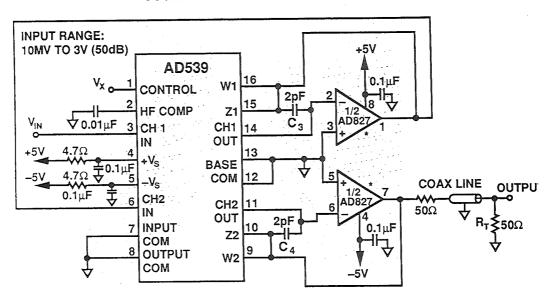

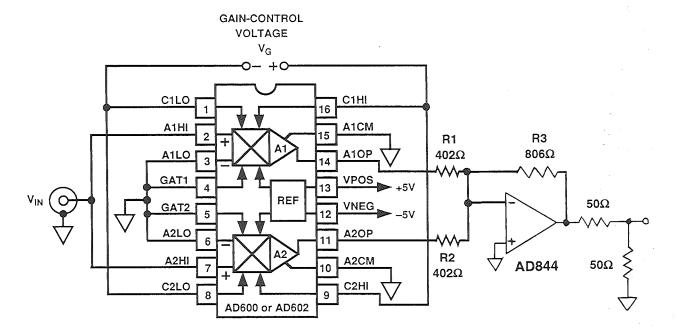

Many practical circuits can be built using multipliers. We begin with a discussion of the AD539 and its use in conjunction with such transimpedance amplifiers as the AD844, because the AD539's basic structure is similar to that of the cell described in the last section, but the means have been included to provide accurate *linear* gain control, rather than the roughly-exponential, temperature-dependent gain control function of the basic cell. Figure 9.2.3 shows the essential pieces of the AD539. Note that there are two nominally identical channels whose gains are simultaneously controlled by a common voltage, V<sub>X</sub>. These may be used separately, or in simple parallel to improve bandwidth and noise performance, or in a differential mode with appropriate support circuits.

# SIMPLIFIED SCHEMATIC OF THE AD539 ANALOG MULTIPLIER

Figure 9.2.3

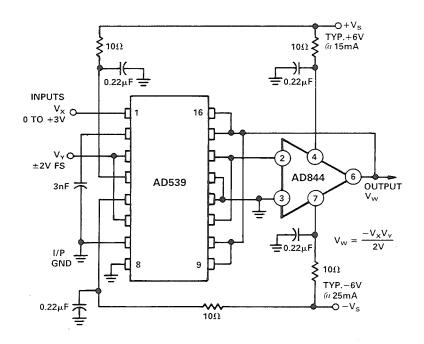

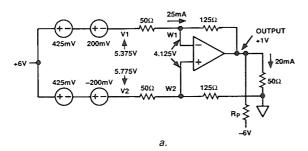

Two applications are shown. In Figure 9.2.4, the two sections of the AD539 are connected in simple parallel to double the output current. An AD844 transimpedance amplifier provides current-to-voltage conversion. The transfer function of this circuit is

$$V_{W} = \frac{-V_{X}V_{Y}}{2V}$$

Eq. 9.2.4

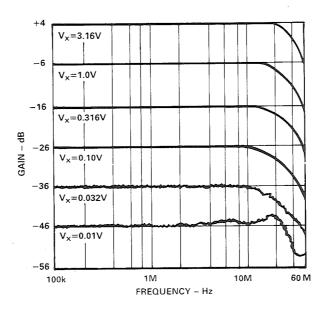

where  $V_X$  is the gain-control voltage, a positive input from 0 V to 3.2 V, and  $V_Y$  is the signal input voltage, nominally  $\pm 2V$  full scale but capable of operating up to  $\pm 4.2$  V. Connecting all four of the feedback resistors provided on the AD539 in parallel results in a feedback resistance of 1.5 k $\Omega$ , at which value the bandwidth of the AD844 is about 22 MHz, independent of  $V_X$ . The gain at  $V_X = 3.16V$  is +4 dB. Figure 9.2.5 shows the small signal response for a 50 dB gain-control range ( $V_X = +10$  mV to +3.16 V). At small values of  $V_X$ , capacitive feedthrough on the PC board becomes troublesome, and careful layout techniques are needed.

In Figure 9.2.6, The AD827 dual high-speed op amp is used to provide output current-to-voltage conversion and the two sections of the AD539 are connected in series to provide a VCA with a square-law response. The transfer function of this circuit (measured at the reverse-terminated load) is

$$\frac{V_{OUT}}{V_{IN}} = \frac{V_X^2}{8V^2}$$

Eq. 9.2.5

Alternately, the two sections may be operated in parallel with linear gain control. The frequency response of this circuit is about 8 MHz using the AD827 op amp. The AD811 high-speed op amp may be substituted in these circuits for increased performance.

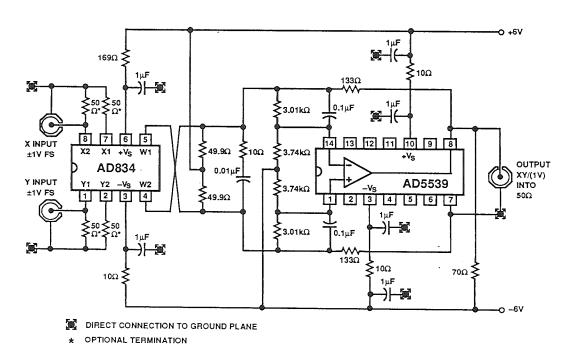

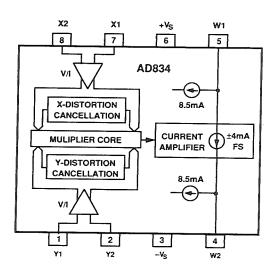

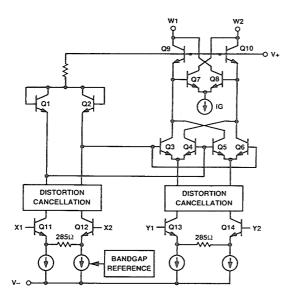

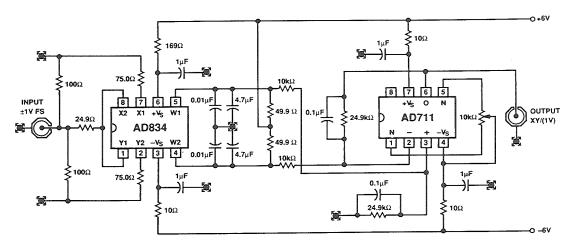

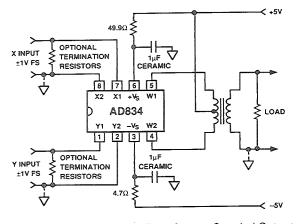

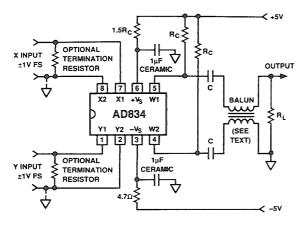

For wider bandwidths, the AD834 multiplier (Figure 9.2.7) may be used with a variety of op amps to build VCAs with small-signal bandwidths as high as 480 MHz. In each case, the op amp converts the differential-current outputs of the AD834 into a voltage.

### A 20MHz VCA USING THE AD539 AND THE AD844

Figure 9.2.4

## FREQUENCY RESPONSE OF THE 20MHz VCA

Figure 9.2.5

# VCA WITH SQUARE LAW GAIN CONTROL USING THE AD539 MULTIPLIER

\*PINOUT SHOWN IS FOR MINI-DIP PACKAGE

$v_{out}$  at termination resistor,  $r_T = v_x^2 v_{in}/8v^2$  $v_{out}$  at pin 7 of ad827 =  $v_x^2 v_{in}/4v^2$

**Figure 9.2.6**

# SIMPLIFIED BLOCK DIAGRAM OF THE AD834 MULTIPLIER

**Figure 9.2.7**

## A 60MHz VCA USING THE AD834 AND THE AD5539

Figure 9.2.8

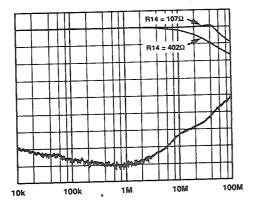

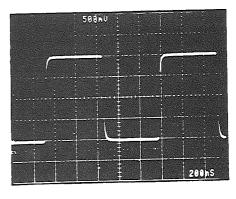

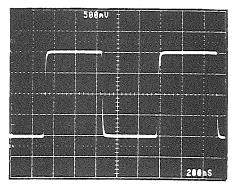

## PULSE RESPONSE OF THE 60MHz VCA

Figure 9.2.9

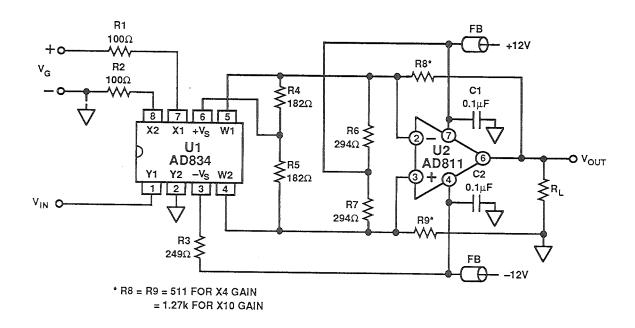

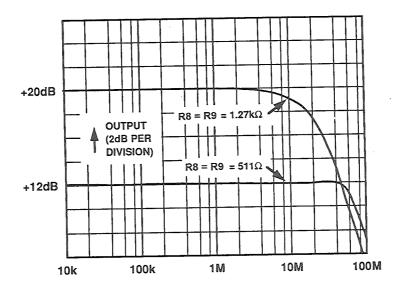

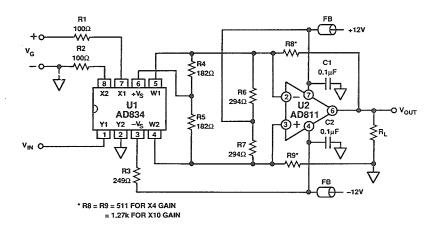

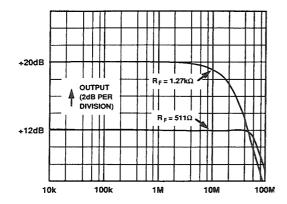

A 90MHz VCA is shown in Figure 9.2.10. The AD834's outputs are in the form of differential currents from a pair of open collectors, ensuring that the full bandwidth of the multiplier (which exceeds 500 MHz) is available. In this case, more moderate bandwidth is obtained using current-to-voltage conversion provided by the AD811 op amp, to realize a practical amplifier with a single-sided ground-referenced output. Using feedback resistors R8 and R9 of 511  $\Omega$  the overall gain ranges from -70 dB for V<sub>G</sub> ~ 0 to +12 dB (a numerical gain of four) when V<sub>G</sub> = +1 V.

The exact transfer function for the AD834 would show that the differential voltage inputs at X1, X2 and Y1, Y2 are first multiplied together, divided by the scaling voltage of 1 V (determined by the on-chip bandgap reference) and the resulting voltage is then divided by an accurate 250  $\Omega$  resistor to generate the output current. A simplified form of this transfer function is

$$I_W = (X_1 - X_2) (Y_1 - Y_2) 4 \text{ mA}$$

Eq. 9.2.6

where  $I_W$  is the differential current output from W1 to W2 and it is understood that the inputs  $X_1$ ,  $X_2$ ,  $Y_1$ , and  $Y_2$  are expressed in Volts. Thus, when both differential inputs are 1 V,  $I_W$  is 4 mA; this current is laser-calibrated to close tolerance, which simplifies the use of the AD834 in many applications. Note the direction of this current in determining the correct polarity of the output connections.

### A 90MHz VCA USING THE AD834 AND THE AD811

Figure 9.2.10

It is easy to show that the output of the AD811 is

$$V_{OUT} = 2 \times I_W \times R_F$$

Eq. 9.2.7

where  $R_F$  is the feedback resistor. For  $R_F = 500 \Omega$  the overall transfer function of the VCA becomes

$$V_{OUT} = 4(X_1 - X_2)(Y_1 - Y_2)$$

Eq. 9.2.8

which reduces to  $V_{OUT} = 4 V_G V_{IN}$  using the labeling conventions shown in Figure 9.2.10. As noted, the phase of the output reverses when  $V_G$  is negative. A slightly higher value of  $R_F$  compensates for the finite gain of the AD811.

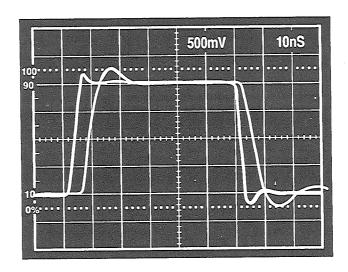

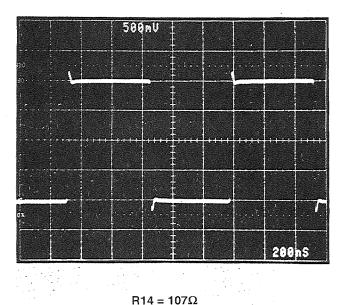

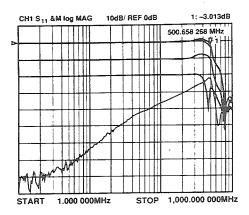

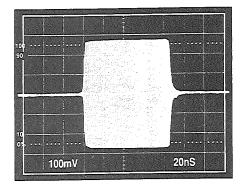

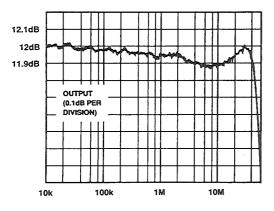

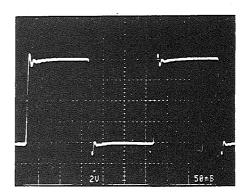

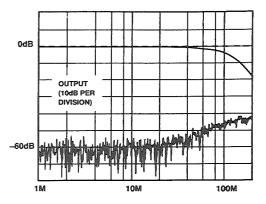

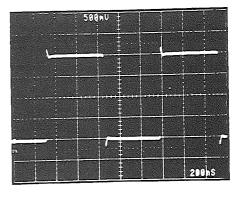

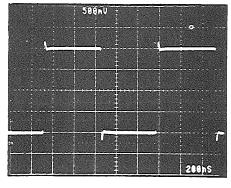

The -3 dB bandwidth is 90 MHz (Figure 9.2.11) and independent of gain. The response can be maintained flat to within  $\pm 0.1$  dB from DC to 40 MHz at full gain with the addition of a 0.3 pF capacitor across the feedback resistor R8. The circuit produces a full-scale output of  $\pm 4$  V for a  $\pm 1$  V input, and can drive a reverse-terminated load of 50  $\Omega$  or 75  $\Omega$  to  $\pm 2$  V. Figure 9.2.12 shows the typical pulse response.

## FREQUENCY RESPONSE OF THE 90MHz VCA

Figure 9.2.11

## PULSE RESPONSE OF THE 90MHz VCA

Figure 9.2.12

The gain can be increased to 20 dB (10) by increasing the values of R8 and R9 to 1.27 k $\Omega$ ; this also reduces the -3 dB bandwidth to about 25 MHz and produces a maximum output voltage of  $\pm 9$  V using  $\pm 12$  V supplies. It is not necessary to alter the values of R6 and R7 for the high-gain version of the amplifier, although an optimized design would increase these slightly to restore the common-mode voltage at the input of the AD811 to +5 V.

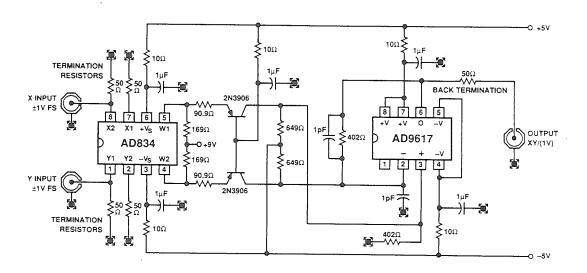

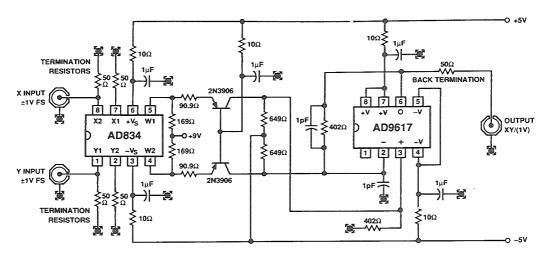

Figure 9.2.13 shows a DC to 480 MHz VCA using a PNP transistor as a common base stage or cascode. The transistor's base is tied to +5 V, ensuring that the emitter potential stays at 5.7 V and provides a steady voltage drop across the emitter resistors. In this circuit, the AD9617 op amp's inputs are 350 mV below ground and within their common mode range.

#### A 480MHz VCA USING THE AD834 AND THE AD9617

Figure 9.2.13

The bandwidth of a transistor configured as a cascode is approximately the unity gain frequency (f<sub>t</sub>) of the transistor, provided that the user does not create any spurious poles. Choosing emitter resistors which are too large for the transistor's parasitic emitter-base capacitance or collector resistors too large for the transistor's parasitic collector-base capacitance will create unwanted poles that lower the frequency response of the circuit.

Another potential pitfall when using the active PNP level shifter is oscillations at the cascode's emitter. The input impedance of a bipolar junction transistor's emitter is inductive at frequencies approaching f<sub>t</sub>, while the AD834's output is capacitive. These conditions can lead to oscillations.

#### AMPLIFIER APPLICATIONS GUIDE

To prevent such oscillations, the PNP's emitters in Figure 9.2.13 have been isolated from the AD834's output by the  $90.9\Omega$  resistors. These dampen any tendency to oscillate and provide signal attenuation. The 2N3906s and their accompanying network has proven to provide wideband level shifting without resonance or oscillation. Care must be taken when specifying alternative transistors.

The signal currents at the 2N3906s' collectors are now fed to an AD9617 op amp in a differential current-to-voltage converter configuration. This configuration is similar to the op-amp driven current-to-voltage converter that typically follows a current-output multiplying digital-to-analog converter.

The AD9617's inputs are connected to the collectors of the 2N3906s. The op amp creates a virtual short between the input nodes, forcing all the signal current to flow in the feedback paths. The differential transresistance of the converter is 400  $\Omega$ . The full scale gain of the circuit (X=Y=1V) at the AD9617's output is calculated as:

Maximum Gain =

$$2 \times 2.6 \text{ mA} \times 400 \Omega = 2.08$$

Eq. 9.2.9

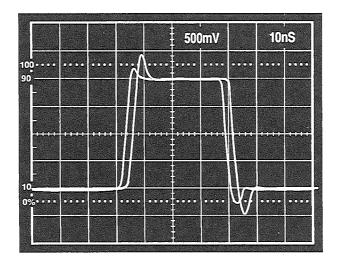

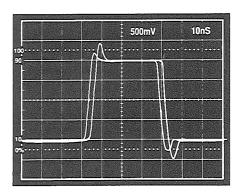

or 1.04 at the load after the reverse termination resistor. The actual circuit shows a full scale gain closer to unity. Figure 9.2.14 shows the pulse response. The small signal bandwidth is 480 MHz.

## PULSE RESPONSE OF THE 480MHz VCA

Figure 9.2.14

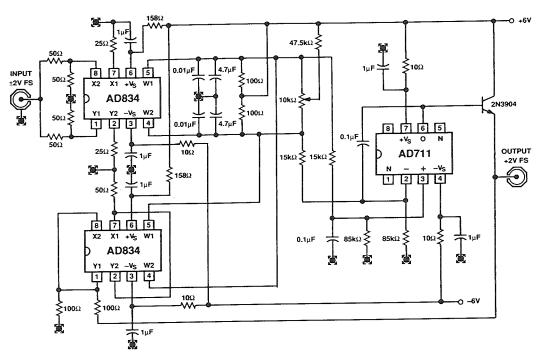

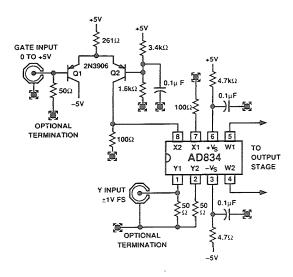

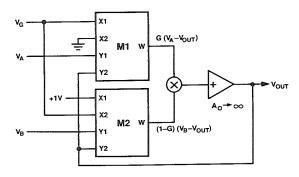

#### 9.2.2.1 VIDEO KEYER

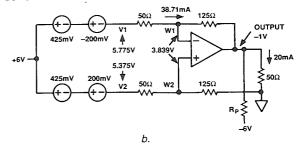

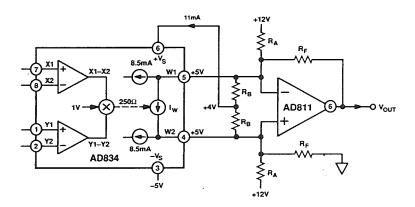

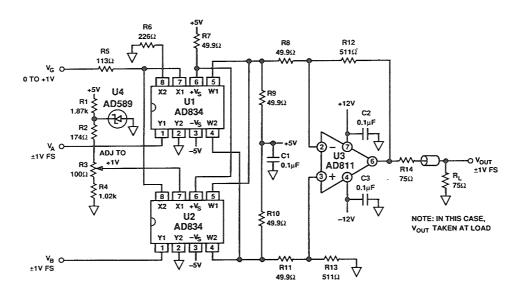

The AD834 also lends itself to a special form of a VCA called a video keyer. Keying is the term used in reference to blending two or more video sources under the control of a further signal or signals to create such special effects as dissolves and overlays. The circuit described here is a two-input keyer, with video inputs  $V_A$  and  $V_B$ , and a control input  $V_G$ .

The output at the load is given by

$$V_{OUT} = G V_A + (1-G) V_B$$

Eq. 9.2.10

where G is a dimensionless variable (actually, just the gain of the "A" signal path) that ranges from 0 when  $V_G = 0$ , to 1 when  $V_G = +1$  V. Thus,  $V_{OUT}$  varies continuously between  $V_A$  and  $V_B$  as G varies from 0 to 1.

#### A 2-INPUT VIDEO KEYER

$V_{OUT} = GV_A + (1 - G)V_B$

Figure 9.2.15

Figure 9.2.15 shows the circuit. Note first that  $V_{OUT}$  is returned to the inverting inputs Y2 of the multipliers and that their outputs are added. The sum is forced to zero by the assumed high open-loop gain of the op amp. Multiplier U1 produces an output  $G(V_A - V_{OUT})$ , while U2 produces an output  $(1-G)(V_B-V_{OUT})$ , where G is  $V_G/(1\ V)$  and ranges from 0 to 1. Therefore, the complete system is described by the limiting condition

$$G(V_A - V_{OUT}) + (1-G)(V_B - V_{OUT}) \rightarrow 0$$

Eq. 9.2.11

which requires that

$$V_{OUT} = GV_A + (1-G)V_B$$

Eq. 9.2.12

exactly as required for a two-input keyer. The summation of the differential current-mode outputs of the two AD834s is achieved by connecting together their respective W1 and W2 nodes. The resulting signal — essentially the loop error represented by the left-hand-side of Equation 9.2.11 — is forced to zero by the high gain of an AD811 op amp.

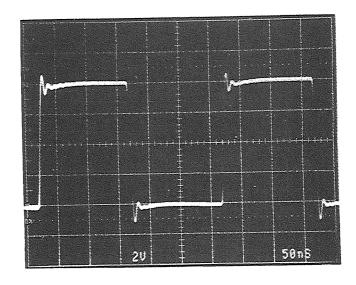

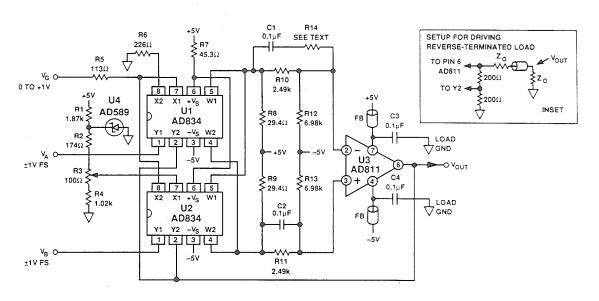

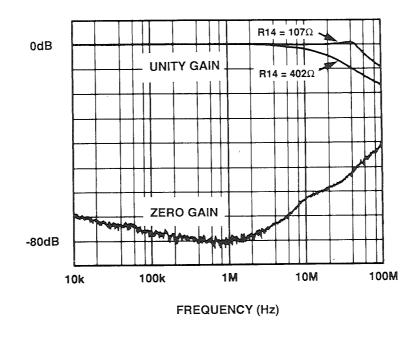

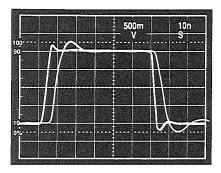

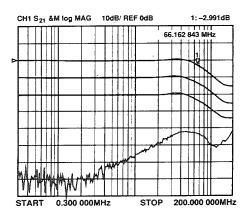

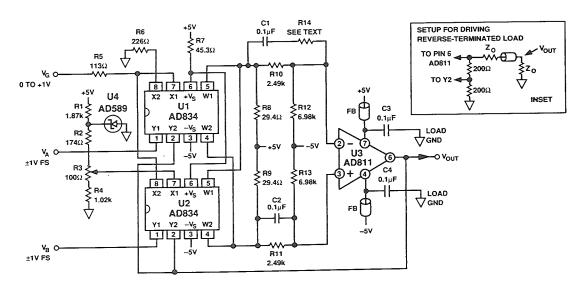

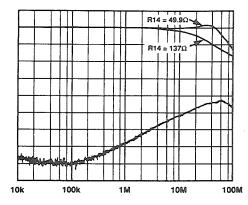

The operation is straightforward. Consider first the signal path through U1, which handles video input  $V_A$ . Its gain is zero when  $V_G = 0$  and the scaling we have chosen ensures that it is unity when  $V_G = +1$  V; this takes care of the first term in Equation 9.2.12. On the other hand, the  $V_G$  input to U2 is taken to the *inverting* input X2 while X1 is biased at an accurate +1 V. Thus, when  $V_G = 0$ , the response to video input  $V_B$  is already at its full-scale value of unity, whereas when  $V_G = +1$  V, the differential input  $X_1 - X_2$  is zero. This generates the second term in Equation 9.2.12. Figure 9.2.16 shows the AC response and Figure 9.2.17 shows the pulse response.

# FREQUENCY RESPONSE OF THE 2-INPUT VIDEO KEYER

Figure 9.2.16

#### PULSE RESPONSE OF THE 2-INPUT VIDEO KEYER

Figure 9.2.17

To generate the 1 V DC needed for the "1-G" term, an AD589 reference supplies 1.225V±25mV to a voltage divider consisting of resistors R2 through R4. Potentiometer R3 should be adjusted to provide +1 V at the X1 input.

The bias currents required at the output of the multipliers are provided by R8 and R9. A DC-level-shifting network comprising R10/R12 and R11/R13 ensures that the input nodes of the AD811 are positioned within an acceptable common-mode range for this IC. At high frequencies, C1 and C2 bypass R10 and R11, respectively.

#### 9.2.3 THE X-AMP

Two new dual-channel voltage-controlled amplifiers, the AD600 and AD602, have recently been introduced by Analog Devices. They differ from the multipliers just discussed in that the signal passes only through circuits that are linear: specifically a resistive ladder attenuator and a fixed-gain amplifier that uses negative feedback to enhance linearity. The term "X-AMP", coined to apply to this proprietary architecture, is a reference to the *exponential* gain function which they provide.

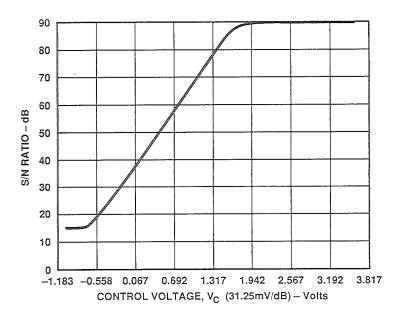

The X-AMP was developed for medical ultrasound applications. It provides the unusual combination of low noise (1.4 nV/ $\sqrt{\text{Hz}}$ ), good signal-handling capabilities (1 V RMS at the input, 2 V RMS at the output), a constant 3 dB bandwidth of DC to 35 MHz, constant phase and group-delay characteristics, low distortion (-60 dBc to 10 MHz) and low power consumption (125 mW maximum per channel). The gain is an exponential function of the control voltage, VG, which means it is "linear in dB", calibrated to 32 dB/Volt (31.25 mV/dB).

The two channels are independent and may be cascaded for a gain range of up to 80 dB in one package. Separate high-impedance, differential gain-control interfaces are provided. In the AD600 the gain for each section is 0 dB for  $V_G = -625$  mV, 20 dB for 0 V, and 40 dB for +625 mV. When  $V_G$  exceeds these values, the minimum gain becomes -1.07 dB and the maximum is 41.07 dB. The AD602 is similar, except that each VCA provides a gain of -11.07 dB to 31.07 dB.

These precise over-range values will later be important in understanding the gain-sequencing scheme used in one of the circuits presented. The sections can also be operated in parallel, to achieve a noise spectral density of 1 nV/VHz with no compromise in other aspect of performance.

As we will show, by adding an RMS converter to two series-connected VCA sections (a single AD600), a circuit can be built which provides both accurate automatic gain control (AGC) and an accurately-calibrated output voltage proportional to the decibel value of the RMS input over an 80 dB range.

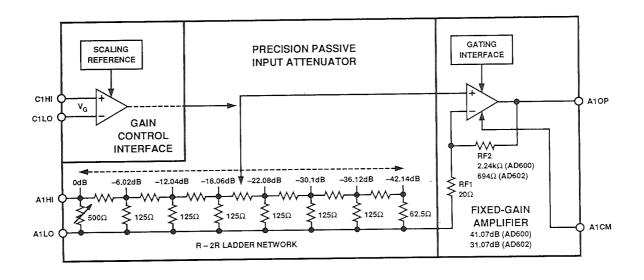

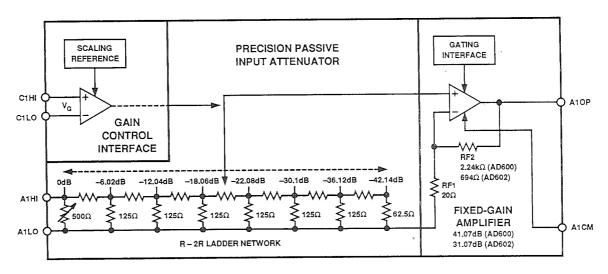

#### 9.2.3.1 X-AMP BASICS

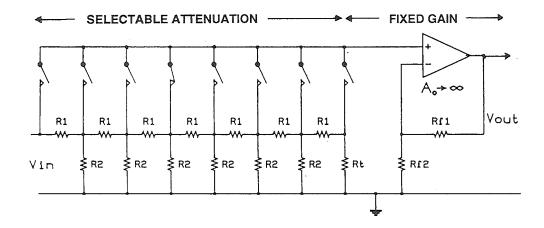

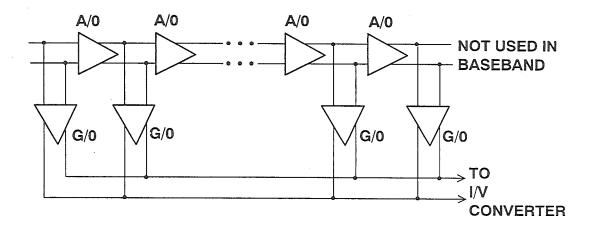

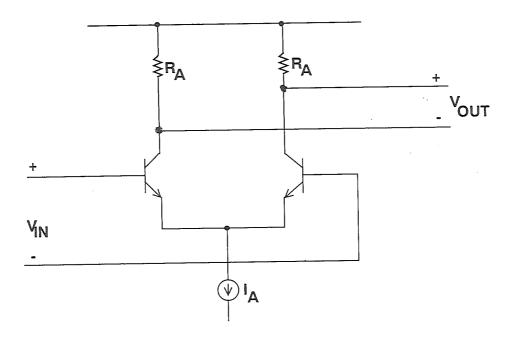

The key idea behind these amplifiers is the use of a low-noise *fixed-gain* amplifier, which employs negative feedback to achieve low distortion and high gain-accuracy, preceded by a broadband *passive* R-2R attenuator network.

The new technique allows the attenuator to be *continuously* interpolated, thus providing the smooth decibel-scaled gain function. The fixed-gain amplifier (Figure 9.2.18) uses classical negative feedback to achieve accurate gain. Since it never has to cope with large input signals it can be optimized for low noise and low distortion. The overall bandwidth is constant. The resulting amplifier comes very close to the ideal VCA.

When a correctly-terminated regular ladder network is used for this attenuator, a "linear-dB" control law is *automatically guaranteed*, because the signals between adjacent tap-points bear a constant ratio, diminishing in an exponential fashion from input to termination. Using the familiar R-2R network the voltage ratio from left to right is exactly two, or about 6.02 dB. Using an R-R network, the attenuation would be 8.36 dB. Obviously, any desired ratio can be used; in practice, the use of integer resistor multiples ensures excellent attenuation accuracy without the need for trimming.

# THE STARTING POINT IN THE SYNTHESIS OF THE X-AMP

Figure 9.2.18

A seven-section R-2R attenuator provides a total attenuation of 42.14 dB (corresponding to an overall voltage ratio of 128). For the moment, assume that the taps on this attenuator are selected by a simple rotary switch, to provide eight discrete values of gain, separated by constant decibel steps of 6.02 dB. When a large input is to be handled, the full attenuation is used: a 1V input is reduced to 7.8 mV, easily handled by the main amplifier stage.

On the other hand, for small signals, the amplifier's input can be *directly* connected to the source, with essentially no extra thermal noise. In this condition, the noise generation mechanisms can be reduced to those fundamentally attributable to shot noise in the input stage of the amplifier and the combined Johnson noise of the source and feedback resistors. This is a distinct and unique advantage of the technique.

In an IC realization, the rotary switch might be replaced by eight digitally-selected MOS transistors. However, these would introduce significant amounts of extra noise due to their channel resistance, unless they were made very large, in which case parasitic capacitances would cause very undesirable feedthrough effects at high frequencies. They would still only provide discrete gain steps; any attempt to increase the resolution by using more attenuator sections with closer tap points, adding correspondingly more switches, would only exacerbate the feedthrough problem.

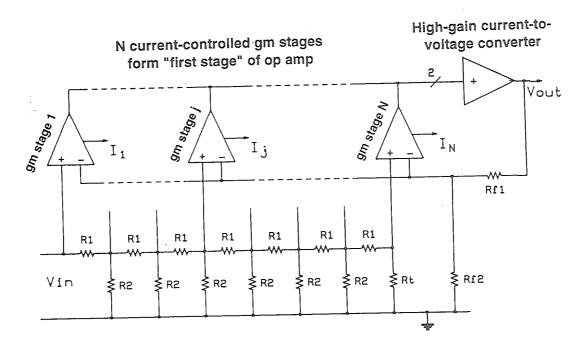

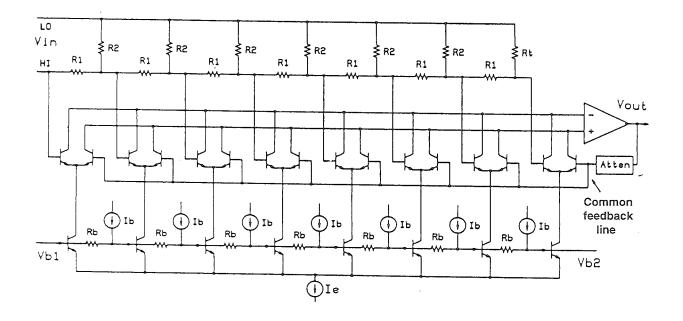

The key step in the development of the X-AMP concept is to replace the switches with controllable gm stages, as shown in Figure 9.2.19. These are bipolar differential pairs having a set of tail currents that are in the form of overlapping Gaussian sections. In this way, the effective input of the amplifier can be moved continuously from the source to the last tap on the attenuator. By correctly proportioning the interpolation currents, excellent gain linearity can be achieved: for the AD600 and AD602 it is about ±0.1 dB. Further development of the X-AMP showing the bipolar differential pairs is shown in Figure 9.2.20.

## DEVELOPMENT OF THE X-AMP IDEA

Figure 9.2.19

### FURTHER DEVELOPMENT OF THE X-AMP IDEA

Figure 9.2.20

The fundamental noise floor for a differential bipolar transconductance (gm) stage, limited by shot-noise, is

$$S_{I} = \frac{0.926 \text{nV} / \sqrt{\text{Hz}}}{\sqrt{I_{T}}}$$

Eq. 9.2.13

at 300 K (27°C) where  $I_T$  is the differential amplifier "tail" current expressed in milliamps. In the AD600 and AD602,  $I_T$  is 2.4 mA, producing a theoretical noise-spectral-density (NSD) of 0.6 nV/ $\sqrt{\text{Hz}}$ . In addition, there will be Johnson noise in the resistances associated with the source, input stage and attenuators; at 300 K this evaluates to

$$S_{\Omega} = 0.129 \sqrt{R_T}$$

$nV/\sqrt{Hz}$ , Eq. 9.2.14

where  $R_T$  is the total ohmic resistance associated with the input system, that is, the sum of the source or tap resistance, the feedback resistor  $R_{F1}$  and the two base resistances of the input

transistors,  $r_{bb'}$ . For the AD600 and AD602,  $R_T$  is about 80  $\Omega$ , producing a NSD of 1.15 nV/VHz. The RMS sum of the shot noise  $S_I$  and Johnson noise  $S_\Omega$  is 1.3 nV/VHz. Some second-stage noise contributions and base-current noise raise this to 1.4 nV/VHz.

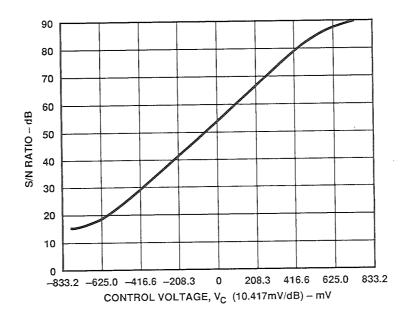

Note that the *output* noise of the X-AMP is constant as the gain is varied. For the AD600, with a gain of 41.07 dB, or X113, the NSD is simply 1.4 nV/ $\sqrt{\text{Hz}} \times 113$  or 158 nV/ $\sqrt{\text{Hz}}$ . In a 1 MHz bandwidth this amounts to 158  $\mu$ V RMS. Relative to a 1 V RMS output, this amounts to a signal-noise-ratio (S/N ratio) of 76 dB. For the AD602, having a gain which is 10 dB lower, the S/N ratio is 86 dB in a 1 MHz bandwidth.

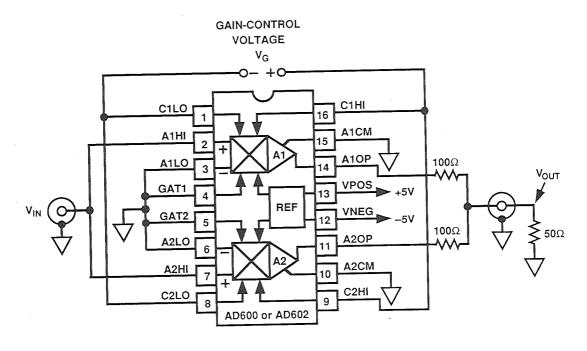

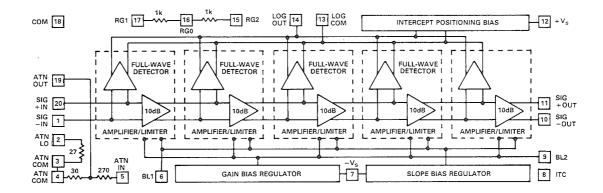

Each gain control voltage  $V_G$  is applied to differential inputs (Figure 9.2.21), which have a scale factor of 32 dB per Volt; thus, a change of 31.25 mV always changes the gain by 1 dB. For the AD600, the gain for  $V_G = 0$  is at the midpoint, that is, 20 dB. It is reduced to 0 dB when  $V_G = -625$  mV and raised to 40 dB when  $V_G = +625$  mV. Over this 0 to 40 dB range the gain is closely-specified. When  $V_G$  exceeds these values, the minimum gain is -1.07 dB and the maximum is 41.07 dB. The AD602 is very similar, but each fixed-gain amplifier now provides a gain of 31.07 dB, so each VCA section spans -10 dB to 30 dB (-11.07 dB to 31.07 dB max). The lower gain of the fixed amplifier in the AD602 improves the *output* signal-to-noise ratio by 10 dB; however, the input noise remains 1.4 nV $\sqrt{\text{Hz}}$ .

## **BLOCK DIAGRAM OF THE AD600 AND AD602**

Figure 9.2.21

Since the AD600 and AD602 each provide two independent VCAs, A1 and A2, gain ranges of over 80 dB can be achieved. In the simplest case, their individual gain-control inputs are connected in parallel, and the gain varies by 64 dB per Volt. However, in order to optimize the signal-to-noise performance over the entire gain range, a sequential arrangement of the A1 and A2 gain control voltages can be used, in which the gain of A1 is first varied over its 40 dB range, while A2 operates at minimum gain (thus, with the lowest coupling of the output noise of A1); thereafter, only the gain of A2 is varied to provide the second 40 dB segment of the overall gain range. This "sequential-gain" function can be achieved by including an offset voltage (corresponding to about 40 dB) between the A1 and A2 gain-control inputs. We shall later show another modification to the gain-control function, using a small control offsets (3 dB in the case of two cascaded VCAs, 2 dB in the case of three sections) to achieve exceptionally accurate gain and excellent logarithmic linearity. Figure 9.2.22 lists the highlights of the X-AMP.

### HIGHLIGHTS OF THE X-AMP

- Precise Decibel-Scaled Gain Control

- Accurate Absolute Gain Calibration

- Low Noise (1.4nV/ √Hz)

- Constant Bandwidth (dc to 35MHz)

- Stable Group Delay (±2ns over gain range)

- Low Distortion -- Uses Negative Feedback

- Low Power (125mW per channel maximum)

### Figure 9.2.22

#### 9.2.4 APPLYING THE X-AMP

The X-AMP is simple to apply. However, as for all wideband, high-gain amplifiers, careful PC board layout and adequate supply decoupling are important. This is particularly true when the amplifier sections are used in cascade. To simplify the following explanation, references to pin labels will be for amplifier A1, the connections for which are shown in Figure 9.2.23.

## CHANNEL A1 OF THE AD600 OR AD602

Figure 9.2.23

The input is applied to pins A1HI and A1LO, and may have a maximum value of 1 V RMS ( $\pm 1.4$  V peak), ultimately limited by the common-mode range of the eight  $g_m$  stages. The resistance from A1HI to A1LO is trimmed to  $100~\Omega \pm 2~\Omega$ , which allows the introduction of accurate external attenuation by the simple expedient of adding a series resistor. However, it is important to note that these pins do *not* form a fully differential input pair, as a glance at Figure 9.2.23 will show. In fact, A1LO must be always be very *well grounded*, since it carries not only the current in the ladder network but also the current in the feedback resistor RF1, which is about five times lower. Thus, the resistance which would be seen looking into A1LO if A1HI were grounded would be  $100~\Omega$  in parallel with  $20~\Omega$ , or  $16.7~\Omega$ . (Internally, A1LO is connected by multiple bond-wires to lower the impedance in this path.)

The output appears at pin A1OP but is referenced to an independent output ground, A1CM ("common"). A small common-mode voltage can exist between A1LO and A1CM, and this voltage will be rejected by the amplifier. (The details of the circuitry providing this feature are not shown explicitly in Figure 9.2.23.). Thus, if we denote the numerical gain of the amplifier by G, the output can be expressed as

$$V_{A1OP} = G(V_{A1HI} - V_{A1LO}) + V_{A1CM}$$

Eq. 9.2.15

For the AD600, G is accurately controlled from X1 to X100 while for the AD602 the specified range is X0.316 to X31.6.

The peak output voltage into resistive loads greater than 500  $\Omega$ , such as a flash A/D converter, is specified as  $\pm 3$  V when using the recommended  $\pm 5$  V supplies. For a 200  $\Omega$  load, an output of  $\pm 1.5$ V can be supported while still meeting the distortion specifications. Even lower load resistances can be driven if an external pull-down resistor is added between the output and the negative supply; for example, a 1 k $\Omega$  resistor would provide an extra current of 5 mA. Considerable load current can occur at high frequencies when the load is purely capacitive; in these cases, a small series resistor (5 to 50  $\Omega$ ) will improve the overall stability, often with little loss of bandwidth. In most cases, the output will be AC-coupled to the load.

The gain is controlled by the voltage  $V_G$  applied to the fully-differential pins C1HI and C1LO, which exhibit an input resistance of about 15 M $\Omega$  in shunt with 2 pF. This high resistance makes it an easy matter to control a large number of X-AMPs operating in parallel, as in the ultrasound application. Thus,

$$V_G = V_{C1HI} - V_{C1LO}$$

Eq. 9.2.16

and has a maximum specified range of ±625 mV.

The decibel gain is simply

$$G_{dB} = 32 V_G + 20$$

for the AD600 Eq. 9.2.17

or

$$G_{dB} = 32 V_G + 10$$

for the AD602 Eq. 9.2.18

where V<sub>G</sub> is in Volts.

The differential gain-control interface allows a variety of control schemes to be employed. In the simplest example, the gain can be made to either increase or decrease with a positive voltage, depending on whether C1HI or C1LO is connected to the control voltage. Because these inputs are essentially non-loading, it is a simple matter to provide an offset voltage to shift the control voltage to a particular range, using a resistor network across the supply. Thus, if the control input is connected to C1HI, while C1LO is offset to +625 mV, the control range now runs from 0 to +1.25 V.

If A1 and A2 are used in cascade and the same gain voltage is applied to both control interfaces in simple parallel, the gain factor is doubled to 64 dB/V, because the gains of both amplifiers vary simultaneously. However, if one of the control interfaces is offset by the appropriate

voltage we can arrange for the gain of A1 and A2 to vary sequentially, which keeps the scaling at 32 dB/V but now requires 2.5 V for the full 80 dB range, conveniently supplied by an inexpensive 8-bit DAC, such as the AD558. An example is shown in the next section.

The AD600 and AD602 also provide a TTL-compatible gating feature. When the pin GAT1 (or GAT2) is HI, the channel is shut down, and the output is set to within a few millivolts of the voltage on A1CM (or A2CM) with an attendant large reduction in output noise. This feature is useful in multi-channel synthetic-aperture or beam-forming systems, where channels having a weighting below some threshold can be switched off and their noise contribution to the summed signal thus minimized.

The gain-control range of the last circuit can be extended to 100 dB by using a further VCA section. Fully-tested implementations are shown later; in both, precise gain offsets are used to achieve either (1) a very high gain linearity of ±0.1 dB over the full 100 dB range, or (2) the optimal signal-to-noise ratio at any gain.

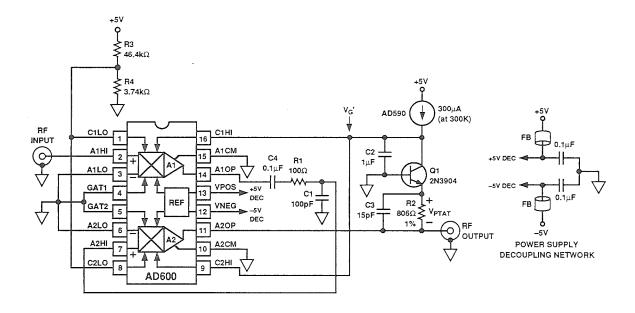

### 9.2.5 A LOW-NOISE AGC AMPLIFIER

Figure 9.2.24 provides an example of the ease with which the AD600 can be connected as an AGC amplifier. A1 and A2 are cascaded, with 6 dB of attenuation introduced by the 100  $\Omega$  resistor R1, while a time- constant of 5 ns is formed by C1 and the 50  $\Omega$  of net resistance at the input of A2. This introduces a single-pole low-pass filter at about 32 MHz,to ensure stability at maximum gain It also lowers the overall gain range to -6dB to 74dB. C4 blocks the small DC offset voltage at the output of A1 (which might otherwise saturate A2 at its maximum gain) and introduces a high-pass corner at about 8 kHz, eliminating low-frequency noise and spurious signals which may be present at the input.

A half-wave detector is used, based on Q1 and R2. The current into capacitor C2 is just the difference between the current provided by the AD590 (300  $\mu$ A at 300 K, 27 °C) and the collector current of Q1. In turn, the control voltage  $V_G$  is the time-integral of this *error* current. In order for  $V_G$  (and thus the gain) to remain stable, the rectified current in Q1 must, on average, exactly balance the current in the AD590. If the output of A2 is too small to do this,  $V_G$  will ramp up, causing the gain to increase, until Q1 conducts sufficiently.

First consider the particular case where R2 is zero and the output voltage  $V_{OUT}$  is a squarewave at, say, 100 kHz, that is, well above the corner frequency of the control loop. During the time  $V_{OUT}$  is negative, Q1 conducts; when  $V_{OUT}$  is positive, it is cut off. Since the average collector current is forced to be 300  $\mu$ A, and the squarewave has a duty-cycle of 1:1, the current when conducting must be 600  $\mu$ A. With R2 omitted, the peak value of  $V_{OUT}$  is forced to be just the  $V_{BE}$  of Q1 at 600  $\mu$ A, typically about 700 mV, or  $2V_{BE}$  peak-to-peak. This voltage, hence the amplitude at which the output stabilizes, has a strong negative temperature coefficient (TC), typically -1.7 mV/°C. While this may not be troublesome in some applications, the addition of R2 will render the output stable with temperature.

### A SIMPLE BUT ACCURATE AGC AMPLIFIER

Figure 9.2.24

To understand this, first note that the current in the AD590 is proportional to absolute temperature (PTAT). (The AD590 is a temperature-dependent current source with a 1  $\mu$ A/K temperature coefficient. At T = 300 K, its output is 300  $\mu$ A.) For the moment, continue to assume that the signal is a squarewave. When Q1 is conducting,  $V_{OUT}$  is now the *sum* of  $V_{BE}$  and a voltage which is PTAT and which can be chosen to have an equal but opposite TC to that of the  $V_{BE}$ . This is actually nothing more than an application of the "bandgap voltage reference" principle. When R2 is chosen such that the sum of the voltage across it and the  $V_{BE}$  of Q1 is close to the bandgap voltage of about 1.2 V,  $V_{OUT}$  will be stable over a wide range of temperatures, provided, of course, that Q1 and the AD590 share the same thermal environment.

Since the average emitter current is 600  $\mu A$  during each half-cycle of the squarewave a resistor of 833  $\Omega$  would add a PTAT voltage of 500 mV at 300 K, increasing by 1.66 mV/°C. In practice, the optimum value will depend on the type of transistor used, and, to a lesser extent, on the waveform for which the temperature stability is to be optimized; for the inexpensive 2N3904 and sinewave signals, the recommended value is 806  $\Omega$ . This resistor also serves to lower the peak current in Q1 when more typical signals (usually, sinusoidal) are involved, and the 200-Hz LP filter it forms with C2 helps to minimize distortion due to ripple in  $V_G$ . Note that the output amplitude under sinewave conditions will be higher than for a squarewave, since the average value of the current *for an ideal rectifier* would be 0.637 times as large, causing the output

amplitude to be 1.88 (=1.2/0.637) V, or 1.33 V RMS. In practice, the somewhat non-ideal rectifier results in the sinewave output being regulated to about 1.275 V RMS.

An offset of +375 mV is applied to the inverting gain-control inputs C1LO and C2LO. Thus the nominal -625 mV to +625 mV range for  $V_G$  is translated upwards (at the node labeled  $V_G$ ') to -0.25 V for minimum gain to +1 V for maximum gain. This prevents Q1 from going into heavy saturation at low gains and leaves sufficient "headroom" of 4 V for the AD590 to operate correctly at high gains when using a +5V supply.

In fact, the 6 dB interstage attenuator means that the overall gain of this AGC system actually runs from -6 dB to +74 dB. Thus, an input of 2 V RMS would be required to produce a 1 V RMS output at the minimum gain, which exceeds the 1 V RMS maximum input specification of the AD600. The *available* gain range is therefore 0 to 74 dB (or, X1 to X5000). Since the gain scaling is 15.625 mV/dB (because of the cascaded stages) the minimum value of  $V_G$ ' is actually increased by 6 X 15.625 mV, or about 94 mV, to -156 mV, so the risk of saturation in Q1 is further reduced.

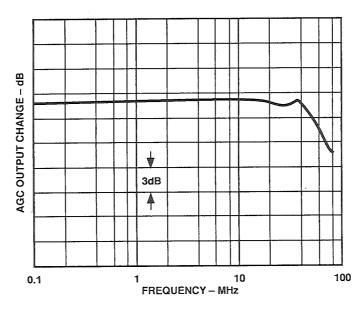

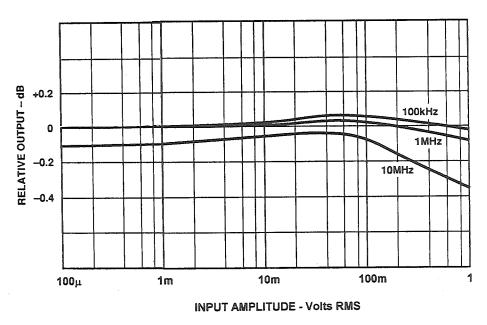

The emitter circuit of Q1 is somewhat inductive (due its finite  $f_t$  and base resistance). Consequently, the effective value of R2 increases with frequency. This would result in an increase in the stabilized output amplitude at high frequencies, but for the addition of C3, determined experimentally to be 15 pF for the 2N3904 for maximum response flatness. Alternatively, a faster transistor can be used here to reduce HF peaking. Figure 9.2.25 shows the AC response at the stabilized output level of about 1.3 V RMS. Figure 9.2.26 demonstrates the output stabilization for sinewave inputs of 1 mV to 1V RMS at frequencies of 100 kHz, 1 MHz and 10 MHz.

### STABILIZATION OF Vout VERSUS FREQUENCY

Figure 9.2.25

### STABILIZATION OF Vout VERSUS INPUT LEVEL

Figure 9.2.26

While the "bandgap" principle used here sets the output amplitude to 1.2 V (for the squarewave case), the stabilization point can be set to any higher amplitude, up to the maximum output of  $\pm (V_S - 2)$  V which the AD600 can support. It is only necessary to split R2 into two components of appropriate ratio whose parallel sum remains close to the zero-TC value of 806  $\Omega$ . For example, using R2a = 1.62 k $\Omega$  from the emitter of Q1 to VOUT and R2b = 1.62 k $\Omega$  from the emitter node to ground, the output can be raised to 2 V RMS for sinewave signals, without altering the temperature stability.

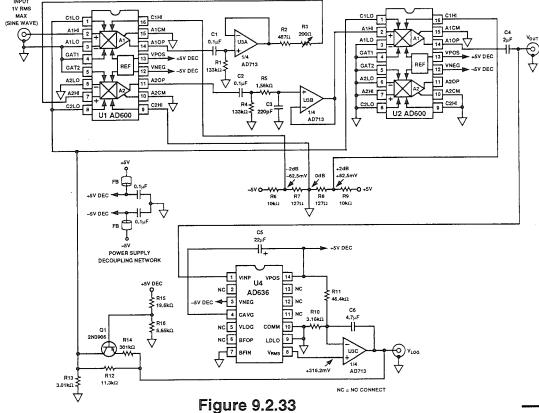

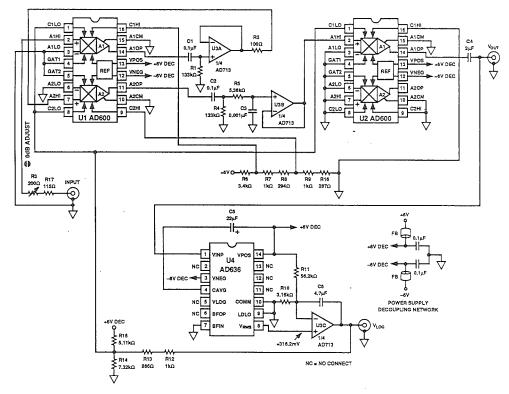

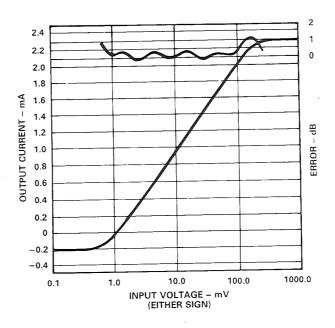

#### 9.2.7 AN 80 dB RMS-LINEAR-dB MEASUREMENT SYSTEM

Monolithic RMS-DC converters provide an inexpensive means to measure the RMS value of a signal of arbitrary waveform. They also may provide a low-accuracy logarithmic ("decibel-scaled") output. However, they have a fairly small dynamic range – typically only 50 dB. More troublesome is that the bandwidth is roughly proportional to the signal level; for example, the AD636 provides a 3 dB bandwidth of 900 kHz for an input of 100 mV RMS, but only a 100kHz bandwidth for an input of 10 mV RMS. Its "raw" logarithmic output is unbuffered, uncalibrated and not stable over temperature requiring considerable support circuitry, including at least two adjustments and a special high-TC resistor.

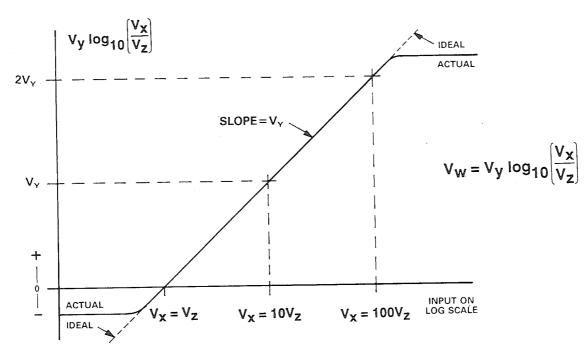

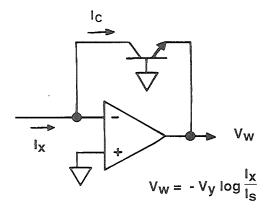

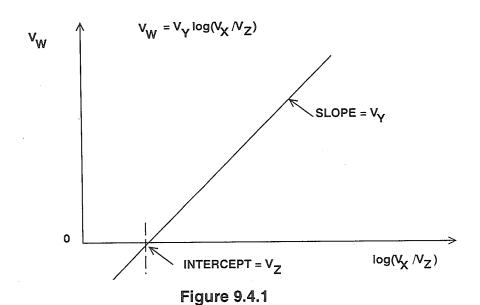

All of these problems can be eliminated using an AD636 as merely the detector element in an AGC loop, in which the difference between the RMS output of the amplifier and a fixed DC reference are nulled in a loop integrator. The dynamic range and the accuracy with which the signal can be determined are now entirely dependent on the amplifier used in the AGC system. Since the input to the RMS-DC converter is forced to a constant amplitude, close to its maximum input capability, the bandwidth is no longer signal-dependent. If the amplifier has an exactly-exponential ("linear-dB") gain-control law its control voltage is forced by the AGC loop to have the general form

$$V_{LOG} = V_S lgt \frac{V_{IN (RMS)}}{V_Z}$$

Eq. 9.2.19

where  $V_S$  is the logarithmic slope and  $V_Z$  is the logarithmic intercept, that is, the value of  $V_{IN}$  for which  $V_{LOG}$  is zero. (Compare this with Equation 9.3.1 in the section to follow on logarithmic amplifiers).

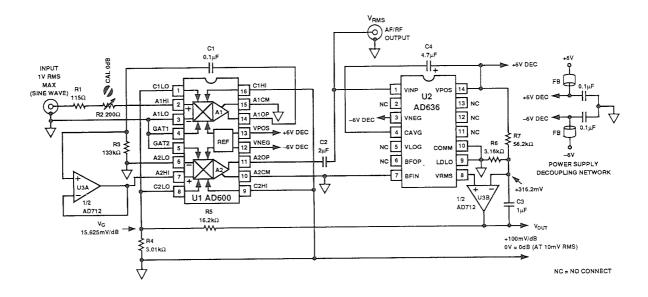

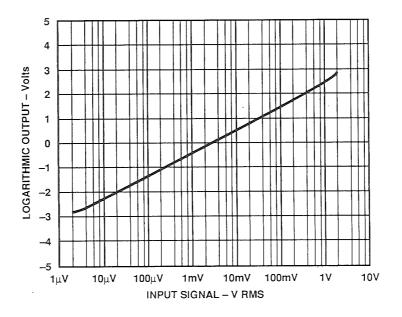

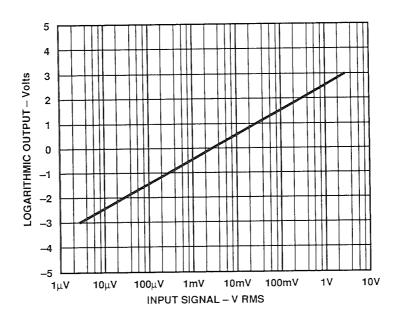

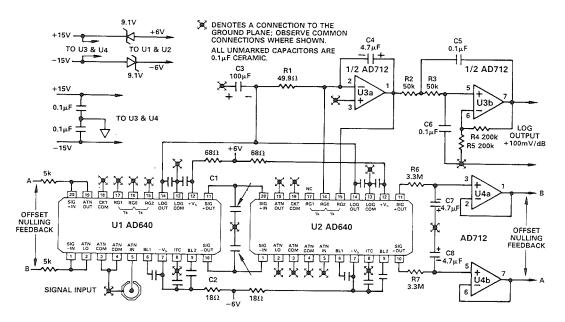

Figure 9.2.27 shows a practical wide-dynamic-range RMS-responding measurement system using the AD600. It can handle inputs of from 100  $\mu V$  to 1 V RMS with a constant measurement bandwidth of 20 Hz to 2 MHz, limited primarily by the AD636 RMS converter. Its logarithmic output is a loadable voltage, accurately-calibrated to 100 mV/dB, or 2V per decade, which simplifies the interpretation of the reading when using a DVM, and is arranged to be –4 V for an input of 100  $\mu V$  RMS input, zero for 10 mV, and +4 V for a 1V RMS input. In terms of Eq. 9.2.19,  $V_S$  is 2 V and  $V_Z$  is 10 mV.

## A COMPLETE 80dB RMS-LINEAR-dB MEASUREMENT SYSTEM

Figure 9.2.27

Note that the peak "log-output" of  $\pm 4$  V requires the use of  $\pm 6$  V supplies for the dual op-amp U3 (AD712) although lower supplies would suffice for the AD600 and AD636. If only  $\pm 5$  V supplies are available it will be either necessary to use a reduced value for  $V_S$  (say, 1 V, in which case the peak output would be only  $\pm 2$  V) or restrict the dynamic range of the signal to about 60 dB.

As in the previous case, the two amplifiers of the AD600 are used in cascade. However, the 6 dB attenuator and low-pass filter found in Figure 9.2.24 are replaced by a unity-gain buffer amplifier U3A, whose modest bandwidth eliminates the risk of instability at the highest gains. The buffer also allows the use of a high-impedance coupling network (C1/R3) which introduces a high-pass corner at about 12 Hz. An input attenuator of 10 dB (X 0.316) is now provided by R1 + R2 operating in conjunction with the AD600's input resistance of 100  $\Omega$ . The adjustment provides exact calibration of  $V_Z$  in critical applications, but R1 and R2 may be replaced by a fixed resistor of 215  $\Omega$  if very close calibration is not needed, since the input resistance of the AD600 (and all other key parameters of it and the AD636) are already laser-trimmed for accurate operation. This attenuator allows inputs as large as  $\pm 4$  V to be accepted, that is, signals with an RMS value of 1 V combined with a crest-factor of up to 4.

The output of A2 is AC-coupled via another 12 Hz high-pass filter formed by C2 and the 6.7 k $\Omega$  input resistance of the AD636. The averaging time-constant for the RMS-DC converter is determined by C4. The unbuffered output of the AD636 (at pin 8) is compared with a fixed voltage of +316 mV set by the positive supply voltage of +6 V and resistors R6 and R7. ( $V_Z$  is proportional to this voltage and systems requiring greater calibration accuracy should replace the supply-dependent reference with a more stable source. However,  $V_S$  is independent of the supply voltages, being determined by the on-chip band-gap reference in the X-AMP.) Any difference in these voltages is integrated by the op-amp U3B, with a time-constant of 3 ms formed by the parallel sum of R6/R7 and C3.

Now, if the gain of the AD600 is too high,  $V_{OUT}$  will be greater than the "set-point" of 316 mV, causing the output of U3B – that is,  $V_{LOG}$  – to ramp up (note that the integrator is non-inverting). A fraction of  $V_{LOG}$  is connected to the *inverting* gain-control inputs of the AD600, so causing the gain to be reduced, as required, until  $V_{OUT}$  is exactly equal to 316 mV (DC), at which time the AC voltage at the output of A2 is forced to be exactly 316 mV (RMS). This fraction is set by R4 and R5 such that a 15.625 mV change in the control voltages of A1 and A2 – which would change the gain of the two cascaded amplifiers by 1 dB – requires a change of 100mV at  $V_{LOG}$ . Notice here that since A2 is forced to operate at an output level well below its capacity, waveforms of high crest-factor can be tolerated throughout the amplifier.

To verify the operation, assume an input of 10 mV RMS is applied to the input, which results in a voltage of 3.16 mV RMS at the input to A1, due to the 10 dB loss in the attenuator. If the system performs as claimed,  $V_{LOG}$  (and hence  $V_{G}$ ) should be zero. This being the case, the gain of both A1 and A2 will be 20 dB and the output of the AD600 will therefore be 100 times (40dB) greater than its input, which evaluates to 316 mV RMS. This is the input required at the AD636 to balance the loop, confirming the basic operation. Note that unlike most AGC circuits,

(which often have a high temperature-coefficient of gain due to the internal "kT/q" scaling – see Eq. 9.2.1) these voltages, and thus the output, of this measurement system is very stable over temperature. This behavior arises directly from the fundamental and exact exponential calibration of the ladder attenuator.

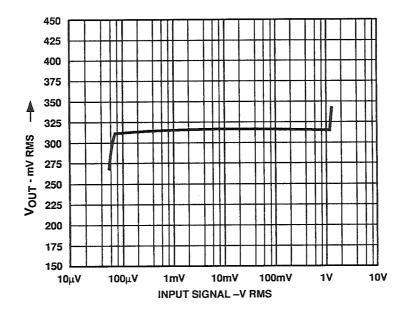

Typical results are presented for a sinewave input at 100 kHz. Figure 9.2.28 shows that the output is held very close to the set-point of 316 mV RMS over an input range in excess of 80dB.

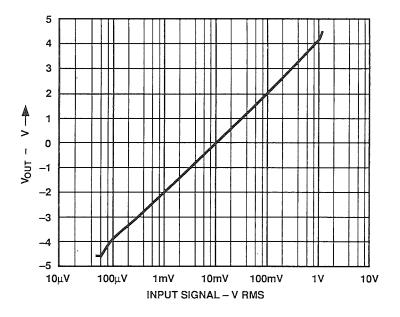

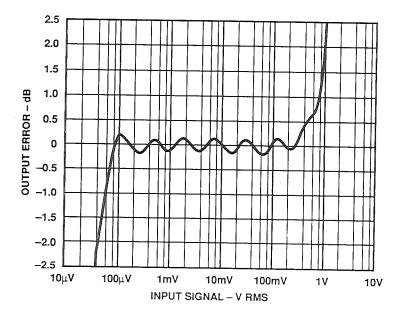

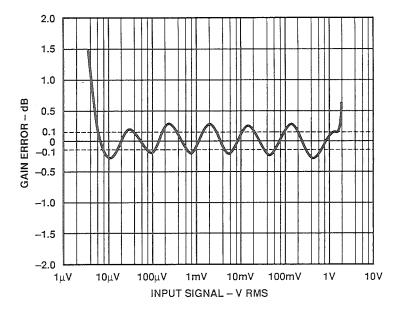

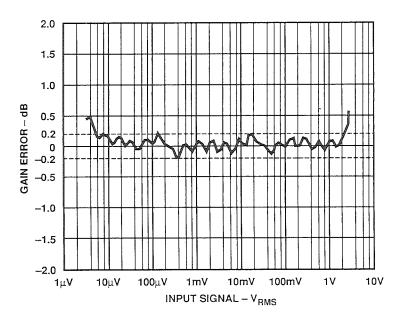

Figure 9.2.29 shows the "decibel" output voltage,  $V_{LOG}$ , and Figure 9.2.30 shows that the *deviation* from the ideal output predicted by Eq. 9.2.19 is within  $\pm 1$  dB for the 80 dB range from 80  $\mu$ V to 800 mV.

### SIGNAL OUTPUT Vout VERSUS INPUT LEVEL

Figure 9.2.28

### THE LOGARITHMIC OUTPUT VLOG VERSUS INPUT LEVEL

Figure 9.2.29

## DEVIATION FROM THE IDEAL LOGARITHMIC OUTPUT

Figure 9.2.30

By suitable choice of the input attenuator R1+R2, this could be centered to cover any range from 25  $\mu$ V to 250 mV to, say, 1 mV to 10 V, with appropriate correction to the value of V<sub>Z</sub>. (Note that V<sub>S</sub> is not affected by the changes in the range). The gain ripple of  $\pm 0.2$  dB seen in this curve is the result of the finite interpolation error of the X-AMP. Note that it occurs with a periodicity of 12 dB – twice the separation between the tap points in each amplifier section.

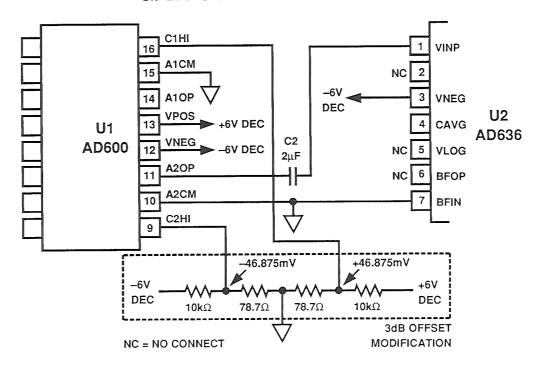

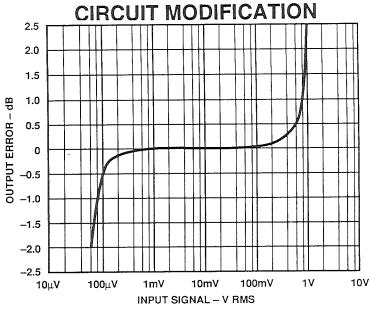

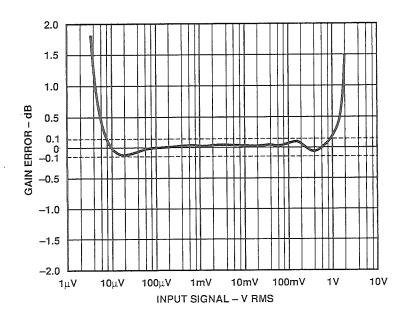

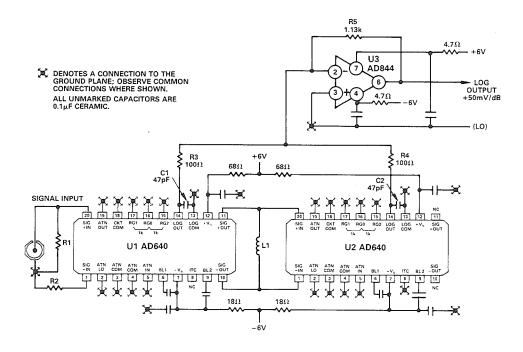

This ripple can be canceled whenever the X-AMP stages are cascaded by introducing a 3 dB offset between the two pairs of control voltages. A simple means to achieve this is shown in Figure 9.2.31: the voltages at C1HI and C2HI are "split" by  $\pm 46.875$  mV, or  $\pm 1.5$  dB. Alternatively, either one of these pins can be individually offset by 3 dB and a 1.5 dB gain adjustment made at the input attenuator (R1+R2). The error curve shown in Figure 9.2.32 demonstrates that over the central portion of the range the output voltage can be maintained very close to the ideal value. The penalty for this modification is the higher errors at the extremities of the range.

## METHOD FOR CANCELING THE GAIN-CONTROL RIPPLE

Figure 9.2.31

## LOGARITHMIC ERROR USING THE PREVIOUS

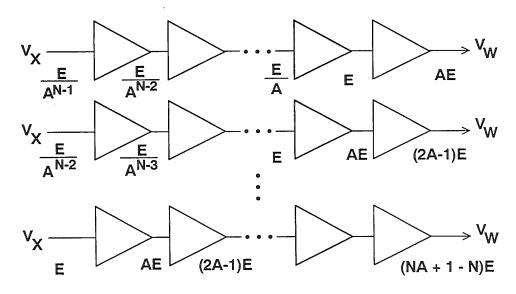

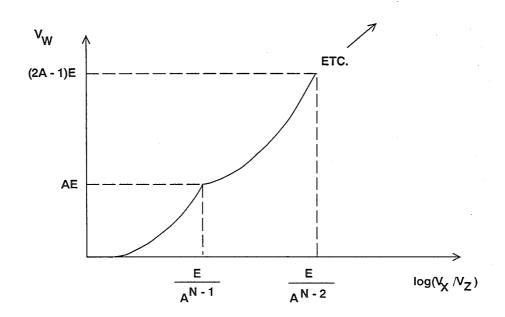

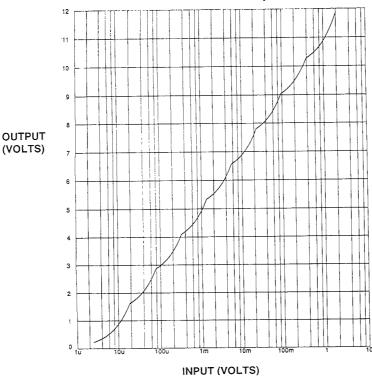

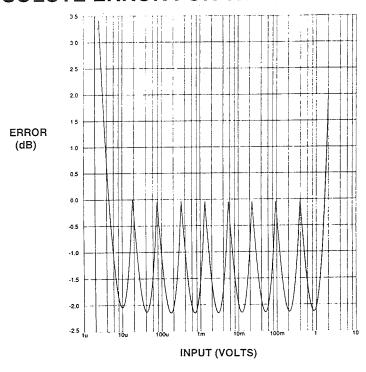

Figure 9.2.32