# MAX32665/MAX32666 USER GUIDE UG6971; Rev 3; 2/2022

Abstract: This user guide provides application developers information on how to use the memory and peripherals of the **MAX32665/MAX32666** microcontroller. Detailed information for all registers and fields in the device are covered. Guidance is given for managing all the peripherals, clocks, power and startup for the device family.

# MAX32665/MAX32666 User Guide

# **Table of Contents**

| 1. ( | Over  | view                                          | 29 |

|------|-------|-----------------------------------------------|----|

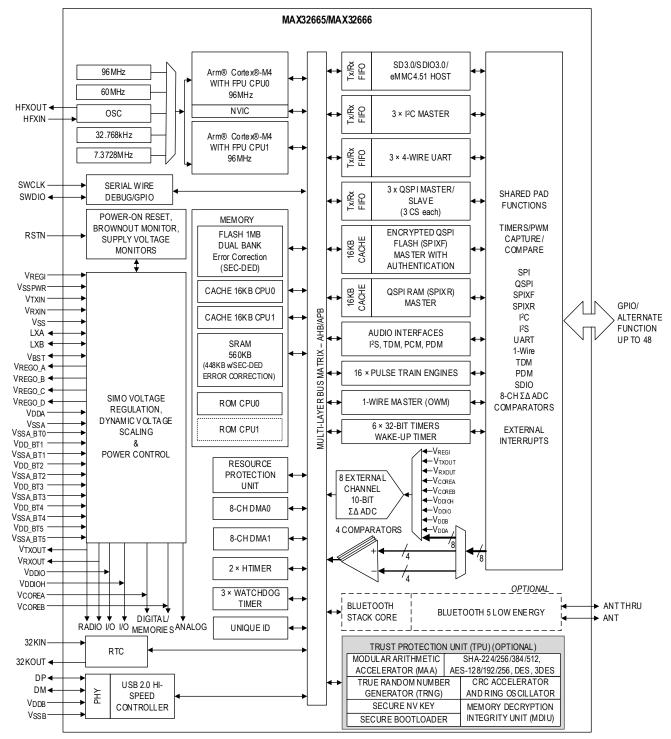

| 1.1  | L     | Block Diagram                                 | 30 |

| 2. I | Reso  | urce Protection Unit (RPU)                    | 31 |

| 2.1  | L     | Instances                                     | 31 |

| 2.2  |       | Usage                                         | 33 |

|      | 2.2.1 | Reset State                                   |    |

|      | 2.2.2 | MPU Implementation                            |    |

|      | 2.2.3 | MPU Protection Fault                          |    |

|      | 2.2.4 | RPU Protection Fault                          | 33 |

|      | 2.2.5 | RPU Fault Handler                             | 33 |

| 2.3  | 3     | Registers                                     | 34 |

| 2.4  | ł     | Register Details                              | 36 |

| 3. I | Mem   | ory, Register Mapping, and Access             | 40 |

| 3.1  |       | Memory, Register Mapping, and Access Overview |    |

| 3.2  |       | Field Access Definitions                      |    |

|      |       |                                               |    |

| 3.3  |       | Standard Memory Regions                       |    |

|      | 3.3.1 | Code Space<br>SRAM Space                      |    |

|      | 3.3.2 |                                               |    |

|      | 3.3.3 | Peripheral Space                              |    |

|      | 3.3.4 | External RAM Space                            |    |

|      | 3.3.5 | External Device Space                         |    |

|      | 3.3.6 | System Area (Private Peripheral Bus)          |    |

|      | 3.3.7 | System Area (Vendor Defined)                  |    |

| 3.4  |       | Device Memory Instances                       |    |

|      | 3.4.1 | Main Program Flash Memory                     |    |

|      | 3.4.2 | Cache Memories                                |    |

|      | 3.4.3 | Information Block Flash Memory                |    |

|      | 3.4.4 | System SRAM                                   |    |

|      | 3.4.5 | AES Key and Working Space Memory              |    |

|      | 3.4.6 | MAA Key and Working Space Memory              |    |

|      | 3.4.7 | TPU Memory                                    | 48 |

| 3.5  | 5     | AHB Interfaces                                | 48 |

| 3.5.1    | Core AHB Interfaces                                | 48 |

|----------|----------------------------------------------------|----|

| 3.5.2    | AHB Masters                                        | 48 |

| 3.6      | Peripheral Register Map                            | 49 |

| 3.6.1    | APB Peripheral Base Address Map                    | 49 |

| 3.6.2    | AHB Peripheral Base Address Map                    | 50 |

| 3.7      | Error Correction Coding (ECC) Module               | 51 |

| 3.7.1    | SRAM                                               | 51 |

| 3.7.2    | FLASH                                              | 51 |

| 3.7.3    | Cache                                              | 52 |

| 4. Syste | em, Power, Clocks, Reset                           | 53 |

| 4.1      | Oscillator Sources and Clock Switching             | 53 |

| 4.1.1    | Oscillator Implementation                          | 55 |

| 4.1.2    | 96MHz Internal Main High-Speed Oscillator          | 55 |

| 4.1.3    | 60MHz Low Power Internal Oscillator                | 55 |

| 4.1.4    | 32MHz Bluetooth Radio Oscillator                   | 55 |

| 4.1.5    | 7.3728MHz Internal Oscillator                      | 56 |

| 4.1.6    | 32.768kHz External Crystal Oscillator              | 56 |

| 4.1.7    | 8kHz Ultra-Low Power Nano-Ring Internal Oscillator | 57 |

| 4.2      | Operating Modes                                    | 57 |

| 4.2.1    | ACTIVE Mode                                        | 58 |

| 4.2.2    | SLEEP Low Power Mode                               | 58 |

| 4.2.3    | DEEPSLEEP Low Power Mode                           | 60 |

| 4.2.4    | BACKUP Low Power Mode                              | 62 |

| 4.3      | Device Resets                                      | 63 |

| 4.3.1    | Peripheral Reset                                   | 66 |

| 4.3.2    | Soft Reset                                         | 66 |

| 4.3.3    | System Reset, External Reset                       | 66 |

| 4.3.4    | Power-On Reset                                     | 66 |

| 4.4      | Cache                                              | 66 |

| 4.5      | Instruction Cache Controller                       | 67 |

| 4.5.1    | Enabling ICC0/ICC1/SFCC                            | 67 |

| 4.5.2    | Flushing the ICC0/ICC1/SFCC Cache                  | 68 |

| 4.5.3    | Flushing SRCC Cache                                | 68 |

| 4.6      | Instruction Cache Controller Registers             | 68 |

| 4.7      | External RAM SPIXR Cache Controller (SRCC)         | 71 |

| 4.8      | RAM Memory Management                              | 71 |

|          |                                                    |    |

| 4.8.1    | RAM Zeroization                                          | 71  |

|----------|----------------------------------------------------------|-----|

| 4.8.2    | RAM Low Power Modes                                      | 71  |

| 4.9      | Miscellaneous Control Registers                          | 72  |

| 4.10     | Miscellaneous Control Registers Details                  | 73  |

| 4.11     | Single Inductor Multiple Output (SIMO) Power Supply      | 75  |

| 4.11.    | 1 Power Supply Monitor                                   | 76  |

| 4.12     | Single Inductor Multiple Output (SIMO) Registers         | 76  |

| 4.13     | Single Inductor Multiple Output (SIMO) Registers Details | 78  |

| 4.14     | Power Sequencer and Always-On Domain Registers           | 83  |

| 4.15     | Power Sequencer and Always-On Domain Register Details    | 84  |

| 4.16     | Global Control Registers (GCR)                           | 92  |

| 4.17     | Global Control Register Details (GCR)                    | 92  |

| 4.18     | Function Control Registers                               | 121 |

| 4.19     | Function Control Register Details                        | 121 |

| 4.20     | AES Key Registers                                        | 122 |

| 4.21     | AES Key Register Details                                 | 122 |

| 5. Inter | rupts and Exceptions                                     | 124 |

| 5.1      | Features                                                 | 124 |

| 5.2      | Interrupt Vector Table                                   | 124 |

| 6. Gen   | eral-Purpose I/O and Alternate Function Pins (GPIO)      | 128 |

| 6.1      | Instances                                                | 128 |

| 6.2      | Usage                                                    | 132 |

| 6.2.1    | Reset State                                              | 132 |

| 6.2.2    | Input Mode Configuration                                 | 132 |

| 6.2.3    | Output Mode Configuration                                | 132 |

| 6.2.4    | Alternate Function Configuration                         | 132 |

| 6.3      | Configuring GPIO (External) Interrupts                   | 132 |

| 6.3.1    | GPIO Interrupt Handling                                  | 133 |

| 6.3.2    | Using GPIO for Wake-up from Low Power Modes              | 133 |

| 6.4      | Registers                                                | 134 |

| 6.5      | Register Details                                         | 135 |

| 7. Flasł | n Controller (FLC)                                       | 143 |

| 7.1      | Instances                                                | 143 |

| 7.2      | Usage                                                    | 143 |

| 7.2.1    | Clock Configuration                                      | 144 |

| 7.2.2   | Lock Protection                           |     |

|---------|-------------------------------------------|-----|

| 7.2.3   | Flash Write Width                         | 144 |

| 7.2.4   | Flash Write                               | 144 |

| 7.2.5   | Page Erase                                | 145 |

| 7.2.6   | Mass Erase                                | 145 |

| 7.3     | Flash Error Correction Coding             | 145 |

| 7.4     | Flash Controller Registers                | 146 |

| 7.5     | Flash Controller Register Details         | 146 |

| 8. Exte | rnal Memory                               | 151 |

| 8.1     | Overview                                  | 151 |

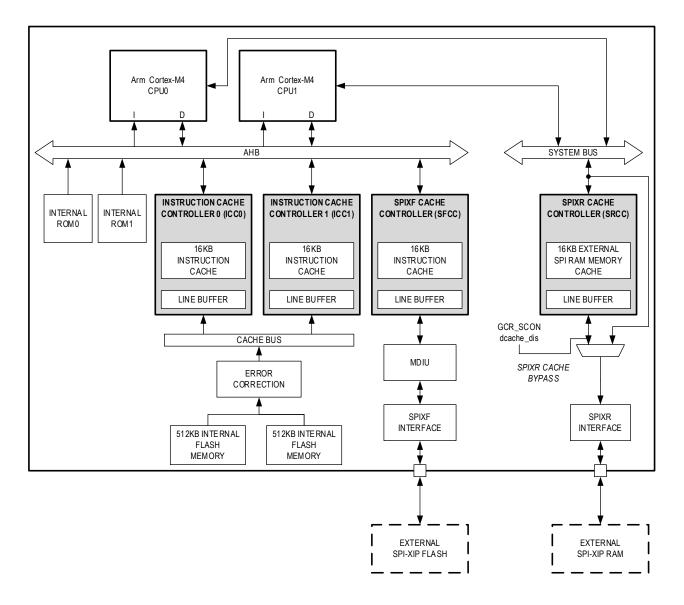

| 8.2     | SPI Execute-in-Place Flash (SPIXF)        | 151 |

| 8.2.1   |                                           |     |

| 8.2.2   | SPIXF Master                              | 166 |

| 8.3     | SPI Execute-in-Place RAM (SPIXR)          | 175 |

| 8.3.1   | SPIXR Master Controller Registers         | 176 |

| 8.3.2   | SPIXR Register Details                    | 176 |

| 8.4     | SPIXR Cache Controller (SRCC)             | 186 |

| 8.4.1   | Features                                  | 186 |

| 8.4.2   | Enabling the SRCC                         | 186 |

| 8.4.3   | Disabling the SRCC                        | 186 |

| 8.4.4   | SRCC Registers                            | 186 |

| 8.4.5   | SRCC Register Details                     | 187 |

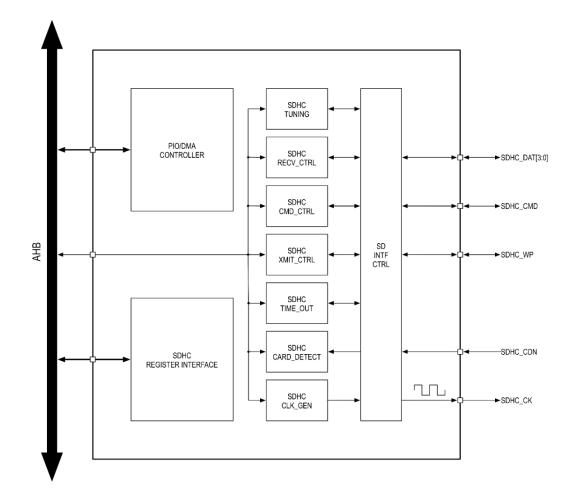

| 8.5     | Secure Digital Host Controller            | 188 |

| 8.5.1   | Instances                                 | 190 |

| 8.5.2   | SDHC Peripheral Clock Selection           | 191 |

| 8.5.3   | Usage                                     |     |

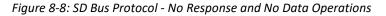

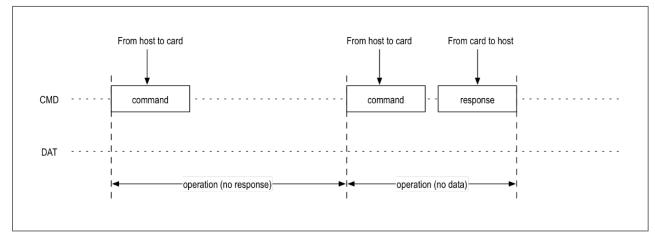

| 8.5.4   | SD Command Generation                     | 192 |

| 8.5.5   | SDHC Registers                            | 193 |

| 8.5.6   | SDHC Register Details                     | 195 |

| 9. Stan | dard DMA (DMA)                            | 232 |

| 9.1     | Instances                                 | 232 |

| 9.2     | DMA Channel Operation (DMA_CH)            | 233 |

| 9.2.1   | DMA Channel Arbitration and DMA Bursts    | 233 |

| 9.2.2   | DMA Source and Destination Addressing     | 233 |

| 9.2.3   | Data Movement from Source to DMA          | 234 |

| 9.2.4   | Data Movement from the DMA to Destination | 235 |

| 9.3   | Usage                                             | 235 |

|-------|---------------------------------------------------|-----|

| 9.4   | Count-to-Zero (CTZ) Condition                     | 236 |

| 9.5   | Chaining Buffers                                  | 236 |

| 9.6   | DMA Interrupts                                    | 238 |

| 9.7   | Channel Timeout Detect                            | 238 |

| 9.8   | Memory-to-Memory DMA                              | 239 |

| 9.9   | DMA Registers                                     | 239 |

| 9.10  | DMA Register Details                              | 239 |

| 9.11  | DMA Channel Register Summary                      | 239 |

| 9.12  | DMA Channel Registers                             | 240 |

| 9.13  | DMA Channel Register Details                      | 240 |

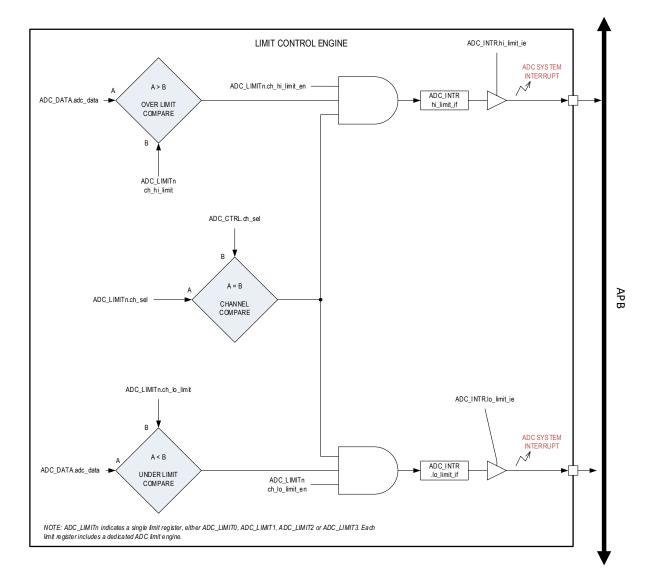

| 10. A | nalog-to-Digital Converter (ADC) and Comparators  | 245 |

| 10.1  | Features                                          |     |

| 10.2  | Instances                                         | 245 |

| 10.3  | Architecture                                      | 245 |

| 10.4  | Clock Configuration                               | 247 |

| 10.5  | Power-Up Sequence                                 | 247 |

| 10.6  | Conversion                                        | 248 |

| 10.7  | Reference Scaling and Input Scaling               | 248 |

| 10.7  |                                                   |     |

| 10.7  | .2 Scale Limitations for All Other Input Channels | 248 |

| 10.7  | .3 Data Conversion Output Alignment               | 249 |

| 10.7  | .4 Data Conversion Value Equations                | 249 |

| 10.7  |                                                   |     |

| 10.7  | .6 Power-Down Sequence                            | 252 |

| 10.8  | Comparator Operation                              |     |

| 10.9  | Registers                                         | 252 |

| 10.10 | Register Details                                  | 252 |

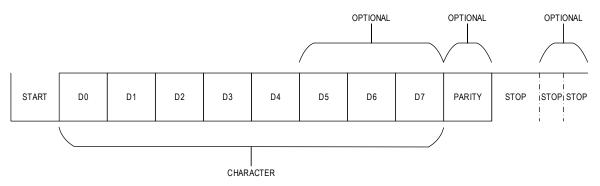

| 11. L | ART                                               | 257 |

| 11.1  | Instances                                         | 257 |

| 11.2  | UART Frame                                        | 257 |

| 11.3  | UART Interrupts                                   | 258 |

| 11.4  | UART Baud Rate Clock Source                       | 258 |

| 11.5  | UART Baud Rate Calculation                        | 258 |

| 11.6  | FIFOs                                             | 260 |

| 11.6.1 Transmit               | t FIFO Operation                                          | 260 |

|-------------------------------|-----------------------------------------------------------|-----|

| 11.6.2 Receive                | FIFO Operation                                            | 260 |

| 11.7 UART Cont                | figuration and Operation                                  | 260 |

| 11.8 Wake-up T                | Time                                                      | 261 |

| 11.9 Hardware                 | Flow Control                                              | 261 |

| 11.10 Registers -             |                                                           | 261 |

| 11.11 Register D              | etails                                                    | 262 |

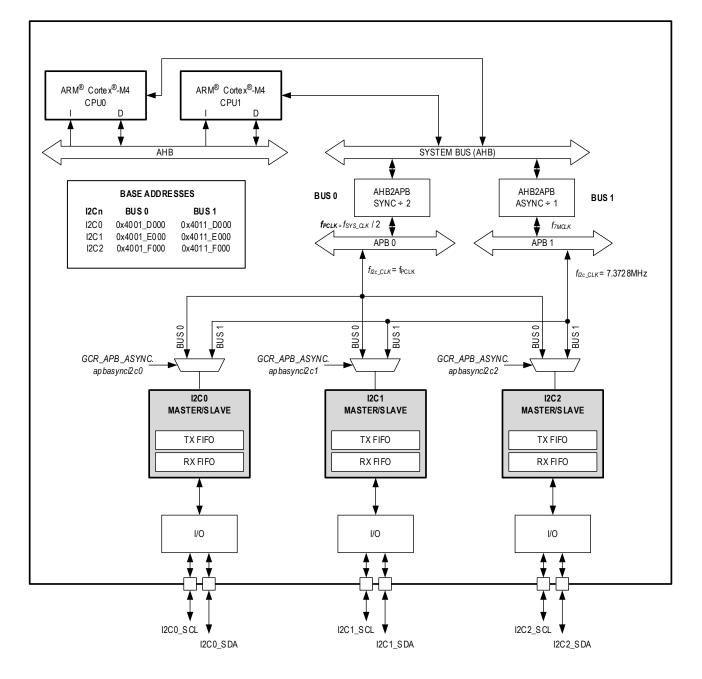

| 12. I <sup>2</sup> C Master/S | Slave Serial Communications Peripheral (I <sup>2</sup> C) | 270 |

|                               | r and Slave Features                                      |     |

|                               |                                                           |     |

|                               | ew                                                        |     |

|                               | Terminology                                               |     |

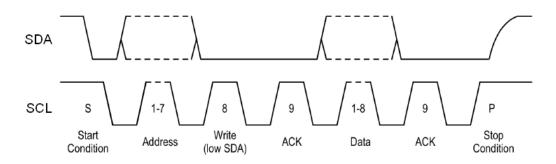

|                               | sfer Protocol Operation                                   |     |

|                               | nd STOP Conditions                                        |     |

|                               | Operation                                                 |     |

|                               | ledge and Not Acknowledge                                 |     |

|                               | sfer Process                                              |     |

|                               | uration and Usage                                         |     |

| -                             | SDA Bus Drivers                                           |     |

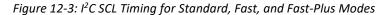

| 12.4.2 SCL Clock              | k Configurations                                          | 275 |

| 12.4.3 SCL Clock              | k Generation for Standard, Fast and Fast-Plus Modes       | 275 |

| 12.4.4 SCL Clock              | k Generation for Hs-Mode                                  | 276 |

| 12.4.5 Master I               | Mode Addressing                                           | 277 |

| 12.4.6 Master I               | Mode Operation                                            | 277 |

| 12.4.7 Slave Mo               | ode Operation                                             | 280 |

| 12.4.8 Interrup               | t Sources                                                 | 284 |

| 12.4.9 Transmit               | t FIFO and Receive FIFO                                   | 284 |

| 12.4.10 Trans                 | smit FIFO Preloading                                      | 285 |

| 12.4.11 Interd                | active Receive Mode (IRXM)                                | 286 |

| 12.4.12 Clock                 | Stretching                                                | 287 |

| 12.4.13 Bus T                 |                                                           | 287 |

| 12.4.14 DMA                   | Control                                                   | 288 |

| 12.5 Registers -              |                                                           | 288 |

| 12.6 Register D               | etails                                                    | 289 |

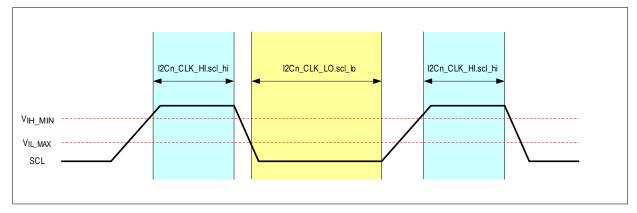

| 13. Serial Periph             | ieral Interface (SPI)                                     | 303 |

| 13.1 Instances-               |                                                           | 304 |

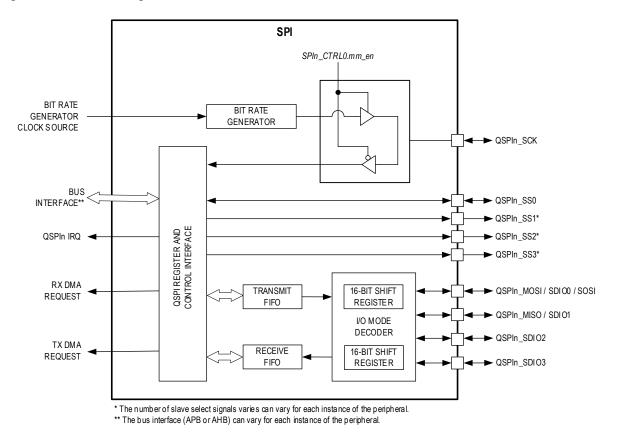

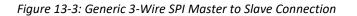

| 13.2 S   | PI Formats                          | 305 |

|----------|-------------------------------------|-----|

| 13.2.1   | Four-Wire SPI                       | 305 |

| 13.2.2   | Three-Wire SPI                      | 306 |

| 13.3 P   | in Configuration                    | 307 |

| 13.3.1   | SPIn Alternate Function Mapping     | 307 |

| 13.3.2   | Four-Wire Format Configuration      | 307 |

| 13.3.3   | Three-Wire Format Configuration     | 307 |

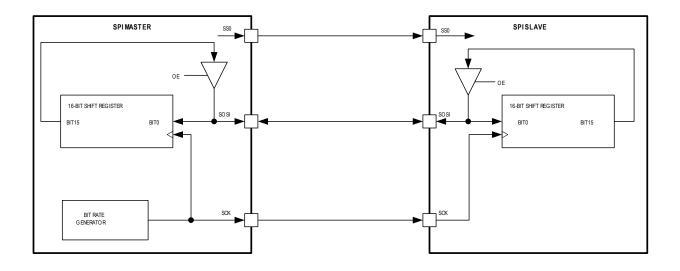

| 13.3.4   | Dual-Mode Format Configuration      | 308 |

| 13.3.5   | Quad-Mode Format Pin Configuration  | 308 |

| 13.4 S   | PI Clock Configuration              | 308 |

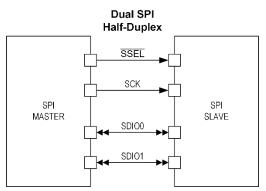

| 13.4.1   | Serial Clock                        | 308 |

| 13.4.2   | SPI Peripheral Clock                | 309 |

| 13.4.3   | Master Mode Serial Clock Generation | 309 |

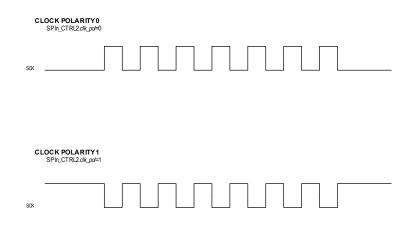

| 13.4.4   | Clock Phase and Polarity Control    | 309 |

| 13.4.5   | SPIn FIFOs                          | 310 |

| 13.4.6   | SPI Interrupts and Wakeups          | 310 |

| 13.5 R   | egisters                            | 311 |

| 13.6 R   | egister Details                     | 312 |

| 14. HTin | ner (HTMR)                          | 322 |

| 14.1 O   | verview                             | 322 |

| 14.2 A   | larm Functions                      | 322 |

| 14.2.1   | Long-Interval Alarm                 | 322 |

| 14.2.2   | Short-Interval Alarm                | 322 |

| 14.3 R   | egister Access Control              | 322 |

| 14.3.1   | Register Write Protection           | 323 |

| 14.3.2   | Register Read Protection            | 323 |

| 14.3.3   | Count Register Access               | 323 |

| 14.3.4   | Alarm Register Access               | 323 |

| 14.4 R   | egisters                            | 323 |

| 14.5 R   | egister Details                     | 324 |

| 15. Time | ers                                 | 326 |

| 15.1 F   | eatures                             | 326 |

| 15.2 B   | asic Operation                      | 326 |

| 15.3 T   | mer Pin Functionality               | 327 |

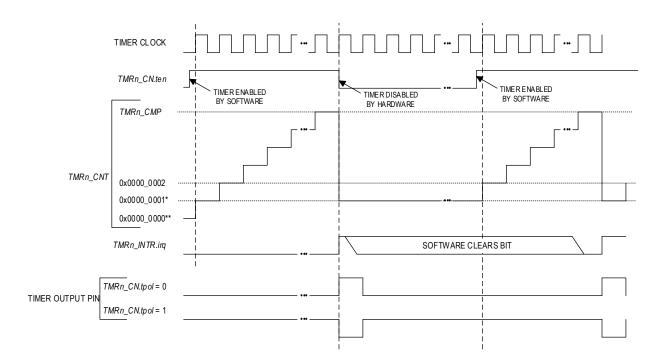

| 15.4 O   | ne-Shot Mode (0)                    | 327 |

| 15.4.1   | One-Shot Mode Timer Period          |     |

| 15.4.2 One-Shot Mode Configuration    | 328 |

|---------------------------------------|-----|

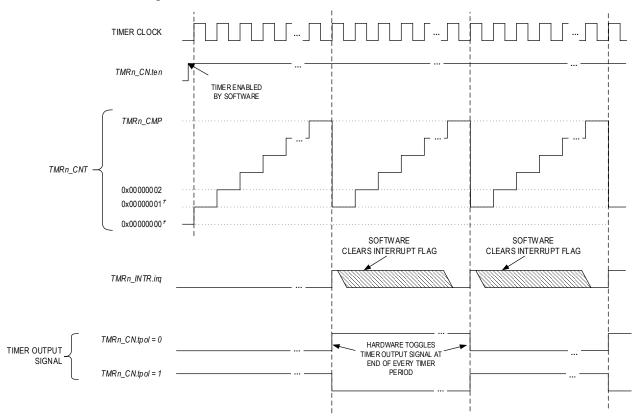

| 15.5 Continuous Mode (1)              | 328 |

| 15.5.1 Continuous Mode Timer Period   |     |

| 15.5.2 Continuous Mode Configuration  |     |

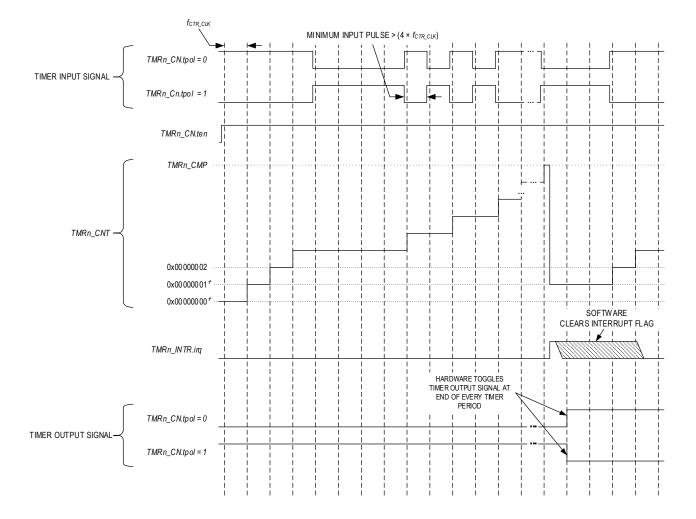

| 15.6 Counter Mode (2)                 | 330 |

| 15.6.1 Counter Mode Timer Period      | 331 |

| 15.6.2 Counter Mode Configuration     | 331 |

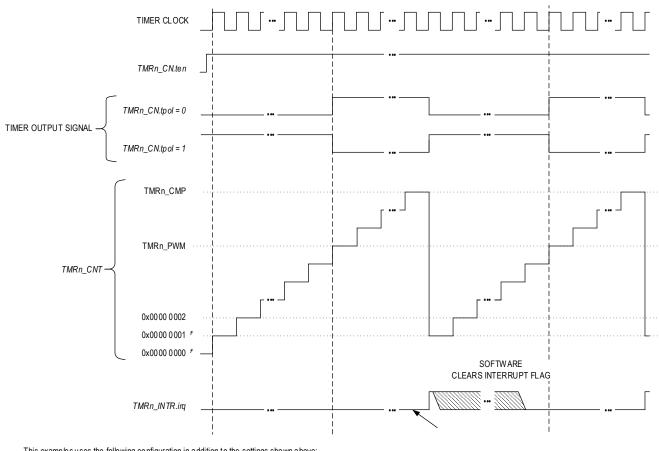

| 15.7 PWM Mode (3)                     | 332 |

| 15.7.1 PWM Mode Timer Period          | 332 |

| 15.7.2 PWM Mode Configuration         | 332 |

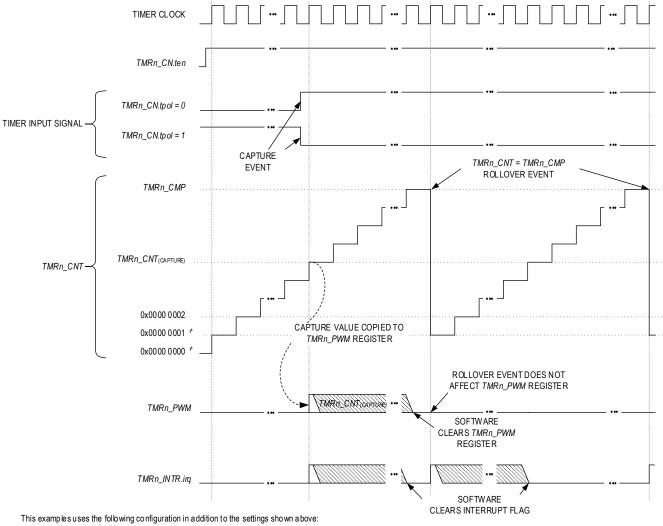

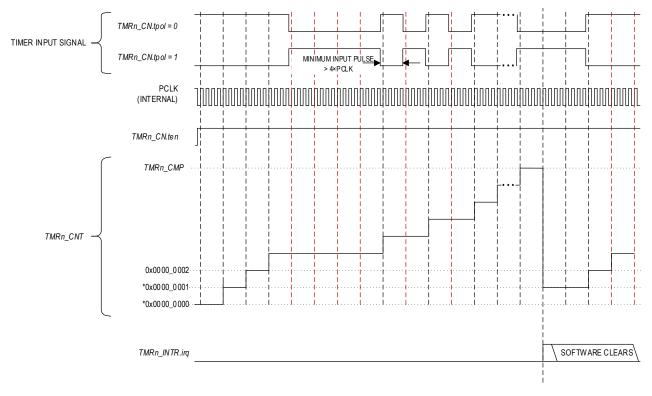

| 15.8 Capture Mode (4)                 | 334 |

| 15.8.1 Capture Mode Timer Period      | 335 |

| 15.8.2 Capture Mode Configuration     | 336 |

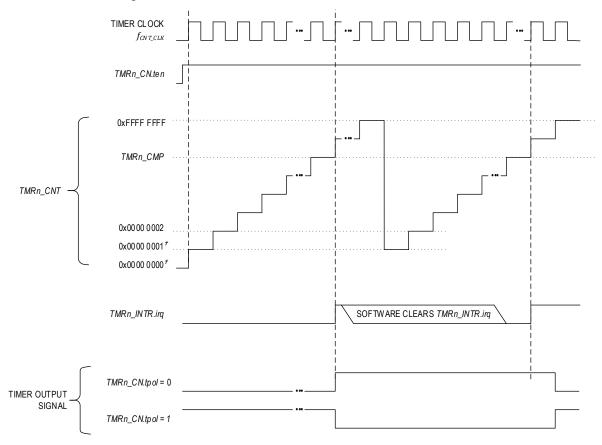

| 15.9 Compare Mode (5)                 | 336 |

| 15.9.1 Compare Mode Timer Period      | 337 |

| 15.9.2 Compare Mode Configuration     | 337 |

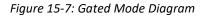

| 15.10 Gated Mode (6)                  | 338 |

| 15.10.1 Gated Mode Timer Period       | 339 |

| 15.10.2 Gated Mode Configuration      |     |

| 15.11 Capture/Compare Mode (7)        | 339 |

| 15.11.1 Capture/Compare Timer Period  | 340 |

| 15.11.2 Capture/Compare Configuration |     |

| 15.12 Registers                       | 341 |

| 15.13 Register Details                | 341 |

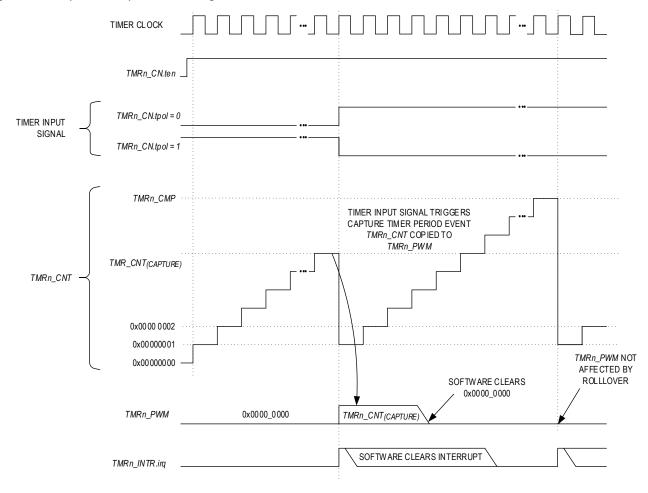

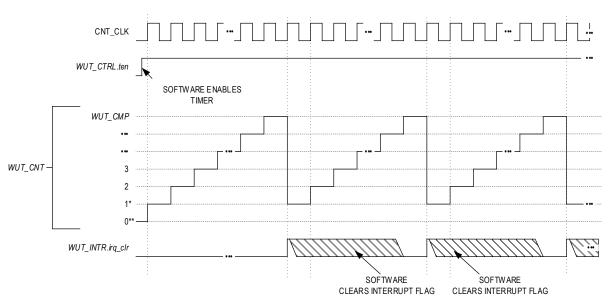

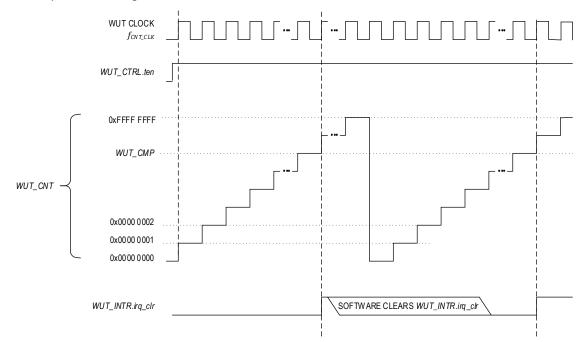

| 16. Wake-Up Timer (WUT0)              | 345 |

| 16.1 Basic Operation                  |     |

| 16.2 One-Shot Mode (000b)             |     |

| 16.2.1 One-Shot Mode Timer Period     |     |

| 16.2.2 One-Shot Mode Configuration    |     |

| 16.3 Continuous Mode (1)              |     |

| 16.3.1 Continuous Mode Timer Period   |     |

| 16.3.2 Continuous Mode Configuration  |     |

| 16.3.3 Compare Mode (5)               |     |

| 16.4 Registers                        |     |

| 16.5 Register Details                 |     |

|                                       |     |

| 17. Pulse Train Engine (PT)           | 352 |

| 17.1   | Instances                                        | 352 |

|--------|--------------------------------------------------|-----|

| 17.2   | Pulse Train Engine Features                      | 352 |

| 17.3   | Engine                                           | 352 |

| 17.3.  | 1 Pulse Train Output Modes                       | 353 |

| 17.4   | Enabling and Disabling a Pulse Train Output      | 354 |

| 17.5   | Atomic Pulse Train Output Enable and Disable     | 354 |

| 17.5.  | 1 Pulse Train Atomic Enable                      | 354 |

| 17.5.  | 2 Pulse Train Atomic Disable                     | 354 |

| 17.6   | Pulse Train Halt and Disable                     | 355 |

| 17.7   | Pulse Train Interrupts                           | 355 |

| 17.8   | Registers                                        | 355 |

| 17.9   | Register Details                                 | 357 |

| 17.9.  | 2 Pulse Train Engine Safe Enable Register        | 366 |

| 17.9.  | 3 Pulse Train Engine Safe Disable Register       | 367 |

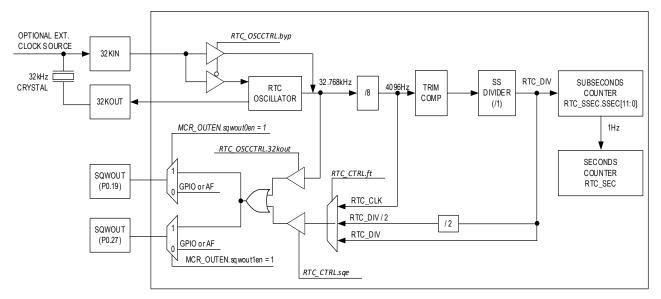

| 18. Re | eal-Time Clock (RTC)                             | 372 |

| 18.1   | Overview                                         | 372 |

| 18.2   | Instances                                        | 372 |

| 18.3   | Register Access Control                          | 373 |

| 18.3.  | 1 RTC_SEC and RTC_SSEC Read Access Control       | 373 |

| 18.3.  | 2 RTC Write Access Control                       | 374 |

| 18.4   | RTC Alarm Functions                              | 374 |

| 18.4.  | 1 Time-of-Day Alarm                              | 374 |

| 18.4.  | 2 Sub-Second Alarm                               | 374 |

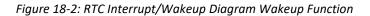

| 18.4.  | 3 RTC Interrupt and Wakeup Configuration         | 375 |

| 18.4.  | 4 Square-Wave Output                             | 375 |

| 18.5   | RTC Calibration                                  | 376 |

| 18.6   | Registers                                        | 378 |

| 18.7   | Register Details                                 | 378 |

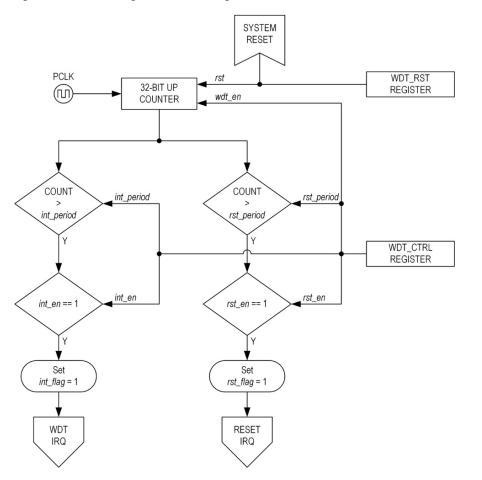

| 19. W  | 'atchdog Timer (WDT)                             | 382 |

| 19.1   | Features                                         | 382 |

| 19.2   | Usage                                            | 382 |

| 19.3   | Interrupt and Reset Period Timeout Configuration | 383 |

| 19.4   | Timed Access Protection                          | 384 |

| 19.5   | Enabling the Watchdog Timer                      | 384 |

| 19.5.  |                                                  |     |

|        |                                                  |     |

| 19.6 Disabling the Watchdog Timer                     | 384 |

|-------------------------------------------------------|-----|

| 19.6.1 Manual Disable                                 | 384 |

| 19.6.2 Automatic Disable                              | 384 |

| 19.7 Resetting the Watchdog Timer                     | 384 |

| 19.7.1 Reset Sequence                                 | 384 |

| 19.8 Detection of a Watchdog Reset Event              | 384 |

| 19.9 Registers                                        | 384 |

| 19.10 Register Details                                | 385 |

| 20. Semaphores                                        | 387 |

| 20.1 Instances                                        |     |

| 20.2 Multiprocessor Communications                    |     |

| 20.2.1 Reset                                          |     |

| 20.2.1 Registers                                      |     |

|                                                       |     |

|                                                       |     |

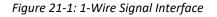

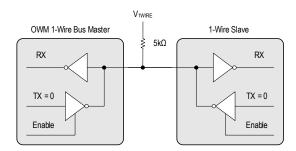

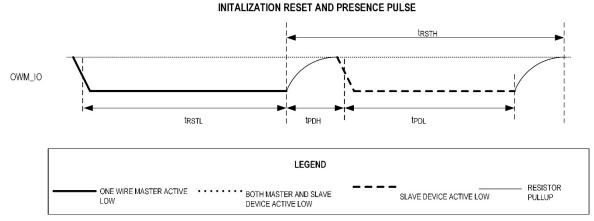

| 21. 1-Wire Master (OWM)                               |     |

| 21.1 Instances                                        | 391 |

| 21.2 Pins and Configuration                           | 392 |

| 21.2.1 Pin Configuration                              | 392 |

| 21.2.2 1-Wire I/O (OWM_IO)                            | 392 |

| 21.2.3 Pullup Enable (OWM_PE)                         | 392 |

| 21.2.4 Clock Configuration                            | 392 |

| 21.3 1-Wire Protocol                                  | 393 |

| 21.3.1 Networking Layers                              | 393 |

| 21.3.2 Read ROM Command                               | 397 |

| 21.3.3 Skip ROM and Overdrive Skip ROM Commands       | 397 |

| 21.3.4 Match ROM and Overdrive Match ROM Commands     | 398 |

| 21.3.5 Search ROM Command                             |     |

| 21.3.6 Search ROM Accelerator Operation               | 398 |

| 21.3.7 Resume Communication Command                   | 399 |

| 21.4 1-Wire Operation                                 | 399 |

| 21.4.1 Resetting the OWM                              | 399 |

| 21.5 1-Wire Data Reads                                | 400 |

| 21.5.1 Reading a Single Bit Value from the 1-Wire Bus | 400 |

| 21.5.2 Reading an 8-Bit Value from the 1-Wire Bus     | 400 |

| 21.6 Registers                                        | 400 |

| 21.7 Register Details                                 | 401 |

| 22. U | ISB 2.0 High-Speed (USBHS) Host Interface with PHY    | 405 |

|-------|-------------------------------------------------------|-----|

| 22.1  | Instances                                             | 405 |

| 22.2  | USBHS Bus Signals                                     | 406 |

| 22.3  | USBHS Device Endpoints                                | 407 |

| 22.4  | USBHS Reset and Clock                                 | 407 |

| 22.5  | USBHS SUSPEND Mode and RESUME States                  | 408 |

| 22.6  | Packet Size                                           | 408 |

| 22.7  | Endpoint 0 Control Transactions                       | 408 |

| 22.7  | .1 Endpoint 0 Error Handling                          | 408 |

| 22.8  | Bulk Endpoints Operation and Options                  | 408 |

| 22.8  | 8.1 Bulk IN Endpoints                                 | 408 |

| 22.8  | B.2 Bulk OUT Endpoints                                | 409 |

| 22.9  | Interrupt Endpoints                                   | 409 |

| 22.9  | 0.1 Interrupt IN Endpoints                            | 409 |

| 22.9  | 0.2 Interrupt OUT Endpoints                           | 410 |

| 22.10 | Isochronous Endpoints                                 | 410 |

| 22.1  | 0.1 Isochronous IN Endpoints                          | 410 |

| 22.1  | 0.2 Isochronous OUT Endpoints                         | 410 |

| 22.11 | USBHS Device Registers                                | 411 |

| 22.12 | USBHS Device Register Details                         | 413 |

| 22.1  | 2.2 Endpoint Register Access Control                  | 420 |

| 22.1  | 2.3 USBHS IN Endpoint Maximum Packet Size Registers   | 420 |

| 22.1  |                                                       |     |

| 22.1  |                                                       |     |

| 22.1  | 2.6 USBHS IN Endpoint Upper Control Registers         | 423 |

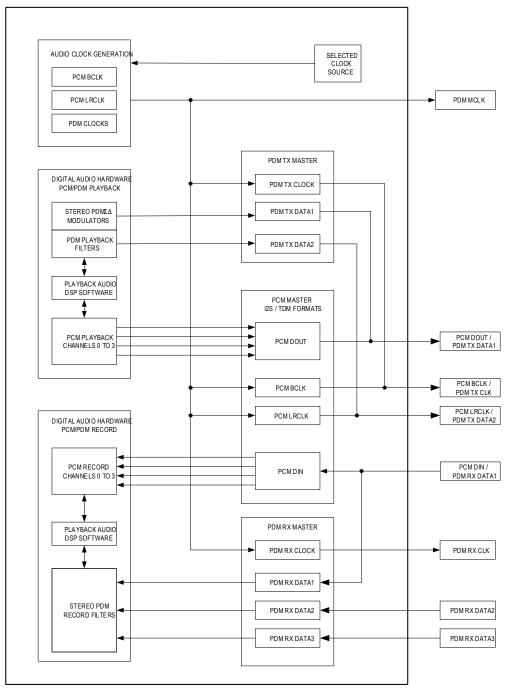

| 23. A | udio Subsystem                                        | 434 |

| 23.1  | Instances                                             | 435 |

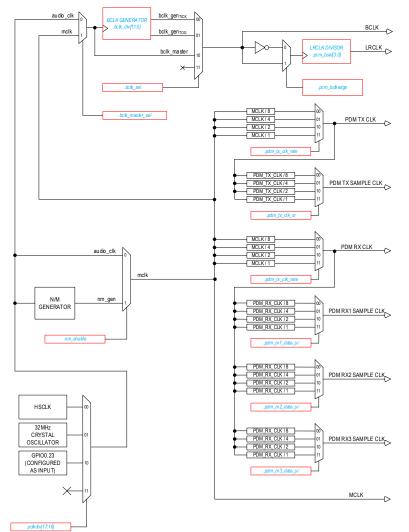

| 23.2  | Clocking                                              | 436 |

| 23.2  | 2.1 Setting the Master Clock for the Audio Peripheral | 438 |

| 23.3  | FIFO and Data Management                              | 438 |

| 23.4  | PCM Master Interface                                  | 439 |

| 23.4  | PCM Master Interface Clock Configuration              | 439 |

| 23.4  | 2.2 Setting the Sample Rate for PCM Mode              | 439 |

| 23.4  | PCM Data Sample Rate and Clock Ratio Configuration    | 440 |

| 23.5  | I <sup>2</sup> S Mode Operation                       | 440 |

| 23.6  | PCM Slave Interface Internal Data Routing             | 441 |

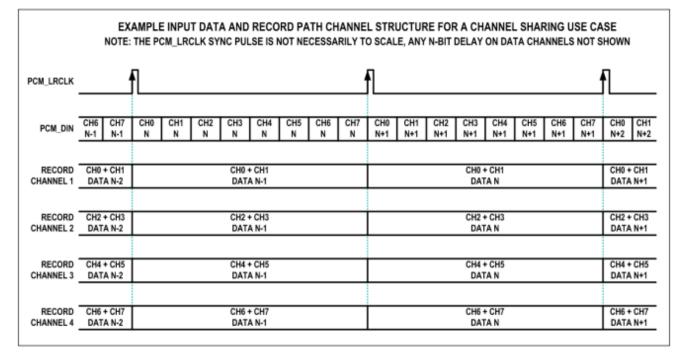

| 23.6                | E.1 PCM Input Data Channel Sharing (PCM_DIN)                                      | 441 |

|---------------------|-----------------------------------------------------------------------------------|-----|

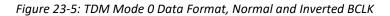

| 23.7                | TDM Mode Operation                                                                | 443 |

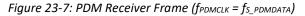

| 23.8                | PDM Master Interface Transmitter (Tx) and Receiver (Rx)                           | 445 |

| 23.8                | P.1 PDM Master Interface Operation in PDM Mode                                    | 445 |

| 23.8                | P.2 PDM Master Interface Operation in PCM Mode                                    | 446 |

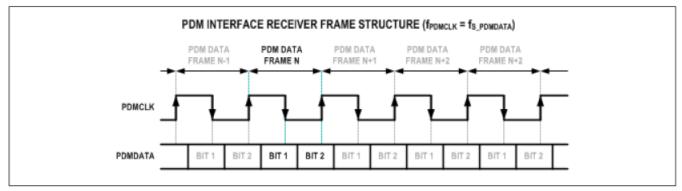

| 23.9                | PDM Master Interface Data Encoding Format                                         | 446 |

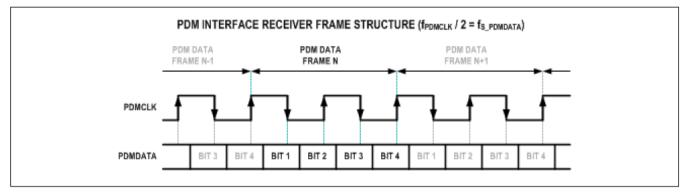

| 23.9                | .1 PDM Master Interface General Frame Structure                                   | 446 |

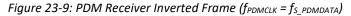

| 23.9                | 2.2 PDM Master Interface Inverted Frame Structure                                 | 447 |

| 23.9                | P.3 PDM Master Interface Automatic Frame Alignment and Synchronization (Receiver) | 447 |

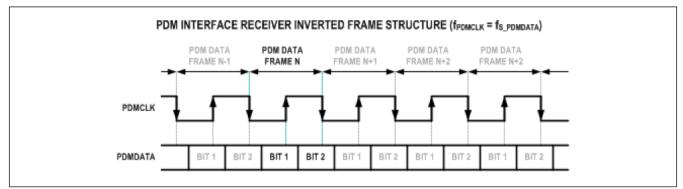

| 23.9                | .4 PDM Master Interface: All Supported Frame Structures                           | 447 |

| 23.10               | Registers                                                                         | 450 |

| 23.11               | Register Details                                                                  | 452 |

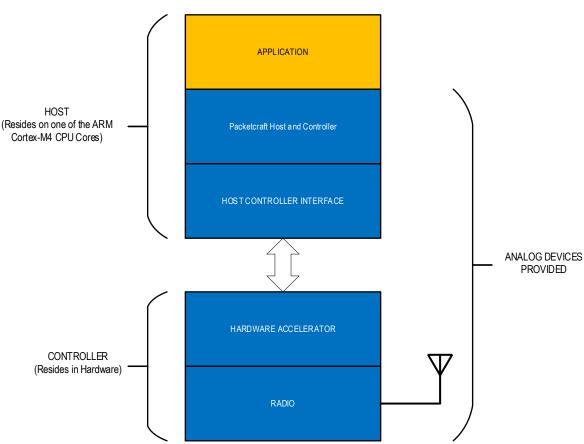

| 24. B               | luetooth 5 Low Energy (LE) Radio                                                  | 481 |

| 24.1                | Power-Efficient Design                                                            |     |

| 24.2                | Bluetooth Hardware Accelerator                                                    |     |

| 24.3                | Packetcraft Software Stack                                                        | 481 |

| 24.4                | Pins                                                                              | 483 |

| 24.5                | Configuration                                                                     |     |

| 24.6                | Documentation                                                                     |     |

|                     | rust Protection Unit (TPU)                                                        |     |

|                     |                                                                                   |     |

| 25.1<br><i>25.1</i> | Dedicated Cryptographic DMA Engine (CDMA)                                         |     |

| 25.1                |                                                                                   |     |

| 25.1                |                                                                                   |     |

|                     | Block Cipher Accelerator                                                          |     |

| 25.2                |                                                                                   |     |

| 25.2                |                                                                                   |     |

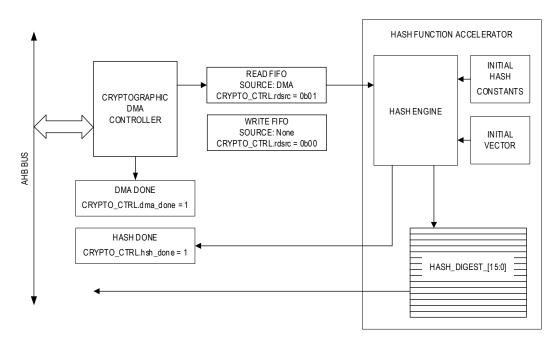

| 25.3                | Hash Function Accelerator                                                         |     |

| 25.3                |                                                                                   |     |

| 25.4                | Hamming Code Accelerator                                                          |     |

| 25.5                | Modular Arithmetic Accelerator                                                    |     |

| 25.5                |                                                                                   |     |

| 25.5                | -                                                                                 |     |

| 25.6                | Cyclic Redundancy Check (CRC) Engine                                              |     |

| 25.7                | Instances                                                                         |     |

|                     |                                                                                   |     |

| 25.8   | Linear Feedback Shift Register (LFSR)           | 498 |

|--------|-------------------------------------------------|-----|

| 25.9   | True Random Number Generation                   | 498 |

| 25.10  | Registers                                       | 498 |

| 25.10  | 0.1 Write Access                                | 499 |

| 25.10  | 0.2 Read Access                                 | 499 |

| 25.11  | Registers                                       | 499 |

| 25.12  | Register Details                                | 500 |

| 26. Se | ecure Communication Protocol Bootloader (SCPBL) | 512 |

| 26.1   | Development Tools                               | 512 |

| 26.2   | Instances                                       | 512 |

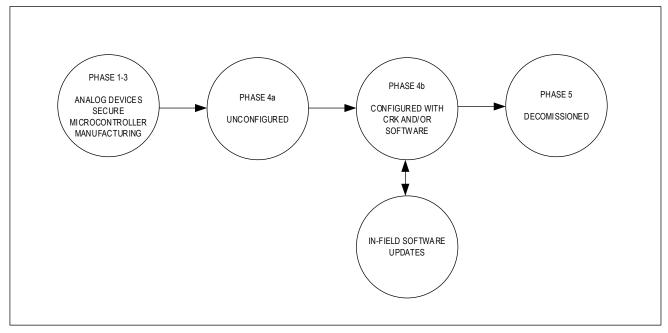

| 26.3   | Secure Product Life Cycle Management            | 513 |

| 26.3.  | 1 Purpose                                       | 513 |

| 26.3.  | 2 Life Cycle Phases                             | 513 |

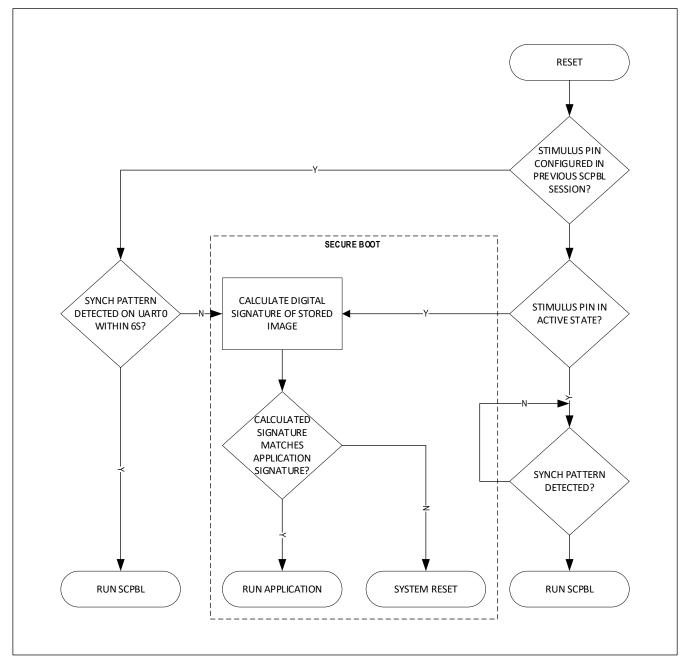

| 26.4   | MAX32666 Bootloader Activation                  | 514 |

| 26.5   | Secure Boot                                     | 516 |

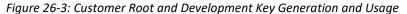

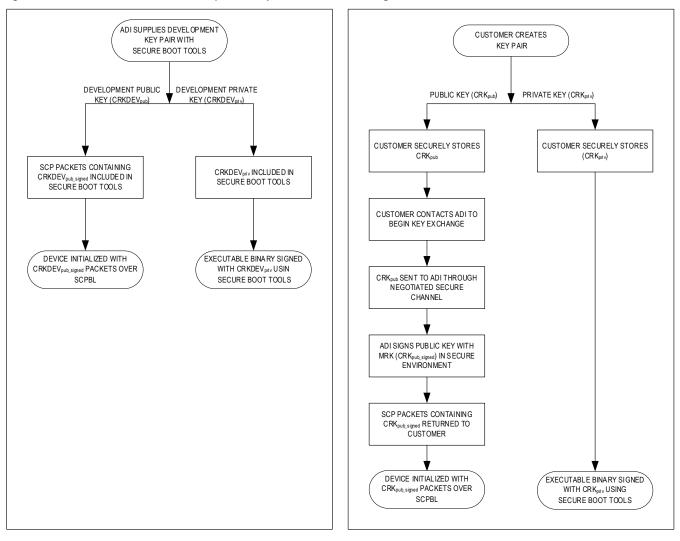

| 26.6   | Root Key Management                             | 516 |

| 26.6.  | 1 Manufacturer Root Key (MRK)                   | 516 |

| 26.6.  | 2 Customer Root Key (CRK)                       | 516 |

| 26.6.  | 3 Developer/Test CRK (DCRK)                     | 516 |

| 26.7   | MAX32666 Checksum/Signature Options             | 518 |

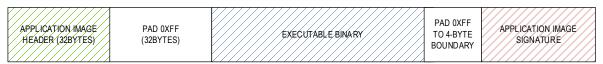

| 26.8   | Building the MAX32666 Application Image         | 519 |

| 26.9   | Selecting the Programming Interface             | 520 |

| 26.10  | SCP Session                                     | 520 |

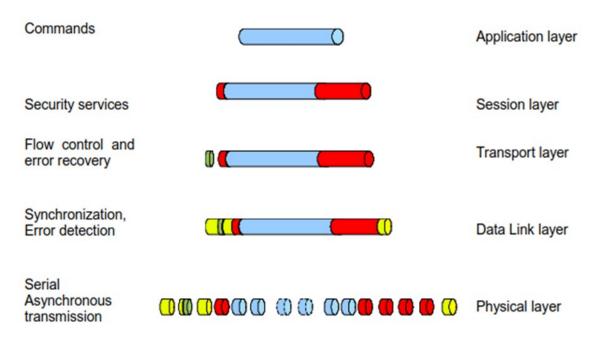

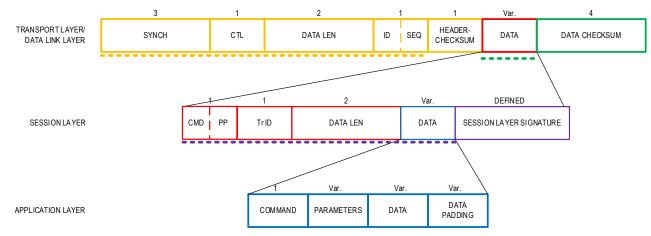

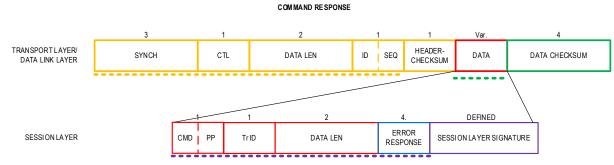

| 26.10  | 0.1 Physical Layer                              | 522 |

| 26.10  | 0.2 Data Link Layer                             | 522 |

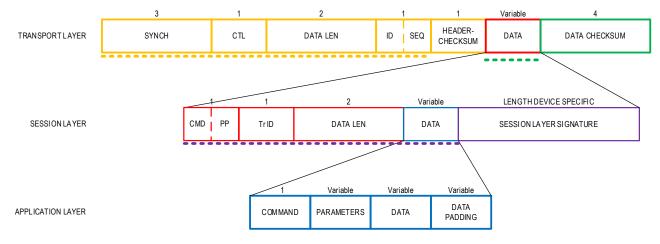

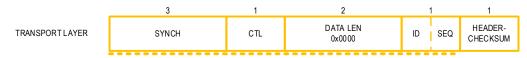

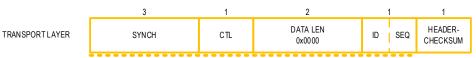

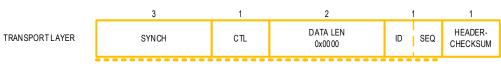

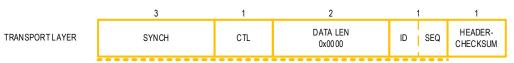

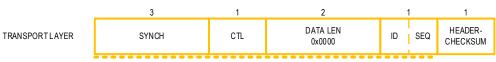

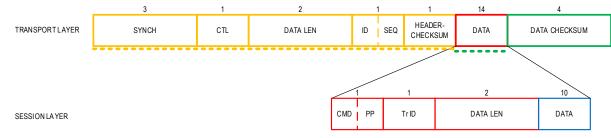

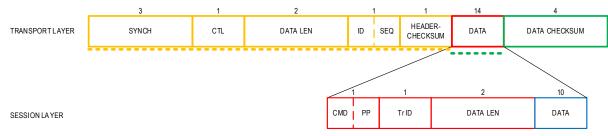

| 26.10  | 0.3 Transport Layer                             | 522 |

| 26.10  | 0.4 Session Layer                               | 522 |

| 26.11  | Sequence and Transaction ID                     | 522 |

| 26.12  | Opening an SCP Session                          | 524 |

| 26.13  | Transport/Session Layer Commands                | 525 |

| 26.14  | Transport/Session Layer Command Details         | 526 |

| 26.14  |                                                 |     |

| 26.14  |                                                 |     |

| 26.14  | _                                               |     |

| 26.14  | _                                               |     |

| 26.14  | _                                               |     |

| 26.14.6     | HELLO                             | 531 |

|-------------|-----------------------------------|-----|

| 26.14.7     | HELLO_REPLY                       | 533 |

| 26.15 Data  | Transfer Command Details          | 535 |

| 26.15.1     | WRITE_DATA                        | 535 |

| 26.15.2     | COMMAND_RSP                       | 537 |

| 26.16 Appl  | ication Layer Commands            | 538 |

| 26.16.1     | Application Layer Command Details | 539 |

| 26.16.2     | EXECUTE_CODE                      | 550 |

| 27. Debug   | Access Port (DAP)                 | 551 |

| 27.1 Insta  | nces                              | 551 |

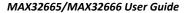

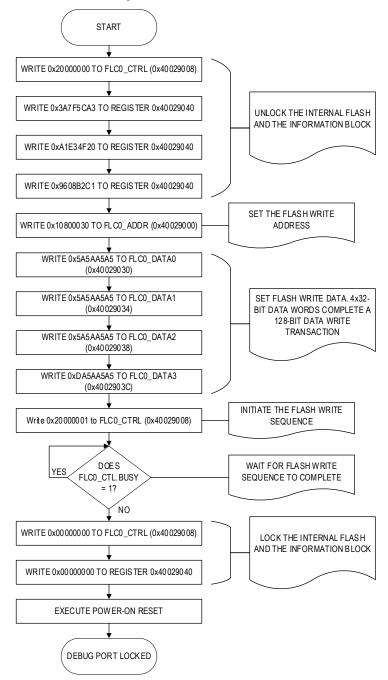

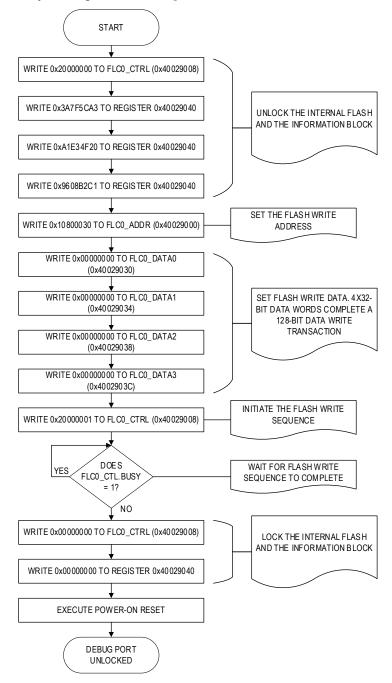

| 27.2 DAP    | Access Control                    | 551 |

| 1.1.1 Lo    | cking the DAP                     | 551 |

| 27.3 Pin C  | Configuration                     | 554 |

| 28. Revisio | n History                         | 556 |

# List of Figures

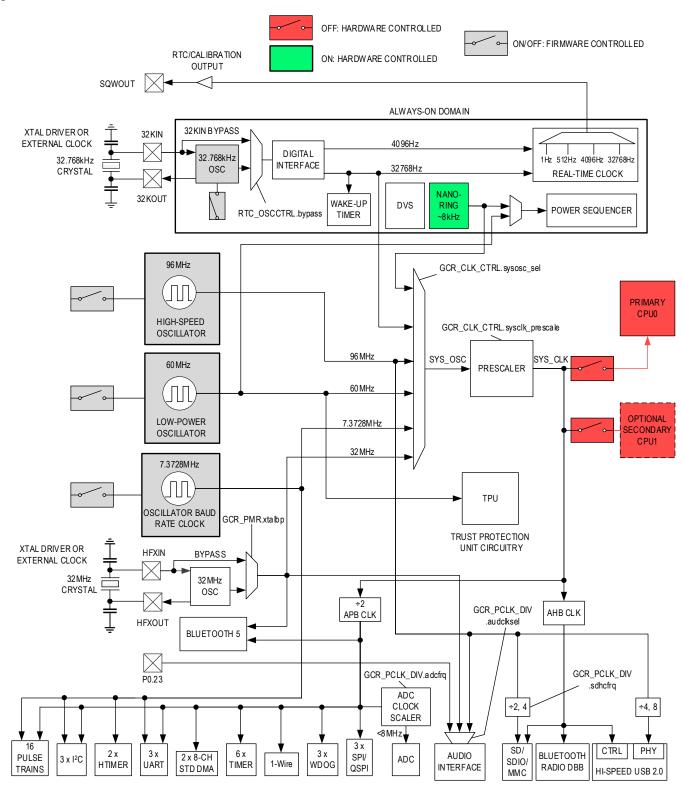

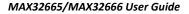

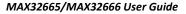

| Figure 1-1: MAX32665/MAX32666 Block Diagram                                      |     |

|----------------------------------------------------------------------------------|-----|

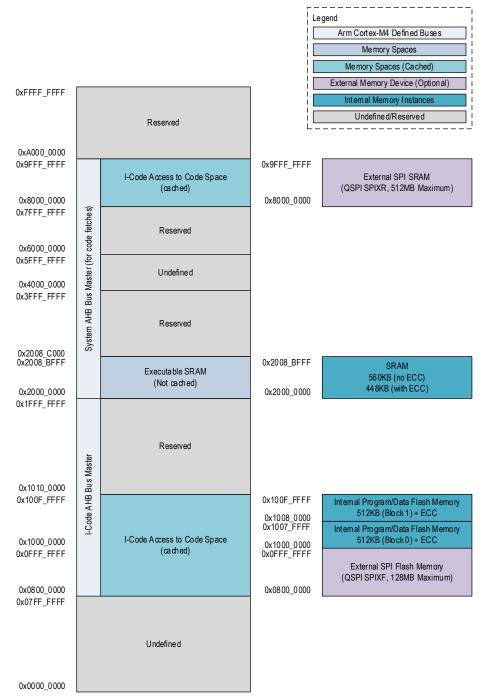

| Figure 3-1: Code Memory Mapping                                                  |     |

| Figure 3-2: Data Memory Mapping                                                  | 42  |

| Figure 3-3: Unique Serial Number Format                                          | 47  |

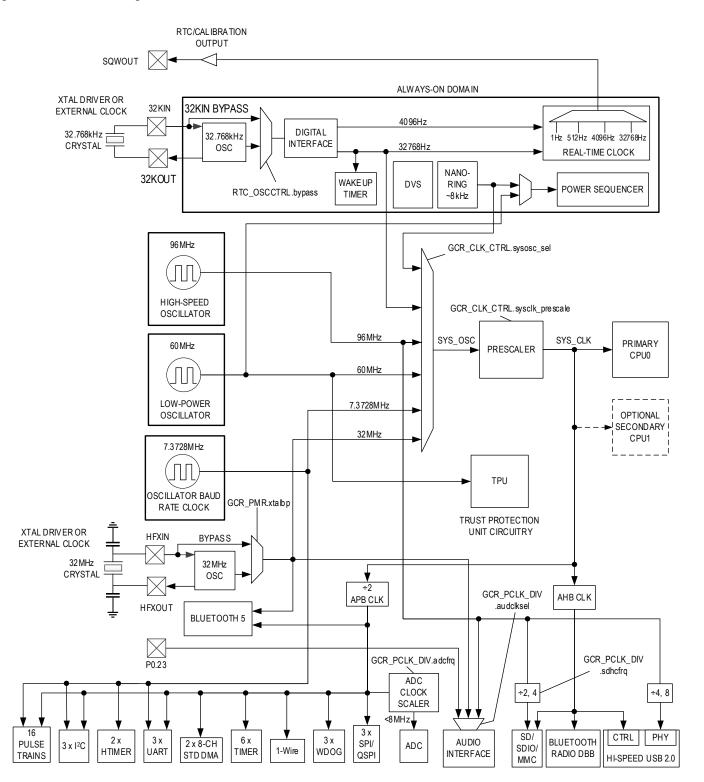

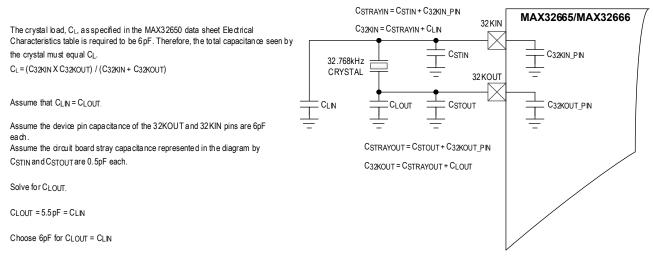

| Figure 4-1: Clock Block Diagram                                                  | 54  |

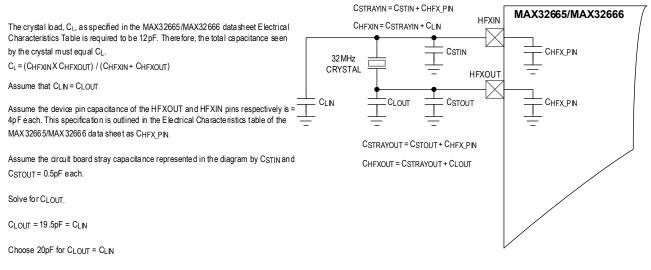

| Figure 4-2: Example 32MHz Crystal Capacitor Determination                        | 56  |

| Figure 4-3: Example 32.768kHz Crystal Capacitor Determination                    | 57  |

| Figure 4-4: SLEEP Mode Clock Control                                             | 59  |

| Figure 4-5: DEEPSLEEP Clock Control                                              |     |

| Figure 4-6: BACKUP Mode Clock Control                                            |     |

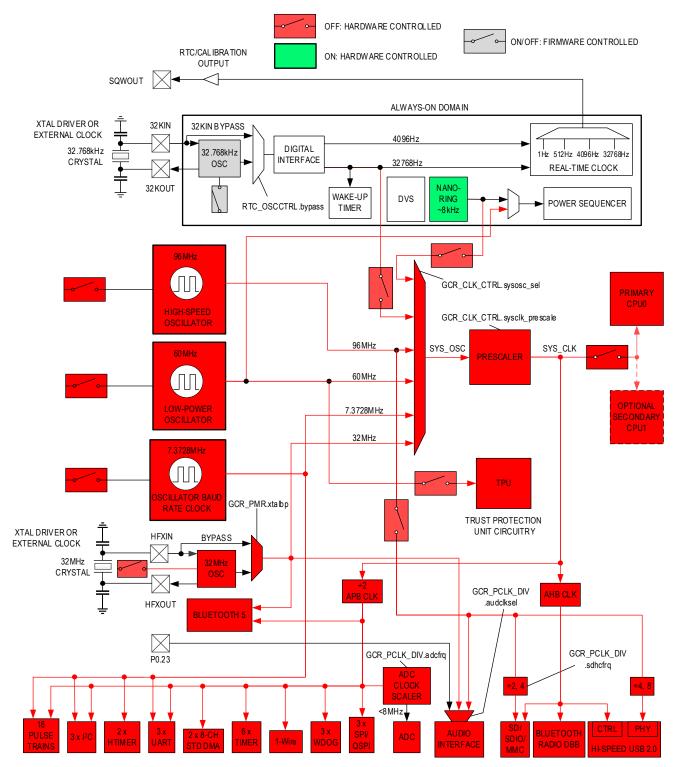

| Figure 4-7: MAX32665/MAX32666 Cache Controllers Control                          | 67  |

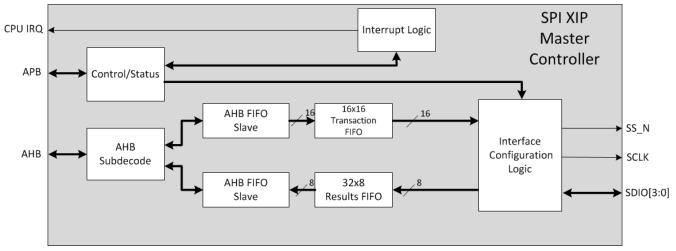

| Figure 8-1: Simplified SPIXF Block Diagram                                       | 152 |

| Figure 8-2: Simplified Block Diagram                                             | 153 |

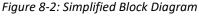

| Figure 8-3: SPIXFC Transaction Delay                                             | 157 |

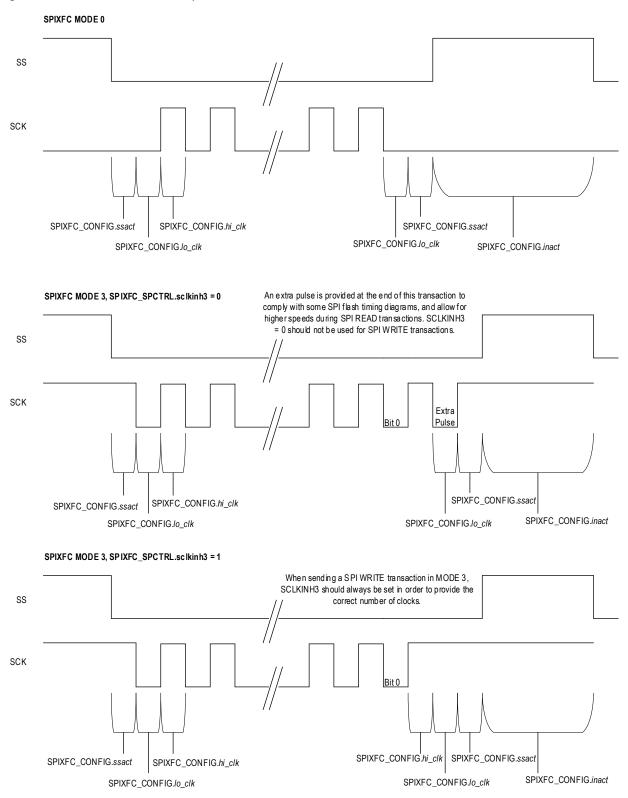

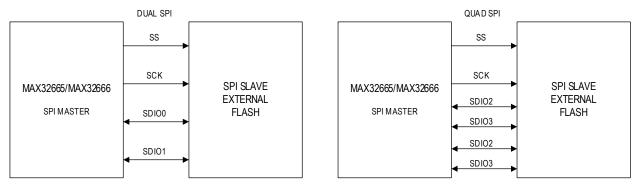

| Figure 8-4: Supported SPI configuration                                          | 167 |

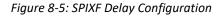

| Figure 8-5: SPIXF Delay Configuration                                            |     |

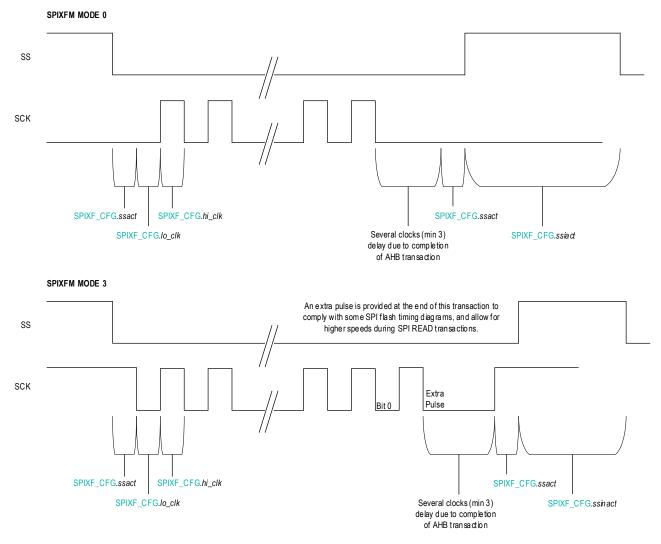

| Figure 8-6: Simplified SPIXR Block Diagram                                       | 175 |

| Figure 8-7: SDHC Block Diagram                                                   | 190 |

| Figure 8-8: SD Bus Protocol - No Response and No Data Operations                 | 191 |

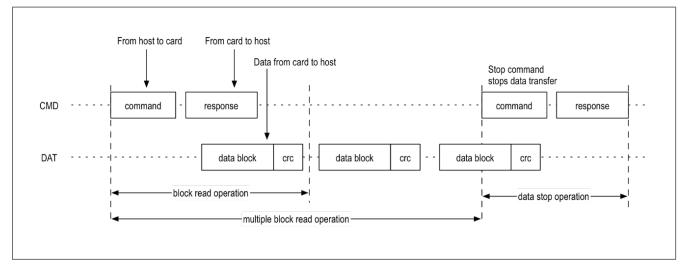

| Figure 8-9: SD Bus Protocol - Multi-Block Read Operation                         | 192 |

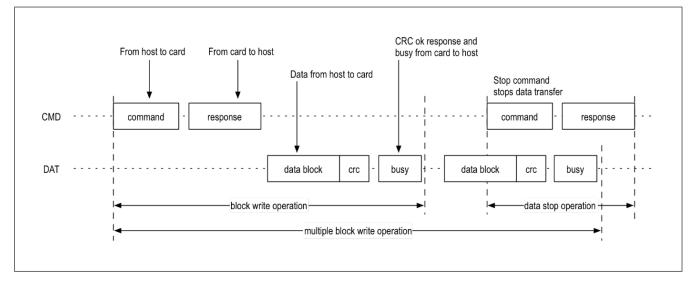

| Figure 8-10: SD Bus Protocol - Multi Block Write Operation                       | 192 |

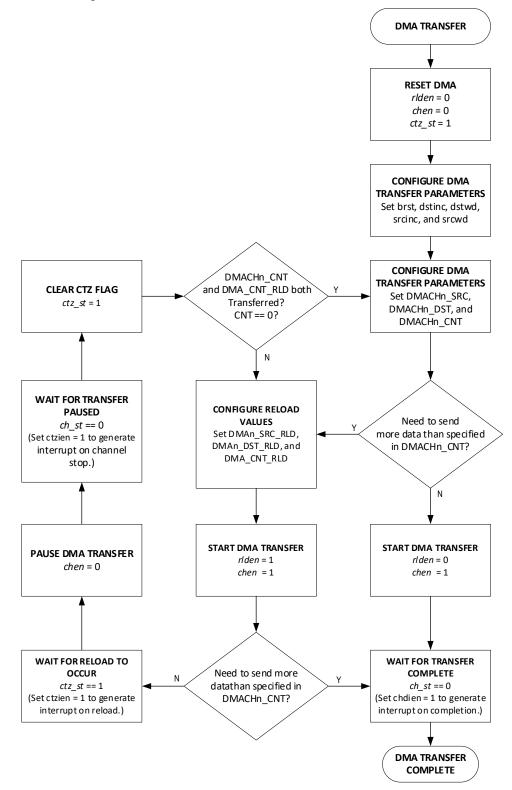

| Figure 9-1: DMA Block-Chaining Flowchart                                         | 237 |

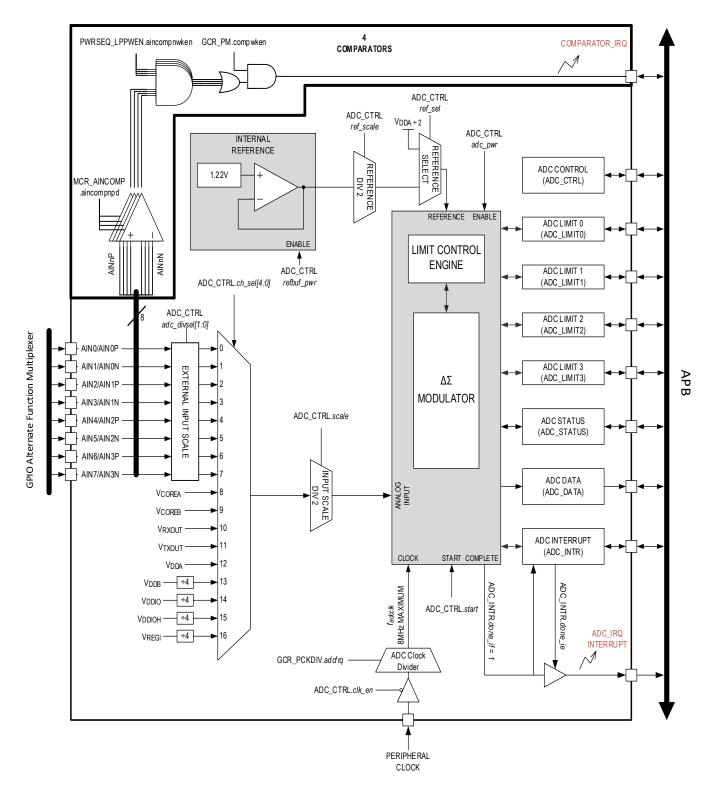

| Figure 10-1: Analog to Digital Converter Block Diagram                           |     |

| Figure 10-2: ADC Limit Engine                                                    | 251 |

| Figure 11-1: UART Frame Diagram                                                  |     |

| Figure 12-1: I <sup>2</sup> C Block Diagram                                      |     |

| Figure 12-2: I <sup>2</sup> C Write Data Transfer                                |     |

| Figure 12-3: I <sup>2</sup> C SCL Timing for Standard, Fast, and Fast-Plus Modes |     |

| Figure 13-1: SPI Block Diagram                                                   |     |

| Figure 13-2: 4-Wire SPI Connection Diagram                                       |     |

| Figure 13-3: Generic 3-Wire SPI Master to Slave Connection                       |     |

| Figure 13-4: Dual-Mode SPI Connection Diagram                                    |     |

| Figure 13-5: SCK Clock Rate Control                                              |     |

| Figure 13-6: SPI Clock Polarity                                                  |     |

| Figure 15-1: One-Shot Mode Diagram                                               |     |

| Figure 15-2: Continuous Mode Diagram                                             |     |

| Figure 15-3: Counter Mode Diagram                                                |     |

| Figure 15-4: PWM Mode Diagram                                                    |     |

| Figure 15-5: Capture Mode Diagram                                                |     |

| Figure 15-6: Counter Mode Diagram                                                |     |

| Figure 15-7: Gated Mode Diagram                                                  |     |

| Figure 15-8: Capture/Compare Mode Diagram                                        |     |

| Figure 16-1: One-Shot Mode Diagram                                               |     |

| Figure 16-2: Continuous Mode Diagram                                             |     |

| Figure 16-3: Compare Mode Diagram                                                |     |

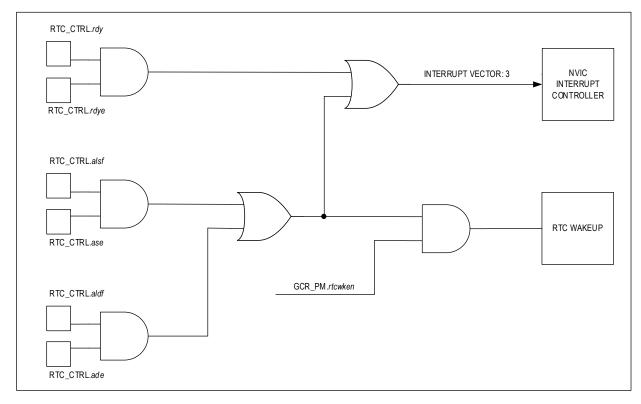

| Figure 18-1: MAX32665/MAX32666 RTC Block Diagram (12-bit Sub-Second Counter)     |     |

| Figure 18-2: RTC Interrupt/Wakeup Diagram Wakeup Function                        |     |

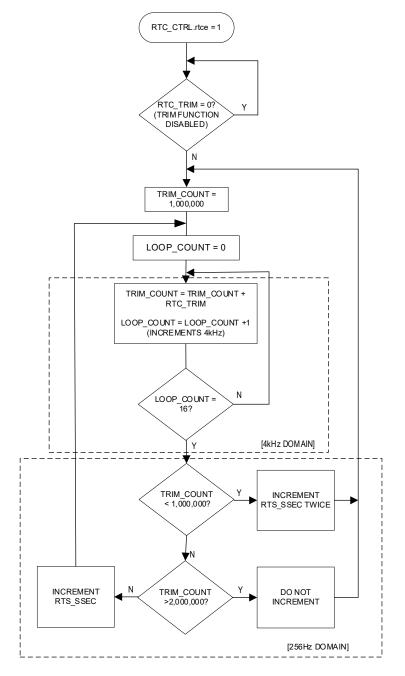

| Figure 18-3: Internal Implementation of Digital Trim, 4kHz                       |     |

| Figure 19-1: Watchdog Timer Block Diagram                                        |     |

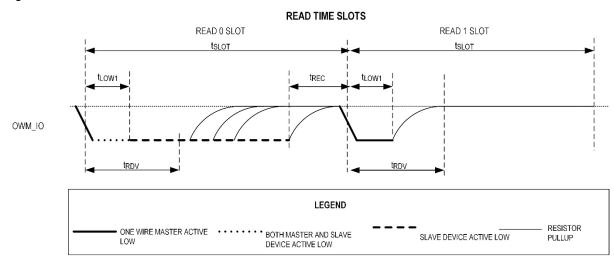

| Figure 21-1: 1-Wire Signal Interface                                                                                | 303 |

|---------------------------------------------------------------------------------------------------------------------|-----|

| Figure 21-2: 1-Wire Beset Pulse                                                                                     |     |

| Figure 21-3: 1-Wire Write Time Slot                                                                                 |     |

| Figure 21-4: 1-Wire Read Time Slot                                                                                  |     |

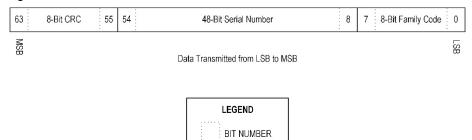

| Figure 21-5: 1-Wire ROM ID Fields                                                                                   |     |

| Figure 23-1: Audio Subsystem Block Diagram                                                                          |     |

| Figure 23-2: Audio Subsystem Clock Tree                                                                             |     |

| Figure 23-3: Standard I <sup>2</sup> S Mode Data Format Example (16-bit Audio Data Word, 24-bit Channel Length)     |     |

| Figure 23-4: PCM Channel Sharing Example                                                                            |     |

| Figure 23-5: TDM Mode 0 Data Format, Normal and Inverted BCLK                                                       |     |

| Figure 23-6: TDM Mode 1 and Mode 2                                                                                  |     |

| Figure 23-7: PDM Receiver Frame (f <sub>PDMCLK</sub> = fs_PDMDATA)                                                  |     |

| Figure 23-8: PDM Receiver Frame (f <sub>PDMCLK</sub> / 2 = f <sub>S_PDMDATA</sub> )                                 |     |

| Figure 23-9: PDM Receiver Inverted Frame (fPDMCLK = fs_PDMDATA)                                                     |     |

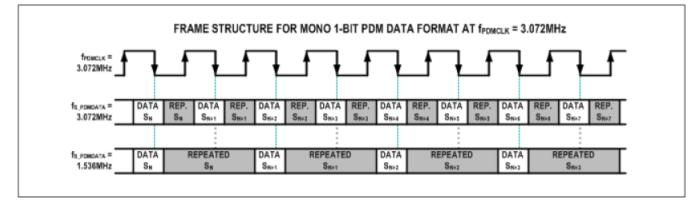

| Figure 23-10: PDM Master Interface Tx/Rx Frame Structure for Mono 1-bit PDM Data (f <sub>PDMCLK</sub> = 6.144MHz)   |     |

| Figure 23-11: PDM Master Interface Tx/Rx Frame Structure for Mono 1-bit PDM Data (fpdmcLk = 3.072MHz)               |     |

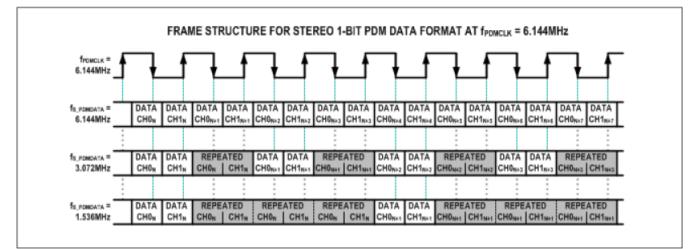

| Figure 23-12: PDM Master Interface Tx/Rx Frame Structure for Stereo 1-bit PDM Data (f <sub>PDMCLK</sub> = 6.144MHz) |     |

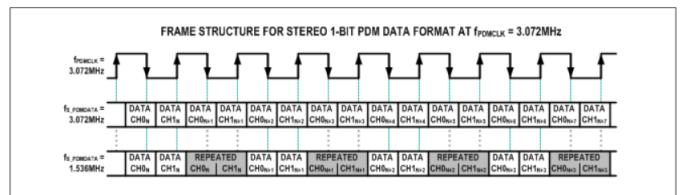

| Figure 23-13: PDM Master Interface Tx/Rx Frame Structure for Stereo 1-bit PDM Data (fPDMCLK = 3.072MHz)             |     |

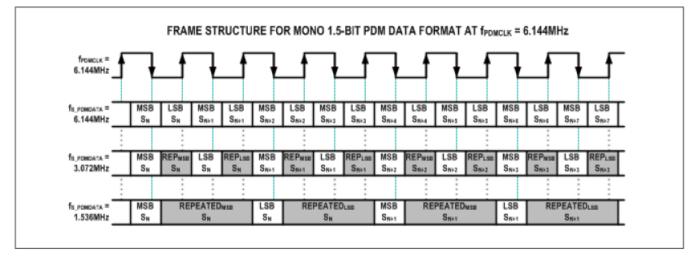

| Figure 23-14: PDM Master Interface Tx/Rx Frame Structure for Mono 1.5-bit PDM Data (fPDMCLK = 6.144MHz)             |     |

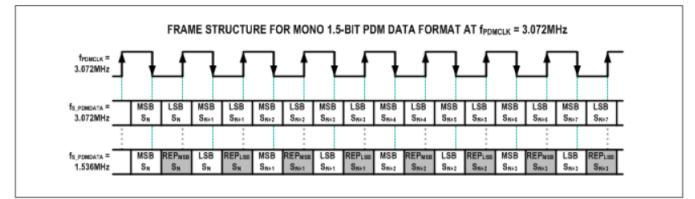

| Figure 23-15: PDM Master Interface Tx/Rx Frame Structure for Mono 1.5-bit PDM Data (fPDMCLK = 3.072MHz)             |     |

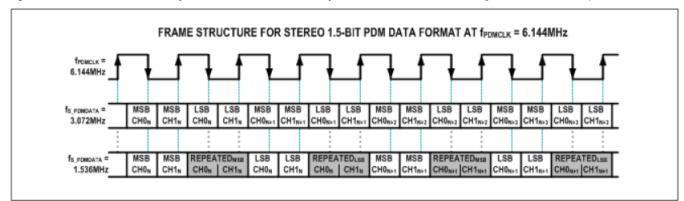

| Figure 23-16: PDM Master Interface Tx/Rx Frame Structure for Stereo 1.5-bit PDM Data (fPDMCLK = 6.144MHz)           |     |

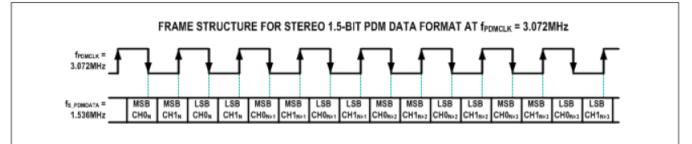

| Figure 23-17: PDM Master Interface Tx/Rx Frame Structure for Stereo 1.5-bit PDM Data (fPDMCLK = 3.072MHz)           |     |

| Figure 24-1: MAX32665/MAX32666 Bluetooth Stack Overview                                                             |     |

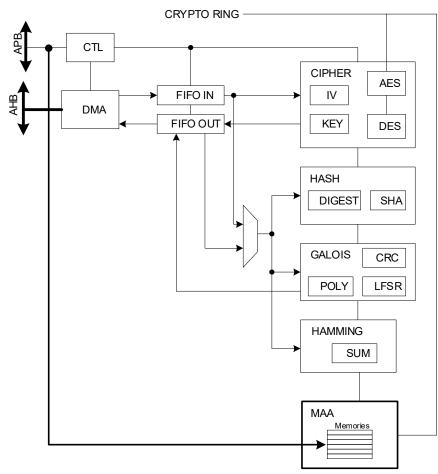

| Figure 25-1: Cryptographic Accelerator Block Diagram                                                                |     |

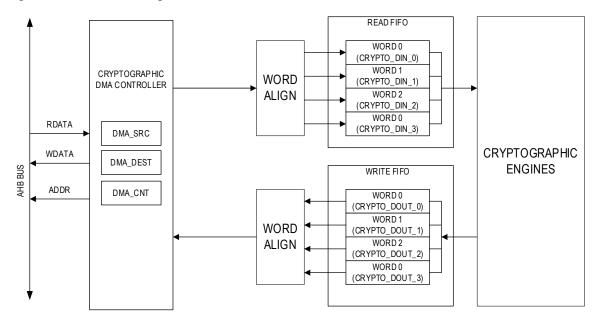

| Figure 25-2: DMA Block Diagram                                                                                      |     |

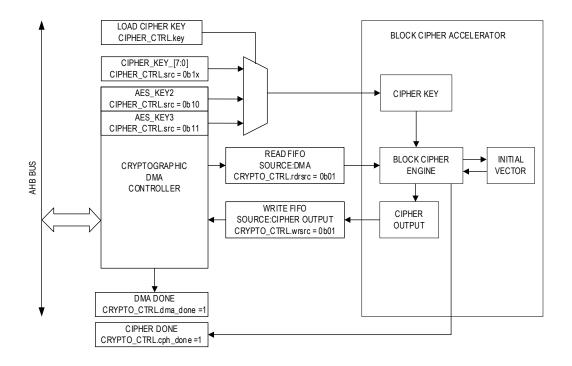

| Figure 25-3: Block Cipher Block Diagram                                                                             | 488 |

| Figure 25-4: Block Cipher Diagram                                                                                   | 490 |

| Figure 25-5: Hamming XOR Calculations                                                                               | 492 |

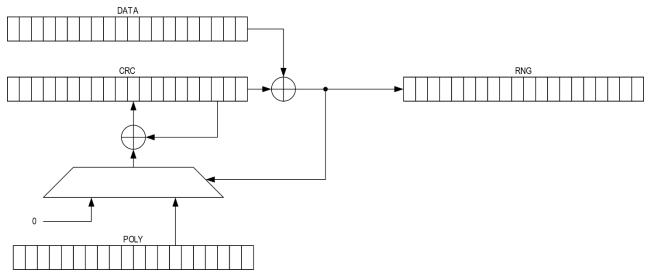

| Figure 25-6: Galois Field CRC and LFSR Architecture                                                                 | 498 |

| Figure 26-1: Life Cycle Phases                                                                                      | 514 |

| Figure 26-2: MAX32666 Bootloader Activation Flow                                                                    | 515 |

| Figure 26-3: Customer Root and Development Key Generation and Usage                                                 | 517 |

| Figure 26-4: Application Image                                                                                      | 519 |

| Figure 26-5: SCPBL Implementation of OSI Model                                                                      | 521 |

| Figure 26-6: SCP Packet Structure                                                                                   | 521 |

| Figure 26-7: CON_REQ Command Structure                                                                              |     |

| Figure 26-8: CON_REP Command Structure                                                                              | 527 |

| Figure 26-9: DISC_REQ Command Structure                                                                             | 528 |

| Figure 26-10: DISC_REP Command Structure                                                                            | 529 |

| Figure 26-11: ACK Command Structure                                                                                 |     |

| Figure 26-12: HELLO Command Structure                                                                               |     |

| Figure 26-13: HELLO_REPLY Structure                                                                                 |     |

| Figure 26-14: WRITE_DATA Command Structure                                                                          |     |

| Figure 26-15: COMMAND_RSP Command Structure                                                                         |     |

| Figure 27-1: Locking the DAP to Make it Available for Unlock Later                                                  |     |

| Figure 27-2: Unlocking the DAP After Being Locked as in Figure 27-1                                                 |     |

| Figure 27-3: Locking the Debug Access Port Permanently                                                              | 554 |

|                                                                                                                     |     |

### **List of Tables**

| Table 2-1: Dual Mapped APB Peripherals                                       |    |

|------------------------------------------------------------------------------|----|

| Table 2-2: MAX32665/MAX32666 Master Permission Bits                          | 31 |

| Table 2-3: MAX32665/MAX32666 AHB Slaves                                      |    |

| Table 2-4: MAX32665/MAX32666 AHB Master/Slave Interconnect Matrix            | 32 |

| Table 2-5: RPU APB Register Offsets, Names, Access, and Descriptions         | 34 |

| Table 2-6: RPU AHB Slave Register Addresses, Names, Access, and Descriptions | 36 |

| Table 2-7: RPU APB Slave Permission Registers                                | 36 |

| Table 2-8: RPU AHB Slave Permission Register                                 | 39 |

| Table 3-1: Field Access Definitions                                          | 43 |

| Table 3-2: SRAM Configuration                                                | 45 |

| Table 3-3: APB Peripheral Base Address Map                                   | 49 |

| Table 3-4: AHB Peripheral Base Address Map                                   |    |

| Table 4-1: Wakeup Sources                                                    |    |

| Table 4-2: Reset and Low Power Mode Effects                                  | 65 |

| Table 4-3: Instruction Cache Controller Register Summary                     | 68 |

| Table 4-4: SPIXF Cache Controller Register Summary                           | 68 |

| Table 4-5: ICCn Cache ID Register                                            | 69 |

| Table 4-6: ICCn Memory Size Register                                         |    |

| Table 4-7: ICCn Cache Control Register                                       |    |

| Table 4-8: ICCn Invalidate Register                                          |    |

| Table 4-9: SFCC Cache ID Register                                            |    |

| Table 4-10: SFCC Memory Size Register                                        |    |

| Table 4-11: SFCC Cache Control Register                                      |    |

| Table 4-12: SFCC Invalidate Register                                         |    |

| Table 4-13: RAM Block Size and Base Address                                  |    |

| Table 4-14: Miscellaneous Control Register Summary                           |    |

| Table 4-15: Error Correction Coding (ECC) Enable Register                    |    |

| Table 4-16: SQWOUT and PDOWN Output Enable Register                          |    |

| Table 4-17: Comparator Enable Register                                       |    |

| Table 4-18: Control Register                                                 |    |

| Table 4-19: SIMO Power Supply Device Pin Connectivity                        |    |

| Table 4-20: SIMO Controller Register Summary                                 |    |

| Table 4-21: Buck Voltage Regulator A Control Register                        |    |

| Table 4-22: Buck Voltage Regulator B Control Register                        |    |

| Table 4-23: Buck Voltage Regulator C Control Register                        |    |

| Table 4-24: Buck Voltage Regulator D Control Register                        |    |

| Table 4-25: High Side FET Peak Current VREGO A VREGO B Register              |    |

| Table 4-26: High Side FET Peak Current VREGO_C VREGO_D Register              |    |

| Table 4-27: Maximum High Side FET Time On Register                           |    |

| Table 4-28: Buck Cycle Count VREGO_A Register                                |    |

| Table 4-29: Buck Cycle Count VREGO_B Register                                |    |

| Table 4-30: Buck Cycle Count VREGO_C Register                                |    |

| Table 4-31: Buck Cycle Count VREGO D Register                                |    |

| Table 4-32: Buck Cycle Count Alert VREGO_A Register                          |    |

| Table 4-33: Buck Cycle Count Alert VREGO B Register                          |    |

| Table 4-34: Buck Cycle Count Alert VREGO_C Register                          |    |

| Table 4-35: Buck Cycle Count Alert VREGO_D Register                          |    |

| Table 4-36: Buck Regulator Output Ready Register                             |    |

| Table 4-37: Zero Cross Calibration VREGO_A Register                          |    |

| Table 4-37. Zero Cross Calibration VREGO_A Register                          |    |

| Table + 30. 2010 Closs calibration Wiedo_b hegister                          |    |

| Table 4-39: Zero Cross Calibration VREGO_C Register                      |      |

|--------------------------------------------------------------------------|------|

| Table 4-40: Zero Cross Calibration VREGO_D Register                      |      |

| Table 4-41: Power Sequencer and Always-On Domain Register Summary        |      |

| Table 4-42: Low Power Control Register                                   |      |

| Table 4-43: GPIO0 Low Power Wakeup Status Flags                          | 85   |

| Table 4-44: GPIO0 Low Power Wakeup Enable Registers                      | 85   |

| Table 4-45: GPIO1 Low Power Wakeup Status Flags                          | 86   |

| Table 4-46: GPIO1 Low Power Wakeup Enable Registers                      | 86   |

| Table 4-47: Peripheral Low Power Wakeup Status Flags                     | 86   |

| Table 4-48: Peripheral Low Power Wakeup Enable Register                  | 88   |

| Table 4-49: RAM Shutdown Control Register                                | 89   |

| Table 4-50: Low Power VDD Power Down Register                            | 90   |

| Table 4-51: BACKUP Return Vector Register                                |      |

| Table 4-52: BACKUP AoD Register                                          | 91   |

| Table 4-53: Global Control Register Summary                              |      |

| Table 4-54: System Control Register                                      |      |

| Table 4-55: Reset Register 0                                             |      |

| Table 4-56: System Clock Control Register                                |      |

| Table 4-57: Power Management Register                                    |      |

| Table 4-58: Peripheral Clock Divisor Register                            |      |

| Table 4-59: Peripheral Clock Disable Register 0                          |      |

| Table 4-60: Memory Clock Control Register                                |      |

| Table 4-61: Memory Zeroization Control Register                          |      |

| Table 4-62: System Status Flag Register                                  |      |

| Table 4-63: Reset Register 1                                             |      |

| Table 4-64: Peripheral Clock Disable Register 1                          |      |

| Table 4-65: Event Enable Register                                        |      |

| Table 4-66: Revision Register                                            |      |

| Table 4-67: System Status Interrupt Enable Register                      |      |

| Table 4-68: Error Correction Coding Error Register                       |      |

| Table 4-69: Error Correction Coding Correctable Error Detected           |      |

| Table 4-70: Error Correction Coding Interrupt Enable Register            |      |

| Table 4-70. Error Correction Coding Address Register                     |      |

| Table 4-71: Error Correction Couling Address Register                    |      |

| Table 4-72: Bluetooth LDO Control Register                               |      |

| Table 4-73: Bidelooth LDO Delay Count Register                           |      |

|                                                                          |      |

|                                                                          |      |

| Table 4-76: Function Control Register Summary                            |      |

| Table 4-77: Function Control Register 0                                  |      |

| Table 4-78: AES Key Register Summary                                     |      |

| Table 4-79: AES Key 0 and 1 Registers                                    |      |

| Table 4-80: AES Key 2 and 3 Registers                                    |      |

| Table 5-1: MAX32665/MAX32666 Interrupt Vector Table                      |      |

| Table 6-1: MAX32665/MAX32666 GPIO Pin Count                              |      |

| Table 6-2: MAX32665/MAX32666 GPIO and Alternate Function Matrix, 140 WLP |      |

| Table 6-3: MAX32665/MAX32666 GPIO Pin Configuration                      |      |

| Table 6-4: MAX32665/MAX32666 Input Mode Configuration                    |      |

| Table 6-5: MAX32665/MAX32666 Output Mode Configuration                   |      |

| Table 6-6: MAX32665/MAX32666 GPIO Port Interrupt Vector Mapping          |      |

| Table 6-7: MAX32665/MAX32666 GPIO Wakeup Interrupt Vector                |      |

| Table 6-8: MAX32665/MAX32666 Power Mode GPIO Interrupt Enable Settings   |      |

| Table 6-9: GPIO Register Summary                                         |      |

| Table 6-10: GPIO Port n Configuration Enable Bit 0 Register              | .135 |

| Table 6-11: GPIO Port n Configuration Enable Atomic Set Bit 0 Register                                                            |     |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 6-12: GPIO Port n Configuration Enable Atomic Set Bit 0 Register                                                            |     |

| Table 6-13: GPIO Port n Output Enable Register                                                                                    |     |

| Table 6-14: GPIO Port n Output Enable Atomic Set Register                                                                         |     |

| Table 6-15: GPIO Port n Output Enable Atomic Clear Register                                                                       |     |

| Table 6-16: GPIO Port n Output Register                                                                                           |     |

| Table 6-17: GPIO Port n Output Atomic Set Register                                                                                |     |

| Table 6-18: GPIO Port n Output Atomic Clear Register                                                                              |     |

| Table 6-19: GPIO Port n Input Register                                                                                            |     |

| Table 6-20: GPIO Port n Interrupt Mode Register                                                                                   |     |

| Table 6-21: GPIO Port n Interrupt Polarity Register                                                                               |     |

| Table 6-22: GPIO Port n Input Enable Register                                                                                     |     |

| Table 6-23: GPIO Port n Interrupt Enable Register                                                                                 |     |

| Table 6-24: GPIO Port n Interrupt Enable Atomic Set Register                                                                      |     |

| Table 6-25: GPIO Port n Interrupt Enable Atomic Clear Register                                                                    |     |

| Table 6-26: GPIO Port n Interrupt Enable Atomic clear Register                                                                    |     |

| Table 6-27: GPIO Port n Interrupt Clear Register                                                                                  |     |

| Table 6-28: GPIO Port n Wakeup Enable Register                                                                                    |     |

| Table 6-29: GPIO Port n Wakeup Enable Atomic Set Register                                                                         |     |

| Table 6-29: GPIO Port n Wakeup Enable Atomic set Register                                                                         |     |

|                                                                                                                                   |     |

| Table 6-31: GPIO Port n Interrupt Dual Edge Mode Select Register                                                                  |     |

| Table 6-32: GPIO Port n Pullup Pulldown Selection 1 Register         Table 6-32: GPIO Port n Pullup Pulldown Selection 2 Register |     |

| Table 6-33: GPIO Port n Pullup Pulldown Selection 2 Register                                                                      |     |

| Table 6-34: GPIO Port n Configuration Enable 1 Register                                                                           |     |

| Table 6-35: GPIO Port n Configuration Enable 1 Atomic Set Register                                                                |     |

| Table 6-36: GPIO Port n Configuration Enable 1 Atomic Clear Register                                                              |     |

| Table 6-37: GPIO Port n Configuration Enable 2 Register                                                                           |     |

| Table 6-38: GPIO Port n Configuration Enable 2 Atomic Set Register                                                                |     |

| Table 6-39: GPIO Port n Configuration Enable Atomic Clear Register                                                                |     |

| Table 6-40: GPIO Port n Output Drive Strength Selection Register                                                                  |     |

| Table 6-41: GPIO Port n Output Drive Strength Selection 1 Register                                                                |     |

| Table 6-42: GPIOn Pulldown/Pullup Strength Select Register                                                                        |     |

| Table 6-43: GPIOn Supply Voltage Select Register                                                                                  |     |

| Table 7-1: MAX32665/MAX32666 Internal Flash Memory Organization                                                                   |     |

| Table 7-2: Valid Addresses Flash Writes                                                                                           |     |

| Table 7-3: Flash Controller Registers                                                                                             |     |

| Table 7-4: Flash Controller Address Pointer Register                                                                              |     |

| Table 7-5: Flash Controller Clock Divisor Register                                                                                |     |

| Table 7-6: Flash Controller Control Register                                                                                      |     |

| Table 7-7: Flash Controller Interrupt Register                                                                                    |     |

| Table 7-8: Flash Controller ECC Data Register                                                                                     |     |

| Table 7-9: Flash Controller Data Register 0                                                                                       |     |

| Table 7-10: Flash Controller Data Register 1                                                                                      | 149 |

| Table 7-11: Flash Controller Data Register 2                                                                                      | 149 |

| Table 7-12: Flash Controller Data Register 3                                                                                      |     |

| Table 7-13. Flash Controller Access Control Register                                                                              | 150 |

| Table 8-1: SPI Header Format                                                                                                      | 154 |

| Table 8-2: Clock Polarity and Phase Combinations                                                                                  | 155 |

| Table 8-3: Encrypted Data Write Order to SPIX Flash Memory                                                                        | 158 |

| Table 8-4: SPIXF Master Controller Register Offsets, Names, Access, and Description                                               | 159 |

| Table 8-5: SPIXF Controller Configuration Register                                                                                | 159 |

| Table 8-6: SPIXF Controller Slave Select Polarity Register                                                                        | 161 |

| Table 8-7: SPIXF Controller General Control Register                                                                              | 161 |

|                                                                                                                                   |     |

| Table 8-8: SPIXF Controller FIFO Control and Status Register                                  |     |

|-----------------------------------------------------------------------------------------------|-----|

| Table 8-9: SPIXF Controller Special Control Register                                          | 163 |

| Table 8-10: SPIXF Controller Interrupt Status Register                                        | 164 |

| Table 8-11: SPIXF Controller Interrupt Enable Register                                        | 165 |

| Table 8-12: SPIXF Master Controller FIFO Register Offsets, Names, Access and Description      | 166 |

| Table 8-13: SPIXF Master Controller TX FIFO Register                                          | 166 |

| Table 8-14: SPIXF Master Controller TX FIFO Register                                          | 166 |

| Table 8-15: SPIXF Master Register Offsets, Names, Access and Description                      |     |

| Table 8-16: SPIXF Master Configuration Register                                               | 170 |

| Table 8-17: SPIXF Master Fetch Control Register                                               |     |

| Table 8-18: SPIXF Master Mode Control Register                                                |     |

| Table 8-19: SPIXF Master Mode Data Register                                                   |     |

| Table 8-20: SPIXF Master SCK Feedback Control Register                                        |     |

| Table 8-21: SPIXF Master I/O Control Register                                                 |     |

| Table 8-22: SPIXF Master Memory Security Control Register                                     |     |

| Table 8-23: SPIXF Master Bus Idle Detection                                                   |     |

| Table 8-24: SPIXR Master Controller Register Offsets, Names, Access, and Descriptions         |     |

| Table 8-25: SPIXR FIFO Data Register                                                          |     |

| Table 8-26: SPIXR Master Signals Control Register                                             |     |

| Table 8-27: SPIXR Transmit Packet Size Register                                               |     |

| Table 8-28: SPIXR Static Configuration Register                                               |     |

| Table 8-29: SPIXR Slave Select Timing Register                                                |     |

| Table 8-20: SPIXR Master Baud Rate Generator                                                  |     |

| Table 8-30. SPIXR Master Badd Rate Generator                                                  |     |

| Table 8-31. SPIXE DMA Control Register                                                        |     |

| Table 8-32: SPIXR Interrupt Status Flag Register                                              |     |

|                                                                                               |     |

| Table 8-34: SPIXR Wakeup Flag Register                                                        |     |

| Table 8-35: SPIXR Wakeup Enable Register                                                      |     |

| Table 8-36: SPIXR Active Status Register                                                      |     |

| Table 8-37: SPIXR External Memory Control Register                                            |     |

| Table 8-38: External Memory Cache Controller Register Addresses and Descriptions              |     |

| Table 8-39: SRCC Cache ID Register                                                            |     |

| Table 8-40: SRCC Memory Size Register                                                         |     |

| Table 8-41: SRCC Cache Control Register                                                       |     |

| Table 8-42: SRCC Invalidate Register                                                          |     |

| Table 8-43: MAX32665/MAX32666 SDHC Alternate Function Mapping to SDHC Specification Pin Names |     |

| Table 8-44: Registers Used to Generate SD Commands                                            |     |

| Table 8-45: SDHC Register Offsets, Names and Descriptions                                     |     |

| Table 8-46: SDHC SDMA System Address / Argument Register                                      |     |

| Table 8-47: SDHC SDMA Block Size Register                                                     |     |

| Table 8-48: SDHC SDMA Block Count Register                                                    |     |

| Table 8-49: SDHC SDMA Argument 1 Register                                                     |     |

| Table 8-50: SDHC SDMA Transfer Mode Register                                                  |     |

| Table 8-51: Summary of how register settings determine type of data transfer                  |     |

| Table 8-52: SDHC Command Register                                                             |     |

| Table 8-53: Relationship between Parameters and the Name of Response Type                     |     |

| Table 8-54: SDHC Response 0 Register                                                          |     |

| Table 8-55: SDHC Response 1 Register                                                          | 200 |

| Table 8-56: SDHC Response 2 Register                                                          |     |

| Table 8-57: SDHC Response 3 Register                                                          |     |

| Table 8-58: SDHC Response 4 Register                                                          | 201 |

| Table 8-59: SDHC Response 5 Register                                                          | 201 |

| Table 8-60: SDHC Response 6 Register                                                          | 201 |

| Table 8-61: SDHC Response 7 Register                                                                                           | 202 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 8-62: SDHC Response Register Mapping to SD Host Controller Response Register Convention                                  |     |

| Table 8-63: Kind of SD Card Response Mapping to SDHC Response Registers                                                        |     |

| Table 8-64: SDHC Buffer Data Port Register                                                                                     |     |

| Table 8-65: SDHC Present State Register                                                                                        |     |

| Table 8-66: SDHC Host Control 1 Register                                                                                       |     |

| Table 8-67: SDHC Power Control Register                                                                                        |     |

| Table 8-68: SDHC Fower control Register                                                                                        |     |

| Table 8-69: SDHC Wakeup Control Register                                                                                       |     |

| Table 8-09: SDHC Wakeup Control Register                                                                                       |     |

| Table 8-71: SDHC Timeout Control Register                                                                                      |     |

| Table 8-72: SDHC Software Reset Register                                                                                       |     |

| Table 8-73: SDHC Normal Interrupt Status Register                                                                              |     |

| Table 8-74: Transfer Complete and Data Timeout Error Priority and Status                                                       |     |

| Table 8-75: Command Complete and Command Timeout Error Priority and Status                                                     |     |

| Table 8-76: SDHC Error Interrupt Status Register                                                                               |     |

| Table 8-70: SDHC Error Interrupt Status Register                                                                               |     |

| Table 8-77: SDHC Normal interrupt Status Register                                                                              |     |

| Table 8-78: SDHC Error Interrupt Status Errorie Register                                                                       |     |

| Table 8-79. SDHC Normal Interrupt Signal Enable Register                                                                       |     |

| Table 8-80: SDHC Error Interrupt Signal Enable Register                                                                        |     |

| Table 8-82: SDHC Auto CMD Error Status Register                                                                                |     |

| -                                                                                                                              |     |

| Table 8-83: SDHC Capabilities Register 0                                                                                       |     |

| Table 8-84: SDHC Capabilities Register 1                                                                                       |     |

| Table 8-85: SDHC Maximum Current Capabilities Register                                                                         |     |

| Table 8-86: SDHC Force Event Register for Auto CMD Error Status Register                                                       |     |

| Table 8-87: SDHC Force Event Register for Error Interrupt Status                                                               |     |

| Table 8-88: SDHC ADMA Error Status Register                                                                                    |     |

| Table 8-89: SDHC ADMA System Address Register 0                                                                                |     |

| Table 8-90: SDHC ADMA System Address Register 1                                                                                |     |

| Table 8-91: Preset Value Register Example                                                                                      |     |

| Table 8-92: Preset Value Register Selection Conditions                                                                         |     |

| Table 8-93: SDHC Preset Value 0 to Preset Value 7 Registers         Table 8-94: SDHC Slot Interrupt Status Register            |     |

|                                                                                                                                |     |

| Table 8-95: SDHC Host Controller Version Register                                                                              |     |

| Table 9-1: MAX32665/MAX32666 DMA and Channel Instances                                                                         |     |

| Table 9-2: MAX32665/MAX32666 DMA Source and Destination by Peripheral         Table 9-3: Data Movement from Source to DMA FIFO |     |

|                                                                                                                                |     |

| Table 9-4: Data Movement from the DMA FIFO to Destination                                                                      |     |