# MAX2990 INTEGRATED POWER-LINE DIGITAL TRANSCEIVER PROGRAMMING MANUAL

## TABLE OF CONTENTS

| MAX2990 Functional Description                        |    |

|-------------------------------------------------------|----|

| Buffer Manager:                                       |    |

| Data Manager:                                         |    |

| CRC/DES:                                              |    |

| MCU SPR Registers:                                    |    |

| MCU SFR Registers:                                    |    |

| Flash, Util. ROM, Data SRAM and MMU:                  |    |

| JTAG/EMM:                                             |    |

| CLKGEN:                                               |    |

| MAXQ Core:                                            |    |

| MAXQ Peripherals:                                     |    |

| MAXQ MCU                                              | 6  |

| Special Purpose Registers:                            |    |

| Special Function Registers:                           |    |

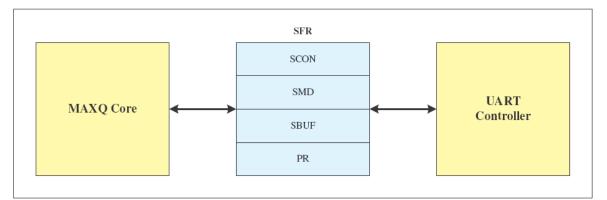

| UART (Universal Asynchronous Receiver/Transmitter)    |    |

| UART SFRs                                             |    |

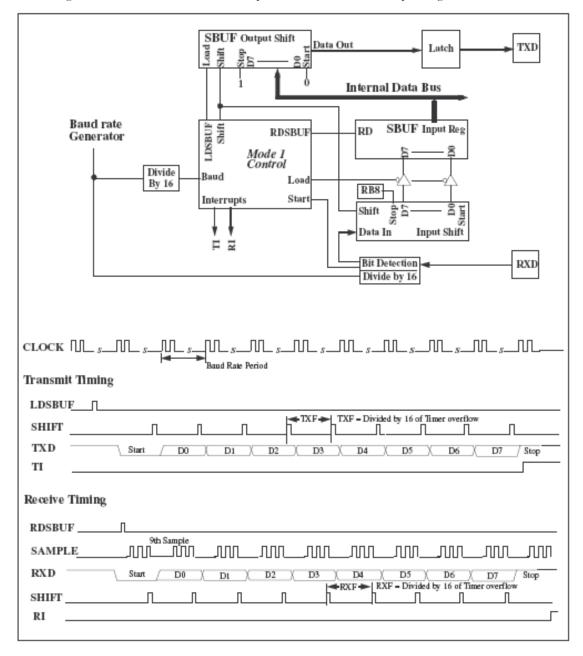

| UART Operating Modes                                  |    |

| UART Baud Rate Generation                             |    |

| Timer B                                               |    |

| GPIO                                                  |    |

| I/O Port Description                                  |    |

| The Test Access (JTAG) Port                           | 66 |

| PHY Frame Format                                      |    |

| MAC Code                                              |    |

| Changing Transmitter Gain                             |    |

| Changing Modulation Scheme and Communication Standard |    |

| MAC functions description                             |    |

| Main function example flowchart                       |    |

| System Init                         | 70 |

|-------------------------------------|----|

| Interrupt                           | 74 |

| LED                                 | 76 |

| Timer                               | 76 |

| Encryption                          | 77 |

| MAC functions                       |    |

| PHY functions                       |    |

| Channel Estimation                  |    |

| CSMA(Carrier Sense Multiple Access) |    |

| Miscellaneous                       |    |

| Macros description                  |    |

| Global variables description        |    |

|                                     |    |

## MAX2990 Functional Description

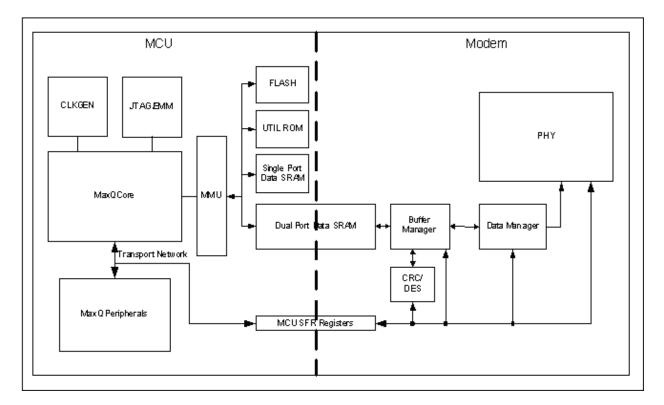

Figure 1 shows the MAX2990 functional diagram.

Figure1. MAX2990 Functional Diagram

The MAX2990 is functionally split into two blocks: MAXQ® MCU and the Modem. The communication between MCU and Modem is either through RX/TX memory writes or through MCU SFR registers. Each functional block in Modem and MCU is explained in brief in the following section.

#### Buffer Manager:

The Buffer Manager block is responsible for arbitrating access to the packet memory (implemented as the dual port data memory) between the Data Manager and the DES/CRC32 engines. Access arbitration is handled as a "fair arbitration" scheme in which all data sources and destinations have equal priority and are handled in a first come, first serve manner. Data writes to the memory through the Buffer Manager can be handled as byte writes to the 16 bit wide memory, so this block is also responsible for controlling the byte masking controls and byte to word multiplexing required to write bytes into the word wide memory.

#### Data Manager:

The Data Manager block is responsible for transferring whole frames of data between the PHY and the Buffer Manager. Each frame of data is stored in the buffer memory in separate header and data sections. When the frame has been completely read out of the PHY, the Data Manager asserts an interrupt to the MCU.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

#### CRC/DES:

The DES encryption and CRC32 functions can be enabled separately. If DES function is enabled, data is encrypted or decrypted, depending on the mode set, and written back to memory. If CRC32 is enabled, a CRC32 checksum is calculated and appended to the end of data block. If both CRC32 and DES are enabled, CRC32 checksum is calculated, encrypted and then appended to the data block.

#### MCU SPR Registers:

MCU SPR Registers are explained in detail in MAXQ Core description.

#### MCU SFR Registers:

MCU SFR Registers are explained in detail in MAXQ Core description.

#### Flash, Util. ROM, Data SRAM and MMU:

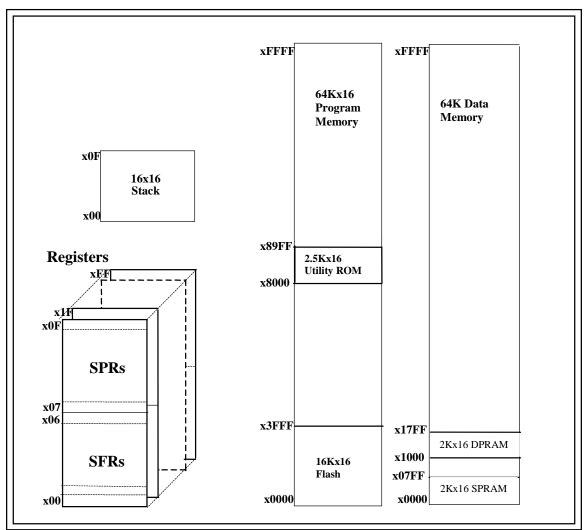

Figure 2 shows the MAX2990 memory organization.

Figure 2. MAX2990 Memory Organization

The MAX2990 has 32KB of flash memory, 5KB of Utility ROM for system startup and programming routines, test support routines and miscellaneous non-volatile data that is not used for system configuration (such as the boot loader access password). There are two data memories, 4KB Single Port Data SRAM and 128KB of Dual Port Data SRAM.

Memory Management Unit (MMU) provides memory allocation and access control to program and data memories.

#### <u>JTAG/EMM:</u>

JTAG is a debug/programming port for MAXQ MCU. JTAG interface is discussed in detail in MAXQ MCU core section.

#### CLKGEN:

CLKGEN is a functional block, which generates system clock from external clock source (oscillator or resonator) or an internal oscillator circuit.

#### MAXQ Core:

MAXQ is a low-power 16-bit RISC processor based on Harvard Memory Architecture. It has 16-bit program memory bus and all instructions are 16 bits in length. The registers and the peripherals are explained in detail in MAXQ MCU section.

#### MAXQ Peripherals:

MAXQ MCU has seven 16-bit timers, UART, 4-wire SPI<sup>™</sup>, I<sup>2</sup>C, and Real Time Clock (RTC). Each peripheral description is in the MAXQ MCU section.

## MAXQ MCU

#### Special Purpose Registers:

| Register           | Description                                                                                     |

|--------------------|-------------------------------------------------------------------------------------------------|

| AP (00h, 08h)      | Accumulator Pointer (8-bit register)                                                            |

| Initialization:    | This register is cleared to 00h on all forms of reset.                                          |

| Read/Write Access: | Unrestricted direct Read/Write.                                                                 |

| AP.3 – AP.0        | Active Accumulator select bits. The setting of these bits activates one of the 8/16 Accumulator |

|                    | in the Accumulator module (A) to function as the Active Accumulator for arithmetic and logical  |

|                    | operations. The setting of the these bits can be automatically incremented/decremented in a     |

|                    | modulo fashion according to the setting to the APC register.                                    |

|                    | (Bit 3 is reserved and is tried to 0 for Implementation with 8 accumulators)                    |

| AP.7 – AP.4        | Reserved, read returns 0.                                                                       |

SPI is a trademark of Motorola, Inc.

| Register           | Description                                                                                       |                                                               |  |  |

|--------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|

| APC (01h, 08h)     | Accumulator Pointer Control (8-bit register)                                                      |                                                               |  |  |

| Initialization:    | This register is cleared to 00h on all forms of reset.                                            |                                                               |  |  |

| Read/Write Access: | Unrestricted direct Read/Wri                                                                      | te.                                                           |  |  |

| APC.0: MOD0        | Modulo Bit 0                                                                                      |                                                               |  |  |

| APC.1: MOD1        | Modulo Bit 1                                                                                      |                                                               |  |  |

| APC.2: MOD2        | Modulo Bit 2                                                                                      |                                                               |  |  |

|                    | The Accumulator Pointer Au                                                                        | to-Increment/Decrement function will be activate when these   |  |  |

|                    | bits are set to value other then 000b. The modulo is selected accordingly when Active             |                                                               |  |  |

|                    | Pointer Auto-Increment/Decrement is active:                                                       |                                                               |  |  |

|                    | MOD2,MOD1,MOD0                                                                                    | Modulo                                                        |  |  |

|                    | 000                                                                                               | Default, no AP auto-increment/decrement                       |  |  |

|                    | 001                                                                                               | Modulo 2                                                      |  |  |

|                    | 010                                                                                               | Modulo 4                                                      |  |  |

|                    | 011                                                                                               | Modulo 8                                                      |  |  |

|                    | 100                                                                                               | Modulo 16 (not valid for 8 accumulators, MOD2 is tied to 0)   |  |  |

|                    | 101 – 111                                                                                         | Reserved (for 16 accumulators modulo 16 if set; MOD2 is tied  |  |  |

|                    |                                                                                                   | 0 for 8-accumulator implementation).                          |  |  |

|                    | Note the MOVE AP, Acc instruction (880Ah) causing AP auto-Inc/Dec will happen if enabled, no      |                                                               |  |  |

|                    | data transfer will perform.                                                                       |                                                               |  |  |

| APC.5 – APC.3      | Reserved, read returns 0.                                                                         |                                                               |  |  |

| APC.6: IDS         | Increment/Decrement Sele                                                                          | ect. When this bit is cleared to 0, the content of AP will be |  |  |

|                    | increment after an arithmetic or logical operation, When this bit is set to 1, the content of     |                                                               |  |  |

|                    | AP will be decremented after                                                                      | an arithmetic or logical operation.                           |  |  |

| APC.7: CLR         | AP Clear. When this bit is set to 1, the content of AP will be cleared to 0. This bit will be     |                                                               |  |  |

|                    | automatically reset to 0 after clearing the AP register. Note if the MOVE APC, Acc instruction    |                                                               |  |  |

|                    | (980Ah) causes the CLR bit to set, the clear operation will override other functions, i.e. the AP |                                                               |  |  |

|                    | auto-Inc/Dec will not happen.                                                                     |                                                               |  |  |

| Register                                                                                   | Description                                                                                                |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PSF (04h, 08h)                                                                             | Processor Status Flags Register (8-bit register)                                                           |  |  |  |  |  |

| Initialization:                                                                            | This register is cleared to x80h on all forms of reset.                                                    |  |  |  |  |  |

| Read/Write Access:                                                                         | Unrestricted direct Read. Write access to OV, E, C, GPF1 and GPF0 bits only.                               |  |  |  |  |  |

| <i>PSF.0: E</i>                                                                            | Equal Flag. This flag reflects the state of Equal bit of a compare operation. It will be 1                 |  |  |  |  |  |

|                                                                                            | when the two values are equal. It will be 0 when the two values are different. Write a 1 to                |  |  |  |  |  |

|                                                                                            | this bit by software is effectively set the Equal flag.                                                    |  |  |  |  |  |

| <i>PSF.1: C</i>                                                                            | Carry Flag. This flag reflects the state of Carry bit of the active Accumulator. Its state                 |  |  |  |  |  |

|                                                                                            | may change after an arithmetic and logical operation. This flag is set to 1 if the last                    |  |  |  |  |  |

|                                                                                            | operation resulted in a carry/borrow. Otherwise it is cleared to 0. Write a 1 to this bit by               |  |  |  |  |  |

|                                                                                            | software is effectively set the Carry flag.                                                                |  |  |  |  |  |

| PSF.2: OV                                                                                  | Overflow Flag. This flag is set to 1 if there is a carry out of bit 14 but not out of bit 15, or a carry   |  |  |  |  |  |

|                                                                                            | out of bit 15 bit not out of bit 14 from the last arithmetic operation, otherwise, the OV is remained      |  |  |  |  |  |

|                                                                                            | as 0. When adding signed numbers, OV indicates a negative number resulted as the sum of two                |  |  |  |  |  |

|                                                                                            | positive operands, or a positive sum resulted from two negative operands. For subtraction, OV is           |  |  |  |  |  |

|                                                                                            | set if a borrow is needed into bit 14 but not into bit 15, or into bit 15 but not into bit 14. This bit is |  |  |  |  |  |

|                                                                                            | read and write to the CPU to allow it to be restored after events such as interrupt servicing and          |  |  |  |  |  |

|                                                                                            | debug operations.                                                                                          |  |  |  |  |  |

| PSF.3: GPF0                                                                                | General-Purpose Flag 0. This is a general-purpose flag for software control.                               |  |  |  |  |  |

| PSF.4: GPF1                                                                                | General-Purpose Flag 1. This is a general-purpose flag for software control.                               |  |  |  |  |  |

| PSF.5                                                                                      | Reserved, read returns 0                                                                                   |  |  |  |  |  |

| <i>PSF.6: S</i>                                                                            | Sign Flag. This flag reflects the state of Sign bit of the active Accumulator (the most                    |  |  |  |  |  |

|                                                                                            | significant bit of the active Accumulator). Its state may change after an arithmetic and                   |  |  |  |  |  |

|                                                                                            | logical operation or after switch of active Accumulator. When it is set to 1, it indicates a               |  |  |  |  |  |

|                                                                                            | negative value in the active Accumulator from the last operation. When it is cleared to 0, it              |  |  |  |  |  |

|                                                                                            | indicates a positive value. This is a read only bit.                                                       |  |  |  |  |  |

| <i>PSF.7: Z</i>                                                                            | Zero Flag. This flag reflects the state of Zero bit of the active Accumulator (bit-wise NOR                |  |  |  |  |  |

|                                                                                            | of the active Accumulator). Its state may change after an arithmetic and logical operation                 |  |  |  |  |  |

|                                                                                            | or after switch of active Accumulator. When it is set to 1, it indicates a zero value as result            |  |  |  |  |  |

|                                                                                            | of the last operation. When it is cleared to 0, it indicates a non-zero value. This is a read only bit.    |  |  |  |  |  |

| IC (05h, 08h)                                                                              | Interrupt and Control Register (8-bit register)                                                            |  |  |  |  |  |

| Initialization:                                                                            | This register is cleared to 00h on all forms of reset.                                                     |  |  |  |  |  |

| Read/Write Access:                                                                         | Unrestricted direct Read/Write.                                                                            |  |  |  |  |  |

| IC.0: IGE                                                                                  | Interrupt Global Enable The IGE bit enables the interrupt handler if set to 1. No                          |  |  |  |  |  |

|                                                                                            | interrupt to the CPU is allowed if this bit is cleared to 0.                                               |  |  |  |  |  |

| IC.1: INS                                                                                  | <b>Interrupt In Service</b> . The INS will be set by the interrupt handler automatically when an           |  |  |  |  |  |

|                                                                                            | interrupt is acknowledged. No further interrupt will occur as long as the INS remains set. The             |  |  |  |  |  |

|                                                                                            | interrupt service routine can clear the INS to allow interrupt nesting. Otherwise, execution of an         |  |  |  |  |  |

|                                                                                            | RETI/POPI instruction the INS will be cleared automatically by the interrupt handler.                      |  |  |  |  |  |

| IC.4 – IC.2                                                                                | Reserved, read returns 0.                                                                                  |  |  |  |  |  |

| IC.5: CGDS                                                                                 | System Clock Gating Disable. The system clock gating circuitry is disabled if the CGDS                     |  |  |  |  |  |

| bit is set to 1. When this bit is cleared, the system clock gating circuitry is activated. |                                                                                                            |  |  |  |  |  |

| IC.7 – IC.6                                                                                | Reserved, read returns 0.                                                                                  |  |  |  |  |  |

| Register           | Description                                                                                       |

|--------------------|---------------------------------------------------------------------------------------------------|

| MR (06h, 08h)      | Interrupt Mask Register (8-bit register)                                                          |

| Initialization:    | This register is 00h on all forms of reset.                                                       |

| Read/Write Access: | Unrestricted direct Read/Write                                                                    |

| IMR.0: IM0         | Interrupt Mask 0. This bit is the module level interrupt enable for register module 0. To         |

|                    | activate the interrupt request from module 0, the IGE and IM0 must be set and the INS is not set. |

|                    | Clearing this bit to 0 disables all interrupt sources in module 0.                                |

| IMR.1: IM1         | Interrupt Mask 1. This bit is the module level interrupt enable for register module 1. To         |

|                    | activate the interrupt request from module 1, the IGE and IM01 must be set and the INS is not set |

|                    | Clearing this bit to 0 disables all interrupt sources in module 1.                                |

| IMR.2: IM2         | Interrupt Mask 2. This bit is the module level interrupt enable for register module 2. To         |

|                    | activate the interrupt request from module 2, the IGE and IM2 must be set and the INS is not set. |

|                    | Clearing this bit to 0 disables all interrupt sources in module 2.                                |

| IMR.3: IM3         | Interrupt Mask 3. This bit is the module level interrupt enable for register module 3. To         |

|                    | activate the interrupt request from module 3, the IGE and IM3 must be set and the INS is not set. |

|                    | Clearing this bit to 0 disables all interrupt sources in module 3.                                |

| IMR.4: IM4         | Interrupt Mask 4. This bit is the module level interrupt enable for register module 4. To         |

|                    | activate the interrupt request from module 4, the IGE and IM4 must be set and the INS is not set. |

|                    | Clearing this bit to 0 disables all interrupt sources in module 4.                                |

| IMR.5: IM5         | Interrupt Mask 5. This bit is the module level interrupt enable for register module 5. To         |

|                    | activate the interrupt request from module 5, the IGE and IM5 must be set and the INS is not set. |

|                    | Clearing this bit to 0 disables all interrupt sources in module 5.                                |

| IMR.6:             | Reserved, read returns 0.                                                                         |

| IMR.7: IMS         | Interrupt Mask System. This bit is the module level interrupt enable for SPR modules. To          |

|                    | activate the interrupt request from any SPR modules, the IGE and IMS must be set and the INS is   |

|                    | not set. Clearing this bit to 0 disables all interrupt sources in all SPR modules.                |

| Register           | Description                                                                                         |                                             |                                                  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------|--|--|--|

| SC (08h, 08h)      | System Control Register (8-bit register)                                                            |                                             |                                                  |  |  |  |

| Initialization:    | This register is 100000s0b on all forms of reset. Bit 1 (PWL) is set by power-on reset only         |                                             |                                                  |  |  |  |

| Read/Write Access: | Unrestricted direct Read/Write.                                                                     |                                             |                                                  |  |  |  |

| SC.0:              | Reserved, read re                                                                                   | turns 0.                                    |                                                  |  |  |  |

| SC.1: PWL          | Password Lock.                                                                                      | This bit defaults to 1 on a power-or        | on reset. When this bit is 1, it requires a 32-  |  |  |  |

|                    | byte password to be matched with the password in the program space before allowing access to        |                                             |                                                  |  |  |  |

|                    | the ROM Loader                                                                                      | 's utilities for read/write of program      | n memory and debug functions. Clearing this      |  |  |  |

|                    | bit to 0 disables t                                                                                 | he password protection to the ROM           | I Loader.                                        |  |  |  |

| <i>SC.2:</i> ROD   | <b>ROM Operation</b>                                                                                | <b>Done</b> . This bit is used to signify c | completion of a ROM operation sequence to        |  |  |  |

|                    | the control units.                                                                                  | This allows the Debug engine to d           | etermine the status of a ROM sequence.           |  |  |  |

|                    | Setting this bit to                                                                                 | logic 1 causes an internal system re        | eset if the SPE bit is also set. Setting the ROD |  |  |  |

|                    | bit will clear the SPE bit if it is set and the ROD bit will be automatically cleared by hardware   |                                             |                                                  |  |  |  |

|                    | once the control unit acknowledged the done indication.                                             |                                             |                                                  |  |  |  |

| SC.3: UPA          | <b>Upper Program Access</b> . The physical program memory is logically divided into four pages; P0  |                                             |                                                  |  |  |  |

|                    | and P1 occupy the lower 32K words while P2 and P3 occupy the upper 32K words. P0 and P1 are         |                                             |                                                  |  |  |  |

|                    | assigned to the lower half of the program space and is always active. However, P2 and P3 must be    |                                             |                                                  |  |  |  |

|                    | implicitly activated in the upper half of the program space by setting the UPA bit to logic 1 for   |                                             |                                                  |  |  |  |

|                    | normal program execution. When UPA bit is cleared to 0, the upper program memory space is           |                                             |                                                  |  |  |  |

|                    | occupied by the Utility ROM and the physical data to be accessible as program memory.               |                                             |                                                  |  |  |  |

|                    | Note that the UPA is not implemented if the upper 32K of the program space is not used for the      |                                             |                                                  |  |  |  |

|                    | user code.                                                                                          |                                             |                                                  |  |  |  |

| SC.4: CDA0         | Code Data Acce                                                                                      | ess Bit 0.                                  |                                                  |  |  |  |

| SC.5: CDA1         | Code Data Access Bit 1.                                                                             |                                             |                                                  |  |  |  |

|                    | The CDA bits are used to logically map physical program memory page to the data space for           |                                             |                                                  |  |  |  |

|                    | read/write access:                                                                                  |                                             |                                                  |  |  |  |

|                    | CDA1 CDA0                                                                                           | Byte Mode Active Page                       | Word Mode Active Page                            |  |  |  |

|                    | 0 0                                                                                                 | P0                                          | P0 and P1                                        |  |  |  |

|                    | 0 1                                                                                                 | P1                                          | P0 and P1                                        |  |  |  |

|                    | 1 0                                                                                                 | P2                                          | P2 and P3                                        |  |  |  |

|                    | 1 1                                                                                                 | Р3                                          | P2 and P3                                        |  |  |  |

|                    | The logical addresses are depending on which memory segment is executing. Note that CDA1 is         |                                             |                                                  |  |  |  |

|                    | not implemented if the upper 32K of the program space is not used for the user code. No CDA         |                                             |                                                  |  |  |  |

|                    | bits are needed if only one page program space is incorporated.                                     |                                             |                                                  |  |  |  |

| SC.6               | Reserved, read returns 0.                                                                           |                                             |                                                  |  |  |  |

| SC.7:TAP           | Test Access (JTAG) Port Enable. This bit controls whether the Test Access Port special              |                                             |                                                  |  |  |  |

|                    | function pins are enabled. The TAP defaults to being enabled. Clearing this bit to a logic '0' will |                                             |                                                  |  |  |  |

|                    | disable the TAP special function on the JTAG pins.                                                  |                                             |                                                  |  |  |  |

| legister           | Description                                                                                      |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IR (0Bh, 08h)      | Interrupt Identification Register (8-bit register)                                               |  |  |  |  |  |

| Initialization:    | This register is 00h on all forms of reset.                                                      |  |  |  |  |  |

| Read/Write Access: | Unrestricted direct Read. Write access is a no-operation.                                        |  |  |  |  |  |

| <i>IIR.0: II0</i>  | Interrupt ID 0. When this bit is set to 1, it indicates that there is at least one pending       |  |  |  |  |  |

|                    | interrupt in register module 0. This bit is set only if the interrupt flag and its corresponding |  |  |  |  |  |

|                    | enable bit are set. The II0 is cleared by hardware when the interrupt source is disabled or      |  |  |  |  |  |

|                    | the flag is cleared by software.                                                                 |  |  |  |  |  |

| IIR.1: II1         | Interrupt ID 1. When this bit is set to 1, it indicates that there is at least one pending       |  |  |  |  |  |

|                    | interrupt in register module 1. This bit is set only if the interrupt flag and its corresponding |  |  |  |  |  |

|                    | enable bit are set. The II1 is cleared by hardware when the interrupt source is disabled or      |  |  |  |  |  |

|                    | the flag is cleared by software                                                                  |  |  |  |  |  |

| IIR.2: II2         | Interrupt ID 2. When this bit is set to 1, it indicates that there is at least one pending       |  |  |  |  |  |

|                    | interrupt in register module 2. This bit is set only if the interrupt flag and its corresponding |  |  |  |  |  |

|                    | enable bit are set. The II2 is cleared by hardware when the interrupt source is disabled or      |  |  |  |  |  |

|                    | the flag is cleared by software                                                                  |  |  |  |  |  |

| IIR.3: II3         | Interrupt ID 3. When this bit is set to 1, it indicates that there is at least one pending       |  |  |  |  |  |

|                    | interrupt in register module 3. This bit is set only if the interrupt flag and its corresponding |  |  |  |  |  |

|                    | enable bit are set. The II3 is cleared by hardware when the interrupt source is disabled or      |  |  |  |  |  |

|                    | the flag is cleared by software                                                                  |  |  |  |  |  |

| IIR.4: II4         | Interrupt ID 4. When this bit is set to 1, it indicates that there is at least one pending       |  |  |  |  |  |

|                    | interrupt in register module 4. This bit is set only if the interrupt flag and its corresponding |  |  |  |  |  |

|                    | enable bit are set. The II4 is cleared by hardware when the interrupt source is disabled or      |  |  |  |  |  |

|                    | the flag is cleared by software.                                                                 |  |  |  |  |  |

| IIR.5: II5         | Interrupt ID 5. When this bit is set to 1, it indicates that there is at least one pending       |  |  |  |  |  |

|                    | interrupt in register module 5. This bit is set only if the interrupt flag and its corresponding |  |  |  |  |  |

|                    | enable bit are set. The II5 is cleared by hardware when the interrupt source is disabled or      |  |  |  |  |  |

|                    | the flag is cleared by software.                                                                 |  |  |  |  |  |

| <i>IIR.6:</i>      | Reserved, read returns 0.                                                                        |  |  |  |  |  |

| IIR.7: IIS         | Interrupt ID System. When this bit is set to 1, it indicates that there is at least one pending  |  |  |  |  |  |

|                    | interrupt in SPR modules. This bit is set only if the interrupt flag and its corresponding       |  |  |  |  |  |

|                    | enable bit are set. The IIS is cleared by hardware when the interrupt source is disabled         |  |  |  |  |  |

|                    | or the flag is cleared by software.                                                              |  |  |  |  |  |

| Register               | Description                                                                                                                                                                     |            |                                                               |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| CKCN (0Eh, 08h)        | System Clock Cont                                                                                                                                                               | rol Regis  | ster                                                          |  |  |  |

| Initialization:        | Bits 4:0 and 7 are cleared to 0 on all forms of reset. See bit description for bits 6:5.                                                                                        |            |                                                               |  |  |  |

| Read/Write Access:     | Unrestricted read/write, except there is locking mechanism for the PMME, CD1 and                                                                                                |            |                                                               |  |  |  |

|                        | CD0 bits when cha                                                                                                                                                               | nging th   | eir bits values; bit 5 is read only.                          |  |  |  |

| CKCN.0: CD0            | Clock Divide Cor                                                                                                                                                                | trol Bit   | 0.                                                            |  |  |  |

| CKCN.1: CD1            | Clock Divide Cor                                                                                                                                                                | trol Bit   | 1.                                                            |  |  |  |

| CKCN.2: PMME           | Power Manageme                                                                                                                                                                  | ent Mod    | e Enable.                                                     |  |  |  |

|                        | These control bits                                                                                                                                                              | select the | e divide ratio of the system clock from a clock source.       |  |  |  |

|                        | PMME CD1                                                                                                                                                                        | CD0        | Clock Divide Ratio                                            |  |  |  |

|                        | 0 0                                                                                                                                                                             | 0          | Divide by 1 (default)                                         |  |  |  |

|                        | 0 0                                                                                                                                                                             | 1          | Divide by 2                                                   |  |  |  |

|                        | 0 1                                                                                                                                                                             | 0          | Divide by 4                                                   |  |  |  |

|                        | 0 1                                                                                                                                                                             | 1          | Divide by 8                                                   |  |  |  |

|                        | 1 x                                                                                                                                                                             | х          | Divide by 256                                                 |  |  |  |

|                        | A default of divide                                                                                                                                                             | by 1 is s  | elected after all Resets.                                     |  |  |  |

|                        |                                                                                                                                                                                 | -          | enables the PMM mode which forces all functional modules to   |  |  |  |

|                        | operate at divide by 256 clock ratio, independent of the setting of CD1 and CD0. In PMM                                                                                         |            |                                                               |  |  |  |

|                        | mode, if the automatic Switch-Back is activated, and the potential Switch-Back source has                                                                                       |            |                                                               |  |  |  |

|                        | been properly programmed, the PMME bit will be automatically reset to 0 and it will be                                                                                          |            |                                                               |  |  |  |

|                        | impossible to set the PMME bit to a divide by 256 until all potential sources are not active.                                                                                   |            |                                                               |  |  |  |

|                        | Automatic Switch-Back is supported only from the divide by 256 mode. When PMME is                                                                                               |            |                                                               |  |  |  |

|                        | set, it is also impossible to change the CD1 and CD0 setting. The divide ratio for Switch-                                                                                      |            |                                                               |  |  |  |

|                        |                                                                                                                                                                                 |            |                                                               |  |  |  |

| CKCN.3: SWB            | Back and Stop mode exits is determined by the original setting of CD1 and CD0 bits.         Switch-Back Enable. When set to 1, SWB will allow mask enabled external interrupts, |            |                                                               |  |  |  |

| CRCI <b>1.9.</b> 5 W D | -                                                                                                                                                                               |            |                                                               |  |  |  |

|                        | enabled serial port receive functions, or entering into active debug mode to reset the PMME bit                                                                                 |            |                                                               |  |  |  |

|                        | from 1 to 0, allowing the processor to switch back to the original system frequency as selected by                                                                              |            |                                                               |  |  |  |

|                        | the CD1 and CD0 bits. When SWB is cleared to 0, Switch-Back mode is disabled.                                                                                                   |            |                                                               |  |  |  |

|                        | -The first Switch-Back condition is initiated by the detection of a selected edge                                                                                               |            |                                                               |  |  |  |

|                        | transaction on any of the external interrupts when the respective pin has been                                                                                                  |            |                                                               |  |  |  |

|                        | programmed and enabled to issue an interrupt. Note that the Switch-Back                                                                                                         |            |                                                               |  |  |  |

|                        | interrupt relationship requires that the respective external interrupt source be                                                                                                |            |                                                               |  |  |  |

|                        | allowed to actually generate an interrupt, before the Switch-Back will actually                                                                                                 |            |                                                               |  |  |  |

|                        | occur.                                                                                                                                                                          |            |                                                               |  |  |  |

|                        | -The second Switch-Back condition will occur when the Serial Port is enabled to                                                                                                 |            |                                                               |  |  |  |

|                        | receive data and is found to have an active low start bit on the receive input pin.                                                                                             |            |                                                               |  |  |  |

|                        | Serial Port transmit activity will also force a Switch-Back if the SWB is set. Note                                                                                             |            |                                                               |  |  |  |

|                        | that the Serial Port activity, as related to the Switch-Back, is independent of the                                                                                             |            |                                                               |  |  |  |

|                        | Serial Port interrupt relationship.                                                                                                                                             |            |                                                               |  |  |  |

|                        | - The third Switch-Back is triggered by the SPI activity.                                                                                                                       |            |                                                               |  |  |  |

|                        | - The fourth Switch-Back is triggered by entry into active debug mode either by a breakpoint                                                                                    |            |                                                               |  |  |  |

|                        | match or issuance of the debug command.                                                                                                                                         |            |                                                               |  |  |  |

|                        | The automatic Switch-Back is only enabled when the PMME bit has established a divide                                                                                            |            |                                                               |  |  |  |

|                        | by 256 mode and t                                                                                                                                                               | he SWB     | is set to 1.                                                  |  |  |  |

| CKCN.4: STOP           | Stop Mode Select                                                                                                                                                                | Setting    | this bit to 1 stops program execution and commences low power |  |  |  |

| Register     | Description                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------|

|              | operation. This bit is cleared by a reset or any of the enabled external interrupts. Setting and    |

|              | resetting the STOP bit will not change the system clock source and the divide ratio.                |

| CKCN.5: RGMD | Ring Oscillator Mode. This read only bit reflects the selection of clock source. RGMD=1             |

|              | indicates the ring oscillator is providing the system clock. RGMD=0 indicates that the system       |

|              | clock is being derived from the external crystal or clock.                                          |

| CKCN.6: RGSL | Ring Oscillator Select. This bit selects the internal ring oscillator for system clock generation.  |

|              | When RGSL is set to 1, the internal ring oscillator (following the PMME, CD1:0 selected divide      |

|              | ratio) is immediately sourced as the system clock and the internal crystal amplifier and PLL are    |

|              | disabled. When RGSL is cleared to 0, the internal ring oscillator (following the clock divide       |

|              | selection) will continue to serve as the system clock until the crystal warm-up counter has expired |

|              | and PLL output is ready. At which point, that clock (following the PMME, CD1:0 selected divide      |

|              | ratio) is sourced as the system clock. The RGSL bit is cleared to 0 on power-on reset only and is   |

|              | unaffected by other resets.                                                                         |

| CKCN.7: IDLE | IDLE Mode Select. Setting this bit to a 1 stops program execution by halting the Instruction        |

|              | Pointer and disabling the internal module selects (similar to a NOP operation). This provides a     |

|              | low power mode that does not require a crystal warmup on exit.                                      |

| Register           | Description                                                                                                                                                                                                                                                                                                      |             |              |                                                                                                                                    |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| WDCN (0Fh, 08h)    | Watchdog Timer Control                                                                                                                                                                                                                                                                                           |             |              |                                                                                                                                    |  |

| Initialization:    | Bits 5, 4, 3 and 0 are cleared to 0 on all forms of reset. For others, see bit descriptions.                                                                                                                                                                                                                     |             |              |                                                                                                                                    |  |

| Read/Write Access: | Unrestricted Read/Write.                                                                                                                                                                                                                                                                                         |             |              |                                                                                                                                    |  |

| WDCN.0: RWT        | <b>Reset Watchdog Timer.</b> Setting this bit resets the Watchdog Timer count and reset counter. This bit must be set before the Watchdog Timer expires, or a Watchdog Timer reset and/or interrupt will be generated if enabled. The time-out period is defined by WD1 and WD0. This bit is always 0 when read. |             |              |                                                                                                                                    |  |

| WDCN.1: EWT        | Enable Wa                                                                                                                                                                                                                                                                                                        | atchdog     | Timer Re     | eset. Setting this bit to 1 enables the Watchdog Timer to reset                                                                    |  |

|                    | the device;                                                                                                                                                                                                                                                                                                      | clearing t  | his bit to ( | 0 disables the Watchdog Timer reset. It has no effect on the                                                                       |  |

|                    | Timer itself                                                                                                                                                                                                                                                                                                     | and its a   | bility to g  | enerate a Watchdog interrupt. This bit is cleared following a                                                                      |  |

|                    | power-on r                                                                                                                                                                                                                                                                                                       | eset and u  | unaffected   | l by all other resets.                                                                                                             |  |

| WDCN.2: WTRF       | Watchdog                                                                                                                                                                                                                                                                                                         | Timer F     | Reset Flag   | g. When set, this bit indicates that a Watchdog Timer reset has                                                                    |  |

|                    | occurred. I                                                                                                                                                                                                                                                                                                      | t is typica | lly interrog | gated to determine if a reset was caused by the Watchdog                                                                           |  |

|                    | Timer. It is                                                                                                                                                                                                                                                                                                     | cleared b   | y power-o    | on reset but otherwise must be cleared by software before the                                                                      |  |

|                    | next reset of                                                                                                                                                                                                                                                                                                    | of any kin  | d to allow   | software to work correctly. Setting this bit by software will                                                                      |  |

|                    | not generat                                                                                                                                                                                                                                                                                                      | e a Watch   | ndog Time    | er reset. If EWT bit is cleared, the Watchdog Timer has no                                                                         |  |

|                    | effect on th                                                                                                                                                                                                                                                                                                     | nis bit.    |              |                                                                                                                                    |  |

| WDCN.3: WDIF       | <b>Watchdog Interrupt Flag.</b> This bit is set to 1 by a Watchdog time-out which indicates a Watchdog Timer event has occurred if EWT and/or EWDI are set. When the WDIF is s and EWDI determine the action to be taken. Setting this bit from 0 to 1 also activates the                                        |             |              | curred if EWT and/or EWDI are set. When the WDIF is set, EWT on to be taken. Setting this bit from 0 to 1 also activates the reset |  |

|                    |                                                                                                                                                                                                                                                                                                                  |             | 0            | et time-out which allows 512 system cycles for the system to reset                                                                 |  |

|                    | the Watchdog Timer via the RWT bit. Setting this bit in software will generate a Watchdog                                                                                                                                                                                                                        |             |              |                                                                                                                                    |  |

|                    | -                                                                                                                                                                                                                                                                                                                |             | 00           | r the reset counter. This bit must be cleared in software before                                                                   |  |

|                    | be cleared l                                                                                                                                                                                                                                                                                                     |             |              | utine, or another interrupt will be generated. The reset counter must                                                              |  |

|                    | EWT                                                                                                                                                                                                                                                                                                              | EWDI        |              | Actions                                                                                                                            |  |

|                    | х                                                                                                                                                                                                                                                                                                                | х           | 0            | No interrupt has occurred.                                                                                                         |  |

|                    | 0                                                                                                                                                                                                                                                                                                                | 0           | х            | Watchdog disable, clock is gated off.                                                                                              |  |

|                    | 0                                                                                                                                                                                                                                                                                                                | 1           | 1            | Watchdog interrupt has occurred.                                                                                                   |  |

|                    | 1                                                                                                                                                                                                                                                                                                                | 0           | 1            | No interrupt has been generated. Watchdog reset will                                                                               |  |

|                    |                                                                                                                                                                                                                                                                                                                  |             |              | occur in 512 system clock cycles if RWT is not set or WDIF                                                                         |  |

|                    |                                                                                                                                                                                                                                                                                                                  |             |              | is not cleared.                                                                                                                    |  |

|                    | 1                                                                                                                                                                                                                                                                                                                | 1           | 1            | Watchdog interrupt has occurred. Watchdog reset will                                                                               |  |

|                    |                                                                                                                                                                                                                                                                                                                  |             |              | occur in 512 system clock cycles if RWT is not set or WDIF                                                                         |  |

|                    |                                                                                                                                                                                                                                                                                                                  |             |              | is not cleared.                                                                                                                    |  |

| Register           | Description                                                                                                                                                                                                            |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| WDCN.4: WD0        | Watchdog Timer Mode Select Bit 0.                                                                                                                                                                                      |  |  |  |  |

| WDCN.5: WD1        | Watchdog Timer Mode Select Bit 1.                                                                                                                                                                                      |  |  |  |  |

|                    | These bits are used to provide a user selection of Watchdog Timer interrupt periods which                                                                                                                              |  |  |  |  |

|                    | determine the Watchdog Timer interrupt time-out when the Watchdog Timer is enabled. All                                                                                                                                |  |  |  |  |

|                    | Watchdog Timer reset time-outs follow the programmed interrupt time-outs by 512 times the                                                                                                                              |  |  |  |  |

|                    | clock divide ratio oscillator cycles. Changing the WD1:0 bit settings will reset the                                                                                                                                   |  |  |  |  |

|                    | Watchdog timer unless the 512 system clock reset counter has already started, in which case,                                                                                                                           |  |  |  |  |

|                    | changing the WD1:0 bits will not effect the Watchdog timer or reset counter.                                                                                                                                           |  |  |  |  |

| WDCN.6: EWDI       | Watchdog Interrupt Enable. Setting this bit to 1 enables interrupt requests generated                                                                                                                                  |  |  |  |  |

|                    | by the Watchdog Timer. Clearing this bit to 0 disables the interrupt requests. This bit is                                                                                                                             |  |  |  |  |

|                    | cleared following a power-on reset and unaffected by all other resets.                                                                                                                                                 |  |  |  |  |

| WDCN.7: POR        | <b>Power-On Reset Flag.</b> This bit indicates whether the last reset was a power-on/brown-out                                                                                                                         |  |  |  |  |

|                    | reset. This bit is typically interrogated following a reset. It must be cleared before the next                                                                                                                        |  |  |  |  |

|                    | reset of any kind for software to work correctly. This bit is set following a power-on/                                                                                                                                |  |  |  |  |

|                    | brown-out reset and unaffected by all other resets.                                                                                                                                                                    |  |  |  |  |

| A0 (00h, 09h)      | Accumulator 0                                                                                                                                                                                                          |  |  |  |  |

| Initialization:    | All bits are cleared to 0 on all forms of reset.                                                                                                                                                                       |  |  |  |  |

| Read/Write Access: | Unrestricted direct Read/Write.                                                                                                                                                                                        |  |  |  |  |

| A0.15 - A0.0       | Accumulator 0 bits 15:0. This register serves as the accumulator for arithmetic and logical operation                                                                                                                  |  |  |  |  |

|                    | when activated by the Accumulator Pointer. Otherwise, it can be used as general-purpose working register.                                                                                                              |  |  |  |  |

| A1 (01h, 09h)      | Accumulator 1                                                                                                                                                                                                          |  |  |  |  |

| Initialization:    | All bits are cleared to 0 on all forms of reset.                                                                                                                                                                       |  |  |  |  |

| Read/Write Access: | Unrestricted direct Read/Write.                                                                                                                                                                                        |  |  |  |  |

| A1.15 – A1.0       | Accumulator 1 bits 15:0. This register serves as the accumulator for arithmetic and logical operation when activated by the Accumulator Pointer. Otherwise, it can be used as general-purpose working register.        |  |  |  |  |

| A2 (02h, 09h)      | Accumulator 2                                                                                                                                                                                                          |  |  |  |  |

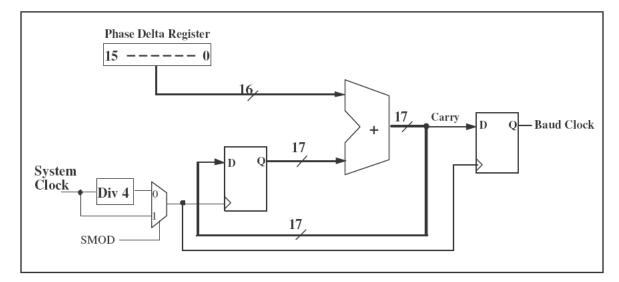

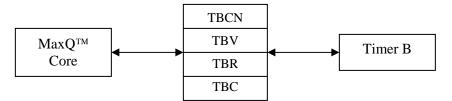

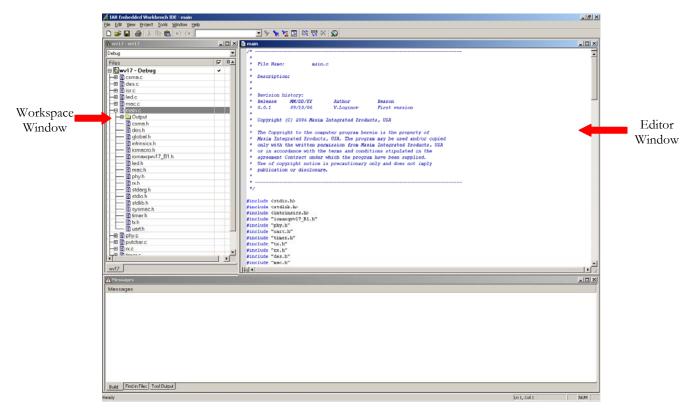

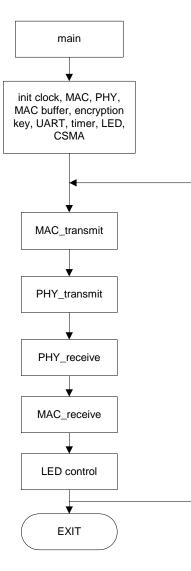

| Initialization:    | All bits are cleared to 0 on all forms of reset.                                                                                                                                                                       |  |  |  |  |