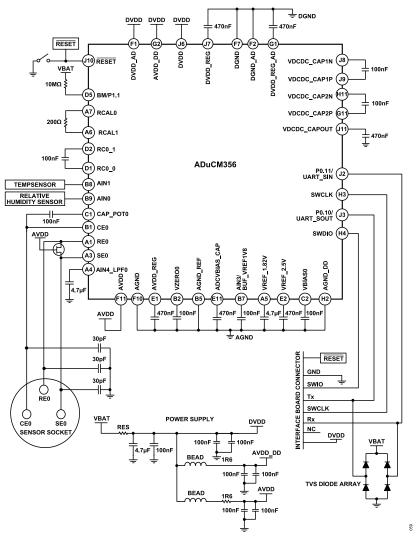

#### ADuCM356 Hardware Reference Manual

#### PREFACE

The ADuCM356 hardware reference manual published by Analog Devices, Inc., employs the following terminology to indicate actions, functions, and processes that are mandatory in ensuring that the ADuCM356 performs to the standards established by the ISO 26262-2018:

- ▶ Required, requires, requirement: indicates no other option.

- Must: indicates an obligatory action.

- ▶ Can: indicates a possible option.

- ▶ May: indicates either optional or permissible, context dependent.

- Should: a recommended condition or action that is not required but that reflects best practice.

- Comply, complies, compliance: meets specifications or other requirements provided by a secondary source, such as a data sheet.

- Obligation: refers to the responsibility of the user, including a potential legal responsibility.

- Must not: refrain from taking an action or refrain from causing a condition.

- ▶ Do not: refrain from taking an action.

#### SCOPE

This reference manual provides a detailed description of the functionality and features of the ADuCM356.

Full specifications on the ADuCM356 are available in the product data sheet. Consult the data sheet in conjunction with this reference manual when working with this device. Refer to the ADuCM356 data sheet for the functional block diagram.

| Preface                                       | 1   |

|-----------------------------------------------|-----|

| Scope                                         | 1   |

| Using the ADuCM356 Hardware Reference         |     |

| Manual                                        |     |

| Number Notations                              |     |

| Register Access Conventions                   |     |

| ADuCM356 Overview                             | .10 |

| Main Features of the ADuCM356                 | .10 |

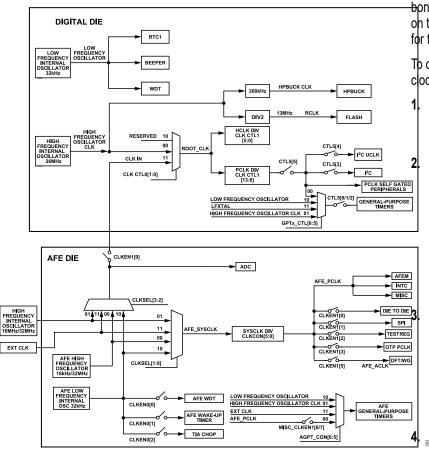

| Clocking Architecture                         |     |

| Clocking Architecture Operation               | .12 |

| Required Clock Ratio Between Digital Die      |     |

| and Analog Die System Clocks                  | .12 |

| Digital Die Clock Features                    | .12 |

| Analog Die Clock Features                     | .12 |

| Clock Gating                                  | .13 |

| Connecting AFE Die Clock to Digital Die       |     |

| Clock Input                                   | 13  |

| Register Summary: Clock Architecture          | .15 |

| Register Details: Clock Architecture          | .16 |

| Key Protection for CTL Register               | .16 |

| Oscillator Control Register                   | 16  |

| Clock Control 0 Register                      | 16  |

| Clock Dividers Register                       | .17 |

| User Clock Gating Control Register            | 17  |

| Clocking Status Register                      | .18 |

| Clock Divider Configuration Register          | 18  |

| Clock Gate Enable Register                    |     |

| Clock Select Register                         | .19 |

| GPIO Clock Mux Select to GPIO1 Pin            |     |

| Register                                      |     |

| Key Protection for CLKCON0 Register           | 20  |

| Clock Control of Low-Power TIA Chop,          |     |

| Watchdog, and Wake-Up Timers Register         | 20  |

| Key Protection for OSCCON Register            | .21 |

| Oscillator Control Register                   | 21  |

| High-Power Oscillator Configuration Register. |     |

| Power Mode Configuration Register             | 22  |

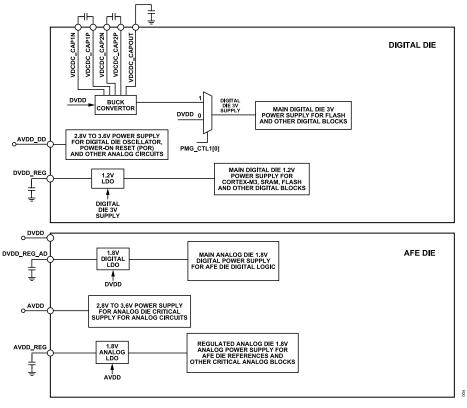

| Power Management Unit                         | .23 |

| Power Management Unit Features                | .23 |

| Power Management Unit Operation               | .23 |

| Code Examples                                 |     |

| Monitor Voltage Control                       | .25 |

| Register Summary: Power Management Unit       | 27  |

| Register Details: Power Management Unit       |     |

| Power Supply Monitor Interrupt Enable         |     |

| Register                                      |     |

| Power Supply Monitor Status Register          | .28 |

| Power Mode Register                           | .29 |

|                                               |     |

| SRAMRET Register       29         Control for Retention SRAM During       Hibernate Mode Register       29         High-Power Buck Control Register       30         Control for SRAM Parity and Instruction       SRAM Register       30         Initialization Status Register       31         Power Modes Register       32         Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor       33         Arm Cortex-M3 Processor Features       33         Arm Cortex-M3 Processor Related       34         Documents       34         System Resets       35         Digital Die Reset Operation       35         Register Details: System Resets       36         Register Details: System Resets       37         Analog Die Status Register       37         Analog Die Status Register       37         Programming, Protection, and Debug       38         Safety Features       38         Safety Features       38         System Exceptions and Peripheral Interrupts       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         External Interrupts       45         External Interrupt Con                                                             | Key Protection for PWRMOD and           |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|

| Hibernate Mode Register       29         High-Power Buck Control Register       30         Control for SRAM Parity and Instruction       SRAM Register         SRAM Register       30         Initialization Status Register       31         Power Modes Register       32         Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor Features       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Related       0         Documents       34         System Resets       35         Digital Die Reset Operation       35         Register Details: System Resets       37         Digital Die Reset Status Register       37         Anlog Die Status Register       37         Analog Die Status Register       37         Programming, Protection, and Debug       38         Security Features       38         Safety Features       38         System Exceptions and Peripheral Interrupts       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         Cortex-M3 NVIC Register List       42                                                                             | SRAMRET Register                        | . 29 |

| High-Power Buck Control Register       30         Control for SRAM Parity and Instruction       SRAM Register       30         Initialization Status Register       31         Power Modes Register       32         Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor Features       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Operation       34         System Resets       35         Digital Die Reset Operation       35         Register Details: System Resets       36         Register Details: System Resets       37         Digital Die Reset Status Register       37         Analog Die Status Register       37         Analog Die Status Register       38         Socting       38         Security Features       38         Safety Features       38         Safety Features       38         Safety Features       38         Safety Features       38         Sortex-M3 and Fault Management       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         Exter                                                                                       | Control for Retention SRAM During       |      |

| High-Power Buck Control Register       30         Control for SRAM Parity and Instruction       SRAM Register       30         Initialization Status Register       31         Power Modes Register       32         Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor Features       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Operation       34         System Resets       35         Digital Die Reset Operation       35         Register Details: System Resets       36         Register Details: System Resets       37         Digital Die Reset Status Register       37         Analog Die Status Register       37         Analog Die Status Register       38         Socting       38         Security Features       38         Safety Features       38         Safety Features       38         Safety Features       38         Safety Features       38         Sortex-M3 and Fault Management       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         Exter                                                                                       | Hibernate Mode Register                 | . 29 |

| SRAM Register       30         Initialization Status Register       31         Power Modes Register       32         Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor       33         Arm Cortex-M3 Processor Coperation       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Related       Documents         Documents       34         System Resets       35         Digital Die Reset Operation       35         Register Summary: System Resets       36         Register Details: System Resets       37         Digital Die Reset Status Register       37         Analog Die Status Register       37         Analog Die Status Register       37         Programming, Protection, and Debug       38         Soting       38         Safety Features       38         Safety Features       38         System Exceptions and Peripheral Interrupts       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         External Interrupt Co                                                                              |                                         |      |

| Initialization Status Register       31         Power Modes Register       32         Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor       33         Arm Cortex-M3 Processor Coperation       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Related       0         Documents       34         System Resets       35         Digital Die Reset Operation       35         Register Summary: System Resets       36         Register Details: System Resets       37         Digital Die Reset Status Register       37         Always On Reset Status Register       37         Analog Die Status Register       38         Sofety Features       38         Safety Features       38 <td< td=""><td>Control for SRAM Parity and Instruction</td><td></td></td<>                                                                                 | Control for SRAM Parity and Instruction |      |

| Power Modes Register.       32         Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor.       33         Arm Cortex-M3 Processor Coperation.       33         Arm Cortex-M3 Processor Operation.       33         Arm Cortex-M3 Processor Related       0         Documents.       34         System Resets.       35         Digital Die Reset Operation.       35         Register Summary: System Resets.       36         Register Details: System Resets.       37         Digital Die Reset Status Register.       37         Always On Reset Status Register.       37         Analog Die Status Register.       38         Sooting.       38         Sotty Features.       38         Safety Features.       38         System Exceptions and Peripheral Interrupts.       39         Interrupt Sources from the Analog Die.       41         Clearing Analog Die Interrupt Sources.       42         Cortex-M3 NVIC Register List.       42         Cortex-M3 NVIC Register List.       42         Cortex-M3 NVIC Register Exceptions and       44         Register Summary: System Exceptions and       42         Peripheral Interrupt Configuration 0 Register.                                                           |                                         |      |

| Key Protection for PWRMOD Register       32         Arm Cortex-M3 Processor       33         Arm Cortex-M3 Processor Coperation       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Related       0         Documents       34         System Resets       35         Digital Die Reset Operation       35         Register Summary: System Resets       37         Digital Die Reset Status Register       37         Always On Reset Status Register       37         Analog Die Status Register       38         Socting       38         Security Features       38         Safety Features       38         System Exceptions and Peripheral Interrupts       39         Cortex-M3 and Fault Management       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         External Interrupt Configuration       43         Register Details: System Exceptions and       44         Peripheral Interrupt Configuration 0 Register       45         External Interrupt Configuration 0 Register       46         Nonmaskable Interrupt Clear Register                                                     |                                         |      |

| Arm Cortex-M3 Processor       33         Arm Cortex-M3 Processor Features       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Related       34         Documents       34         System Resets       35         Digital Die Reset Operation       35         Register Summary: System Resets       36         Register Details: System Resets       37         Digital Die Reset Status Register       37         Always On Reset Status Register       37         Analog Die Status Register       38         Soting       38         Security Features       38         Safety Features       38         System Exceptions and Peripheral Interrupts       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         External Interrupt Configuration       43         Register Details: System Exceptions and       9         Peripheral Interrupt Configuration 0 Register       45         External Interrupt Configuration 0 Register       45         External Interrupt Configuration 0 Register       46         Analog Die Interrupt Status Register <td></td> <td></td>                          |                                         |      |

| Arm Cortex-M3 Processor Features       33         Arm Cortex-M3 Processor Operation       33         Arm Cortex-M3 Processor Related       0         Documents       34         System Resets       35         Digital Die Reset Operation       35         Register Summary: System Resets       36         Register Details: System Resets       37         Digital Die Reset Status Register       37         Always On Reset Status Register       37         Analog Die Status Register       37         Programming, Protection, and Debug       38         Booting       38         Safety Features       38         Safety Features       38         System Exceptions and Peripheral Interrupts       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         External Interrupt Configuration       43         Register Details: System Exceptions and       9         Peripheral Interrupt Configuration 0 Register       45         External Interrupt Configuration 0 Register       46         Nonmaskable Interrupt Clear Register       46         Analog Die Interrupt Status Register<                                           |                                         |      |

| Arm Cortex-M3 Processor Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |      |

| Arm Cortex-M3 Processor Related       34         Documents.       35         Digital Die Resets       35         Digital Die Reset Operation.       35         Register Summary: System Resets.       36         Register Details: System Resets.       37         Digital Die Reset Status Register.       37         Always On Reset Status Register.       37         Analog Die Status Register.       37         Programming, Protection, and Debug.       38         Booting.       38         Security Features.       38         Safety Features.       38         System Exceptions and Peripheral Interrupts.       39         Interrupt Sources from the Analog Die.       41         Clearing Analog Die Interrupt Sources.       42         Cortex-M3 NVIC Register List.       42         External Interrupt Configuration.       43         Register Summary: System Exceptions and       44         Peripheral Interrupt Configuration 0 Register.       45         External Interrupt Configuration 0 Register.       46         Nonmaskable Interrupt Clear Register.       46         Analog Die Interrupt Enable Register.       46         Analog Die Interrupt Enable Register.       46                                                    |                                         |      |

| Documents.34System Resets.35Digital Die Reset Operation.35Register Summary: System Resets.36Register Details: System Resets.37Digital Die Reset Status Register.37Always On Reset Status Register.37Analog Die Status Register.37Programming, Protection, and Debug.38Booting.38Security Features.38Safety Features.38System Exceptions and Peripheral Interrupts.39Cortex-M3 and Fault Management.39Interrupt Sources from the Analog Die.41Clearing Analog Die Interrupt Sources.42Cortex-M3 NVIC Register List.42External Interrupt Configuration.43Register Summary: System Exceptions and44Peripheral Interrupt Configuration 0 Register.45External Nake-Up Interrupt Status Register.46Nonmaskable Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Enable Register.46Analog Die Interrupt Enable Register.46Analog Die Circuitry Summary.48ADC, High-Speed DAC, and Associated48Amplifiers Operating Mode Configuration48Register Summary: Analog Die Circuitry                                                                                                                                                                                                                 |                                         | . 33 |

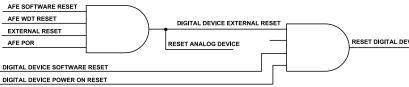

| System Resets.       35         Digital Die Reset Operation.       35         Register Summary: System Resets.       36         Register Details: System Resets.       37         Digital Die Reset Status Register.       37         Always On Reset Status Register.       37         Analog Die Status Register.       37         Programming, Protection, and Debug.       38         Booting.       38         Security Features.       38         Safety Features.       38         System Exceptions and Peripheral Interrupts.       39         Interrupt Sources from the Analog Die.       41         Clearing Analog Die Interrupt Sources.       42         Cortex-M3 NVIC Register List.       42         External Interrupt Configuration.       43         Register Summary: System Exceptions and       9         Peripheral Interrupts.       44         Register Details: System Exceptions and       9         Peripheral Interrupt Configuration 0 Register.       46         Nonmaskable Interrupt Clear Register.       46         Nonmaskable Interrupt Enable Register.       46         Analog Die Interrupt Enable Register.       46         Analog Die Interrupt Summary.       48                                                    |                                         |      |

| Digital Die Reset Operation       35         Register Summary: System Resets       36         Register Details: System Resets       37         Digital Die Reset Status Register       37         Always On Reset Status Register       37         Analog Die Status Register       37         Programming, Protection, and Debug       38         Booting       38         Security Features       38         Safety Features       38         System Exceptions and Peripheral Interrupts       39         Cortex-M3 and Fault Management       39         Interrupt Sources from the Analog Die       41         Clearing Analog Die Interrupt Sources       42         Cortex-M3 NVIC Register List       42         External Interrupt Configuration       43         Register Details: System Exceptions and       9         Peripheral Interrupts       44         Register Details: System Exceptions and       9         Peripheral Interrupt Configuration 0 Register       45         External Interrupt Clear Register       46         Nonmaskable Interrupt Clear Register       46         Analog Die Interrupt Enable Register       46         Analog Die Interrupt Enable Register       46         A                                           |                                         |      |

| Register Summary: System Resets.       36         Register Details: System Resets.       37         Digital Die Reset Status Register.       37         Always On Reset Status Register.       37         Always On Reset Status Register.       37         Analog Die Status Register.       37         Programming, Protection, and Debug.       38         Booting.       38         Security Features.       38         System Exceptions and Peripheral Interrupts.       39         Cortex-M3 and Fault Management.       39         Interrupt Sources from the Analog Die.       41         Clearing Analog Die Interrupt Sources.       42         Cortex-M3 NVIC Register List.       42         External Interrupt Configuration.       43         Register Summary: System Exceptions and       44         Register Details: System Exceptions and       44         Peripheral Interrupts.       45         External Interrupt Configuration 0 Register.       46         Nonmaskable Interrupt Clear Register.       46         Analog Die Interrupt Enable Register.       46         Analog Die Circuitry Summary.       48         ADC, High-Speed DAC, and Associated       Amplifiers Operating Mode Configuration       48                      |                                         |      |

| Register Details: System Resets.       37         Digital Die Reset Status Register.       37         Always On Reset Status Register.       37         Analog Die Status Register.       37         Programming, Protection, and Debug.       38         Booting.       38         Security Features.       38         System Exceptions and Peripheral Interrupts.       39         Cortex-M3 and Fault Management.       39         Interrupt Sources from the Analog Die.       41         Clearing Analog Die Interrupt Sources.       42         Cortex-M3 NVIC Register List.       42         External Interrupt Configuration.       43         Register Summary: System Exceptions and       44         Peripheral Interrupts.       45         External Interrupt Configuration 0 Register.       45         External Interrupt Clear Register.       46         Nonmaskable Interrupt Clear Register.       46         Analog Die Circuitry Summary.       48         ADC, High-Speed DAC, and Associated       47         Amplifiers Operating Mode Configuration       48         System Bandwidth Configuration.       48         Register Summary: Analog Die Circuitry.       50                                                                 |                                         |      |

| Digital Die Reset Status Register.37Always On Reset Status Register.37Analog Die Status Register.37Programming, Protection, and Debug.38Booting.38Security Features.38Safety Features.38System Exceptions and Peripheral Interrupts.39Cortex-M3 and Fault Management.39Interrupt Sources from the Analog Die.41Clearing Analog Die Interrupt Sources.42Cortex-M3 NVIC Register List.42External Interrupt Configuration.43Register Summary: System Exceptions and44Peripheral Interrupts.45External Interrupt Configuration 0 Register.45External Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Enable Register.46Analog Die Circuitry Summary.48ADC, High-Speed DAC, and Associated48Amplifiers Operating Mode Configuration48Register Summary: Analog Die Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |      |

| Always On Reset Status Register.       37         Analog Die Status Register.       37         Programming, Protection, and Debug.       38         Booting.       38         Security Features.       38         Safety Features.       38         System Exceptions and Peripheral Interrupts.       39         Cortex-M3 and Fault Management.       39         Interrupt Sources from the Analog Die.       41         Clearing Analog Die Interrupt Sources.       42         Cortex-M3 NVIC Register List.       42         External Interrupt Configuration.       43         Register Summary: System Exceptions and       9         Peripheral Interrupts.       44         Register Details: System Exceptions and       9         Peripheral Interrupt Configuration 0 Register.       45         External Interrupt Clear Register.       46         Nonmaskable Interrupt Clear Register.       46         Analog Die Interrupt Enable Register.       46         Analog Die Circuitry Summary.       48         ADC, High-Speed DAC, and Associated       48         Amplifiers Operating Mode Configuration       48         System Bandwidth Configuration.       48         Register Summary: Analog Die Circuitry.       50 <td></td> <td></td> |                                         |      |

| Analog Die Status Register.       37         Programming, Protection, and Debug.       38         Booting.       38         Security Features.       38         Safety Features.       38         System Exceptions and Peripheral Interrupts.       39         Cortex-M3 and Fault Management.       39         Interrupt Sources from the Analog Die.       41         Clearing Analog Die Interrupt Sources.       42         Cortex-M3 NVIC Register List.       42         External Interrupt Configuration.       43         Register Summary: System Exceptions and       44         Peripheral Interrupts.       45         External Interrupt Configuration 0 Register.       45         External Interrupt Clear Register.       46         Nonmaskable Interrupt Clear Register.       46         Analog Die Interrupt Enable Register.       46         Analog Die Interrupt Enable Register.       46         Analog Die Circuitry Summary.       48         ADC, High-Speed DAC, and Associated       Amplifiers Operating Mode Configuration                                                                                                                                                                                                       |                                         |      |

| Programming, Protection, and Debug.38Booting.38Security Features.38Safety Features.38System Exceptions and Peripheral Interrupts.39Cortex-M3 and Fault Management.39Interrupt Sources from the Analog Die.41Clearing Analog Die Interrupt Sources.42Cortex-M3 NVIC Register List.42External Interrupt Configuration.43Register Summary: System Exceptions and44Peripheral Interrupts.44Register Details: System Exceptions and45External Interrupt Configuration 0 Register.45External Interrupt Configuration 0 Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Enable Register.46Analog Die Circuitry Summary.48ADC, High-Speed DAC, and Associated48Amplifiers Operating Mode Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • •                                     |      |

| Booting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |      |

| Security Features.38Safety Features.38System Exceptions and Peripheral Interrupts.39Cortex-M3 and Fault Management.39Interrupt Sources from the Analog Die.41Clearing Analog Die Interrupt Sources.42Cortex-M3 NVIC Register List.42External Interrupt Configuration.43Register Summary: System Exceptions and44Peripheral Interrupts.44Register Details: System Exceptions and45External Interrupt Configuration 0 Register.45External Interrupt Configuration 0 Register.46Nonmaskable Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Enable Register.46Analog Die Interrupt Summary.48ADC, High-Speed DAC, and Associated48Amplifiers Operating Mode Configuration48Register Summary: Analog Die Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |      |

| Safety Features.38System Exceptions and Peripheral Interrupts.39Cortex-M3 and Fault Management.39Interrupt Sources from the Analog Die.41Clearing Analog Die Interrupt Sources.42Cortex-M3 NVIC Register List.42External Interrupt Configuration.43Register Summary: System Exceptions and44Peripheral Interrupts.44Register Details: System Exceptions and45External Interrupt Configuration 0 Register.45External Interrupt Configuration 0 Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Enable Register.46Analog Die Circuitry Summary.48ADC, High-Speed DAC, and Associated48Amplifiers Operating Mode Configuration48Register Summary: Analog Die Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |      |

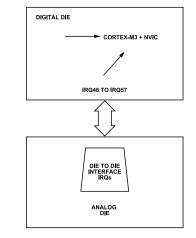

| System Exceptions and Peripheral Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |      |

| Cortex-M3 and Fault Management.39Interrupt Sources from the Analog Die.41Clearing Analog Die Interrupt Sources.42Cortex-M3 NVIC Register List.42External Interrupt Configuration.43Register Summary: System Exceptions and44Peripheral Interrupts.44Register Details: System Exceptions and45External Interrupts.45External Interrupt Configuration 0 Register.46Nonmaskable Interrupt Clear Register.46Analog Die Interrupt Clear Register.46Analog Die Interrupt Enable Register.48ADC, High-Speed DAC, and Associated48Amplifiers Operating Mode Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                       |      |

| Interrupt Sources from the Analog Die                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |      |

| Clearing Analog Die Interrupt Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |      |

| Cortex-M3 NVIC Register List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |      |

| External Interrupt Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |      |

| Register Summary: System Exceptions and         Peripheral Interrupts       44         Register Details: System Exceptions and         Peripheral Interrupts       45         External Interrupt Configuration 0 Register       45         External Wake-Up Interrupt Status Register       46         Nonmaskable Interrupt Clear Register       46         Analog Die Interrupt Enable Register       46         Analog Die Circuitry Summary       48         ADC, High-Speed DAC, and Associated       48         System Bandwidth Configuration       48         Register Summary: Analog Die Circuitry       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                       |      |

| Peripheral Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | . 43 |

| Register Details: System Exceptions and         Peripheral Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | 4.4  |

| Peripheral Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         | .44  |

| External Interrupt Configuration 0 Register45<br>External Wake-Up Interrupt Status Register46<br>External Interrupt Clear Register46<br>Nonmaskable Interrupt Clear Register46<br>Analog Die Interrupt Enable Register46<br>Analog Die Circuitry Summary48<br>ADC, High-Speed DAC, and Associated<br>Amplifiers Operating Mode Configuration48<br>System Bandwidth Configuration48<br>Register Summary: Analog Die Circuitry50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         | 15   |

| External Wake-Up Interrupt Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • •                                     |      |

| External Interrupt Clear Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |      |

| Nonmaskable Interrupt Clear Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |      |

| Analog Die Interrupt Enable Register46<br>Analog Die Circuitry Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                       |      |

| Analog Die Circuitry Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |      |

| ADC, High-Speed DAC, and Associated<br>Amplifiers Operating Mode Configuration 48<br>System Bandwidth Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                       |      |

| Amplifiers Operating Mode Configuration 48<br>System Bandwidth Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | . 40 |

| System Bandwidth Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         | 48   |

| Register Summary: Analog Die Circuitry50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Register Details: Analog Die Circuitry  |      |

| AFE Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |      |

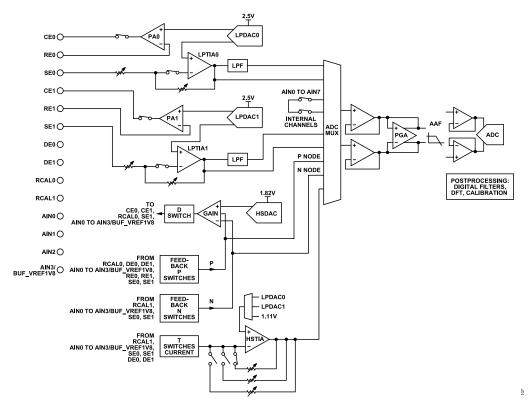

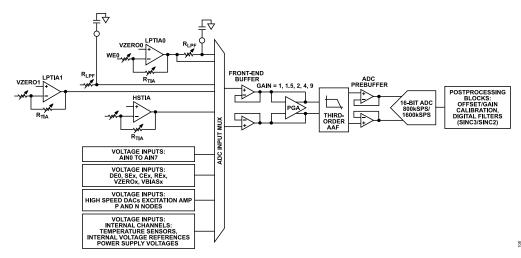

| ADC Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |      |

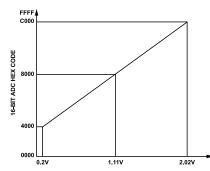

| ADC Circuit Overview                         | 53   |

|----------------------------------------------|------|

| ADC Circuit Features                         | . 53 |

| ADC Circuit Operation                        | 54   |

| ADC Transfer Function                        |      |

| ADC Low-Power Current Input Channels         | 55   |

| ADC Input Circuit                            |      |

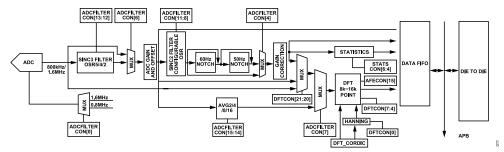

| ADC Postprocessing Filter Options            |      |

| Averaging, Statistics, and Outlier Detection |      |

| Options                                      | .57  |

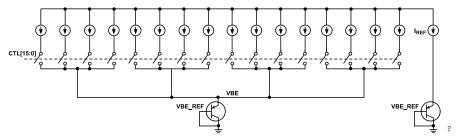

| Internal Temperature Sensor Channels         |      |

| ADC Initialization                           |      |

| ADC Calibration                              |      |

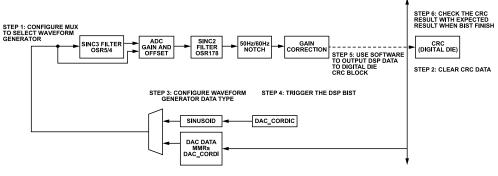

| ADC Digital Signal Processor (DSP) Built In  |      |

| Self Test                                    | 50   |

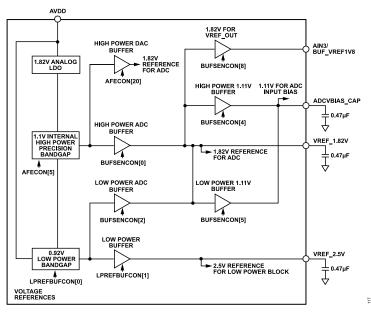

| Voltage Reference Options                    |      |

| Register Summary: ADC Circuit                |      |

| Register Details: ADC Circuit                |      |

|                                              |      |

| ADC Configuration Register                   |      |

| ADC Output Filters Configuration Register    |      |

| Raw Result Register                          |      |

| DFT Result, Real Part Register               |      |

| DFT Result, Imaginary Part Register          | . 66 |

| Sinc2 and Supply Rejection Filter Result     | ~~   |

| Register                                     |      |

| Temperature Sensor 0 Result Register         |      |

| Analog Capture Interrupt Enable Register     |      |

| Analog Capture Interrupt Register            |      |

| AFE DSP Configuration Register               | . 68 |

| Temperature Sensor 0 Configuration           |      |

| Register                                     | . 69 |

| High-Power and Low-Power Buffer Control      |      |

| Register                                     | . 69 |

| Number of Repeat ADC Conversions             |      |

| Register                                     |      |

| Buffer Configuration Register                | .70  |

| Calibration Lock Register                    | .71  |

| Offset Calibration Low-Power TIA0 Channel    |      |

| Register                                     | .71  |

| Gain Calibration for Low-Power TIA0          |      |

| Channel Register                             | 71   |

| Offset Calibration Low-Power TIA1 Channel    |      |

| Register                                     | .72  |

| Gain Calibration for Low-Power TIA1          |      |

| Channel Register                             | 72   |

| Offset Calibration High-Speed TIA Channel    |      |

| Register                                     | .72  |

| Gain Calibration for High-Speed TIA          | _    |

| Channel Register                             | 73   |

| 0                                            | . •  |

| Offset Calibration Voltage Channel (PGA                           |     |

|-------------------------------------------------------------------|-----|

| Gain = 1) Register                                                | 73  |

| Gain Calibration Voltage Input Channel                            |     |

| (PGA Gain = 1) Register                                           | 73  |

| Offset Calibration Voltage Channel (PGA                           |     |

| Gain = 1.5) Register                                              | 73  |

| Gain Calibration Voltage Input Channel                            |     |

| (PGA Gain = 1.5) Register                                         | 74  |

| Offset Calibration Voltage Input Channel                          |     |

| (PGA Gain = 2) Register                                           | 74  |

| Gain Calibration Voltage Input Channel                            |     |

| (PGA Gain = 2) Register                                           | 74  |

| Offset Calibration Voltage Input Channel                          |     |

| (PGA Gain = 4) Register                                           | 75  |

| Gain Calibration Voltage Input Channel                            | 70  |

| (PGA Gain = 4) Register                                           | 76  |

| Offset Calibration Voltage Input Channel                          | 76  |

| (PGA Gain = 9) Register<br>Gain Calibration Voltage Input Channel | 70  |

| (PGA Gain = 9) Register                                           | 76  |

| Offset Calibration Temperature Sensor                             | 70  |

| Channel 0 Register                                                | 76  |

| Gain Calibration Temperature Sensor                               |     |

| Channel 0 Register                                                | 77  |

| Minimum Value Check Register                                      |     |

| Minimum Slow Moving Value Register                                |     |

| Maximum Value Check Register                                      |     |

| Maximum Slow Moving Register                                      | 78  |

| Delta Check Register                                              |     |

| Statistics Module Configuration Register                          |     |

| Mean Output Register                                              |     |

| Key Access for DSPUPDATEEN Register                               |     |

| Digital Logic Test Enable Register                                |     |

| Temperature Sensor 1 Control Register                             | 80  |

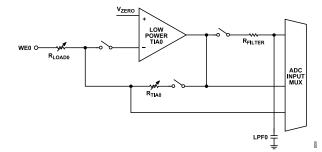

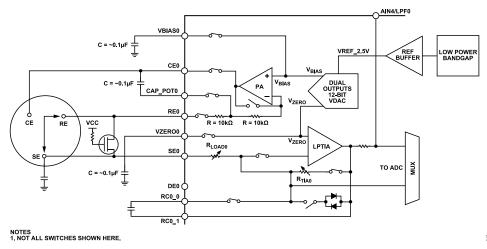

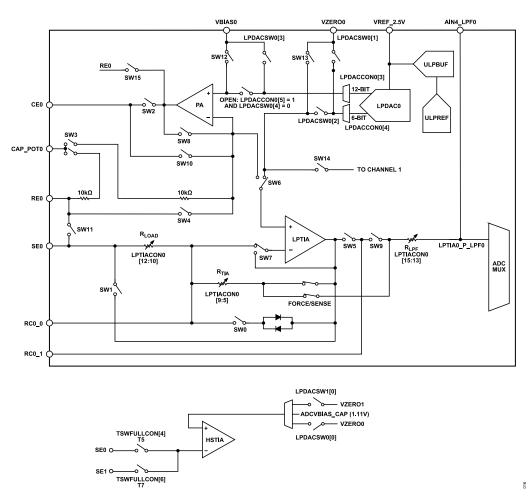

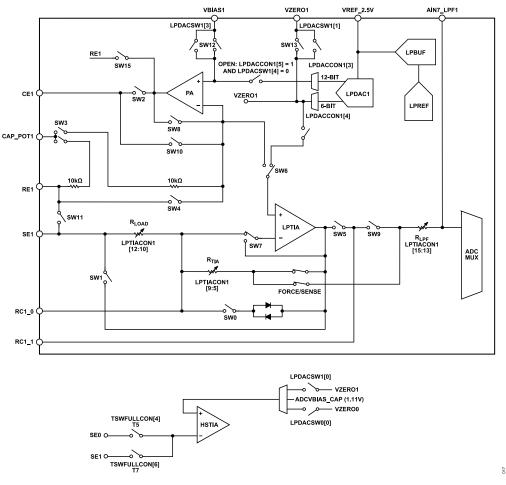

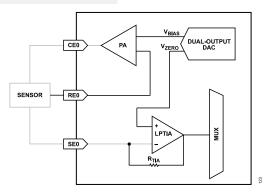

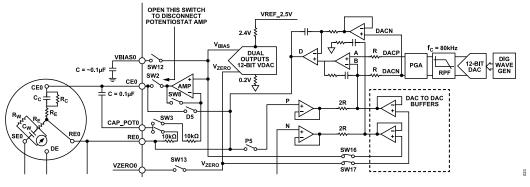

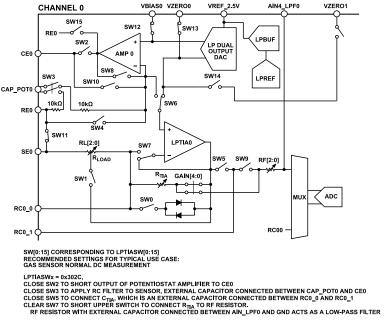

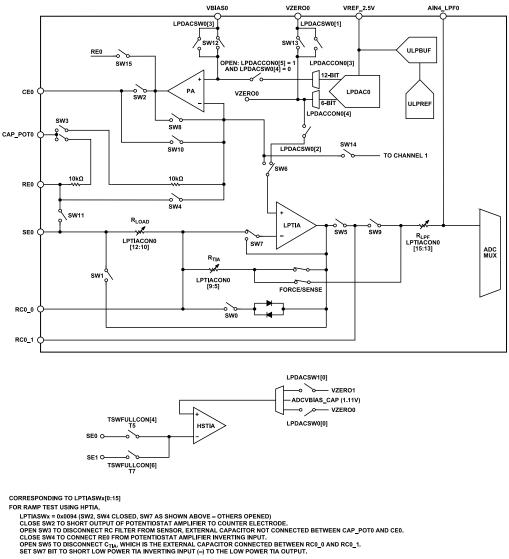

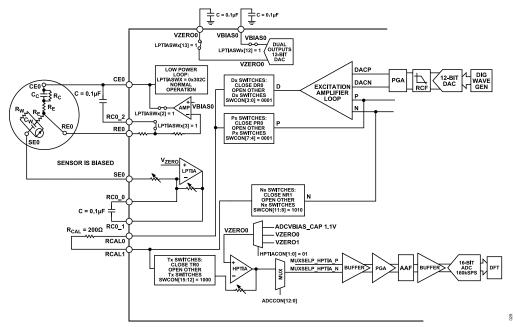

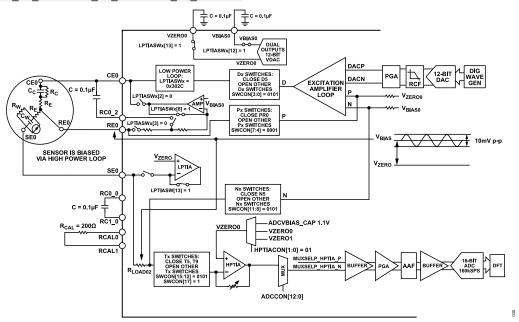

| Low-Power Potentiostat Amplifiers and Low-                        | 0.4 |

| Power TIAs                                                        |     |

| Low-Power Potentiostat Amplifiers                                 |     |

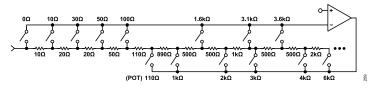

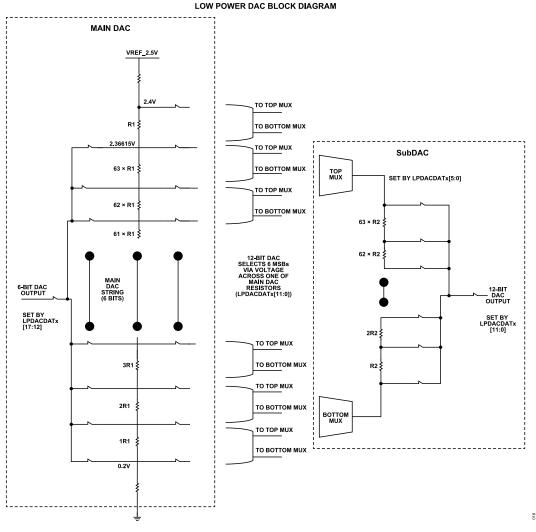

| Low-Power TIAs<br>Low-Power DACs                                  |     |

| Register Summary: Low-Power TIA/                                  | 04  |

| Potentiostat and DAC Circuits                                     | 88  |

| Register Details: Low Power TIA/Potentiostat                      | 00  |

| and DAC Circuits                                                  | 89  |

Low-Power TIA Control Bits Channel 0

Low-Power TIA Switch Configuration for

Low-Power TIA Control Bits Channel 1

Channel 0 Register.....90

Register......91

| Low-Power TIA Switch Configuration for             |     |

|----------------------------------------------------|-----|

| Channel 1 Register                                 | 93  |

| LPDAC0 Data Out Register                           |     |

| LPDAC0 Switch Control Register                     | 94  |

| LPDAC0 Control Register                            | 95  |

| LPDAC1 Data Out Register                           | 96  |

| LPDAC1 Switch Control Register                     | 96  |

| LPDAC1 Control Register                            |     |

| Low-Power Reference Control Register               | 97  |

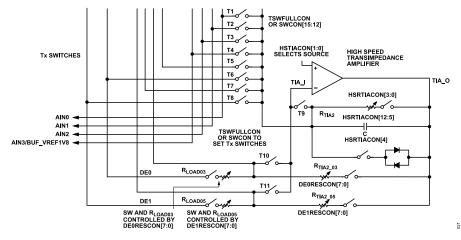

| High-Speed TIA Circuits                            | 98  |

| Key Features                                       | 98  |

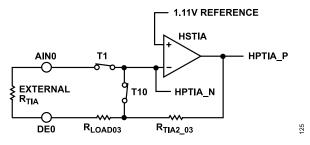

| Using DE0 and DE1 Inputs with the High-            |     |

| Speed TIA                                          | 99  |

| External R <sub>TIA</sub> Selection                |     |

| Register Summary: High-Speed TIA Circuits          | 101 |

| Register Details: High-Speed TIA Circuits          |     |

| High-Speed R <sub>TIA</sub> Configuration Register |     |

| DE1 High-Speed TIA Resistor Configuration          |     |

| Register                                           | 102 |

| DE0 High-Speed TIA Resistor Configuration          |     |

| Register                                           | 102 |

| High-Speed TIA Amplifier Configuration             |     |

| Register                                           | 103 |

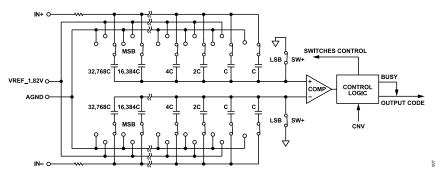

| High-Speed DAC Circuits                            |     |

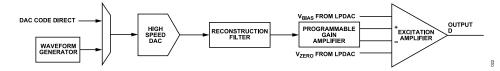

| High-Speed DAC Output Signal Generation            |     |

| High-Speed DAC Core Power Modes                    |     |

| Recommended Configuration in Hibernate             |     |

| Mode                                               | 105 |

| High-Speed DAC Filter Options                      |     |

| High-Speed DAC Output Attenuation                  |     |

| •                                                  | 105 |

| Coupling an AC Signal from High-Speed              |     |

| DAC onto the DC Level Set by Low-Power             |     |

| DAC                                                | 106 |

| Avoiding Incoherency Errors Between                |     |

| Excitation and Measurement Frequencies             |     |

| During Impedance Measurements                      | 106 |

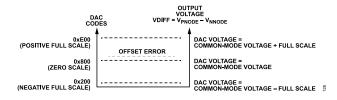

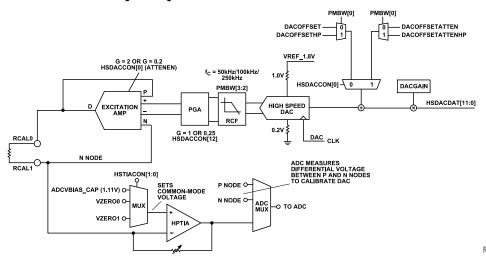

| Calibrating the High-Speed DAC                     |     |

| Register Summary: High-Speed DAC Circuits          |     |

| Register Details: High-Speed DAC Circuits          |     |

| High-Speed DAC Configuration Register              |     |

| Direct Write to DAC Output Control Value           |     |

| Register                                           | 109 |

| DAC DC Buffer Configuration Register               |     |

| DAC Gain Register                                  |     |

| DAC Offset with Attenuator Enabled (Low-           |     |

| Power Mode) Register                               | 110 |

| DAC Offset with Attenuator Disabled (Low-          |     |

| Power Mode) Register                               | 110 |

|                                                    |     |

| DAC Offset with Attenuator Enabled (High-     |       |

|-----------------------------------------------|-------|

| Power Mode) Register                          | . 110 |

| DAC Offset with Attenuator Disabled (High-    |       |

| Power Mode) Register                          | . 111 |

| Waveform Generator Configuration Register.    | 111   |

| Waveform Generator for Sinusoid               |       |

| Frequency Control Word Register               | 111   |

| Waveform Generator for Sinusoid Phase         |       |

| Offset Register                               | 112   |

| Waveform Generator for Sinusoid Offset        | 2     |

| Register                                      | 112   |

| Waveform Generator for Sinusoid Amplitude     | 112   |

|                                               | 110   |

| Register                                      | 112   |

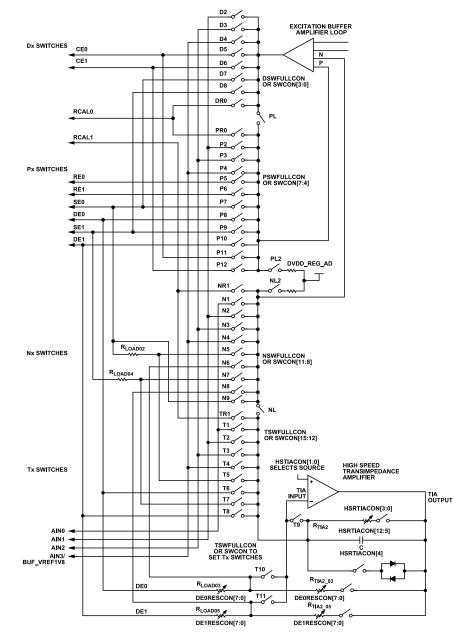

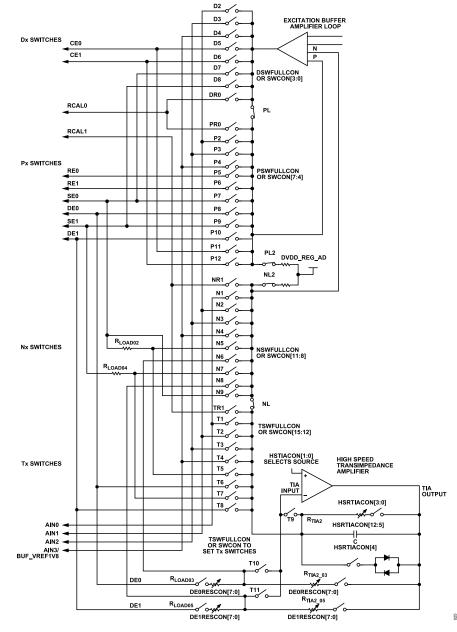

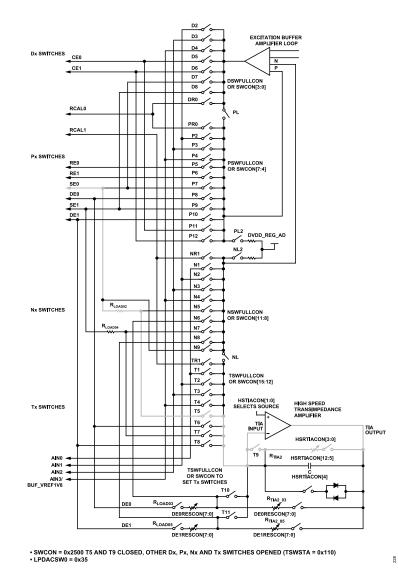

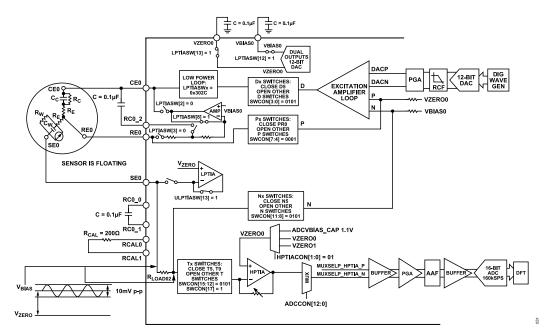

| Programmable Switches Connecting the          |       |

| External Sensor to the High-Speed DAC and     |       |

| High-Speed TIA                                |       |

| Dx Switches                                   |       |

| Px Switches                                   |       |

| Nx Switches                                   |       |

| Tx Switches                                   |       |

| Options for Controlling All Switches          |       |

| Register Summary: Programmable Switches       |       |

| Register Details: Programmable Switches       | 117   |

| Switch Matrix Configuration Register          | 117   |

| Dx Switch Matrix Full Configuration Register. | 118   |

| Nx Switch Matrix Full Configuration Register. |       |

| Px Switch Matrix Full Configuration Register. |       |

| Tx Switch Matrix Full Configuration Register. |       |

| Dx Switch Matrix Status Register              |       |

| Px Switch Matrix Status Register              |       |

| Nx Switch Matrix Status Register              |       |

| Tx Switch Matrix Status Register              |       |

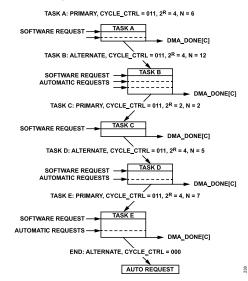

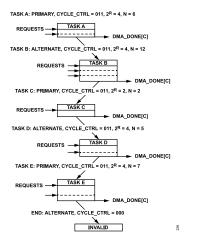

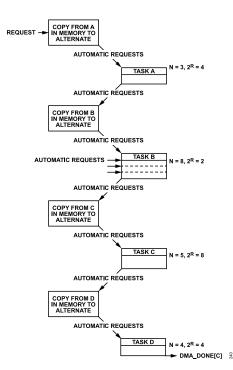

| Sequencer                                     |       |

| Sequencer Features                            |       |

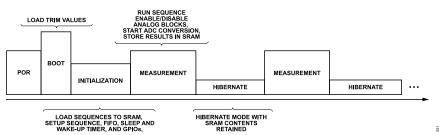

| Sequencer Overview                            |       |

| •                                             |       |

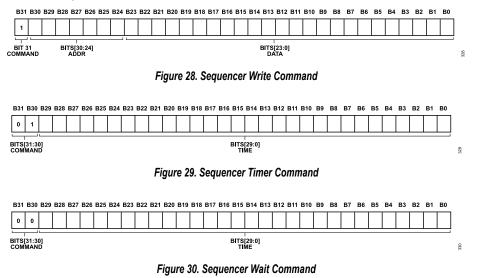

| Sequencer Commands                            |       |

| Sequencer Operation                           |       |

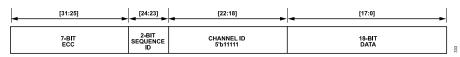

| Sequencer and FIFO Registers                  |       |

| AFE Interrupts                                |       |

| Interrupt Controller Interrupts               |       |

| Configuring the Interrupts                    |       |

| Custom Interrupts                             |       |

| Interrupt Registers                           |       |

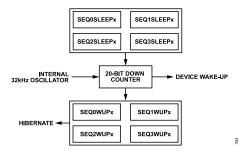

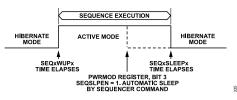

| Sleep and Wake-Up Timer                       |       |

| Sleep and Wake-Up Timer Features              |       |