## AD2426/7/8 Automotive Audio Bus (A<sup>2</sup>B) Transceiver Technical Reference

Revision 1.3, June 2023

Part Number 82-100138-01

# **Copyright Information**

©2023 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

Printed in the USA.

#### Disclaimer

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

#### Trademark and Service Mark Notice

The Analog Devices logo, A<sup>2</sup>B, Blackfin, Blackfin+, CrossCore, EngineerZone, EZ-Board, EZ-KIT, EZ-KIT Lite, EZ-Extender, SHARC, SHARC+, and VisualDSP++ are registered trademarks of Analog Devices, Inc.

EZ-KIT Mini and SigmaStudio are trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

## Contents

#### Preface

| Purpose of This Manual             | 1–1 |

|------------------------------------|-----|

| Intended Audience                  | 1–1 |

| Manual Contents                    | 1–1 |

| What's New in This Manual          | 1–2 |

| Register Documentation Conventions | 1–2 |

### A<sup>2</sup>B Overview

| A <sup>2</sup> B Terminology                  |      |

|-----------------------------------------------|------|

| A <sup>2</sup> B Bus Details                  | 2–4  |

| Functional Description                        |      |

| Architectural Concepts                        |      |

| I <sup>2</sup> C Interface                    |      |

| Transceiver I <sup>2</sup> C Accesses         |      |

| Transceiver I <sup>2</sup> C Access Latencies | 2–13 |

| Pulse-Density Modulation Interface (PDM)      |      |

| PDM Sampling Edge of a Connected Microphone   |      |

| PDM Enhancements                              |      |

| I <sup>2</sup> S/TDM Interface                |      |

| Time Division Multiplexing (TDM) Protocol     |      |

| Mailboxes                                     | 2–19 |

| Mailbox Programming and Operation             |      |

| Mailbox Latency                               |      |

|                                               |      |

### A<sup>2</sup>B Operation and Configuration

| I <sup>2</sup> C Port Programming Concepts |  |

|--------------------------------------------|--|

| Direct I <sup>2</sup> C Register Accesses  |  |

| Remote Target I <sup>2</sup> C Register Accesses                                               |

|------------------------------------------------------------------------------------------------|

| Remote Peripheral I <sup>2</sup> C Accesses                                                    |

| System Bring-Up and Discovery                                                                  |

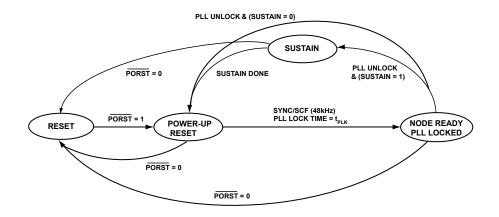

| Reset and Operating States                                                                     |

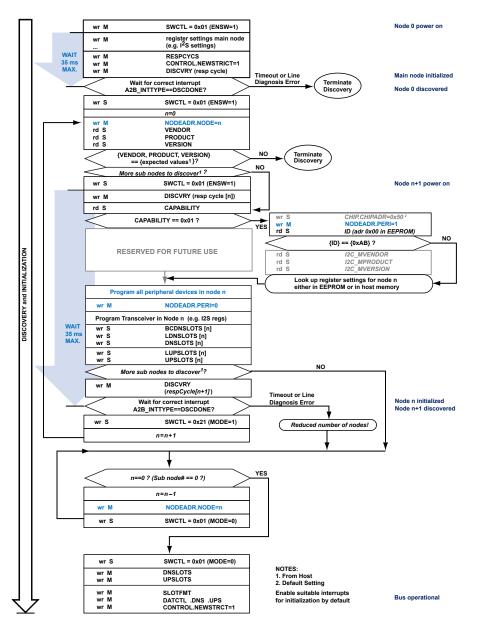

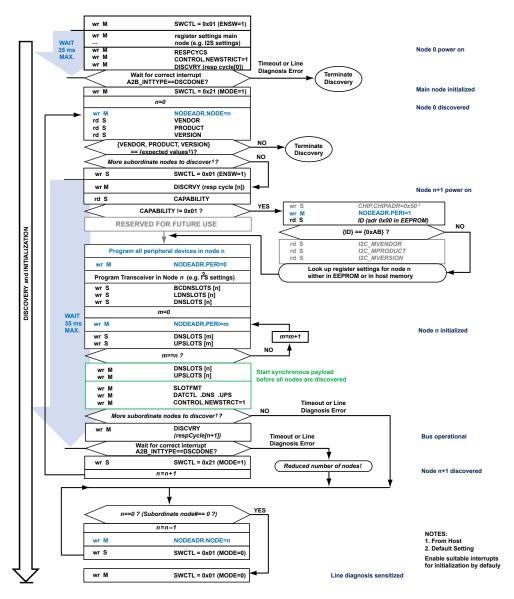

| Main Node Bring-Up and Operation                                                               |

| Subordinate Node Bring-Up and Operation                                                        |

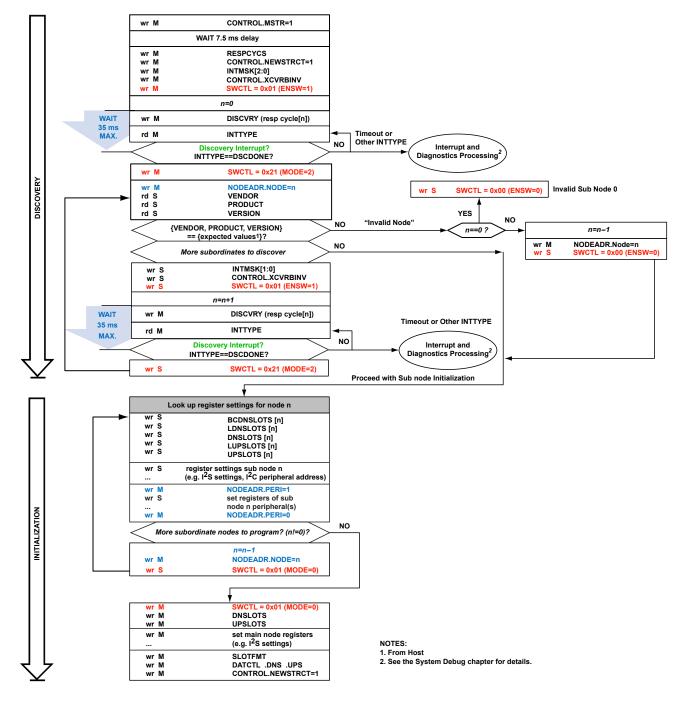

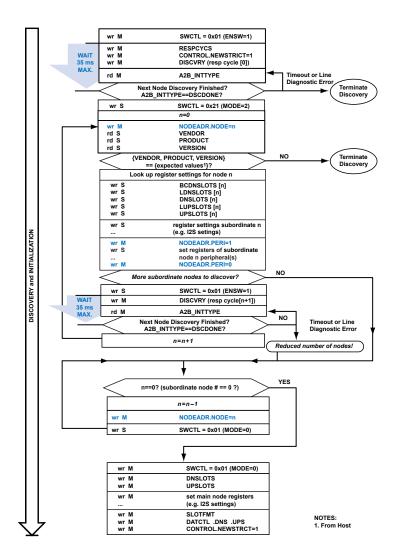

| Node Discovery and Initialization                                                              |

| Simple Discovery Flow                                                                          |

| Response Cycles                                                                                |

| Managing A <sup>2</sup> B System Data Flow                                                     |

| A <sup>2</sup> B Slot Format                                                                   |

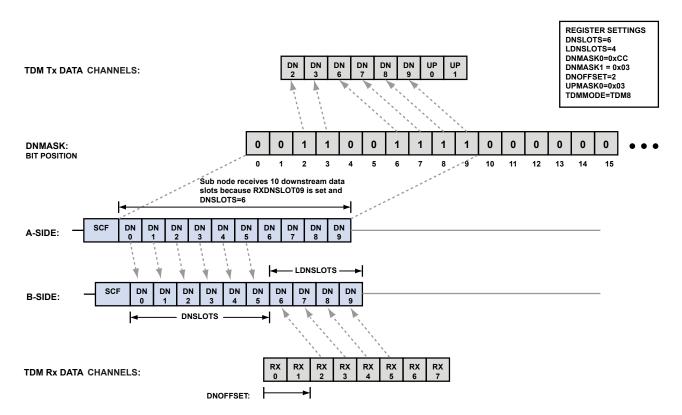

| Downstream Data Slots                                                                          |

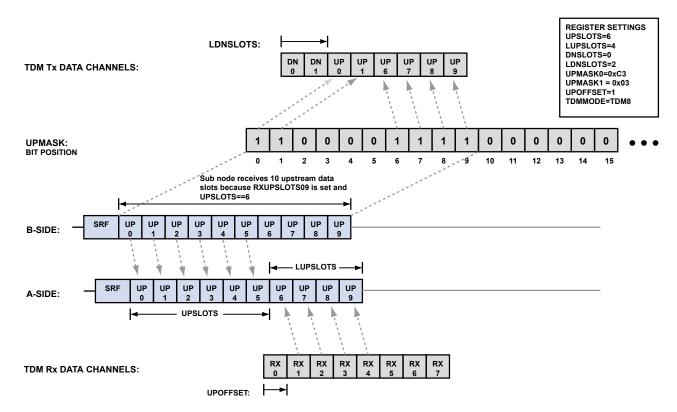

| Upstream Data Slots                                                                            |

| A <sup>2</sup> B Bandwidth                                                                     |

| I <sup>2</sup> S/TDM Port Programming Concepts                                                 |

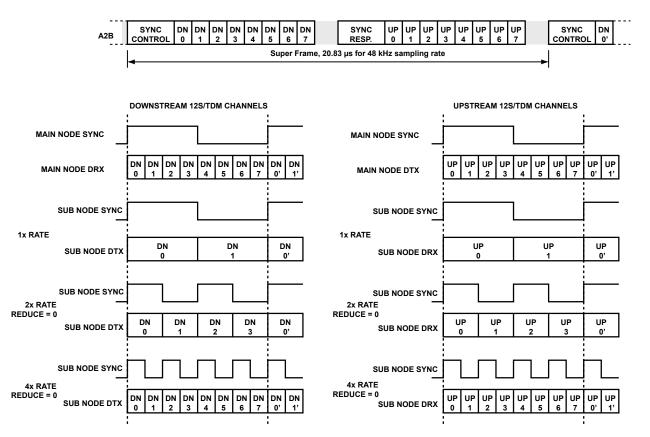

| Synchronizing Subordinate Nodes                                                                |

| I <sup>2</sup> S Reduced Data Rate                                                             |

| I <sup>2</sup> S Reduced Rate Restrictions                                                     |

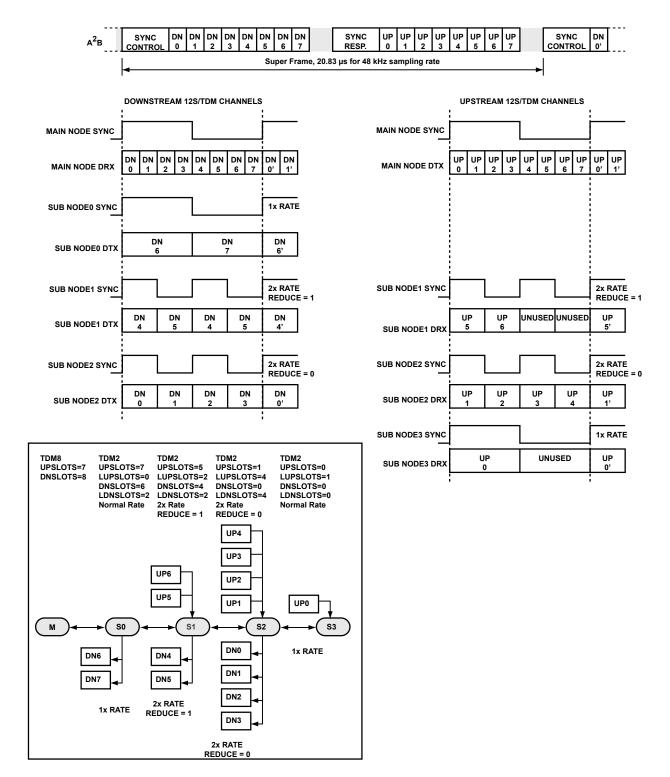

| I <sup>2</sup> S Increased Data Rate                                                           |

| GPIO Over Distance                                                                             |

| GPIO Over Distance Programming Examples                                                        |

| Mapping the Main Node DRX1/IO6 Pin to the Subordinate Node 2 ADR1/IO1 Pin                      |

| Mapping the Subordinate Node 1 DTX1/IO4 Pin to the Main Node ADR1/IO1 Pin                      |

| Mapping the ADR1/IO1 Pins on Subordinate Node 0 Through 2 to the Main Node ADR1/IO1 Pin . 3–36 |

| Transceiver Identification                                                                     |

| Standby Mode                                                                                   |

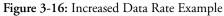

| Bus Monitor Support                                                                            |

| I <sup>2</sup> S/TDM Channel Format                                                            |

| Start Up Sequence                                                                              |

| Optimizing EMC Performance             |  |

|----------------------------------------|--|

| Spread-Spectrum Clocking               |  |

| Programmable LVDS Transmit Levels      |  |

| Data-Only and Power-Only Bus Operation |  |

| Cross-Over or Straight-Through Cabling |  |

## A<sup>2</sup>B Event Control

| Error Management                              |

|-----------------------------------------------|

| Downstream Data Error Detection               |

| Upstream Data Error Detection                 |

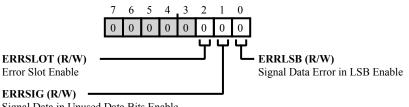

| Data Slot Error Correction                    |

| Control and Response Error Handling4–4        |

| Error Signaling                               |

| A <sup>2</sup> B Communication and Bit Errors |

| Subordinate Node Interrupt Handling4–5        |

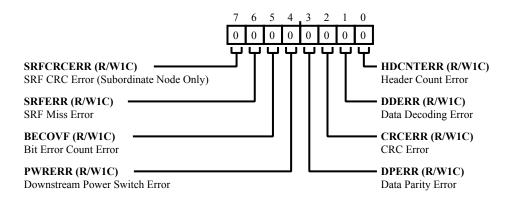

| Error Management Register                     |

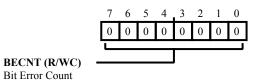

| Bit Error Control Register                    |

| Testing and Debugging                         |

| Unique ID                                     |

## A<sup>2</sup>B System Debug

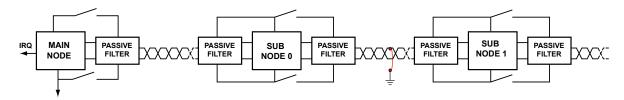

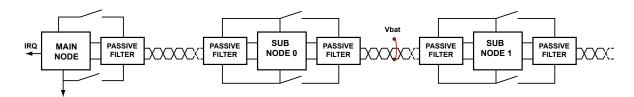

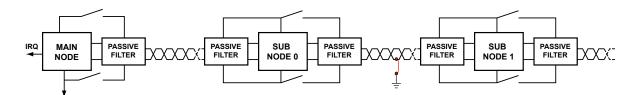

| Line Fault Diagnostics         | 5–1 |

|--------------------------------|-----|

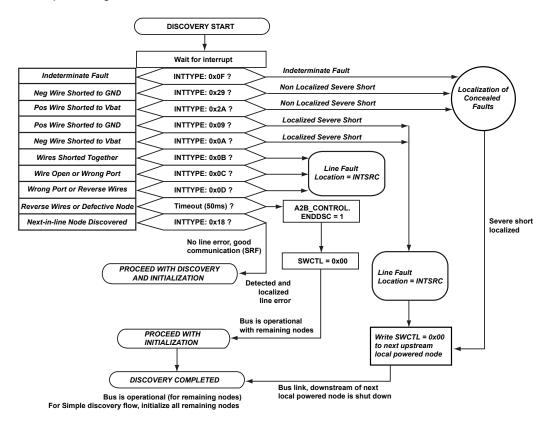

| Diagnostics During Discovery   | 5–1 |

| Registers for Line Diagnostics | 5–3 |

| Open Wire Fault                | 5–3 |

| Short of Wires Fault           | 5–3 |

| Short To GND BP                | 5–4 |

| Short to V <sub>BAT</sub> BN   | 5–4 |

| Short To GND BN                | 5–4 |

| Short to V <sub>BAT</sub> BP   | 5–5 |

| Line Diagnostics After Discovery                           |  |

|------------------------------------------------------------|--|

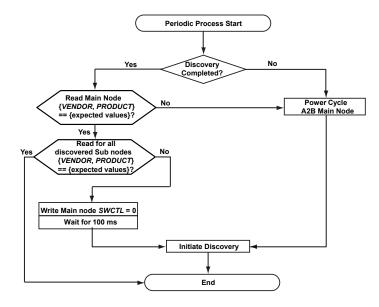

| Diagnostics Software Flow                                  |  |

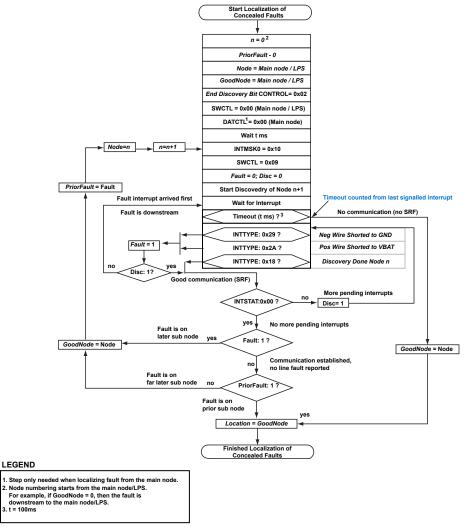

| Localizing Concealed Faults                                |  |

| Bus Drop Detection                                         |  |

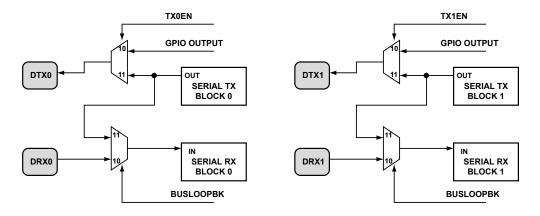

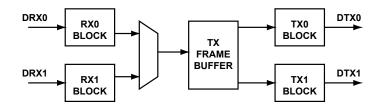

| I <sup>2</sup> S Loopback                                  |  |

| I <sup>2</sup> S TDM Test Mode (I <sup>2</sup> S Loopback) |  |

### Register Summary

### AD2428 A2B Register Descriptions

| I2C Chip Address Register (Target Only)                |

|--------------------------------------------------------|

| Node Address Register (Main Node Only)                 |

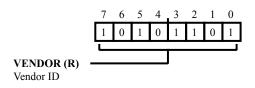

| Vendor ID Register                                     |

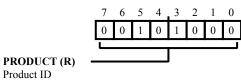

| Product ID Register                                    |

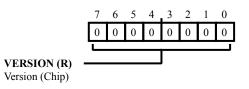

| Version ID Register                                    |

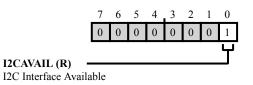

| Capability ID Register                                 |

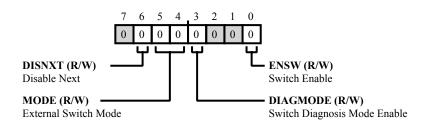

| Switch Control Register                                |

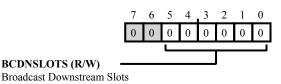

| Broadcast Downstream Slots Register (Subordinate Only) |

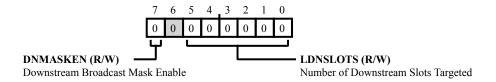

| Local Downstream Slots Register (Subordinate Only)     |

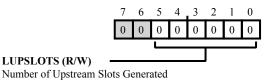

| Local Upstream Slots Register (Subordinate Only)       |

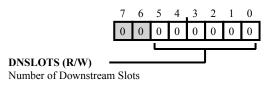

| Downstream Slots Register                              |

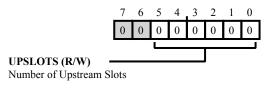

| Upstream Slots Register                                |

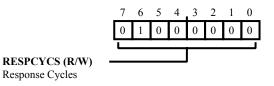

| Response Cycles Register                               |

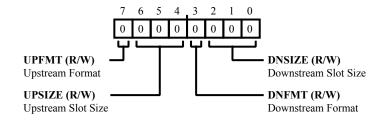

| Slot Format Register (Main Node Only, Auto-Broadcast)  |

| Data Control Register (Main Node Only, Auto-Broadcast) |

| Control Register                                       |

| Discovery Register (Main Node Only)                    |

| Switch Status Register                                 |

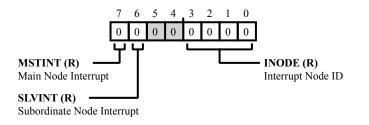

| Interrupt Status Register                              |

| Interrupt Source Register (Main Node Only)             |

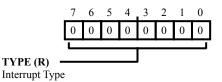

| Interrupt Type Register (Main Node Only)               |

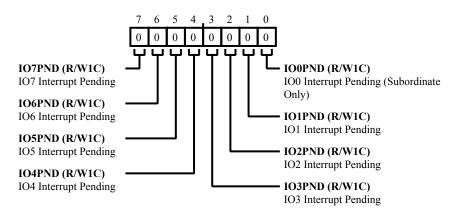

| Interrupt Pending 0 Register                        |

|-----------------------------------------------------|

| Interrupt Pending 1 Register                        |

| Interrupt Pending 2 Register (Main Node Only)       |

| Interrupt Mask 0 Register                           |

| Interrupt Mask 1 Register                           |

| Interrupt Mask 2 Register (Main Node Only)          |

| Bit Error Count Control Register                    |

| Bit Error Count Register                            |

| Testmode Register                                   |

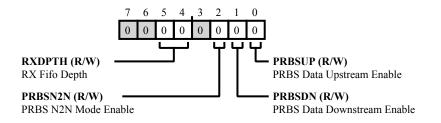

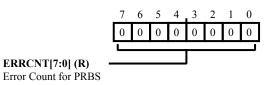

| PRBS Error Count Byte 0 Register                    |

| PRBS Error Count Byte 1 Register                    |

| PRBS Error Count Byte 2 Register                    |

| PRBS Error Count Byte 3 Register                    |

| Node Register                                       |

| Discovery Status Register (Main Node Only)          |

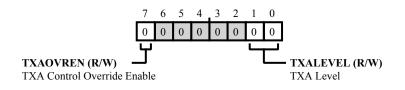

| LVDSA TX Control Register                           |

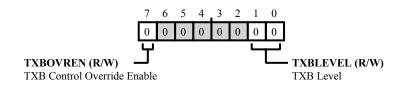

| LVDSB TX Control Register                           |

| Local Interrupt Type (Subordinate Only)             |

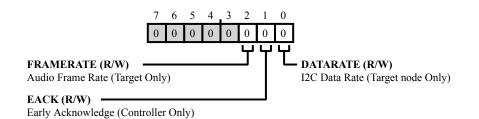

| I2C Configuration Register                          |

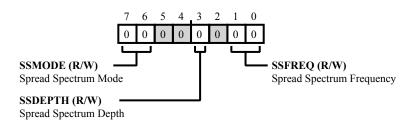

| PLL Control Register                                |

| I2S Global Configuration Register                   |

| I2S Configuration Register                          |

| I2S Rate Register (Target Only)                     |

| I2S Transmit Data Offset Register (Controller Only) |

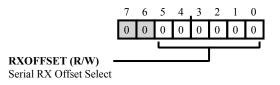

| I2S Receive Data Offset Register (Controller Only)  |

| SYNC Offset Register (Subordinate Only)             |

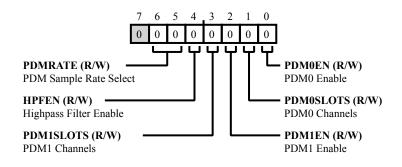

| PDM Control Register                                |

| Error Management Register                           |

|                                                     |

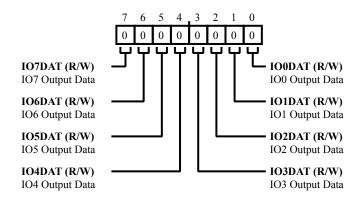

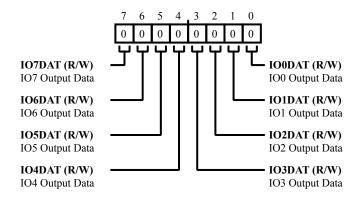

| GPIO Output Data Register                           |

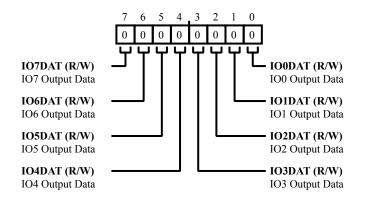

| GPIO Output Data Clear Register                                  |

|------------------------------------------------------------------|

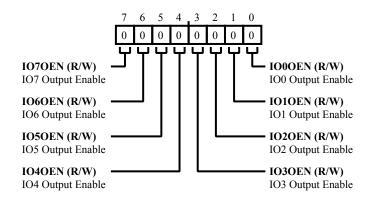

| GPIO Output Enable Register                                      |

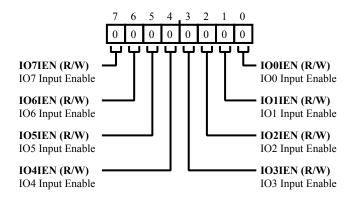

| GPIO Input Enable Register                                       |

| GPIO Input Value Register                                        |

| Pin Interrupt Enable Register                                    |

| Pin Interrupt Invert Register                                    |

| Pin Configuration Register                                       |

| I2S Test Register                                                |

| Raise Interrupt Register                                         |

| Generate Bus Error                                               |

| I2S Reduced Rate Register (Controller Node Only, Auto-Broadcast) |

| I2S Reduced Rate Control Register                                |

| I2S Reduced Rate SYNC Offset Register (Target Only)              |

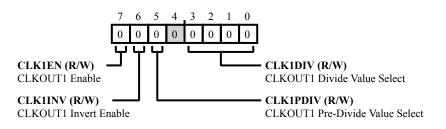

| CLKOUT1 Configuration Register                                   |

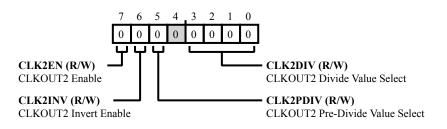

| CLKOUT2 Configuration Register                                   |

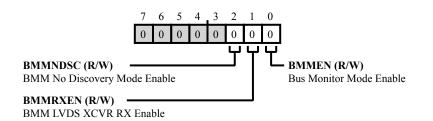

| Bus Monitor Mode Configuration Register                          |

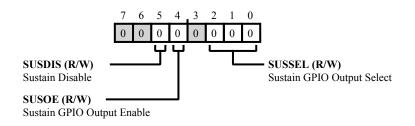

| Sustain Configuration Register (Subordinate Only)7-102           |

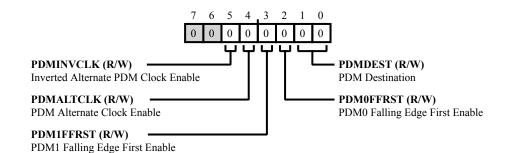

| PDM Control 2 Register                                           |

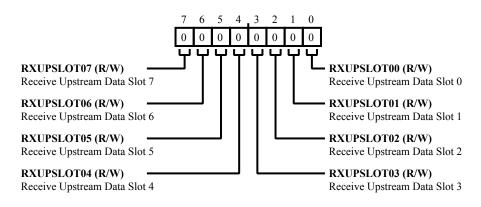

| Upstream Data RX Mask 0 Register (Target Only)                   |

| Upstream Data RX Mask 1 Register (Target Only)                   |

|                                                                  |

| Upstream Data RX Mask 2 Register (Target Only)                   |

| Upstream Data RX Mask 2 Register (Target Only)                   |

|                                                                  |

| Upstream Data RX Mask 3 Register (Target Only)7-111              |

| Upstream Data RX Mask 3 Register (Target Only)                   |

| Upstream Data RX Mask 3 Register (Target Only)                   |

| Upstream Data RX Mask 3 Register (Target Only)                   |

| Upstream Data RX Mask 3 Register (Target Only)                   |

| Upstream Data RX Mask 3 Register (Target Only)                   |

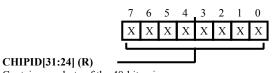

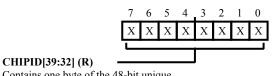

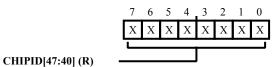

|   | Chip ID Register 2                                |

|---|---------------------------------------------------|

|   | Chip ID Register 3                                |

|   | Chip ID Register 4                                |

|   | Chip ID Register 5                                |

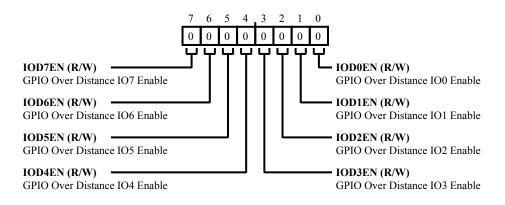

|   | GPIO Over Distance Enable Register                |

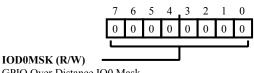

|   | GPIO Over Distance Mask 0 Register                |

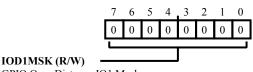

|   | GPIO Over Distance Mask 1 Register                |

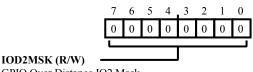

|   | GPIO Over Distance Mask 2 Register                |

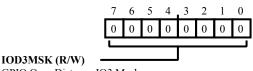

|   | GPIO Over Distance Mask 3 Register                |

|   | GPIO Over Distance Mask 4 Register                |

|   | GPIO Over Distance Mask 5 Register                |

|   | GPIO Over Distance Mask 6 Register                |

|   | GPIO Over Distance Mask 7 Register                |

|   | GPIO Over Distance Data Register                  |

|   | GPIO Over Distance Invert Register                |

|   | Mailbox 0 Control Register (Subordinate Only)     |

|   | Mailbox 0 Status Register (Subordinate Only)      |

|   | Mailbox 0 Byte 0 Register (Subordinate Only)      |

|   | Mailbox 0 Byte 1 Register (Subordinate Only)      |

|   | Mailbox 0 Byte 2 Register (Subordinate Only)      |

|   | Mailbox 0 Byte 3 Register (Subordinate Only)      |

|   | Mailbox 1 Control Register (Subordinate Only)     |

|   | Mailbox 1 Status Register (Subordinate Only)7-150 |

|   | Mailbox 1 Byte 0 Register (Subordinate Only)      |

|   | Mailbox 1 Byte 1 Register (Subordinate Only)      |

|   | Mailbox 1 Byte 2 Register (Subordinate Only)      |

|   | Mailbox 1 Byte 3 Register (Subordinate Only)      |

| / | ppendix A: Additional Discovery Flow Examples     |

| Γ |                                                   |

|   | Modified Discovery Flow                           |

| Optimized Discovery Flow                              |  |

|-------------------------------------------------------|--|

| Advanced Discovery Flow                               |  |

| Appendix B: Response Cycle Formula                    |  |

| Appendix C: Module ID and Module Configuration Memory |  |

| Configuration Memory                                  |  |

| Appendix D: Interrupt Processing                      |  |

| Main Node Running Interrupts                          |  |

| Discovery Done Interrupts                             |  |

| Line Fault Interrupts                                 |  |

| Error Interrupts                                      |  |

| General Purpose IO Pin Interrupts                     |  |

# 1 Preface

Thank you for purchasing and developing systems using an Automotive Audio Bus A<sup>2</sup>B<sup>®</sup> Transceiver from Analog Devices.

## **Purpose of This Manual**

The AD2426/7/8 Automotive Audio Bus A<sup>2</sup>B Transceiver Technical Reference provides information about the transceivers, including register and bit descriptions. For timing, electrical, and package specifications, see the AD2426/7/8 Automotive Audio Bus A<sup>2</sup>B Transceiver Data Sheet.

## **Intended Audience**

This manual is intended for system designers and programmers who want to develop systems using the A<sup>2</sup>B transceiver.

## Manual Contents

This manual consists of the following chapters:

- $A^2B$  Overview Provides a basic description and the features supported.

- *A*<sup>2</sup>*B Operation and Configuration* Provides information on bringing up the main node and discovery of the subordinate nodes. Provides a simple System Discovery Example.

- $A^2B$  Event Control Provides information on system interrupts and their use.

- $A^2B$  System Debug Provides information that allows you to perform system diagnostics in order to isolate and correct faults. Additionally, a loop back test mode provides easy validation of I<sup>2</sup>S/TDM connectivity in main and subordinate nodes.

- Register Summary Provides the register map and bit definitions for the integrated transceiver.

- Register Descriptions Provides the detailed descriptions of the registers and bits.

- Appendix A: Additional Discovery Flow Examples

- Appendix B: Response Cycle Formula

- Appendix C: Module ID and Module Configuration Memory

- Appendix D: Interrupt Processing

## What's New in This Manual

This is revision (1.3). The following changes were made to content in this revision:

- Document title change to reflect updated part numbering

- Updated the *Simple Discovery Flow* figure in the A<sup>2</sup>B Operation and Configuration chapter.

- Updated topics:

- Subordinate Node Interrupt Handling

- Diagnostics Software Flow

- Updated Register Summary section to correct the reset values for the NODE, MBOX0STAT, MBOX1STAT, and MOBIX1CTL registers.

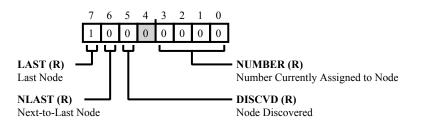

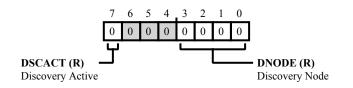

## **Register Documentation Conventions**

The register sections and diagrams use the following conventions:

- Registers are presented in address order.

- The reset value appears in binary in the individual bits and in hexadecimal to the left of the register.

- Shaded bits are reserved.

- **NOTE:** To ensure upward compatibility with future implementations, write back the value that is read for reserved bits in a register, unless otherwise specified.

Register description tables use the following conventions:

- Each bit's or bit field's access type appears beneath the bit number in the table in the form (read-access/write-access). The access types include:

- R= read, RC= read clear, RS= read set, R0= read zero, R1= read one, Rx= read undefined

- W= write, NW= no write, W1C= write one to clear, W1S= write one to set, W0C= write zero to clear, W0S= write zero to set, WS= write to set, WC = write to clear, W1A= write one action, XCVRA/B= transceiver (A-port /B-port )

- Many bit and bit field descriptions include enumerations, identifying bit values and related functionality. Unless otherwise indicated (with a prefix), these enumerations are decimal values.

# 2 A<sup>2</sup>B Overview

The Automotive Audio Bus ( $A^2B^{(B)}$ ) connects multichannel I<sup>2</sup>S synchronous PCM data over a distance of up to 15m between nodes. It also extends the synchronous, time-division multiplexed (TDM) nature of I<sup>2</sup>S to a system that connects multiple nodes, where each node can consume data, provide data, or both.

The transceivers support these A<sup>2</sup>B functions with a direct interface to general-purpose digital signal processors (DSPs), field programmable gate arrays (FPGAs), application specific integrated circuits (ASICs), microphones, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and codecs through a multichannel I<sup>2</sup>S/TDM interface. They also provide a PDM interface for direct connection of up to four PDM digital microphones. Enabling the A<sup>2</sup>B bus-powering feature supplies voltage and current to the subordinate nodes over the same, daisy-chained, twisted pair wire cable as used for the communication link. The transceiver also fully supports I<sup>2</sup>C communication over the A<sup>2</sup>B link.

The transceivers have the following features.

- Line topology

- Single main node, multiple subordinate nodes

- Unshielded, single twisted pair wire (UTP) cable link between nodes (cable length is specified in the product data sheet)

- Communication over distance

- Synchronous data

- Multichannel I<sup>2</sup>S/TDM to I<sup>2</sup>S/TDM interface

- Synchronous, phase-aligned clock in all nodes

- Low-latency subordinate node-to-subordinate node communication

- I<sup>2</sup>C to I<sup>2</sup>C control and status information

- GPIO over distance

- Configurable with SigmaStudio<sup>®</sup> graphical development tool

- Qualified for automotive applications

- Configurable as A<sup>2</sup>B bus main or subordinate

- I<sup>2</sup>C interface

- 8-bit to 32-bit multichannel I<sup>2</sup>S/TDM interface

- I<sup>2</sup>S/TDM/PDM programmable data rate

- Up to 32 channels (1 x TDM32 or 2 x TDM16), mapped to up to 32 upstream and 32 downstream A<sup>2</sup>B bus slots

- PDM inputs supporting up to 4 high-dynamic-range microphones

- Unique ID register for each transceiver

- Support for crossover or straight-through cabling

- Programmable settings to optimize EMC performance

## A<sup>2</sup>B Terminology

To make the best use of the A<sup>2</sup>B system, it is helpful to understand the following terms.

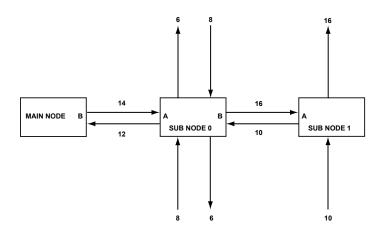

#### A-Side or A-Port

A<sup>2</sup>B transceiver interface that faces toward the main (toward the immediately upstream node).

#### **B-Side or B-Port**

A<sup>2</sup>B transceiver interface that faces toward the last-in-line subordinate node (toward the immediately downstream next-in-line subordinate node).

#### Bus Link

The A<sup>2</sup>B bus can consist of multiple daisy-chained subordinate nodes connected to a single main node. The physical connection between a main and sub node 0, as well as all physical A<sup>2</sup>B connections between subordinates, are called bus links. An unshielded twisted wire pair is typically used for each bus link.

#### **Bus Power**

Subordinate nodes can tap into the bias voltage on the A<sup>2</sup>B bus link and use it as the sole power supply.

#### Data Channel

A data channel carries the synchronous I<sup>2</sup>S/TDM data for a single sensor/actuator (for example, an ADC, a microphone, or a speaker). The I<sup>2</sup>S/TDM interface uses equally sized data channels, where the width of the data word is often smaller than the width of the I<sup>2</sup>S/TDM data channel. The I<sup>2</sup>S/TDM interface of the transceiver supports programmable data channel lengths of 16 or 32 bits.

#### Data Slot

A synchronous data word of a single sensor/actuator (for example, an ADC, a microphone, or a speaker), as mapped onto the A<sup>2</sup>B bus.

#### Downstream

Communication flow from the main node toward the subordinate nodes, terminating at the last-in-line subordinate.

#### Host

Processor that programs the main transceiver. The host is also the source for the synchronous clock on the A<sup>2</sup>B bus. The clock signal (BCLK) is part of the I<sup>2</sup>S/TDM interface between the host and main.

#### I<sup>2</sup> S/TDM

The inter IC sound ( $I^2S$ ) bus carries pulse code modulated (PCM) information between audio chips on a PCB. The  $I^2S$ /TDM interface extends the  $I^2S$  stereo (2-channel) content to multiple channels using time-division multiplexing (TDM).

#### Local Power Subordinate Node (LPS)

Subordinate nodes that do not operate on A<sup>2</sup>B bus power use local power, which is sourced by extra wires.

#### LVDS

Low voltage differential signaling.

#### Main Node

Originator of the clock (derived from the I<sup>2</sup>S input), downstream data, network control, and power. The main node is comprised of the host processor and an A<sup>2</sup>B main transceiver, which receives payloads from the host and sends payloads to the host.

#### PDM

Pulse Density Modulation (PDM) is used in sigma delta converters. PDM format represents an over-sampled 1-bit sigma delta ADC signal before decimation and is often used as the output format in digital microphones.

#### PRBS

Pseudo random binary sequence.

#### Preamble

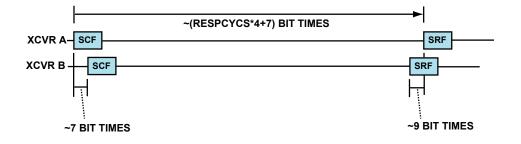

Synchronization bits to signal the start of a control or response frame. The downstream control frame preamble is sent by the main node for every superframe. Subordinate transceivers synchronize to the downstream control preamble and generate a local, phase-aligned main clock from it.

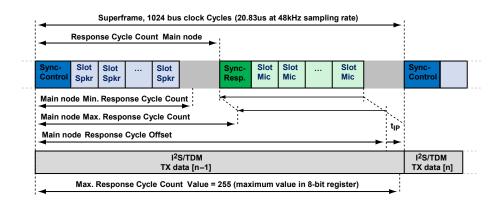

#### **Response Time**

Specifies the time a last node waits after the start of a superframe before the node responds with the Synchronization Response Frame (SRF). Response time is programmed in the main node and all subordinate nodes closest to the main so that these nodes know when to expect the direction to switch from downstream to upstream.

#### Subordinate Node

Addressable network connection point. Subordinate nodes can be the source and/or destination of both downstream and upstream data slots. Every A<sup>2</sup>B subordinate node has an A<sup>2</sup>B subordinate transceiver.

#### Synchronization Control and Response Frames (SCF/SRF)

Control frame for nodes (control header) and response frame from nodes (response header). Headers include a preamble for synchronization and enable read and write access to all nodes.

#### Synchronous Data

Data streamed continuously (for example, audio signals) with a fixed time interval (selectable between 44.1 kHz or 48 kHz) between two successive transmissions to and from the same node.

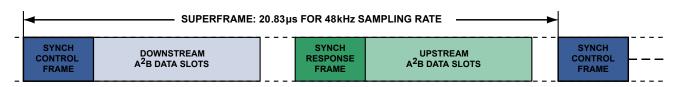

#### Superframe

The overall frame structure for A<sup>2</sup>B. It starts with an SCF, includes optional data slots, and concludes with an SRF. Superframes repeat every 1024 bus clock cycles.

#### Upstream

Communication flow the last-in-line subordinate node to the main node.

## A<sup>2</sup>B Bus Details

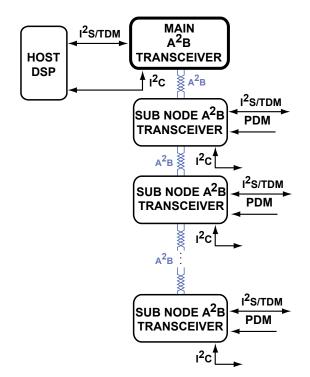

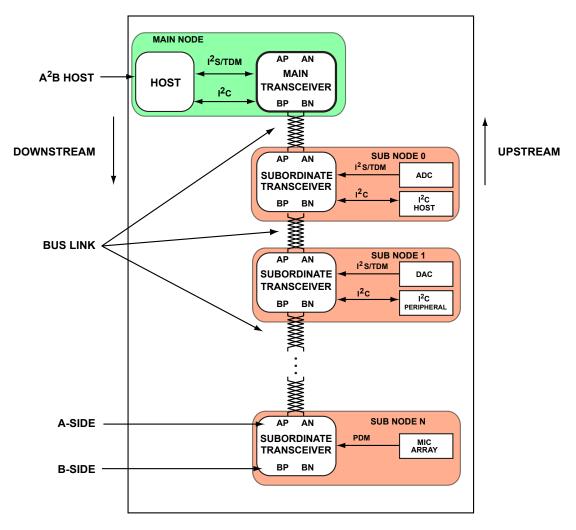

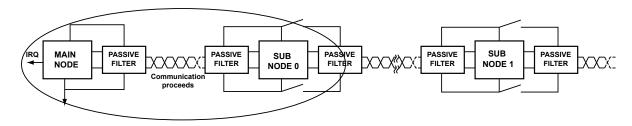

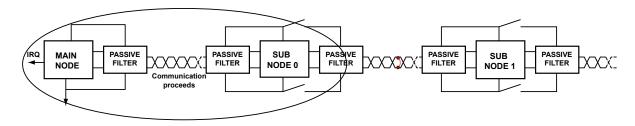

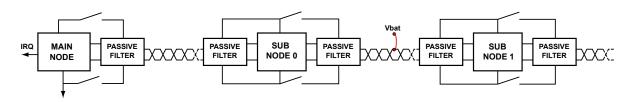

The *Communication System Block Diagram* shows an A<sup>2</sup>B communications system, which is a single-main, multiple-subordinate system where the main transceiver is controlled by the host. The host generates a periodic

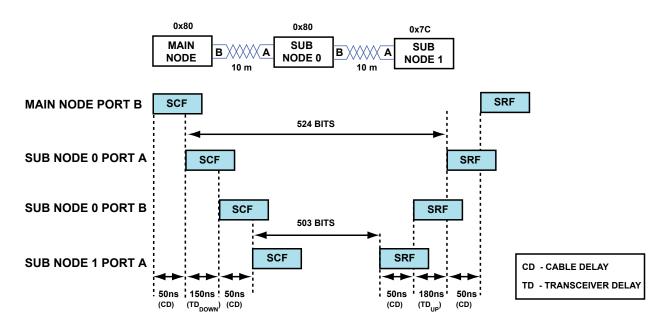

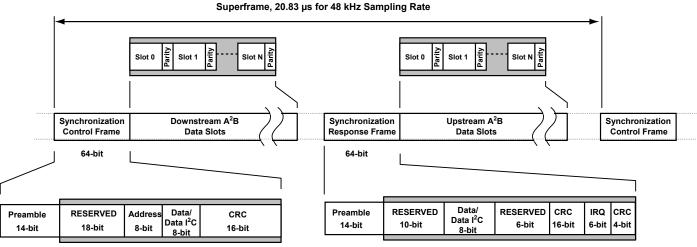

synchronization signal (SYNC) on the I<sup>2</sup>S/TDM interface at a fixed frequency (selectable between 44.1 kHz and 48 kHz), to which all A<sup>2</sup>B nodes synchronize. Communication over the A<sup>2</sup>B bus occurs in periodic superframes at this rate. Data is transferred at the A<sup>2</sup>B system bit clock (SYSBCLK) rate, which is 1024 times faster than the superframe rate (49.152 MHz for a frame rate of 48 kHz, 45.158 MHz for a frame rate of 44.1 kHz). Each superframe is divided into periods of downstream transmission, upstream transmission, and no transmission (where the bus is not driven).

Figure 2-1: Communication System Block Diagram

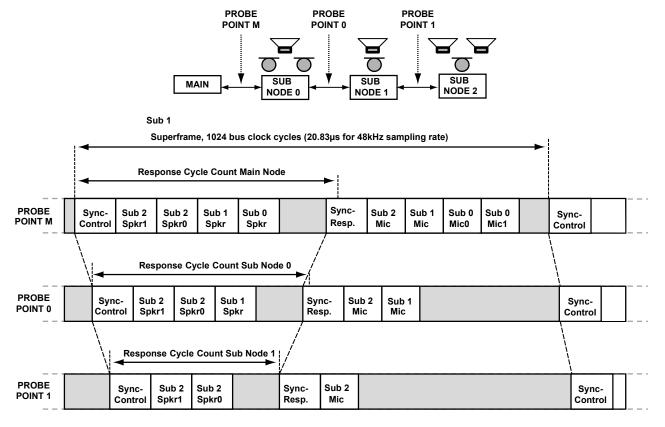

The  $A^2B$  Superframe figure shows a superframe with an initial period of downstream transmission and a later period of upstream transmission.

All signals on the A<sup>2</sup>B bus are line-coded, and the main node forwards the synchronization signal downstream to the last subordinate node in the form of a synchronization preamble. This preamble is followed by the control frame (SCF). Downstream, TDM synchronous data is added directly after the control frame. Every subordinate node can use or consume some of the downstream data and add data for downstream nodes. The last subordinate node responds after the response time with a response frame (SRF). Upstream synchronous data is added by each node directly after the response frame. Each node can also use or consume upstream data. All synchronous data is organized

into data slots of equal width, though the upstream and downstream slot widths can be different. For more details, see A<sup>2</sup>B Slot Format.

The embedded control and response frames allow the host to individually address each subordinate node over the  $A^2B$  bus. In a similar fashion, the host can also access remote peripheral devices that are connected to any discovered subordinate transceivers using  $I^2C$ - to- $I^2C$  communication over distance.

All nodes in an  $A^2B$  system are sampled synchronously in the same  $A^2B$  superframe. Synchronous  $I^2S/TDM$  downstream data from the main arrives at all subordinates in the same  $A^2B$  superframe, and each node's upstream audio data arrives synchronously in the same  $I^2S/TDM$  frame at the main. The remaining audio phase differences between subordinates can be compensated for by register-programmable fine adjustment of the SYNC pin signal delay using the  $A2B_SYNCOFFSET$  register.

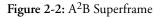

Because data is received and transmitted over the I<sup>2</sup>S/TDM port every sample period, there is a delay incurred for data moving between the A<sup>2</sup>B bus and the I<sup>2</sup>S/TDM interfaces. The timing relationship between samples over the A<sup>2</sup>B bus is shown in the A<sup>2</sup>B Bus Synchronous Data Exchange figure.

Figure 2-3: A<sup>2</sup>B Bus Synchronous Data Exchange

Note in the  $A^2B$  Bus Synchronous Data Exchange figure, both downstream and upstream samples are named for the superframe where they enter the  $A^2B$  system, as follows:

- Data transmitted by the main node transceiver in superframe M creates downstream data M

- Data transmitted by the subordinate node transceivers in superframe N creates upstream data N

- Data received over the I<sup>2</sup>S/TDM interface by the A<sup>2</sup>B transceiver chip is transmitted over the A<sup>2</sup>B bus in the following superframe

- Data on the A<sup>2</sup>B bus is transmitted over the I<sup>2</sup>S/TDM interface of an A<sup>2</sup>B chip transceiver in the following superframe

Data transmitted across the A<sup>2</sup>B bus (main node to subordinate node or subordinate to main) has two superframes of latency, plus any internal delay that has accumulated in the transceiver chips, as well as delays due to wire length. Therefore, overall latency is slightly over two superframes from the I<sup>2</sup>S/TDM interface in one A<sup>2</sup>B transceiver chip to the I<sup>2</sup>S/TDM interface of another A<sup>2</sup>B transceiver chip.

### **Functional Description**

The  $A^2B$  transceiver connects multichannel I<sup>2</sup>S (inter-IC sound) synchronous, pulse-code modulated (PCM) data over a distance between nodes (the cable length is specified in the product data sheet). It also extends the synchronous, time-division multiplexed nature of I<sup>2</sup>S to a system that connects multiple nodes, where each node can consume data, provide data, or both.

The A<sup>2</sup>B transceiver supports these A<sup>2</sup>B functions with a direct interface to general-purpose DSPs, FPGAs, ASICs, microphones, ADCs, DACs, and codecs through a multichannel I<sup>2</sup>S/TDM interface. The data over the A<sup>2</sup>B bus link is manchester encoded. The transceiver also fully supports I<sup>2</sup>C communication over the A<sup>2</sup>B link. The A<sup>2</sup>B transceiver can be used in either a subordinate node or in a main node. By default, the transceiver starts up as a subordinate transceiver but can be configured as a main transceiver if the host sets the A2B CONTROL.MSTR bit.

The *Simplified*  $A^2B$  *System with Four Nodes* figure shows a simple  $A^2B$  system example. The host programs registers in each of the nodes to control the data traffic on the  $A^2B$  bus. Microphone data from subordinate nodes 0 and 2 is delivered to the host, and speaker data for subordinate nodes 1 and 2 is delivered from the host to the DACs.

Figure 2-4: Simplified A<sup>2</sup>B System with Four Nodes

## **Architectural Concepts**

The following sections provide information that describes the hardware blocks, interfaces and interconnections.

### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is used to directly access the transceiver register space from a locally connected host and to remotely exchange I<sup>2</sup>C data over the A<sup>2</sup>B bus between the main transceiver and any discovered subordinate node in the system. This protocol is referred to as  $I^2C$  over distance, where the exchanged I<sup>2</sup>C data is embedded within the synchronization control frame (downstream, from the I<sup>2</sup>C controller to the target) and the synchronization response frame (upstream, from the I<sup>2</sup>C target to the controller).

The I<sup>2</sup>C interface in the transceiver is compatible with up to 5 V logic levels and has the following features:

• Target only operation in an A<sup>2</sup>B main node

- Controller, multi-controller, or target operation in an A<sup>2</sup>B sub node

- Operations at 100k or 400k bits/s rate, as configured by the A2B\_I2CCFG. DATARATE bit

- 7-bit addressing

- Clock stretching

**NOTE:** The A<sup>2</sup>B host on the main node must support I<sup>2</sup>C clock stretching in order to interface to the main transceiver.

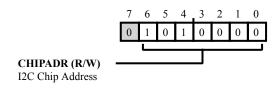

A transceiver that is configured as a main recognizes two I<sup>2</sup>C device addresses:

- BASE\_ADDR for direct accesses via the I<sup>2</sup>C port to its register space

- BUS\_ADDR for remote access to sub node registers and target node I<sup>2</sup>C peripherals over the A<sup>2</sup>B bus using the  $I^2C$  over distance protocol

The I<sup>2</sup>C BASE\_ADDR is set by the logic levels on the ADR2/IO2 and ADR1/IO1 pins at power-on reset, thus providing support for up to four controller devices connecting to the same I<sup>2</sup>C bus. The LSB of the 7-bit device address determines whether an I<sup>2</sup>C data exchange uses the BASE\_ADDR (bit 1 = 0) to access the transceiver or BUS\_ADDR (bit 1 = 1) to access a bus node through a controller-enabled transceiver, as described in the  $I^2CAd$ -*dress* table.

| ADR2/IO2 Setting | ADR1/IO1 Setting | BASE_ADDR | BUS_ADDR |

|------------------|------------------|-----------|----------|

| 0                | 0                | 0x68      | 0x69     |

| 0                | 1                | 0x6A      | 0x6B     |

| 1                | 0                | 0x6C      | 0x6D     |

| 1                | 1                | 0x6E      | 0x6F     |

Table 2-1:

I<sup>2</sup>C Device Address

A transceiver that is configured as a subordinate does not recognize BUS\_ADDR. On subordinate transceivers, the I<sup>2</sup>C interface allows for both I<sup>2</sup>C controller and target behavior. It is the I<sup>2</sup>C controller when the transceiver receives a remote I<sup>2</sup>C peripheral access request from the host through the A<sup>2</sup>B bus. The main transceiver functioning as the I<sup>2</sup>C controller then forwards the I<sup>2</sup>C transaction to the I<sup>2</sup>C target address programmed in its A2B\_CHIP register. It is the I<sup>2</sup>C target when the transceiver registers (BASE\_ADDR) are accessed by a local external controller through the I<sup>2</sup>C port.

**NOTE:** While a local external controller can program the register space of a subordinate transceiver, the A2B\_SWCTL, A2B\_RESPCYCS, A2B\_SLOTFMT, A2B\_DATCTL, A2B\_RAISE, and A2B\_GENERR registers must be written over the A<sup>2</sup>B bus by the remote host. A write to any of these registers from the local I<sup>2</sup>C port has no effect on the register.

The I<sup>2</sup>C interface on the transceiver allows register programming before PLL lock. Write 1 for action (W1A) bits (for example, A2B\_CONTROL.ENDDSC and A2B\_CONTROL.NEWSTRCT) have no effect prior to PLL lock since the protocol engine is still in reset.

- **NOTE:** The A2B\_SWCTL, A2B\_SLOTFMT, A2B\_DATCTL, and A2B\_DISCVRY registers cannot be written in a main transceiver prior to PLL lock. Writes to these registers before PLL lock is established have no effect.

- **CAUTION:** System software must be designed to avoid simultaneous writes to the same subordinate register from both the A<sup>2</sup>B host (through the A<sup>2</sup>B bus) and the local processor (through the I<sup>2</sup>C port). When write contention occurs, both writes complete, but the order in which they complete is unpredictable.

#### I<sup>2</sup>C Clock Stretching

The transceiver uses the I<sup>2</sup>C clock stretching feature to ensure that the I<sup>2</sup>C accesses have enough time to be processed. It is applied mainly for host I<sup>2</sup>C accesses to sub node transceivers and target node I<sup>2</sup>C peripherals over the A<sup>2</sup>B bus. Clock stretching is initiated by the main transeiver in response to host I<sup>2</sup>C accesses at the following times:

- During write accesses before the acknowledge bit after each data byte

- During read accesses before the acknowledge bit following the read request

- During burst read/write accesses of more than one byte before the first bit of subsequent data bytes

Pulling the SCL signal low indicates to the host that the transceiver needs more time to process the request. Once the transceiver is ready to acknowledge the request, it lets the SCL signal go high so the host can gain back control of the SCL and proceed with the acknowledge (ACK) and the next byte.

**IMPORTANT:** It is mandatory that the host (I<sup>2</sup>C controller) supports I<sup>2</sup>C clock stretching in an A<sup>2</sup>B system design.

When a peripheral in a sub node stretches the  $I^2C$  clock, the SCL signal is also stretched between the main transceiver and the host. If the SCL signal is not released by the peripheral within the time of 32 superframes, the main transceiver registers a timeout (A2B\_INTPND2.I2CERR = 1), releases the SCL, and ceases stretching of the host clock. This timeout ensures a subordinate peripheral cannot bring the  $I^2C$  interface of the host to a permanent halt.

#### Transceiver I<sup>2</sup>C Accesses

The LSB of the 7-bit device address determines whether an  $I^2C$  data exchange uses the BASE\_ADDR (bit 1 = 0) to access the transceiver or BUS\_ADDR (bit 1 = 1) to access a bus node through a main configured transceiver, as shown in the following table.

Table 2-2: I<sup>2</sup>C Device Addresses

| Bit Number | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2    | Bit 1 (LSB) | Bit 0 $(R/\overline{W})$ |

|------------|-------|-------|-------|-------|----------|----------|-------------|--------------------------|

| Start bit  | 1     | 1     | 0     | 1     | ADR2/IO2 | ADR1/IO1 | 0 = BASE    | 0 = write                |

|            |       |       |       |       |          |          | 1 = BUS     | 1 = read                 |

The A<sup>2</sup>B transceiver supports the following read and write operations:

- Single-word write operation the A<sup>2</sup>B main transceiver (I<sup>2</sup>C target) issues an acknowledge by pulling SDA low during the ninth clock pulse, thus completing the access.

- Burst mode write sequence the transceiver automatically increments the register address pointer after each data byte, so sequential data registers can be written without reprogramming the address.

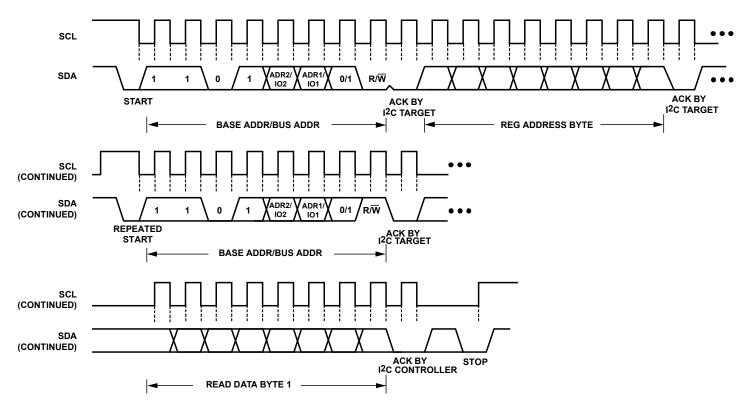

- Single-word read operation the first read/write (R/W) bit is 0, indicating a write operation. This is because

the register address must still be written to set up the internal address. After the I<sup>2</sup>C target acknowledges the

receipt of the register address, the I<sup>2</sup>C controller must issue a repeated start command, followed by the chip

address byte with the R/W bit set to 1 (read). This causes the I<sup>2</sup>C data line SDA to reverse direction and begin

driving data back to the I<sup>2</sup>C controller. The I<sup>2</sup>C controller then responds every ninth pulse with an acknowledge pulse to the target.

- Burst mode read sequence the transceiver automatically increments the register address pointer after every read of a data byte, so sequential data registers can be read without reprogramming the address.

Data transfers over the I<sup>2</sup>C interface require the following steps:

- 1. A data transfer is initiated by a microcontroller that is connected to an A<sup>2</sup>B transceiver.

- 2. The microcontroller establishes a start condition (a high to low transition on SDA while SCL remains high), which indicates that an address/data stream follows.

- 3. In the next eight SCL cycles, the A<sup>2</sup>B transceiver receives a 7-bit address and the R/W bit from the host (MSB first).

- 4. The A<sup>2</sup>B transceiver recognizes the transmitted address and responds by pulling the data line low during the ninth clock pulse (acknowledge bit).

The R/W bit determines the direction of the data. When the LSB of the first byte is cleared (=0), the host writes information to the main transceiver. When the LSB of the first byte is set (=1), the host reads information from the main transceiver. Data transfers take place until a stop condition (when SDA transitions from low to high while SCL is held high) is encountered. The register address pointer auto increments to support burst mode I<sup>2</sup>C writes and burst mode I<sup>2</sup>C reads for both mains and subordinates.

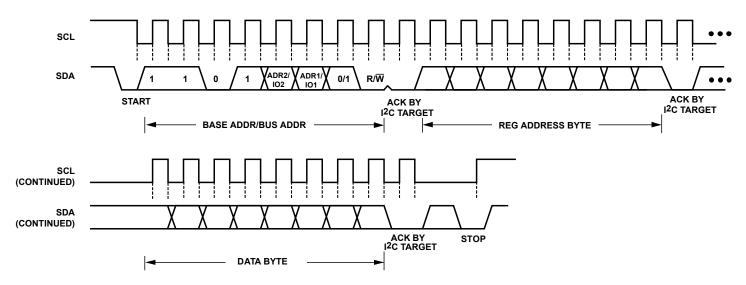

The  $I^2C$  Formats figure shows the format of the following I<sup>2</sup>C operations:

- Writes to BASE\_ADDR/BUS\_ADDR can contain one or more bytes of data. The first byte after the device address sets the register address in the device. The subsequent byte is written to the addressed register. Since the address pointer increments after each write, sequential registers can be written in a single transaction.

- Reads from BASE\_ADDR/BUS\_ADDR can contain one or more bytes of data. The device address with write indication is followed by the register address in the device and a repeated device address with a read access indication.

#### SINGLE WORD I<sup>2</sup>C WRITE FORMAT

| s | BASE ADDR/<br>BUS ADDR | AS | REG ADDR<br>BYTE | AS | DATA BYTE 1 | AS | Ρ |

|---|------------------------|----|------------------|----|-------------|----|---|

|---|------------------------|----|------------------|----|-------------|----|---|

#### BURST MODE I<sup>2</sup>C WRITE FORMAT

| s | BASE ADDR/<br>BUS ADDR R/W=0 | AS | REG ADDR<br>BYTE | AS | DATA<br>BYTE 1 | AS | DATA<br>BYTE 2 | AS | DATA<br>BYTE 3 | AS | DATA<br>BYTE 4 | AS |  | AS | Ρ |

|---|------------------------------|----|------------------|----|----------------|----|----------------|----|----------------|----|----------------|----|--|----|---|

|---|------------------------------|----|------------------|----|----------------|----|----------------|----|----------------|----|----------------|----|--|----|---|

#### SINGLE WORD I<sup>2</sup>C READ FORMAT

| s | BASE ADDR/<br>BUS ADDR R/W=0 | AS | REG ADDR<br>BYTE | AS | S | BASE ADDR/<br>BUS ADDR R/W=1 | AS | DATA<br>BYTE 1 | AM | Ρ |

|---|------------------------------|----|------------------|----|---|------------------------------|----|----------------|----|---|

|---|------------------------------|----|------------------|----|---|------------------------------|----|----------------|----|---|

BURST MODE I<sup>2</sup>C READ FORMAT

| S | BASE ADDR/<br>BUS ADDR R/W=0 | AS | REG ADDR<br>BYTE | AS | s | BASE ADDR/<br>BUS ADDR R/W=1 | AS | DATA<br>BYTE 1 | АМ | DATA<br>BYTE 2 | АМ |  | АМ | Р |

|---|------------------------------|----|------------------|----|---|------------------------------|----|----------------|----|----------------|----|--|----|---|

|---|------------------------------|----|------------------|----|---|------------------------------|----|----------------|----|----------------|----|--|----|---|

#### S = START BIT P = STOP BIT AM = ACKNOWLEDGE BY I<sup>2</sup>C CONTROLLER AS = ACKNOWLEDGE BY I<sup>2</sup>C TARGET

Figure 2-5: I<sup>2</sup>C Formats

The first byte after the repeated device address contains the value of the register addressed. The first byte after the device address sets the register address in the device. It is followed by the repeated device address, but with read access indication. The subsequent bytes contain the values of the automatically incremented register addresses.

The  $I^2C$  Write Timing figure shows I<sup>2</sup>C write timing.

Figure 2-6: I<sup>2</sup>C Write Timing

The  $I^2C$  Read Timing figure shows  $I^2C$  read timing.

Figure 2-7: I<sup>2</sup>C Read Timing

#### Transceiver I<sup>2</sup>C Access Latencies

When an I<sup>2</sup>C access is made over distance to a remote transceiver via the A<sup>2</sup>B bus, there are latencies incurred. A<sup>2</sup>B bus latencies for different types of I<sup>2</sup>C accesses are provided in the *Bus Latencies for I<sup>2</sup>C Accesses* table.

| I <sup>2</sup> C Access Type                                                                            | Estimated A <sup>2</sup> B Bus Latency (µs) |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------|

| (Conditions)                                                                                            |                                             |

| I <sup>2</sup> C write of N data bytes to subordinate transceiver registers                             | N × 22                                      |

| (clock stretching enabled via main A2B_I2CCFG.EACK = 0)                                                 |                                             |

| I <sup>2</sup> C read of N data bytes from subordinate transceiver registers                            | N × 22                                      |

| (clock stretching enabled via main A2B_I2CCFG.EACK = 0)                                                 |                                             |

| I <sup>2</sup> C write of N >1 data byte to subordinate transceiver registers                           | 2                                           |

| (clock stretching disabled via main A2B_I2CCFG.EACK = 1, host I <sup>2</sup> C using 400 kHz data rate) |                                             |

| I <sup>2</sup> C write of N data bytes to subordinate transceiver registers                             | 0                                           |

| (clock stretching enabled via main A2B_I2CCFG.EACK= 1, host I <sup>2</sup> C using 100 kHz data rate)   |                                             |

Table 2-3: Bus Latencies for I<sup>2</sup>C Accesses (48 kHz Superframe Rate)

Table 2-3: Bus Latencies for I<sup>2</sup>C Accesses (48 kHz Superframe Rate) (Continued)

| I <sup>2</sup> C Access Type<br>(Conditions)                                                                               | Estimated A <sup>2</sup> B Bus Latency (µs) |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| I <sup>2</sup> C write of N data bytes to remote I <sup>2</sup> C peripheral<br>(target A2B_I2CCFG.DATARATE = 0 = 100 kHz) | ((N – 1) × 113) + 213                       |

| I <sup>2</sup> C write of N data bytes to remote I <sup>2</sup> C peripheral<br>(target A2B_I2CCFG.DATARATE = 1 = 400 kHz) | ((N – 1) × 45) + 70                         |

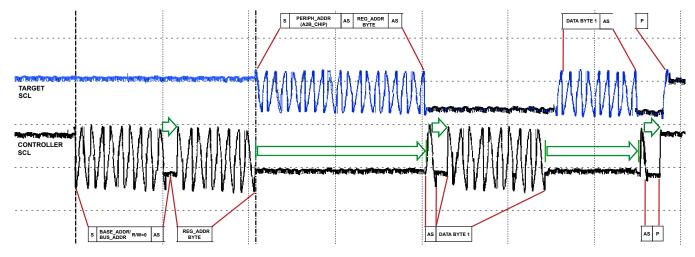

For example, consider a case where a remote peripheral (connected to a subordinate node) register is being written. In the  $I^2C$  Access Latency figure, the I<sup>2</sup>C access latency is marked with green arrows.

Figure 2-8: I<sup>2</sup>C Access Latency

**NOTE:** The latencies described in the *Bus Latencies for I<sup>2</sup>C Accesses* table are for accesses with no conflicts. If an I<sup>2</sup>C message doesn't get immediately acknowledged or is otherwise held off due to higher-priority events such as a GPIO interrupt, a line fault interrupt, an I<sup>2</sup>C issue (NACK), etc., the delay incurred before attempting to execute the message exchange is not included in the values provided in the table.

### Pulse-Density Modulation Interface (PDM)

Pulse-density modulation is used in sigma delta converters. The PDM format represents an over-sampled 1-bit sigma delta ADC signal before decimation. It is often used as the output format in digital microphones.

The PDM block supports high dynamic range microphones with a high signal-to-noise ratio (SNR) and an extended maximum sound pressure level (SPL).

The enhanced PDM block of the transceiver supports a lower noise floor than the AD241x transceiver. This provides for an SNR greater than 120 dB. The PDM block on the transceiver supports 24 kHz and 12 kHz sample rates in addition to a 48 kHz sample rate with the same PDM clock rate (3.072 MHz at a 48 kHz frame rate). The cutoff frequency of the high pass filter in the PDM block on the transceiver is fixed to 1 Hz and is not programmable. The highpass filter is a first order IIR filter.

The transceiver is programmable for 1x, 1/2x, or 1/4x PDM sampling (48 kHz, 24 kHz, or 12 kHz typical) relative to the superframe rate (48 kHz typical). For 1/2x or 1/4x PDM sampling, synchronous data in an A<sup>2</sup>B slot is duplicated in order to match the superframe rate. Even lower PDM sampling rates are possible when the reduced rate feature of the transceiver is used in combination with this (for example, down to 375 Hz).

The PDM bit clock output frequency from the transceiver is 64x faster than the PDM audio sampling rate (typically, 3.072 MHz for 48 kHz PDM audio sampling).

Each PDM-enabled receive pin can receive up to two channels of audio data (stereo). One of the channels is associated with the rising edge of the clock and the other with the falling edge of the clock.

The PDM block is configured using the PDM control ( A2B\_PDMCTL ) register:

- When A2B\_PDMCTL.PDM0EN = 1, the DRX0/IO5 pin is enabled to receive PDM data, and the BCLK pin is an output, typically producing a 3.072 MHz clock for the TDM2 setting. In this mode, the DRX0/IO5 pin data is not passed to the I<sup>2</sup>S/TDM port. Similarly, the A2B\_PDMCTL.PDM1EN bit controls PDM data reception on the DRX1/IO6 pin.

- The A2B\_PDMCTL.PDMxSLOTS bits select whether the PDM signals on the DRX pins use one (mono) or two (stereo) channels.

#### PDM Sampling Edge of a Connected Microphone

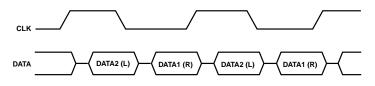

The pulse-density modulation (PDM) interface allows PDM input from two microphones to be time-multiplexed on a single data line using a single clock.

A PDM microphone encodes data such that the left channel is valid on the falling edge of the clock (CLK) signal and the right channel is valid on the rising edge of the CLK signal. After the DATA signal is driven during the appropriate half phase of the CLK signal, the microphone output is tristated. As such, two microphones (one set to the left channel and the other set to the right channel) can share a single DATA line (see the *Stereo PDM Format* figure).

Figure 2-9: Stereo PDM Format

In the transceiver, the PDM block samples the microphone data on all 64 clock edges. The transceiver must be programmed to a TDM mode that produces 64 BCLKs per frame (either the default TDM2/32 or TDM4/16 mode). The TDM settings do not affect the PDM block.

In the transceiver, the data sampled on the rising edge of BCLK is always the first channel. If A2B\_PDMCTL.PDM0SLOTS = 1 or A2B\_PDMCTL.PDM1SLOTS = 1, the first slot is associated with the rising edges of BCLK, and the second slot is associated with the falling edges of BCLK.

For example, two microphones are connected to each of the DRX0/IO5 and DRX1/IO6 pins of a sub node with the PDM0 and PDM1 slots configured as 2-slot. In this case, the PDM block samples 64-bit data each frame, converts it to 24-bit PCM data, and drives the converted output as follows:

- Right microphone data is sampled on the DRX0 pin on rising clock edges and driven in the first\* transmit slot on the A<sup>2</sup>B bus.

- Left microphone data is sampled on the DRX0 pin on falling clock edges and driven in the second\* transmit slot on the A<sup>2</sup>B bus.

- Right microphone data is sampled on the DRX1pin on rising clock edges and driven in the third\* transmit slot on the A<sup>2</sup>B bus.

- Left microphone data is sampled on the DRX1 pin on falling clock edges and driven in the fourth\* transmit slot on the A<sup>2</sup>B bus.

Note that \* is the actual slot number, based on the system slot configuration.

**NOTE:** When using the default A2B\_PDMCTL2 settings, PDM pins are always sampled with rising edge data first; therefore, the A2B\_I2SCFG.RXBCLKINV and A2B\_I2SCFG.TXBCLKINV clock inversion settings are ignored when the transceiver is configured in PDM mode.

If using the default A2B\_PDMCTL2 settings and A2B\_PDMCTL.PDM0SLOTS = 0 or A2B\_PDMCTL.PDM1SLOTS = 0, only the right channel data is sampled on the PDM pin. If sampling only left channel data is desired, this can be supported by setting A2B\_PDMCTL.PDM0EN = A2B\_PDMCTL.PDM0SLOTS = A2B\_UPOFFSET = 1.

#### **PDM Enhancements**

The default PDM functionality is fully backward-compatible with previous transceiver generations; however, there are several additional features which make the PDM interface more flexible.

#### PDM Clocking Options

The DRX0 and DRX1 input pins can be configured individually as PDM inputs. When the PDM interface is enabled on an  $A^2B$  sub node on one or both of the DRX pins, a PDMCLK signal running at  $64 \times f_{SYNCM}$  (3.072 MHz at 48 kHz  $f_{SYNCM}$ ) is required to clock the PDM device. The transceivers allow either the PDMCLK/IO7 or BCLK pin to produce the required PDMCLK. PDMCLK on IO7 can be enabled by setting the A2B\_PDMCTL2.PDMALTCLK bit.

If PDMCLK/IO7 is used instead of BCLK, the restriction limiting operating to TDM2/32 or TDM4/16 is removed. The BCLK frequency can be set to a different frequency using the I<sup>2</sup>S/TDM registers. In this case, PDMCLK/IO7 is used to capture PDM input on DRX0/DRX1.

BCLK and PDMCLK/IO7 can also be used concurrently to clock the PDM microphones at the same frequency and phase alignment, but with opposite polarity. This is accomplished by setting the A2B\_PDMCTL2.PDMALTCLK bit. Additionally, a register controls whether the rising edge data or falling edge data is sampled first:

- When A2B\_PDMCTL2.PDMOFFRST = 0 (default), the PDM0 data on DRX0 is sampled rising edge first. When A2B\_PDMCTL2.PDMOFFRST = 1, it is sampled falling edge first.

- When A2B\_PDMCTL2.PDM1FFRST = 0 (default), the PDM1 data on DRX1 is sampled rising edge first. When A2B\_PDMCTL2.PDM1FFRST = 1, it is sampled falling edge first.

- **NOTE:** In a main node, BCLK is always an input; therefore, the clock output to PDM microphones connected to a main transceiver typically comes from PDMCLK/IO7.

#### PDM Data Routing Options

The PDM interface can be used on main or subordinate transceivers. The PDM data received by the transceiver can then be sent to any node on the  $A^2B$  bus, sent out to the local  $I^2S$  port, or both. This option is configured using the A2B\_PDMCTL2.PDMDEST field.

#### Full-Duplex I<sup>2</sup>S With Four PDM Microphones

If both pins (DRX0 and DRX1) are used to receive PDM data, it is possible to change the function of DTX1 so that it acts as the alternate DRX1, enabling concurrent use of up to four PDM microphones and full-duplex I<sup>2</sup>S communications. This is accomplished by setting the A2B\_I2SGCFG.RXONDTX1 bit.

### I<sup>2</sup>S/TDM Interface

The I<sup>2</sup>S/TDM serial port operates in full-duplex mode, where both the transmitter and receiver operate simultaneously using the same critical timing bit clock (BCLK) and frame synchronization (SYNC) signals. A<sup>2</sup>B subordinate transceivers generate the timing signals on the BCLK and SYNC output pins with frequencies based on the settings in the I<sup>2</sup>S global configuration register (A2B\_I2SGCFG), the I<sup>2</sup>S rate register (A2B\_I2SRATE), and the I<sup>2</sup>S reduced rate register (A2B\_I2SRATE). A<sup>2</sup>B main transceivers use the same BCLK and SYNC pins as inputs. The host drives the pins which provides the time base for the full A<sup>2</sup>B bus topology.

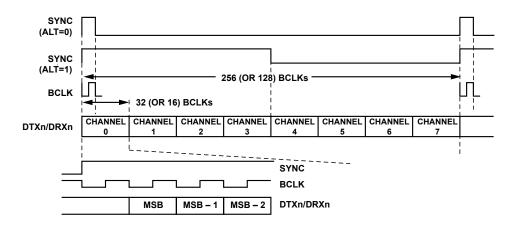

#### Time Division Multiplexing (TDM) Protocol

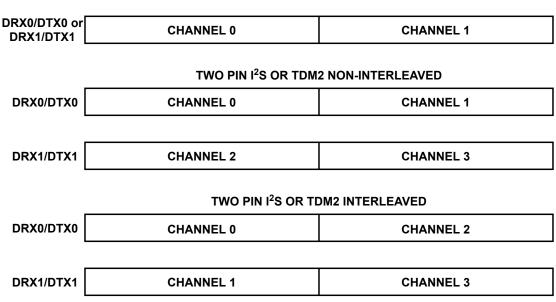

TDM mode extends an I<sup>2</sup>S interface to more than a stereo 2-channel (TDM2) signal. When the transceiver is programmed in the A2B\_I2SCFG register to support a certain number of TDM channels, this number of TDM channels is available on each enabled I<sup>2</sup>S/TDM data pin (DTX0 and DTX1 or DRX0 and DRX1). TDM2, TDM4, TDM8, TDM12, TDM16, TDM20, TDM24, and TDM32 modes are supported.

For example, if TDM4 is selected and one transmit pin (DTX0) is enabled, there are four transmit data channels. If TDM4 is selected and both transmit pins (DTX1 and DTX0) are enabled, there are eight transmit data channels, shown in the *Data Channel Structure for TDM4 Setting* figure.

|                           |           | ONE PIN        | N TDM4         |           |

|---------------------------|-----------|----------------|----------------|-----------|

| DRX0/DTX0 or<br>DRX1/DTX1 | CHANNEL 0 | CHANNEL 1      | CHANNEL 2      | CHANNEL 3 |

|                           |           | TWO PIN TDM4 N | ON-INTERLEAVED |           |

| DRX0/DTX0                 | CHANNEL 0 | CHANNEL 1      | CHANNEL 2      | CHANNEL 3 |

| •                         |           |                |                |           |

| DRX1/DTX1                 | CHANNEL 4 | CHANNEL 5      | CHANNEL 6      | CHANNEL 7 |

|                           |           |                |                |           |

|                           |           | TWO PIN TDM4   | INTERLEAVED    |           |

| DRX0/DTX0                 | CHANNEL 0 | CHANNEL 2      | CHANNEL 4      | CHANNEL 6 |

| _                         |           |                |                |           |

| DRX1/DTX1                 | CHANNEL 1 | CHANNEL 3      | CHANNEL 5      | CHANNEL 7 |

| -                         |           |                |                |           |

Figure 2-10: Data Channel Structure for TDM4 Setting (TDMMODE == 001)

The I<sup>2</sup>S/TDM serial port supports data channel widths of 16 bits or 32 bits to carry signals of varying word length. Data words are always represented in MSB first format. The BCLK signal frequencies for different TDM modes are shown in the  $I^2S/TDM$  Clock Frequency Settings for 48 kHz Superframe Rates table.

| TDM Mode | 16-bit TDM      | Channel Size        | 32-bit TDM      | Channel Size        |

|----------|-----------------|---------------------|-----------------|---------------------|

|          | Frequency (MHz) | Comments            | Frequency (MHz) | Comments            |

| TDM2     | 1.536           |                     | 3.072           |                     |

| TDM4     | 3.072           |                     | 6.144           |                     |

| TDM8     | 6.144           |                     | 12.288          |                     |

| TDM12    | 9.216           | No sub node support | 18.432          | No sub node support |

| TDM16    | 12.288          |                     | 24.576          |                     |

| TDM20    | 15.36           | No sub node support | 30.72           | No sub node support |

| TDM24    | 18.432          | No sub node support | 36.864          | No sub node support |

| TDM32    | 24.576          |                     | 49.152          |                     |

Table 2-4: I<sup>2</sup>S/TDM Clock Frequency Settings for 48 kHz Superframe Rates

The DRX0 and DRX1 input pins can be configured individually as PDM inputs. When PDM is enabled on an  $A^{2}B$  sub node on one or both of the DRX pins, a PDM clock running at  $64 \times f_{SYNCM}$  (3.072 MHz at 48 kHz  $f_{SYNCM}$ ) is required to clock the PDM device. Either the PDMCLK/IO7 pin or the BCLK pin can produce the required PDM clock. The transceiver can simultaneously transmit TDM data over the DTX0 or DTX1 pin while receiving PDM streams. However, when BCLK is used as the PDM clock, only I<sup>2</sup>S/TDM2 and 32-bit channel widths or TDM4 with 16-bit channel widths are supported. Using PDMCLK/IO7 instead of BCLK to clock PDM devices

allows BCLK to be used for a variety of TDM modes. If both DRX0 and DRX1 are used to receive PDM data, it is possible to change the function of DTX1 such that it acts as an alternate DRX1. This enables the concurrent use of up to 4 PDM microphones and full duplex I<sup>2</sup>S communication.

If using only one pin (DRX0 or DRX1) for PDM, the other pin is available simultaneously for I<sup>2</sup>S/TDM transfers.

#### Mailboxes

There are two virtual mailboxes, MBOX0 and MBOX1, that allow for inter-processor communication between the host and a subordinate node control processor.

NOTE: Throughout this section, all specific references to MBOX0 also apply to the MBOX1 instance.

The processor in a subordinate node can send a message over I<sup>2</sup>C to registers in the A<sup>2</sup>B subordinate transceiver. In the main node, the host processor is informed about the new message by an interrupt on the main transceiver's IRQ/IO0 pin and can read out the message from A<sup>2</sup>B subordinate transceiver registers over I<sup>2</sup>C using the BUS\_ADDR. If a mailbox message exchange is from the A<sup>2</sup>B main node to the A<sup>2</sup>B subordinate node, the host places a message in A<sup>2</sup>B subordinate transceiver registers over I<sup>2</sup>C using the BUS\_ADDR. In the subordinate transceiver registers over I<sup>2</sup>C using the BUS\_ADDR. In the subordinate node, the processor is informed of this new message by an interrupt on the subordinate transceiver's IRQ/IO0 pin and can directly read out the message over I<sup>2</sup>C from A<sup>2</sup>B subordinate transceiver registers after checking the A2B\_LINTTYPE register.

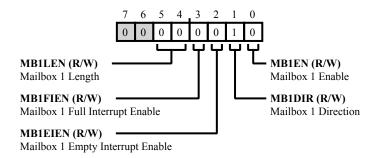

#### Mailbox Programming and Operation

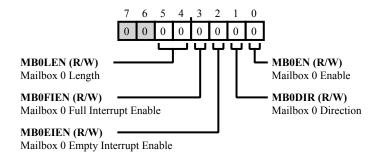

The A2B\_MBOX0CTL register provides bit fields to enable the mailbox and control direction, message length, and interrupt capabilities.

By default, mailbox 0 is configured as a receive mailbox (written by the host, read by the subordinate node processor), and mailbox 1 is configured as a transmit mailbox (written by the subordinate node processor, read by the host). Manipulating the A2B MBOX0CTL.MB0DIR bit controls the direction of the mailbox.

Each mailbox can hold either 8-, 16-, 24-, or 32-bit messages, as configured in the A2B\_MBOX0CTL.MB0LEN field. The value in this field determines which of the four byte-wide A2B\_MBOX0B0 through A2B\_MBOX0B3 registers to use for the data, where the first byte is always in the A2B\_MBOX0B0 register, and the final byte is in the highest data register required to accommodate the programmed data length, as shown in the following table.

| MBxLEN Field | Final Byte in Register |

|--------------|------------------------|

| 0b00         | A2B_MBOX0B0            |

| 0b01         | A2B_MBOX0B1            |

| 0b10         | A2B_MBOX0B2            |

| 0b11         | A2B_MBOX0B3            |

For an enabled receive mailbox (A2B\_MBOX0CTL.MB0EN = 1 and A2B\_MBOX0CTL.MB0DIR = 0), if the A2B\_MBOX0CTL.MB0FIEN bit is set, an interrupt to the subordinate node occurs after the final byte of the mailbox is written by the host and received by the  $A^2B$  subordinate transceiver. If the A2B\_MBOX0CTL.MB0EIEN bit

is set, an interrupt is propagated back upstream over the A<sup>2</sup>B bus to the host after the final byte of the mailbox is read by the local processor in the subordinate node.

For an enabled transmit mailbox (A2B\_MBOX0CTL.MB0EN = 1 and A2B\_MBOX0CTL.MB0DIR = 1), if the A2B\_MBOX0CTL.MB0FIEN bit is set, an interrupt to the host occurs after the final byte of the mailbox is written by the local processor in the subordinate node. If the A2B\_MBOX0CTL.MB0EIEN bit is set, an interrupt is propagated downstream over the A<sup>2</sup>B bus to the subordinate node after the final byte of the mailbox is read by the host.

**CAUTION:** Dynamic reconfiguration of an enabled mailbox (A2B\_MBOX0CTL.MB0EN = 1) is forbidden. The host must first disable the mailbox (A2B\_MBOX0CTL.MB0EN = 0) and then re-enable it in two separate accesses if reconfiguration is required.

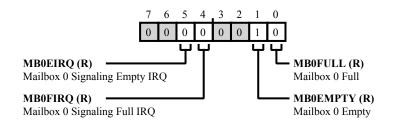

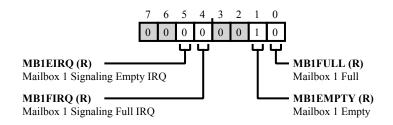

The A2B MBOX0STAT register provides status information for the mailboxes:

- When a mailbox is filled, the A2B\_MBOX0STAT.MB0FULL bit is set, and the A2B\_MBOX0STAT.MB0EMPTY bit is cleared.

- When a mailbox is emptied, the A2B\_MBOX0STAT.MB0EMPTY bit is set, and the A2B\_MBOX0STAT.MB0FULL bit is cleared.

- The A2B\_MBOX0STAT.MB0EIRQ and A2B\_MBOX0STAT.MB0FIRQ bits are set when the mailbox signals an interrupt to the host or local processor, and the bits are cleared when the interrupt is processed by the host or local processor.

Multiple subordinate nodes can communicate to the main node through their TX mailboxes. In the main node, the A2B\_INTTYPE register contains information about the pending interrupt generated by any subordinate node, with the subordinate node indicated in the A2B\_INTSRC register.

When two subordinates write to their mailboxes simultaneously, the main gets the interrupt indication from the subordinate that is closer to the main. Upon detecting the interrupt, the host extracts the interrupt information by reading the A<sup>2</sup>B main transceiver's interrupt type (A2B\_INTTYPE) and interrupt source (A2B\_INTSRC) registers to determine which interrupt occurred and which subordinate node generated it, respectively. Upon reading the A2B\_INTTYPE register, the interrupt request for that interrupt is cleared in the subordinate node identified by the value in the A2B\_INTSRC register. The IRQ/IOO pin toggles to the deasserted state and then immediately back into the asserted state due to the still active interrupt from the other subordinate node, and the host can again read the main transceiver's A2B\_INTTYPE and A2B\_INTSRC registers to acknowledge the other subordinate node's mailbox interrupt.

#### **Mailbox Latency**

The mailbox transactions are made up of register reads and writes over the I<sup>2</sup>C bus. The interrupt request from a subordinate to the main transceiver is part of the SRF packet, so the latency on the subordinate to main transceiver mailbox can include an extra superframe waiting for this time.

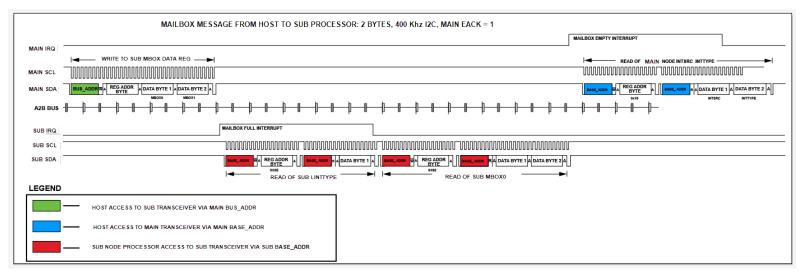

The following figures show the system timing for the mailbox transactions in both directions. The light gray slots indicate the SCF field, and the dark gray slots indicate the SRF field.

As shown in the *Mailbox Latency (from Host to Subordinate)* figure, when the mailbox message is from the host to a subordinate processor, the host processor writes the mailbox data to the A<sup>2</sup>B subordinate node through the SCF field using a 2-byte burst write access to the main transceiver BUS\_ADDR device address. When the writes complete, the subordinate transceiver immediately generates the interrupt to its local node processor. As a result, the subordinate interrupt request (SUBORDINATE IRQ) asserted on IRQ/IO0 aligns with the SCF field. Once this interrupt is asserted, the locally-connected processor can use the subordinate transceiver BASE\_ADDR device address to interrogate the A2B\_LINTTYPE register to determine that it is the mailbox full interrupt, after which it can then extract the data from the mailbox data registers using a 2-byte burst read. Once those transactions finish, the mailbox empty interrupt is generated at the main node (MAIN IRQ), aligned with the SRF field, and the host proceeds with reading the A2B\_INTSRC and A2B\_INTTYPE registers of the main transceiver (using the main transceiver BASE\_ADDR device address) to determine that it is the mailbox empty interrupt originating with the indicated subordinate.

Figure 2-11: Mailbox Latency (from Host to Subordinate)

Similarly, as shown in the *Mailbox Latency (from Subordinate to Host)* figure, when the mailbox message is from a subordinate processor to the host, the subordinate node processor populates the mailbox data registers at any time by issuing writes to the registers using the subordinate transceiver BASE\_ADDR device address, and the interrupt indication to the main A<sup>2</sup>B node goes through the SRF field. As a result, the main mailbox full interrupt request (MAIN IRQ) asserted on IRQ/IO0 aligns with the SRF field. Once this interrupt is asserted, the host (using the main transceiver BASE\_ADDR device address) interrogates the A2B\_INTSRC and A2B\_INTTYPE registers to determine that it is the mailbox full interrupt originating with the indicated subordinate.

|                                             | MAILBOX MESSAGE FROM SUB PROCESSOR TO HOST: 2 BYTES, 400 KHZ I2C                                                                                                           |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SUB IRQ<br>SUB SCL<br>SUB SDA               |                                                                                                                                                                            |  |

| A2B BUS<br>MAIN IRQ<br>MAIN SCL<br>MAIN SDA |                                                                                                                                                                            |  |

|                                             | HOST ACCESS TO SUB TRANSCEIVER VIA MAIN BUS_ADDR     HOST ACCESS TO MAIN TRANSCEIVER VIA MAIN BASE_ADDR     SUB NODE PROCESSOR ACCESS TO SUB TRANSCEIVER VIA SUB BASE_ADDR |  |

Figure 2-12: Mailbox Latency (from Subordinate to Host)

To subsequently extract the data from the mailbox of the subordinate transceiver, the host must first set the A2B\_NODEADR register to the subordinate node that generated the interrupt (using a main transceiver BASE\_ADDR write access), and then issue the BUS\_ADDR accesses to read the mailbox data byte registers of the subordinate transceiver (note the superframe spacing required for these reads to take place). Once the last byte is read by the host, the mailbox empty interrupt request of the subordinate node (SUBORDINATE IRQ) gets asserted in the next SCF. Then, the subordinate node processor can use a subordinate transceiver BASE\_ADDR access to read the A2B\_LINTTYPE register and take action after identifying that it was the mailbox empty interrupt that occurred (for example, load the mailbox data registers again to restart the process).

# **3** A<sup>2</sup>B Operation and Configuration

The A<sup>2</sup>B bus is high-level programmable and can address many use cases. A<sup>2</sup>B systems are easy to configure, based on knowledge of the system, nodes, and peripherals. The exact system configuration can be gained by collecting information individually from each subordinate. As an example, the same A<sup>2</sup>B module can be supplied by different vendors, with each of the modules having unique register programming requirements. One module can use TDM4 as an audio interface, while another one uses TDM8. One module can provide two upstream channels, while another can provide three upstream channels, all with the host not having prior knowledge of how many nodes are connected.

**IMPORTANT:** Ensure that the register programming results in a valid system configuration.

Analog Devices provides free SigmaStudio<sup>TM</sup> (http://www.analog.com/SigmaStudio) tools featuring an intuitive graphical user interface to architect, configure, and set up the A<sup>2</sup>B bus. The tools also generate driver code for embedded software.

Linux and QNX software drivers also are available upon request.

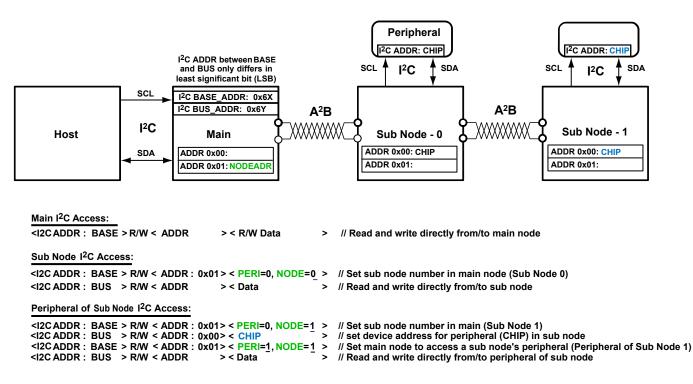

## I<sup>2</sup>C Port Programming Concepts

Main transceiver enabled registers are programmed directly by the A<sup>2</sup>B host via the I<sup>2</sup>C port using Direct I<sup>2</sup>C Register Accesses. Transceiver sub node enabled registers can also be programmed in this fashion by an I<sup>2</sup>C-connected controller on the subordinate node; however, A<sup>2</sup>B subordinate transceiver registers are typically programmed remotely by the A<sup>2</sup>B host through the main transceiver over the A<sup>2</sup>B bus using Remote Target I<sup>2</sup>C Register Accesses. Further, if a subordinate transceiver is locally connected to an I<sup>2</sup>C target device on the subordinate node, that connected I<sup>2</sup>C target device can also be accessed remotely by the A<sup>2</sup>B host over the A<sup>2</sup>B bus using Remote Peripheral I<sup>2</sup>C Accesses. The *Programming Sequence for I<sup>2</sup>C Accesses* figure is a graphical representation of the programming sequences that are required when programming transceiver registers and accessing target node I<sup>2</sup>C peripheral devices.

Figure 3-1: Programming Sequence for I<sup>2</sup>C Accesses

In the *Programming Sequence for I*<sup>2</sup>*C Accesses* figure:

- I2C ADDR is the controller transceiver I<sup>2</sup>C device address:

- Direct I<sup>2</sup>C Register Accesses to the main transceiver use BASE\_ADDR (I2C ADDR: BASE).

- Remote Target I<sup>2</sup>C Register Accesses to a subordinate transceiver and Remote Peripheral I<sup>2</sup>C Accesses to an I<sup>2</sup>C-connected peripheral on a subordinate node use BUS\_ADDR (I2C ADDR: BUS).

**NOTE:** See Transceiver I<sup>2</sup>C Accesses for more details regarding BASE\_ADDR and BUS\_ADDR.

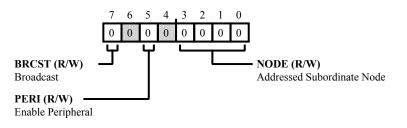

- NODEADR is the main transceiver A2B\_NODEADR register:

- NODE is the A2B NODEADR.NODE field.

- PERI is the A2B\_NODEADR.PERI bit.

- CHIP is the A2B\_CHIP register:

- Black text indicates the A2B\_CHIP register itself.

- Blue text indicates the value of the A2B CHIP register.

### Direct I<sup>2</sup>C Register Accesses

The I<sup>2</sup>C port can be used to directly access the transceiver register space, whether the transceiver is configured as a main or as a subordinate:

- On the main node, the A<sup>2</sup>B host directly accesses the main transceiver register space using this method.

- On a subordinate node, a locally-connected I<sup>2</sup>C host directly accesses the subordinate transceiver register space using this method.

As shown in the *Main*  $I^2C$  Access portion of the *Programming Sequence for*  $I^2C$  Accesses figure, a main transceiver register access requires the I<sup>2</sup>C transfer from the host to consist of the main transceiver I<sup>2</sup>C device address (I2C ADDR: BASE = BASE\_ADDR), followed by the register address (ADDR), followed finally by the data associated with the main transceiver register (R/W Data). For further details, see Transceiver I<sup>2</sup>C Accesses.

**NOTE:** This *Main I^2C Access* sequence is identical for an  $I^2C$ -connected host on the subordinate node directly accessing a subordinate transceiver's register space.

## Remote Target I<sup>2</sup>C Register Accesses

Though a locally-connected I<sup>2</sup>C host on a subordinate node can directly program subordinate transceiver registers over the I<sup>2</sup>C port, A<sup>2</sup>B systems are typically fully configured by the A<sup>2</sup>B host from the main node. As shown in the *Subordinate 0 I<sup>2</sup>C Access* portion of the *Programming Sequence for I<sup>2</sup>C Accesses* figure, the 2-step process consists of the A<sup>2</sup>B host first directly configuring the main transceiver before using remote I<sup>2</sup>C accesses to program a specific subordinate transceiver over the A<sup>2</sup>B bus. The A<sup>2</sup>B host must use the following programming sequence to access an A<sup>2</sup>B subordinate transceiver register space remotely over the A<sup>2</sup>B bus from the main node.

Use a Direct I<sup>2</sup>C Register Accesses to set the main transceiver A2B\_NODEADR.NODE field to the subordinate node ID to be accessed. Be sure the A2B\_NODEADR.PERI bit is set to 0 in this write so that subsequent bus accesses target the indicated subordinate transceiver register space rather than an I<sup>2</sup>C peripheral connected to the indicated subordinate.

ADDITIONAL INFORMATION: Setting the A2B\_NODEADR.NODE field to 0 means that subsequent bus accesses will target subordinate node 0. If this field were set to 1, subsequent bus accesses would target subordinate node 1. If the intent is to broadcast the write to all of the discovered nodes (main and subordinates), be sure to also set the broadcast bit (A2B\_NODEADR.BRCST) in this write.

To access the subordinate transceiver register, the I<sup>2</sup>C transfer from the host consists of the main transceiver's bus address (I2C ADDR: BUS = BUS\_ADDR), followed by the subordinate transceiver register address (ADDR), followed finally by the data associated with the subordinate transceiver register (Data). For more details, see Transceiver I<sup>2</sup>C Accesses.

## Remote Peripheral I<sup>2</sup>C Accesses

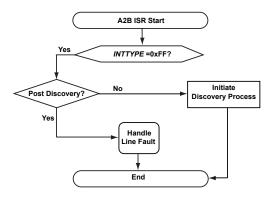

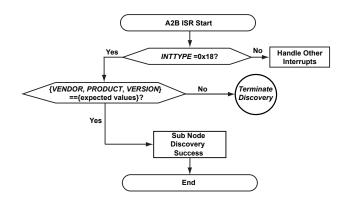

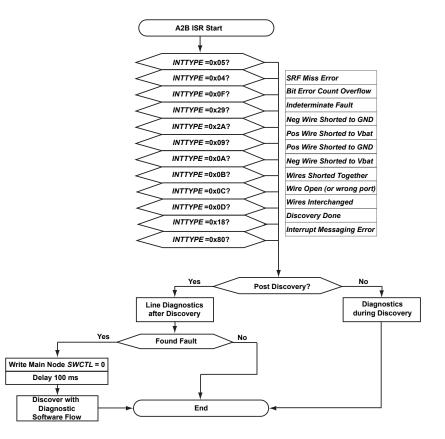

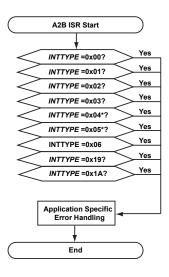

The *Peripheral of Target 1 I*<sup>2</sup>*C Access* portion of the *Programming Sequence for I*<sup>2</sup>*C Accesses* figure illustrates the sequence required for the A<sup>2</sup>B host to access a peripheral connected to the I<sup>2</sup>C port of a subordinate transceiver over