# The LT1167: Precision, Low Cost, Low Power Instrumentation Amplifier Requires a Single Gain-Set Resistor

# Introduction

The LT1167 is the next-generation instrumentation amplifier designed to replace the previous generation of monolithic instrumentation amps, as well as discrete, multiple op amp solutions. Instrumentation amplifiers differ from operational amplifiers in that they can amplify input signals that are not ground referenced. The output of an instrumentation amplifier is referenced to an external voltage that is independent of the input. Conversely, the output voltage of an op amp, due to the nature of its feedback, is referenced to the differential and common mode input voltage.

A separate ground reference and the high CMRR of the LT1167 instrumentation amplifier reduce the effect of the input common mode voltage on the output signal. The closed-loop gain of an op amp and of most instrumentation amps is set by a resistor ratio; the gain of the LT1167 is set by the absolute value of one external resistor. Gain error depends on the ratio of one external resistor to the value of the LT1167's internal, lasertrimmed resistors, which are trimmed to better than 0.1%. Once the gain is set, it is expected to remain constant when the output voltage or output current changes. Any change in gain with output swing will show up as gain nonlinearity.

Parameters such as gain error, voltage offset and CMRR are a function of trimming. Gain nonlinearity cannot be trimmed; it is a function of careful design and die layout. The use of common centroid geometries and isothermal layout cancels the errors due to die stress and thermal gradients. If this is not done correctly, all the trimming in the world will not improve performance.

### **Input Protection**

Instrumentation amplifiers must survive in a hostile environment. Not only does the LT1167 have to endure ESD during handling (power off) but it must also survive excessive voltage during operation. The inputs of the LT1167 have low leakage internal diodes from each input to the supplies. These diodes have a maximum current rating of 20mA and protect the IC when the input voltage exceeds the supply rails. Precision and indestructibility are combined when an external 20k resistor is placed in series with each input. There is little offset voltage penalty because the 320pA offset current from the LT1167 multiplied by the 20k input resistors contributes only  $6.4\mu$ V additional offset. With the 20k resistors, the LT1167 can handle both ±400VDC input faults and ESD spikes over 4kV. This meets the IEC 1004-2 level 2 European standard.

The low noise voltage of  $7.5nV\sqrt{Hz}$ is achieved by idling a large portion of the 0.9mA supply current in the input stage. Input bias current is not compromised due to the use of superbeta transistors, current-cancellation circuitry and trimming. The LT1167's input bias current is better than that of a JFET input stage at only 350pA maximum at room temperature; it does not double for every 10°C. The LT1167 is also trimmed for critical DC parameters, such as input offset voltage and CMRR. These trims allow the amplifier to achieve very high DC accuracy; total input-referred offset voltage is only 60µV and CMRR is better than 110dB at a gain of ten. Worst-case input offset is at a gain of one; it is guaranteed to be less than  $240\mu V$  for the prime grade. The LT1167 is offered in 8-pin PDIP and

# by Alexander Strong

SO packages, saving significant board space compared to discrete designs. With these advantages, the LT1167 will easily find its way into many applications.

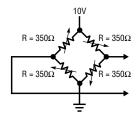

PRECISION BRIDGE TRANSDUCER

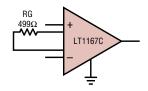

LT1167 MONOLITHIC INSTRUMENTATION AMPLIFIER, G = 100 SUPPLY CURRENT = 1.3mA MAX

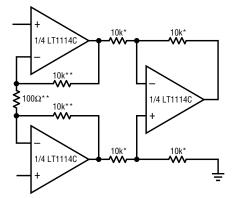

"ROLL YOUR OWN" INSTRUMENTATION AMP, G = 100 \*0.02% RESISTOR MATCH, 3PPM/°C TRACKING \*\*DISCRETE 1%RESISTOR, 100PPM/°C TRACKING SUPPLY CURRENT = 1.35mA FOR THREE AMPLIFIERS

Figure 1. "Roll your own" vs LT1167

|                                                       |                                                         | "D-11 V 0 " 0''                                             | Error (PPM) of Full Scale |                    |

|-------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|---------------------------|--------------------|

| Error Source                                          | LT1167 Circuit Calculations                             | "Roll Your Own" Circuit<br>Calculations                     | LT1167                    | "Roll Your<br>Own" |

|                                                       | Absolute Accurat                                        | cy at T <sub>A</sub> = 25°C                                 |                           |                    |

| Input Offset Current                                  | $I_{OS} \times R_S / V_{FS}$                            | $I_{0S} \times R_S / V_{FS}$                                | 4                         | 4                  |

| nput Offset Voltage V <sub>OSI</sub> /V <sub>FS</sub> |                                                         | $\Delta V_{0S}/V_{FS}$                                      | 3000                      | 6500               |

| Output Offset Voltage                                 | : Voltage V <sub>OSO</sub> /G/V <sub>FS</sub>           |                                                             | 150                       | 75                 |

| CMRR                                                  | $CMRR \times V_{CM}/V_{FS}$                             | $\rm RM \times \rm V_{CM}/\rm G/V_{FS}$                     | 790                       | 500                |

| Total Absolute Error                                  | 3944                                                    | 7079                                                        |                           |                    |

|                                                       | Drift to                                                | 85°C                                                        | 1                         |                    |

| Input Offset Voltage Drift                            | $TCV_{OSI} \times \DeltaT/V_{FS}$                       | $\rm TC\Delta V_{\rm OS} \times \ \Delta T/V_{\rm FS}$      | 1200                      | 5700               |

| Output Offset Voltage Drift                           | ${\sf TCV}_{\sf OSO} 	imes \Delta {\sf T/G/V}_{\sf FS}$ | $\rm TCV_{\rm OS} \times ~NG \times ~\Delta T/G/V_{\rm FS}$ | 180                       | 78                 |

| Gain Drift                                            | $(TCG + TCR) \times \Delta T$                           | $TCRM \times \DeltaT$                                       | 3,600                     | 6000               |

| Total Drift Error                                     | 4980                                                    | 11,778                                                      |                           |                    |

|                                                       | Resol                                                   | ution                                                       |                           |                    |

| Gain Nonlinearity                                     | GNL                                                     | RNL                                                         | 15                        | 10                 |

| Typical 0.1Hz–10Hz<br>Voltage Noise                   | e <sub>n</sub> /V <sub>FS</sub>                         | $e_n \times \sqrt{2}/V_{FS}$                                | 14                        | 21                 |

| Total Resolution Error                                | 29                                                      | 31                                                          |                           |                    |

| Grand Total Error                                     | 8953                                                    | 18,888                                                      |                           |                    |

#### Table 1a. "Roll your own" vs LT1167 error budget

### "Roll Your Own"—Discrete vs Monolithic LT1167 Error Budget Analysis

The LT1167 offers performance superior to that of "roll your own," three–op amp discrete designs. A typical application that amplifies and buffers a bridge transducer's differential output is shown in Figure 1. The amplifier, with its gain set to one hundred, amplifies a differential, fullscale output voltage of 20mV over the industrial temperature range. The discrete instrumentation amp uses the best precision, low power, superbeta quad op amp available, the LT1114. This comparison demonstrates that the LT1167 outperforms a discrete instrumentation amplifier using a state-of-the-art op amp. The error budget comparison in Table 1 shows how various errors are calculated and referenced to the bridge's full-scale output of 20mV. The table shows that some of the greatest differences in error between the LT1167 and the discrete solution are input offset voltage, input offset voltage drift and CMRR. Expensive precision resistor arrays that can deliver 0.02%

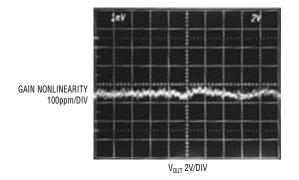

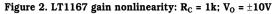

Figure 3. Gain nonlinearity of a previous generation instrumentation amp:  $R_C$  = 1k;  $V_O$  =  $\pm 10V$

# ▲ DESIGN FEATURES

matching are required to match the LT1167's CMRR performance. The total error for the LT1167 solution is much lower than that of the discrete solution. The LT1167 has other advantages over a discrete design, including lower power dissipation, lower component cost and smaller size. The clear advantage goes to the LT1167.

# LT1167 vs the Competition

What was said about the LT1167 when compared to discrete solutions is also applicable to previous IC instrumentation amplifiers. Improvements in circuit design and common centroid layout greatly enhance the CMRR, PSRR, gain error and nonlinearity over competitive IC solutions.

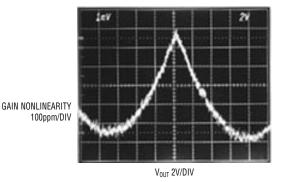

Figure 4. Single-supply pressure monitor

The LT1167 has a 10dB improvement for CMRR and a 20dB improvement in PSRR for the worst-case condition of unity gain. Gain error is better than

|                                 | Table 1b. Terms used in Table 1a |                      |                                                     |  |  |  |

|---------------------------------|----------------------------------|----------------------|-----------------------------------------------------|--|--|--|

| Term                            | LT1167 Spec                      | LT1114C Spec         | Comment                                             |  |  |  |

| I <sub>OS</sub>                 | 450pA                            | 500pA                | Input Offset Current                                |  |  |  |

| R <sub>s</sub>                  | 350Ω/2                           | 350Ω/2               | Source Resistance                                   |  |  |  |

| V <sub>FS</sub>                 | 20mV                             | 20mV                 | Full-Scale Input Voltage                            |  |  |  |

| V <sub>OSI</sub>                | 60µV                             | N/A                  | Input Offset Voltage                                |  |  |  |

| $\Delta V_{OS}$                 | N/A                              | 130µV                | Input Offset Voltage Match                          |  |  |  |

| V <sub>OSO</sub>                | 300µV                            | N/A                  | Output Offset Voltage                               |  |  |  |

| V <sub>OS</sub>                 | N/A                              | 75µV                 | Offset Voltage                                      |  |  |  |

| NG                              | N/A                              | 2V/V                 | Noise Gain of Output Op Amp                         |  |  |  |

| G                               | 100V/V                           | 100V/V               | Gain                                                |  |  |  |

| CMRR                            | 110dB (3.16ppm)                  | N/A                  | Common Mode Rejection Ratio                         |  |  |  |

| V <sub>CM</sub>                 | 5V                               | 5V                   | Common Mode Voltage                                 |  |  |  |

| RM                              | NA                               | 0.02%                | Resistor Match                                      |  |  |  |

| TCV <sub>OSI</sub>              | 0.4V/°C                          | N/A                  | Temperature Coefficient of<br>Input Offset Voltage  |  |  |  |

| ΔΤ                              | 60°C                             | 60°C                 | Change in Temperature                               |  |  |  |

| TC <sub>2</sub> V <sub>0S</sub> | N/A                              | 1.9µV/°C             | Temperature Coefficient of<br>Offset Voltage Match  |  |  |  |

| TCV <sub>OSO</sub>              | 6µV/°C                           | N/A                  | Temperature Coefficient of<br>Output Offset Voltage |  |  |  |

| TCV <sub>OS</sub>               | N/A                              | 1.3µV/°C             | Temperature Coefficient of<br>Offset Voltage        |  |  |  |

| TCG                             | 50ppm/°C                         | N/A                  | Temperature Coefficient of Gain                     |  |  |  |

| TCR                             | 10ppm/°C                         | N/A                  | Temperature Coefficient of<br>Resistance            |  |  |  |

| TCRM                            | N/A                              | 100ppm/°C            | Temperature Coefficient of<br>Resistor Match        |  |  |  |

| GNL                             | 15ppm                            | N/A                  | Gain Nonlinearity                                   |  |  |  |

| RNL                             | N/A                              | 10ppm                | Resistor Nonlinearity                               |  |  |  |

| en                              | 0.28μV <sub>P-P</sub>            | 0.3μV <sub>P-P</sub> | 0.1Hz–10Hz Voltage Noise                            |  |  |  |

0.1% for all gains up to one hundred, which is a  $2.5 \times$  to  $5 \times$  improvement over previous ICs. This gain error is maintained even when the output has to drive heavy loads, thanks to improvements in common centroid layout. The LT1167 maintains excellent performance even when driving heavy loads. Figure 2 is a photo of the LT1167 in a gain of one thousand driving a 1k load. Figure 3 is a previous generation IC instrumentation amplifier in the same condition. You can see why a 10k load resister and not a 1k resistor was specified for older ICs.

### Low I<sub>B</sub> Favors High Impedance Bridges, Lowers Dissipation

The LT1167's low supply current, low supply voltage operation and low input bias current (350pA max) allow it to fit nicely into battery powered applications. Low overall power dissipation necessitates using higher impedance bridges. Figure 4 shows the LT1167 connected to a  $3k\Omega$ bridge's differential output. The bridge's impedance is almost an order of magnitude higher than that of the bridge used in the error-budget table. The picoampere input bias currents will still keep the error caused by offset current to a negligible level. The LT1112 level shifts the LT1167's reference pin and the ADC's analog ground pins above ground. This is necessary in single-supply applications because the output cannot swing to ground. The LT1167's and LT1112's

**Nerve-Impulse Amplifier**

combined power dissipation is still less than the bridge's. This circuit's total supply current is just 3mA.

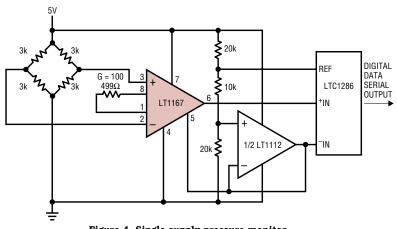

# **ADC Signal Conditioning**

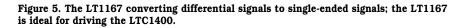

The LT1167 is shown in Figure 5 changing a differential signal into a single-ended signal. The single-ended signal is then filtered with a passive 1st order RC lowpass filter and applied to the LTC1400 12-bit analog-to-digital converter (ADC). The LT1167's output stage can easily drive the ADC's small nominal input capacitance, preserving signal integrity. Figure 6 shows two FFTs of the amplifier/ADC's output. Figures 6a and 6b show

the results of operating the LT1167 at unity gain and a gain of ten, respectively. This results in a typical SINAD of 70.6dB.

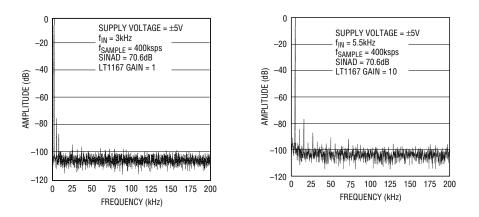

### **Current Source**

Figure 7 shows a simple, accurate, low power programmable current source. The differential voltage across pins 2 and 3 is mirrored across  $R_G$ . The voltage across  $R_G$  is amplified and applied across R1, defining the output current. The 50µA bias current flowing from pin 5 is buffered by the LT1464 JFET operational amplifier, which increases the resolution of the current source to 3pA.

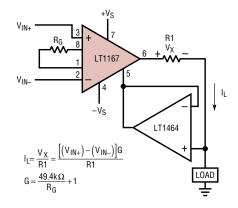

The LT1167's low current noise makes it ideal for ECG monitors that have  $M\Omega$  source impedances. Demonstrating the LT1167's ability to amplify low level signals, the circuit in Figure 8 takes advantage of the amplifier's high gain and low noise operation. This circuit amplifies the low level nerve impulse signals received from a patient at pins 2 and 3 of the LT1167. R<sub>G</sub> and the parallel combination of R3 and R4 set a gain of ten. The potential on LT1112's pin 1 creates a ground for the common mode signal. The LT1167's high CMRR of 110db ensures that the desired differential signal is amplified and unwanted common mode signals are attenuated. Since the DC portion of the signal is not important, R6 and C2 make up a 0.3Hz highpass filter. The AC signal at LT1112's pin 5 is amplified by a gain of 101 set by R7/R8 + 1. The parallel combination of C3 and R7 forms a lowpass filter that decreases this gain at frequencies above 1kHz.

The ability to operate at  $\pm 3V$  on 0.9mA of supply current makes the LT1167 ideal for battery-powered applications. Total supply current for this application is 1.7mA. Proper safeguards, such as isolation, must be added to this circuit to protect the patient from possible harm.

continued on page 38

Figure 7. Precision current source

Figure 6. Operating at a gain of one (left) or ten (right), Figure 5's circuit achieves 12-bit operation with a SINAD of 70.6dB

LT1167, continued from page 9

### Conclusion

The LT1167 instrumentation amplifier delivers the best precision, lowest noise, highest fault tolerance, plus the ease of use provided by singleresistor gain setting. The LT1167 is offered in 8-pin PDIP and SO packages. The SO uses significantly less board space than discrete designs. With these advantages and the ability to operate over a wide range of supply voltages at a quiescent current of 0.9mA, the LT1167 is appropriate for a wide range of applications.  $\checkmark$