RELIABILITY REPORT FOR MAX1426CAI PLASTIC ENCAPSULATED DEVICES

December 15, 2008

## MAXIM INTEGRATED PRODUCTS

120 SAN GABRIEL DR.

SUNNYVALE, CA 94086

| Approved by                       |  |  |

|-----------------------------------|--|--|

| Ken Wendel                        |  |  |

| Quality Assurance                 |  |  |

| Director, Reliability Engineering |  |  |

Maxim Integrated Products. All rights reserved.

### Conclusion

The MAX1426CAI successfully meets the quality and reliability standards required of all Maxim products. In addition, Maxim's continuous reliability monitoring program ensures that all outgoing product will continue to meet Maxim's quality and reliability standards.

### **Table of Contents**

I. ......Device Description II. ......Manufacturing Information III. .....Packaging Information IV. .....Die Information V. .....Quality Assurance Information VI. .....Reliability Evaluation

.....Attachments

### I. Device Description

A. General

The MAX1426 10-bit, monolithic analog-to-digital converter (ADC) is capable of a 10Msps sampling rate. This device features an internal track-and-hold (T/H) amplifier for excellent dynamic performance; at the same time, it minimizes the number of external components. Low input capacitance of only 8pF minimizes input drive requirements. A wide input bandwidth (up to 150MHz) makes this device suitable for digital RF/IF downconverter applications employing undersampling techniques.

The MAX1426 employs a differential pipelined architecture with a wideband T/H amplifier to maximize throughput while limiting power consumption to only 156mW. The MAX1426 generates an internal +2.5V reference that supplies three additional reference voltages (+3.25V, +2.25V, and +1.25V). These reference voltages provide a differential input range of +2V to -2V. The analog inputs are biased internally to correct the DC level, eliminating the need for external biasing on AC-coupled applications.

A separate +3V digital logic supply input allows for separation of digital and analog circuitry. The output data is in two's complement format. The MAX1426 is available in the space-saving 28-pin SSOP package. For a pin-compatible version at a higher data rate, refer to the MAX1424 or MAX1425.

#### B. Absolute Maximum Ratings

| Item                                         | Rating                           |

|----------------------------------------------|----------------------------------|

| AVDD to AGND                                 | -0.3V to +6V                     |

| DVDD to DGND                                 | -0.3V to +6V                     |

| AVDD to DGND                                 | -0.3V to +6V                     |

| DGND to AGND                                 | ±0.3V                            |

| REFP, REFIN, REFN, CMLN, CMLP, CML, INP, INN | (VAGND - 0.3V) to (VAVDD + 0.3V) |

| CLK, OE/PD, D0–D9                            | (VDGND - 0.3V) to (VDVDD + 0.3V) |

| Operating Temperature Ranges                 |                                  |

| MAX1426CAI                                   | 0°C to +70°C                     |

| MAX1426EAI                                   | -40°C to +85°C                   |

| Maximum Junction Temperature                 | +150°C                           |

| Storage Temperature Range                    | -65°C to +150°C                  |

| Lead Temperature (soldering, 10s)            | +300°C                           |

| Continuous Power Dissipation (TA = +70°C)    |                                  |

| 28-Pin SSOP                                  | 762mW                            |

| Derates above +70°C                          |                                  |

| 28-Pin SSOP                                  | 9.5mW/°C                         |

## II. Manufacturing Information

| A. Description/Function:         | 10-Bit, 10Msps ADC      |  |  |

|----------------------------------|-------------------------|--|--|

| B. Process:                      | TC06                    |  |  |

| C. Number of Device Transistors: | 5305                    |  |  |

| D. Fabrication Location:         | Taiwan                  |  |  |

| E. Assembly Location:            | Philippines or Malaysia |  |  |

| F. Date of Initial Production:   | January, 2000           |  |  |

# III. Packaging Information

| A. Package Type:                                                            | 28-Lead SSOP             |

|-----------------------------------------------------------------------------|--------------------------|

| B. Lead Frame:                                                              | Copper                   |

| C. Lead Finish:                                                             | Solder Plate             |

| D. Die Attach:                                                              | Silver-filled Epoxy      |

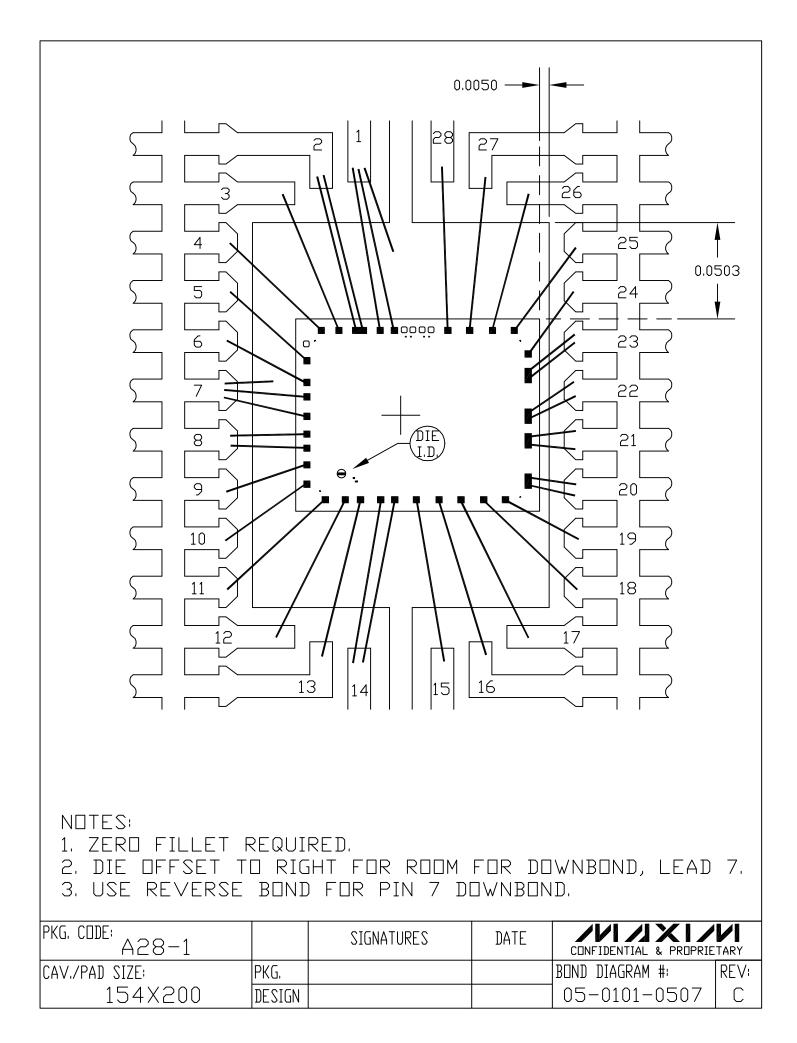

| E. Bondwire:                                                                | Gold (1.0 mil dia.)      |

| F. Mold Material:                                                           | Epoxy with silica filler |

| G. Assembly Diagram:                                                        | # 05-0101-0507           |

| H. Flammability Rating:                                                     | Class UL94-V0            |

| I. Classification of Moisture Sensitivity<br>per JEDEC standard JESD22-112: | Level 1                  |

## **IV.** Die Information

| A. Dimensions:             | 135 x 110 mils                                           |

|----------------------------|----------------------------------------------------------|

| B. Passivation:            | $Si_3N_4/SiO_2$ (Silicon nitride/ Silicon dioxide)       |

| C. Interconnect:           | Aluminum/Si (Si = 1%)                                    |

| D. Backside Metallization: | None                                                     |

| E. Minimum Metal Width:    | Metal 1 - 0.9 microns / Metal 2 - 0.9 microns (as drawn) |

| F. Minimum Metal Spacing:  | Metal 1 - 0.9 microns / Metal 2 - 0.9 microns (as drawn) |

| G. Bondpad Dimensions:     | 5 mil. Sq.                                               |

| H. Isolation Dielectric:   | SiO <sub>2</sub>                                         |

| I. Die Separation Method:  | Wafer Saw                                                |

### V. Quality Assurance Information

| Α. | Quality Assurance Contacts: | Ken Wendel (Director, Reliability Engineering) |

|----|-----------------------------|------------------------------------------------|

|    |                             | Bryan Preeshl (Managing Director of QA)        |

- B. Outgoing Inspection Level: 0.1% for all electrical parameters guaranteed by the Datasheet.

0.1% For all Visual Defects.

- C. Observed Outgoing Defect Rate: < 50 ppm

- D. Sampling Plan: Mil-Std-105D

## VI. Reliability Evaluation

A. Accelerated Life Test

The results of the 135°C biased (static) life test are shown in **Table 1**. Using these results, the Failure Rate ( $\lambda$ ) is calculated as follows:

$\lambda = \underbrace{1}_{\text{MTTF}} = \underbrace{\frac{1.83}{192 \times 4340 \times 50 \times 2}}_{\text{Temperature Acceleration factor assuming an activation energy of 0.8eV}$

$\lambda = 21.99 \times 10^{-9}$

$\lambda$  = 21.99 F.I.T. (60% confidence level @ 25°C)

This following failure rate represents data collected from Maxim's reliability monitor program. Maxim performs quarterly 1000 hour life test monitors on its processes. The Data is published in the Product Reliability report found at http://www.maxim-ic.com/. Current monitor data for the TSMC 0.6" Process results in a FIT Rate of 0.5 @25C and 8.57@55C (0.8eV, 60% UCL).

The industry standard 85°C/85%RH or HAST testing is monitored per device process once a quarter.

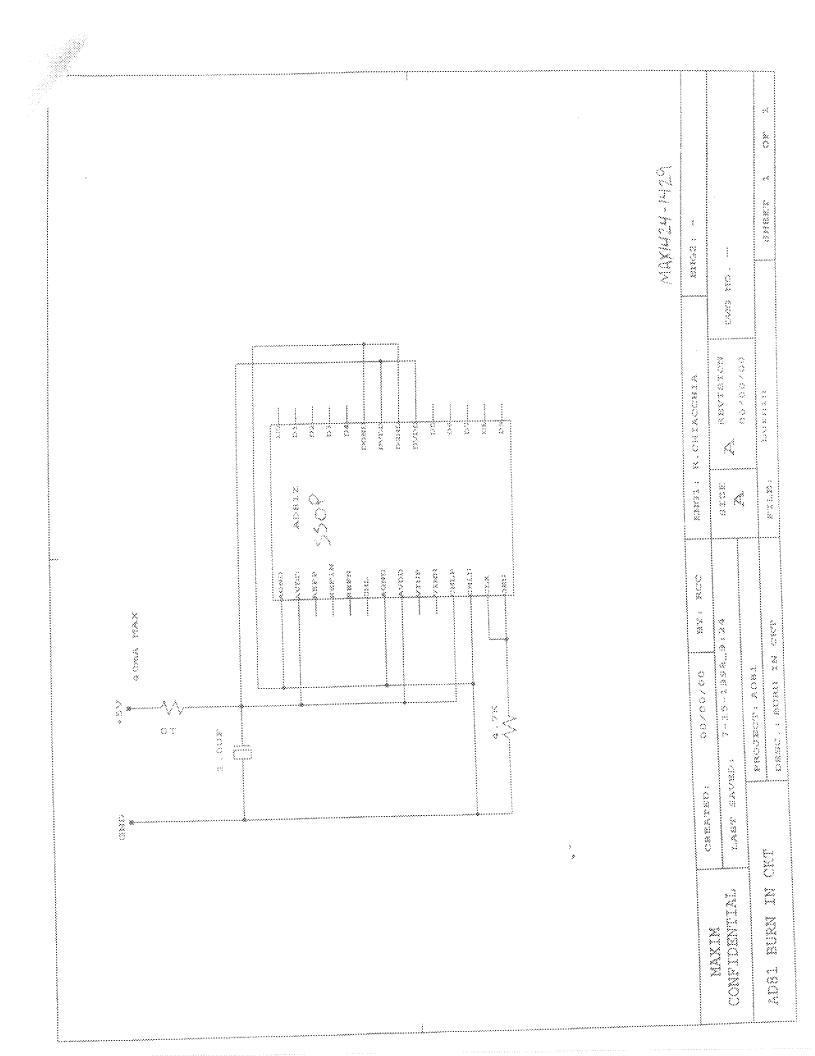

C. E.S.D. and Latch-Up Testing

The AD81 die type has been found to have all pins able to withstand a transient pulse of  $\pm 500$ V, per JESD22-A114-D. Latch-Up testing has shown that this device withstands a current of  $\pm 250$ mA.

B. Moisture Resistance Tests

### Table 1 Reliability Evaluation Test Results

### MAX1426CAI

| TEST ITEM            | TEST CONDITION                                          | FAILURE<br>IDENTIFICATION        | PACKAGE | SAMPLE<br>SIZE | NUMBER OF<br>FAILURES |

|----------------------|---------------------------------------------------------|----------------------------------|---------|----------------|-----------------------|

| Static Life Test     | : (Note 1)                                              |                                  |         |                |                       |

|                      | Ta = 135°C<br>Biased<br>Time = 192 hrs.                 | DC Parameters & functionality    |         | 50             | 0                     |

| Moisture Testir      | ng (Note 2)                                             |                                  |         |                |                       |

| Pressure Pot         | Ta = 121°C<br>P = 15 psi.<br>RH= 100%<br>Time = 168hrs. | DC Parameters<br>& functionality | SSOP    | 77             | 0                     |

| 85/85                | Ta = 85°C<br>RH = 85%<br>Biased<br>Time = 1000hrs.      | DC Parameters<br>& functionality |         | 77             | 0                     |

| Mechanical Str       | ess (Note 2)                                            |                                  |         |                |                       |

| Temperature<br>Cycle | -65°C/150°C<br>1000 Cycles<br>Method 1010               | DC Parameters<br>& functionality |         | 77             | 0                     |

Note 1: Life Test Data may represent plastic DIP qualification lots. Note 2: Generic Package/Process data