# **Ultralow Distortion**, 600 MHz Buffer

# AD9620\*

#### **FEATURES**

Excellent Gain Accuracy: 0.994 V/V

Wide Bandwidth: 600 MHz Slew Rate: 2200 V/µs **Ultralow Distortion:** -73 dBc @ 20 MHz -91 dBc @ 2.3 MHz

Fast Settling Time: 8 ns to 0.02%

Low Noise: 2.0 nV/√Hz

## APPLICATIONS

IF/Communications

Impedance/Transformations

Drives Flash ADCs Line Driving

## GENERAL DESCRIPTION

The AD9620 is a monolithic, unity gain buffer amplifier that sets new standards in gain accuracy wide bandwidth and low distortion. Its large signal bandwidth, ultralow distortion over frequency, and drive capabilities of the AD9620 make this buffer an ideal driver for flash ADCs. Other applications which require increased current drive at unity voltage gain, such as cable driving, also benefit from the AD9620's performance.

In addition to innovative (patent pending) feedback architecture, special packaging techniques improve dynamic performance by minimizing the reactive effects associated with standard packages. The result is -73 dBc harmonic suppression at 20 MHz, and -91 dBc at 2.3 MHz. The AD9620 also outperforms other amplifiers, including its predecessor AD9630, in terms of smallsignal pulse response and dc linearity. These features make the AD9620 the premier driver for high speed, high resolution ADCs.

\*Patent(s) Pending.

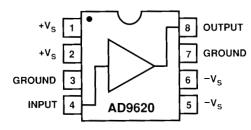

### DIP CONFIGURATION

NC = NO CONNECT

Available in side brazed ceramic DIP packages, the "A" suffix unit is guaranteed for 40°C to +85°C operating temperatures; the "S" suffix device is guaranteed from  $-55^{\circ}$ C to  $+125^{\circ}$ C.

AD9620 die are de tested at  $+25^{\circ}$ C

714/641-9391

# AD9620—SPECIFICATIONS

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>     |                                                             |

|-------------------------------------------|-------------------------------------------------------------|

| Supply Voltages $(\pm V_S) \dots \pm 7 V$ | Storage Temperature                                         |

| Input Voltage Range $\pm V_S$             |                                                             |

| Continuous Output Current <sup>2</sup>    | AD9620SD65°C to +150°C                                      |

| Operating Temperature Ranges              | Junction Temperature <sup>3</sup> +175°C                    |

| AD9620AD                                  | Lead Soldering Temperature (10 seconds) <sup>4</sup> +300°C |

| AD9620SD                                  |                                                             |

# DC ELECTRICAL CHARACTERISTICS (unless otherwise noted, $\pm V_S = \pm 5$ V; $R_{IN} = 50 \Omega$ , $R_{LOAD} = 100 \Omega$ )

|                               |                                                    |                               | Test           | est AD9620AD |                   |               | AD9620SD |                 |        |         |  |

|-------------------------------|----------------------------------------------------|-------------------------------|----------------|--------------|-------------------|---------------|----------|-----------------|--------|---------|--|

| Parameter                     | Conditions                                         | Temp                          | Level          |              | Typ               | Max           | Min      | Typ             | Max    | Units   |  |

| DC SPECIFICATIONS             |                                                    |                               |                |              |                   |               |          |                 |        |         |  |

| Output Offset Voltage         |                                                    | +25°C                         | I              | -8           | ±2                | +8            | -8       | $\pm 2$         | +8     | mV      |  |

| Offset Voltage TC             |                                                    | Full                          | IV             | -25          | ±5                | +25           | -25      | ±5              | +25    | μV/°C   |  |

| Input Bias Chrrent            |                                                    | +25°C                         | I              | -35          | ±6                | +35           | -35      | ±6              | +35    | μA      |  |

| Bias Current TC               |                                                    | Full                          | ĪV             | -150         |                   | +150          | -150     | ±50             | +150   | nA/°C   |  |

| Input Resistance              | _                                                  | +25°C to T <sub>max</sub>     | VI             | 400          | 800               |               | 400      | 800             |        | kΩ      |  |

| Input Resistance              |                                                    | T <sub>min</sub>              | VI             | 190          | 000               |               | 190      | 000             |        | kΩ      |  |

| Input Capacitance             |                                                    | +25°C                         | v              | 27 0         | 1.0               |               |          | 1.0             |        | pF      |  |

| Gain                          | $V_{\text{out}} = \sum_{i} V_{i} = \sum_{i} V_{i}$ | Full                          | VI             | 0.989        |                   |               | 0.989    |                 |        | V/V     |  |

| Output Voltage Range          | $V_{OUT} = 2 V_{p-p}$                              | Full                          | VĪ             | +2.8         | ••••              | -2.8          | +2.8     | ••••            | -2.8   | v       |  |

| Output Current (50  Q. Load)  |                                                    | Full )                        | ki /           | 40           | _                 |               | 40       |                 | 2.0    | mA      |  |

| Output Impedance              | ANDC /                                             | +25°C                         | $\sqrt{V}$     | "            | 0/4               |               |          | 0.4             |        | Ω       |  |

| Power Supply Rejection Ratio  | $\Delta V_{S} = \pm 5\%$                           | Full                          | $\dot{V}_{VI}$ | 52           | #6 T              |               | J2/_     | <u>60</u>       |        | dB      |  |

| DC Nonlinearity               | ±2 V Full Scale                                    | +25°C / /                     | $\sqrt{v}$     | 32           | 0.005             | _             |          | <b>10</b> .005  |        | %<br>%  |  |

|                               | =2 v I un ocuic                                    |                               | <u>'</u> [     |              | 1 -               | $\overline{}$ |          | 1:00            | $\sim$ |         |  |

| FREQUENCY DOMAIN              |                                                    | <u> </u>                      |                | <b>\</b>     | / /               | $\sim$        |          | / /             | /      |         |  |

| Bandwidth $(-3 \text{ dB})$   |                                                    |                               | ;;             | IJ. /        |                   | _             | /        |                 | - /    | <u></u> |  |

| Small Signal                  | $V_{OUT} = \leq 0.7 \text{ V p-p}$                 | $T_{\min}$ to $+25^{\circ}$ C | II             | 320 4        | <del>-6</del> 00_ | _ ``          | 320 /    | 690             | - / ,  | MHz     |  |

| Small Signal                  | $V_{OUT} = \leq 0.7 \text{ V p-p}$                 | T <sub>max</sub>              | II             | 260          |                   | $\sim$        | 260      | $\int_{\Omega}$ |        | MHz     |  |

| Large Signal                  | $V_{OUT} = 4 V p-p$                                | $T_{\min}$ to +25°C           | IV             | 60           | 80                |               | 60 ~     | <b>-</b> 80     | / 4    | MHz     |  |

| Large Signal                  | $V_{OUT} = 4 \text{ V p-p}$                        | T <sub>max</sub>              | IV             | 45           | 0.0               |               | 45       | 0.0             | ·      | MHz     |  |

| Amplitude of Peaking          | ≤150 MHz                                           | $T_{\min}$ to +25°C           | II             |              | 0.8               | 1.5           |          | 0.8             | 1.5    | dB      |  |

| Amplitude of Peaking          | ≤150 MHz                                           | T <sub>max</sub>              | II             |              | 1.5               | 2.2           |          | 1.5             | 2.2    | dB      |  |

| Amplitude of Rolloff          | ≤150 MHz                                           | Full                          | II             |              | 0                 | 0.3           |          | 0               | 0.3    | dB      |  |

| Group Delay                   | DC to 150 MHz                                      | +25°C                         | V              |              | 0.75              |               |          | 0.75            |        | ns      |  |

| Phase Nonlinearity            | DC to 150 MHz                                      | +25°C                         | V              |              | 1.4               |               |          | 1.4             |        | Degrees |  |

| 2nd Harmonic Distortion       | 2 V p-p; 2.3 MHz                                   | +25°C to T <sub>max</sub>     | IV             |              | -91               | -82           |          | <b>−91</b>      | -82    | dBc     |  |

|                               | 2 V p-p; 2.3 MHz                                   | $T_{\min}$                    | IV             |              | -81               | -73           |          | -81             | -73    | dBc     |  |

|                               | 2 V p-p; 20 MHz                                    | Full                          | IV             |              | -71               | -63           |          | -71             | -63    | dBc     |  |

|                               | 2 V p–p; 60 MHz                                    | +25                           | I              |              | -69               | -60           |          | -69             | -60    | dBc     |  |

|                               | 2 V p-p; 60 MHz                                    | $T_{\min}$ and $T_{\max}$     | V              |              | -62               |               |          | -62             |        | dBc     |  |

| 3rd Harmonic Distortion       | 2 V p-p; 2.3 MHz                                   | Full                          | IV             |              | 94                | -86           |          | -94             | -86    | dBc     |  |

|                               | 2 V p-p; 20 MHz                                    | Full                          | IV             |              | -81               | -71           |          | -81             | -71    | dBc     |  |

|                               | 2 V p-p; 60 MHz                                    | +25°C                         | I              |              | -60               | -52           |          | -60             | -52    | dBc     |  |

| Spectral Input Noise Voltage  | 10 MHz                                             | +25°C                         | V              |              | 2.0               |               |          | 2.0             |        | nV/√Hz  |  |

| Average Equivalent Integrated |                                                    |                               |                |              |                   |               |          |                 |        |         |  |

| Output Noise Voltage          | 0.1 to 200 MHz                                     | +25°C                         | V              |              | 28                |               |          | 28              |        | μV      |  |

| TIME DOMAIN                   |                                                    |                               |                |              |                   |               |          |                 |        |         |  |

| Slew Rate                     | $V_{OUT} = 4 \text{ V Step}$                       | +25°C                         | IV             | 1500         | 2200              |               | 1500     | 2200            |        | V/µs    |  |

| Rise/Fall Time                | $V_{OUT} = 1 \text{ V Step}$                       | $T_{\min}$ to +25°C           | IV             |              | 0.8               | 1.2           |          | 0.8             | 1.2    | ns      |  |

|                               | $V_{OUT} = 1 \text{ V Step}$                       | T <sub>max</sub>              | IV             |              | 1.1               | 1.5           |          | 1.1             | 1.5    | ns      |  |

|                               | $V_{OUT} = 4 \text{ V Step}$                       | $T_{\min}^{\max}$ to +25°C    | IV             |              | 1.7               | 2.5           |          | 1.7             | 2.5    | ns      |  |

|                               | $V_{OUT} = 4 \text{ V Step}$                       | T <sub>max</sub>              | IV             |              | 2.3               | 3.4           |          | 2.3             | 3.4    | ns      |  |

| Overshoot                     | $V_{OUT} = 2 \text{ V Step}$                       | Full                          | IV             |              | 3                 | 12            |          | 3               | 12     | %       |  |

| Settling Time                 | 001                                                |                               |                |              |                   |               |          |                 |        |         |  |

| To 0.1%                       | $V_{OUT} = 2 \text{ V Step}$                       | Full                          | IV             |              | 6                 | 10            |          | 6               | 10     | ns      |  |

| To 0.02%                      | $V_{OUT} = 2 \text{ V Step}$                       | Full                          | IV             |              | 8                 | 16            |          | 8               | 16     | ns      |  |

| Differential Gain             | 4.4 MHz                                            | +25°C                         | $\mathbf{v}$   |              | 0.02              |               |          | 0.02            |        | %       |  |

| Differential Phase            | 4.4 MHz                                            | +25°C                         | v              |              | 0.02              |               |          | 0.02            |        | Degrees |  |

|                               | 1                                                  |                               | L .            |              |                   |               | L        | <b>-</b>        |        | 1 8 0.  |  |

-2-

|                     |               |      | Test  | AD9620AD |     |     | AD9620SD |     |     |       |

|---------------------|---------------|------|-------|----------|-----|-----|----------|-----|-----|-------|

| Parameter           | Conditions    | Temp | Level | Min      | Typ | Max | Min      | Тур | Max | Units |

| POWER SUPPLY REQUIF | REMENTS       |      |       |          |     |     |          |     |     |       |

| Quiescent Current   |               |      |       |          |     |     |          |     |     |       |

| $+I_S$              | $+V_S = +5 V$ | Full | VI    |          | 40  | 48  |          | 40  | 48  | mA    |

| $-I_S$              | $-V_S = -5 V$ | Full | VI    |          | 40  | 48  |          | 40  | 48  | mA    |

#### NOTES

Specifications subject to change without notice.

### THEORY OF OPERATION

The AD9620 is a wide bandwidth, unity gain buffer amplifier that utilizes innovative (patent pending) voltage feedback architecture. Large loop gain and high slew rate significantly improve dc linearity and large signal bandwidth when compared with that achieved with more conventional designs.

Its large-signal bandwidth compares favorably with competitive devices of open-loop design without their limitations. Open-loop devices often sacrifice dc linearity and introduce frequency distortion when driving low load impedances; the AD9620 does not. Its design yields low distortion products that are relatively constant for any resistive load greater than 50 ohms.

The AD9620 will satisfy any high performance analog signal processing application requiring isolation or current boosting between the signal source and load. Its combination of high input resistance and low capacitance, dc precision, and exceptional dynamic characteristics sets a new standard in performance that has no equal.

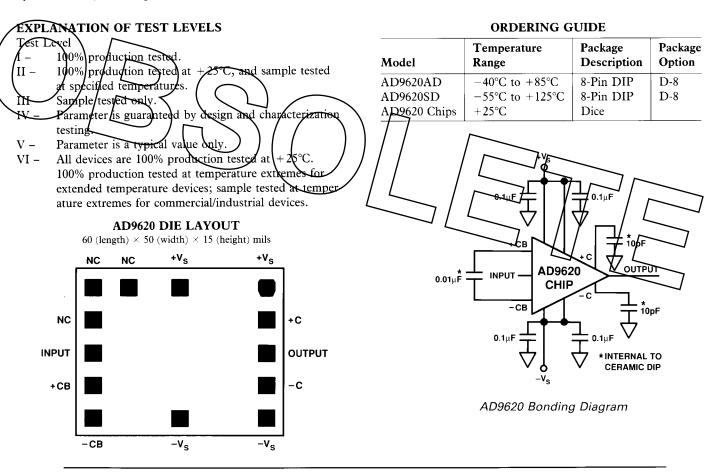

Excessive peaking may occur when using the AD9620 to directly drive loads with more than 3 pF of capacitance. To prevent this, a small value of resistance ( $R_s$ ) should be placed in series with

REV. A -3-

Absolute maximum ratings are limiting values to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability is not necessarily implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.

<sup>&</sup>lt;sup>2</sup>Output is short-circuit protected to ground, but not to supplies. Continuous short circuit to ground may affect device reliability.

<sup>&</sup>lt;sup>3</sup>Typical side-brazed thermal impedances (part soldered onto board):  $\theta_{JA} = 110^{\circ}\text{C/W}; \;\; \theta_{JC} = 20^{\circ}\text{C/W}.$

External capacitor of AD9620 is attached with 62 Sn/36 Pb/2 Ag solder. Board attachment temperatures should be reviewed to insure the capacitor does not reflow during board mounting.

## AD9620

the buffer output. The following figure shows various values of  $R_S$  as a function of capacitive load.

Figure 2. Frequency Response vs.  $C_L$  with Recommended  $R_S$

Capacitive loads up to 50 pF can be driven with minimal degradation in pulse response with  $R_{\rm S}$  equal to approximately 12 ohms.

The output stage has short-circuit protection to ground, but average load currents greater than 70 mA may reduce device reliability. The output driver will shut down if more than approximately 130 mA of instantaneous sink or source current is flowing. This ensures that output clipping will not occur during high slew conditions when driving capacitive loads.

### LAYOUT CONSIDERATIONS

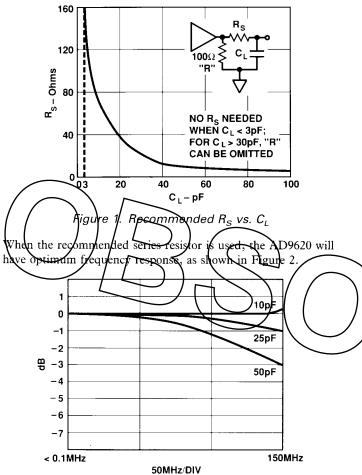

Although the AD9620AD/SD is housed in a specially designed package with built-in decoupling capacitors, the layout of the circuit containing the buffer requires careful attention. Without it, dynamic performance may be less than desired.

Optimum performance depends on connecting all of the supply pins and ground pins of the AD9620. If they are not connected, the inherent benefits of the buffer's special package will not be realized.

A two-ounce copper ground plane on the component side of the board is recommended. It should cover as much of the board as possible with appropriate openings for supply decoupling capacitors and for load and source resistors. Settling time and ac performance will be optimized with surface mount  $0.1~\mu F$  supply decoupling capacitors. These should be located within 50 mils of their corresponding device pins, with the opposite side of the capacitor soldered directly to the ground plane.

If surface mount capacitors cannot be used, radial/lead ceramic capacitors with lead lengths less than 30 mils are recommended. Low frequency power supply decoupling is also necessary and can be accomplished with 4.7  $\mu$ F tantalum capacitors mounted within 0.5 inch of the voltage supply pins. The interaction of the series inductance of the tantalum capacitor with the 0.1  $\mu$ F decoupling capacitor and the supply leads may cause high frequency oscillations at the output. These can be eliminated with a ferrite bead mounted between the tantalum and ceramic capacitors.

Connections to the AD9620 should be as short as possible. If either the source circuit or the driven circuit is further than one inch from the buffer, the printed circuit board (PCB) line impedances should be matched to the buffer input and output resistances. Basic microstrip techniques should be observed. The input termination resistor  $(R_{\rm IN})$  and  $R_{\rm S}$  should both be connected as close to the AD9620 as possible.

Its performance characteristics allow the AD9620 to drive terminated cables directly without the use of an output termination resistor for many applications. When used, termination resistors ( $R_{\rm S}$  and  $R_{\rm IN}$ ) can be either carbon composition or microwave types. When matching characteristic impedances, precision microwave resistors with tolerance of 1% or better are recommended.

The AD9620 should be soldered directly to the PCB with minimum vertical clearance. The use of zero-insertion sockets is discouraged because of their high pin reactances. Use of this type socket will result in peaking and possibly induce oscillation. If sockets must be used for test or prototyping purposes, individual pin sockets such as the AMP 6-330808 series are recommended.

4- REV. A

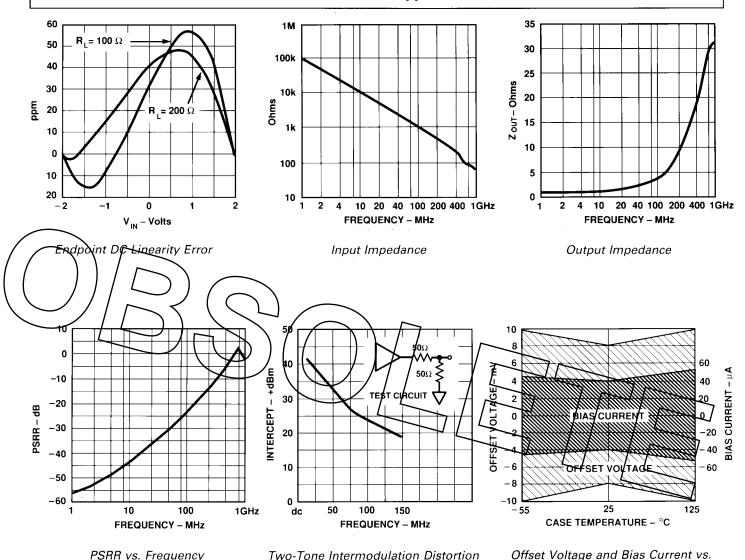

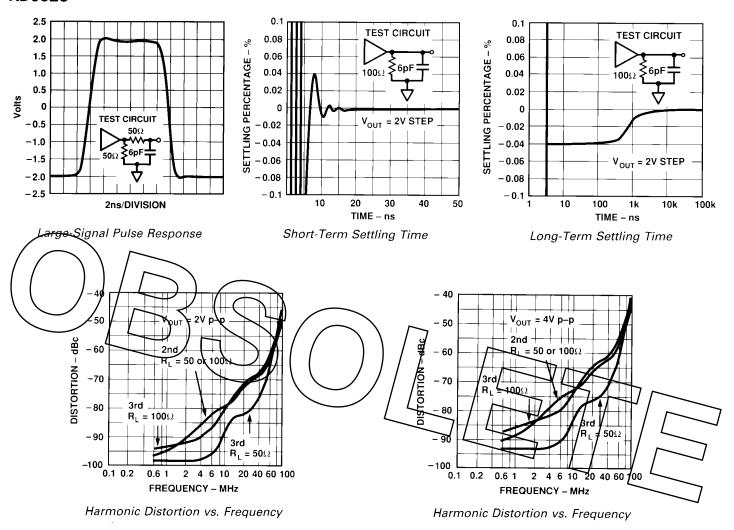

# Typical Performance Curves—AD9620

Temperature (Worst Case)

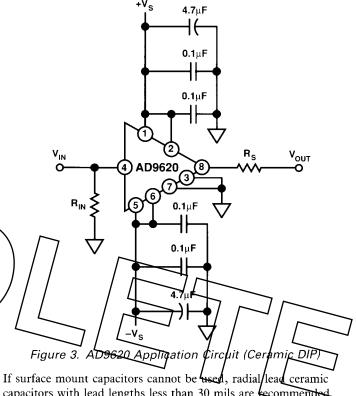

0.8 2 0.6  $R_L = 200\Omega$ 0.4  $V_{IN} = 700 \text{mV}$ MAGNITUDE - dB PHASE - Degrees MAGNITUDE - dB  $R_L = 50\Omega$ 0.2 Volts  $R_L = 100\Omega$ -2 0 PHASE -3 -0.2 $V_{IN} = 700 \text{mV}$ -5 -135 -0.4-180 -6 -0.6-6 -7 -0.8120 200 300 400 80 160 200 2ns/DIVISION FREQUENCY - MHz FREQUENCY - MHz

Two-Tone Intermodulation Distortion

Frequency Response vs.  $R_{LOAD}$ Forward Gain and Phase Small-Signal Pulse Response

PSRR vs. Frequency

# AD9620

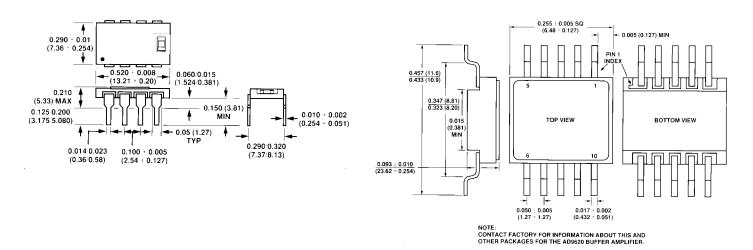

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

### Suffixes AD and SD

-6-