# AD9889B to ADV7513 Changeover Guide

# **SECTION 1: INTRODUCTION**

The Analog Devices AD9889B HDMI Transmitter has been successfully employed for over 5 years now, but now we recommend to those considering this to upgrade to the ADV7513. The ADV7513 is the equal or better in every metric of the AD9889B. Listed below are a few of the improvements that the ADV7513 offers to the HDMI Tx designer:

- Internal HDCP keys (similar to AD9389B)

- Integrated CEC with 3 message buffer

- HDMI v1.4a features supported

- o 3D video

- o Advanced Colorimetry

- xYCC601

- Adobe RGB

- Adobe YCC601

- o High bit-rate (HBR) audio

- Improved PLL for elimination of frequency 'gear' hopping in automatic mode.

- Expanded lower temperature range -25C to +85C

The following will need to be considered when converting from the AD9889B to the ADV7513:

- General board layout such as video data, audio data and TMDS lines are very similar

- Not pin-for-pin drop in mode compatibility

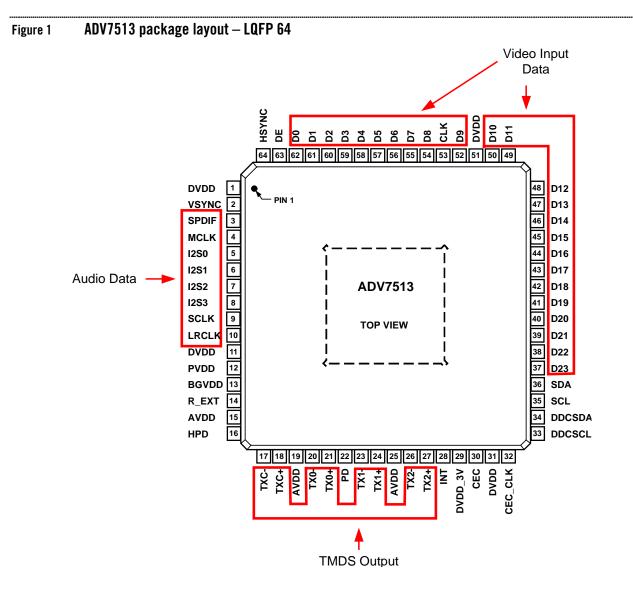

- ADV7513 offered in 64-lead LQFP package (12mm x 12mm outer pin dimension)

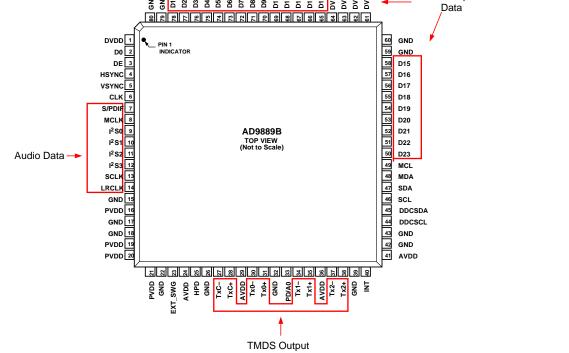

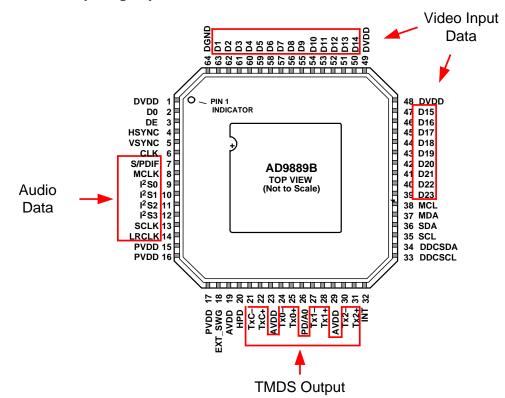

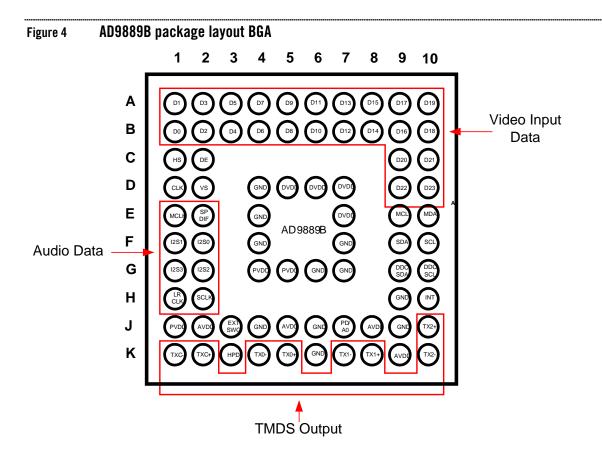

- AD9889B offered in 3 packages: 80-lead LQFP (16mm x 16mm), 64-lead LFCSP (9mm x 9mm) and a 76-ball BGA (6mm x 6mm).

- Use of CEC requires a clock source typically a 12MHz crystal oscillator

- 3.3V supply required for internal memory as well as for CEC support

- No EEPROM required for HDCP keys; no MDA/MCL lines

- Ground on EPAD below package

- Lower power consumption: @1080p60, AD9889B = 504mW (max); ADV7513 = 326mW (max)

- The software driver is different for the ADV7513. However most calls will be similar or the same

# **1.1** Similar board layout

The data-bus input orientation as well as the TMDS output of the ADV7513 are generally compatible with those of the AD9889B. To illustrate this, the pin-outs for all packages are shown below. The pin-out for the ADV7513 is in  $\blacktriangleright$  Figure 1; pin-out for the AD9889B (LQFP) is in  $\blacktriangleright$  Figure 2; pin-out for the AD9889B (LFCSP) is in  $\triangleright$  Figure 3; pin-out for the AD9889B (BGA) is in  $\triangleright$  Figure 4.

Figure 2 AD9889B package layout LQFP

Video Input

Figure 3 AD9889B package layout LFCSP

## **New Features:**

ADV7513 has the following features that were not included in the AD9889B:

- CEC

- 3D

- Packet update Pre-load

- HPD bypass

### 1.2.1 **CEC – Consumer Electronics Control**

The ADV7513 has a Consumer Electronic Control (<u>CEC</u>) receiver/transmitter function which captures and buffers three (3) command messages and passes them on to the host, reducing the real-time monitoring required by a host uP.

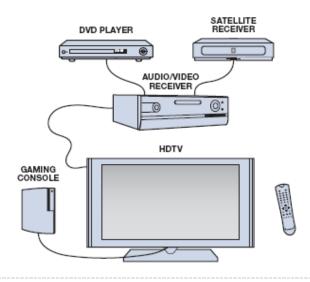

CEC is a single-wire, bidirectional interface intended to facilitate the control of any device on an HDMI network, as typified in  $\blacktriangleright$  Figure 5, with the remote control unit or on-device control buttons of any other device connected to the network. Defined as an optional feature in the HDMI specification, it is based on the AV Link function defined in the European SCART (Syndicat des Constructeurs d'Appareils Radiorécepteurs et Téléviseurs) specification.  $\blacktriangleright$  Table 1 describes some typical end-user CEC features.

#### Figure 5 Typical All-HDMI Home Theatre

#### Table 1 Some useful "End-User" CEC Features:

| Feature Description |                                                                                                                              |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| One-Touch Play      | Pushing the "play" button commands a source to play and become the active video source for the TV.                           |  |

| Stand-By            | Pushing the "power down" button of any active device commands all devices on the HDMI network to shut down.                  |  |

| One-Touch Record    | Pushing the "record" button commands a recording device to power up<br>and record the content currently displayed on the TV. |  |

Many of these end-user features require sending multiple messages over the CEC bus such as "Active Source," and "Routing Change," which support the CEC feature "Routing Control." This feature allows a device to play and become the active source by switching the TV's source input. If the TV is displaying another source at the time this command is used, it may place the other source into "stand-by" mode, depending on the implementation.

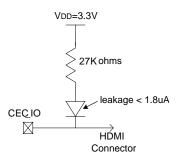

Use of the CEC feature in the ADV7513 only requires 3 components: an external CMOS clock (from 3MHz – 100MHz – default is 12MHz), a low-leakage diode and a 27K ohm resistor pulled up to 3.3V.

#### Figure 6 CEC Connection to HDMI Connector

CEC programming registers and message storage are located in a separate map from the rest of the ADV7513. The address for this map is programmable (from the 'Main' map register 0xE1). Default map

address is 0x78. Registers 0x92 and 0x93 contain the interrupt enables and interrupt bits for the CEC wake-up opcodes. Registers 0x95 and 0x97 contain the interrupt enables and interrupt bits for CEC operation. The CEC Power Down bit is located in register 0xE2[0] of the 'Main' map.

### 1.2.2 **3D Supported Formats**

The ADV7513 has added 3D video support as defined in HDMI v 1.4a. If an HDMI source (TX) has 3D format capability, it must support at least one of the formats in Table 8-15 of the HDMI 1.4a specification. These primary 3D formats are shown in ► Table 2 as well as a number of secondary formats which are additionally supported. The ADV7513 does not detect the VIC for 3D formats, but the VIC in the AVI InfoFrame and the Vendor Specific InfoFrame must be setup. The VIC must be programmed using the manual pixel repeat mode by setting register 0x3B[6:5] to 0b10. The VIC should be programmed in register bits 0x3C[5:0]. A list of VICs can be found in the CEA861 document.

The Pixel repeat value should be set in register 0x3B[2:1] and register 0x3B[4:3]. This will be 0 for most formats; however, depending on the audio and video formats used, sometimes pixel repeat must be used to increase the bandwidth available for audio. Refer to the ADV7513 Programming Guide for further information.

| HDMI 1.4a Primary 3D Mode Support |               |                     |                |  |  |  |  |

|-----------------------------------|---------------|---------------------|----------------|--|--|--|--|

| Format (VIC)                      | Frame Packing | Side-by-Side (Half) | Top-and-Bottom |  |  |  |  |

| 720p 60 (4)                       | No            | Yes                 | Yes            |  |  |  |  |

| 720p 50 (19)                      | No            | Yes                 | Yes            |  |  |  |  |

| 720p 24 (60)                      | No            | Yes                 | Yes            |  |  |  |  |

| 720p 30 (62)                      | No            | Yes                 | Yes            |  |  |  |  |

| 1080i 60 (5)                      | No            | Yes                 | Yes            |  |  |  |  |

| 1080i 50 (20)                     | No            | Yes                 | Yes            |  |  |  |  |

| 1080p 24 (32)                     | No            | Yes                 | Yes            |  |  |  |  |

| 1080p 30 (34)                     | No            | Yes                 | Yes            |  |  |  |  |

| 1080p 60 (16)                     | No            | No                  | No             |  |  |  |  |

| 1080p 50 (31)                     | No            | No                  | No             |  |  |  |  |

#### Table 2**3D Format Support**

= Primary 3D Format

= Secondary 3D Format

# 1.2.3 Packet Update and Coefficient Pre-loading

#### 1.2.3.1 Packet Update

The AD9889B supported packets for:

| <u>Packet</u>  | <u>Update bit</u> |

|----------------|-------------------|

| AVI InfoFrame  | Register 0x4A[6]  |

| MPEG Infoframe | Register 0x3F[7]  |

| GMP Packet     | Register 0xBF[7]  |

| Audio InfoFrame | Register 0x4A[5] |

|-----------------|------------------|

| GC Packet       | Register 0x4A[4] |

| SPD Packet      | Register 0x1F[7] |

| ACP Packet      | Register 0x5F[7] |

| ISRC1 Packet    | Register 0x7F[7] |

| ISRC2 Packet    | Register 0x9F[7] |

| Spare Packet 1  | Register 0xDF[7] |

| Spare Packet 2  | Register 0xFF[7] |

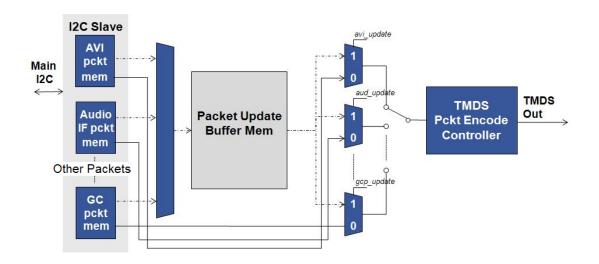

It was possible, however for these packets to be sent when only partially updated. This might have happened if insufficient time was available to update the packet before the blanking periods in which they are sent. To address this issue, the ADV7513 has incorporated a packet update feature which insures that the present contents of each packet continue to be sent until the update is complete. At that time, then the complete, updated contents are transmitted. Because there is only 1 packet update buffer (see > Figure 7 below), only 1 packet may be updated at a time.

To avoid a partial update of the packets, the Packet Update feature should be used. By setting the Packet Update register bit (see column next to Packet list above) to '1', the current values will be stored and sent in the packets. The user should update the values then set the Packet Update register bit to '0' to begin sending the new packets.

When Packet Update is used, there are 3 steps for updating

a) Set Packet Update = 1 to buffer the packet contents

b) Set the new packet contents in I2C memory

c) Set Packet Update = 0 to enable the new packet contents at the next blanking period (Hsync or Vsync)

Updating then occurs during a blanking period which will guarantee complete frames to contain the same packet content.

#### Figure 7 Packet Update Block Diagram

#### 1.2.3.2 Coefficient Pre-loading

The CSC (colorspace converter) can experience a similar issue to the packet update when changing the colorspace conversion coefficients. There are potentially 22 registers that may need to be changed from one colorspace definition to another. In order to prevent colorspace display errors due to incomplete update of the coefficients, an update feature (enabled with register 0x1A[5]) has been incorporated into this circuitry which allows the pre-loading of coefficients without enabling them to the matrix.

When Coefficient Update is used, there are 3 steps for updating

a) Set Coefficient Update = 1 to buffer the CSC Coefficients

b) Set the new CSC Coefficients

c) Set Coefficient Update = 0 to enable the new CSC Coefficients at the next Vsync rising edge

Updating then occurs during a Vsync blanking period which will guarantee complete frames to contain the same colorspace definition.

#### 1.2.4 HPD Bypass

In the AD9889B, most registers were reset and the chip powered down upon loss of the HPD (Hot Plug Detect) signal. The loss of this signal indicates that no monitor is attached to the TX output. When this signal becomes active, the TX initiates a read of the monitor EDID and the driver configures the TX for the highest level of video supported. With the addition of a bypass for this signal, the initial debug and troubleshooting of a design is improved. HPD Bypass is enabled by setting register 0xD6[7:6] (Main map) to 0b11.

# SECTION 2: ADV7513 REGISTER MAP

Main Map

The ADV7513 contains four 256-byte register maps as described in the ADV7513 Programming Guide. The four maps are:

0x72 or 0x7A based upon whether the PD/AD pin (pin 22) is pulled low (0x72) or pulled high (0x7A)

EDID addressprogrammable and controlled in register 0x43, default address is 0x7EPacket Memoryprogrammable and controlled in register 0x45, default address is 0x70.CEC Memoryprogrammable and controlled in register 0xE1, default address is 0x78.

|                   | ADV7513 Main Register Map |                    |                       |                             |                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-------------------|---------------------------|--------------------|-----------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Address<br>(Main) | Туре                      | Bits               | Default<br>Value      | Register Name               | Function                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 0x00              | RO                        | [7:0]              | 00010000              | Chip Revision               | Revision of the chip                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 0x01              |                           |                    | ****0000              |                             |                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 0x02              | R/W                       | [19:0]             | 00000000              | Ν                           | 20 bit N used with CTS to regenerate the audio clock in the receiver.                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0x03              |                           |                    | 00000000              |                             |                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 0x04              | RO                        | [7:4]              | 0000****              | SPDIF Sampling<br>Frequency | SPDIF Sampling Frequency from SPDIF Channel<br>Status.<br>0000 = 44.1 kHz<br>0001 = N/A<br>0010 = 48.0 kHz<br>0011 = 32.0 kHz<br>0100 = N/A<br>0101 = N/A<br>0110 = N/A<br>0111 = N/A<br>1000 = 88.2 kHz<br>1001 = N/A<br>1010 = 96.0 kHz<br>1011 = N/A<br>1100 = 176.4 kHz<br>1110 = 192.0 kHz<br>1111 = N/A |  |  |  |  |  |

| 0x04              |                           |                    | ****0000              |                             | Cycle Time Stamp (CTS) Automatically Generated<br>This 20 bit value is used in the receiver with the N value                                                                                                                                                                                                  |  |  |  |  |  |

| 0x05              | RO                        | [19:0]             | 00000000              | CTS Automatic               | to regenerate an audio clock. For remaining bits see                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 0x06              |                           |                    | 00000000              |                             | 0x05 and 0x06.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 0x07              |                           |                    | ****0000              |                             | Cycle Time Stamp (CTS) Manually Entered<br>This 20 bit value is used in the receiver with the N value                                                                                                                                                                                                         |  |  |  |  |  |

| 0x08              | R/W                       | R/W [19:0] 000     | 0000000               | CTS Manual                  | to regenerate an audio clock. For remaining bits see                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 0x09              |                           |                    | 0000000               |                             | 0x08 and 0x09.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 0x0A              | R/W                       | [7]                | 0*****                | CTS Select                  | CTS Source Select.<br>0 = CTS Automatic<br>1 = CTS Manual                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                   |                           | <mark>[6:4]</mark> | <mark>*000****</mark> | Audio Select                | Audio Select                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

#### Highlighted sections indicate differences from the AD9889B Main Map

|                   | ADV7513 Main Register Map |                    |                       |                                         |                                                                                                                                                                                                                                     |     |     |     |                      |                         |                                                                                                                    |

|-------------------|---------------------------|--------------------|-----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|

| Address<br>(Main) | Туре                      | Bits               | Default<br>Value      | Register Name                           | Function                                                                                                                                                                                                                            |     |     |     |                      |                         |                                                                                                                    |

|                   |                           |                    |                       |                                         | All others invalid<br>000 = I2S<br>001 = SPDIF<br>010 = N/A<br>011 = High Bit Rate (HBR Audio)<br>100 = N/A<br>101 = N/A<br>110 = N/A<br>111 = N/A                                                                                  |     |     |     |                      |                         |                                                                                                                    |

|                   |                           | <mark>[3:2]</mark> | <mark>****00**</mark> | Audio Mode                              | Mode Selection for Audio Select<br>HBR (Audio Select register bits (0x0A[6:4] = 0b011))<br>00 = 4 stream, with BPM encoding<br>01 = 4 stream, no BPM encoding<br>10 = 1 stream, with BPM encoding<br>11 = 1 stream, no BPM encoding |     |     |     |                      |                         |                                                                                                                    |

|                   |                           | [1:0]              | *****01               | MCLK Ratio                              | MCLK Ratio<br>The ratio between the audio sampling frequency and<br>the clock described using N and CTS<br>00 = 128xfs<br>01 = 256xfs<br>10 = 384xfs<br>11 = 512xfs                                                                 |     |     |     |                      |                         |                                                                                                                    |

|                   |                           | [7]                | <mark>0*****</mark>   | SPDIF Enable                            | Enable or Disable SPDIF receiver – <mark>was 0x44[7]</mark><br>0 = disable<br>1 = Enabled                                                                                                                                           |     |     |     |                      |                         |                                                                                                                    |

| 0x0B              | R/W                       | R/W                | R/W                   | R/W                                     | R/W                                                                                                                                                                                                                                 | R/W | R/W | [6] | *0*****              | Audio Clock<br>Polarity | SPDIF MCLK, I2S SCLK Polarity<br>Indicates edge where input data is latched<br>0 = rising edge<br>1 = falling edge |

|                   |                           |                    |                       |                                         |                                                                                                                                                                                                                                     |     |     | [5] | <mark>**0****</mark> | MCLK Enable             | MCLK Enable<br>0 = MCLK internally generated<br>1 = MCLK is available                                              |

|                   |                           | [4:1]              | ***0111*              | Fixed                                   | Must be set to Default Value                                                                                                                                                                                                        |     |     |     |                      |                         |                                                                                                                    |

| 0x0C              | R/W                       | [7]                | <mark>1*****</mark>   | Audio Sampling<br>Frequency Select      | Select source of audio sampling frequency for pixel<br>repeat and I2S mode 4<br>0 = use sampling frequency from I2S stream<br>1 = use sampling frequency from I2C register                                                          |     |     |     |                      |                         |                                                                                                                    |

|                   |                           | <mark>[6]</mark>   | <mark>*0****</mark>   | <mark>Channel Status</mark><br>Override | Source of channel status bits when using I2S mode 4<br>0 = use channel status bits from I2S stream<br>1 = use channel status bits from I2C registers                                                                                |     |     |     |                      |                         |                                                                                                                    |

|                   |                           | [5]                | **1****               | I2S3 Enable                             | I2S3 enable for the 4 I2S pins.<br>0 = Disabled<br>1 = Enabled                                                                                                                                                                      |     |     |     |                      |                         |                                                                                                                    |

|                   |                           | [4]                | ***1****              | I2S2 Enable                             | I2S2 enable for the 4 I2S pins.                                                                                                                                                                                                     |     |     |     |                      |                         |                                                                                                                    |

|                   | ADV7513 Main Register Map |                  |                      |                                 |                                                                                                                                                                   |  |  |  |  |  |

|-------------------|---------------------------|------------------|----------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Address<br>(Main) | Туре                      | Bits             | Default<br>Value     | Register Name                   | Function                                                                                                                                                          |  |  |  |  |  |

|                   |                           |                  |                      |                                 | 0 = Disabled<br>1 = Enabled                                                                                                                                       |  |  |  |  |  |

|                   |                           | [3]              | ****1***             | I2S1 Enable                     | I2S1 enable for the 4 I2S pins.<br>0 = Disabled<br>1 = Enabled                                                                                                    |  |  |  |  |  |

|                   |                           | [2]              | ****1**              | I2S0 Enable                     | I2S0 enable for the 4 I2S pins.<br>0 = Disabled<br>1 = Enabled                                                                                                    |  |  |  |  |  |

|                   |                           | [1:0]            | *****00              | I2S Format                      | I2S Format<br>00 = Standard I2S mode<br>01 = right justified mode<br>10 = left justified mode<br>11 = AES3 direct mode                                            |  |  |  |  |  |

| 0x0D              | R/W                       | [4:0]            | ***11000             | I2S Bit Width                   | I2S Bit Width<br>For right justified audio only. Default is 24. Not valid<br>for widths greater than 24.                                                          |  |  |  |  |  |

| 0x0E              | DAV                       | [5:3]            | **000***             | Subpacket 0 L<br>Source         | Source of sub packet 0, left channel                                                                                                                              |  |  |  |  |  |

| UXUE              | R/W                       | [2:0]            | ****001              | Subpacket 0 R<br>Source         | Source of sub packet 0, right channel                                                                                                                             |  |  |  |  |  |

| 0x0F              | R/W                       | [5:3]            | **010***             | Subpacket 1 L<br>Source         | Source of sub packet 1, left channel                                                                                                                              |  |  |  |  |  |

| UXUF              | K/ W                      | [2:0]            | *****011             | Subpacket 1 R<br>Source         | Source of sub packet 1, right channel                                                                                                                             |  |  |  |  |  |

| 0x10              | R/W                       | [5:3]            | **100***             | Subpacket 2 L<br>Source         | Source of sub packet 2, left channel                                                                                                                              |  |  |  |  |  |

| 0x10              | K/ W                      | [2:0]            | ****101              | Subpacket 2 R<br>Source         | Source of sub packet 2, right channel                                                                                                                             |  |  |  |  |  |

| 0x11              | R/W                       | [5:3]            | **110***             | Subpacket 3 L<br>Source         | Source of sub packet 3, left channel                                                                                                                              |  |  |  |  |  |

| 0411              | 1\/ VV                    | [2:0]            | ****111              | Subpacket 3 R<br>Source         | Source of sub packet 3, right channel                                                                                                                             |  |  |  |  |  |

|                   |                           | [7]              | <mark>0*****</mark>  | Audio Sample<br>Word (CS bit 1) | Audio Sample Word<br>0 = Audio sample word represents linear PCM samples<br>1 = Audio sample word used for other purposes<br>Consumer Use<br>Should be 0 for HDMI |  |  |  |  |  |

| 0x12              | R/W                       | <mark>[6]</mark> | <mark>*0*****</mark> | Consumer Use<br>(CS bit 0)      | Consumer Use Bit<br>0 = Audio sample word represents linear PCM samples<br>1 = Audio sample word used for other purposes                                          |  |  |  |  |  |

|                   |                           | [5]              | **0****              | Copyright Bit<br>(CS bit 2)     | Copy Right Bit<br>0 = Copyright Protected                                                                                                                         |  |  |  |  |  |

|                   |      |       |                  | ADV7513 Main                                 | Register Map                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------|-------|------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address<br>(Main) | Туре | Bits  | Default<br>Value | Register Name                                | Function                                                                                                                                                                                                                                                                                                                                                                                      |

|                   |      |       |                  |                                              | 1 = Not Copyright Protected                                                                                                                                                                                                                                                                                                                                                                   |

|                   |      | [4:2] | ***000**         | Additional<br>Audio Info (CS<br>bits 5-3)    | Additional information for Channel Status Bits<br>000 = 2 audio channels w/o pre-emphasis<br>001 = 2 audio channels with 50/15uS pre-emphasis<br>010 = Fixed<br>011 = Fixed                                                                                                                                                                                                                   |

|                   |      | [1:0] | *****00          | Audio Clock<br>Accuracy (CS<br>bits 29-28)   | Audio Clock Accuracy<br>00 = level II - normal accuracy +/-1000 X 10-6<br>10 = level III -variable pitch shifted clock<br>01 = level I - high accuracy +/-50 X 10-6<br>11 = Fixed                                                                                                                                                                                                             |

| 0x13              | R/W  | [7:0] | 00000000         | Category Code<br>(CS bits 15-8)              | Channel Status Category Code                                                                                                                                                                                                                                                                                                                                                                  |

|                   |      | [7:4] | 0000****         | Source Number<br>(CS bits 19-16)             | Channel Status Source Number                                                                                                                                                                                                                                                                                                                                                                  |

| 0x14              | R/W  | [3:0] | ****0000         | Word Length<br>(CS bits 35-32)               | Audio Word Length<br>0000 = Not Specified<br>0001 = Not Specified<br>0010 = 16 Bits<br>0011 = 20 Bits<br>0100 = 18 Bits<br>0101 = 22 Bits<br>0110 = No description<br>0111 = No description<br>1000 = 19 Bits<br>1001 = 23 Bits<br>1010 = 20 Bits<br>1010 = 20 Bits<br>1011 = 24 Bits<br>1100 = 17 Bits<br>1101 = 21 Bits<br>1101 = 21 Bits<br>1110 = No description<br>1111 = No description |

| 0x15              | R/W  | [7:4] | 0000****         | I2S Sampling<br>Frequency (CS<br>bits 27-24) | Sampling frequency for I2S audio. This information is<br>used by both the audio Rx and the pixel repetition.<br>0000 = 44.1 kHz<br>0001 = Do not use<br>0010 = 48.0 kHz<br>0011 = 32.0 kHz<br>0100 = Do not use<br>0101 = Do not use<br>0101 = Do not use<br>0110 = Do not use<br>1010 = 88.2 kHz<br>1001 = HBR Audio<br>1010 = 96.0 kHz<br>1011 = Do not use<br>1100 = 176.4 kHz             |

|                   | ADV7513 Main Register Map |                    |                       |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |     |     |     |       |          |             |

|-------------------|---------------------------|--------------------|-----------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-------|----------|-------------|

| Address<br>(Main) | Туре                      | Bits               | Default<br>Value      | Register Name                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |     |     |     |       |          |             |

|                   |                           |                    |                       |                                                      | 1101 = Do not use<br>1110 = 192.0 kHz<br>1111 = Do not use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |     |     |       |          |             |

|                   |                           | <mark>[3:0]</mark> | <mark>****0000</mark> | Input ID                                             | Input Video Format<br>See $\blacktriangleright$ Error! Reference source not found. to $\blacktriangleright$ Error!<br>Reference source not found.<br>0000 = 24 bit RGB 4:4:4 or YCbCr 4:4:4 (separate syncs)<br>0001 = 16, 20, 24 bit YCbCr 4:2:2 (separate syncs)<br>0010 = 16, 20, 24 bit YCbCr 4:2:2 (embedded syncs)<br>0011 = 8, 10, 12 bit YCbCr 4:2:2 (2x pixel clock,<br>separate syncs)<br>0100 = 8, 10, 12 bit YCbCr 4:2:2 (2x pixel clock,<br>embedded syncs)<br>0101 = 12, 15, 16 bit RGB 4:4:4 or YCbCr (DDR with<br>separate syncs) (0xD0[3:2] must be set to 2'b11)<br>0110 = 8,10,12 bit YCbCr 4:2:2 (DDR with separate<br>syncs) (0xD0[3:2] must be set to 2'b11)<br>0111 = 8, 10, 12 bit YCbCr 4:2:2 (DDR separate syncs)<br>(0xD0[3:2] must be set to 2'b11)<br>1000 = 8, 10, 12 bit YCbCr 4:2:2 (DDR embedded<br>syncs) (0xD0[3:2] must be set to 2'b11) |     |     |     |     |       |          |             |

|                   |                           | [7]                | <mark>0*****</mark>   | Output Format                                        | Output Format<br>0 = 4:4:4<br>1 = 4:2:2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |     |     |     |       |          |             |

|                   |                           | <mark>[6]</mark>   | <mark>*0*****</mark>  | Reserved                                             | Must be set to Default Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |     |     |       |          |             |

|                   | R/W                       | [5:4]              | **00****              | Color Depth                                          | Color Depth for Input Video Data.<br>See ► <b>Error! Reference source not found.</b> to ► <b>Error!</b><br><b>Reference source not found.</b><br>00 = invalid<br>10 = 12 bit<br>01 = 10 bit<br>11 = 8 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |     |     |     |       |          |             |

| 0x16              |                           | R/W                | R/W                   | R/W                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W | R/W | R/W | R/W | [3:2] | ****00** | Input Style |

|                   |                           | [1]                | *****0*               | DDR Input Edge                                       | Video data input edge selection. Defines the first half of<br>pixel data clocking edge. Used for DDR Input ID 5 and<br>6 only.<br>0 = falling edge<br>1 = rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |     |     |       |          |             |

|                   |                           | <mark>[0]</mark>   | <mark>******0</mark>  | Output<br>Colorspace for<br><mark>Black Image</mark> | Input Color Space Selection<br>Used for Black Image and Range Clipping<br>0 = RGB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |     |     |       |          |             |

|                   | ADV7513 Main Register Map |                    |                       |                                          |                                                                                                                                                                                                                                                                          |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|-------------------|---------------------------|--------------------|-----------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|-----|---------|------------------------|---------------------------------------------------------------------------------|

| Address<br>(Main) | Туре                      | Bits               | Default<br>Value      | Register Name                            | Function                                                                                                                                                                                                                                                                 |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|                   |                           |                    |                       |                                          | 1 = YCbCr                                                                                                                                                                                                                                                                |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|                   |                           | <mark>[7]</mark>   | <mark>0*****</mark>   | <mark>Fixed</mark>                       | Must be set to Default Value                                                                                                                                                                                                                                             |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|                   |                           | [6]                | *0****                | Vsync Polarity                           | Case 1: Sync Adjustment Register (0x41[1]) = 1<br>0 = high polarity<br>1 = low polarity<br>Case 2: Sync Adjustment Register (0x41[1]) = 0<br>0 = sync polarity pass through<br>1 = sync polarity invert<br>0 = High polarity<br>1 = Low polarity                         |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

| 0x17              | R/W                       | R/W                | R/W                   | R/W                                      | R/W                                                                                                                                                                                                                                                                      | [5]                       | **0**** | Hsync Polarity | Hsync polarity for Embedded Sync Decoder and Sync<br>Adjustment<br>Case 1: Sync Adjustment Register (0x41[1]) = 1<br>0 = high polarity<br>1 = low polarity<br>Case 2: Sync Adjustment Register (0x41[1]) = 0<br>0 = sync polarity pass through<br>1 = sync polarity invert<br>0 = High polarity<br>1 = Low polarity |  |  |  |  |     |         |                        |                                                                                 |

|                   |                           | [4:3]              | <mark>***00***</mark> | Reserved @ 00b                           | Must be set to Default Value                                                                                                                                                                                                                                             |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|                   |                           | [2]                | ****0**               | 4:2:2 to 4:4:4<br>Interpolation<br>Style | 4:2:2 to 4:4:4 Up Conversion Method<br>0 = use zero order interpolation<br>1 = use first order interpolation                                                                                                                                                             |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|                   |                           | [1]                | *****0*               | Aspect Ratio                             | Aspect ratio of input video.<br>0 = 4:3 Aspect Ratio<br>1 = 16:9 Aspect Ratio                                                                                                                                                                                            |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|                   |                           |                    |                       |                                          |                                                                                                                                                                                                                                                                          |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  | [0] | ******0 | DE Generator<br>Enable | Enable DE Generator<br>See registers 0x35 - 0x3A<br>0 = Disabled<br>1 = Enabled |

|                   |                           | [7]                | <mark>0*****</mark>   | CSC Enable                               | Color Space Converter Enable <mark>was 0x3B[0]</mark><br>0 = CSC Disabled<br>1 = CSC Enabled                                                                                                                                                                             |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

| 0x18 R/V          | R/W                       | <mark>[6:5]</mark> | *10*****              | CSC Scaling<br>Factor                    | Color Space Converter Mode – was $0x17[4:3]$<br>Sets the fixed point position of the CSC coefficients.<br>Including the a4, b4, c4, offsets.<br>00 = +/- 1.0, -4096 - 4095<br>01 = +/- 2.0, -8192 - 8190<br>10 = +/- 4.0, -16384 - 16380<br>11 = +/- 4.0, -16384 - 16380 |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

| 0x18              | D /147                    | [13.0]             | ***00110              | A1(CSC)                                  | Color space Converter (CSC) coefficient for equations:                                                                                                                                                                                                                   |                           |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

| 0x19              | R/W                       | R/W                | [12:0]                | 01100010                                 | A1 (CSC)                                                                                                                                                                                                                                                                 | Equation 1: CSC Channel A |         |                |                                                                                                                                                                                                                                                                                                                     |  |  |  |  |     |         |                        |                                                                                 |

|                   | ADV7513 Main Register Map |        |                          |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------------|---------------------------|--------|--------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Address<br>(Main) | Туре                      | Bits   | Default<br>Value         | Register Name                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                   |                           |        |                          |                                    | $Out_{A} = \left[ In_{A} \frac{A1}{4096} + In_{B} \frac{A2}{4096} + In_{C} \frac{A3}{4096} + A4 \right] 2^{CSC\_Mode}$<br>Equation 2: CSC Channel B<br>$Out_{B} = \left[ In_{A} \frac{B1}{4096} + In_{B} \frac{B2}{4096} + In_{C} \frac{B3}{4096} + B4 \right] 2^{CSC\_Mode}$<br>Equation 3: CSC Channel C<br>$Out_{C} = \left[ In_{A} \frac{C1}{4096} + In_{B} \frac{C2}{4096} + In_{C} \frac{C3}{4096} + C4 \right] 2^{CSC\_Mode}$                                                            |  |  |  |  |

| 0x1A              | R/W                       | [5]    | <mark>**0</mark> ****    | <mark>Coefficient</mark><br>Update | There are 2 methods to update the coefficients.<br>Method 1:<br>When Coefficient Update is always 0, the coefficient<br>will be updated directly.<br>Method 2:<br>When Coefficient Update is used, there are 3 steps for<br>updating<br>a) Set Coefficient Update = 1 to buffer the CSC<br>Coefficients<br>b) Set the new CSC Coefficients<br>c) Set Coefficient Updated = 0 to enable the new CSC<br>Coefficients at the next Vsync rising edge<br>0 = Update Complete<br>1 = Allow CSC Update |  |  |  |  |

| 0x1A              | R/W                       | [12:0] | ***00100                 | A2 (CSC)                           | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x1B<br>0x1C      |                           |        | 10101000<br>***00000     |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0x10              | R/W                       | [12:0] | 0000000                  | A3 (CSC)                           | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x1E              |                           |        | ***11100                 |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0x1F              | R/W                       | [12:0] | 10000100                 | · A4 (CSC)                         | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x20              | -                         | [      | ***11100                 | R. (22.2)                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 0x21              | R/W                       | [12:0] | 10111111                 | B1 (CSC)                           | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x22              | D /147                    | [12.0] | ***00100                 |                                    | See description for registers 0x18 and 0x10                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x23              | R/W                       | [12:0] | 10101000                 | B2 (CSC)                           | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x24              | D /147                    | [12:0] | ***11110                 | $B_{2}(CSC)$                       | San description for registers (1)18 and (1)19                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 0x25              | R/W                       |        | 01110000                 | B3 (CSC)                           | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x26              | R/W                       | [12:0] | ***00010                 | B4 (CSC)                           | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x27              | 17/ 11                    | [12.0] | 00011110                 | D1(000)                            | see description for registers on to and on ty                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 0x28              | R/W                       | [12:0] | [12:0] ***00000 C1 (CSC) | C1 (CSC)                           | See description for registers 0x18 and 0x19                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 0x29              |                           | [-=.0] | 0000000                  | (200)                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                   |           |                  |                  | ADV7513 Main                            | Register Map                                                                                                         |                                                                         |

|-------------------|-----------|------------------|------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Address<br>(Main) | Туре      | Bits             | Default<br>Value | Register Name                           | Function                                                                                                             |                                                                         |

| 0x2A              | R/W       | [12:0]           | ***00100         | C2 (CSC)                                | San description for registers 0x18 and 0x10                                                                          |                                                                         |

| 0x2B              | K/ W      | [12:0]           | 10101000         | 02 (030)                                | See description for registers 0x18 and 0x19                                                                          |                                                                         |

| 0x2C              | R/W       | [12:0]           | ***01000         | C3 (CSC)                                | See description for registers 0x18 and 0x19                                                                          |                                                                         |

| 0x2D              | 10, 11    | [12.0]           | 00010010         | (636)                                   | see description for registers ox to and ox to                                                                        |                                                                         |

| 0x2E              | R/W       | [12:0]           | ***11011         | C4 (CSC)                                | See description for registers 0x18 and 0x19                                                                          |                                                                         |

| 0x2F              | 10, 11    | [12.0]           | 10101100         | 01(000)                                 | oce ascription for registers ox to and ox to                                                                         |                                                                         |

| 0x30              |           |                  | 00000000         | Hsync                                   |                                                                                                                      |                                                                         |

| 0x31              | R/W       | [9:0]            | 00*****          | Placement<br>(Embedded Sync<br>Decoder) | Embedded Sync Decoder Hsync Placement (In Pixels)                                                                    |                                                                         |

| 0x31              | DUU       |                  | **000000         | Hsync Duration                          |                                                                                                                      |                                                                         |

| 0x32              | R/W       | [9:0]            | 0000****         | (Embedded Sync<br>Decoder)              | Embedded Sync Decoder Hsync Duration (In Pixels)                                                                     |                                                                         |