## **MAX77720**

# Wide Output-Voltage Range, Dual-Polarity PMIC

# **General Description**

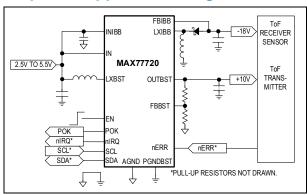

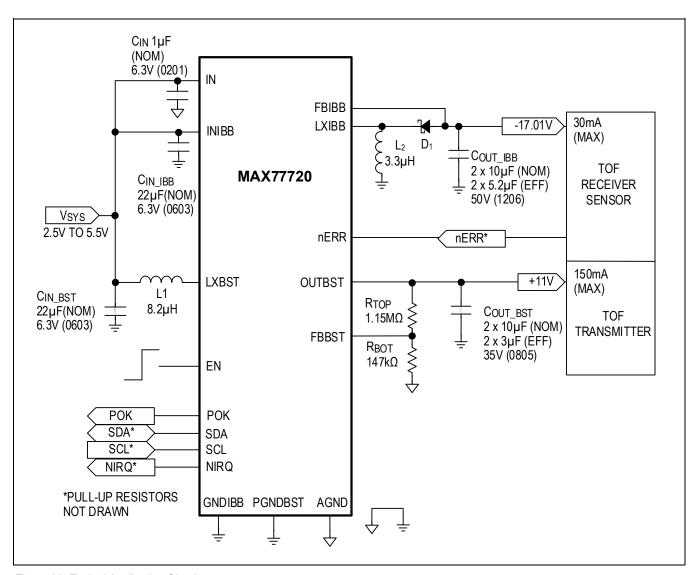

The MAX77720 dual-output DC-DC converter generates two independently regulating positive and negative supply voltages. The positive output delivers up to 4W of power at the output while the negative output delivers up to 4.8W of power. The MAX77720 is ideal for powering time of flight (ToF) imaging sensors and OLED displays in smart internet of things (IoT) devices.

The MAX77720 generates an adjustable negative output down to -24V and a positive output voltage up to +20V. The negative output operates at a fixed 1.5MHz frequency while the positive output operates at a fixed 1MHz frequency to ease noise filtering in sensitive applications and to reduce external component size.

The nERR pin, when connected to an external device's output pin, is used to disable the regulators to signal an external error. This error can be cleared through I<sup>2</sup>C from a host processor to re-enable the regulators. While in the error on state, there is an option for the active discharge to be enabled or disabled (for example, to set the regulator outputs to a high-Z floating).

A bidirectional  $I^2C$  serial interface allows for configuring and checking the status of the devices. Numerous factory-programmable options allow the device to be tailored for many applications, enabling faster time to market.

# **Simplified Application Diagram**

# **Key Applications**

- ToF Sensors

- OLED Displays

- Bipolar Amplifiers

## **Benefits and Features**

- 2.5V to 5.5V Input Voltage Range

- Programmable Output-Voltage Range (Up to +20V and Down to -24V)

- Flexible and Configurable

- o I2C Interface

- Factory OTP Settings Available

- Programmable Turn-On and -Off Delay Between Rails

- 1.2V to 3.6V V<sub>IO</sub>-Compatible

- True Shutdown<sup>™</sup> for Boost

- Programmable Peak Current Limit for Boost (Up to 1A and Down to 0.5A)

- Thermal-Shutdown Protection

- Fault-Condition Flag

- Error Pin for External Sensor Fault Condition

- Controlled Inrush Current During Soft-Start

- -40°C to +125°C Operating Temperature Range

- Small Size

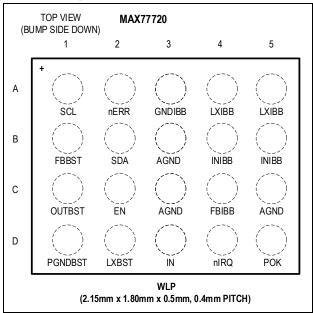

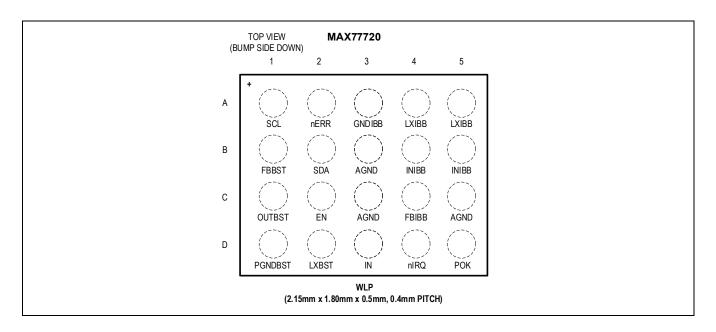

- o 3.86mm<sup>2</sup> Wafer-Level Package (WLP)

- o 20-Bump, 0.4mm-Pitch, 5 x 4 Array

# **Pin Configuration**

True Shutdown is a trademark of Maxim Integrated Products, Inc.

Ordering Information appears at end of data sheet.

Click here to ask an associate for production status of specific part numbers.

### **MAX77720**

# Wide Output-Voltage Range, Dual-Polarity PMIC

# **TABLE OF CONTENTS** Electrical Characteristics......8 Part Number Decoding 20 Shutdown 21 IN Overvoltage Lockout (OVLO) ......27

| Inverting Buck-Boost Functional Modes               | 30 |

|-----------------------------------------------------|----|

| Skip Mode                                           | 30 |

| PWM Mode                                            | 30 |

| Programming the Inverting Buck-Boost Output Voltage | 30 |

| Detailed Description—Boost Converter                | 31 |

| Boost-Converter Functional Modes                    | 31 |

| Skip Mode                                           | 31 |

| PWM Mode                                            | 31 |

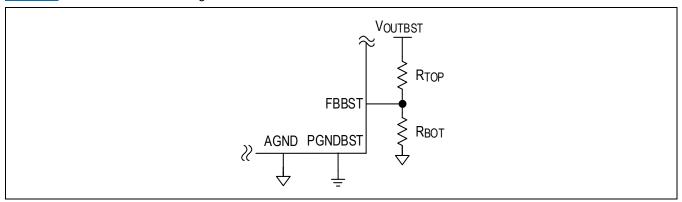

| Configuring the Boost Output Voltage                | 31 |

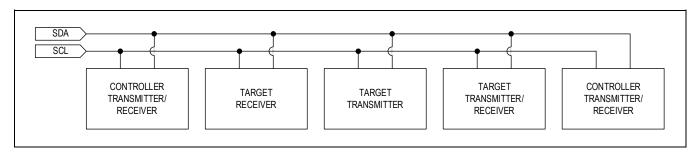

| Detailed Description—Two-Wire Communication         | 32 |

| General Description                                 | 32 |

| System Configuration                                | 32 |

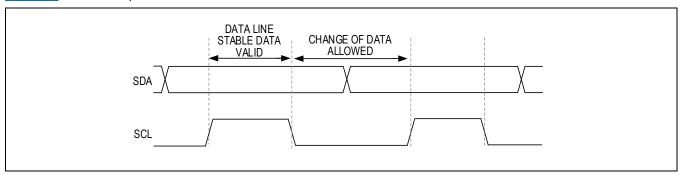

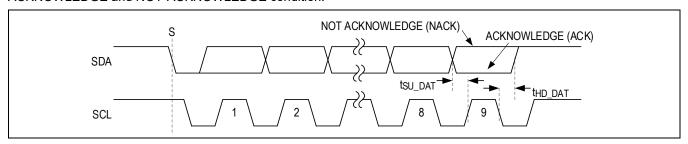

| Bit Transfer                                        | 33 |

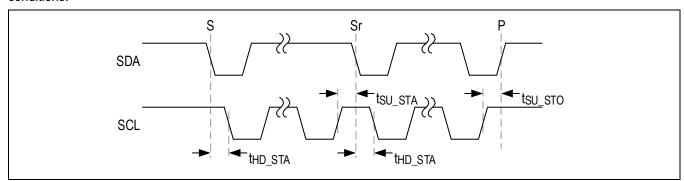

| START and STOP Conditions                           | 33 |

| Acknowledge Bit                                     | 34 |

| Data Order                                          | 34 |

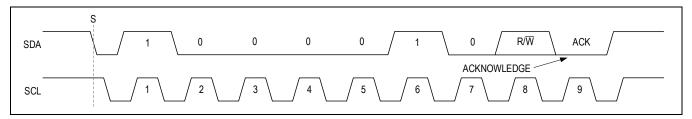

| Target Address                                      | 34 |

| Clock Stretching                                    | 35 |

| General Call Address                                | 35 |

| Communication Speed                                 | 35 |

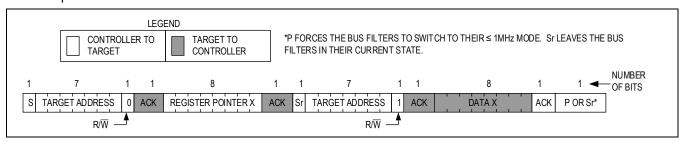

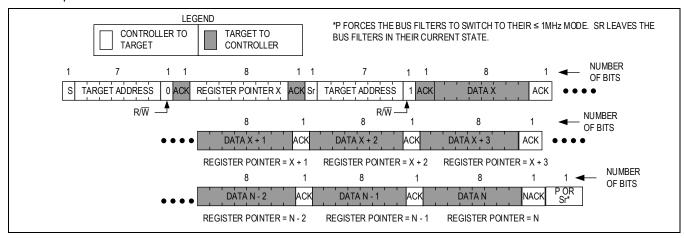

| Communication Protocols                             | 35 |

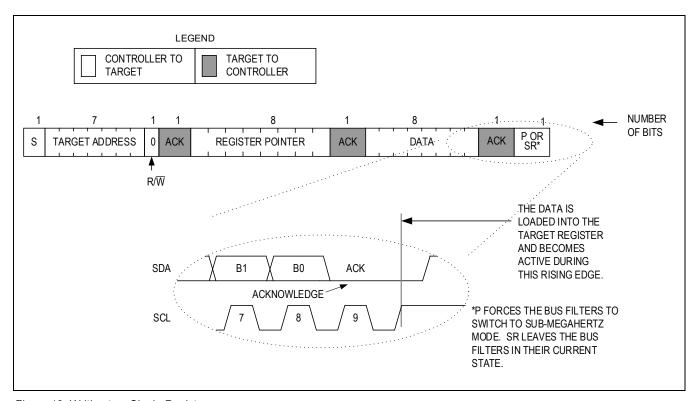

| Writing to a Single Register                        | 35 |

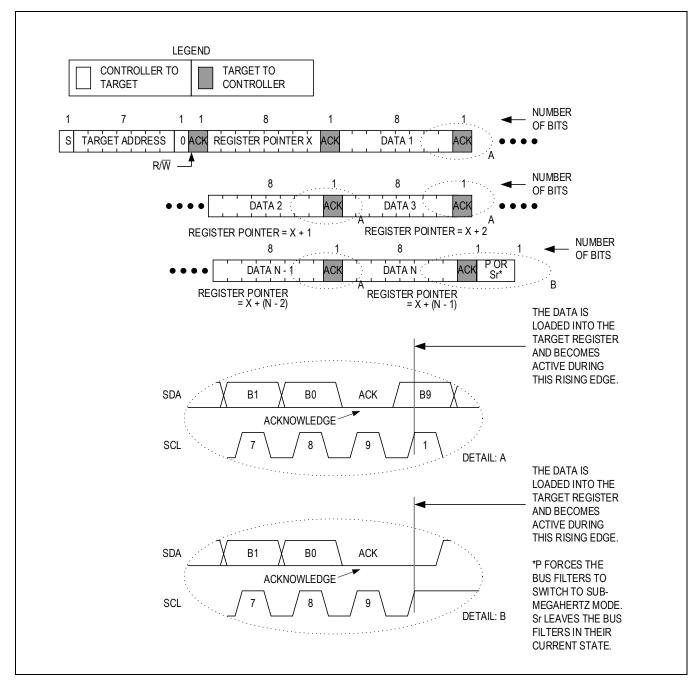

| Writing to Sequential Registers                     | 36 |

| Reading from a Single Register                      | 38 |

| Reading from Sequential Registers                   | 38 |

| Applications Information                            | 39 |

| Inverting Buck-Boost and Boost Enable Options       | 39 |

| Input-Capacitor Selection                           | 39 |

| Inverting Buck-Boost Inductor Selection             | 39 |

| Inverting Buck-Boost Diode Selection                | 40 |

| Inverting Buck-Boost Output Capacitor Selection     | 40 |

| Boost-Inductor Selection                            | 40 |

| Boost Output-Capacitor Selection                    | 41 |

| General PCB Layout Guidelines                       | 41 |

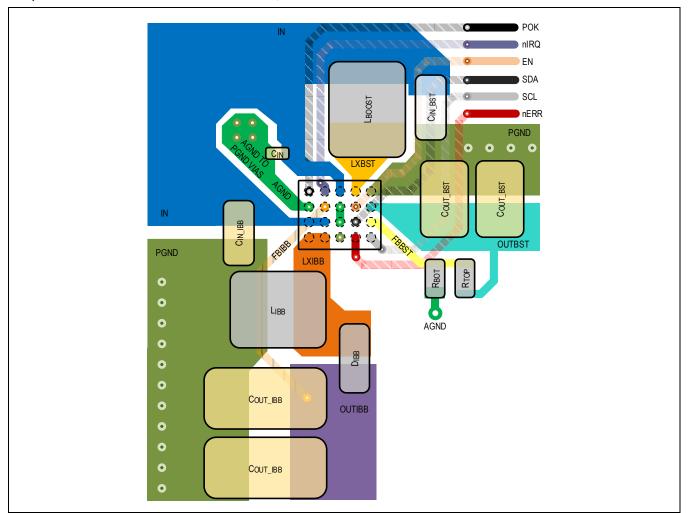

| Example PCB Layout                                  | 42 |

| Гурісаl Application Circuits                        | 43 |

| Register Map                                        | 44 |

| Ordering Information                                | 51 |

MAX77720

# **LIST OF FIGURES**

| Figure 1. MAX77720 Detailed Functional Diagram                                                      | 19 |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 2. Part Number Decode                                                                        |    |

| Figure 3. Start-Up Programmable Timing Diagram (Includes EN_Bias Timing with CNFG_GLBL.EN_BIAS = 0) | 21 |

| Figure 4. Error Pin Functional Diagram                                                              | 22 |

| Figure 5. Error-State Timing Diagram                                                                | 22 |

| Figure 6. Re-Enabling Regulator Using the CNFG_GLBL.EN_IBB Bit                                      | 23 |

| Figure 7. Top-Level State Diagram                                                                   |    |

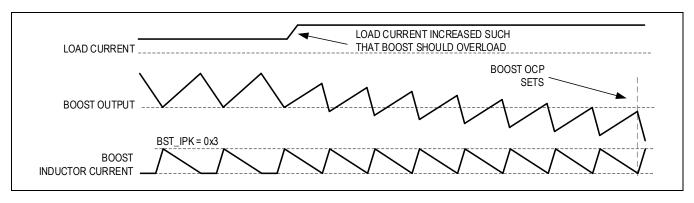

| Figure 8. OCP Conditions for the Boost Converter when IPK_BST = 0x3                                 | 28 |

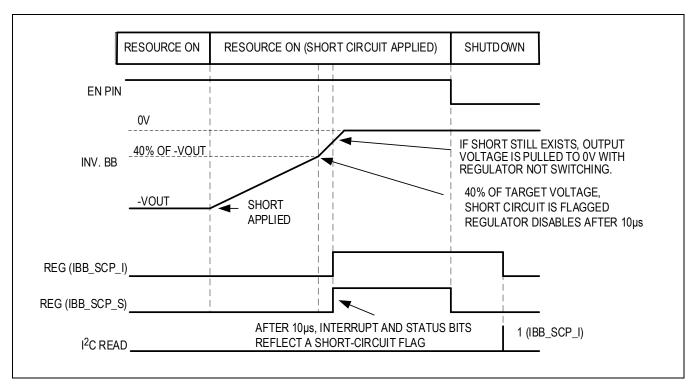

| Figure 9. IBB Short-Circuit Protection Timing Diagram                                               |    |

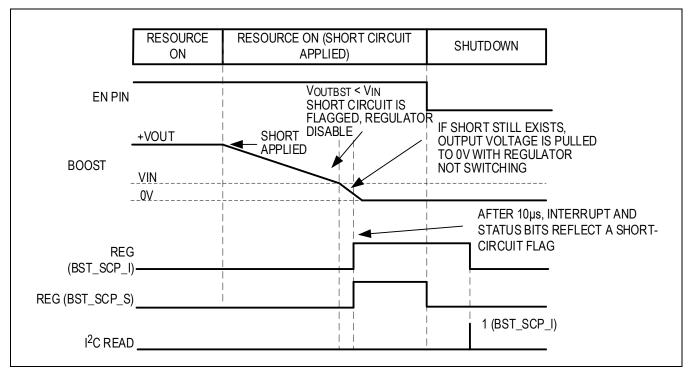

| Figure 10. BST Short-Circuit Protection Timing Diagram                                              | 29 |

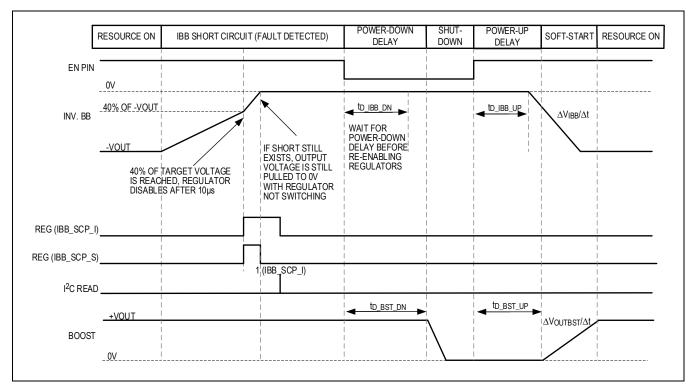

| Figure 11. IBB Short-Circuit Protection Re-Enabling Timing Diagram                                  | 30 |

| Figure 12. Connecting External Feedback Network                                                     |    |

| Figure 13. Functional Logic Diagram for the Communications Controller                               | 32 |

| Figure 14. I <sup>2</sup> C Bit Transfer                                                            | 33 |

| Figure 15. START and STOP Conditions                                                                |    |

| Figure 16. Acknowledge Bit                                                                          |    |

| Figure 17. Target Address Byte Example—SDA Shows the 7-Bit Target Address at 0x42                   |    |

| Figure 18. Writing to a Single Register                                                             | 36 |

| Figure 19. Writing to Sequential Registers                                                          |    |

| Figure 20. Reading to a Single Register                                                             | 38 |

| Figure 21. Reading from Sequential Registers                                                        |    |

| Figure 22. PCB Top Layer and Component Placement Example                                            | 42 |

| Figure 23. Typical Application Circuit                                                              | 43 |

MAX77720

# **LIST OF TABLES**

| Table 1. | OTP Options Table                         | 20 |

|----------|-------------------------------------------|----|

| Table 2. | Error Pin Summary                         |    |

| Table 3. | POK Pin Truth Table                       |    |

| Table 4. | State Diagram Details                     | 25 |

| Table 5. | Inverting Buck-Boost Output-Voltage Range |    |

| Table 6. | I <sup>2</sup> C Target Addresses         |    |

| Table 7. | Boost Inductor-Value Recommendation       |    |

# **Absolute Maximum Ratings**

| EN, nIRQ, nERR, POK to AGND  | 0.3V to IN + 0.3V   |

|------------------------------|---------------------|

| SDA, SCL to AGND             | 0.3V to IN + 0.3V   |

| nIRQ, SDA Continuous Current | ±20mA               |

| IN to AGND                   | 0.3V to +6.0V       |

| INIBB to GNDIBB              | 0.3V to +6V         |

| IN to PGNDBST                | 0.3V to +6V         |

| V <sub>OUTBST</sub> to AGND  | 0.3V to +22V        |

| LXBST to PGNDBST             | 0.3V to +24V        |

| LXIBB to GNDIBB              | 30V to INIBB + 0.3V |

| PGNDBST, GNDIBB to AGND      | 0.3V to +0.3V       |

| FBIBB to AGND30V to +0.3V                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBBST to AGND0.3V to +6V                                                                                                                              |

| LXBST Continuous Current1.6A <sub>RMS</sub> to +1.6A <sub>RMS</sub>                                                                                   |

| LXIBB Continuous Current1.6A <sub>RMS</sub> to +1.6A <sub>RMS</sub>                                                                                   |

| Continuous Power Dissipation for WLP package $(T_A = +70^{\circ}C \text{ derate } 20.4\text{mW/°C above } +70^{\circ}C \text{ (Note 1))}840\text{mW}$ |

| Operating Temperature Range40°C to +125°C                                                                                                             |

| Maximum Junction Temperature+150°C                                                                                                                    |

| Storage Temperature Range65°C to +150°C                                                                                                               |

| Soldering Temperature (reflow)+260°C                                                                                                                  |

**Note 1:** Limits are 100% production tested at T<sub>J</sub> = +25°C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Operating Junction Temperature | 40°C to +125°C |

|--------------------------------|----------------|

| Operating Ambient Temperature  | 40°C to +125°C |

| Input Voltage Range            | 2.5V to 5.5V   |

| V <sub>IO</sub> Voltage Range  | 1.2V to 3.6V   |

# **Package Information**

| Package Code                           | N201D2+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | 21-100659                      |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four Layer Board:  |                                |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 55.49°C/W                      |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com">www.maximintegrated.com</a>.

### **Electrical Characteristics**

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T_J = +25°C.$  Limits over the operating temperature range  $(T_J = -40°C \text{ to } +125°C)$  and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                  | SYMBOL          | CONDITIONS                                                        | MIN | TYP | MAX | UNITS |

|----------------------------|-----------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| Operating Voltage<br>Range | V <sub>IN</sub> |                                                                   | 2.5 |     | 5.5 | V     |

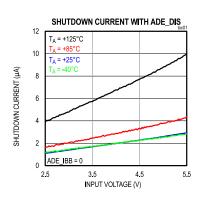

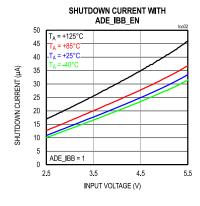

| Shutdown Supply<br>Current |                 | Main bias is off (CNFG_DCDC0.ADE_IBB = 0x0)                       |     | 3   |     |       |

|                            | ISHDN           | Main bias is off (CNFG_DCDC0.ADE_IBB = 0x1)                       |     | μΑ  |     |       |

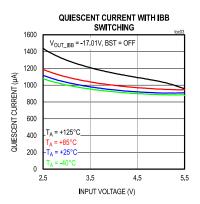

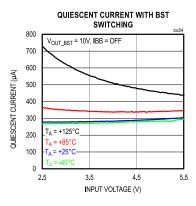

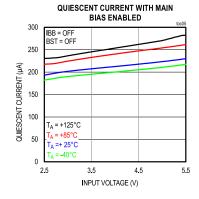

| Quiescent Current          |                 | Main bias is on                                                   |     | 235 |     |       |

|                            |                 | Main bias is on and BST regulator on (device not switching)       |     | 252 |     |       |

|                            | IQ              | Main bias is on and IBB regulator on (device not switching)       |     | 742 |     | μΑ    |

|                            |                 | Main bias is on and both regulators are on (device not switching) |     | 757 |     |       |

# **Electrical Characteristics—Global Resources**

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T<sub>J</sub> = +25°C. Limits over the operating temperature range (T<sub>J</sub> = -40°C to +125°C) and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)$

| PARAMETER                             | SYMBOL                | CONDITIONS                                                                                   | MIN  | TYP    | MAX  | UNITS |

|---------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|------|--------|------|-------|

| GENERAL CHARACTER                     | RISTICS               |                                                                                              |      |        |      |       |

| Main Bias Enable Time                 | tSBIAS_EN             |                                                                                              |      | 60     |      | μs    |

| VOLTAGE MONITORS/F                    | POWER-ON RES          | ET (POR)                                                                                     |      |        |      | •     |

| POR Threshold                         | V <sub>POR</sub>      | V <sub>IN</sub> falling                                                                      |      | 1.5    |      | V     |

| POR Threshold<br>Hysteresis           | V <sub>POR_HYS</sub>  |                                                                                              |      | 100    |      | mV    |

| VOLTAGE MONITORS/U                    | JNDERVOLTAGI          | E LOCKOUT (UVLO)                                                                             |      |        |      | •     |

| UVLO Threshold                        | V <sub>UVLO</sub>     | V <sub>IN</sub> falling                                                                      | 2.3  | 2.4    | 2.5  | V     |

| UVLO Threshold<br>Hysteresis          | V <sub>UVLO_HYS</sub> |                                                                                              |      | 100    |      | mV    |

| VOLTAGE MONITORS/0                    | OVERVOLTAGE           | LOCKOUT (OVLO)                                                                               |      |        |      | •     |

| OVLO Threshold                        | V <sub>OVLO</sub>     | V <sub>IN</sub> rising                                                                       | 5.70 | 5.85   | 6.00 | V     |

| VOLTAGE MONITORS/1                    | THERMAL MONI          | TORS                                                                                         |      |        |      | •     |

| Overtemperature<br>Lockout Threshold  | T <sub>OTLO</sub>     | T <sub>J</sub> rising                                                                        |      | +165   |      | °C    |

| Overtemperature<br>Lockout Hysteresis | T <sub>OTLO_HYS</sub> |                                                                                              |      | 15     |      | °C    |

| OPEN-DRAIN INTERRU                    | PT OUTPUT (nIF        | RQ)                                                                                          |      |        |      | •     |

| Output Voltage Low                    | V <sub>OL</sub>       | I <sub>SINK</sub> = 2mA                                                                      |      |        | 0.4  | V     |

| Leakage Current                       | I <sub>nIRQ_LKG</sub> | $V_{IN}$ = 5.5V, nIRQ is high impedance (no interrupts), $V_{nIRQ}$ = 5.5V, $T_{J}$ = +25°C  | -1   | ±0.001 | +1   | μА    |

| -                                     | _                     | $V_{IN}$ = 5.5V, nIRQ is high impedance (no interrupts), $V_{nIRQ}$ = 5.5V, $T_{J}$ = +125°C |      | ±0.01  |      |       |

| OPEN-DRAIN POK OUT                    | PUT (POK)             |                                                                                              |      |        |      |       |

| POK Output Voltage<br>Low             | V <sub>POK_L</sub>    | I <sub>POK</sub> = 2mA                                                                       |      |        | 0.4  | V     |

| DOM I DOM I                           | lnov vy               | $V_{IN} = 5.5V, V_{POK} = 5.5V, T_{J} = +25^{\circ}C$                                        | -1   | ±0.001 | +1   |       |

| POK Leakage Current                   | I <sub>POK_LK</sub>   | $V_{IN} = 5.5V$ , $V_{POK} = 5.5V$ , $T_{J} = +125$ °C                                       |      | ±0.01  |      | μA    |

| ENABLE INPUT (EN)                     |                       |                                                                                              |      |        |      | 1     |

| Enable Voltage Falling<br>Threshold   | V <sub>EN_IL</sub>    | V <sub>IN</sub> = 2.5V to 5.5V, EN falling                                                   |      |        | 0.36 | V     |

| Enable Voltage Rising Threshold       | V <sub>EN_IH</sub>    | V <sub>IN</sub> = 2.5V to 5.5V, EN rising                                                    | 0.84 |        |      | V     |

|                                       |                       | V <sub>EN</sub> = 0 to 5.5V, T <sub>J</sub> = +25°C                                          | -1   | ±0.001 | +1   |       |

| Enable Input Leakage                  | I <sub>EN_LK</sub>    | V <sub>EN</sub> = 0 to 5.5V, T <sub>J</sub> = +125°C                                         |      | ±0.01  |      | μA    |

| ERROR PIN (nERR)                      | 1                     | 1                                                                                            |      | -      |      | 1     |

| Error Voltage Falling Threshold       | V <sub>nERR_IL</sub>  | $V_{IN}$ = 2.5V to 5.5V, nERR falling                                                        |      |        | 0.36 | V     |

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T_J = +25°C. Limits over the operating temperature range (T_J = -40°C to +125°C) and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)$

| PARAMETER                                    | SYMBOL                    | CONDITIONS                                             | MIN  | TYP    | MAX | UNITS |

|----------------------------------------------|---------------------------|--------------------------------------------------------|------|--------|-----|-------|

| Error Voltage Rising<br>Threshold            | V <sub>nERR_IH</sub>      | V <sub>IN</sub> = 2.5V to 5.5V, nERR rising            | 0.84 |        |     | V     |

| Error Input Leakage                          | I <sub>nERR_LK</sub>      | V <sub>nERR</sub> = 0 to 5.5V, T <sub>J</sub> = +25°C  | -1   | ±0.001 | +1  |       |

| Elloi iliput Leakage                         | INERK_LK                  | V <sub>nERR</sub> = 0 to 5.5V, T <sub>J</sub> = +125°C |      | ±0.01  |     | μΑ    |

| POWER-UP/POWER-DO                            | WN DELAY (T <sub>DI</sub> | ELAY)                                                  |      |        |     |       |

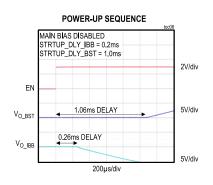

| Power-Up Delay for<br>Inverting Buck-Boost   | t <sub>D_IBB_UP</sub>     | Programmable between 0.2ms and 3.2ms                   |      | 0.2    |     | ms    |

| Power-Down Delay for<br>Inverting Buck-Boost | t <sub>D_IBB_DN</sub>     | Programmable between 0.2ms and 3.2ms                   |      | 0.2    |     | ms    |

| Power-Up Delay for Boost                     | t <sub>D_BST_UP</sub>     | Programmable between 0.2ms and 3.2ms                   |      | 0.2    |     | ms    |

| Power-Down Delay for Boost                   | t <sub>D_BST_DN</sub>     | Programmable between 0.2ms and 3.2ms                   |      | 0.2    |     | ms    |

# **Electrical Characteristics—Boost Regulator**

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T<sub>J</sub> = +25°C. Limits over the operating temperature range (T<sub>J</sub> = -40°C to +125°C) and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)$

| PARAMETER                       | SYMBOL                   | CONE                                                              | DITIONS                           | MIN                    | TYP   | MAX   | UNITS |

|---------------------------------|--------------------------|-------------------------------------------------------------------|-----------------------------------|------------------------|-------|-------|-------|

| BOOST REGULATOR                 |                          |                                                                   |                                   |                        |       |       | •     |

| Boost Output-Voltage<br>Range   | V <sub>OUTBST</sub>      | V <sub>IN</sub> + 0.5V < V <sub>OUT</sub> _TARGET                 |                                   | V <sub>IN</sub> + 0.5V |       | 20    | V     |

| Boost Feedback (FB)             | ACC <sub>CCM</sub>       | V <sub>FBBST</sub> falling wher<br>frequency = 1MHz (             |                                   | -1.5                   |       | +1.5  | %     |

| Accuracy                        | ACC <sub>DCM</sub>       | V <sub>FBBST</sub> falling wher frequency < 1MHz (                |                                   | 1.239                  | 1.258 | 1.277 | V     |

| Boost Output Load<br>Regulation | ACC <sub>LDREG</sub>     | 10mA < I <sub>OUTBST</sub> <                                      | 160mA                             |                        | 2.0   |       | %     |

| LXBST Leakage Current           | I <sub>LXP_LK</sub>      | $V_{LX} = 5.5V, V_{EN} = V_{OUT} = 0V,$<br>$T_{J} = +25^{\circ}C$ |                                   |                        | 10    | 500   | nA    |

|                                 |                          | CNFG_IBB0.IPK_B                                                   | ST[2:1] = 0b00                    | 0.8                    | 1.0   | 1.2   |       |

| LXBST Inductor Peak             | I <sub>BST_ILIM</sub>    | CNFG_IBB0.IPK_BST[2:1] = 0b01                                     |                                   |                        | 0.781 |       |       |

| Current Limit (Note 3)          |                          | CNFG_IBB0.IPK_B                                                   | ST[2:1] = 0b10                    |                        | 0.563 |       | Α     |

| ,                               |                          | DCM only                                                          | CNFG_IBB0.IPK_B<br>ST[2:1] = 0b11 |                        | 0.5   |       |       |

| Boost Soft-Start Ramp<br>Rate   | ΔV <sub>OUTBST</sub> /Δt | $C_{OUT\_BST} = 20\mu F$ ,                                        | 35V, nominal                      |                        | 7     |       | mV/μs |

| LXBST Maximum Duty<br>Cycle     | DC <sub>BST</sub>        | V <sub>IN</sub> = 2.5V ( <u>Note 4</u> )                          |                                   |                        | 90    |       | %     |

| LXBST Maximum On-<br>Time       | ton_max                  |                                                                   |                                   | 1.9                    | 3.4   | 6.1   | μs    |

| LXBST On-Time                   | t <sub>BST_ON</sub>      | V <sub>IN</sub> = 5.5V ( <u>Note 4</u> )                          |                                   |                        | 450   |       | ns    |

|                                 |                          | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> =                        | 12.0V, T <sub>J</sub> = +25°C     | 230                    | 255   | 280   |       |

| LXBST Off-Time (Note 4)         | e t <sub>BST_OFF</sub>   | V <sub>IN</sub> = 5.5V, V <sub>OUT</sub> =                        | 12.0V                             |                        | 350   |       | ns    |

| ''                              |                          | V <sub>IN</sub> = 5.0V, V <sub>OUT</sub> =                        | 7.0V                              |                        | 530   |       |       |

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T_J = +25°C.$  Limits over the operating temperature range  $(T_J = -40°C \text{ to } +125°C)$  and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                   | SYMBOL                 | CONDITIONS                                                         | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------|------------------------|--------------------------------------------------------------------|------|------|------|-------|

|                                             |                        | V <sub>IN</sub> = 3.0V, V <sub>OUT</sub> = 18V                     |      | 147  |      |       |

|                                             |                        | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 12V                     |      | 1.0  |      |       |

| LXBST Switching                             | f <sub>BST_SW</sub>    | V <sub>IN</sub> = 5.0V, V <sub>OUT</sub> = 7.0V                    |      | 1.0  |      | MHz   |

| Frequency                                   |                        | V <sub>IN</sub> = 3.0V, V <sub>OUT</sub> = 18V                     |      | 1.0  |      |       |

| Boost n-Channel On-<br>Resistance           | R <sub>BST_RDSON</sub> | V <sub>IN</sub> = 3.6V                                             |      | 320  | 650  | mΩ    |

| Boost p-Channel On-<br>Resistance           | R <sub>BST_RDSON</sub> | V <sub>IN</sub> = 3.6V                                             |      | 320  | 650  | mΩ    |

| Boost Diode Forward<br>Voltage              | V <sub>F</sub>         | V <sub>IN</sub> = 3.6V, I <sub>LX</sub> = 100mA                    |      | 0.4  |      | V     |

| Boost FB Leakage                            | I <sub>FB_BST_LK</sub> | V <sub>FBBST</sub> = 1.25V                                         | -100 | 0.5  | +100 | nA    |

| Boost Active Discharge<br>Resistance        | R <sub>BST_AD</sub>    | V <sub>IN</sub> = 3.6V                                             |      | 320  |      | Ω     |

| BOOST POK                                   |                        |                                                                    |      |      |      |       |

| Boost POK Rising<br>Threshold               | V <sub>POK_BST_R</sub> | V <sub>OUT</sub> when POK switches,<br>V <sub>OUT</sub> BST rising |      | 92   |      | %     |

| Boost POK Falling<br>Threshold              | V <sub>POK_BST_F</sub> | V <sub>OUT</sub> when POK switches, V <sub>OUT_BST</sub> falling   |      | 89.5 |      | %     |

| BST Short-Circuit Fault<br>Rising Threshold | V <sub>SC_BST</sub>    | Rising, 10µs timer, enabled at 2800µs after the rail is turned on  |      | IN   |      | V     |

# **Electrical Characteristics—Inverting Buck-Boost**

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T<sub>J</sub> = +25°C. Limits over the operating temperature range (T<sub>.I</sub> = -40°C to +125°C) and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)$

| PARAMETER                      | SYMBOL                | CONDITIONS                                                                                                  | MIN    | TYP    | MAX    | UNITS   |

|--------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|--------|--------|--------|---------|

| INVERTING BUCK-BOO             | ST REGULATO           | R                                                                                                           |        |        |        |         |

| IBB Programmable               | V                     | Low range                                                                                                   | -24.00 | -18.00 | -17.01 | .,,     |

| Output-Voltage Range           | V <sub>IBB_RNG</sub>  | High range                                                                                                  | -17.00 | -11.00 | -10.01 | V       |

| IBB Output-Voltage<br>Step     | V <sub>IBB_STEP</sub> | 9-bit (2 bytes) configuration                                                                               |        | 15     |        | mV      |

| IBB Output-Voltage<br>Accuracy | V <sub>IBB_ACC</sub>  | T <sub>A</sub> = -40°C to +125°C                                                                            | -2.0   |        | +2.0   | %       |

| FBN Input Current              | I <sub>IBB_FBN</sub>  | At -15V, FBN sense input current                                                                            |        | -50    |        | μΑ      |

| LXN Switching Frequency        | f <sub>IBB_SW</sub>   |                                                                                                             | 1275   | 1500   | 1725   | kHz     |

| IBB Maximum Duty<br>Cycle      | D <sub>IBB_MAX</sub>  |                                                                                                             | 91     | 95     | 98     | %       |

| LXN On-Resistance              | R <sub>IBB_ON</sub>   |                                                                                                             |        | 0.25   | 0.5    | Ω       |

| LXN Leakage Current            | I <sub>IBB_LK</sub>   | Block disabled, V <sub>LXN</sub> = -24V                                                                     |        |        | 20     | μΑ      |

| LXN Current Limit              | I <sub>IBB_ILIM</sub> | V <sub>IN</sub> = 3.6V, FBIBB = -18V                                                                        |        | 1.5    |        | Α       |

| IBB Soft-Start Ramp            | ΔV <sub>IBB</sub> /Δt | V <sub>IN</sub> = 2.5V, FBIBB = -24V, C <sub>OUT_IBB</sub> = 20μF 50V, nominal, I <sub>IBB_SS</sub> = 600mA |        | -4     |        | m\///:- |

| Rate                           | ¬ΛIBB\¬η              | $V_{IN}$ = 5.5V, FBIBB = -17V, $C_{OUT\_IBB}$ = 20 $\mu$ F, 50V, nominal, $I_{IBB}$ SS = 600mA              |        | -8     |        | mV/µs   |

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T_J = +25°C.$  Limits over the operating temperature range  $(T_J = -40°C \text{ to } +125°C)$  and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                   | SYMBOL                 | CONDITIONS                                                                                            | MIN | TYP  | MAX | UNITS |

|---------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| IBB Soft-Start Current                      | l                      | CNFG_DCDC0.SS_IBB = 0x0, V <sub>IN</sub> = 3.6V                                                       |     | 400  |     |       |

| Limit                                       | I <sub>IBB_</sub> SS   | CNFG_DCDC0.SS_IBB = 0x1, V <sub>IN</sub> = 3.6V                                                       |     | 600  |     | mA    |

| IBB Active Discharge<br>Resistance          | R <sub>IBB_AD</sub>    | V <sub>IN</sub> = 3.6V                                                                                |     | 320  |     | Ω     |

| INVERTING BUCK-BOO                          | ST POK                 |                                                                                                       |     |      |     |       |

| IBB POK Rising<br>Threshold                 | V <sub>POK_IBB_R</sub> | V <sub>OUT_IBB</sub> when POK switches,<br>V <sub>OUT_IBB</sub> rising                                |     | 90   |     | %     |

| IBB POK Falling                             | K Falling              | V <sub>OUT_IBB</sub> when POK switches,<br>V <sub>OUT_IBB</sub> falling (V <sub>OUT_IBB</sub> = -18V) |     | 81.7 |     | 0/    |

| Threshold                                   | V <sub>POK_IBB_F</sub> | V <sub>OUT_IBB</sub> when POK switches,<br>V <sub>OUT_IBB</sub> falling (V <sub>OUT_IBB</sub> = -11V) |     | 76.5 |     | %     |

| IBB Short-Circuit Fault<br>Rising Threshold | V <sub>SC_IBB</sub>    | Rising, 10µs timer, enabled at 2800µs after the rail is turned on                                     |     | 40   |     | %     |

# Electrical Characteristics—I<sup>2</sup>C Serial Interface

$(V_{IN} = 3.6V, V_{OUTIBB} = -18V, V_{OUTBST} = 10V, limits are 100\% production tested at T_J = +25°C.$  Limits over the operating temperature range  $(T_J = -40°C \text{ to } +125°C)$  and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                            | SYMBOL                | CONDITIONS                          | MIN  | TYP   | MAX  | UNITS |

|------------------------------------------------------|-----------------------|-------------------------------------|------|-------|------|-------|

| I/O STAGE                                            |                       |                                     | ·    |       |      |       |

| SCL, SDA Input High<br>Voltage                       | $V_{IH}$              |                                     | 0.84 |       |      | V     |

| SCL, SDA Input Low<br>Voltage                        | $V_{IL}$              |                                     |      |       | 0.36 | V     |

| SDA Output Low<br>Voltage                            | $V_{OL}$              | I <sub>SINK</sub> = 4mA             |      |       | 0.4  | V     |

| SCL, SDA Input<br>Capacitance                        | C <sub>I</sub>        |                                     |      | 6     |      | pF    |

| SCL, SDA Input<br>Leakage Current                    | I <sub>LK</sub>       |                                     | -10  | 0.001 | +10  | μA    |

| I <sup>2</sup> C-COMPATIBLE INTER                    | RFACE TIMING          | (STANDARD) ( <u>Note 5</u> )        |      |       |      |       |

| Clock Frequency                                      | f <sub>SCL</sub>      |                                     | 0    |       | 1000 | kHz   |

| Bus Free Time Between<br>STOP and START<br>Condition | t <sub>BUSF</sub>     |                                     | 0.5  |       |      | μs    |

| Hold Time (REPEATED)<br>START Condition              | tHD_START             | ( <u>Note 6</u> )                   | 0.26 |       |      | μs    |

| SCL Low Period                                       | $t_{LOW}$             |                                     | 0.5  |       |      | μs    |

| SCL High Period                                      | <sup>t</sup> HIGH     |                                     | 0.3  |       |      | μs    |

| Setup Time REPEATED START Condition                  | t <sub>SU_START</sub> |                                     | 0.26 |       |      | μs    |

| DATA Hold Time                                       | t <sub>HD_DATA</sub>  | ( <u>Note 7</u> and <u>Note 8</u> ) | 0    |       |      | μs    |

| Setup Time for STOP condition                        | t <sub>SU_STO</sub>   |                                     | 0.26 |       |      | μs    |

| Pulse Width of<br>Suppressed Spikes                  | t <sub>SP</sub>       |                                     |      | 50    |      | ns    |

- Note 2: Output accuracy does not include load, line, or ripple.

- Note 3: This is a static measurement. The actual peak current limit depends upon V<sub>IN</sub> and the inductor due to propagation delays.

- Note 4: Measured opened loop. Propagation delays not included.

- Note 5: Design guidance only. Not production tested.

- Note 6: f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.

- Note 7: The maximum t<sub>HD\_DATA</sub> has to be met only if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- Note 8: This device internally provides a hold time of at least 100ns for the SDA signal (referred to the minimum V<sub>IH</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

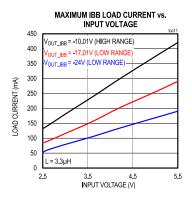

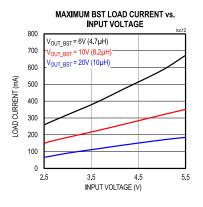

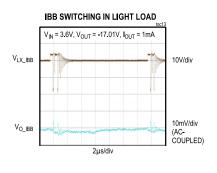

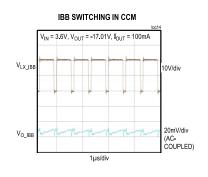

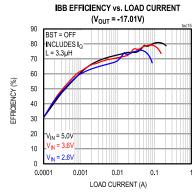

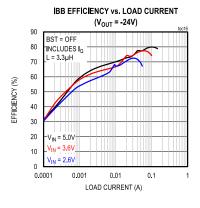

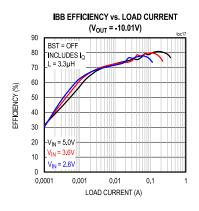

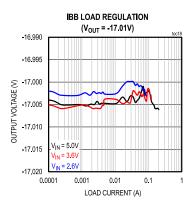

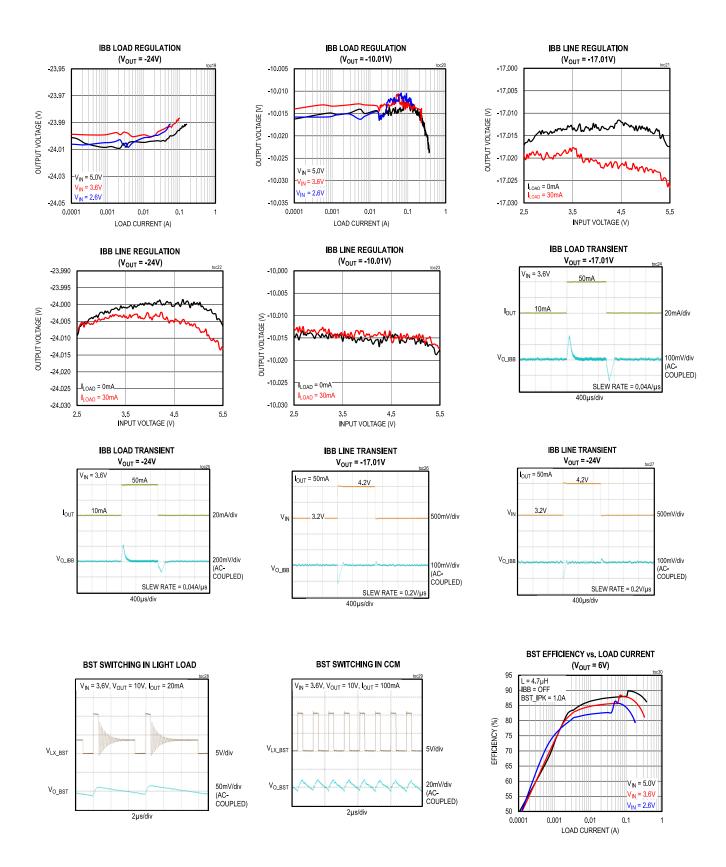

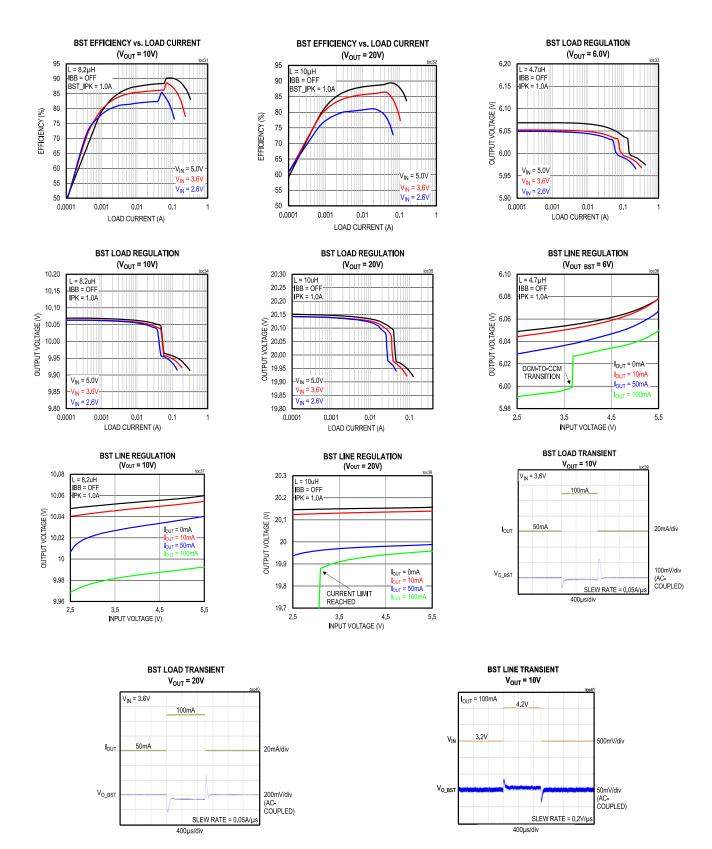

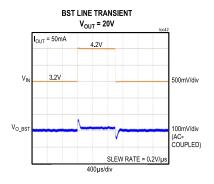

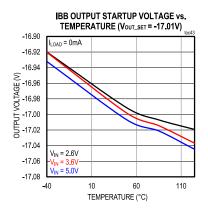

# **Typical Operating Characteristics**

$V_{IN}$  = 3.6V,  $V_{OUTIBB}$  = -18V,  $V_{OUTBST}$  = 10V, limits are 100% production tested at  $T_J$  = +25°C. Limits over the operating temperature range ( $T_J$  = -40°C to +125°C) and relevant voltage range are guaranteed by design and characterization, unless otherwise noted.

# **Pin Configuration**

# **Pin Description**

| PIN        | NAME | FUNCTION                                                                                             | Туре              |

|------------|------|------------------------------------------------------------------------------------------------------|-------------------|

| C2         | EN   | Active-High Enable Input                                                                             | Digital<br>Input  |

| D4         | nIRQ | Active-Low, Open-Drain Interrupt. Connect a 100kΩ pull-up resistor from nIRQ to external logic rail. | Digital<br>Output |

| A1         | SCL  | I <sup>2</sup> C Clock                                                                               | Digital<br>Input  |

| B2         | SDA  | I <sup>2</sup> C Data                                                                                | Digital I/O       |

| D3         | IN   | Input Voltage Connection. Bypass to AGND with a 1µF ceramic capacitor.                               | Power<br>Input    |

| B3, C3, C5 | AGND | Quiet Ground                                                                                         | Ground            |

| D5         | POK  | Open-Drain, Power-OK Output. Connect a 100kΩ pull-up resistor from POK to external logic rail.       | Digital<br>Output |

| A2     | nERR        | Active-Low Error Input. Connect a $100k\Omega$ pull-up resistor from nERR to external logic rail.                                                                                                                                      | Digital<br>Input |

|--------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B4, B5 | INIBB       | Inverting Buck-Boost Power Input. Bypass to GNDIBB with a 22µF ceramic capacitor.                                                                                                                                                      | Power<br>Input   |

| C4     | FBIBB       | Inverting Buck-Boost Output-Voltage Sense Input. Connect to the output at the point-of-load (close to the output capacitor).                                                                                                           | Power<br>Input   |

| A4, A5 | LXIBB       | Switching Node for Inverting Buck-Boost. Connect LXIBB to an external Schottky diode.                                                                                                                                                  | Power<br>Output  |

| A3     | GNDIBB      | Ground for Inverting Buck-Boost                                                                                                                                                                                                        | Ground           |

| C1     | OUTBST      | Boost Output-Voltage                                                                                                                                                                                                                   | Power<br>Output  |

| B1     | FBBST       | Boost Output-Voltage Feedback Input. Connect to the center tap of an external resistor-divider from the output to AGND to set the output voltage. See the <u>Configuring</u> the <u>Boost Output Voltage</u> section for more details. | Power<br>Input   |

| D2     | LXBST       | Switching Node Pin of Boost. Connect the inductor from IN to LXBST.                                                                                                                                                                    | Power<br>Output  |

| D1     | PGNDBS<br>T | Power Ground for Boost                                                                                                                                                                                                                 | Ground           |

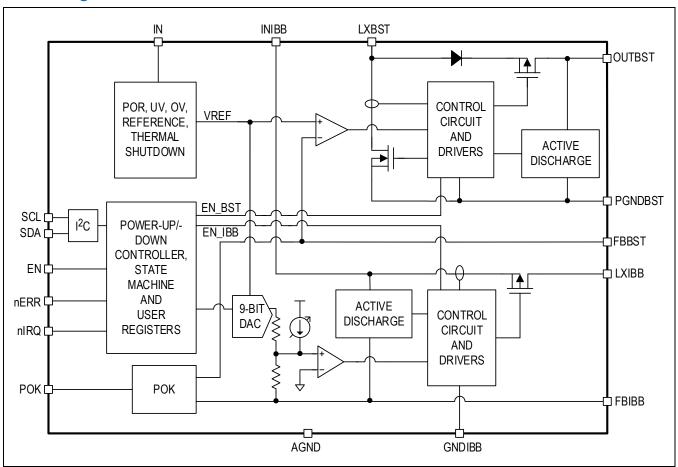

# **Block Diagram**

Figure 1. MAX77720 Detailed Functional Diagram

## **Detailed Description**

The MAX77720 is a wide-range, dual-polarity integrated circuit that generates both a positive and negative output voltage by combining both a step-up boost converter and an asynchronous inverting buck-boost converter. The boost converter has True Shutdown, which disconnects the output from the input with no forward or reverse current.

Each regulator is independently regulated and separately controlled by a pulse-width-modulated (PWM) controller. Additionally, the boost converter allows for programmability of changing the peak current limit thresholds. The different peak current limit thresholds for the boost converter allow the use of lower profile and smaller external components optimized for a particular application. The use of external feedback resistors for the boost converter allows for wider output-voltage range and customizable output voltages at startup.

The inverting buck-boost converter allows for programmable voltages from a host processor through I<sup>2</sup>C.

An optional I<sup>2</sup>C serial interface allows dynamic control of the following:

- · Output voltage for the inverting regulator (using internal reference voltage)

- Programmable peak current limit for the positive regulator (using I2C)

- · Turn on and shutdown delay for the positive and negative regulator

- POK status and fault interrupts

- Enabling and disabling active discharge for the positive and negative regulator

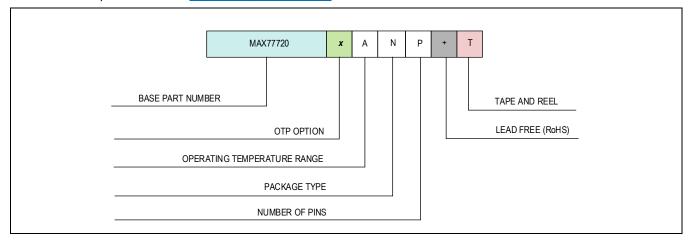

## **Part Number Decoding**

The MAX77720 has different one-time programming (OTP) options and variants to support a variety of applications. Variants are versions of the MAX77720 with different features. See <u>Figure 2</u> for an explanation of the MAX77720 part number decoding. The MAX77720 offers various settings such as settings for default output voltages or power-on delay. These OTP variants are identified by the register name, which can be read in the OTP\_REV register. <u>Table 1</u> lists all available OTP options. Refer to <u>Key Package Information</u> for more details.

Figure 2. Part Number Decode

# **Table 1. OTP Options Table**

|        |                     |                                               | OTP LETTER AND SETTINGS |

|--------|---------------------|-----------------------------------------------|-------------------------|

| BLOCK  | BITFIELD NAME       | SETTING NAME                                  | S                       |

| Global | ADDR                | I <sup>2</sup> C Address (7-Bit)              | 0x41                    |

| Global | OTP_REV[5:0]        | OTP Revision                                  | 0x21                    |

|        | VOUT_IBB[9:0]       | Inverting Buck-Boost VOUT                     | -17.01V                 |

|        | RNG_IBB             | Inverting Buck-Boost Output-Voltage Range     | Low Range               |

|        | SS_IBB              | Inverting Buck-Boost Soft-Start Current Limit | 600mA                   |

| IBB    | ADE_IBB             | Inverting Buck-Boost Active Discharge Enable  | Enabled                 |

| IDD    | STRTUP_DLY_IBB[7:4] | Inverting Buck-Boost Startup Delay            | 0.2ms                   |

|        | PWRDN_DLY_IBB[3:0]  | Inverting Buck-Boost Power-Down Delay         | 0.2ms                   |

|        | IPK_BST             | Boost Peak Current Limit                      | 1.0A                    |

|        | ADE_BST             | Boost Active Discharge Enable                 | Enabled                 |

| BST    | STRTUP_DLY_BST[7:4] | Boost Startup Delay                           | 0.2ms                   |

|        | PWRDN_DLY_BST[3:0]  | Boost Power-Down Delay                        | 0.2ms                   |

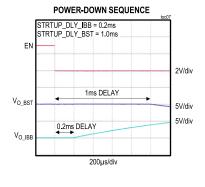

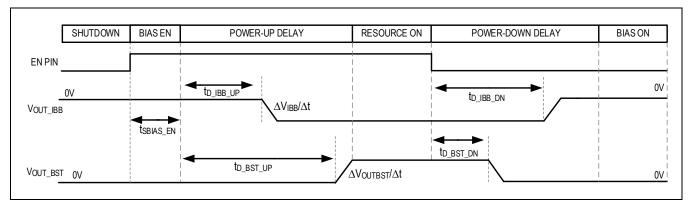

#### Power-Up/Power-Down Sequence

The MAX77720 integrates a timer delay that controls the power-up/power-down timing of the regulators. The functionality of the power-up and power-down is described as follows:

- The power-up delays start from the time the EN pin goes from low to high.

- The power-down delays start from the time the EN pin goes from high to low.

- The 16 programmable power-up and power-down delays range from 0.2ms to 3.2ms in 0.2ms increments.

- The soft-start feature limits the slew rate of the output voltage during startup (each regulator has their own soft-start feature).

- The power-down ramp rate depends on the output load current and active discharge circuit.

Figure 3 shows an example of the power-up/power-down sequence with respect to the EN pin.

Figure 3. Start-Up Programmable Timing Diagram (Includes EN\_Bias Timing with CNFG\_GLBL.EN\_BIAS = 0)

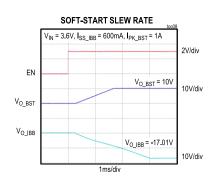

#### Soft-Start

The soft-start feature of the device limits inrush current during startup, which is achieved by limiting the slew rate of the output voltage during startup ( $d_V/d_{TSS}$ ). The MAX77720 soft-start begins when the EN pin is pulled high above  $V_{IH}$  and after the programmed delay for each individual regulator.

The output-voltage ramp rate for the boost regulator is a fixed 7mV/µs. The output-voltage ramp rate for the inverting buck-boost regulator is dependent on the soft-start current limit setting, input voltage, and output voltage. See the <u>Electrical Characteristics</u> for typical soft-start ramp rates for the selected settings. The two selectable soft-start current limits allow for trading power-up time for minimum battery transient impact and should be changed for certain applications.

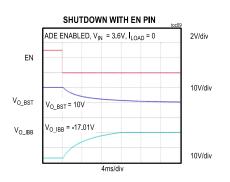

### **Shutdown**

When the EN pin is pulled low ( $V_{EN} < V_{EN\_IL}$ ), the MAX77720 goes into the shutdown state. While in the shutdown state, both regulators are not switching but are still programmable through I<sup>2</sup>C. See <u>Figure 7</u> and <u>Table 4</u> for details. The current consumed in this mode is 235 $\mu$ A if the main bias is on with no regulators enabled.

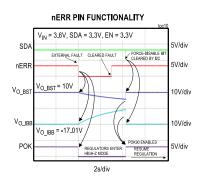

### nERR Error Pin

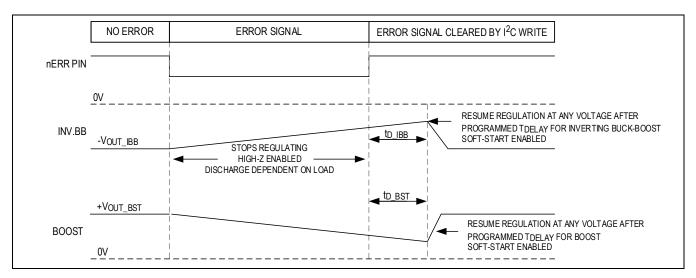

The error pin (nERR) is an active-low, digital input. When this pin receives a falling edge, the STAT\_GLBL.ERR\_PIN\_S asserts high and both the boost and the inverting buck-boost converters stop regulating. If the active discharge is disabled, both regulators remain in a high-Z state, and the rate of discharge depends on the output load condition. To re-enable the regulators, write a 0 to the CNFG\_GLBL.FORCE\_DIS bitfield through I<sup>2</sup>C. Once I<sup>2</sup>C clears it, both the boost and the inverting buck-boost converters resume regulation again after the programmed timing startup delay with the programmed soft-start enabled at any voltage.

<u>Table 2</u> gives a summary of certain states while <u>Figure 4</u> displays the output voltages with respect to the nERR pin if the active discharge is disabled.

**Table 2. Error Pin Summary**

| nERR<br>PIN    | ERROR PIN STATUS (STAT_GLBL.ERR_PIN_S) | FORCE DISABLE BIT (CFNG_GLBL.FORCE_DIS)                          | INVERTING BUCK-BOOST                                | BOOST                                               |

|----------------|----------------------------------------|------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| High to<br>Low | 1                                      | 1                                                                | High-Z                                              | High-Z                                              |

| Low to<br>High | 0                                      | Keep 1 until I <sup>2</sup> C clears the error by writing to a 0 | Keep high-Z until I <sup>2</sup> C clears the error | Keep high-Z until I <sup>2</sup> C clears the error |

Figure 4. Error Pin Functional Diagram

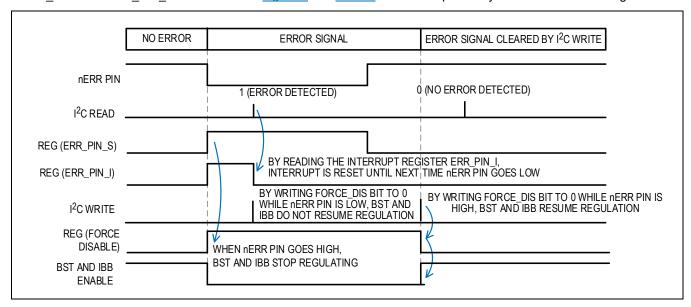

There are multiple ways to re-enable the regulators during the error-on state. Each scenario assumes that an error signal has already been received by the nERR pin going from high to low:

1. After the nERR pin returns high, regulation for both the inverting buck-boost and boost converters resumes with the programmed timing delays and soft-start after writing a 0 to the CNFG\_GLBL.FORCE\_DIS bitfield.

**Note:** This method only works when the EN pin is still held high. Otherwise, CNFG\_GLBL.FORCE\_DIS does not reenable the regulators. *Figure 5* shows the requirements to resume regulation using this method.

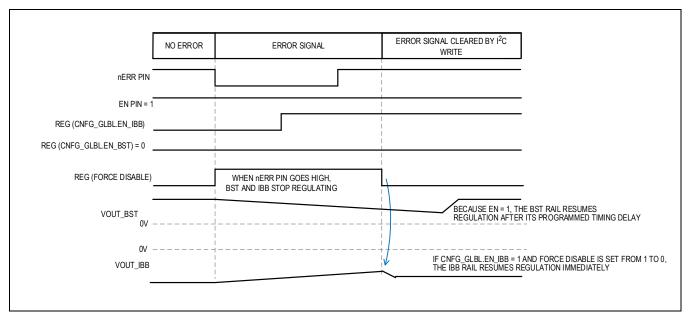

2. After the nERR pin returns high, regulation for both the inverting buck-boost and boost converter can be enabled individually through I<sup>2</sup>C by writing to registers CNFG\_GLBL.FORCE\_IBB\_ON = 1 or CNFG\_GLBL.FORCE\_BST\_ON = 1 and by writing CNFG\_GLBL.FORCE\_DIS = 0. If CNFG\_GLBL.FORCE\_XXX\_ON = 1, no timing delay is implemented for the regulator to resume regulation. If the EN pin is still held high, while only one CNFG\_GLBL.FORCE\_XXX\_ON = 1, the other regulator resumes regulation after its programmed timing delay. <u>Figure 6</u> shows this behavior with the CNFG\_GLBL.FORCE\_IBB\_ON = 1 scenario. <u>Figure 7</u> and <u>Table 4</u> show the top-level system flow to resume regulation.

Figure 5. Error-State Timing Diagram

Figure 6. Re-Enabling Regulator Using the CNFG\_GLBL.EN\_IBB Bit

## **Output Active-Discharge**

Each regulator has an active-discharge resistor (R<sub>AD\_BST</sub> and R<sub>AD\_IBB</sub>). The active-discharge feature may be enabled (CNFG\_DCDC0.ADE\_BST or CNFG\_DCDC0.ADE\_IBB = 1) or disabled (CNFG\_DCDC0.ADE\_BST or CNFG\_DCDC0.ADE\_IBB = 0) independently for each individual regulator. Enabling the active discharge feature ensures a complete and timely power-down of all system peripherals.

Note: The R<sub>AD IBB</sub> turns off once the output voltage of the inverting buck-boost reaches 0V.

#### **Power-OK Monitor**

The IC features power-OK (POK) status bits (STAT\_GLBL.POK\_IBB\_S and STAT\_GLBL.POK\_BST\_S) and interrupt flags (INT GLBL0.POK IBB I and INT GLBL0.POK BST I).

In addition, the open-drain POK digital output pin reflects the logical AND of all POK flags of enabled regulators. If either regulators are disabled, the POK pin is pulled low. See <u>Table 3</u> for the truth table. Connect the POK pin with a pull-up resistor to an external logic rail.

While in the error-on state (see <u>Table 2</u>), both regulators are disabled. Therefore, the POK pin is pulled low.

Table 3. POK Pin Truth Table

| IBB ENABLE | POK_IBB_S  | BST ENABLE | POK_BST_S  | POK PIN STATE |   |

|------------|------------|------------|------------|---------------|---|

| Disabled   | Don't Care | Disabled   | Don't Care | 0             |   |

| Disabled   | Don't Core | Frablad    | 0          | 0             |   |

| Disabled   | Don't Care | Enabled    | 1          | 0             |   |

| C nobled   | 0          | Disabled   | Disabled   | Don't Care    | 0 |

| Enabled    | 1          |            | Don't Care | 0             |   |

|            | 0          |            | 0          | 0             |   |

| Fachlad    | 0          | Fraklad    | 1          | 0             |   |

| Enabled    | 1          | Enabled    | 0          | 0             |   |

|            | 1          |            | 1          | High-Z        |   |

If the target output voltage of the inverting buck-boost is changed to a higher absolute value (e.g., -17.01V to -24V), STAT\_GLBL.POK\_IBB\_S can be 0 during the voltage transition. To avoid false flags, ignore STAT\_GLBL.POK\_IBB\_S during a voltage transition and clear the interrupt flag (INT\_GLBL0.POK\_IBB\_I) after the regulator output settles.

## Interrupt (nIRQ)

The nIRQ pin is an active-low, open-drain output typically routed to a controller interrupt input for triggering off interrupt events. Several status, interrupt, and interrupt mask registers monitor key information and update when an interrupt event has occurred. See the Register Map for a comprehensive list of all interrupt bits and status registers. Depending on the OTP, some or all interrupts are masked by default. Initialization software unmasks interrupts of interest.

When any unmasked interrupt occurs, this pin is asserted low. A  $100k\Omega$  pull-up resistor is required for this signal and is typically found inside the controller. If one is unavailable, a board-mounted  $100k\Omega$  pull-up resistor to a logic rail is required.

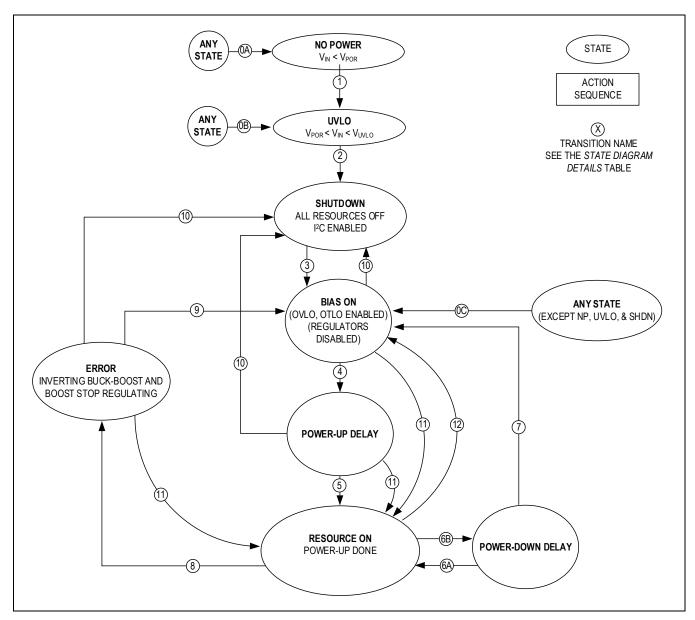

## System State Flow

<u>Figure 7</u> and <u>Table 4</u> describe from a top level the different conditions to enable or disable resources (e.g., switching regulators) in the MAX77720. <u>Figure 7</u> organizes the device's behavior as a set of states (shown in bubbles). For example, the shutdown state is a state in which all regulators and the bias are disabled and the device draws the lowest current from the input. <u>Table 4</u> details the conditions to trigger transitions between two states. For example, to wake up the device and start the power-up sequence (transition 3 to 4 and transition 4 to 5), apply a high signal to the EN pin.

Figure 7. Top-Level State Diagram

# **Table 4. State Diagram Details**

| TRANSITION/STATE | CONDITION                                                                                                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0A               | IN voltage is below the POR threshold ( $V_{IN} < V_{POR}$ ).                                                                                                                                                                                                |

| 0B               | IN voltage is above the POR threshold but is below the UVLO threshold ( $V_{POR} < V_{IN} < V_{UVLO}$ ).                                                                                                                                                     |

| 0C               | Fault detected:  • System overtemperature lockout (T <sub>J</sub> > T <sub>OTLO</sub> ) or  • System overvoltage lockout (V <sub>IN</sub> > V <sub>OVLO</sub> ) or  • Bias circuits are not OK  Both regulators are immediately shut down to protect the IC. |

| No Power         | All registers are reset. I <sup>2</sup> C disabled.                                                                                                                                                                                                          |

| 1                | IN voltage is above the POR threshold ( $V_{IN} > V_{POR}$ ).                                                                                                                                                                                                |

|                  | IN voltage is above the POR threshold but is below the UVLO threshold ( $V_{POR} < V_{IN} < V_{UVLO}$ ).                                                                 |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| UVLO             | All registers are reset in this state except for the fault registers.                                                                                                    |  |  |  |

|                  | *State of ERCFLAG.UVLO, ERCFLAG.OVLO, and ERCFLAG.OTLO is preserved.                                                                                                     |  |  |  |

| 2                | IN voltage is above the UVLO threshold (V <sub>IN</sub> > V <sub>UVLO</sub> + V <sub>INUVLO</sub> HYS).                                                                  |  |  |  |

| _                | The device is waiting for a wake-up signal to power up the regulators.                                                                                                   |  |  |  |

|                  | I <sup>2</sup> C is enabled.                                                                                                                                             |  |  |  |

| Shutdown         | When EN = 0, active discharge immediately turns on and pulls all output voltages down to 0V.                                                                             |  |  |  |

|                  | *This is the lowest current state of the device (I <sub>SHDN</sub> ).                                                                                                    |  |  |  |

|                  | A wake-up signal has been received. Wake-up signals include:                                                                                                             |  |  |  |

| 3                | ● EN = 1 or                                                                                                                                                              |  |  |  |

| ·                | Setting CNFG_GLBL.FRC_IBB_ON or CNFG_GLBL.FRC_BST_ON or                                                                                                                  |  |  |  |

|                  | CNFG_GLBL.EN_BIAS register bit to 1                                                                                                                                      |  |  |  |

| Bias On          | Bias circuits (REF, I <sub>BIAS</sub> , OSC) and fault detection circuits (OVLO and OTLO) are enabled.                                                                   |  |  |  |

|                  | Inverting buck-boost and boost regulators are disabled.  Bias circuits are OK.                                                                                           |  |  |  |

| 4                | No faults detected: UVLO = 0, OVLO = 0, and OTLO = 0.                                                                                                                    |  |  |  |

| 7                | CNFG_GLBL.FRC_IBB_ON and CNFG_GLBL.FRC_BST_ON register bits are both 0.                                                                                                  |  |  |  |

| Power-Up Delay   | Start power-up counter                                                                                                                                                   |  |  |  |

| •                | Inverting buck-boost and boost regulator programmed power-up t <sub>DELAY</sub> reached. Set                                                                             |  |  |  |

| 5                | PU BST DONE = 1 and PU IBB DONE = 1.                                                                                                                                     |  |  |  |

| Resource On      | Buck-boost and boost regulator are enabled.                                                                                                                              |  |  |  |

| 11030dioc Oil    | Request to power down received. Software power-down enabled.                                                                                                             |  |  |  |

|                  | (EN = 0) and {(PU_DONE_BST = 1 and CNFG_GLBL.FRC_BST_ON = 0) or (PU_IBB_DONE                                                                                             |  |  |  |

|                  | = 1 and CNFG_GLBL.FRC_IBB_ON = 0)}                                                                                                                                       |  |  |  |

| 6A               | Boost powers down after t <sub>D BST</sub> . This is from when power-down request is received to                                                                         |  |  |  |

|                  | programmed t <sub>D_BST</sub> time.                                                                                                                                      |  |  |  |

|                  | Inverting buck-boost powers down after t <sub>D_IBB</sub> . This is from when power down request is                                                                      |  |  |  |

|                  | received to programmed t <sub>D_IBB</sub> time.                                                                                                                          |  |  |  |

|                  | Not transition 6A.                                                                                                                                                       |  |  |  |

|                  | (EN = 1) and {(PU_DONE_BST = 0 and CNFG_GLBL.FRC_BST_ON = 1) or (PU_IBB_DONE                                                                                             |  |  |  |

| 6B               | = 0 and CNFG_GLBL.FRC_IBB_ON = 1)}                                                                                                                                       |  |  |  |

|                  | This transition happens if CNFG_GLBL.FRC_BST_ON = 1 or CNFG_GLBL.FRC_IBB_ON = 1 and EN = 1 signal is received during the power-down delay time.                          |  |  |  |

|                  | If the transition occurs, the power-down delay counter is terminated and regulators remain on.                                                                           |  |  |  |

| D D D I          | Start power-down counter.                                                                                                                                                |  |  |  |

| Power-Down Delay | Note: Only resource that is on is powered down.                                                                                                                          |  |  |  |

| 7                | Buck-boost and boost regulator programmed power-down t <sub>DELAY</sub> reached.                                                                                         |  |  |  |

| 7                | Set PU_BST_DONE = 0 and PU_IBB_DONE = 0.                                                                                                                                 |  |  |  |

| 8                | nERR pin has been flagged. (From 1 to 0) while EN = 1 and both regulators are on.                                                                                        |  |  |  |

|                  | Regulators are disabled.                                                                                                                                                 |  |  |  |

|                  | Depending on the OTP, if the active discharge is disabled (CNFG_DCDC0.ADE_IBB and                                                                                        |  |  |  |

| ERROR            | CNFG_DCDC0.ADE_BST = 0 default), output regulators are in high-Z mode.                                                                                                   |  |  |  |

|                  | Depending on the OTP, if the active discharge is enabled, (CNFG_DCDC0.ADE_IBB and                                                                                        |  |  |  |

|                  | CNFG_DCDC0.ADE_BST = 1), output regulators discharge back to 0V.                                                                                                         |  |  |  |

| 9                | nERR pin output has been reset to 1 AND an I <sup>2</sup> C signal has been sent to reenable the negative buck-boost and boost regulators (CNFG GLBL.FORCE DIS bit = 0). |  |  |  |

|                  | Not transition 3.                                                                                                                                                        |  |  |  |

| 40               | The wake-up signal is no longer enabled, which causes the regulators to power down.                                                                                      |  |  |  |

| 10               | Neither the EN pin nor the following register bits (CNFG_GLBL.FRC_IBB_ON,                                                                                                |  |  |  |

|                  | CNFG_GLBL.FRC_BST_ON, and CNFG_GLBL.EN_BIAS) are set to 1.                                                                                                               |  |  |  |

| 11 | The boost or inverting buck-boost is forced on and no power-up delay is implemented.  CNFG_GLBL.FRC_IBB_ON = 1 or CNFG_GLBL.FRC_BST_ON = 1. Bias circuits are OK  No faults detected: UVLO = 0, OVLO = 0, and OTLO = 0.  Note:  CNFG_GLBL.FRC_IBB_ON = 1 clears PU_DONE_IBB.  CNFG_GLBL.FRC_BST_ON = 1 clears PU_DONE_BST. |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 | The boost or inverting buck-boost is forced off and no power-down delay is implemented.  (CNFG_GLBL.FRC_IBB_ON = 0 and PU_DONE_IBB = 0) and (CNFG_GLBL.FRC_IB_ON = 0 and PU_DONE_BST = 0)                                                                                                                                  |

### **Protection Features**

# **IN Overvoltage Lockout (OVLO)**

The overvoltage protection feature ensures that the input voltage  $V_{IN}$  never exceeds the overvoltage limit threshold  $(V_{OVLO})$ . When  $V_{IN}$  rises up to  $V_{OVLO}$ , the device detects the overvoltage, sets the ERCFLAG.OVLO bit, and activates the overvoltage lockout by disabling all the regulators.

## IN Undervoltage Lockout (UVLO)

The undervoltage lockout feature prevents operation in abnormal input conditions when the input voltage  $V_{IN}$  falls below the UVLO falling voltage  $(V_{UVLO\_F})$ . Regardless of the EN pin status, the device is disabled, and all registers are reset until  $V_{IN}$  rises above the UVLO rising threshold  $(V_{UVIO\_R})$ .

### Overtemperature Lockout (OTLO)

The MAX77720 has a on-chip thermal sensor to monitor overtemperature conditions. The thermal overtemperature lockout alarm generates an ERCFLAG.OTLO signal when the junction temperature exceeds the overtemperature lockout specification (see T<sub>OTLO</sub> in. *Electrical Characteristics—Global Resources*. When OTLO is asserted, the system resets which disables all functions of the MAX77720. Once all functions are disabled, a wake-up event is required to turn the MAX77720 on again. To wake up the MAX77720 after a overtemperature lockout condition, the junction temperature must be below T<sub>OTLO</sub> - T<sub>OTLO</sub><sub>HYS</sub>. If a wake-up event turns the MAX77720 on when the junction temperature is still above T<sub>OTLO</sub> - T<sub>OTLO</sub><sub>HYS</sub>, the MAX77720 promptly forces system reset which disables all functions again. The host can check if a overtemperature lockout condition occurred by reading the ERCFLAG.OTLO flag.

#### Overcurrent Protection (OCP)

The MAX77720 limits the inductor peak current limit for both the inverting buck-boost and boost converter. The MAX77720 allows an inductor current limit of  $I_{BB\ ILIM}$  (1.5A typical) on the inverting buck-boost converter.

For the boost converter, there are four inductor peak current limit options (see I<sub>BST\_ILIM</sub> in <u>Electrical Characteristics—Boost Regulator</u> section). The boost inductor peak current limit is programmable at the bitfield CNFG\_IBB0.IPK\_BST. This allows for flexibility in designing for higher load-current applications or for more compact designs when less power is needed. Note that the currents listed above are peak inductor currents and not output load currents.

If the lowest boost inductor peak current limit is used (CNFG\_DCDC0.IPK\_BST = 0x3), the regulator operates in discontinuous mode (DCM) only, and OCP sets if the output voltage is below target when the inductor current reaches 0A. *Figure 8* shows a diagram of when the OCP sets for this condition.

Figure 8. OCP Conditions for the Boost Converter when IPK\_BST = 0x3

Additionally, the MAX77720 includes dedicated status, interrupt, and mask register bits. This is used to monitor overcurrent conditions and to notify application processors or microcontroller units of whether an overcurrent condition occurred (interrupt flag) and is still occurring (status flag). These bits can be found in the Register Map section under INT GLBL0, INTM GLBL0, and STAT GLBL.

### **Output Short-Circuit Protection (SCP)**

The MAX77720 has a short-circuit protection for the inverting buck-boost converter and boost converter.

For the inverting buck-boost converter, the output voltage is considered short-circuited if it is 40% of the target output voltage. If a short circuit is detected, the regulator disables after 10µs along with the status and interrupt bits reflecting the short circuit on the inverting buck-boost converter (INT\_GLBL0.IBB\_SCP = 1 and STAT\_GLBL.IBB\_SCP = 1). *Figure* 9 shows the timing of the short-circuit protection implementation for the inverting buck-boost regulator.

Figure 9. IBB Short-Circuit Protection Timing Diagram

For the boost converter, the output voltage is considered short-circuited if  $V_{OUTBST} < V_{IN}$ . If a short-circuit is detected, the regulator disables after 10 $\mu$ s along with the status and interrupt bits reflecting the short circuit on the boost converter (INT\_GLBL0.BST\_SCP = 1 and STAT\_GLBL.BST\_SCP = 1). <u>Figure 10</u> shows the timing of the short-circuit protection implementation for the boost regulator.

Figure 10. BST Short-Circuit Protection Timing Diagram

Additionally, the MAX77720 includes a dedicated status, interrupt, and mask register bits for monitoring the short-circuit conditions for each individual regulator. This is used to help monitor short-circuit conditions and to notify application processors or microcontroller units of whether a short-circuit condition occurred (interrupt flag) and is still occurring (status flag). These bits can be found in the Register Map section under INT\_GLBL0, INTM\_GLBL0, and STAT\_GLBL.

To re-enable the regulators after a short-circuit condition, set the EN pin low, wait for the power-down delay time (see the <u>Power-Up/Power-Down</u> section), then set the EN pin high again. <u>Figure 11</u> shows how to re-enable the regulators as described above if a short circuit occurs on the inverting buck-boost regulator. Note that if CNFG\_GLBL.FRC\_IBB\_ON = 1 or CNFG\_GLBL.FRC\_BST\_ON = 1, a regulator can be enabled without waiting for the power-down delay time after a short-circuit event occurs.

Figure 11. IBB Short-Circuit Protection Re-Enabling Timing Diagram

# **Detailed Description—Inverting Buck-Boost Converter**

The asynchronous, inverting buck-boost converter generates a negative output voltage in two output voltage ranges: from -17.01V to -24.00V and from -17.00V to -10.01V, programmable through I<sup>2</sup>C. It is recommended that the inverting buck-boost converter is disabled before changing between output voltage ranges.

#### **Inverting Buck-Boost Functional Modes**

The MAX77720 inverting buck-boost converter operates in two functional modes: skip mode and PWM mode.

#### Skip Mode

The MAX77720 inverting buck-boost converter automatically enters skip mode at no load or light load conditions to improve efficiency. During this mode, the high-side MOSFET skips on pulses when the error amplifier output voltage is less than the target skip threshold. The target skip threshold determines the peak inductor current (400mA typ).

#### **PWM Mode**

The MAX77720 inverting buck-boost converter uses a peak current-mode control architecture with internal loop compensation at a 1.5MHz switching frequency pulse-width modulation. At the rising edge of each clock, the high-side MOSFET turns on and the inductor current ramps up. An internal error amplifier integrates the error between a fraction of the output voltage at the FBIBB pin and an internal reference. To program the duty cycle of the regulator, the output of the error amplifier sets the peak current in the inductor at which the high-side MOSFET turns off. Once the MOSFET turns off, the current in the inductor discharges the negative voltage rail (V<sub>OUT\_IBB</sub>) through the external Schottky diode. The inductor current continues to discharge V<sub>OUT\_IBB</sub> until the inductor current reaches zero or when the next rising clock edge is received.

#### **Programming the Inverting Buck-Boost Output Voltage**

The MAX77720 configures the inverting buck-boost output voltage through  $I^2C$ . The target output voltage is between -10.01V and -17.00V in 15mV steps, while the range bit is high (CNFG\_DCDC0.RNGIBB = 1). See <u>Table 5</u> for a summary of programmable voltage ranges and step sizes.

| Table 5. | Inverting | <b>Buck-Boost</b> ( | Output-Voltag | ge Range |

|----------|-----------|---------------------|---------------|----------|

|          |           |                     |               |          |

| RANGE BIT                             | VIBB_RNG PROGRAMMABLE VOLTAGE<br>RANGE (V) | VOLTAGE STEP PER LSB (mV) |

|---------------------------------------|--------------------------------------------|---------------------------|

| Low Range<br>(CNFG_DCDC0.RNGIBB = 0)  | -17.01 to -24.00                           | 15                        |