Click here to ask an associate for production status of specific part numbers.

### **MAX31888**

## ±0.25°C Accurate 1-Wire® Temperature Sensor

## **General Description**

The MAX31888 is a 1-Wire high precision, low power digital temperature sensor with  $\pm 0.25^{\circ}$ C accuracy from -20°C to +105°C for precision temperature monitoring. The MAX31888 operates at  $68\mu$ A operating current during measurement and has 16-bit resolution (0.005°C).

The sensor communicates with a microcontroller over a 1-Wire® bus that requires only one data line (and a ground reference) for communication. In addition, the sensor can derive power directly from the data line through "parasite power", eliminating the need for an external power supply. Each MAX31888 has its own unique 64-bit registration number that is factory programmed into the chip. This unique 64-bit registration number acts as the node address in the case of a multi-drop 1-Wire® network. In multi-drop networks, optional GPIO pins can be used as address bits to identify each device's physical location.

The MAX31888 is available in a 6-pin uDFN package. The power supply voltage range is from 1.7V to 3.6V for external power supplies. The operating temperature range is from -40°C to +125°C.

## **Applications**

- Precision Temperature Monitoring

- RTD Replacement

- Internet of Things (IoT) Sensors

- Cold Chain

#### **Benefits and Features**

- High Accuracy and Precision

- ±0.25°C Accuracy from -20°C to +105°C

- ±0.65°C Accuracy from -40°C to +125°C

- Long Battery Life

- 1.7V to 3.6V Operating Voltage

- 68µA Operating Current During Measurement

- 0.6µA Standby Current

- Small Size

- 2mm x 2mm x 0.8mm, 6-Pin μDFN

- Safety and Compliance

- Unique ROM IDs Allow Device to be NIST Traceable

- High and Low Temperature Alarms

- · Simple and Robust Digital Interface

- 1-Wire® Interface

- · CRC (Cyclic Redundancy Check)

- · Multi-Drop Capability

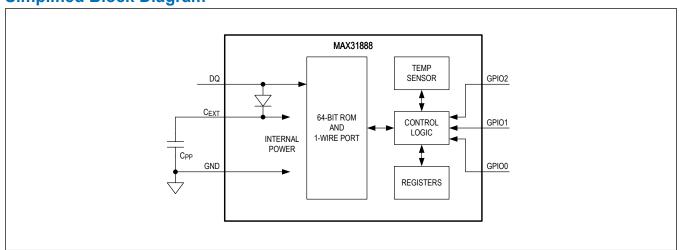

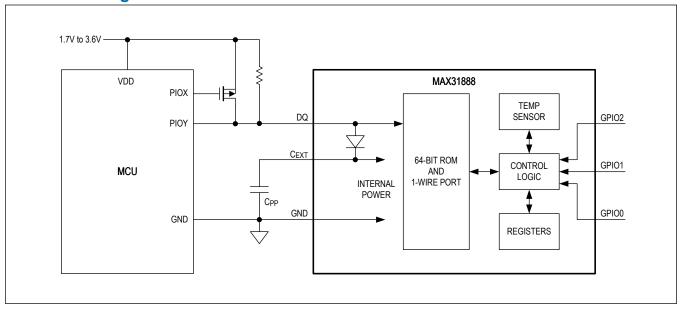

## Simplified Block Diagram

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

Ordering Information appears at end of data sheet.

19-101243; Rev 1; 8/23

© 2023 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

## **TABLE OF CONTENTS**

| General Description                                  | 1  |

|------------------------------------------------------|----|

| Applications                                         |    |

| Benefits and Features                                |    |

| Simplified Block Diagram                             |    |

| Absolute Maximum Ratings                             |    |

| Package Information                                  |    |

| μDFN                                                 |    |

| Electrical Characteristics                           |    |

| Typical Operating Characteristics                    |    |

| Pin Configuration                                    |    |

| MAX31888                                             |    |

| Pin Description                                      |    |

| Functional Diagrams                                  |    |

| Detailed Description                                 |    |

| Operation                                            |    |

| Measuring Temperature                                |    |

| Alarm Signaling                                      |    |

| GPIO                                                 | 14 |

| 1-Wire Bus System                                    | 15 |

| Transaction Sequence                                 | 15 |

| Initialization.                                      | 16 |

| ROM Commands                                         | 16 |

| Search ROM [0xF0]                                    | 16 |

| Read ROM [0x33]                                      | 16 |

| Match ROM [0x55]                                     | 16 |

| Skip ROM [0xCC]                                      | 16 |

| Alarm Search [0xEC]                                  | 16 |

| Resume ROM [0xA5]                                    | 17 |

| Overdrive Skip ROM [0x3C]                            | 17 |

| Overdrive Match ROM [0x69]                           | 17 |

| Function Commands                                    | 17 |

| Convert T [0x44]                                     | 18 |

| Write Register [0xCC]                                | 19 |

| Read Register [0x33]                                 | 19 |

| Soft Reset [0x82]                                    | 19 |

| 1-Wire Signaling                                     | 19 |

| Initialization Procedure: Reset and Presence Pulses. | 20 |

| Read/Write Time Slots                                | 20 |

| Master-to-Slave                                      | 20 |

## TABLE OF CONTENTS (CONTINUED)

| Slave-to-Master                                                           | 21 |

|---------------------------------------------------------------------------|----|

| Parasite Power                                                            | 22 |

| 64-Bit OTP ROM Code                                                       | 23 |

| Registers                                                                 | 23 |

| CRC Generation                                                            | 23 |

| 8-Bit CRC for ROM Code                                                    | 24 |

| 16-Bit CRC for 1-Wire Device Function Commands                            | 24 |

| Operation Examples                                                        | 25 |

| Example 1                                                                 | 25 |

| Example 2                                                                 | 26 |

| FIFO Description                                                          | 26 |

| Register Map                                                              | 30 |

| Register Map                                                              | 30 |

| Register Details                                                          | 31 |

| Applications Information                                                  |    |

| Measurement Considerations                                                |    |

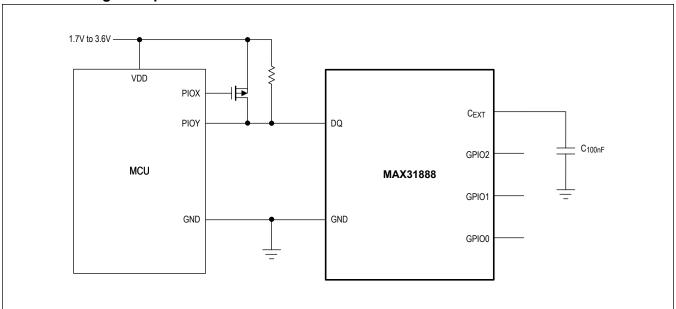

| Typical Application Circuit                                               |    |

| MAX31888 Single-Drop                                                      |    |

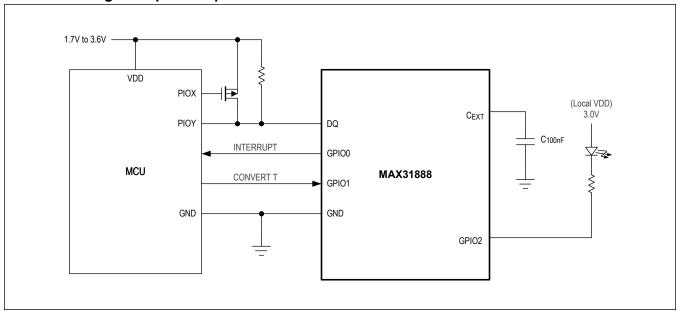

| MAX31888 Single-Drop With Special Functions                               | 40 |

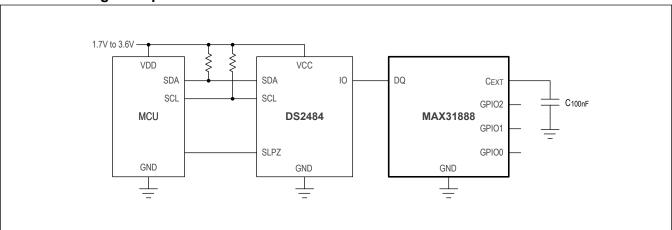

| MAX31888 Single-Drop With 1-Wire Master                                   | 40 |

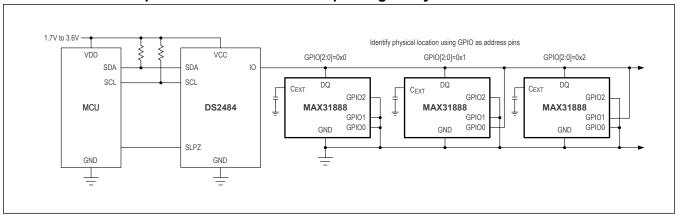

| MAX31888 Multi-Drop With 1-Wire Master and up to Eight Physical Locations | 41 |

| Ordering Information                                                      | 41 |

| Revision History                                                          | 42 |

## **LIST OF FIGURES**

| Figure 1. Temperature Data Register Format                                               | 13 |

|------------------------------------------------------------------------------------------|----|

| Figure 2. Alarm Threshold Register Format                                                | 14 |

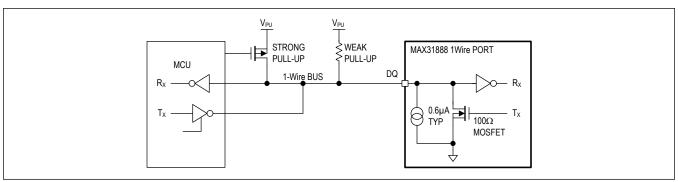

| Figure 3. Simplified Diagram of the 1-Wire Port                                          | 15 |

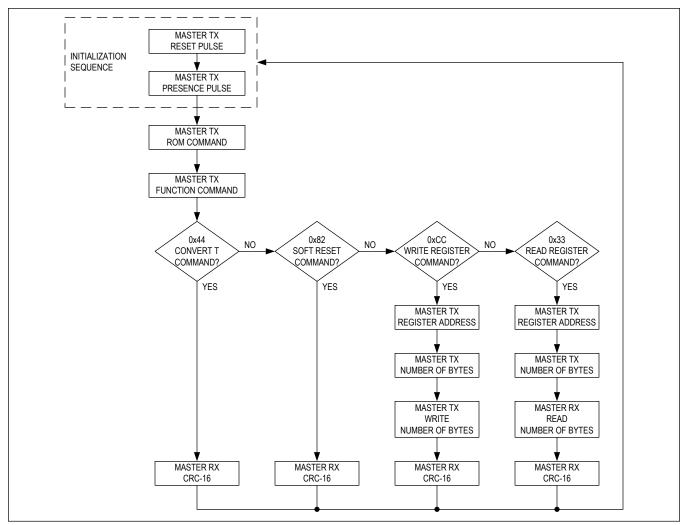

| Figure 4. The Function Command Execution Procedure                                       | 18 |

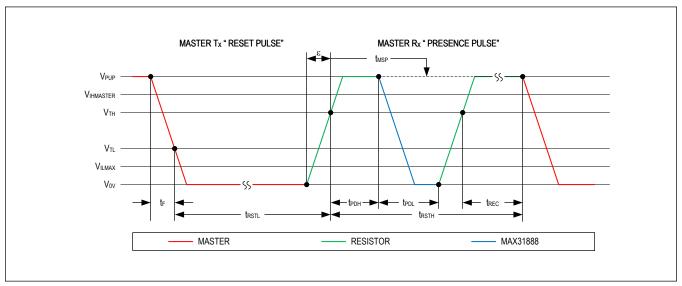

| Figure 5. 1-Wire Initialization Sequence                                                 | 20 |

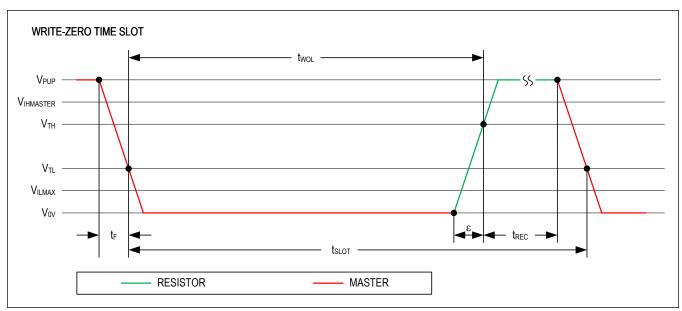

| Figure 6. Master Write 0 Timing                                                          | 21 |

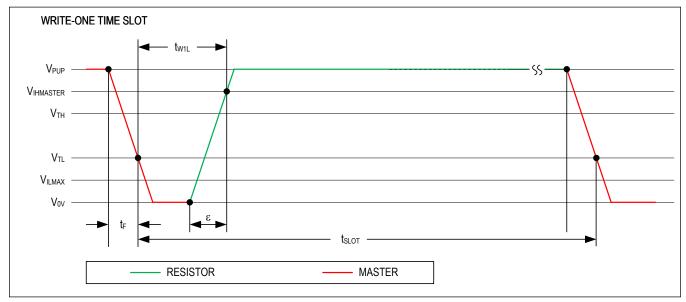

| Figure 7. Master Write 1 Timing                                                          | 21 |

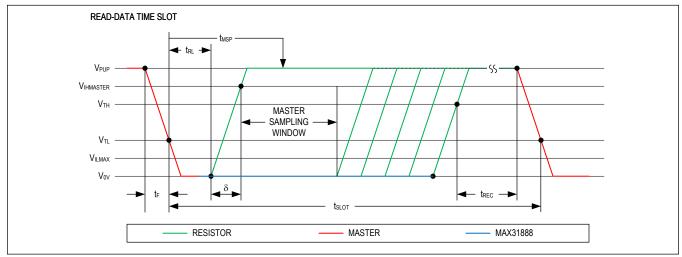

| Figure 8. Master Read Data Timing                                                        | 22 |

| Figure 9. Providing a Strong Pullup to Power the MAX31888 During Temperature Conversions | 23 |

| Figure 10. MAX31888 ROM Structure                                                        | 23 |

| Figure 11. 8-bit CRC State Machine                                                       | 24 |

| Figure 12. 16-bit CRC State Machine                                                      | 25 |

# LIST OF TABLES

| Table 1. 16-bit Temperature Data Format        |    |

|------------------------------------------------|----|

| Table 2. GPIO Mode Functions                   | 14 |

| Table 3. Summary of MAX31888 Function Commands | 17 |

| Table 4. FIFO Register Map                     | 26 |

| Table 5. Temperature FIFO Data Format          | 27 |

| Table 6. FIFO Data Read Format                 | 28 |

## **Absolute Maximum Ratings**

| DQ to GND0.3V to +6V                                                           | Operating Temperature Range40°C to 125°C |

|--------------------------------------------------------------------------------|------------------------------------------|

| CEXT to GND0.3V to +6V                                                         | Junction Temperature+150°C               |

| GPIOx to GND0.3V to +6V                                                        | Storage Temperature Range65°C to +150°C  |

| DQ Sink Current±20mA                                                           | Lead Temperature (soldering, 10s)+300°C  |

| Continuous Power Dissipation (Multilayer Board $\mu$ DFN, T <sub>A</sub> = +70 | Soldering Temperature (reflow)+260°C     |

| °C, derate 5.47mW/°C above 70°C )437.25mW/°C                                   |                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### μ**DFN**

| <u>-</u>                               |                  |  |  |  |  |

|----------------------------------------|------------------|--|--|--|--|

| Package Code                           | L622+2           |  |  |  |  |

| Outline Number                         | <u>21-100397</u> |  |  |  |  |

| Land Pattern Number                    | <u>90-100138</u> |  |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                  |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 182.96°C/W       |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 50.75°C/W        |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(DQ = 1.8V,  $T_A$  = +25°C, minimum and maximum limits are from  $T_A$  = -40°C to +125°C, unless otherwise noted. (Note 1))

| PARAMETER                          | SYMBOL            | CONDITIONS                    |                             | MIN   | TYP   | MAX   | UNITS          |  |  |

|------------------------------------|-------------------|-------------------------------|-----------------------------|-------|-------|-------|----------------|--|--|

| TEMPERATURE SENSOR                 |                   |                               |                             |       |       |       |                |  |  |

| Temperature<br>Measurement Error   |                   |                               | -20°C to +105°C,<br>3-sigma | -0.25 |       | +0.25 | - °C           |  |  |

|                                    |                   | DQ = 1.7V to 3.6V             | -20°C to +105°C,<br>6-sigma | -0.45 |       | +0.45 |                |  |  |

|                                    |                   | DQ = 1.7V to 3.6V             | -40°C to +125°C,<br>3-sigma | -0.65 |       | +0.65 |                |  |  |

|                                    |                   |                               | -40°C to +125°C,<br>6-sigma | -0.9  |       | +0.9  |                |  |  |

| Resolution                         |                   | 16-Bit                        |                             |       | 0.005 |       | °C             |  |  |

| Repeatability                      |                   | DQ = 1.7V to 3.6V             | DQ = 1.7V to 3.6V           |       | 0.008 |       | °C RMS         |  |  |

| Conversion Time                    | t <sub>CONV</sub> | 16-bit                        | 16-bit                      |       | 16.5  | 17.85 | ms             |  |  |

| Long-Term Stability                |                   | T <sub>A</sub> = +70°C, 0% RH |                             |       | 0.015 |       | °C/<br>1000hrs |  |  |

| Operating Supply Voltage           | DQ                | Guaranteed by PSRR            |                             | 1.7   |       | 3.6   | V              |  |  |

| DC Power Supply<br>Rejection Ratio | PSRR              | T <sub>A</sub> = +25°C        |                             |       | 0.006 |       | °C/V           |  |  |

## **Electrical Characteristics (continued)**

(DQ = 1.8V,  $T_A$  = +25°C, minimum and maximum limits are from  $T_A$  = -40°C to +125°C, unless otherwise noted. (Note 1))

| PARAMETER                        | SYMBOL                 | COND                                                                      | ITIONS                                | MIN                        | TYP                        | MAX  | UNITS |

|----------------------------------|------------------------|---------------------------------------------------------------------------|---------------------------------------|----------------------------|----------------------------|------|-------|

|                                  |                        | During Conversion,<br>DQ = 1.8V                                           | T <sub>A</sub> = +25°C                |                            | 67                         | 105  |       |

| Operating Current                |                        | During Conversion,<br>DQ = 3.6V                                           | T <sub>A</sub> = +25°C                |                            | 68                         | 105  | μΑ    |

|                                  |                        | During Conversion,                                                        | T <sub>A</sub> = +85°C                |                            | 70                         | 110  |       |

|                                  |                        | DQ = 1.7V to 3.6V                                                         | T <sub>A</sub> = +125°C               |                            | 87                         | 140  |       |

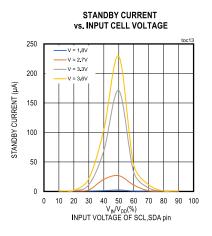

|                                  |                        |                                                                           | T <sub>A</sub> = +25°C                |                            | 0.6                        | 3    |       |

| Standby Current                  |                        | DQ = 3.6V                                                                 | T <sub>A</sub> = +85°C                |                            | 3.5                        | 10   | μΑ    |

|                                  |                        |                                                                           | T <sub>A</sub> = +125°C               |                            | 15                         | 38   |       |

| 1-Wire / DQ PIN GENERA           | AL DATA                |                                                                           |                                       |                            |                            |      |       |

| 1-Wire Pullup Voltage            | V <sub>PUP</sub>       | Note 2                                                                    |                                       | 1.7                        |                            | 3.6  | V     |

| 1-Wire Pullup<br>Resistance      | R <sub>PUP</sub>       | (Note 2, 3)                                                               |                                       | 300                        |                            | 1000 | Ω     |

| Input Capacitance                | C <sub>DQ</sub>        | (Note 3, 4)                                                               |                                       |                            | 100                        |      | pF    |

| High to Low Switching Threshold  | V <sub>TL</sub>        | (Notes 5, 6, 7)                                                           |                                       |                            | 0.65 x<br>V <sub>PUP</sub> |      | V     |

| Input Low Voltage                | V <sub>IL</sub>        | (Notes 2, 8)                                                              |                                       |                            | 0.15 x<br>V <sub>PUP</sub> | V    |       |

| Low to High Switching Threshold  | V <sub>TH</sub>        | (Notes 5, 6, 9)                                                           |                                       | 0.75 x<br>V <sub>PUP</sub> |                            | ٧    |       |

| Switching Hysteresis             | V <sub>HY</sub>        | (Notes 5, 6, 10)                                                          |                                       | 0.3                        |                            | V    |       |

| Output Low Voltage               | V <sub>OL</sub>        | At 4mA current load (Note 11)                                             |                                       |                            |                            | 0.4  | V     |

| Recovery Time                    | t <sub>REC</sub>       | $R_{PUP}$ = 750Ω and single device attached to a 1-Wire line (Note 2, 12) |                                       | 5                          |                            |      | μs    |

| Time Slot Duration (Notes 2, 13) |                        | (Note 3)                                                                  |                                       |                            | t <sub>W0L</sub> +         |      | μs    |

| 1-Wire / DQ PIN 1-Wire R         | RESET, PRESEN          | ICE DETECT CYCLE                                                          |                                       |                            |                            |      |       |

| Reset Low Time (Notes            |                        | Standard Speed                                                            |                                       | 480                        |                            | 640  |       |

| 2)                               | <sup>t</sup> RSTL      | Overdrive Speed                                                           |                                       | 48                         |                            | 80   | μs    |

| Reset High Time (Note            | <b>4</b>               | Standard Speed                                                            |                                       | 480                        |                            |      |       |

| 15)                              | trsth                  | Overdrive Speed                                                           |                                       | 48                         |                            |      | μs    |

| Presence Detect High             | High Standard Speed 15 |                                                                           |                                       | 60                         | 110                        |      |       |

| Time                             | t <sub>PDH</sub>       | Overdrive Speed                                                           |                                       | 2                          |                            | 6    | μs    |

| Presence Detect Low              |                        | Standard Speed                                                            |                                       | 60                         |                            | 240  | 110   |

| Time                             | t <sub>PDL</sub>       | Overdrive Speed                                                           |                                       | 8                          |                            | 24   | μs    |

| Presence Detect                  |                        | Standard Speed                                                            |                                       | 60                         |                            | 75   |       |

| Sample Time (Notes 2, 16)        | t <sub>MSP</sub>       | Overdrive Speed                                                           | · · · · · · · · · · · · · · · · · · · |                            |                            | 10   | μs    |

| 1-Wire / DQ PIN 1-Wire V         | VRITE                  |                                                                           |                                       |                            |                            |      |       |

| Write-Zero Low Time              | t <sub>WOL</sub>       | Standard Speed                                                            |                                       | 60                         |                            | 120  | μs    |

| (Notes 2, 17)                    | -WOL                   | Overdrive Speed                                                           |                                       | 6                          |                            | 15.5 | P     |

## **Electrical Characteristics (continued)**

(DQ = 1.8V,  $T_A$  = +25°C, minimum and maximum limits are from  $T_A$  = -40°C to +125°C, unless otherwise noted. (Note 1))

| PARAMETER                | SYMBOL                      | CONDITIONS                                   | MIN                 | TYP  | MAX    | UNITS                                    |  |  |  |  |

|--------------------------|-----------------------------|----------------------------------------------|---------------------|------|--------|------------------------------------------|--|--|--|--|

| Write-One Low Time       | 4                           | Standard Speed                               | 0.25                |      | 15     |                                          |  |  |  |  |

| (Notes 2, 17)            | t <sub>W1L</sub>            | Overdrive Speed                              | 0.25                |      | 2      | μs                                       |  |  |  |  |

| 1-Wire / DQ PIN 1-Wire F | 1-Wire / DQ PIN 1-Wire READ |                                              |                     |      |        |                                          |  |  |  |  |

| Read Low Time (Notes     |                             | Standard Speed                               | 0.25                |      | 15 - δ |                                          |  |  |  |  |

| 2, 18)                   | t <sub>RL</sub>             | Overdrive Speed                              | 0.25                |      | 2 - δ  | ря р |  |  |  |  |

| Read Sample Time         | 1                           | Standard Speed                               | t <sub>RL</sub> + δ |      | 15     |                                          |  |  |  |  |

| (Notes 2, 18)            |                             | Overdrive Speed                              | t <sub>RL</sub> + δ |      | 2      | μs                                       |  |  |  |  |

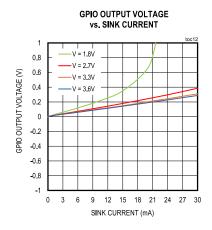

| GPIO PINS                | •                           |                                              | •                   |      |        |                                          |  |  |  |  |

| Input Voltage Low        | V <sub>IL_GPIO</sub>        |                                              |                     |      | 0.4    | V                                        |  |  |  |  |

| Input Voltage High       | V <sub>IH_GPIO</sub>        |                                              | 1.4                 |      |        | V                                        |  |  |  |  |

| Input Hysteresis         | V <sub>HYS_GPIO</sub>       |                                              |                     | 320  |        | mV                                       |  |  |  |  |

| Input Leakage Current    | I <sub>IN_GPIO</sub>        | V <sub>IN</sub> = 0V, T <sub>A</sub> = +25°C |                     | 0.01 | 1      | μA                                       |  |  |  |  |

| Input Capacitance        | C <sub>IN_GPIO</sub>        |                                              |                     | 10   |        | pF                                       |  |  |  |  |

| Input Low Pulse Width    |                             |                                              | 5                   |      |        | μs                                       |  |  |  |  |

| Output Low Voltage       | V <sub>OL_GPIO</sub>        | I <sub>SINK</sub> = 2mA                      |                     |      | 0.4    | V                                        |  |  |  |  |

- Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over temperature limits are guaranteed by design and characterization.

- Note 2: For design guidance only. Not production tested.

- **Note 3:** System requirement. The Pullup Voltage specification assumes that the pullup device is ideal, and therefore the high level of the pullup is equal to V<sub>PUP</sub>. The actual supply rail for the strong pullup mode must include a margin for the voltage drop across the strong pullup transistor.

- **Note 4:** Maximum allowable pullup resistance is a function of the number of 1-Wire devices in the system and 1-Wire recovery times. The specified value here applies to systems with only one device and with the minimum 1-Wire recovery times.

- Note 5: Maximum value represents the internal parasite capacitance when VPUP is first applied. Once the parasite capacitance is charged, it does not affect normal communication

- Note 6: Guaranteed by design, characterization, and/or simulation only. Not production tested.

- Note 7: V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub> are a function of the internal supply voltage, which is a function of V<sub>PUP</sub>, R<sub>PUP</sub>, 1-Wire timing, and capacitive loading on DQ. Lower V<sub>PUP</sub>, higher R<sub>PUP</sub>, shorter t<sub>REC</sub>, and heavier capacitive loading all lead to lower values of V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub>.

- Note 8: Voltage below which, during a falling edge on DQ, a logic 0 is detected.

- Note 9: The voltage on DQ must be less than or equal to V<sub>ILMAX</sub> at all times the master is driving DQ to a logic 0 level.

- Note 10: Voltage above which, during a rising edge on DQ, a logic 1 is detected.

- Note 11: After V<sub>TH</sub> is crossed during a rising edge on DQ, the voltage on DQ must drop by at least V<sub>HY</sub> to be detected as logic 0.

- Note 12: The I-V characteristic is linear for voltages less than 1V.

- Note 13: Applies to a single device attached to a 1-Wire line.

- Note 14: Defines maximum possible bit rate. Equal to  $1/(t_{W0LMIN} + t_{RECMIN})$ .

- Note 15: An additional reset or communication sequence cannot begin until the reset high time has expired.

- Note 16: Interval after t<sub>RSTL</sub> during which a bus master can read a logic 0 on DQ if there is a MAX31888 present. The power-up presence detect pulse could be outside this interval but will be complete within 2ms after power-up.

- Note 17:  $\epsilon$ , defined in the 1-Wire Signaling section, represents the time required for the pullup circuitry to pull the voltage on DQ up from  $V_{IL}$  to  $V_{TH}$ . The actual maximum duration for the master to pull the line low is  $t_{W1L}(MAX) + t_F \epsilon$  and  $t_{W0L}(MAX) + t_F \epsilon$ , respectively.

- Note 18: δ, defined in the 1-Wire Signaling section, represents the time required for the pullup circuitry to pull the voltage on DQ up from V<sub>IL</sub> to the input-high threshold of the bus master. The actual maximum duration for the master to pull the line low is t<sub>RLMAX</sub> + t<sub>F</sub>.

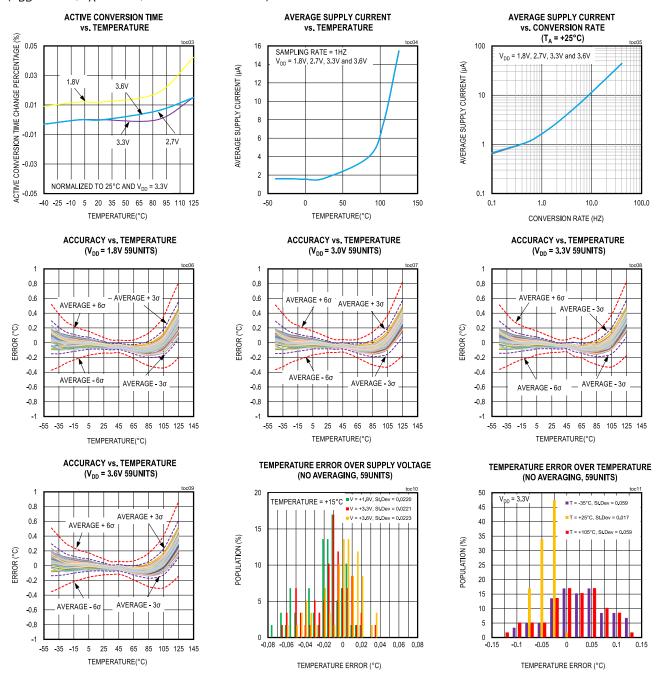

## **Typical Operating Characteristics**

$(V_{DD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

$(V_{DD} = +1.8V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

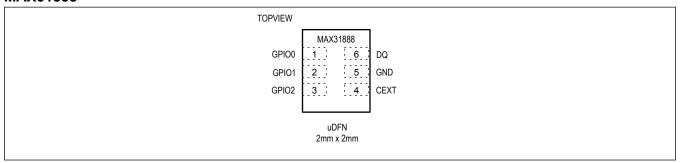

## **Pin Configuration**

### **MAX31888**

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                               |

|-----|-------|------------------------------------------------------------------------------------------------------------------------|

| 1   | GPIO0 | General Purpose Input/Output 0. Programmable digital input or output.                                                  |

| 2   | GPIO1 | General Purpose Input/Output 1. Programmable digital input or output.                                                  |

| 3   | GPIO2 | General Purpose Input/Output 2. Programmable digital input or output.                                                  |

| 4   | CEXT  | External Parasitic Power Supply. Connect 0.1µF ceramic capacitor between CEXT and GND.                                 |

| 5   | GND   | Ground                                                                                                                 |

| 6   | DQ    | 1-Wire Bus Interface. Open-drain signal. Requires an external pullup resistor. Data interface and power to the device. |

## **Functional Diagrams**

## **Detailed Description**

The MAX31888 temperature sensor provides 13-bit to 16-bit Celsius temperature measurements with excellent accuracy over a wide temperature range. It communicates over a 1-Wire bus that requires only one data line and ground for communication with a microcontroller. In addition, the MAX31888 derives power directly from the data line using parasite power, eliminating the need for an external power supply.

Each device has a unique 64-bit serial code, allowing multiple MAX31888 devices to function on the same 1-Wire bus. Therefore, it is simple to use one microcontroller to control many devices distributed over a large area. The 64-bit ROM stores each sensor's unique serial code. The memory mapped registers contain a data FIFO storing up to 32 measurement results from the temperature sensor. In addition, the 2-byte high alarm trigger and 2-byte low alarm trigger registers (AH and AL) allow trip thresholds to be set for detection of temperature excursions beyond predetermined boundaries. The configuration register allows the user to set the resolution of the temperature-to-digital conversion to 13, 14, 15, or 16 bits. The AH, AL, and configuration registers are volatile, so they don't retain data when the device is powered down.

The 1-Wire bus protocol implements bus communication using one control line. The control line requires a weak pullup resistor since all devices are linked to the bus through a three-state or open-drain port (i.e., the MAX31888's DQ pin). In this bus system, the microcontroller (the master device) identifies and addresses devices on the bus using each device's unique 64-bit code. Because each device has a unique code, the number of devices that can be addressed on one bus is virtually unlimited. The 1-Wire bus protocol, including detailed explanations of the commands and time slots, is covered in the 1-Wire Bus System section. Additionally, the GPIO pins can be configured as digital inputs, outputs or special functions. When configured as digital inputs, they can be used as address bits to provide location information to the master device. This is achieved by connecting each GPIO pin to the DQ or GND pins locally to provide a unique set of "location bits".

The device operates without an external power supply. Power is supplied through the 1-Wire pullup resistor through the DQ pin when the bus is high. The high bus signal also charges an external capacitor (C<sub>PP</sub>), which then supplies power to the device when the bus is low. This method of deriving power from the 1-Wire bus is referred to as "parasite power."

### Operation

#### **Measuring Temperature**

The device's core functionality is its direct-to-digital temperature sensor. The device powers up in a low-power standby state. There are two ways to initiate a temperature measurement. The master can write a "1" to the CONVERT\_T bit in the TEMP\_SENSOR\_SETUP [0x14] register or set GPIO1 as an active low convert trigger to allow temperature conversions to be triggered by an external signal. Following the conversion, the resulting temperature sensor data is stored in the FIFO memory as a 2-byte temperature word and the device returns to the standby state.

The output temperature data is calibrated in degrees Celsius. The temperature data is stored as a left-justified, 16-bit sign-extended two's complement number in the FIFO Data register (see <u>Figure 1</u>). The data is two's complement where the MSB indicates the sign of the temperature, with an MSB of 1 indicating a negative temperature and an MSB of 0 indicating a positive temperature.

To calculate the temperature from the measurement data, convert the two's complement value to the decimal value and use the following equation for 16-bit resolution.

T = Decimal Value x 0.005

For example, if the result is 0x1CE8, convert to decimal to get 7400, then T = 7400 x 0.005, or  $37^{\circ}C$ . Table 1 gives examples of digital output data and the corresponding temperature reading.

|     | TEMPERATURE DA | ATA REGISTER FOR | RMAT  |       |       |       |      |      |

|-----|----------------|------------------|-------|-------|-------|-------|------|------|

|     | Bit15          | Bit14            | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 |

| MSB | T15            | T14              | T13   | T12   | T11   | T10   | Т9   | Т8   |

|     | Bit7           | Bit6             | Bit5  | Bit4  | Bit3  | Bit2  | Bit1 | Bit0 |

| LSB | T7             | T6               | T5    | T4    | Т3    | T2    | T1   | ТО   |

Figure 1. Temperature Data Register Format

## **Table 1. 16-bit Temperature Data Format**

| TEMPERATURE (°C) | DIGITAL OUTPUT (BINARY) | DIGITAL<br>OUTPUT (HEX) | DIGITAL OUTPUT (DEC) |

|------------------|-------------------------|-------------------------|----------------------|

| +125             | 0110 0001 1010 1000     | 61A8                    | 25000                |

| +100             | 0100 1110 0010 0000     | 4E20                    | 20000                |

| +85              | 0100 0010 0110 1000     | 4268                    | 17000                |

| +70              | 0011 0110 1011 0000     | 36B0                    | 14,000               |

| +50              | 0010 0111 0001 0000     | 2710                    | 10,000               |

| +41              | 0010 0000 0000 1000     | 2008                    | 8,200                |

| +37              | 0001 1100 1110 1000     | 1CE8                    | 7,400                |

| +35.8            | 0001 1011 1111 1000     | 1BF8                    | 7,160                |

| +25              | 0001 0011 1000 1000     | 1388                    | 5,000                |

| +15              | 0000 1011 1011 1000     | 0BB8                    | 3,000                |

| +0.04            | 0000 0000 0000 1000     | 8000                    | 8                    |

| +0.02            | 0000 0000 0000 0100     | 0004                    | 4                    |

| +0.01            | 0000 0000 0000 0010     | 0002                    | 2                    |

| +0.005           | 0000 0000 0000 0001     | 0001                    | 1                    |

| 0                | 0000 0000 0000 0000     | 0000                    | 0                    |

| -0.005           | 1111 1111 1111 1111     | FFFF                    | -1                   |

| -0.01            | 1111 1111 1111 1110     | FFFE                    | -2                   |

| -0.02            | 1111 1111 1111 1100     | FFFC                    | -4                   |

| -0.04            | 1111 1111 1111 1000     | FFF8                    | -8                   |

| -20              | 1111 0000 0110 0000     | F060                    | -4000                |

| -40              | 1110 0000 1100 0000     | E0C0                    | -8000                |

### **Alarm Signaling**

After the device performs a temperature conversion, the temperature value is compared with the user-defined two's complement alarm trigger values stored in the 2-byte Alarm High and 2-byte Alarm Low registers (see <u>Figure 2</u>). The default value for AH is 0x7FFF (+163.835°C) and the default value for AL is 0x8000 (-163.840°C). The MSB indicates if the value is positive or negative; for positive numbers the MSB is 0 and for negative numbers the MSB is 1. The Alarm High threshold (AH) is programmed in registers ALARM\_HI\_MSB [0x10] and ALARM\_HI\_LSB [0x11]. The alarm low

threshold (AL) is programmed in registers ALARM\_LO\_MSB [0x12] and ALARM\_LO\_LSB [0x13].

If the measured temperature is lower than AL or higher than AH, an alarm condition exists and the corresponding status bit (TEMP\_LO or TEMP\_HI) is set in the STATUS [0x00] regsiter. When the alarm condition is detected and the corresponding interrupt enable bit (TEMP\_LO\_EN or TEMP\_HI\_EN) is set in the INTERRUPT\_ENABLE [0x01] register and if GPIO0\_MODE in the GPIO\_SETUP [0x20] register is set to 0x3, then a hardware interrupt asserts on the GPIO0 pin. The status bits, the alarm flag and the hardware interrupt stay asserted until the STATUS [0x00] register is read through the serial interface. The alarm flag only clears when STATUS is read. If the alarm flag is set and the next result does not trip the flag, then the flag remains set.

If the resolution or alarm settings change while the device is under an alarm condition, the alarm status must be cleared and another temperature conversion executed to update the alarm condition.

|         | Bit15                         | Bit14                            | Bit13         | Bit12         | Bit11 | Bit10         | Bit9        | Bit8 |

|---------|-------------------------------|----------------------------------|---------------|---------------|-------|---------------|-------------|------|

| MSB     | AH15                          | AH14                             | AH13          | AH12          | AH11  | AH10          | AH9         | AH8  |

| _       | Bit7                          | Bit6                             | Bit5          | Bit4          | Bit3  | Bit2          | Bit1        | Bit0 |

| LSB     | AH7                           | AH6                              | AH5           | AH4           | AH3   | AH2           | AH1         | AH0  |

| L       |                               |                                  |               |               |       |               |             |      |

| L       |                               | REGISTER FORMAT                  |               | Bit12         | Bit11 | Bit10         | Bit9        | Bit8 |

| L       | OW THRESHOLD<br>Bit15<br>AL15 | REGISTER FORMAT<br>Bit14<br>AL14 | Bit13         | Bit12<br>AL12 | Bit11 | Bit10<br>AL10 | Bit9<br>AL9 | Bit8 |

| ALARM L | Bit15<br>AL15                 | Bit14<br>AL14                    | Bit13<br>AL13 | AL12          | AL11  | AL10          | AL9         | AL8  |

| ALARM L | Bit15                         | Bit14                            | Bit13         |               | -     |               |             |      |

Figure 2. Alarm Threshold Register Format

#### **GPIO**

The MAX31888 provides access to three GPIO pins which can be used to provide additional functionality as shown in <u>Table 2</u>. GPIO0 can be configured to output an active low interrupt. The interrupt on GPIO0 is triggered based on selectable status bits in the INTERRUPT\_ENABLE[0x01] register. By setting one or more of the available bits in the INTERRUPT\_ENABLE register, the flag for an interrupt is raised if the corresponding status register bit is set and GPIO0\_MODE[1:0] in the GPIO\_SETUP [0x20] register is set to 11. GPIO1 can be configured as an input for a temperature conversion. When GPIO1\_MODE[1:0] in the GPIO\_SETUP register is set to 11, driving the line low initiates an external temperature conversion.

**Table 2. GPIO Mode Functions**

| GPIOX_MODE[1:0] (X = 0,1) | GPIO0                       | GPIO1                       | GPIO2                       |  |

|---------------------------|-----------------------------|-----------------------------|-----------------------------|--|

| 00                        | Hi-Z Input                  | Hi-Z Input                  | Hi-Z Input                  |  |

| 01                        | Output                      | Output                      | Output                      |  |

| 10 (default)              | 1MΩ Internal Pulldown Input | 1MΩ Internal Pulldown Input | 1MΩ Internal Pulldown Input |  |

## **Table 2. GPIO Mode Functions (continued)**

### 1-Wire Bus System

The 1-Wire bus system uses a single bus master to control one or more slave devices. The MAX31888 is always a slave. When there is only one slave on the bus, the system is referred to as a single-drop system; if there is more than one slave on the bus, the system is referred to as multi-drop system. All data and commands are transmitted least significant bit first over the 1-Wire bus.

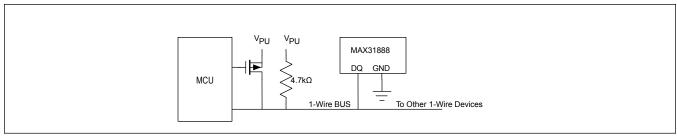

The 1-Wire bus has, by definition, only a single data line. Each device (master or slave) interfaces to the data line through an open-drain or three-state port. This allows each device to release the data line when the device is not transmitting data so the bus is available for use by another device. The 1-Wire port of the MAX31888 (the DQ pin) is open drain with an internal circuit equivalent to that shown in Figure 3.

Figure 3. Simplified Diagram of the 1-Wire Port

The 1-Wire bus requires an external pullup resistor, thus the idle state for the 1-Wire bus is high. If for any reason a transaction needs to be suspended, the bus must be left in the idle state (which is also the shutdown state) if the transaction is to resume. Infinite recovery time can occur between bits so long as the 1-Wire bus is in the inactive (high) state during the recovery period. If the bus is held low for more than 480µs, all components on the bus are reset. Additionally, to ensure that the device has sufficient supply current during temperature conversions, it is necessary to provide a strong pullup (such as a MOSFET) on the 1-Wire bus whenever temperature conversions are performed.

#### **Transaction Sequence**

The transaction sequence for accessing the device is as follows:

- Step 1: Initialization

- Step 2: ROM command (followed by any required data exchange)

- Step 3: MAX31888 Function command (followed by any required data exchange)

The bus master must follow this sequence every time a slave device is accessed. Slave devices do not respond if any steps in the sequence are missing or out of order. Exceptions to this rule are the Search ROM [0xF0] and Alarm Search [0xEC] commands. After issuing either of these ROM commands, the master must return to Step 1 in the sequence.

#### Initialization

All transactions on the 1-Wire bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master, followed by presence pulse(s) transmitted by the slave(s). The presence pulse lets the bus master know that slave devices (such as the MAX31888) are on the bus and are ready to operate. Timing for the reset and presence pulses is detailed in the 1-Wire Signaling section.

#### **ROM Commands**

After the bus master detects a presence pulse, it can issue a ROM command. These commands operate on the unique 64-bit ROM codes of each slave device and allow the master to single out a specific device when several are present on the 1-Wire bus. These commands also allow the master to determine the number and types of devices present on the bus and the alarm state of any device. There are five ROM commands, each of which is 8 bits long. The master device must issue an appropriate ROM command before issuing a MAX31888 Function command. Figure 4 shows a flowchart for operation of the ROM commands.

#### Search ROM [0xF0]

When a system initially powers up, the master must identify the ROM codes of all slave devices on the bus. This allows the master to determine the number of slaves and their device types. The master identifies the ROM codes through a process of elimination that requires the master to perform a Search ROM cycle (i.e. Search ROM command followed by data exchange) as many times as necessary to identify all the slave devices. If there is only one slave on the bus, the simpler Read ROM command can replace the Search ROM process. For a detailed explanation of the Search ROM procedure, refer to Application Note 937: *Book of iButton Standards*. After every Search ROM cycle, the bus master must return to Step 1 (initialization) in the transaction sequence.

### Read ROM [0x33]

The Read ROM command can only be used when there is one slave on the bus. It allows the bus master to read the slave's 64-bit ROM code without using the Search ROM procedure. If this command is used when there is more than one slave present on the bus, a data collision occurs when all the slaves attempt to respond at the same time.

### Match ROM [0x55]

The Match ROM command, followed by a 64-bit ROM code sequence, allows the bus master to address a specific slave device on a multi-drop or single-drop bus. Only the slave that exactly matches the 64-bit ROM code sequence responds to the function command issued by the master. All other slaves on the bus wait for a reset pulse.

#### Skip ROM [0xCC]

The Skip ROM command addresses all devices on the bus simultaneously without sending out any ROM code information. This behavior makes sending function commands when there is only one slave on the bus faster and allows a master to send global commands when all slaves are the same device type.

For example, if all devices on the bus are MAX31888, the master can make all devices perform simultaneous temperature conversions by issuing a Skip ROM command followed by a Convert T [0x44] command.

Note that the Read FIFO [0xBE] command can follow the Skip ROM command only if a MAX31888 is the only device on the bus. The Skip ROM command saves time by allowing the master to read from the slave without sending the device's 64-bit ROM code. A Skip ROM command followed by a Read FIFO command causes a data collision on the bus if there is more than one slave, as multiple devices attempt to transmit data simultaneously.

### Alarm Search [0xEC]

The Alarm Search command operates identically to the Search ROM command except that only slaves with a set alarm flag respond. This command allows the master device to determine if any MAX31888s experienced an alarm condition during a past recent temperature conversion. The master must read the status of each MAX31888 in the alarm state to clear that device's alarm flag. After every Alarm Search cycle (i.e., Alarm Search command followed by data exchange), the bus master must return to Step 1 (initialization) in the transaction sequence. See the <u>Alarm Signaling</u> section for an explanation of alarm flag operation.

### Resume ROM [0xA5]

The Resume command maximizes the data throughput in a multi-drop environment, . This command checks the status of an internal RC flag and, if it is set, transfers control to the device function commands, similar to a Skip ROM command. The only way to set the RC flag is through successfully executing the Match ROM, Search ROM, or Overdrive-Match ROM command. Once the RC flag is set, the master can repeatedly access the device through the Resume command. Accessing another device on the bus clears the RC flag, preventing two or more devices from simultaneously responding to the Resume command.

#### Overdrive Skip ROM [0x3C]

The Overdrive Skip ROM command functions like the Skip ROM command and allows the master to address all devices on the bus simultaneously. On a single-drop bus, this command allows for faster execution by allowing the bus master to access the device functions without providing the 64-bit ROM ID. Unlike the normal Skip ROM command, the Overdrive-Skip ROM command sets the MAX31888 into the overdrive mode (OD = 1). All communication following this command must occur at overdrive speed until a reset pulse of minimum 480µs duration resets all devices on the bus to standard speed (OD = 0). Slaves already in overdrive mode from a previous overdrive command remain in overdrive mode.

### Overdrive Match ROM [0x69]

The Overdrive-Match ROM command functions like the Match ROM command and allows the bus master to address a specific MAX31888 on a multi-drop bus. Only the MAX31888 that exactly matches the 64-bit ROM sequence responds to the subsequent device function command. Unlike the normal Match ROM command, the Overdrive-Match ROM command sets the MAX31888 into the overdrive mode (OD = 1) by transmitting the 64-bit ROM sequence at overdrive speed after transmitting the Overdrive-Match command. All communication following this command must occur at overdrive speed until a reset pulse of minimum 480µs duration resets all devices on the bus to standard speed (OD = 0). Slaves already in overdrive mode from a previous overdrive command remain in overdrive mode. The Overdrive-Match ROM command can be used with a single device or multiple devices on the bus.

#### **Function Commands**

After the bus master uses a ROM command to select a device, the master can issue one of the device function commands. These commands allow the master to write to and read from the device's register memory, initiate temperature conversions, and determine the power-supply mode. <u>Table 3</u> summarizes the device function commands, and <u>Figure 4</u> illustrates those commands.

**Table 3. Summary of MAX31888 Function Commands**

| COMMAND<br>NAME   | DESCRIPTION                                                                  | COMMAND<br>CODE | 1-WIRE BUS ACTIVITY AFTER COMMAND IS ISSUED                                    |

|-------------------|------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------|

| CONVERT<br>T      | Initiates a temperature conversion                                           | 0x44            | None                                                                           |

| WRITE<br>REGISTER | Write to registers starting at the address specified in the command sequence | 0xCC            | The master transmits number of bytes of data specified in the command sequence |

| READ<br>REGISTER  | Read registers starting at the address specified in the command sequence     | 0x33            | The device transmits number of bytes of data specified in the command sequence |

| SOFT<br>RESET     | Reset all configuration registers                                            | 0x82            | None                                                                           |

Figure 4. The Function Command Execution Procedure

#### Convert T [0x44]

The Convert T command initiates a single temperature conversion. Following the conversion, the resulting temperature sensor data is stored in the FIFO memory and the device returns to its shutdown state. Within 10µs (max) after this command is issued, the master must enable a strong pullup on the 1-Wire bus for the duration of the conversion (t<sub>CONV</sub>), as described in the <u>Parasite Power</u> section.

A Convert T command sequence executes as follows:

- 1. Reset

- 2. Presence Pulse

- 3. ROM Command (e.g. Match ROM or Skip ROM)

- 4. Master TX: Convert T Command (0x44)

- 5. Master RX: Inverted CRC-16 (command)

#### Write Register [0xCC]

The Write Register command writes data to the registers beginning at the specified address. It supports burst mode at the starting address and autoincrements after each byte.

A Write Register command sequence executes as follows:

- 1. Reset

- 2. Presence Pulse

- 3. ROM Command

- 4. Master TX: Write Register Command (0xCC)

- 5. Master TX: Starting Register Address (e.g. Match ROM or Skip ROM)

- 6. Master TX: Length Byte (number of bytes to write -1); 0 to 255

- 7. Master TX: Write Register Data (number of bytes)

- 8. Master RX: Inverted CRC-16 (command + starting address+ length byte + write register data)

#### Read Register [0x33]

The Read Register command reads data from the registers beginning at the specified address. It supports burst mode at the starting address and autoincrements after each byte.

A Read Register command sequence executes as follows:

- 1. Reset

- 2. Presence Pulse

- 3. ROM Command (e.g. Match ROM or Skip ROM)

- 4. Master TX: Read Register Command (0x33)

- 5. Master TX: Starting Register Address

- 6. Master TX: Length Byte (number of bytes to read -1); 0 to 255

- 7. Master RX: Read Register Data (number of bytes)

- 8. Master RX: Inverted CRC-16 (command + starting address+ length byte + read register data)

#### Soft Reset [0x82]

The Soft Reset command resets all configuration registers and the device returns to its shutdown state.

The Soft Reset command executes as follows:

- 1. Reset

- 2. Presence Pulse

- 3. ROM Command (e.g. Match ROM or Skip ROM)

- 4. Master TX: Soft Reset Command (0x82)

- 5. Master RX: Inverted CRC-16

#### 1-Wire Signaling

The MAX31888 uses a strict 1-Wire communication protocol to ensure data integrity. Several signal types are defined by this protocol: reset pulse, presence pulse, write 0, write 1, read 0, and read 1. Except for the presence pulse, the bus master initiates all falling edges. The MAX31888 can communicate at two different speeds: standard speed and overdrive speed. If not set into the overdrive mode, the MAX31888 defaults to standard speed. While in overdrive mode, the fast timing applies to all waveforms.

To transition from the idle to active state, the voltage on the 1-Wire line must fall from  $V_{PUP}$  to below the threshold  $V_{TL}$ . Conversely, the voltage must rise from  $V_{ILMAX}$  to above the threshold  $V_{TH}$  to transition from the active to idle state. The time required for the voltage to rise is represented by  $\epsilon$  in Figure 5. The duration of  $\epsilon$  depends on the pullup resistor (RPUP) and the total capacitance of the 1-Wire bus. The voltage  $V_{ILMAX}$  only determines the MAX31888 logic level and does not affect event triggering.

#### Initialization Procedure: Reset and Presence Pulses

Figure 5 illustrates the initialization sequence required to begin any communication with one or more MAX31888s. A reset pulse followed by a presence pulse indicates that the devices are ready to receive ROM commands. If the bus master uses slew-rate control on the falling edge, it must pull down the line for  $t_{RSTL} + t_F$  to compensate for the longer falling edge. A  $t_{RSTL}$  duration of 480µs or longer resets the bus and returns all devices to standard speed. If the MAX31888 is in overdrive mode and  $t_{RSTL}$  is shorter than 80µs, the device remains in overdrive mode. If the device is in overdrive mode and  $t_{RSTL}$  is between 80µs and 480µs, the device resets with an undetermined communication speed.

The bus master enters receive mode after it releases the bus at the end of  $t_{RSTL}$ . The 1-Wire bus is then pulled to  $V_{PUP}$  through the pullup resistor. When the threshold  $V_{TH}$  is crossed, the MAX31888 waits for  $t_{PDH}$  and then transmits a presence pulse by pulling the line low for  $t_{PDL}$ . To detect a presence pulse, the master must test the logical state of the 1-Wire line at  $t_{MSP}$ .

Figure 5. 1-Wire Initialization Sequence

#### Read/Write Time Slots

Data communication with the MAX31888 takes place in time slots that carry a single bit each. Write time slots transport data from bus master to slave. Read time slots transfer data from slave to master. <u>Figure 6</u>, <u>Figure 7</u>, and <u>Figure 8</u> show how the write and read time slots are defined.

All communication begins with the master pulling the data line low. As the voltage on the 1-Wire line falls below the threshold  $V_{TL}$ , the MAX31888 starts its internal timing generator. This generator determines when the data line is sampled during a write time slot and how long data is considered valid during a read time slot.

#### Master-to-Slave

For a write 0 time slot, the voltage on the data line must stay below the  $V_{TH}$  threshold until the write 0 low time  $t_{W0L}(MIN)$  expires. For a write 1 time slot, the voltage on the data line must have crossed the  $V_{TH}$  threshold before the write 1 low time  $t_{W1L}(MAX)$  expires. For the most reliable communication, the voltage on the data line must not exceed  $V_{ILMAX}$  during the entire  $t_{W0L}$  or  $t_{W1L}$  window. After crossing the  $V_{TH}$  threshold, the MAX31888 must wait for the recovery time  $t_{REC}$  before it is ready for the next time slot.

Figure 6. Master Write 0 Timing

Figure 7. Master Write 1 Timing

#### Slave-to-Master

A read-data time slot begins like a write 1 time slot. The voltage on the data line must remain below  $V_{TL}$  until the read low time  $t_{RL}$  expires. During the  $t_{RL}$  window, when responding with a 0, the MAX31888 pulls the data line low. Its internal timing generator determines when this pulldown ends and the voltage rises again. When responding with a 1, the MAX31888 does not hold the data line low, and the voltage rises as soon as  $t_{RL}$  elapses.

The sum  $t_{RL}$  +  $\delta$  (rise time) defines the start of the master sampling window and the internal timing generator of the MAX31888 defines the end ( $t_{MSRMIN}$  to  $t_{MSRMAX}$ ). The master sampling window is the period of time in which the master must perform a read from the data line. For the most reliable communication,  $t_{RL}$  should be as short as permissible, and the master should read close to but no later than  $t_{MSRMAX}$ . After reading from the data line, the

master must wait until  $t_{SLOT}$  expires. This guarantees sufficient recovery time,  $t_{REC}$ , for the MAX31888 to prepare for the next time slot. Note that  $t_{REC}$  applies only to a single MAX31888 attached to a 1-Wire line. For multi-drop network configurations,  $t_{REC}$  must be extended to accommodate the additional 1-Wire device input capacitance.

Figure 8. Master Read Data Timing

#### **Parasite Power**

The MAX31888's parasite power circuit allows it to operate without a local power supply. Parasite power is useful for space constrained applications or applications that require remote temperature sensing away from the main PCB. Figure 9 shows the device's parasite-power control circuitry, which "steals" power from the 1-Wire bus through the DQ pin when the bus is high. The parasite power capacitor CPP stores charge while the DQ line is high. This stored charge is used to power the device while the bus is low.

In parasite power mode, the 1-Wire bus and C<sub>PP</sub> provide the device with sufficient current to execute most operations as long as the specified timing and voltage requirements are met (see the DC Electrical Characteristics and AC Electrical Characteristics in the *Electrical Characteristics* table). However, the conversion current can reach 100µA (max) while the device performs a Convert T [0x44] command. During conversion, the current can exceed the C<sub>PP</sub> supply capability and can cause an unacceptable voltage drop across the weak 1-Wire pullup resistor. To ensure that the device has sufficient supply current, it is necessary to provide a strong pullup on the 1-Wire bus when performing temperature conversions. This can be accomplished by using an external MOSFET to pull the bus directly to the rail, as shown in Figure 9. Alternatively, the bus master can provide the supply path if it has an internal, weak pullup that can be switched directly to the rail. The 1-Wire bus must switch to the strong pullup within 10µs (max) after a Convert T [0x44] command is issued, and the bus must be held high by the strong pullup for the duration of the conversion (t<sub>CONV</sub>). No other activity can take place on the 1-Wire bus until the temperature measurement is completed.

In order to minimize current, the MAX31888 enters standby when inactive. In standby mode, all blocks are shut-down except for a low power input monitor circuit and the volatile register bits. The device only exits standby mode when the 1-Wire master pulls down the bus.

When the part first turns on, the 1-Wire bus should remain high for  $\tau \times 5$  seconds, where  $\tau = R_{PULLUP} \times C_{PP}$ , to fully charge  $C_{PP}$  before sending the first 1-Wire reset.

Figure 9. Providing a Strong Pullup to Power the MAX31888 During Temperature Conversions

#### 64-Bit OTP ROM Code

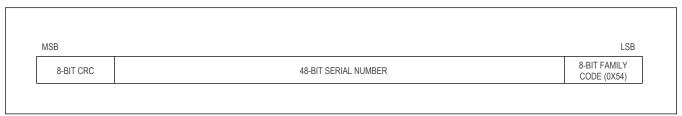

Each device contains a unique 64-bit code stored in ROM, the structure of which is shown in <u>Figure 10</u>. The 8 least significant bits of the ROM code contain the device's 1-Wire family code, 0x54. The next 48 bits contain a unique serial number. The 8 most significant bits contain a cyclic-redundancy-check (CRC) byte that is calculated from the 56 bits of the serial number and family code. A detailed explanation of the CRC bits is provided in the <u>CRC Generation</u> section. The 64-bit ROM code and associated ROM function control logic allow the device to operate as a 1-Wire device using the protocol detailed in the <u>1-Wire Bus System</u> section. The 8-byte ROM code is transmitted LSB first.

Figure 10. MAX31888 ROM Structure

#### Registers

The MAX31888 has memory mapped registers for temperature, alarm high, alarm low, and configuration settings. These registers are written or read using the 1-Wire Function commands Write Register [0x80] and Read Register [0x81], respectively. All 1-Wire commands are described in detail in the MAX31888 *Function Commands* section. See the Register Map section for descriptions of each register.

#### **CRC Generation**

The CRCs provide the bus master with a method of data validation when data is read from the device. To verify that the data has been read correctly, the bus master must recalculate the CRC from the received data and then compare this value to the CRC. If the calculated CRC matches the read CRC, the data has been received error free. The comparison of CRC values and the decision to continue with an operation are determined entirely by the bus master. There is no circuitry inside the device that prevents a command sequence from proceeding if the device CRC does not match the value generated by the bus master.

MAX31888 has two CRC Generators:

- 8 bit CRC for ROM Code

- 16 bit CRC for all 1-Wire commands

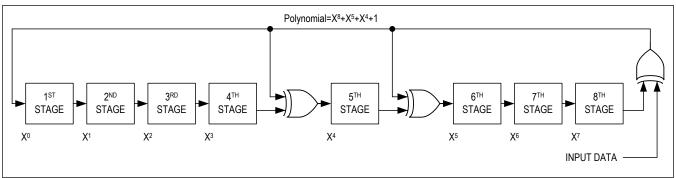

#### 8-Bit CRC for ROM Code

The ROM Code CRC is calculated from the lower 56 bits read of the ROM code. The 8-bit CRC forms the upper 8 bits of the 64-bit ROM Code.

The equivalent polynomial function of the 8-bit CRC is:  $CRC = X^8 + X^5 + X^4 + 1$

The bus master can recalculate the CRC and compare it to the CRC values from the MAX31888 using the polynomial generator shown in <a href="Figure 11">Figure 11</a>. This circuit consists of a shift register and XOR gates, and the shift register bits are initialized to 0. Starting with the least significant bit of byte 0 of the ROM code, one bit at a time should be shifted into the shift register. After shifting in the 56th bit of the ROM code, the polynomial generator contains the recalculated CRC. Next, the 8-bit ROM code CRC from the device must be shifted into the circuit. At this point, if the recalculated CRC was correct, the shift register contains all 0s. Additional information about the Maxim Integrated 1-Wire CRC is available in Application Note 27: <a href="Understanding and Using Cyclic Redundancy Checks with Maxim iButton® Products">Understanding and Using Cyclic Redundancy Checks with Maxim iButton® Products</a>. See <a href="Figure 11">Figure 11</a> for more details.

Figure 11. 8-bit CRC State Machine

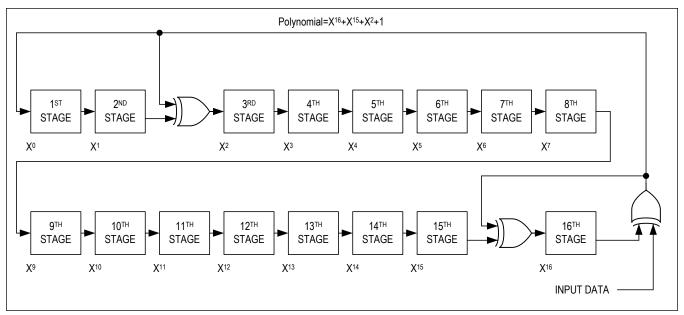

### 16-Bit CRC for 1-Wire Device Function Commands

The Command CRC for the 1-Wire device function commands is calculated from the command sequence which includes the Command, Register Address, Length-1, and Data bytes. The inverted 16-bit CRC is read by the 1-Wire bus master at the end of each Command sequence and is transmitted by the MAX31888 LSB first.

The equivalent polynomial function of the 16-bit CRC is:  $CRC = X^{16} + X^{15} + X^2 + 1$

The bus master can recalculate the CRC and compare it to the CRC values from the MAX31888 using the polynomial generator shown in <a href="Figure 12">Figure 12</a>. This circuit consists of a shift register and XOR gates, and the shift register bits are initialized to 0. Starting with the least significant bit of the command sequence, one bit at a time should be shifted into the shift register. After shifting in the last bit, the polynomial generator contains the recalculated CRC. Next, the 16-bit Command CRC from the device must be shifted into the circuit. At this point, if the recalculated CRC was correct, the shift register contains all 0s. Additional information about the Maxim Integrated 1-Wire CRC is available in Application Note 27: <a href="Understanding and Using Cyclic Redundancy Checks with Maxim iButton® Products">Understanding and Using Cyclic Redundancy Checks with Maxim iButton® Products</a>. See <a href="Figure 12">Figure 12</a> for more details.

Figure 12. 16-bit CRC State Machine

### **Operation Examples**

### Example 1

In the following table there are multiple devices on the bus. The bus master initiates a temperature conversion in a specific MAX31888 and then reads its Temperature Data registers and recalculates the CRC to verify the data.

| MASTER<br>MODE | DATA<br>(LSB<br>FIRST)                        | COMMENTS                                                                                                                                                                                                                                                          |  |  |  |  |

|----------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Tx             | Reset                                         | Master issues reset pulse.                                                                                                                                                                                                                                        |  |  |  |  |

| Rx             | Presence                                      | Devices respond with presence pulse.                                                                                                                                                                                                                              |  |  |  |  |

| Tx             | 0x55                                          | laster issues Match ROM command.                                                                                                                                                                                                                                  |  |  |  |  |

| Tx             | 64-bit ROM code                               | aster sends device ROM code.                                                                                                                                                                                                                                      |  |  |  |  |

| Tx             | 0x44                                          | aster issues Convert T command.                                                                                                                                                                                                                                   |  |  |  |  |

| Tx             | DQ line held<br>high by<br>strong pull-<br>up | Master applies strong pullup to DQ for the duration of the conversion.                                                                                                                                                                                            |  |  |  |  |

| Tx             | Reset                                         | Master issues reset pulse.                                                                                                                                                                                                                                        |  |  |  |  |

| Rx             | Presence                                      | Devices respond with presence pulse.                                                                                                                                                                                                                              |  |  |  |  |

| Tx             | 0x55                                          | Master issues Match ROM command.                                                                                                                                                                                                                                  |  |  |  |  |

| Tx             | 64-bit ROM code                               | Master sends device ROM code.                                                                                                                                                                                                                                     |  |  |  |  |

| Tx             | 0x33                                          | Master issues Read Register command                                                                                                                                                                                                                               |  |  |  |  |

| Rx             | 5 data bytes                                  | Master reads two bytes of Temperature data and CRC bytes. The master then recalculates the CRC of the first 2 data bytes received and compares the calculated CRC with the read CRC. If they match, the master continues; if not, the read operation is repeated. |  |  |  |  |

#### Example 2

In the following table there is only one device on the bus. The master writes to the alarm high, alarm low, and configuration registers in the device's Register Map and then reads the scratchpad and recalculates the CRC to verify the data.

| MASTER<br>MODE | DATA<br>(LSB<br>FIRST) | COMMENTS                                                                                                                                                                                                                                                          |  |  |  |  |  |

|----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Tx             | Reset                  | Master issues a reset pulse.                                                                                                                                                                                                                                      |  |  |  |  |  |

| Rx             | Presence               | evice responds with presence pulse.                                                                                                                                                                                                                               |  |  |  |  |  |

| Tx             | 0xCC                   | Master issues Skip ROM command.                                                                                                                                                                                                                                   |  |  |  |  |  |

| Tx             | 0xCC                   | laster issues Write Register command.                                                                                                                                                                                                                             |  |  |  |  |  |

| Тх             | 9 data<br>bytes        | Master sends Register Address, number of bytes -1, 5 data bytes and CRC bytes to the Registers (alarm high, alarm low, and configuration registers).                                                                                                              |  |  |  |  |  |

| Tx             | Reset                  | Master issues reset pulse.                                                                                                                                                                                                                                        |  |  |  |  |  |

| Rx             | Presence               | Device responds with presence pulse.                                                                                                                                                                                                                              |  |  |  |  |  |

| Tx             | 0xCC                   | Master issues Skip ROM command.                                                                                                                                                                                                                                   |  |  |  |  |  |

| Tx             | 0x33                   | Master issues Read Registers command.                                                                                                                                                                                                                             |  |  |  |  |  |

| Rx             | 5 data<br>bytes        | Master reads two bytes of Temperature data and CRC bytes. The master then recalculates the CRC of the first 2 data bytes received and compares the calculated CRC with the read CRC. If they match, the master continues; if not, the read operation is repeated. |  |  |  |  |  |

### **FIFO Description**

The FIFO is 32 samples long and is designed for 16-bit temperature data. The master does a burst read of two bytes starting at register 0x08 to read one 16-bit temperature sample, referred to as a word, from the FIFO. The master reads 2N bytes from the FIFO to get N samples.

There are seven registers that control how the FIFO is configured and read out. These registers are described in <u>Table</u> 4.

### Table 4. FIFO Register Map

| ADDRESS | REGISTER NAME         | В7 | В6 | B5                 | B4                 | В3             | B2          | B1      | B0 |  |

|---------|-----------------------|----|----|--------------------|--------------------|----------------|-------------|---------|----|--|

| 0x04    | FIFO Write Pointer    | -  | -  | -                  | - FIFO_WR_PTR[4:0] |                |             |         |    |  |

| 0x05    | FIFO Read Pointer     | -  | -  | -                  | - FIFO_RD_PTR[4:0] |                |             |         |    |  |

| 0x06    | FIFO Overflow Counter | -  | -  | - OVF_COUNTER[4:0] |                    |                |             |         |    |  |

| 0x07    | FIFO Data Counter     | -  | -  |                    |                    | FIFO_DATA_CC   | DUNT[5:0]   |         |    |  |

| 0x08    | FIFO Data Register    |    |    |                    |                    | FIFO_DATA[7:0] |             |         |    |  |

| 0x09    | FIFO Configuration 1  | -  | -  | - FIFO_A_FULL[4:0] |                    |                |             |         |    |  |

| 0x0A    | FIFO Configuration 2  | -  | -  | -                  | FLUSH_FIFO         | FIFO_STAT_CLR  | A_FULL_TYPE | FIFO_RO | -  |  |

#### FIFO\_WR\_PTR (address 0x04), Write Pointer