### **MAX25432**

### **General Description**

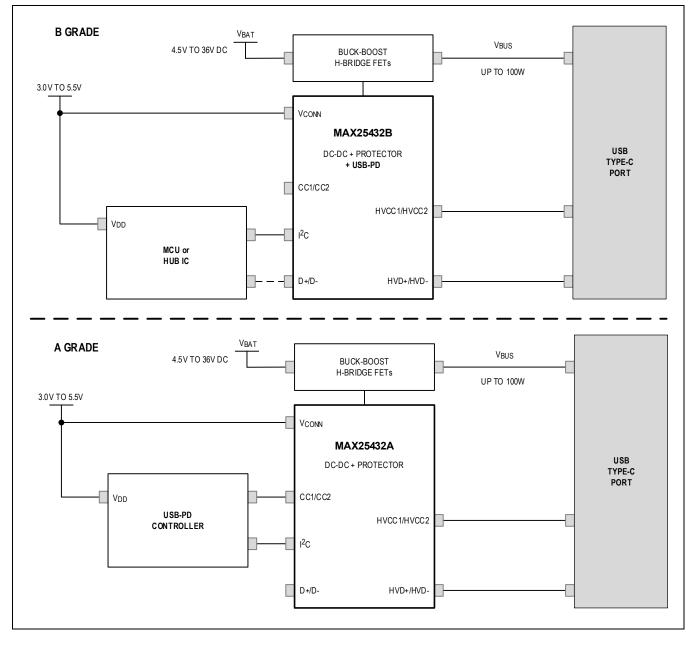

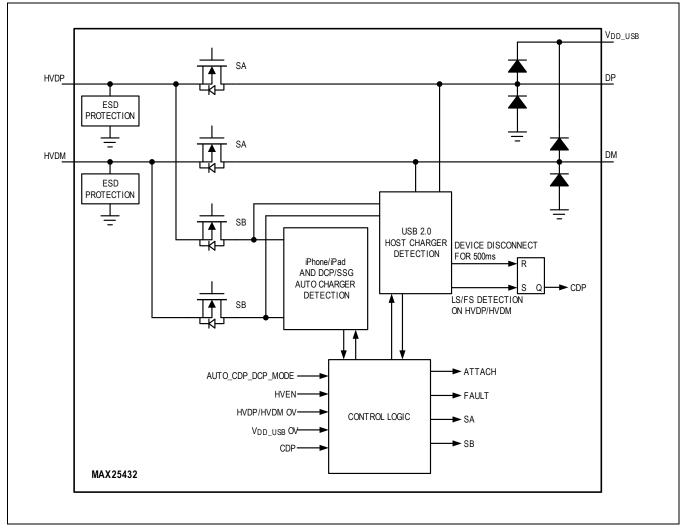

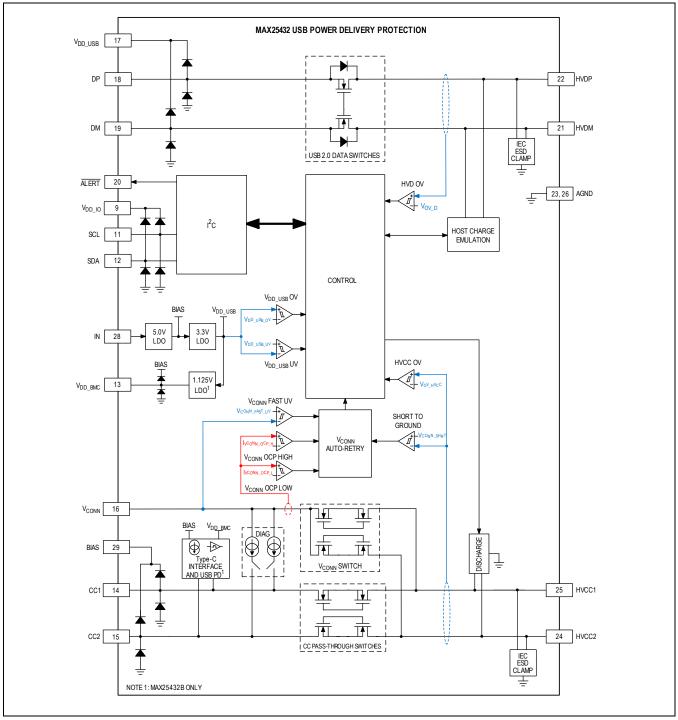

The MAX25432 combines an automotive-grade buckboost controller capable of full-range 3.3V to 21V programmable power supply (PPS) at up to 6.35A, USB Power Delivery (USB PD) analog front-end (AFE), legacy USB charging support, and USB Type-C<sup>®</sup> protection switches for automotive USB host or downstream-facing (DFP) applications. The USB Type-C protection switches provide automotive system-level ESD protection and 24V short-circuit protection for D+, D-, CC1, CC2, and V<sub>CONN</sub>. The device can optionally support legacy charging modes for older passenger phones including BC1.2, Apple<sup>®</sup> Charge, Apple CarPlay<sup>®</sup>, Apple MFi, and USB On-The-Go (OTG).

The MAX25432B integrates a USB PD AFE, which supports the USB-IF Type-C Port Controller Interface (TCPCI) specification and can interface with any I<sup>2</sup>C controller in the application. The MAX25432A provides configuration channel (CC) signal pass-through protection for an external USB PD controller.

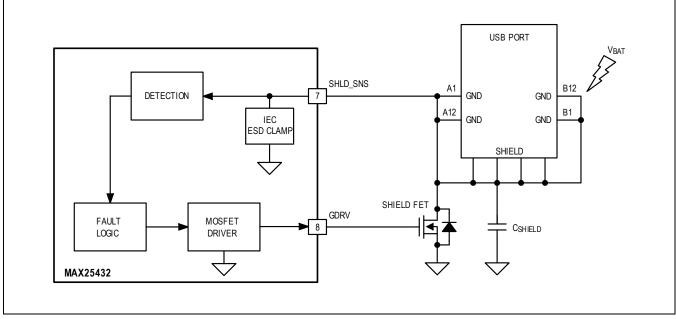

P-suffix and G-suffix devices include intelligent detection and protection to avoid high short-circuit currents flowing from the car battery through the cable shield to ground during fault events, thus preventing car module damage.

The MAX25432 is available in a small, 6mm x 6mm, 40pin TQFN-EP package and requires very few external components. The MAX25432 evaluation (EV) kit and collateral provide a convenient platform to the design engineer for rapid evaluation with reduced test and firmware development time.

### **Applications**

- USB Hubs, Breakout Boxes, and Multimedia Hubs

- Dedicated Charging Modules

- Rear-Seat Entertainment Modules

- Head Unit, Radio, Navigation

### **Benefits and Features**

- Integrated I<sup>2</sup>C Buck-Boost Controller with PPS

- 4.5V to 36V Input Operating Range

- 3.3V to 21V Constant Voltage, 10mV LSB

- 1A to 6.35A Current Limit, 25mA LSB

- 220kHz, 300kHz, and 400kHz Switching Frequency

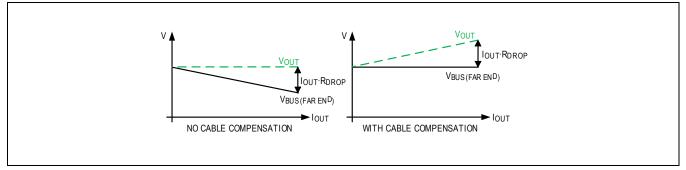

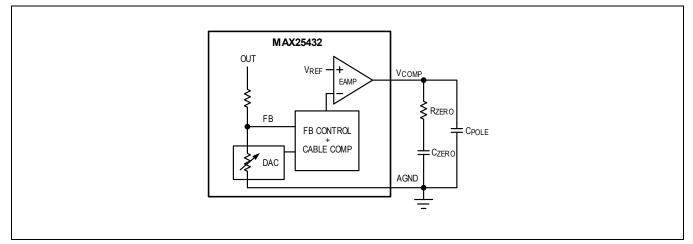

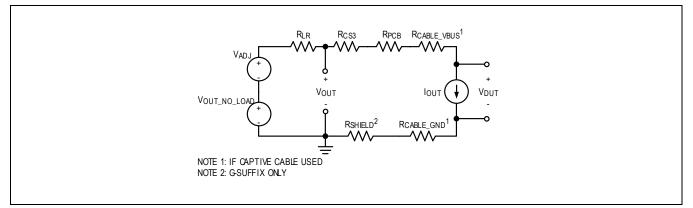

- +  $V_{BUS}$  Cable Compensation up to  $516m\Omega$

- External Frequency Synchronization and Spread Spectrum for Reduced EMI

- USB PD 3.1 Type-C Port Controller

- USB-IF Compliant TID 9154

- Up to 800mV Ground Offset

- Pairs with ADI TCPM for Turn-Key Solution

- MAX25432BATLP Enables:

- ADI TCPM Alternate Mode and Dual-Role Port

- Improved CC Detection

- Advanced Monitoring Algorithms (V, T)

- Dynamic Loop Control

- Highest Performance, Safest, and Lowest Cost Passenger Cable-Shield Short-to-Battery Protection

- Minimizes Short-Circuit Currents with a Small, Single-FET Solution

- Integrated Current-Sense Amplifiers, ADC and DAC

- Integrated 3.3V to 5.0V, 1.5W, Smart, Reliable V<sub>CONN</sub> Switches and Protection, 50mA to 500mA OCP

- Integrated 24V DC Protection on Protected HVD+, HVD-, HVCC1, HVCC2 Outputs

- Integrated Legacy USB 2.0 Charging Including BC1.2, Apple CarPlay, OTG, and Apple MFi Rev 3x

- Integrated ±15kV Air-Gap/±8kV Contact-Discharge ISO 10605 and IEC 61000-4-2 ESD Protection

- -40°C to +125°C Operating Temperature Range

- 40-Pin, 6mm x 6mm, TQFN Package with EP

- AEC-Q100 and AEC-Q006 Qualified

#### Ordering Information appears at end of data sheet.

Apple and CarPlay are registered trademarks of Apple, Inc. iPhone and iPad are registered trademarks of Apple Inc. OnePlus is a registered trademark of OnePlus Technology (Shenzhen) Co., Ltd. Oppo is a registered trademark of GuangDong OPPO Mobile Telecommunications Corp., Ltd. Samsung is a registered trademark of Samsung Electronics Co., Ltd. USB Type-C is a registered trademark of USB Implementers Forum, Inc.

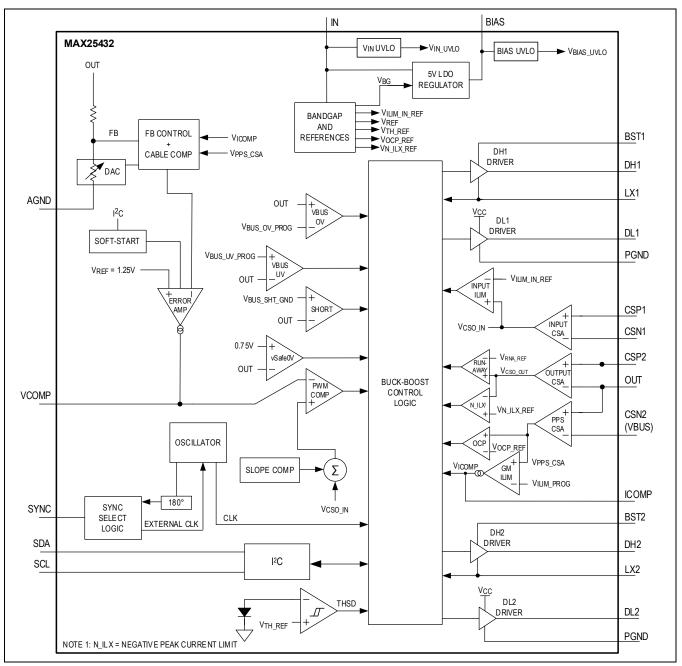

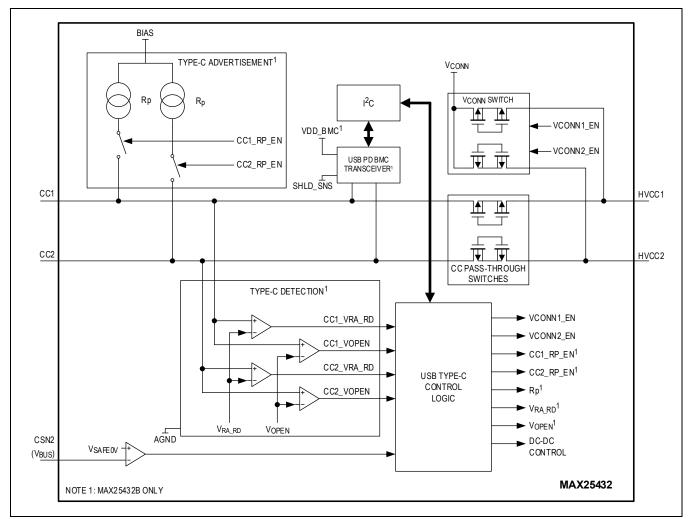

# Simplified Block Diagram

### **Absolute Maximum Ratings**

| IN to PGND                                                           | 0.3V to +40V                    |

|----------------------------------------------------------------------|---------------------------------|

| HVEN, CSP1, CSN1 to PGND                                             | 0.3V to V <sub>IN</sub> +0.3V   |

| LX1 to PGND ( <u>Note 1</u> )                                        | 0.3V to V <sub>IN</sub> +0.3V   |

| OUT, CSP2, CSN2 to PGND                                              | -0.3V to +30V                   |

| LX2 to PGND ( <u>Note 1</u> )                                        | 0.3V to V <sub>IN</sub> +0.3V   |

| CSP_ to CSN                                                          | -0.3V to +0.3V                  |

| BST1 to LX1, BST2 to LX2                                             | -0.3V to +6V                    |

| BST1, DH1 to PGND                                                    | 0.3V to +46V                    |

| BST2, DH2 to PGND                                                    | 0.3V to +36V                    |

| DH_ to LX                                                            | 0.3V to V <sub>BST</sub> _+0.3V |

| DL_, V <sub>COMP</sub> , I <sub>COMP</sub> to PGND                   | 0.3V to V <sub>BIAS</sub> +0.3V |

| BIAS, V <sub>DD_USB</sub> , V <sub>DD_IO</sub> , V <sub>DD_BMC</sub> | c, to AGND0.3V to +6V           |

| PGND to AGND0.3V to +0.3V                                 |

|-----------------------------------------------------------|

| HVCC1, HVCC2, HVDP, HVDM to AGND0.3V to +24V              |

| SHLD_SNS to AGND                                          |

| CC1, CC2, $V_{\mbox{CONN}}$ to AGND0.3V to +6V            |

| DP, DM to AGND0.3V to $V_{\mbox{VDD}_{\mbox{USB}}}$ +0.3V |

| ADDR, ALERT, GDRV, SYNC, to AGND0.3V to +6V               |

| SCL, SDA to AGND0.3V to $V_{\mbox{VDD\_IO}}$ +0.3V        |

| Continuous Power Dissipation ( <u>Note 2</u> )2963mW      |

| Operating Temperature Range40°C to +125°C                 |

| Junction Temperature+150°C                                |

| Storage Temperature Range40°C to +150°C                   |

| Soldering Temperature (reflow)+260°C                      |

Note 1: Self-protected from transient voltages exceeding these limits in circuit under normal operation.

Note 2: Multilayer board; T<sub>A</sub> = +70°C, derate 37mW/°C above +70°C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### TQFN

| Package Code                           | T4066+5C       |

|----------------------------------------|----------------|

| Outline Number                         | <u>21-0141</u> |

| Land Pattern Number                    | <u>90-0055</u> |

| Thermal Resistance, Four-Layer Board:  |                |

| Junction to Ambient (θ <sub>JA</sub> ) | 27°C/W         |

| Junction to Case (θ <sub>JC</sub> )    | 1°C/W          |

For the latest package outline information and land patterns (footprints), go to the <u>Package Index</u> on the Analog Devices website. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>Thermal Characterization of IC Packages</u>.

### **Electrical Characteristics**

$(V_{IN} = 14V, V_{HVEN} = V_{IN}, V_{VCONN} = 5V, V_{VDDIO} = 3.3V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . (*Note 3*)

| PARAMETER                            | SYMBOL                | CONDITIONS                                                              | MIN | TYP | MAX | UNITS |

|--------------------------------------|-----------------------|-------------------------------------------------------------------------|-----|-----|-----|-------|

| POWER SUPPLY                         |                       |                                                                         |     |     |     |       |

| Input Voltage Range on<br>IN         | V <sub>IN</sub>       |                                                                         | 4.5 |     | 36  | V     |

| IN Supply Current – Off<br>State     | I <sub>IN_OFF</sub>   | V <sub>IN</sub> = 18V, HVEN = 0V, V <sub>VCONN</sub> = 0V,<br>Off state |     | 16  |     | μA    |

| IN Supply Current –<br>Standby State | I <sub>IN_STDBY</sub> | Powered; enabled; V <sub>BUS</sub> off                                  |     | 2.4 |     | mA    |

$(V_{IN} = 14V, V_{HVEN} = V_{IN}, V_{VCONN} = 5V, V_{VDDIO} = 3.3V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . (*Note 3*)

| PARAMETER                                                   | SYMBOL                        | CONDITIONS                                                                                                                    | MIN               | TYP      | MAX               | UNITS |

|-------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------|----------|-------------------|-------|

| IN Undervoltage<br>Lockout Rising<br>Threshold              | V <sub>IN_UVLO_R</sub>        | V <sub>IN</sub> rising. Default setpoint.<br>Programmable from 4.5V to 8.5V in 0.4V<br>steps with IN_UV_THRESH[3:0] register. |                   | 4.5      |                   | V     |

| IN Undervoltage<br>Lockout Falling<br>Threshold             | VIN_UVLO_F                    | V <sub>IN</sub> falling. Default setpoint.                                                                                    |                   | 4.3      |                   | V     |

| IN Undervoltage<br>Lockout Accuracy –<br>Rising and Falling | V <sub>IN_UVLO_AC</sub><br>C  | Setpoint programmable in 0.4V steps with IN_UV_THRESH[3:0] register                                                           | Setpoint<br>- 0.3 | Setpoint | Setpoint<br>+ 0.3 | V     |

| IN Undervoltage<br>Blanking Time                            | <sup>t</sup> DEB_IN_UVLO      |                                                                                                                               |                   | 150      |                   | μs    |

| INTERNAL REGULATOR                                          | RS                            |                                                                                                                               |                   |          |                   |       |

| BIAS Output Voltage                                         | V <sub>BIAS</sub>             | $V_{IN} > 6V$ , $I_{BIAS} = 0$ to $80mA$                                                                                      | 4.7               | 5.0      | 5.4               | V     |

| BIAS Dropout Voltage                                        | V <sub>BIAS_DROP</sub>        | V <sub>IN</sub> = 4.5V, I <sub>BIAS</sub> = 20mA                                                                              |                   | 0.125    | 0.25              | V     |

| BIAS Undervoltage                                           | V <sub>UV_BIAS</sub>          | V <sub>BIAS</sub> falling                                                                                                     | 2.7               | 3.0      | 3.3               | V     |

| BIAS Undervoltage<br>Lockout Hysteresis                     | V <sub>UV_BIAS_HY</sub><br>ST |                                                                                                                               |                   | 0.25     |                   | V     |

| BIAS Short-Circuit<br>Current Limit                         | I <sub>BIAS_SC</sub>          | V <sub>BIAS</sub> shorted to AGND                                                                                             | 100               | 200      |                   | mA    |

| V <sub>DD_USB</sub> OutputVoltage                           | V <sub>DD_USB</sub>           |                                                                                                                               | 3.0               | 3.3      | 3.6               | V     |

| V <sub>DD_USB</sub> Overvoltage                             | V <sub>DD_USB_OV</sub>        | Rising                                                                                                                        | 3.8               | 4.0      | 4.3               | V     |

| V <sub>DD_BMC</sub> Output<br>Voltage                       | V <sub>DD_BMC</sub>           | MAX25432B only, SHLD_SNS = 0V                                                                                                 | 1.05              | 1.125    | 1.2               | V     |

| THERMAL SHUTDOWN                                            |                               |                                                                                                                               |                   |          |                   |       |

| Thermal Shutdown<br>Temperature                             | T <sub>SHDN</sub>             | ( <u>Note 4</u> ), T <sub>J</sub> rising                                                                                      |                   | 165      |                   | °C    |

| Thermal Shutdown<br>Hysteresis                              | T <sub>SHDN_HYST</sub>        | ( <u>Note 4</u> )                                                                                                             |                   | 10       |                   | °C    |

| BUCK-BOOST CONTRO                                           | LLER                          |                                                                                                                               |                   |          |                   |       |

| Programmable V <sub>BUS</sub><br>Voltage Range              | V <sub>OUT</sub>              |                                                                                                                               | 3.3               |          | 21.0              | V     |

| V <sub>BUS</sub> Voltage Step Size                          | V <sub>STEP</sub>             | VBUS_HIRES = 0b (10-bit resolution mode)                                                                                      |                   | 20.51    |                   | mV    |

| - B03 go                                                    | - STEF                        | VBUS_HIRES = 1b (11-bit resolution mode)                                                                                      |                   | 10.255   |                   | IIIV  |

| V <sub>BUS</sub> Voltage Accuracy                           | V <sub>OUT_ACC</sub>          | 3.3V ≤ V <sub>OUT</sub> < vSafe5V, CV mode, no<br>load, VBUS_HIRES = 0b and 1b                                                | -3.03             |          | +3.03             | %     |

|                                                             | ·001_ACC                      | vSafe5V ≤ V <sub>OUT</sub> ≤ 21V, CV mode, no<br>load, VBUS_HIRES = 0b and 1b                                                 | -2.0              |          | +2.0              | 70    |

| V <sub>BUS</sub> Slew Rise and                              |                               | VBUS_HIRES = 0b                                                                                                               |                   | 0.2      |                   |       |

| Fall Times During<br>Transitions                            | <sup>t</sup> SLEW             | VBUS_HIRES = 1b                                                                                                               |                   | 0.1      |                   | mV/µs |

| Soft-Start Ramp Time                                        | <sup>t</sup> START            |                                                                                                                               | 4.0               | 6.5      | 9.0               | ms    |

| Minimum On-Time                                             | <sup>t</sup> ON_MIN           | Buck mode, 400kHz switching                                                                                                   |                   | 80       |                   | ns    |

| Minimum Off-Time                                            | toff_min                      | Boost mode, 400kHz switching                                                                                                  |                   | 120      |                   | ns    |

| Dead Time                                                   | DT                            | Rising and falling edges of DH_ to DL_<br>and DL_ to DH_                                                                      |                   | 17       |                   | ns    |

| DH Pullup Resistance                                        | R <sub>DH_PU</sub>            | V <sub>BIAS</sub> = 5V, I <sub>DH</sub> = -100mA                                                                              |                   | 2        | 4                 | Ω     |

| PARAMETER                                       | SYMBOL                   | CONDITIONS                                                                                                                                                                  | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| DH Pulldown<br>Resistance                       | R <sub>DH_PDWN</sub>     | V <sub>BIAS</sub> = 5V, I <sub>DH</sub> = +100mA                                                                                                                            |      | 1    | 2    | Ω     |

| DL Pullup Resistance                            | R <sub>DL_PU</sub>       | V <sub>BIAS</sub> = 5V, I <sub>DL</sub> = -100mA                                                                                                                            |      | 2    | 4    | Ω     |

| DL Pulldown Resistance                          | R <sub>DL_PDWN</sub>     | V <sub>BIAS</sub> = 5V, I <sub>DL</sub> = +100mA                                                                                                                            |      | 1    | 2    | Ω     |

| DL1, DL2 Leakage<br>Current                     | I <sub>DL_LKG</sub>      | V <sub>DL1</sub> = V <sub>DL2</sub> = 0 to 5V, T <sub>A</sub> = +25°C                                                                                                       |      |      | 1    | μA    |

| DH1 Leakage Current                             | IDH1_LKG                 | $V_{DH1} = V_{LX1} = 0V, T_A = +25^{\circ}C$                                                                                                                                |      |      | 1    | μA    |

| DH2 Leakage Current                             | I <sub>DH2_LKG</sub>     | $V_{DH2} = V_{LX2} = 0V, T_A = +25^{\circ}C$                                                                                                                                |      |      | 1    | μA    |

| BUCK-BOOST OSCILLA                              | TOR                      |                                                                                                                                                                             |      |      |      |       |

|                                                 |                          | FSW[1:0] = 00b                                                                                                                                                              | 200  | 220  | 240  |       |

| Buck-Boost Oscillator                           | f                        | FSW[1:0] = 01b                                                                                                                                                              | 270  | 300  | 330  | ]     |

| Switching Frequency                             | fsw                      | FSW[1:0] = 10b                                                                                                                                                              | 350  | 400  | 450  | kHz   |

|                                                 |                          | FSW[1:0] = 11b                                                                                                                                                              | 2000 | 2200 | 2400 |       |

| SYNC Input Frequency<br>Lock Range              | <sup>f</sup> synci_range | External frequency lock range with<br>respect to internal f <sub>SW</sub> setting when<br>SYNC_DIR = 1b (SYNC Input mode).<br>SYNC input duty cycle range is 30% to<br>70%. | 80   |      | 120  | %     |

| Spread-Spectrum                                 |                          | SS SEL[1:0] = 01b                                                                                                                                                           |      | ±3   |      |       |

| Frequency Modulation                            | SPS                      | SS_SEL[1:0] = 10b                                                                                                                                                           |      | ±6   |      | %     |

| Range (with respect to fsw)                     |                          | SS_SEL[1:0] = 11b                                                                                                                                                           |      | ±9   |      |       |

| Slope Compensation<br>Peak Ramp Voltage         | V <sub>SLOPE_PK</sub>    | Peak ramp voltage per switching period.<br>Default setpoint shown. Programmable<br>from 100mV to 800mV in steps of 100mV<br>with SLP[2:0] register.                         |      | 400  |      | mV    |

| BUCK-BOOST CURREN                               | T SENSE                  |                                                                                                                                                                             |      |      |      | 1     |

| Input Current-Limit<br>Threshold                | V <sub>OC1</sub>         | V <sub>CSP1</sub> - V <sub>CSN1</sub> rising                                                                                                                                |      | 50   | 60   | mV    |

| Output Runaway Limit<br>Threshold               | V <sub>OC2</sub>         | V <sub>CSP2</sub> - V <sub>OUT</sub> rising, V <sub>OUT</sub> > 0V                                                                                                          |      | 75   | 90   | mV    |

| CS Negative Limit<br>Threshold                  | V <sub>OC3</sub>         | $ V_{CSP2} - V_{OUT} $ rising, $V_{OUT} > 4.5V$                                                                                                                             | -26  | -20  | -14  | mV    |

| 0.1.1.0                                         | ILIM_OUT_1A              | $R_{CS3} = 5m\Omega$                                                                                                                                                        | 0.9  | 1.0  | 1.1  |       |

| Output Overcurrent<br>Limit Accuracy            | ILIM_OUT_3A              | $R_{CS3} = 5m\Omega$                                                                                                                                                        | 2.85 | 3.00 | 3.15 | А     |

| Limit / looding y                               | ILIM_OUT_5A              | $R_{CS3} = 5m\Omega$                                                                                                                                                        | 4.75 | 5.00 | 5.25 |       |

| Output Overcurrent<br>Programmable Step<br>Size | I <sub>OUT_LSB</sub>     | R <sub>CS3</sub> = 5mΩ                                                                                                                                                      |      | 25   |      | mA    |

| Output Overcurrent<br>Protection                | IOUT_OCP                 | R <sub>CS3</sub> = 5mΩ                                                                                                                                                      |      | 6.4  |      | А     |

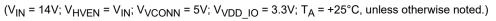

| CABLE COMPENSATIO                               | N                        |                                                                                                                                                                             |      |      |      |       |

| Cable Comp Loop Gain<br>– V <sub>ADJ</sub>      | V <sub>ADJ</sub>         | 3mV < V <sub>OUT</sub> - V <sub>CSN2</sub> < 30mV, GAIN[5:0]<br>= 111111b                                                                                                   | 99   | 103  | 107  | V/V   |

| R-Cable<br>Adjustment/LSB                       | R <sub>COMP_LSB</sub>    |                                                                                                                                                                             |      | 8.2  |      | mΩ    |

| HVEN AND SYNC I/O PI                            | NS                       |                                                                                                                                                                             |      |      |      |       |

$(V_{IN} = 14V, V_{HVEN} = V_{IN}, V_{VCONN} = 5V, V_{VDDIO} = 3.3V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . (*Note 3*)

| PARAMETER                                                        | SYMBOL                         | CONDITIONS                                                                                           | MIN                | ТҮР      | MAX                | UNITS |

|------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------|--------------------|----------|--------------------|-------|

| SYNC Input Logic-High                                            | VIH <sub>SYNC</sub>            | V <sub>SYNC</sub> rising                                                                             | 2.0                |          |                    | V     |

| SYNC Input Logic-Low                                             | VIL <sub>SYNC</sub>            | V <sub>SYNC</sub> falling                                                                            |                    |          | 0.5                | V     |

| HVEN Rising Threshold                                            | V <sub>HVEN_R</sub>            | V <sub>HVEN</sub> rising threshold; guaranteed logic-<br>high level when V <sub>HVEN</sub> ≥ 1.8V    | 1.20               | 1.45     | 1.80               | V     |

| HVEN Falling Threshold                                           | V <sub>HVEN_F</sub>            | V <sub>HVEN</sub> falling threshold; guaranteed<br>logic-low level when V <sub>HVEN</sub> ≤ 1.0V     | 1.00               | 1.26     | 1.60               | V     |

| HVEN Input Leakage                                               | I <sub>HVEN_LKG</sub>          | V <sub>HVEN</sub> = 5.5V, T <sub>A</sub> = +25°C                                                     |                    |          | +1                 | μΑ    |

| SYNC Pulldown<br>Resistance                                      | R <sub>SYNC-PD</sub>           |                                                                                                      |                    | 1        |                    | MΩ    |

| V <sub>CONN</sub> SWITCH                                         |                                |                                                                                                      |                    |          |                    |       |

| V <sub>CONN</sub> Valid Voltage<br>Range                         | V <sub>VCONN</sub>             |                                                                                                      | 3.0                |          | 5.5                | V     |

| V <sub>CONN</sub> Switch On-<br>Resistance                       | R <sub>ON_VCONN</sub>          | $V_{VCONN} = 5.0V$ and $V_{VCONN} = 3.3V$ ,<br>$I_{HVCC} = 0.25A$                                    |                    | 400      | 800                | mΩ    |

| V <sub>CONN</sub> Programmable<br>Overcurrent Threshold<br>(Low) | IVCONN_OCP_<br>L               | Measured on CC1 and CC2;<br>V <sub>VCONN</sub> = 5.0V or 3.3V                                        | 50                 |          | 500                | mA    |

| V <sub>CONN</sub> OCP Low<br>Programmable Step<br>Size           | IVCONN_OCP_<br>L_LSB           |                                                                                                      |                    | 50       |                    | mA    |

| V <sub>CONN</sub> Overcurrent<br>Threshold (High)                | IVCONN_OCP_                    | Measured on CC1 and CC2;<br>V <sub>VCONN</sub> = 3.3V and V <sub>VCONN</sub> = 5.0V                  |                    | 750      |                    | mA    |

| V <sub>CONN</sub> Start-up Time at<br>90%                        | <sup>t</sup> vconn_on          | Time from $V_{CONN}$ switch enable to CC<br>settled at 90% of final value with $V_{VCONN}$<br>= 5.0V |                    | 300      |                    | μs    |

| V <sub>CONN</sub> Leakage<br>Current                             | IVCONN_LKG                     | V <sub>CONN</sub> switch disabled; V <sub>VCONN</sub> = 5.0V                                         |                    |          | 5                  | μA    |

| V <sub>CONN</sub> Fast UV<br>Comparator Trip<br>Threshold        | V <sub>VCONN_FAS</sub><br>T_UV | $V_{CONN}$ enabled, measured at $V_{CONN}$ pin, $V_{VCONN}$ falling                                  | Setpoint<br>- 0.25 | Setpoint | Setpoint<br>+ 0.25 | V     |

| USB TYPE-C/CURRENT                                               | LEVEL CHARAG                   | CTERISTICS                                                                                           |                    |          |                    |       |

| CC DFP Default Current<br>Source                                 | IDFP_DEF_CC                    |                                                                                                      | 64                 | 80       | 96                 | μA    |

| CC DFP 1.5A Current<br>Source                                    | I <sub>DFP1.5_CC</sub>         |                                                                                                      | 166                | 180      | 194                | μA    |

| CC DFP 3.0A Current<br>Source                                    | I <sub>DFP3.0_CC</sub>         |                                                                                                      | 304                | 330      | 356                | μA    |

| CC PASS-THROUGH AN                                               | IALOG SWITCHI                  | ES                                                                                                   |                    |          |                    |       |

| Analog Signal Range                                              |                                |                                                                                                      | 0                  |          | 5.5                | V     |

| CC Switch On-<br>Resistance                                      | R <sub>ON_CC</sub>             | Resistance from CC1 to HVCC1 or CC2 to HVCC2                                                         |                    | 4        |                    | Ω     |

| HVCC OV Protection<br>Trip Threshold                             | V <sub>OV_HVCC</sub>           |                                                                                                      | 5.65               | 5.80     | 5.95               | V     |

| HVCC OV Blanking<br>Timeout Period                               | t <sub>FP_HVCC</sub>           | From OV condition to switch opened                                                                   |                    | 1.0      |                    | μs    |

| CC Switch ON Leakage                                             | ICC_ON_LKG                     | CC switch ON, CC pullup voltage 5.5V;<br>leakage to GND                                              |                    |          | 10                 | μA    |

| HVCC Pin OFF                                                     | IHVCC_OFF_L                    | HVCC switch OFF; V HVCC_ = 20V;<br>HVCC_ pins leakage to GND                                         |                    |          | 25                 | μA    |

$(V_{IN} = 14V, V_{HVEN} = V_{IN}, V_{VCONN} = 5V, V_{VDDIO} = 3.3V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . (*Note 3*)

| $(V_{IN} = 14V, V_{HVEN} = V_{II}$         | N, $V_{VCONN} = 5V$ , | $V_{VDDIO} = 3.3V,$ | $T_A = -40^{\circ}C$ to | +125°C, unle | ss otherwise n | oted. Typical va | alues are at |

|--------------------------------------------|-----------------------|---------------------|-------------------------|--------------|----------------|------------------|--------------|

| T <sub>A</sub> = +25°C. ( <u>Note 3</u> )) |                       |                     |                         |              |                |                  |              |

| PARAMETER                                           | SYMBOL                         | CONDITIONS                                                                                                                        | MIN   | TYP   | MAX                     | UNITS |

|-----------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------------------------|-------|

| HVCC Open<br>Termination Impedance                  | Z <sub>OPEN</sub>              | Impedance to GND                                                                                                                  | 500   |       |                         | kΩ    |

| HVCC Discharge<br>Resistance                        | R <sub>DCH_HVCC</sub>          |                                                                                                                                   |       | 3.0   | 6.2                     | kΩ    |

| USB PD BMC (MAX2543                                 | 2B ONLY)                       |                                                                                                                                   |       |       |                         |       |

| BMC Tx Rise Time                                    | t <sub>RISE</sub>              | 10% to 90% with no load on CC wires                                                                                               | 300   | 430   |                         | ns    |

| BMC Tx Fall Time                                    | t <sub>FALL</sub>              | 90% to 10% with no load on CC wires                                                                                               | 300   | 430   |                         | ns    |

| BMC Tx Swing                                        | V <sub>SWING</sub>             | Applies to no load and with max load defined by cable/receiver model                                                              | 1.05  | 1.125 | 1.2                     | V     |

| BMC Driver Output<br>Impedance                      | ZDRIVER                        | Source output impedance                                                                                                           | 33    | 48    | 75                      | Ω     |

| BMC Receiver Noise<br>Filter                        | <sup>t</sup> RXFILTER          | Time constant of noise filter in Rx path                                                                                          | 100   |       |                         | ns    |

| Receiver Input<br>Impedance                         | ZBMCRX                         |                                                                                                                                   |       | 2     |                         | MΩ    |

| Receiver Detect Rising<br>Threshold                 | V <sub>BMCRxDet_</sub> Rt<br>h |                                                                                                                                   | 0.645 | 0.685 | 0.725                   | V     |

| Receiver Detect Falling<br>Threshold                | V <sub>BMCRxDet_</sub> Ft<br>h |                                                                                                                                   | 0.565 | 0.605 | 0.645                   | V     |

| DP, DM ANALOG USB S                                 | WITCHES                        |                                                                                                                                   |       |       |                         |       |

| Analog Signal Range                                 | V <sub>D_RANGE</sub>           |                                                                                                                                   | 0     |       | V <sub>DD_US</sub><br>B | V     |

| Protection Trip<br>Threshold                        | V <sub>OV_D_L</sub>            | V <sub>HVDP</sub> /V <sub>HVDM</sub> rising; only for<br>AUTO_CDP_DCP_MODE[1:0] = 01b<br>(Auto-CDP mode)                          | 3.65  | 3.85  | 4.05                    | V     |

|                                                     | V <sub>OV_D_H</sub>            | V <sub>HVDP</sub> /V <sub>HVDM</sub> rising; all other modes                                                                      | 4.0   | 4.15  | 4.30                    |       |

| Protection Response<br>Time                         | <sup>t</sup> FP_D              | $V_{HVEN} = 4.0V, V_{HVDP} = V_{HVDM} = 3.3V$<br>to 4.3V step, $R_L = 15k\Omega$ on DP and DM,<br>delay to $V_{DP} = V_{DM} < 3V$ |       | 2     |                         | μs    |

| Data Switch Differential<br>Bandwidth               | BW <sub>D_DIFF</sub>           | USB TEST_PACKET at 240MHz<br>fundamental; -3dB BW                                                                                 |       | 1000  |                         | MHz   |

| On-Resistance Switch A                              | R <sub>ON_SA</sub>             | $I_L = 10$ mA, $V_D_= 0$ V to $V_{DD_USB}$ ,<br>$V_{DD_USB} = 3.3$ V                                                              |       | 4     | 8                       | Ω     |

| On-Resistance Match<br>between Channels<br>Switch A | ∆R <sub>ON_SA</sub>            | I <sub>L</sub> = 10mA, V <sub>D</sub> _ = 1.5V or 3.0V                                                                            |       |       | 0.25                    | Ω     |

| On-Resistance Flatness<br>Switch A                  | R <sub>FLAT(ON)</sub> A        | I <sub>L</sub> = 10mA, V <sub>D</sub> _ = 0V or 0.4V                                                                              |       |       | 0.25                    | Ω     |

| On-Resistance of<br>HVDP/HVDM Short                 | R <sub>SHORT</sub>             | V <sub>DP</sub> = 1V, I <sub>DM</sub> = 500µA                                                                                     |       | 90    | 180                     | Ω     |

| HVDP/HVDM On-<br>Leakage Current                    | I <sub>HVD_ON</sub>            | V <sub>HVDP</sub> = V <sub>HVDM</sub> = 3.6V or 0V                                                                                | -7    |       | +7                      | μΑ    |

| HVDP/HVDM Off-<br>Leakage Current                   | I <sub>HVD_OFF</sub>           | $V_{HVDP}$ = 18V or $V_{HVDM}$ = 18V,<br>$V_{DP}$ = $V_{DM}$ = 0V                                                                 |       |       | 100                     | μA    |

| DP/DM Off-Leakage<br>Current                        | I <sub>D_OFF</sub>             | $V_{HVDP} = V_{HVDM} = 18V, V_{DP} = V_{DM} = 0V$                                                                                 | -1    |       | +1                      | μA    |

| USB 2.0 HOST CHARGE                                 | R DETECTION,                   | HVDP/HVDM                                                                                                                         |       |       |                         |       |

| Input Logic-High                                    | V <sub>IH_CD</sub>             |                                                                                                                                   | 2.0   |       |                         | V     |

| Input Logic-Low                                     | V <sub>IL_CD</sub>             |                                                                                                                                   |       |       | 0.8                     | V     |

| PARAMETER                                                        | SYMBOL                       | CONDITIONS                                                                                            | MIN                          | TYP    | MAX                          | UNITS |

|------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------|--------|------------------------------|-------|

| Data Sink Current                                                | I <sub>DAT_</sub> SINK       | V <sub>DAT_SINK</sub> = 0.25V to 0.4V                                                                 | 50                           | 85     | 150                          | μA    |

| Data Detect Voltage<br>High                                      | V <sub>DAT_REFH</sub>        |                                                                                                       | 0.4                          |        |                              | V     |

| Data Detect Voltage<br>Low                                       | V <sub>DAT_REFL</sub>        |                                                                                                       |                              |        | 0.25                         | V     |

| Data Detect Voltage<br>Hysteresis                                | V <sub>DAT_HYST</sub>        |                                                                                                       |                              | 60     |                              | mV    |

| Data Source Voltage                                              | V <sub>DAT_SRC</sub>         | Ι <sub>SRC</sub> = 200μΑ                                                                              | 0.5                          |        | 0.7                          | V     |

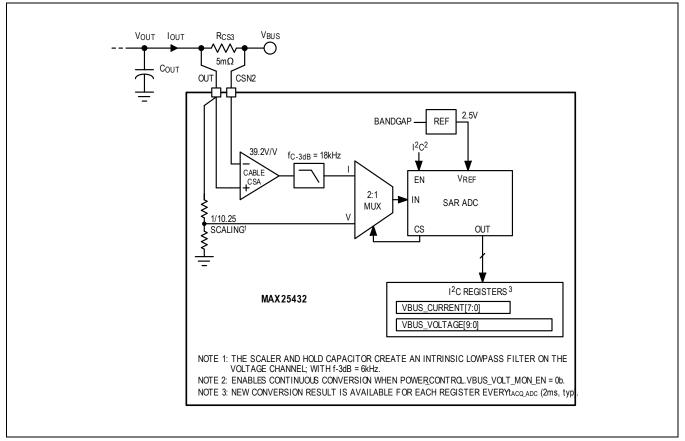

| V <sub>BUS</sub> ADC                                             |                              |                                                                                                       |                              |        |                              |       |

| ADC Resolution                                                   | Res_ADC                      |                                                                                                       |                              | 10     |                              | bits  |

| ADC V <sub>BUS</sub> LSB                                         | V <sub>OUT_LSB_AD</sub><br>C | VBUS_VOLTAGE[9:0] register                                                                            |                              | 25     |                              | mV    |

| ADC I <sub>BUS</sub> LSB                                         | IOUT_LSB_ADC                 | VBUS_CURRENT[7:0] register                                                                            |                              | 50     |                              | mA    |

| ADC Acquisition Time<br>(V <sub>BUS</sub> and I <sub>BUS</sub> ) | t <sub>ACQ_ADC</sub>         | Total time for both acquisitions                                                                      |                              | 2      |                              | ms    |

| VBUS OUTPUT MONITO                                               | RS                           |                                                                                                       |                              |        |                              |       |

| V <sub>BUS</sub> OV                                              | V <sub>BUS_OV_PR</sub><br>OG | Programmable in 1.25% steps from<br>+8.75% to +17.5% by changing<br>the VBUS_OV_THRESH[2:0] register  |                              | +12.5% |                              | %     |

| V <sub>BUS</sub> UV                                              | V <sub>BUS_UV_PR</sub><br>OG | Programmable in 1.25% steps from -<br>8.75% to -17.5% by changing the<br>VBUS_UV_THRESH[2:0] register |                              | -12.5% |                              | %     |

| V <sub>BUS</sub> Removal Detect<br>Threshold                     | vSafe0V                      | Falling                                                                                               | 0.6                          | 0.75   | 0.8                          | V     |

| V <sub>BUS</sub> Removal Detect<br>Hysteresis                    | vSafe0V                      | Rising hysteresis                                                                                     |                              | 0.05   |                              | V     |

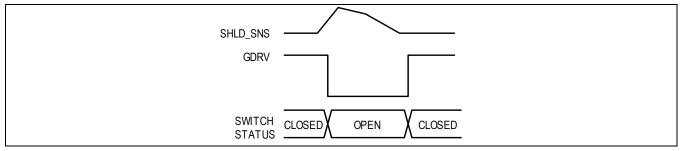

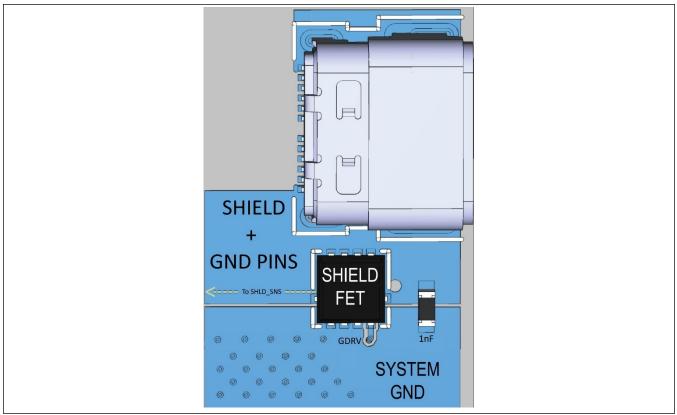

| SHIELD FET CONTROL                                               |                              |                                                                                                       |                              |        |                              |       |

| GDRV Unloaded Output<br>Voltage High                             | V <sub>GDRV,H</sub>          |                                                                                                       | 4.5                          |        | 5.5                          | V     |

| GDRV Output Voltage<br>High                                      | V <sub>GDRV,LOAD</sub>       | I <sub>GDRV</sub> = 10μA (sink)                                                                       | 4                            |        |                              | V     |

| GDRV Output Voltage<br>Low                                       | V <sub>GDRV,L</sub>          | I <sub>SINK</sub> = 1mA (pullup)                                                                      |                              |        | 0.8                          | V     |

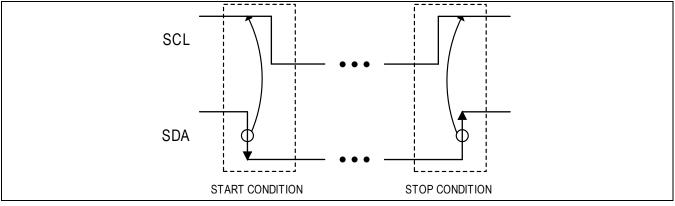

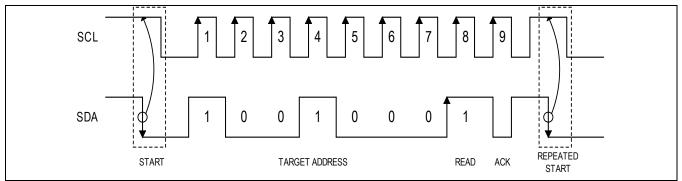

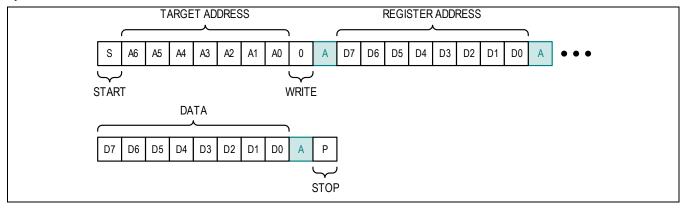

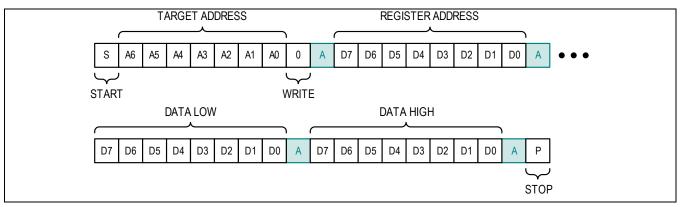

| I <sup>2</sup> C DIGITAL INPUTS (SE                              | DA, SCL) AND V               | DD_IO SUPPLY INPUT                                                                                    |                              |        |                              |       |

| Input Leakage Current<br>(SCL, SDA)                              | II2C_LKG                     | V <sub>PIN</sub> = 5.5V, 0V                                                                           | -5                           |        | 5                            | μA    |

| Logic-High (SCL, SDA)                                            | V <sub>IH</sub>              |                                                                                                       | 0.7 x<br>V <sub>VDD_IO</sub> |        |                              | V     |

| Logic-Low (SCL, SDA)                                             | V <sub>IL</sub>              |                                                                                                       |                              |        | 0.3 x<br>V <sub>VDD_IO</sub> | V     |

| Hysteresis (SCL, SDA)                                            | V <sub>I2C_HYST</sub>        |                                                                                                       |                              | 300    |                              | mV    |

| V <sub>DD_IO</sub> Input Voltage<br>Range                        | V <sub>VDD_IO</sub>          |                                                                                                       | 1.8                          |        | 5.0                          | V     |

| ADDR RESISTOR CONV                                               | 'ERTER                       |                                                                                                       |                              |        |                              |       |

| ADDR Current Leakage                                             | IADDR_LKG                    | V <sub>ADDR</sub> = 0 to 5V                                                                           |                              |        | ±5                           | μA    |

| Minimum Guaranteed<br>Decoding Window<br>Range                   | R <sub>ADDR_TOL</sub>        |                                                                                                       | -5                           |        | 5                            | %     |

$(V_{IN} = 14V, V_{HVEN} = V_{IN}, V_{VCONN} = 5V, V_{VDDIO} = 3.3V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . (*Note 3*))

| PARAMETER                               | SYMBOL              | CONDITIONS                          | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------|---------------------|-------------------------------------|------|-----|------|-------|

| DIGITAL OUTPUTS (ALE                    | RT, SDA)            |                                     |      |     |      |       |

| Output-High Leakage<br>Current          | I <sub>OH_LKG</sub> | Pull up 0V and 5.5V                 | -10  |     | 10   | μA    |

| Output Low Level                        | V <sub>OL</sub>     | Sinking 1mA                         |      |     | 0.4  | V     |

| I <sup>2</sup> C DYNAMIC CHARACT        | ERISTICS            |                                     |      |     |      | -     |

| Clock Frequency                         | fscl                |                                     |      |     | 1000 | kHz   |

| Hold Time (Repeated)<br>START Condition | <sup>t</sup> HD;STA |                                     | 0.26 |     |      | μs    |

| CLK Low Period                          | t <sub>LOW</sub>    |                                     | 0.5  |     |      | μs    |

| CLK High Period                         | t <sub>HIGH</sub>   |                                     | 0.26 |     |      | μs    |

| Setup Time Repeated<br>START Condition  | <sup>t</sup> SU;STA |                                     | 0.26 |     |      | μs    |

| DATA Hold Time                          | t <sub>HD:DAT</sub> |                                     | 0    |     |      | ns    |

| DATA Valid Time                         | <sup>t</sup> SU;DAT |                                     |      |     | 0.45 | μs    |

| DATA Setup Time                         | t <sub>SU;DAT</sub> |                                     | 50   |     |      | ns    |

| Setup Time for STOP<br>Condition        | t <sub>SU;STO</sub> |                                     | 0.26 |     |      | μs    |

| Bus-Free Time Between STOP and START    | t <sub>BUF</sub>    |                                     | 0.5  |     |      | μs    |

| Noise Suppression on SCL and SDA        | NS <sub>I2C</sub>   |                                     |      | 50  |      | ns    |

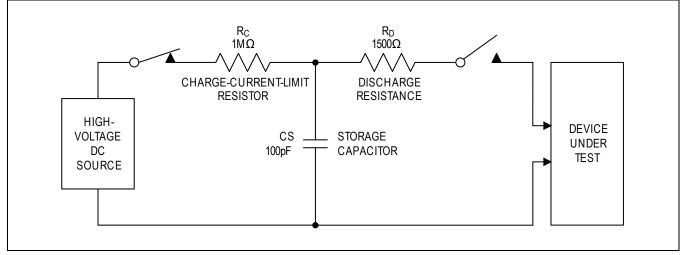

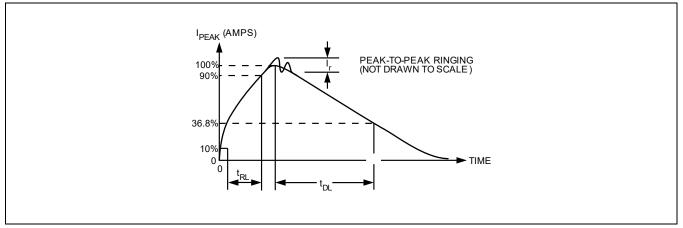

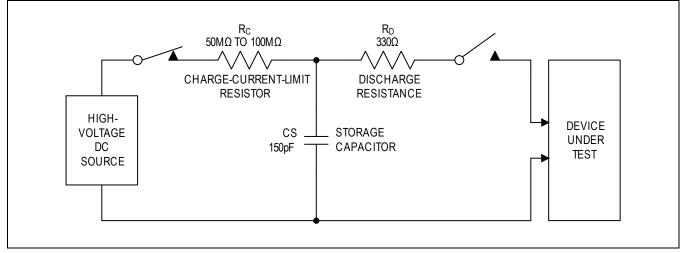

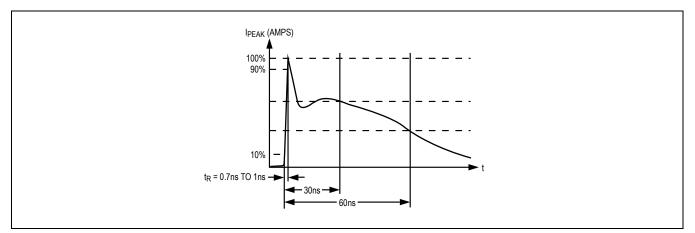

| ESD PROTECTION (ALL                     | PINS)               |                                     |      |     |      |       |

| ESD Protection Level                    | V <sub>ESD</sub>    | Human Body Model (HBM)              |      | ±2  |      | kV    |

| ESD PROTECTION (HVD                     | P, HVDM, HVC        | C1, HVCC2, SHLD_SNS)                |      |     |      |       |

|                                         |                     | ISO 10605 Air Gap (330pF, 2kΩ)      |      | ±15 |      |       |

|                                         |                     | ISO 10605 Contact (330pF, 2kΩ)      |      | ±8  |      |       |

| ESD Protection Level                    | V <sub>ESD</sub>    | IEC 61000-4-2 Air Gap (150pF, 330Ω) |      | ±15 |      | kV    |

|                                         |                     | IEC 61000-4-2 Contact (150pF, 330Ω) |      | ±8  |      |       |

$(V_{IN} = 14V, V_{HVEN} = V_{IN}, V_{VCONN} = 5V, V_{VDDIO} = 3.3V, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ . (*Note 3*))

**Note 3:** Specifications with minimum and maximum limits are 100% production tested at T<sub>A</sub> = +25°C and are guaranteed over the operating temperature range by design and characterization. Actual typical values may vary and are not guaranteed.

Note 4: Guaranteed by design and bench characterization. Limits are not production tested.

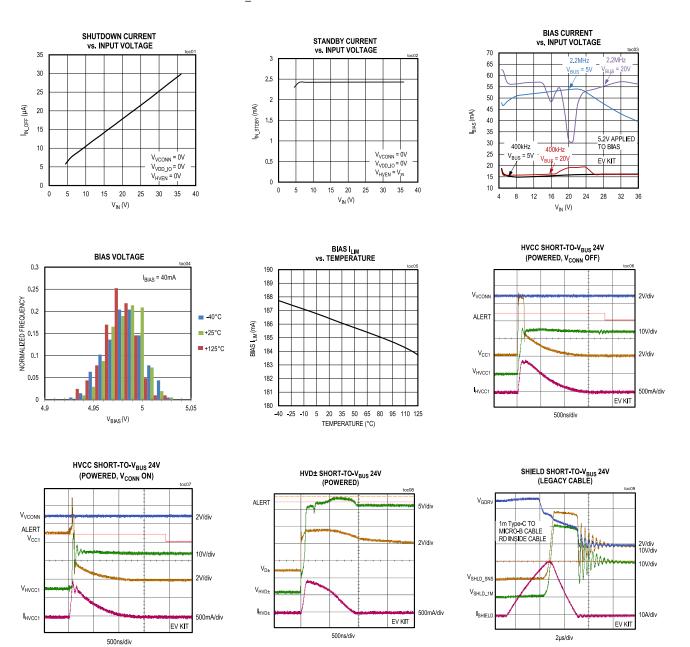

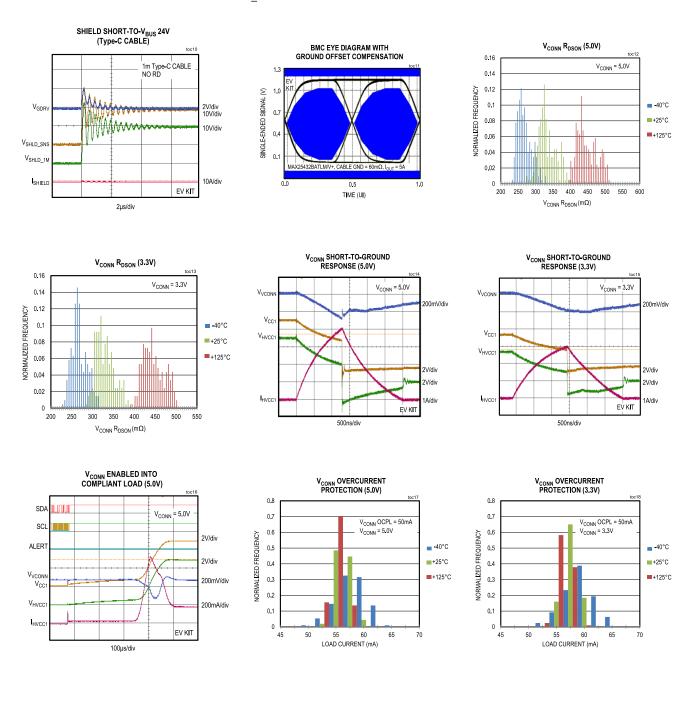

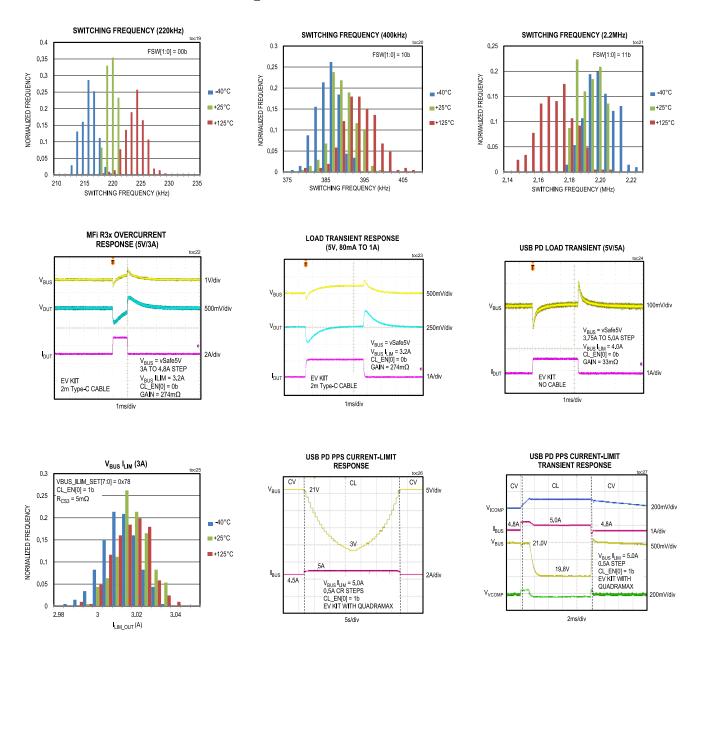

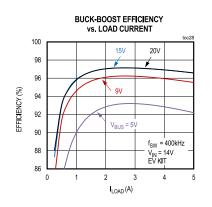

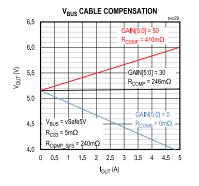

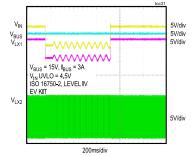

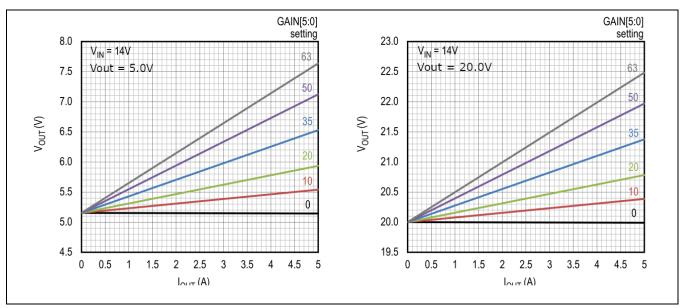

# **Typical Operating Characteristics**

( $V_{IN}$  = 14V;  $V_{HVEN}$  =  $V_{IN}$ ;  $V_{VCONN}$  = 5V;  $V_{VDD_{-}IO}$  = 3.3V;  $T_A$  = +25°C, unless otherwise noted.)

### (V<sub>IN</sub> = 14V; V<sub>HVEN</sub> = V<sub>IN</sub>; V<sub>VCONN</sub> = 5V; V<sub>VDD\_IO</sub> = 3.3V; T<sub>A</sub> = +25°C, unless otherwise noted.)

### (V<sub>IN</sub> = 14V; V<sub>HVEN</sub> = V<sub>IN</sub>; V<sub>VCONN</sub> = 5V; V<sub>VDD\_IO</sub> = 3.3V; T<sub>A</sub> = +25°C, unless otherwise noted.)

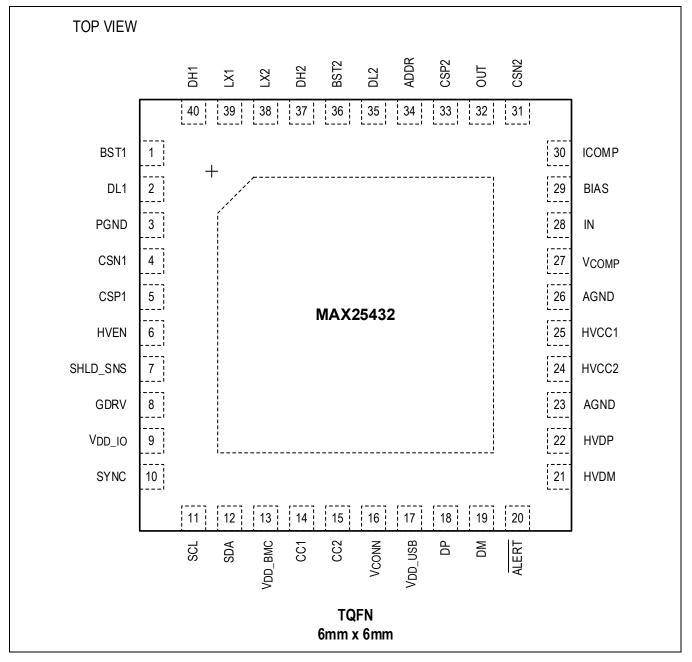

# **Pin Configurations**

### MAX25432

# **Pin Descriptions**

| PIN | NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BST1                | Bootstrap Capacitor Pin for High-Side Driver of LX1 Node. Connect a 0.1µF capacitor between BST1 and LX1.                                                                                                                                                                                                                                                                                                                                                                                    |

| 2   | DL1                 | Buck Low-Side Gate Drive Output. Connect to the gate of Qb1 external N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | PGND                | Buck-Boost Power Ground. Connect directly to GND. Connect to GND copper underneath IC.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4   | CSN1                | Negative Terminal of the Input High-Side Current-Sense Amplifier. Connect CSN1 as close to R <sub>CS1</sub> as possible using a Kelvin sense routing.                                                                                                                                                                                                                                                                                                                                        |

| 5   | CSP1                | Positive Terminal of the Input High-Side Current-Sense Amplifier. Connect CSP1 as close to R <sub>CS1</sub> as possible using a Kelvin sense routing.                                                                                                                                                                                                                                                                                                                                        |

| 6   | HVEN                | High-Voltage Enable Input. Driving HVEN high powers up the IC. This pin can be connected directly to battery voltage or car accessory power. This pin can also be driven by a 3.3V or 5V general-purpose output from a microcontroller.                                                                                                                                                                                                                                                      |

| 7   | SHLD_SN<br>S        | Shield Sense Pin.<br>SSTB devices: in order to protect against shield short-to-battery events, connect SHLD_SNS to the drain<br>of the external shield N-channel FET, which is connected to the SHIELD and GND pins of the USB Type-<br>C receptacle.<br>All MAX25432B devices have optional USB PD physical layer (PHY) ground offset compensation input.<br>Connect to downstream Type-C captive cable ground sense line.<br>For all other devices, or if not used, connect to the IC GND. |

| 8   | GDRV                | Shield FET Gate Drive Output. Active on all MAX25432 devices. Refer to GDRV Truth Table. Connect to the gate of an external N-channel FET to let the MAX25432 control the ground connection on the downstream Type-C connector. If not used, connect a $1M\Omega$ resistor from GDRV to the IC GND.                                                                                                                                                                                          |

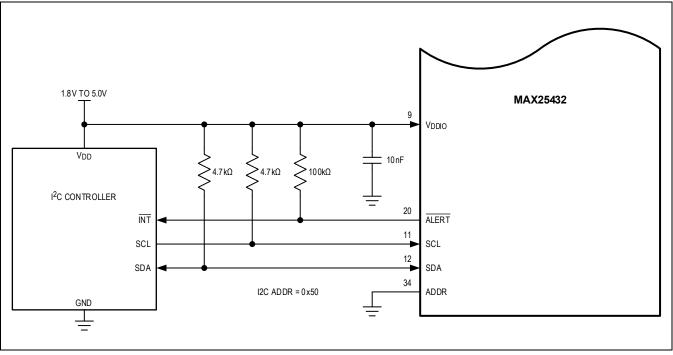

| 9   | V <sub>DD_IO</sub>  | External Input Supply for I <sup>2</sup> C Interface. Bypass with 10nF ceramic capacitor to AGND.                                                                                                                                                                                                                                                                                                                                                                                            |

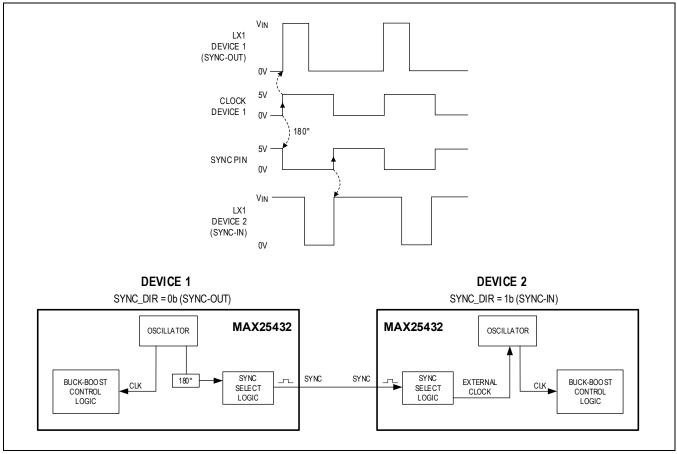

| 10  | SYNC                | Optional Switching Frequency Input/Output for Synchronization with Other Switching Regulators. Leave as an input and tie to the IC GND if not used.                                                                                                                                                                                                                                                                                                                                          |

| 11  | SCL                 | I <sup>2</sup> C Clock Pin. Connect to V <sub>DD_IO</sub> through a pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12  | SDA                 | I <sup>2</sup> C Data Pin. Connect to V <sub>DD_IO</sub> through a pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13  | V <sub>DD_BMC</sub> | MAX25432A: Connect $V_{DD_BMC}$ to AGND.<br>MAX25432B: Internal 1.125V Regulated Supply Output. Powers the biphase mark coding (BMC) Tx driver output. Bypass with a 1µF ceramic capacitor to AGND. Do not connect external loads to $V_{DD_BMC}$ .                                                                                                                                                                                                                                          |

| 14  | CC1                 | MAX25432A: Protected CC1. Connect to upstream CC1 configuration channel of the external USB PD controller.<br>MAX25432B: No Connect.                                                                                                                                                                                                                                                                                                                                                         |

| 15  | CC2                 | MAX25432A: Protected CC2. Connect to upstream CC2 configuration channel of the external USB PD controller.<br>MAX25432B: No Connect.                                                                                                                                                                                                                                                                                                                                                         |

| 16  | V <sub>CONN</sub>   | $V_{CONN}$ Input Supply. Connect to BIAS or an external 5V or 3.3V supply. Bypass with a 10µF ceramic capacitor to GND when connected to a 3.3V supply. Bypass with a 1µF ceramic capacitor to GND when connected to BIAS or a 5V supply.                                                                                                                                                                                                                                                    |

| 17  | V <sub>DD_USB</sub> | Internal 3.3V Regulated Supply Output. Bypass $V_{DD_USB}$ to GND with a 1µF ceramic capacitor. Do not connect external loads to $V_{DD_USB}$ .                                                                                                                                                                                                                                                                                                                                              |

| 18  | DP                  | Protected D+ USB 2.0 Data Path. For charging downstream port (CDP) applications, connect to the low-<br>voltage USB transceiver or HUB IC D+ connection. For dedicated charging port (DCP) applications, tie to<br>the DM pin.                                                                                                                                                                                                                                                               |

| 19  | DM                  | Protected D- USB 2.0 Data Path. For CDP applications, connect to the low-voltage USB transceiver or HUB IC D- connection. For DCP applications, tie to the DP pin.                                                                                                                                                                                                                                                                                                                           |

| 20  | ALERT               | Open-Drain Interrupt Output. Indicates alerts to the I <sup>2</sup> C controller. Connect a 100k $\Omega$ pullup from ALERT to V <sub>DD_IO</sub> .                                                                                                                                                                                                                                                                                                                                          |

| 21  | HVDM                | High-Voltage-Tolerant D- Connection to Downstream USB Type-C Connector or Captive Cable.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22  | HVDP                | High-Voltage-Tolerant D+ Connection to Downstream USB Type-C Connector or Captive Cable.                                                                                                                                                                                                                                                                                                                                                                                                     |

### MAX25432

| 23, 26 | AGND              | Analog Ground Pin (IC GND). Connect directly to GND; tie to GND pour underneath the IC.                                                                                                                                                                                                                                                          |

|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24     | HVCC2             | High-Voltage-Tolerant CC2 Connection to Downstream USB Type-C Connector or Captive Cable.                                                                                                                                                                                                                                                        |

| 25     | HVCC1             | High-Voltage-Tolerant CC1 Connection to Downstream USB Type-C Connector or Captive Cable.                                                                                                                                                                                                                                                        |

| 27     | V <sub>COMP</sub> | Voltage Loop Error Amplifier Output. Connect the external compensation network of the voltage feedback loop between V <sub>COMP</sub> and AGND.                                                                                                                                                                                                  |

| 28     | IN                | Supply Input for Main IC Power and Internal BIAS Linear Regulator. Bypass IN to GND locally with 1µF and 100nF ceramic capacitors (one of each).                                                                                                                                                                                                 |

| 29     | BIAS              | Regulated Output of the Internal 5.0V LDO. BIAS powers the internal circuitry. Bypass with a 4.7µF ceramic capacitor from BIAS to AGND.                                                                                                                                                                                                          |

| 30     | ICOMP             | Error Amplifier Output for the PPS Current Loop. Connect the external compensation network of the PPS current loop between I <sub>COMP</sub> and AGND.                                                                                                                                                                                           |

| 31     | CSN2              | Negative Terminal of the PPS Current-Sense Amplifier. CSN2 connects to the negative side of the $R_{CS3}$                                                                                                                                                                                                                                        |

| 51     | 00112             | sense resistor. Referenced to OUT.                                                                                                                                                                                                                                                                                                               |

| 32     | OUT               | Output Sense Pin. Negative terminal of the high-side output current-sense amplifier (output CSA), input to the internal feedback resistor network and positive terminal of the PPS CSA. Connect OUT as close to $R_{CS3}$ as possible using a Kelvin sense routing. OUT is also connected to the negative side of the sense resistor $R_{CS2}$ . |

| 33     | CSP2              | Positive Terminal of the High-Side Output Current-Sense Amplifier. Connect CSP2 as close to R <sub>CS2</sub> as possible using a Kelvin sense routing. Referenced to OUT.                                                                                                                                                                        |

| 34     | ADDR              | I <sup>2</sup> C Target Address Selection. Connect a resistor to ground to select the last two address bits. See the<br><u>I2C Target Addressing (ADDR Pin)</u> section for selecting the ADDR resistor.                                                                                                                                         |

| 35     | DL2               | Boost Low-Side Gate Drive Output. Connect to the gate of the Qb2 external N-channel FET.                                                                                                                                                                                                                                                         |

| 36     | BST2              | Bootstrap Capacitor Pin for High-Side Driver of the LX2 Node. Connect a 0.1µF capacitor from BST2 to LX2.                                                                                                                                                                                                                                        |

| 37     | DH2               | Boost High-Side Gate Drive Output. Connect to the gate of the Qt2 external N-channel FET.                                                                                                                                                                                                                                                        |

| 38     | LX2               | Boost-Side Switching Output Node. LX2 is Hi-Z when the buck-boost is disabled.                                                                                                                                                                                                                                                                   |

| 39     | LX1               | Buck-Side Switching Output Node. LX1 is Hi-Z when the buck-boost is disabled.                                                                                                                                                                                                                                                                    |

| 40     | DH1               | Buck High-Side Gate Drive Output. Connect to the gate of the Qt1 external N-channel FET.                                                                                                                                                                                                                                                         |

|        | EP                | Exposed Pad. EP must be connected to the ground plane of the PCB for power dissipation. Not electrically connected internally.                                                                                                                                                                                                                   |

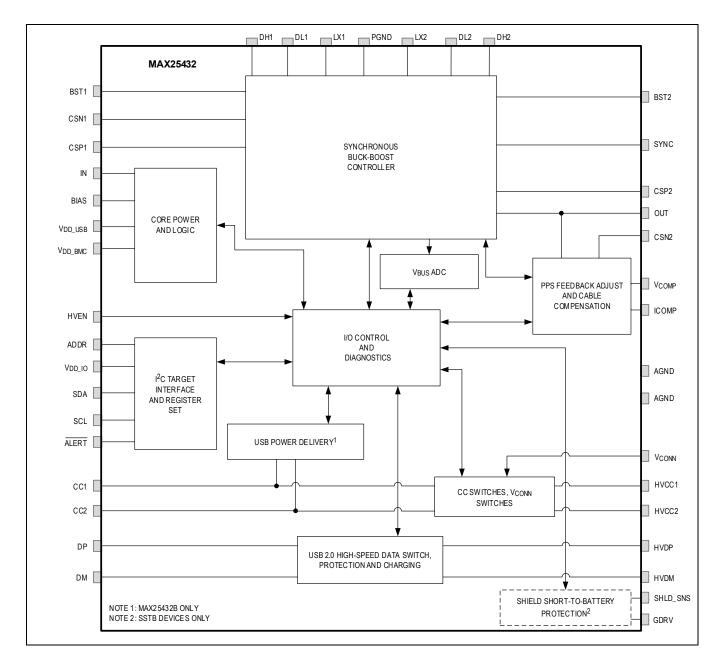

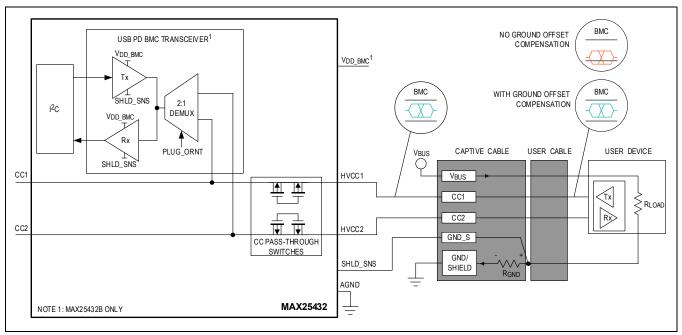

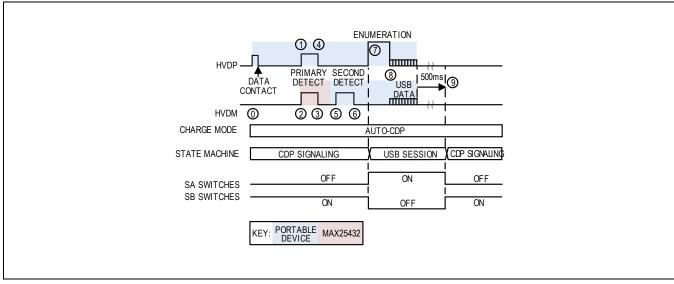

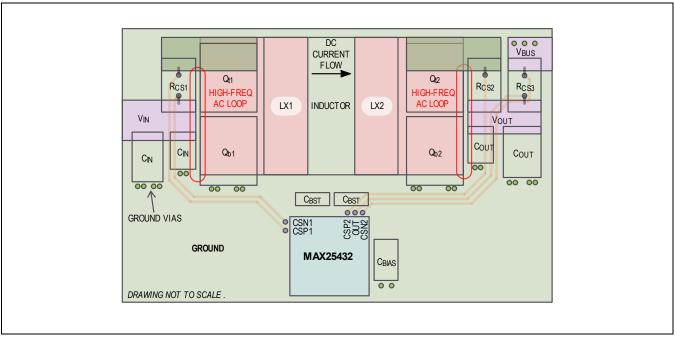

### **Functional Diagrams**

### **Functional Block Diagram**

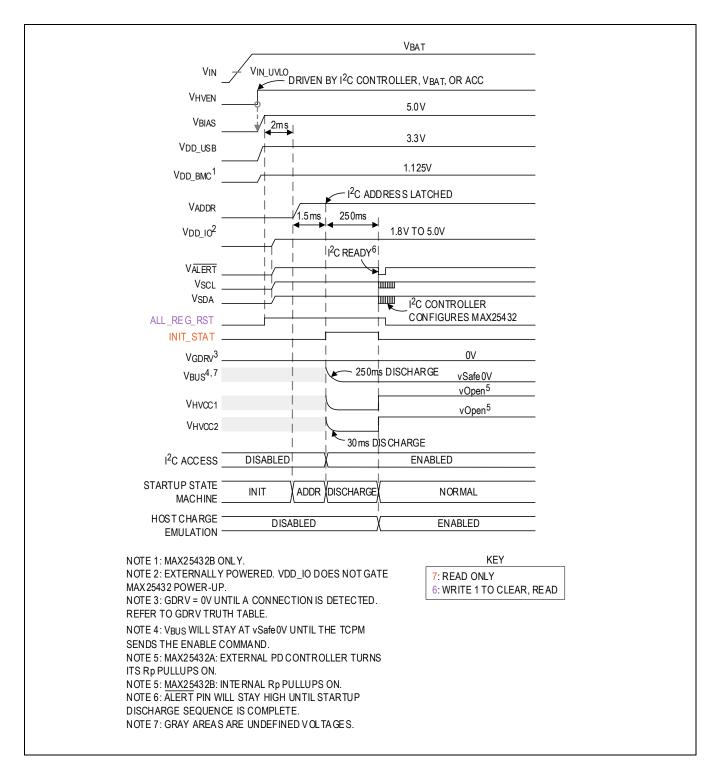

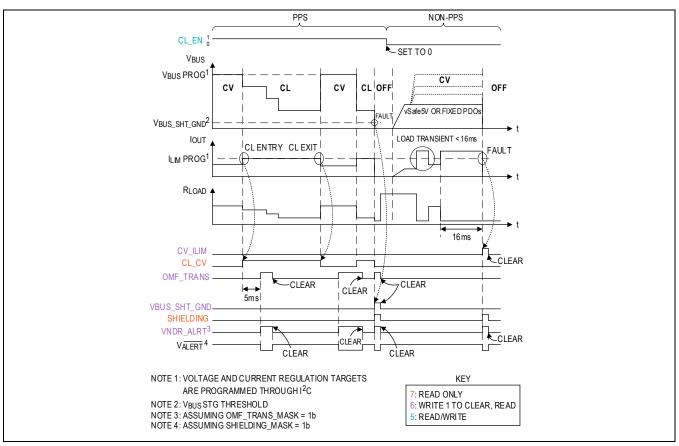

### **Power-Up Sequence**

### **Detailed Description**

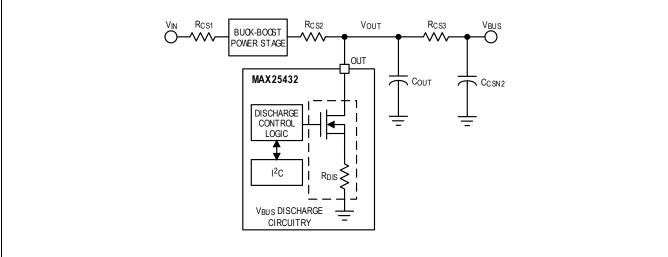

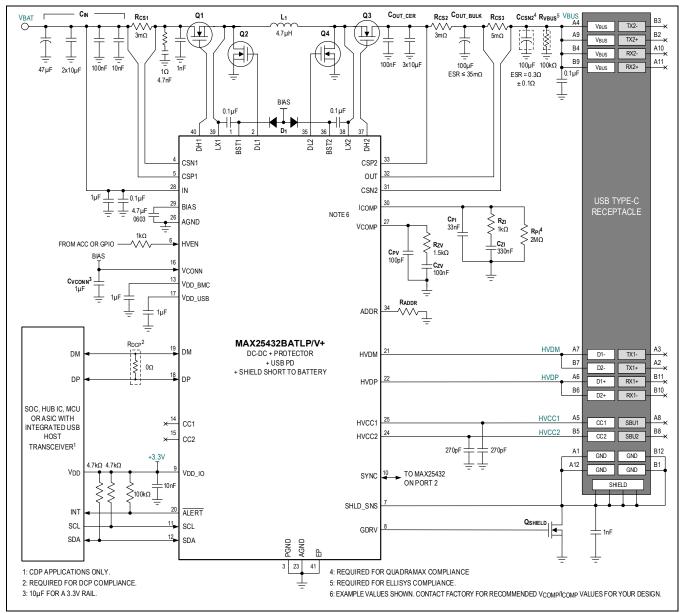

The MAX25432 is a single-chip USB PD charging and protection solution with PPS for multimedia hub, rear-seat entertainment module, and head-unit applications. Combined with either a microcontroller or a USB PD controller it is a two-chip solution for dedicated charging module applications. The MAX25432 provides all the functionality for USB PD car battery to  $V_{BUS}$  regulation, configuration channel communication, and USB 2.0 Hi-Speed protection. It can optionally provide BC1.2 host charge emulation. The device integrates all of the protection needed in an automotive USB PD application.

The MAX25432 offers the design engineer two options for firmware development. The MAX25432B can operate with a system-on-chip (SoC), USB hub IC, or microcontroller, whereas the MAX25432A is designed to operate with a USB PD controller. The MAX25432 evaluation (EV) kit offers a platform where the design engineer can begin early firmware development.

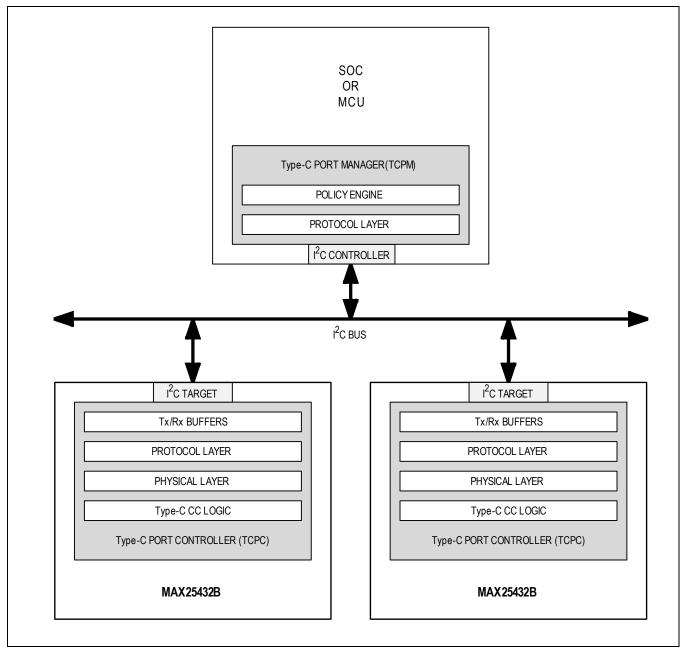

Recent advancements in the automotive infotainment market demand high-efficiency and low footprint power delivery solutions. The push for lower BOM cost has driven USB power applications to integrate more features and responsibilities into a single IC. The proliferation of USB PD-based battery-powered portable devices has resulted in an increase in the number of USB ports in an automobile to charge the passenger's devices. These multiport charging modules can unnecessarily increase per-port cost when a dedicated MCU with firmware is used for each port. The MAX25432B's architecture minimizes per-port cost by enabling a single microcontroller running a USB Type-C policy manager (TCPM) firmware to control multiple MAX25432B devices which integrate a USB Type-C port controller (TCPC). The TCPM and TCPC communicate with each other using I<sup>2</sup>C.

The MAX25432B is an advanced automotive integrated USB PD solution that combines the TCPC along with other USB features such as Type-C, PD with PPS, BC1.2, Apple, and Samsung<sup>®</sup> charging port emulator. All MAX25432 devices implement Analog Devices' proprietary current-mode buck-boost H-bridge controller that can achieve a target USB output voltage with high-efficiency while operating over a wide range of input voltage. The MAX25432 buck-boost controller has robust protection mechanisms such as overvoltage (OV), undervoltage (UV), overcurrent, short-to-ground (STG), short-to-battery, overtemperature, and automotive ESD protections. The MAX25432 implements internal gate drivers to drive external power FETs to accommodate high-power USB requirements. The MAX25432 has an intelligent voltage-adjustment circuit that can adjust the output voltage of the buck-boost converter such that the voltage on the USB receptacle is within specifications regardless of the output current.