**MAX20458**

Click here to ask an associate for production status of specific part numbers.

## 36V Boost Controller with A 3.5A Synchronous Buck Converter for Automotive Applications

#### **General Description**

The MAX20458 is an automotive grade PMIC that includes a 3.5A synchronous buck converter and an asynchronous boost controller with 2.1MHz and 400kHz options. The boost controller can be used to provide power to buck converters and keep them in regulation during coldcrank operation down to 2V battery input. The IC operates with an input voltage supply from 3.5V to 36V and can operate in dropout conditions by running at 95% duty cycle. It is intended for applications with mid- to high-power requirements that operate at a wide input voltage range such as during automotive cold-crank or engine stop-start conditions.

High switching frequency up to 2.1MHz allows small external components, reduced output ripple, and guarantees no AM band interference. The switching frequency is fixed at 400kHz or 2.1MHz. FSYNC input programmability enables three modes for optimized performance: forced fixed-frequency operation, skip mode with ultra-low quiescent current, and phase-locked synchronization to an external clock. The spread spectrum option minimizes EMI interference.

The IC features the power-OK indicators for buck converters and undervoltage lockout for each power rail. Protection features include cycle-by-cycle current limit and thermal shutdown. The MAX20458 is specified for operation over the -40°C to +125°C automotive temperature range.

#### **Applications**

- Automotive Start-Stop System

- Instrument Cluster

- Distributed DC Power Systems

- Navigation and Radio Head Units

#### **Benefits and Features**

- Meets Stringent OEM Module Power Consumption and Performance Specifications

- 10µA Supply Current with 5V Buck On

- · OUT Can Be Either 5V or 3.3V

- 30µA Supply Current with All Regulators On

- Enables Crank-Ready Designs

- Output Voltages in Regulation Through Cold Crank Down to 2V Battery Voltage

- · Wide Input Supply Range from 3.5V to 36V

- EMI Reduction Features Reduce Interference with Sensitive Radio Bands without Sacrificing Wide Input Voltage Range

- 20ns (typ) Minimum On-Time Guarantees Skip-Free Operation for 3.3V Output at 2.1MHz

- · Spread-Spectrum Option

- Phase-Locked Loop (PLL) Frequency Synchronization

- Integration and Thermally Enhanced Packages Save Board Space and Cost

- A 2.1MHz Buck Converters with Asynchronous Boost Controller

- Current-Mode Controller with Forced Fixed Frequency and Skip Modes

- Thermally Enhanced 5mm x 5mm, 28-Pin TQFN-EP Package

- Protection Features Improve System Reliability

- Supply Undervoltage Lockout

- · Overtemperature and Short-Circuit Protection

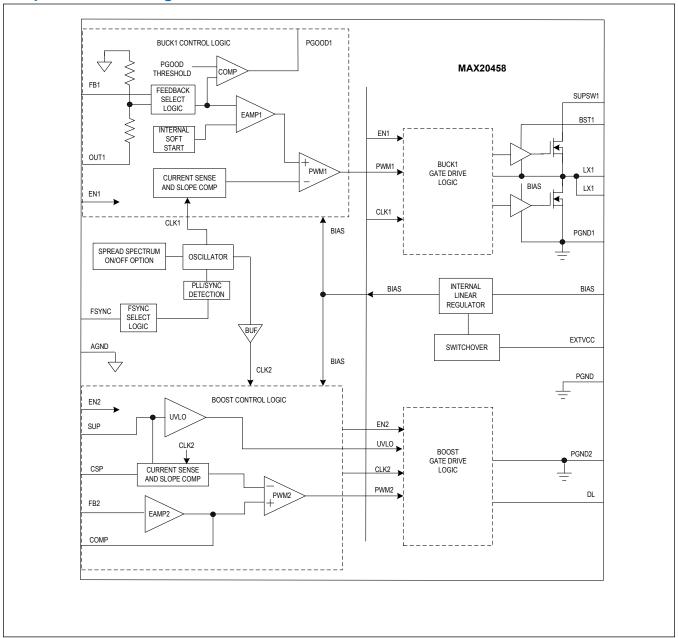

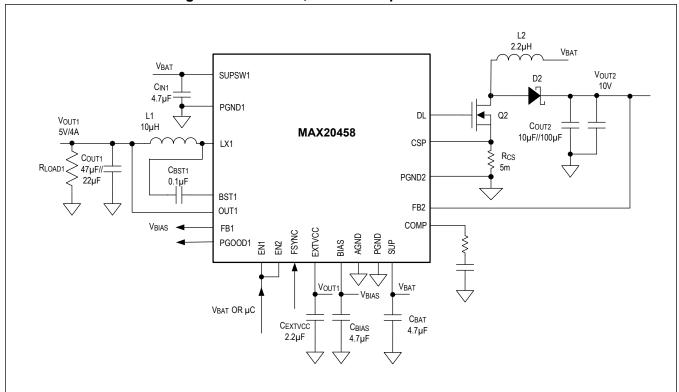

### **Simplified Block Diagram**

#### **Absolute Maximum Ratings**

| SUP, SUPSW1, FB2, EN1, EN2 to AGNE | 00.3V to 40V           |

|------------------------------------|------------------------|

| OUT1 to AGND                       | 0.4V to 15V            |

| BIAS, FSYNC, PGOOD1, FB1 to AGND   | 0.3V to 6V             |

| EXTVCC, COMP, CSP to AGND          | 0.3V to (BIAS + 0.3V)  |

| DL to PGND2                        | -0.3V to (BIAS + 0.3V) |

| LX1 to PGND10                      | .3 to (SUPSW1 + 0.3V)  |

| BST1 to LX1 (Note 1)               | 0.3V to 6V             |

| PGND1, PGND2 to AGND                     | 0.3V to 0.3V   |

|------------------------------------------|----------------|

| Continuous Power Dissipation (TQFN (TA = | = +70°C,       |

| derate 28.6mW/°C above +70°C))           | 2286mW         |

| Operating Temperature Range              | 40°C to 125°C  |

| Storage Temperature Range                | 65°C to +150°C |

| Lead Temperature(soldering,10s)          | 300°C          |

| Soldering Temperature (reflow)           |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### 28 PIN TQFN

| Package Code                                           | T2855Y+5C        |  |  |  |

|--------------------------------------------------------|------------------|--|--|--|

| Outline Number                                         | <u>21-100130</u> |  |  |  |

| Land Pattern Number 90-0027                            |                  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                   |                  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 27°C/W           |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 3°C/W            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

**Note 1:** Self-protected against transient voltages exceeding these limits for  $\leq$  50ns under normal operation and loads up to the maximum rated output current.

**Note 2:** Package thermal resistances were obtained using the Evaluation Kit. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{SUP} = V_{SUPSW1} = 14V, V_{EN} = 14V, T_{J} = -40^{\circ}C$  to +150°C, unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ ) (Notes 3 and 4)

| PARAMETER                        | SYMBOL           | CONDITIONS                                                                                                                                                        | MIN  | TYP | MAX | UNITS           |  |

|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-----------------|--|

| SYNCHRONOUS STEP-DOWN CONVERTERS |                  |                                                                                                                                                                   |      |     |     |                 |  |

|                                  |                  | Normal Operation                                                                                                                                                  | 3.5  |     | 36  |                 |  |

| Supply Voltage Range             | V <sub>SUP</sub> | With preboost after initial start-up condition is satisfied                                                                                                       | 2.05 |     | 36  | V               |  |

| Supply Current                   |                  | V <sub>EN1</sub> = V <sub>EN2</sub> = 0V                                                                                                                          |      | 1   | 5   |                 |  |

|                                  | I <sub>IN</sub>  | V <sub>EN1</sub> = V <sub>SUP</sub> , V <sub>OUT1</sub> = 5V, V <sub>EN2</sub> = 0V, V <sub>EXTVCC</sub> = 5V, No Switching                                       |      | 10  | 18  | μA              |  |

|                                  | ·IIN             | V <sub>EN1</sub> = V <sub>SUP</sub> , V <sub>OUT1</sub> = 5V, V <sub>EN2</sub> = V <sub>SUP</sub> , V <sub>EXTVCC</sub> = 5V, V <sub>FB2</sub> > 1V, No Switching |      | 30  |     | ] <b>P</b> '' ( |  |

### **Electrical Characteristics (continued)**

$(V_{SUP} = V_{SUPSW1} = 14V, V_{EN} = 14V, T_{J} = -40^{\circ}C$  to +150°C, unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ ) (Notes 3 and 4)

| PARAMETER                          | SYMBOL                     | CONDITIONS                                                                              | MIN   | TYP   | MAX   | UNITS |

|------------------------------------|----------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                                    |                            | V <sub>FB1</sub> = V <sub>BIAS</sub> , V <sub>OUT1</sub> = 5V, PWM mode                 | 4.9   | 5     | 5.1   |       |

| Duald Fixed Output                 |                            | V <sub>FB1</sub> = V <sub>BIAS</sub> , V <sub>OUT1</sub> = 5V, skip mode                | 4.85  | 5     | 5.15  | 1     |

| Buck1 Fixed Output<br>Voltage      | V <sub>OUT1</sub>          | V <sub>FB1</sub> = V <sub>BIAS</sub> , V <sub>OUT1</sub> = 3.3V, PWM mode               | 3.234 | 3.3   | 3.366 | V     |

|                                    |                            | V <sub>FB1</sub> = V <sub>BIAS</sub> , V <sub>OUT1</sub> = 3.3V, skip mode              | 3.2   | 3.3   | 3.4   |       |

| Output Voltage<br>Adjustable Range |                            | Buck1 (Note 5)                                                                          | 1     |       | 14    | V     |

| Regulated Feedback<br>Voltage      | V <sub>FB1</sub>           |                                                                                         | 0.985 | 1     | 1.015 | V     |

| Feedback Leakage<br>Current        | I <sub>FB1</sub>           | T <sub>A</sub> = +25°C                                                                  |       | 0.01  | 1     | μA    |

| Feedback Line<br>Regulation Error  |                            | $V_{SUP} = 3.5V \text{ to } 36V, V_{FB1} = 1V$                                          |       | 0.01  |       | %/V   |

| Dead time                          |                            | Buck1 (Note 5)                                                                          |       | 3     |       | ns    |

| Maximum Duty Cycle                 |                            | Buck1                                                                                   | 95    |       |       | %     |

| Minimum On-Time                    | ton_min                    | Buck1 (Note 5)                                                                          |       | 20    |       | ns    |

| PWM Switching<br>Frequency Range   | f <sub>SW</sub>            | OTP Option of 400kHz (see the <u>Ordering</u> <u>Information</u> for exact part number) |       | 2.1   |       | MHz   |

| Switching Frequency<br>Accuracy    |                            |                                                                                         | 1.9   | 2.1   | 2.32  | MHz   |

| Current-Limit                      |                            |                                                                                         | 4.5   | 6     | 7.5   | Α     |

| Soft-Start Ramp Time               |                            | Buck1 fixed soft-start time regardless of frequency.                                    | 3     | 5.5   | 7     | ms    |

| LX1 Leakage Current                |                            | $V_{SUPSW1}$ = 6V, $V_{LX1}$ = $V_{PGND1}$ or $V_{SUPSW1}$ , $T_A$ = +25°C              |       | 0.001 | 5     | μА    |

| High-Side Switch On Resistance     | R <sub>ON_H</sub><br>BUCK1 | I <sub>LX1</sub> = 1A, V <sub>BIAS</sub> = 5V                                           |       | 50    |       | mΩ    |

| Low-Side Switch On Resistance      | R <sub>ON_L</sub><br>BUCK1 | I <sub>LX1</sub> = 1A, V <sub>BIAS</sub> = 5V                                           |       | 45    |       | mΩ    |

| PGOOD1 Threshold                   | V <sub>PGOOD_H</sub>       | % of V <sub>OUT</sub> _, rising                                                         | 93    | 95    | 97    | - %   |

| r GOODT Tillesiloid                | V <sub>PGOOD_F</sub>       | % of V <sub>OUT</sub> _, falling                                                        | 91.5  | 93.5  | 95.5  | /0    |

| PGOOD1 Leakage<br>Current          |                            | V <sub>PGOOD1</sub> = 5V, T <sub>A</sub> = +25°C                                        |       | 0.01  | 1     | μА    |

| PGOOD1 Output Low Voltage          |                            | I <sub>SINK</sub> = 1mA                                                                 |       |       | 0.2   | V     |

| PGOOD1, Debounce<br>Time           |                            | Fault Detection, Rising and Falling                                                     |       | 20    |       | μs    |

| PGOOD1 Assertion<br>Time           |                            | PGOOD1 Low to High (Note 5)                                                             |       | 0     |       | ms    |

| STEP-UP CONTROLLER                 | R .                        |                                                                                         |       |       |       |       |

| Minimum On Time                    | t <sub>ONBST</sub>         | (Note 5)                                                                                |       | 60    |       | ns    |

| Minimum Off Time                   | toffbst                    |                                                                                         |       | 60    |       | ns    |

| Current Limit                      | V <sub>LIMBST</sub>        | V <sub>CS</sub> - V <sub>PGND2</sub>                                                    | 40    | 50    | 60    | mV    |

### **Electrical Characteristics (continued)**

$(V_{SUP} = V_{SUPSW1} = 14V, V_{EN} = 14V, T_{J} = -40^{\circ}C$  to +150°C, unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ ) (Notes 3 and 4)

| PARAMETER                           | SYMBOL                 | CONDITIONS                                                | MIN   | TYP                     | MAX   | UNITS |  |

|-------------------------------------|------------------------|-----------------------------------------------------------|-------|-------------------------|-------|-------|--|

| Undervoltage Lockout                | UVLO                   | Input Voltage Rising                                      |       | 4.5                     |       | V     |  |

| DL Pullup Resistance                |                        | V <sub>BIAS</sub> = 5V, I <sub>DL</sub> = -100mA          |       | 3                       | 6     | Ω     |  |

| DL Pulldown Resistance              |                        | V <sub>BIAS</sub> = 5V, I <sub>DL</sub> = 100mA           |       | 1                       | 2     | Ω     |  |

| Boost Feedback Voltage              | V <sub>FB2</sub>       | Pre-Boost Feedback Voltage, No Load on Boost Output       | 0.985 | 1.005                   | 1.025 | V     |  |

| Transconductance (from FB2 to COMP) | 9M_BOOST               | V <sub>FB2</sub> = 1.005V, V <sub>BIAS</sub> = 5V         | 130   | 230                     | 330   | μS    |  |

| Boost Fixed Output<br>Voltage       | V <sub>OUT2</sub>      | Contact factory for other available options               | 9.75  | 10                      | 10.2  | V     |  |

| Boost Load Regulation<br>Error      |                        | PWM Mode, Load from 1mA to 4A                             |       | 0.05                    |       | %/A   |  |

| FB3 Leakage Current                 | I <sub>FB2</sub>       | T <sub>A</sub> = +25°C                                    |       | 0.01                    | 1     | μA    |  |

| FSYNC INPUT                         |                        |                                                           |       |                         |       |       |  |

| FSYNC frequency                     |                        | Minimum sync pulse of 100ns, f <sub>OSC</sub> = 2.1MHz    | 1.8   |                         | 2.6   | MHz   |  |

| Range                               |                        | Minimum sync pulse of 1.5μs,<br>f <sub>OSC</sub> = 400kHz | 250   |                         | 550   | kHz   |  |

| FSYNC Switching                     |                        | High Threshold                                            | 1.4   |                         |       | V     |  |

| Thresholds                          |                        | Low Threshold                                             |       |                         | 0.4   | ]     |  |

| INTERNAL LDO BIAS AN                | ND EXTVCC              |                                                           |       |                         |       |       |  |

| Internal BIAS Voltage               |                        | V <sub>SUPSW1</sub> > 6V                                  |       | 5                       |       | V     |  |

| BIAS UVLO Threshold                 |                        | V <sub>BIAS</sub> rising                                  |       | 3.1                     | 3.3   | V     |  |

| BING OVEO THICSHOID                 |                        | V <sub>BIAS</sub> falling                                 | 2.4   | 2.6                     |       | v     |  |

| EXTVCC Operating Range              |                        |                                                           | 3.25  |                         | 5.5   | V     |  |

| EXTVCC Threshold                    | V <sub>TH_EXTVCC</sub> | EXTVCC rising, hysteresis = 110mV                         |       | 3                       | 3.25  | V     |  |

| THERMAL OVERLOAD                    |                        |                                                           |       |                         |       |       |  |

| Thermal Shutdown Temperature        |                        | (Note 5)                                                  |       | 170                     |       | °C    |  |

| Thermal Shutdown<br>Hysteresis      |                        | (Note 5)                                                  |       | 20                      |       | °C    |  |

| EN Logic Input                      |                        |                                                           |       |                         |       |       |  |

| High Threshold                      |                        | EN_                                                       | 1.8   |                         |       | V     |  |

| Low Threshold                       |                        | EN_                                                       |       |                         | 8.0   | V     |  |

| EN Input Bias Current               |                        | EN_ Logic Inputs Only, T <sub>A</sub> = +25°C             |       | 0.01                    | 1     | μA    |  |

| SPREAD SPECTRUM                     | SPREAD SPECTRUM        |                                                           |       |                         |       |       |  |

| Spread Spectrum                     |                        | Spread spectrum enabled                                   |       | f <sub>OSC</sub><br>±6% |       |       |  |

Note 3: Limits are 100% tested at +25°C. Limits over operating temperature range and relevant supply voltage are guaranteed by design and characterization. Typical values are at +25°C.

Note 4: The device is designed for continuous operation up to  $T_J = +125^{\circ}\text{C}$  for 95,000 hours and  $T_J = +150^{\circ}\text{C}$  for 5,000 hours

Note 5: Guaranteed by design, not production tested.

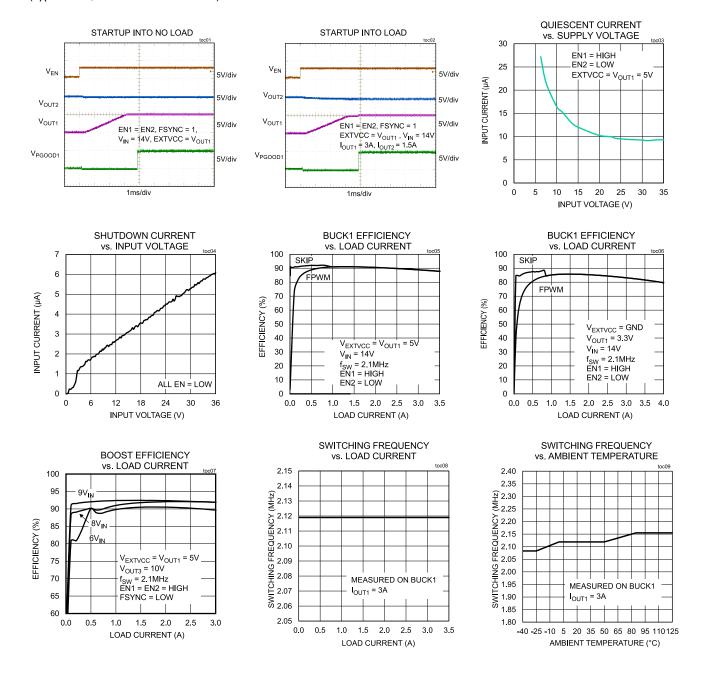

#### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

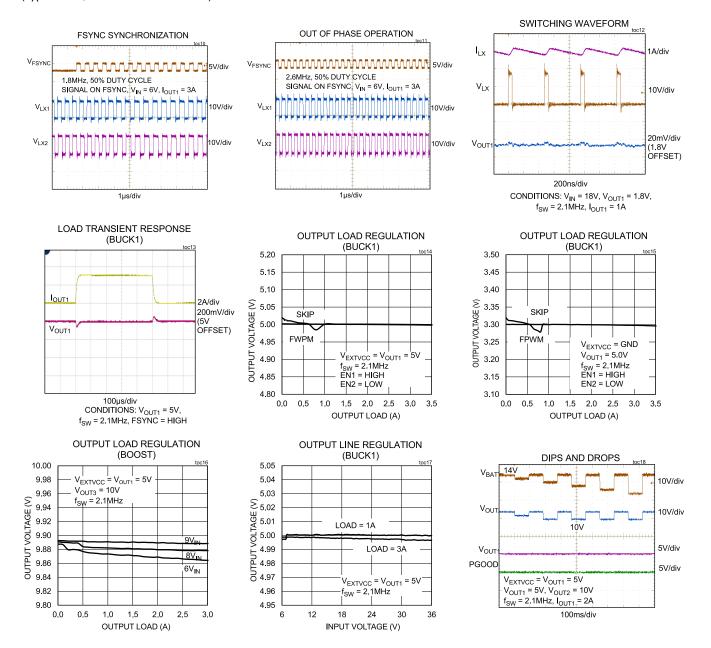

### **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

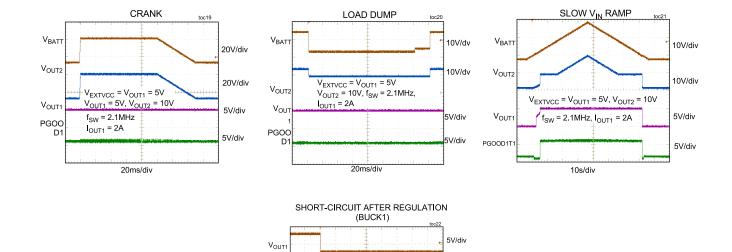

### **Typical Operating Characteristics (continued)**

V<sub>PGOOD1</sub>

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

10ms/div

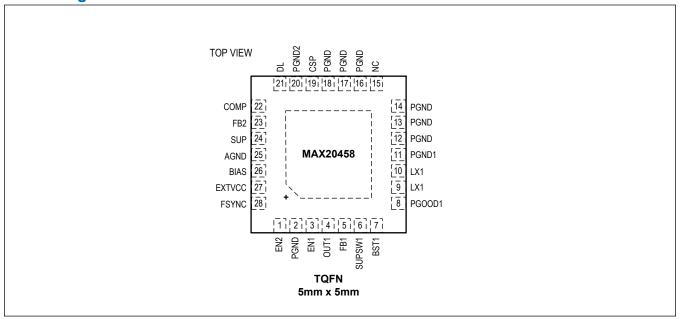

### **Pin Configuration**

### **Pin Description**

| PIN       | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | EN2    | High-Voltage Tolerant, Active-High Digital Enable Input for Boost Controller. Drive EN2 high to enable boost controller.                                                                                                                                                                                                                                                                |

| 2         | PGND   | Power Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 3         | EN1    | High-Voltage Tolerant, Active High Digital Enable Input for Buck 1. Drive EN1 high to enable Buck 1.                                                                                                                                                                                                                                                                                    |

| 4         | OUT1   | Output Sense Input for Buck 1. When using the internal preset 5V feedback divider, FB1 is connected to BIAS, and Buck 1 uses OUT1 to sense the output voltage.                                                                                                                                                                                                                          |

| 5         | FB1    | Feedback Input for Buck 1. Connect FB1 to BIAS for fixed output or to a resistor divider between OUT1 and AGND to adjust the output voltage between 1V and 14V. FB1 is regulated to 1V (typ) in adjustable version.                                                                                                                                                                     |

| 6         | SUPSW1 | Buck 1 Internal High-Side Switch Supply Input and BIAS LDO Input. Bypass SUPSW1 to PGND1 with a 4.7µF ceramic capacitor.                                                                                                                                                                                                                                                                |

| 7         | BST1   | Boost Flying Capacitor Connection for High-Side Gate Voltage of Buck 1. Connect a ceramic capacitor between BST1 and LX1.                                                                                                                                                                                                                                                               |

| 8         | PGOOD1 | Open Drain Power-Good Output for Buck 1. PGOOD1 is low if OUT1 falls below 93.5% (typ) of output regulation voltage. PGOOD1 becomes high impedance when OUT1 rises above 95% (typ) of its regulation voltage. PGOOD1 asserts low during soft-start and in shutdown. To obtain a logic signal, pull up PGOOD1 with an external resistor connected to a positive voltage lower than 5.5V. |

| 9, 10     | LX1    | Buck 1 Inductor Connection. Connect an inductor from LX1 to the Buck 1 output.                                                                                                                                                                                                                                                                                                          |

| 11        | PGND1  | Power Ground for Buck 1                                                                                                                                                                                                                                                                                                                                                                 |

| 12,13, 14 | PGND   | Power Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 15        | N.C.   | Not Connected                                                                                                                                                                                                                                                                                                                                                                           |

| 16,17,18  | PGND   | Power Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 19        | CSP    | Positive Current-Sense Input for Boost Controller. Connect CSP to the positive terminal of the current sense resistor.                                                                                                                                                                                                                                                                  |

### **Pin Description (continued)**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                  |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | PGND2  | Power Ground for Boost Controller. All the high current paths for the boost controller terminates to PGND2.                                                                                                                                               |

| 21  | DL     | Boost Controller N-Channel MOSFET Low Side Gate Driver Output                                                                                                                                                                                             |

| 22  | COMP   | Boost Error Amplifier Output. Connect COMP with an RC compensation network.                                                                                                                                                                               |

| 23  | FB2    | Boost Controller Feedback Input. Connect an external resistive divider from boost output to FB2, and FB2 to AGND to set the output voltage for the boost adjustable output option. Connect FB2 to boost output for the fixed boost output option.         |

| 24  | SUP    | Boost Controller Input Sense                                                                                                                                                                                                                              |

| 25  | AGND   | Quiet Analog Ground for the IC                                                                                                                                                                                                                            |

| 26  | BIAS   | 5V Internal Linear Regulator Output. Bypass BIAS to ground with a low ESR minimum 2.2μF ceramic capacitor. BIAS provides the power to the internal gate drive circuitry.                                                                                  |

| 27  | EXTVCC | Switchover Comparator Input. Connect a voltage between 3.25V and 5.5V to EXTVCC to power the IC and bypass the internal bias LDO. Connect EXTVCC to ground if EXTVCC is not used.                                                                         |

| 28  | FSYNC  | External Clock Synchronization Input. Synchronization operating frequency ratio is 1.                                                                                                                                                                     |

| -   | EP     | Exposed Pad. Connect EP to ground. Connecting EP to ground does not remove the requirement for proper ground connections to PGND and AGND. EP is attached with epoxy to the substrate of the die, making it an excellent path to remove heat from the IC. |

#### **Detailed Description**

The MAX20458 ICs are automotive-grade two output switching power supplies. Each device integrates a synchronous buck converters, and an asynchronous boost controller:

- 1. The Buck 1 converter provides a fixed 5V/3.3V output voltage, or an adjustable 1V to 14V output voltage option, and up to 3.5A continuous current capability.

- 2. The preboost controller has 10V fixed or adjustable output voltage options

Each power supply has its individual enable pin. Connect EN1, or EN2 directly to battery voltage, or to power supply sequencing logic to control each power supply on/off. In standby mode, the total supply current is reduced to  $30\mu$ A (typ). When both regulators are disabled, the total current drawn is further reduced to  $1\mu$ A.

#### Internal 5V BIAS LDO

An internal 5V BIAS LDO supplies the IC internal circuitry. SUPSW1 supplies the internal BIAS LDO. Bypass BIAS with a minimum  $2.2\mu$ F ceramic capacitor. To minimize the internal power dissipation, bypass BIAS to an external 5V rail using the EXTVCC pin.

#### **EXTVCC Switchover**

The internal linear regulator can be bypassed by connecting an external 3.25V to 5.5V supply, or one of the buck converter outputs to EXTVCC. With valid supply applied to EXTVCC, BIAS is internally switched to EXTVCC and the internal linear regulator turns off. This configuration has two main advantages:

- 1. Reduces IC internal power dissipation

- 2. Improves light-load efficiency as the internal supply current is scaled down proportionally to the duty cycle if connecting any buck output to EXTVCC

If V<sub>EXTVCC</sub> drops below 3V (typ), the internal regulator is enabled and BIAS is switched back to 5V.

#### **Switching Frequency/External Synchronization**

The MAX20458 provides an internal oscillator with 400kHz and 2.1MHz options. 2.1MHz frequency operation optimizes the application for the smallest component size, at the cost of lower efficiency. 400kHz frequency operation offers best overall efficiency at the expense of component size and board space.

Apply an external clock to FSYNC to enable frequency synchronization. The MAX20458 uses a phase-locked loop (PLL) to synchronize the internal oscillator to the external clock signal. The Buck 1 converter synchronizes its LX1 falling edge to the FSYNC rising edge, and the boost controller synchronizes the DL rising edge (or LX2 falling edge) to the FSYNC falling edge. The FSYNC signal should have a minimum 100ns high pulse width for 2.1MHz and minimum 1.5µs high pulse width for 400kHz.

#### **Spread Spectrum Option**

The ICs feature enhanced EMI performance with spread spectrum option. The spread spectrum is available as a factory option. When the spread spectrum is enabled, the operating frequency is varied  $\pm 6\%$  centered at switching frequency. The modulation signal is a triangular wave with a period of 110 $\mu$ s at 2.1MHz. Therefore, switching frequency ramps down 6% and back to 2.1MHz in 110 $\mu$ s after which the cycle repeats. For operations at 400kHz, the modulation signal scales proportionally (the 110 $\mu$ s modulation period for 2.1MHz increases to 110 $\mu$ s x 2.1MHz/0.4MHz = 577.5 $\mu$ s). The internal spread spectrum is disabled if the devices are synchronized to an external clock. However, the devices do not filter the input clock on the FSYNC pin and pass any modulation (including spread spectrum) present on the driving external clock.

#### **Overcurrent Protection**

The MAX20458 has a cycle-by-cycle current limit and includes hiccup mode to prevent any damage from overcurrent or short-circuit on both power channels. When the inductor current continuously hits the current limit at overcurrent on any channels, the output voltage starts decreasing. If the IC detects the output voltage drops below 0.7V, it turns off that channel. After waiting for about 10ms (2x soft-start time) of hiccup time, the IC restarts that channel in case the overcurrent or short-circuit condition is removed.

#### **Thermal Overload Protection**

Thermal overload protection limits total power dissipation in the ICs. When the junction temperature exceeds +170°C, an internal thermal sensor shuts down the ICs, allowing them to cool. The thermal sensor turns on the ICs again after the junction temperature cools by 20°C.

#### **Buck Converter**

The ICs provide a synchronous buck converter. The buck converter uses PWM, valley current mode control scheme, making it ideal for applications with high input voltages and low output voltages.

#### Undervoltage Lockout (UVLO)

The internal 5V BIAS LDO undervoltage-lockout (UVLO) circuitry inhibits switching if the BIAS voltage drops below its 2.6V (typ) UVLO falling threshold. Once the BIAS voltage rises above its UVLO rising threshold, 3.1V (typ), and EN1 enables the buck converter, Buck 1 starts switching and its output voltage begins soft-start.

#### **Soft-Start**

Drive EN1 high to enable Buck 1. The soft-start circuitry gradually ramps up the reference voltage during soft-start time (5ms typ) to reduce the input surge currents during startup. BIAS voltage must exceed its UVLO threshold (3.1V typ) before soft-start can be enabled.

#### **FSYNC Mode Selection**

Drive FSYNC low to enable skip mode. In skip mode, the high-side FET turns for fixed adaptable on-time (depend- ing on  $V_{OUT1}$ ,  $V_{SUP}$  and  $f_{SW}$ ). The high-side FET then turns off and the low-side FET turns on until the inductor current falls to the zero cross threshold. Once the low- side FET turns off by hitting the zero-crossing threshold, LX becomes high impedance and the output voltage keeps decreasing. When output voltage or FB voltage is detected below the set point, the new cycle starts by turning on the high-side FET again. In this way, the regulator switches only as needed to service load to improve system efficiency.

Drive FSYNC high to enable forced PWM (FPWM) mode. FPWM mode prevents the regulator from entering skip mode, by disabling the zero-cross detection of the inductor current. The benefit of FPWM mode is to keep the switch- ing frequency constant under all load conditions; however, FPWM operation diverts a considerable amount of the output current to PGND1, reducing the efficiency under light-load conditions. FPWM mode is useful for improving load-transient response and eliminating unknown fre- quency harmonics that can interfere with AM radio bands.

#### Frequency Foldback

Frequency Foldback is implemented in buck converters when operating only at 2.1MHz and when the internal fixed output voltage option is selected. This is useful in case the boost controller is not used to protect its input voltage during  $V_{SUP}$  transient drops. When the input voltage of buck converter drops close to the output volt- age, the converter runs at the maximum duty cycle and the high-side switch off period approaches minimum off time 100ns (typ). To prevent output voltage drifting out of regulation, frequency foldback is used to automatically reduce the switching frequency from 2.1MHz to 350kHz and maintain a high duty cycle of > 95% with 100ns (typ) off time. The frequency foldback occurs when the input voltage drops below a certain threshold calculated by formula of  $V_{SUPSW1}$  = 1.4 X  $V_{OUT1}$  (falling)

#### **High-Side Gate Driver Supply (BST1)**

The buck converter high-side MOSFET is turned on by closing an internal switch between BST1 and the gate of the high-side MOSFET and transferring the bootstrap capacitor's charge at BST1 to the gate of the high-side MOSFET. This charge refreshes when the high-side MOSFET turns off and the LX1 voltage drops down to ground, taking the negative terminal of the capacitor to the same potential. At this time, the bootstrap diode recharges the positive terminal of the bootstrap capacitor to BIAS voltage.

The selected n-channel high-side MOSFET determines the appropriate boost capacitance values (C<sub>BST1</sub> in the Typical Operating Circuit) according to the following equation:

$C_{BST1} = Q_G/\Delta V_{BST1}$

where  $Q_G$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST1}$  is the voltage variation allowed on the

high-side MOSFET driver after turn-on. Choose  $\Delta V_{BST}$  such that the available gate-drive voltage is not significantly degraded (e.g.,  $\Delta V_{BST1}$  = 100mV to 300mV) when determining C<sub>BST1</sub>. The boost capacitor should be a low-ESR ceramic capacitor. A minimum value of 100nF works in most cases.

#### **Power Good Indicator (PGOOD1)**

Each buck converter include a power good indicator to indi- cate the buck output voltage status. The PGOOD1 indicator can be used to enable circuit that is supplied by the cor- responding voltage rail, or to turn-on subsequent supplies.

PGOOD1 goes from low to high impedance when the corresponding regulator output voltage rises above 95% (typ) of its nominal regulation voltage. PGOOD1 goes low when Buck 1 output voltage drops below 93.5% (typ) of its nominal regulation voltage. Connect a  $10k\Omega$  (typ) pullup resistor from PGOOD1 to the relevant logic rail to level- shift the signal. PGOOD1 asserts low during soft-start, and when the buck converter is disabled.

#### **Boost Controller**

The MAX20458 ICs include an asynchronous current-mode boost controller with a fixed or adjustable output voltage option. It can be used independently, and it is also ideally suited for applications that need to stay fully functional during input voltage dropouts, typical for automotive cold-crank or start-stop. It can also be configured as a SEPIC to provide stable regulation voltage over a wide input voltage range. The boost converter is turned on by EN2 high. EN2 can be used for power-supply sequencing and implementing a boost timeout to prevent overheating the components used for the boost converter.

#### Soft-Start

The MAX20458 boost controller has an internal soft-start time of 1ms. After the controller detects valid BIAS voltage with EN2 high, it enters soft-start. During soft-start, the output voltage ramps linearly to its final value in 1ms.

#### Undervoltage Lockout (UVLO)

The boost controller UVLO circuitry monitors the SUP voltages to control boost on/off. The boost controller starts switching when UVLO circuitry detects the SUP voltage rises above 4.5V (typ). Once the controller switches, it keeps switching until the SUP voltage drops below 2.1V (min). This feature allows operation at cold-crank voltages as low as 2.0V battery voltage.

#### **Current Sense Limit**

A current-sense resistor ( $R_{CSP}$ ) connected between the source of the MOSFET and ground to set the current limit of the boost converter. The CSP input has a voltage trip level ( $V_{CSP}$ ) of 50mV (typ). The low 50mV current-limit threshold reduces the power dissipation in the current-sense resistor. When the voltage produced by the current in the inductor exceeds the current-limit comparator threshold, the MOSFET driver (DL) quickly terminates the on-cycle. In some cases, a short time-constant RC filter can be required to filter out the leading-edge spike on the sense waveform in addition to the internal blanking time. The amplitude and width of the leading edge spike depends on the pcb layout, gate capacitance, drain capacitance, and switching speed of the external MOSFET.

#### **N-MOSFET Driver**

DL drives the gate of an external n-channel MOSFET. The driver is powered by the 5V BIAS LDO if the EXTVCC switchover is not used. This makes the devices suitable for use with logic-level MOSFETs. DL can source and sink up to 1.67A peak current. The average current sourced by DL depends on the switching frequency and total gate charge of the external MOSFET.

#### **Applications Information**

#### **Buck Converter**

#### **Setting Output Voltage**

Connect FB1 to BIAS to enable fixed buck output voltages (5V or 3.3V) set by a preset internal resistive divider connected between OUT1 and AGND. To externally adjust the output voltage between 1V and 14V, connect a resistive voltage-divider from OUT1 to FB1 input and then to AGND. Calculate the top-side ( $R_{TOP}$  from output-to-FB\_) and bottom-side ( $R_{BOTTOM}$  from FB1-to-AGND) resistors with the following equation:

$$R_{TOP} = R_{BOTTOM} (V_{OUT1}/V_{FB1}-1)$$

where  $V_{FB1} = 1V$  (typ) (see the <u>Electrical Characteristics</u> table).

#### **Input Capacitor**

A 4.7µF ceramic input capacitor is recommended for proper buck operation. This value can be adjusted based on application input-voltage-ripple requirements.

The input capacitor RMS current requirement (I<sub>RMS</sub>) is defined by the following equation:

$$I_{\text{RMS}} = I_{\text{LOAD(MAX)}} \times \frac{\sqrt{V_{\text{OUT}} \times (V_{\text{SUPSW}} - V_{\text{OUT}})}}{V_{\text{SUPSW}}}$$

I<sub>RMS</sub> has a maximum value when the input voltage equals twice the output voltage:

$V_{SUP} = 2 \times V_{OUT}$

Therefore.

$$I_{\text{RMS}} = \frac{I_{\text{LOAD(MAX)}}}{2}$$

Choose an input capacitor that exhibits less than +10°C self-heating temperature rise at the RMS input current for optimal long-term reliability.

The input-voltage ripple is comprised of  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the capacitor). Use low-ESR ceramic capacitors with high ripple-current capability at the input. The total voltage ripple is the sum of  $\Delta V_Q$  and  $\Delta V_{ESR}$  that peaks at the end of an on-cycle. Calculate the input capacitance and ESR required for a specific ripple using the following equation:

$$\mathsf{ESR}[\Omega] = \frac{{}^{\Delta \, V} \mathsf{ESR}}{(I_{\mathsf{LOAD}(\mathsf{MAX})} + \frac{{}^{\Delta \, I} P - P}{2})}$$

$$C_{\mathsf{IN}}[\mu\mathsf{F}] = \frac{I_{\mathsf{LOAD}(\mathsf{MAX})} \times (\frac{V_{\mathsf{OUT}}}{V_{\mathsf{IN}}})}{(\Delta V_Q \times f_{\mathsf{SW}})}$$

where:

$$\Delta I_{P-P} = \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times V_{\text{OUT}}}{V_{\text{IN}} \times f_{\text{SW}} \times L}$$

and,

$I_{LOAD(MAX)}$  = Maximum output current in A,  $\Delta I_{P-P}$  = Peak-to-peak inductor current in A,  $f_{SW}$  = Switching frequency in MHz, L = Inductor value in  $\mu$ H.

#### Inductor Selection

The MAX20458 operates with two switching frequency options: 2.2MHz and 400kHz. The key parameters on inductor selection are: inductance value (L), inductor saturation current ( $I_{SAT}$ ), and DC resistance ( $R_{DCR}$ ). The minimum required

inductance is calculated as:

$$L_{\text{MIN}} = \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times D}{f_{\text{SW}} \times I_{\text{OUT}} \times \text{LIR}}$$

where LIR is the ratio of the inductor peak-to-peak AC current to DC average current, and 0.3 is a typical value to use. See <u>Table 1</u> for the recommended buck inductors. The inductor's saturation current rating must meet or exceed the LX current limit. For optimum transient response and highest efficiency, use inductors with a low DC resistance.

#### **Output Capacitor**

The actual capacitance value required relates to the physical size needed to achieve low ESR, as well as to the chemistry of the capacitor technology. The capacitor is usually selected by ESR and the voltage rating rather than by capacitance value.

When using low capacity filter capacitors, such as ceramic capacitors, size is usually determined by the capacity needed to prevent  $V_{SAG}$  and  $V_{SOAR}$  from causing problems during load transients. Generally, once enough capacitance is added to meet the overshoot requirement, undershoot is no longer a problem.

The total voltage sag (V<sub>SAG</sub>) can be calculated as follows:

$$V_{\mathsf{SAG}} = \frac{L \times \left( \triangle I_{\mathsf{LOAD}}(\mathsf{MAX}) \right)^2}{2 \times C_{\mathsf{OUT}} \times \left( V_{\mathsf{IN}} \times D_{\mathsf{MAX}} - V_{\mathsf{OUT}} \right)} + \frac{\triangle I_{\mathsf{LOAD}}(\mathsf{MAX}) \times (t - \triangle t)}{C_{\mathsf{OUT}}}$$

The amount of overshoot (V<sub>SOAR</sub>) during a full-load to no-load transient due to stored inductor energy can be calculated as:

$$V_{\mathsf{SOAR}} = \frac{\left(\Delta I_{\mathsf{LOAD}(\mathsf{MAX})}\right)^2 \times L}{2 \times C_{\mathsf{OUT}} \times V_{\mathsf{OUT}}}$$

See Table 1 for recommended output capacitance.

#### Table 1. Buck Converter Inductor and Output Capacitor Selectionwww

| SWITCHING FREQUENCY BUCK1 INDUCTOR (µH) BUCK1 OUTPUT CAPACITOR |     |        |  |

|----------------------------------------------------------------|-----|--------|--|

| 2.2MHz                                                         | 2.2 | 2 x 22 |  |

| 400kHz                                                         | 10  | 2 x 47 |  |

#### **ESR Considerations**

The output capacitor must have low enough equivalent series resistance (ESR) to meet output ripple and load transient requirements. When using high-capacitance, low-ESR capacitors, the ESR of the filter capacitor dominates the output voltage ripple:

$$V_{RIPPLE(P-P)} = ESR \times I_{LOAD(MAX)} \times LIR$$

#### **Boost Controller**

#### **Setting Output Voltage**

The MAX20458 boost controller has two output voltage options: fixed 10V output, and adjustable output voltage. For the fixed 10V output option, connect FB2 to boost output. For the adjustable output option, connect a resistive divider from the output of the boost converter to FB2, then to AGND. Calculate the top-side ( $R_{TOP}$  from output-to-FB2) and bottom-side ( $R_{ROTTOM}$  from FB2-to-AGND) resistors with the following equation:

$$R_{\mathsf{TOP}} = R_{\mathsf{BOTTOM}}(V_{\mathsf{OUT2}} \, \big/ \, V_{\mathsf{FB2}} - 1.005)$$

where  $V_{FB2} = 1.005V$  (typ) (see the <u>Electrical Characteristics</u> table).

#### **Inductor Selection**

Duty cycle and frequency are important to calculate the inductor size, as the inductor current ramps up during the on-time of the switch and ramps down during its off-time. The duty cycle is calculated by the formula:

$$D = \frac{V_{\text{OUT}} + V_D - V_{\text{IN}}}{V_{\text{OUT}} + V_D}$$

Choose 0.3 as the ratio of the inductor peak-to-peak AC current to DC average current, LIR. The inductor value can be calculated as follows:

$$L[\mu \mathsf{H}] = \frac{V_{\mathsf{IN}} \times D}{f_{\mathsf{SW}}[\mathsf{MHz}] \times 0.3 \times I_{\mathsf{OUT}}}$$

With a higher switching frequency, a lower inductance value can be selected to minimize the component size and improve transient response at the expense of reduced efficiency. With a lower switching frequency, a higher inductance value can be selected to reduce the inductor ripple current and achieve better efficiency. Select the inductor with low DC resistance and with a saturation current rating higher than the boost peak switch current limit.

$$I_{L\_SAT} > I_{L\_MAX} + \frac{\Delta I_{L\_PK}}{2}$$

#### **Input Capacitor**

The input current of the boost converter is continuous and its RMS ripple current at the input capacitor is low. Calculate the minimum input capacitor value and the maximum ESR using the following equations:

$$C_{\mathsf{IN}} = \frac{\Delta I_L \times D}{4 \times f_{\mathsf{SW}} \times \Delta V_Q}$$

$$ESR = \frac{\Delta V_{ESR}}{\Delta I_I}$$

where:

$$\Delta I_L = \frac{(V_{\mathsf{IN}} - V_{\mathsf{DS}}) \times D}{f_{\mathsf{SW}} \times L}$$

and,

V<sub>DS</sub> = Total voltage drop across the external MOSFET plus the voltage drop across the inductor ESR,

$\Delta I_{I}$  = Peak-to-peak inductor ripple current,

$\Delta V_{Q}$  = Portion of input ripple due to the capacitor discharge,

$\Delta V_{FSR}$  = Contribution due to ESR of the capacitor.

Assume the input capacitor ripple contribution due to ESR ( $\Delta V_{ESR}$ ) and capacitor discharge ( $\Delta V_Q$ ) are equal when using a combination of ceramic and aluminium capacitors. During the converter turn-on, a large current is drawn from the input source.

#### **Output Capacitor**

In a boost converter, the output capacitor supplies the load current when the main switch is on. The required output capacitance is high, especially at higher duty cycles. Also, the output capacitor ESR needs to be low enough to minimize the voltage drop while supporting the load current. Use the following equations to calculate the output capacitor for a specified output ripple. All ripple values are peak-to-peak:

$$ESR = \frac{\Delta V_{ESR}}{I_{OUT}}$$

$$C_{\text{OUT}} = \frac{I_{\text{OUT}} \times D_{\text{MAX}}}{\Delta V_{\text{O}} \times f_{\text{SW}}}$$

where D<sub>MAX</sub> is the maximum duty cycle at the minimum input voltage. Use a combination of low-ESR ceramic and high-value, low-cost aluminum capacitors for lower output ripple and noise.

#### **Current Sense Resistor Selection**

The current sense resistor R<sub>CS</sub> connected between CSP and PGND2, sets the boost input current limit. The CSP input

has 50mV (typ) voltage trip level. Set the current limit threshold above the peak switch current at the rated output power and minimum input voltage. Use the following equation to calculate the value of R

CS:

$$R_{\rm CS} = \frac{V_{\rm CS}}{I_{\rm IN(MAX)}}$$

where I<sub>IN(MAX)</sub> is the peak current that flows through the MOSFET at full load and minimum V<sub>IN</sub>.

$$I_{\text{IN(MAX)}} = \frac{I_{\text{LOAD(MAX)}}}{1 - D_{\text{MAX}}}$$

When the voltage across the current sense resistor by this current exceeds the current limit comparator threshold, the MOSFET driver (DL) quickly terminates the on-cycle.

#### **MOSFET Selection**

A wide variety of logic-level n-channel power MOSFETs can be used with the boost controller. To achieve the best performance, the key parameters to be considered in MOSFET selection are: maximum gate-source threshold voltage  $(V_{GS(TH)})$ , maximum continuous drain current  $(I_D)$ , drain-source on-resistance  $(R_{DS(ON)})$ , maximum drain-source voltage  $(V_{DS})$ , and total gate charge (Qg).

The boost controller low-side gate driver is powered by the internal 5V BIAS LDO output, or valid external supply connecting to EXTVCC. The chosen MOSFET must be a logic-level type with on-resistance specifications at  $V_{GS} = 4.5V$  or lower.

The MOSFET must deliver the maximum input current  $(I_{IN(MAX)})$  calculated in the <u>Current Sense Resistor Selection</u> section.

The MOSFET must be chosen with an appropriate maximum drain-to-source voltage (V<sub>DS</sub>) rating to cover all input voltage conditions.

The MOSFET drain-source on-resistance ( $R_{DS(ON)}$ ) is the parameter to decide the MOSFET conduction loss. The total gate charge (Qg) affects the MOSFET switching loss. Low  $R_{DS(ON)}$  and low Qg are preferred to minimize the MOSFET power loss to achieve better efficiency.

#### **Diode Selection**

Schottky diodes with low forward voltage are recommended to be used. Lower forward voltage is preferred to minimize the diode power loss. The average current rating of the selected Schottky diode must exceed the peak current limit set by boost current sense resistor (R<sub>CS</sub>). Its maximum reverse voltage rating should be selected above output voltage plus extra voltage stress.

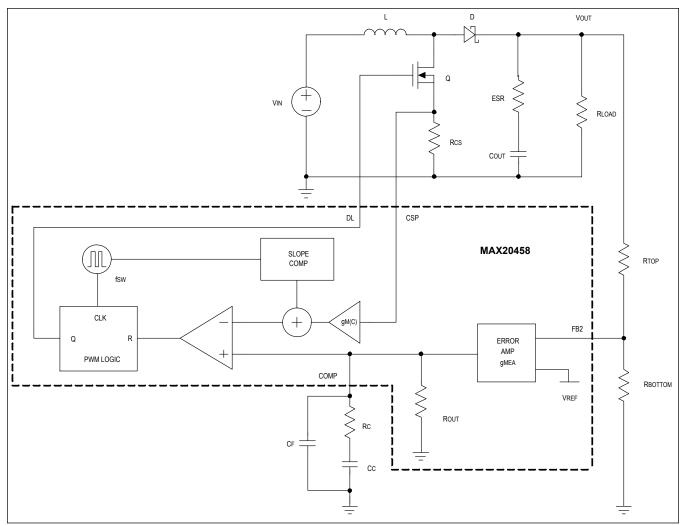

#### **Compensation Component Calculation**

The boost regulation loop consists of power modulator, feedback resistor network, and error amplifier, as shown in Figure 1. The power modulator includes current sense circuitry ( $R_{CS}$ ), the external MOSFET (Q) and rectifier diode (D), the inductor (L), output capacitor ( $C_{OUT}$  and its ESR), and the load ( $R_{LOAD}$ ). Its transfer function is expressed below:

$$G(f) = g_{M(C)} \times R_{\text{LOAD}} \times \frac{1 - D}{2} \times \frac{(1 + J \frac{f}{f_{Z} \text{ESR}}) \times (1 - J \frac{f}{f_{Z} \text{RHP}})}{1 + J \frac{f}{f_{P} \text{LOAD}}}$$

Figure 1. Boost Control Loop

where

$$gM(C) = \frac{1}{A_{V CS} \times R_{CS}}$$

in S, and  $A_{V\ CS}$  is the gain of current sense amplifier, 24V/V. The double poles at half of switching frequency are neglected if it is well damped by slope compensation. Therefore, the power modulator DC gain,

$$G_{\text{MOD}}(\text{DC}) = \frac{R_{\text{LOAD}} \times (1 - D)}{2 \times A_{\text{V_CS}} \times R_{\text{CS}}}$$

The output capacitor and load resistance introduce a pole at:

$$f_{P\_LOAD} = \frac{1}{\pi \times R_{LOAD} \times C_{OUT}}$$

The output capacitor and its ESR introduce a zero at:

$$f_{Z\_ESR} = \frac{1}{2 \times \pi \times ESR \times C_{OUT}}$$

The right half plane zero is:

$$f_{Z\_RHP} = \frac{R_{LOAD} \times (1 - D)^2}{2 \times \pi \times L}$$

For feedback loop, its transfer function can be expressed as:

$$H(f) = \text{gMEA} \times R_{\text{OUT\_EA}} \times \frac{R_{\text{TOP}}}{R_{\text{TOP}} + R_{\text{BOTTOM}}} \times \frac{1 - j \frac{f}{f_{\text{Z\_EA}}}}{(1 + j \frac{f}{f_{\text{P\_EA}}}) \times (1 + j \frac{f}{f_{\text{P2\_EA}}})}$$

The DC gain of transconductance error amplifier is  $G_{EA} = g_{MEA} \times R_{OUT\_EA}$ , where  $g_{MEA}$  is the error-amplifier transconductance, which is 230µS (typ), and  $R_{OUT\_EA}$  is the output resistance of the error amplifier, which is 4.5M $\Omega$  (typ). The dominant pole ( $f_{P\_EA}$ ) is set by the compensation capacitor  $C_{C}$  and the amplifier output resistance  $R_{OUT\_EA}$ . A zero,  $f_{Z\_EA}$ , is set by the compensation resistor  $R_{C}$  and the compensation capacitor  $C_{C}$ . Another pole  $f_{P2\_EA}$  set by  $C_{F}$  and  $R_{C}$  is optional to cancel the output capacitor ESR zero if it occurs near the crossover frequency  $f_{C}$ , where the loop gain equals 0dB. The error amplifier related pole and zero are calculated as:

$$f_{P\_EA} = \frac{1}{2 \times \pi \times R_{OUT\_EA} \times R_C}$$

$$f_{Z\_EA} = \frac{1}{2 \times \pi \times C_C \times R_C}$$

$$f_{P2}_{EA} = \frac{1}{2 \times \pi \times C_F \times R_C}$$

The loop gain crossover frequency,  $f_C$ , should be selected lower than 1/10 of switching frequency ( $f_{SW}$ ) or 1/3 of right-half plane zero frequency ( $f_{ZRHP}$ ).

$f_C \leq Lower of$

$$\frac{f_{SW}}{10}$$

or  $\frac{f_{Z\_RHP}}{3}$

At the crossover frequency, the total loop gain equals 1. Therefore,

$$G_{\text{MOD}}(\text{fc}) \times \frac{V_{\text{FB2}}}{V_{\text{OUT2}}} \times G_{\text{EA}}(\text{fc}) = 1$$

$$G_{FA}(fc) = gMEA \times R_C$$

$$G_{\text{MOD}}(f_c) = G_{\text{MOD}}(DC) \times \frac{f_{\text{P\_LOAD}}}{f_{\text{C}}}$$

Using these formula to solve R<sub>C</sub>:

$$R_{C} = \frac{V_{\text{OUT2}}}{\text{gMEA} \times V_{\text{FB3}} \times G_{\text{MOD}}(\text{fc})}$$

Set the zero formed by  $R_C$  and  $C_C$  at the power modulator pole ( $f_{P\_LOAD}$ ) to cancel this pole. Calculated the value of  $C_C$  as follows:

$$C_C = \frac{1}{2 \times \pi \times G_{\text{MOD}}(f_C)}$$

If  $f_{Z\_ESR}$  is less than 5 x  $f_{C}$ , add the second capacitor ( $C_{F}$ ) from COMP3 to AGND to compensate  $f_{Z\_ESR}$ . The value of  $C_{F}$  is calculated as:

$$C_F = \frac{1}{2 \times \pi \times f_Z \text{ ESR} \times R_C}$$

#### **SEPIC Operation**

For reference, see the example using the MAX20458 boost controller in SEPIC mode in Figure 2.

Figure 2. MAX20458 SEPIC Application Circuit

#### **PCB Layout Guidelines**

Careful PCB layout is critical to achieve low switching losses, low EMI, and clean, stable operation. If possible, mount all power components on the top side of the board, and minimize the high frequency current loop as small as possible. Refer to the MAX20458 EV kit for an example layout. Follow these guidelines for good PCB layout.

For buck converter, place the input bypass capacitors as close to SUPSW1 as possible. The buck input capacitors deliver high di/dt current pulses when its high-side MOSFET turns on. Minimize the parasitic inductance in the power input traces to improve efficiency and reliability.

Minimize the connection from the buck output capacitor's ground terminal to the input capacitor's ground terminal for each buck regulator. This minimizes the area of current loop when the high-side MOSFET is conducting.

Keep buck high-current paths, and power traces wide and short. Minimize the traces from each buck LX node to each inductor and from each inductor to the output capacitors. This minimizes the buck current loop area and minimizes LX trace resistance and stray capacitance to achieve optimal efficiency. Using thick copper PCBs (2 ounces vs. 1 ounce) can improve full load efficiency by 1% or more.

The boost controller loop, including the N-channel MOSFET, diode, and output capacitor has high di/dt cur- rent pulses. Keep this loop as small as possible.

The trace from the boost controller gate driver output DL to the gate of the low-side N-channel MOSFET should be wide and short. The gate driver has a high di/dt when switching. Minimized gate driver traces can reduce rising and falling time to further reduce the switching loss.

Connect the ground terminal of the current sense resistor, boost output capacitors, and PGND2 as close as possible.

Connect current sense resistor to CSP by Kelvin sensing connection to minimize current sensing error.

Keep all sensitive analog signals (FB1, FB2, and COMP) away from noisy switching nodes (LX1, BST1, and DL) and high current loops.

Place the BIAS capacitor as close to the BIAS node as possible. Noise coupling into BIAS can disturb the refer- ence and bias circuitry if this capacitor is installed away from the device.

Ground is the return path for the full load currents flow- ing into and out of the MAX20458. It is also the common reference voltage for all the analog circuits. Improper ground routing can bring extra resistance and inductance into the current loop, causing different voltage reference and worsening voltage ringing or spikes. Place a solid ground plane layer under the power loop components layer to shield the switching noise from other sensi- tive traces. Connect all the analog ground (AGND) and power grounds (PGND1, and PGND2) together at a single point in a star ground connection. The IC exposed pad can be the point for ground connection.

The exposed pad under the bottom of the package is attached with epoxy to the substrate of the IC, making it an excellent path to remove heat from the IC. Connect the exposed pad to large ground plane areas through external or internal layers. Place multiple small vias under the exposed pad to effectively transfer heat down to the internal ground plane and the back side of the PCB to further improve the thermal resistance from the IC pack- age to the ambient.

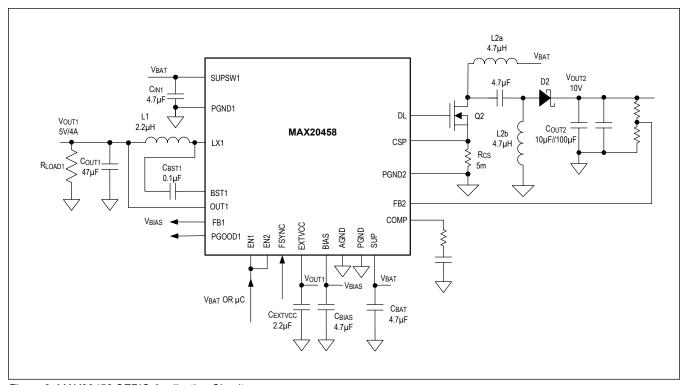

#### **Typical Application Circuits**

#### MAX20458ATIE/VY+ Configuration: 2.1MHz, 5V/ADJ Outputs

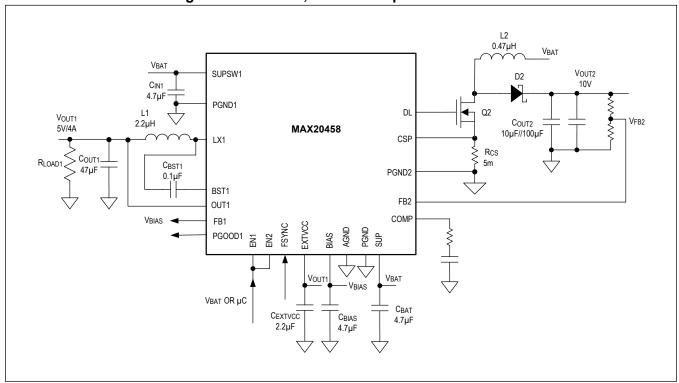

### **Typical Application Circuits (continued)**

### MAX20458ATIE/VY+ Configuration: 400kHz, 5V/10V Outputs

### **Ordering Information**

| PART NUMBER        | VOUT OPTIONS (VOUT1/VOUT2) (V) | SWITCHING FREQUENCY | SPREAD SPECTRUM |

|--------------------|--------------------------------|---------------------|-----------------|

| MAX20458ATIA/VY+   | 3.3/ADJ                        | 2.1MHz              | OFF             |

| MAX20458ATIB/VY+** | 3.3/10                         | 2.1MHz              | ON              |

| MAX20458ATIC/VY+** | 5/10                           | 400kHz              | OFF             |

| MAX20458ATID/VY+** | 5/ADJ                          | 400kHz              | ON              |

| MAX20458ATIE/VY+** | 3.3/10                         | 2.1MHz              | OFF             |

| MAX20458ATIF/VY+   | 3.3/ADJ                        | 2.1MHz              | ON              |

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T Denotes tape-and-reel.

<sup>\*</sup>EP = Exposed pad.

<sup>\*\*</sup> Future Product.

### MAX20458

# 36V Boost Controller with A 3.5A Synchronous Buck Converter for Automotive Applications

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                        | PAGES<br>CHANGED |

|--------------------|---------------|------------------------------------|------------------|

| 0                  | 4/19          | Initial release                    | _                |

| 1                  | 10/21         | Updated Ordering Information table | 22               |