## SPI / Parallel Controlled Quad Low-Side Switches with Reverse Current Detection

### **General Description**

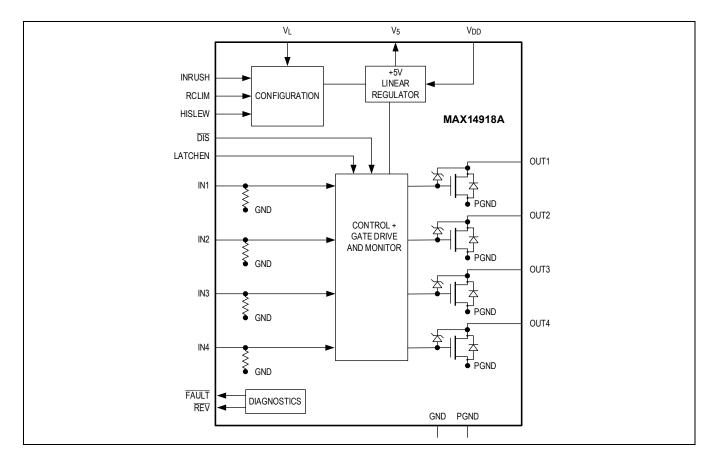

The MAX14918 and MAX14918A are quad 700mA lowside switches for industrial applications. Each device features four 140m $\Omega$  (typ) on-resistance (R<sub>ON</sub>) switches with integrated ±1.2kV/42 $\Omega$  surge protection. Two or more outputs can be connected in parallel to provide higher load current.

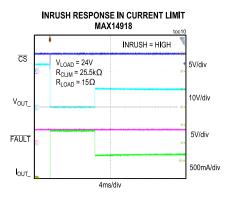

The maximum load current is actively limited and is resistor settable between 100mA (typ) and 900mA (typ). For load that draws high inrush current, the MAX14918 and MAX14918A have the inrush mode which provides 2x current after switch turn-on for 10ms (min).

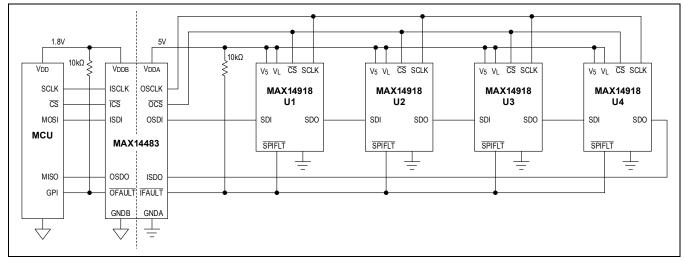

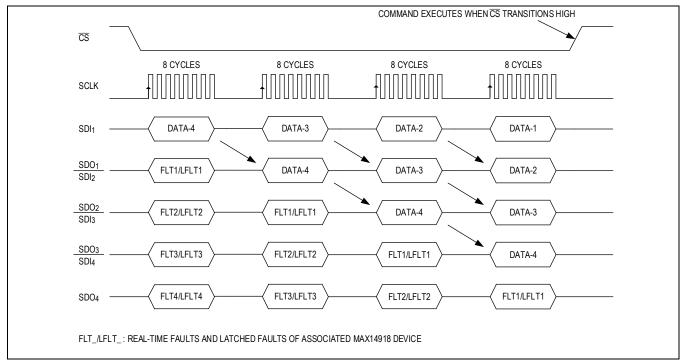

The MAX14918 has an SPI allowing control of multiple MAX14918 devices through a common daisy-chained interface for high channel-count applications, minimizing galvanic isolation channels. Per-channel diagnostics are returned on the serial data output (SDO). Data corruption on the serial data input (SDI) is automatically detected and signaled on the SPIFLT output.

The MAX14918A offers a pin-based switch control with a latch option (LATCHEN) which allows sharing of the four IN\_ control signals among multiple MAX14918A devices.

Slew rate control provides controlled turn-on edge for reducing electromagnetic interference or EMI emissions. Simultaneously, a global DIS control signal allows disabling of all OUT\_switches quickly.

The integrated 5V low dropout (LDO) regulator in the MAX14918 and MAX14918A can be used to power external isolators or other logic circuitry.

### **Applications**

- Industrial Digital Outputs

- Relay and Solenoid Drivers

- Programmable Logic Controllers and Distributed Control Systems

- Motor Control

- Industrial/Process/Building Automation

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- +5V (V<sub>5</sub>) or +7V to +65V (V<sub>DD</sub>) Supply Voltage Operation

- 700mA DC Capability Per Channel across

Temperature Range

- 140mΩ (typ) On-Resistance Per Channel

- Settable Load Current Limit 100mA (typ) to 900mA (typ)

- +5V to +48V Load Voltage Range

- 2x Inrush Load Current Option for 10ms (min)

- Robust Design Features

- Internal Inductive Energy Clamp at +55V (typ)

- Short-Circuit Protection at OUT\_ of up to +49V

- Reverse Current Detection against Load-Supply

Miswiring

- ±1.2kV/42Ω Surge Protection

- ±8kV Contact and ±25kV Air-Gap ESD Protection

- -40°C to +125°C Operating Ambient Temperature

- Diagnostic FAULT Indication for

- Thermal Overload

- Reverse Load Current Detection

- Undervoltage Lockout (UVLO) on V<sub>5</sub> Supply

- Compact 24-Pin, 4mm x 5mm TQFN Package

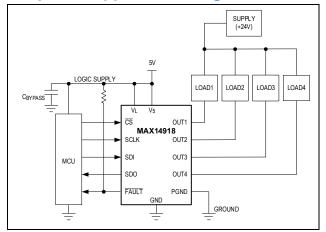

### **Simplified Application Diagram**

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND                                                              | 0.3V to +70V                   |

|-------------------------------------------------------------------------------------|--------------------------------|

| $V_{5},V_{L}$ to $GND$                                                              | 0.3V to +6V                    |

| REV, RCLIM to GND0                                                                  | .3V to (V <sub>5</sub> + 0.3)V |

| $\overline{\text{CS}}$ , SCLK, SDI, $\overline{\text{DIS}}$ , HISLEW, INRUSH, I GND |                                |

| FAULT, SPIFLT to GND                                                                | -0.3V to +6V                   |

| SDO to GND0                                                                         | .3V to (V <sub>L</sub> + 0.3)V |

| GND to PGND                                                                         | -0.3V to +0.3V                 |

| OUT1, OUT2, OUT3, OUT4 to PGND                                                      | 0.3V to V <sub>CLAMP</sub>     |

| Continuous OUT_ Current                                                             | +700mA                         |

# MAX14918, MAX14918A

#### Continuous Power Dissipation (T<sub>A</sub> = +70°C)

| 24 TQFN (Single-Layer Board) (derate at 20.8 mW/°C above +70°C)1666.7mW |

|-------------------------------------------------------------------------|

| 24 TQFN (Multilayer Board) (derate at 28.6 mW/°C above +70°C)2285.7mW   |

| Temperature Ratings                                                     |

| Operating Temperature Range40°C to +125°C                               |

| Maximum Junction Temperature+150°C                                      |

| Storage Temperature Range65°C to +150°C                                 |

| Lead Temperature (soldering, 10s)+300°C                                 |

| Soldering Temperature (reflow)+260°C                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| 24 TQFN                                               |                |  |  |  |

|-------------------------------------------------------|----------------|--|--|--|

| Package Code                                          | T2445+2C       |  |  |  |

| Outline Number                                        | <u>21-0201</u> |  |  |  |

| Land Pattern Number                                   | <u>90-0083</u> |  |  |  |

| THERMAL RESISTANCE, SINGLE LAYER BOARD                |                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 48°C/W         |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 1.8°C/W        |  |  |  |

| THERMAL RESISTANCE, MULTILAYER BOARD                  |                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 35°C/W         |  |  |  |

| Junction-to-Case Thermal Resistance $(\theta_{JC})$   | 1.8°C/W        |  |  |  |

### **Electrical Characteristics**

$(V_{DD} = +7V \text{ to } +65V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted}$ . Typical values are at  $T_A = +25^{\circ}C, V_{DD} = +24V, V_L = V_5)$  (*Note 1*)

| PARAMETER                                         | SYMBOL                  | CONDITIONS MIN TYP MAX                                                                                 |      | UNITS |     |    |  |

|---------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------|------|-------|-----|----|--|

| POWER SUPPLY (V <sub>5</sub> , V <sub>L</sub> )   |                         |                                                                                                        |      |       |     |    |  |

| V <sub>5</sub> Supply Voltage                     | V <sub>5</sub>          | V <sub>DD</sub> = GND or unconnected                                                                   | 4.5  | 5.0   | 5.5 | V  |  |

| V <sub>5</sub> Supply Current                     | I <sub>5_ON</sub>       | All OUT_ switches on or off, V <sub>DD</sub> = GND<br>or unconnected                                   |      | 2.0   | 3.0 | mA |  |

| V <sub>5</sub> Undervoltage<br>Lockout Threshold  | V <sub>5_UVLO</sub>     | V <sub>5</sub> falling, OUT_ switches are three-state<br>in UVLO, V <sub>DD</sub> = GND or unconnected | 3.5  |       | 4.2 | V  |  |

| V <sub>5</sub> Undervoltage<br>Lockout Hysteresis | V <sub>5_UVLO_HYS</sub> | V <sub>DD</sub> = GND or unconnected                                                                   |      | 0.2   |     | V  |  |

| V <sub>L</sub> Supply Voltage                     | VL                      |                                                                                                        | 1.62 |       | 5.5 | V  |  |

| V <sub>L</sub> Supply Current                     | ١L                      | Logic inputs are at GND or $V_L$                                                                       |      | 11    | 50  | μA |  |

| V <sub>L</sub> Undervoltage<br>Lockout Voltage    | V <sub>L_UVLO</sub>     | V <sub>L</sub> falling                                                                                 | 0.7  |       | 1.4 | V  |  |

| V <sub>L</sub> Undervoltage<br>Lockout Hysteresis | VL_UVLO_HYS             |                                                                                                        |      | 50    |     | mV |  |

| $(V_{DD} = +7V \text{ to } +65V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted}$ . Typical values | lues are at |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| $T_A = +25^{\circ}C, V_{DD} = +24V, V_L = V_5) (Note 1)$                                                                                                                                       |             |

| T <sub>A</sub> = +25°C, V <sub>DD</sub> = +24V, V<br><b>PARAMETER</b> | SYMBOL                             |                                            | DITIONS                                                                                                                                                                                                                                                                                               | MIN  | ТҮР                  | MAX   | UNITS |

|-----------------------------------------------------------------------|------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|-------|-------|

| LINEAR REGULATOR (                                                    | / <sub>DD</sub> , V <sub>5</sub> ) | I                                          |                                                                                                                                                                                                                                                                                                       |      |                      |       |       |

| V <sub>DD</sub> Supply Voltage                                        | V <sub>DD</sub>                    |                                            |                                                                                                                                                                                                                                                                                                       | 7    |                      | 65    | V     |

| Range                                                                 |                                    |                                            |                                                                                                                                                                                                                                                                                                       | 1    |                      | 05    | v     |

| V <sub>DD</sub> Supply Current                                        | I <sub>DD</sub>                    |                                            | V <sub>DD</sub> ≥ 7V, no load on V <sub>5</sub>                                                                                                                                                                                                                                                       |      |                      | 3.0   | mA    |

| V <sub>5</sub> Regulator Output<br>Voltage                            | V <sub>5</sub>                     | $V_{DD} \ge 7V$ , 0mA to 3<br>$V_5$        | 30mA load current on                                                                                                                                                                                                                                                                                  | 4.75 | 5.0                  | 5.25  | V     |

| V <sub>5</sub> Regulator Current<br>Limit                             | I <sub>CL_V5</sub>                 | $V_{DD} \ge 7V, V_5 = 4V$                  |                                                                                                                                                                                                                                                                                                       | 35   |                      |       | mA    |

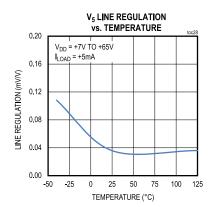

| V <sub>5</sub> Line Regulation                                        |                                    | 7V ≤ V <sub>DD</sub> ≤ 65V, I <sub>5</sub> | = 5mA                                                                                                                                                                                                                                                                                                 |      | 0.035                |       | mV/V  |

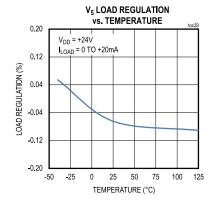

| V <sub>5</sub> Load Regulation                                        |                                    | 0 ≤ I <sub>5</sub> ≤ 20mA, V <sub>DD</sub> | ≥7V                                                                                                                                                                                                                                                                                                   |      | 0.175                |       | %     |

| SWITCH OUTPUTS (OUT                                                   | Γ)                                 | 0 00                                       |                                                                                                                                                                                                                                                                                                       |      | 01110                |       |       |

| On-Resistance                                                         | R <sub>ON</sub>                    | I <sub>OUT</sub> = 500mA                   |                                                                                                                                                                                                                                                                                                       |      | 140                  | 300   | mΩ    |

|                                                                       | 0.1                                | _                                          | R <sub>CLIM</sub> = 100kΩ                                                                                                                                                                                                                                                                             | 140  | 200                  | 270   |       |

| Current Limit                                                         | ILIM                               | INRUSH = 0, or<br>INRUSH = 1 and           | $R_{CLIM} = 27k\Omega$                                                                                                                                                                                                                                                                                | 700  | 800                  | 900   | mA    |

|                                                                       |                                    | t <sub>LIM</sub> > 15ms                    | R <sub>CLIM</sub> = open                                                                                                                                                                                                                                                                              | 650  | 000                  | 950   |       |

| Inrush Current Limit                                                  | IINRUSH_LIM                        | -                                          | for 10ms after switch                                                                                                                                                                                                                                                                                 | 000  | 2 x I <sub>LIM</sub> | 330   | mA    |

| Inductive Clamp Voltage                                               | V <sub>CLAMP</sub>                 | turn-on<br>OUT_ is off, I <sub>OUT</sub> = | = 500mA                                                                                                                                                                                                                                                                                               | 49   | 55                   |       | V     |

| Off-State Leakage<br>Current at OUT                                   | ILKG                               | IN_ = low, V <sub>OUT</sub> _ =            | 0                                                                                                                                                                                                                                                                                                     |      | 3.0                  | μA    |       |

| RCLIM Voltage                                                         | V <sub>RCLIM</sub>                 | R <sub>CLIM</sub> = 27kΩ                   | $R_{CLIM} = 27k\Omega$                                                                                                                                                                                                                                                                                |      |                      | 1.235 | V     |

| RCLIM Short<br>Resistance Threshold                                   | R <sub>CLIM_SHORT</sub>            |                                            |                                                                                                                                                                                                                                                                                                       | 4.5  | 6.5                  | 9     | kΩ    |

| RCLIM Open<br>Resistance Threshold                                    | R <sub>CLIM_OPEN</sub>             |                                            |                                                                                                                                                                                                                                                                                                       | 400  | 650                  | 1000  | kΩ    |

| Maximum Switching                                                     | SR                                 | 50% IN_ Duty                               | HISLEW = low                                                                                                                                                                                                                                                                                          |      | 50                   |       | kU-   |

| Rate                                                                  | SK                                 | Cycle                                      | HISLEW = high                                                                                                                                                                                                                                                                                         |      | 500                  |       | kHz   |

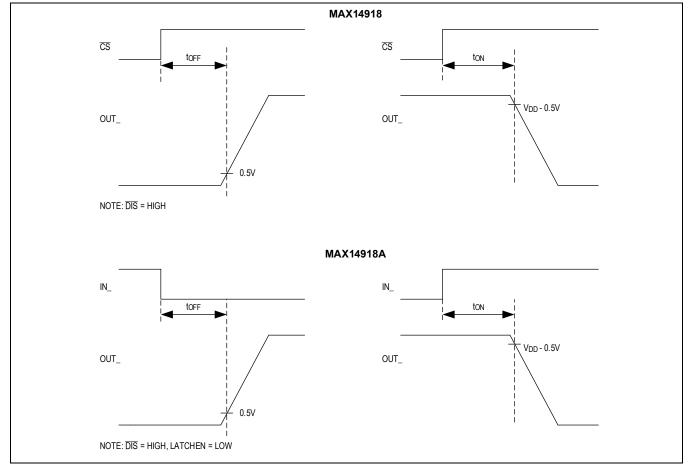

|                                                                       |                                    |                                            | $\begin{array}{l} \text{MAX14918:} \\ \text{delay from } \overline{\text{CS}} \\ \text{going high to OUT}_{} \\ \text{rising by 0.5V, } R_{\text{L}} = \\ 48\Omega, \ \text{C}_{\text{L}} = 100 \text{pF}, \\ \text{V}_{\text{LOAD}} = 24 \text{V} \\ \text{(see } \underline{Figure 1}) \end{array}$ |      | 110                  | 220   |       |

| Turn-Off Propagation<br>Delay (Low-to-High)                           | toff                               | HISLEW = low                               | MAX14918A:<br>delay from IN_<br>switching low to<br>OUT_ rising by<br>$0.5V, R_L = 48\Omega, C_L$<br>= 100pF, V <sub>LOAD</sub> =<br>24V<br>(see <u>Figure 1</u> )<br>MAX14918:                                                                                                                       |      | 110                  | 220   | ns    |

|                                                                       |                                    | HISLEW = high                              | delay from $\overline{CS}$<br>going high to OUT_<br>rising by 0.5V, R <sub>L</sub> =<br>$48\Omega$ , C <sub>L</sub> = 100pF,                                                                                                                                                                          |      | 110                  | 220   |       |

# MAX14918, MAX14918A

| $(V_{DD} = +7V \text{ to } +65V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C,  unless otherwise noted. Typical values of the test of the test of the test of test o$ | ues are at |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $T_A = +25^{\circ}C, V_{DD} = +24V, V_L = V_5) (Note 1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| PARAMETER           | SYMBOL                       | CON           | DITIONS                                     | MIN | TYP  | MAX  | UNITS |

|---------------------|------------------------------|---------------|---------------------------------------------|-----|------|------|-------|

|                     |                              |               | V <sub>LOAD</sub> = 24V                     |     |      |      |       |

|                     |                              |               | (see <u>Figure 1</u> )                      |     |      |      |       |

|                     |                              |               | MAX14918A:                                  |     |      |      |       |

|                     |                              |               | delay from IN_                              |     |      |      |       |

|                     |                              |               | switching low to                            |     |      |      |       |

|                     |                              |               | OUT_ rising by                              |     |      |      |       |

|                     |                              |               | $0.5V, R_{L} = 48\Omega, C_{L}$             |     | 110  | 220  |       |

|                     |                              |               | = 100pF, V <sub>LOAD</sub> =                |     |      |      |       |

|                     |                              |               | 24V                                         |     |      |      |       |

|                     |                              |               | (see <u>Figure 1</u> )                      |     |      |      |       |

|                     |                              |               | MAX14918:                                   |     |      |      |       |

|                     |                              |               | delay from $\overline{CS}$                  |     |      |      |       |

|                     |                              |               | going high to OUT_                          |     |      |      |       |

|                     |                              |               | falling by 0.5V, R <sub>L</sub>             |     | 370  | 750  |       |

|                     |                              |               | $= 48\Omega, C_{L} = 100 \text{pF},$        |     | 370  | 750  |       |

|                     |                              |               | V <sub>LOAD</sub> = 24V                     |     |      |      |       |

|                     |                              |               | -                                           |     |      |      |       |

|                     |                              |               | (see <u>Figure 1</u> )                      |     |      |      | 4     |

|                     |                              | HISLEW = low  | MAX14918A:                                  |     |      |      |       |

|                     |                              |               | delay from IN_                              |     |      |      |       |

|                     |                              |               | switching high to                           |     |      |      |       |

|                     |                              |               | OUT_falling by                              |     | 370  | 750  |       |

|                     |                              |               | $0.5V, R_{L} = 48\Omega, C_{L}$             |     |      | 100  |       |

|                     | = 100pF, V <sub>LOAD</sub> = |               |                                             |     |      |      |       |

|                     |                              |               | 24V                                         |     |      | 150  |       |

| Turn-On Propagation | t <sub>ON</sub>              |               | (see <u>Figure 1</u> )                      |     |      |      | ns    |

| Delay (High-to-Low) | -011                         |               | MAX14918:                                   |     |      |      | 113   |

|                     |                              |               | delay from $\overline{CS}$                  |     | 70   |      |       |

|                     |                              |               | going high to OUT_                          |     |      |      |       |

|                     |                              |               | falling by 0.5V, $R_L$                      |     |      |      |       |

|                     |                              |               | = 48Ω, C <sub>L</sub> = 100pF,              |     |      |      |       |

|                     |                              |               | $V_{LOAD} = 24V$                            |     |      |      |       |

|                     |                              |               | (see <u>Figure 1</u> )                      |     |      |      |       |

|                     |                              | HISLEW = high | MAX14918A:                                  |     |      |      |       |

|                     |                              |               | delay from IN_                              |     |      |      |       |

|                     |                              |               | switching high to                           |     |      |      |       |

|                     |                              |               | OUT_ falling by                             |     |      | 450  |       |

|                     |                              |               | $0.5V, R_{L} = 48\Omega, C_{L}$             |     | 70   | 150  |       |

|                     |                              |               | = 100pF, V <sub>LOAD</sub> =                |     |      |      |       |

|                     |                              |               | 24V                                         |     |      |      |       |

|                     |                              |               | (see Figure 1)                              |     |      |      |       |

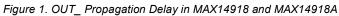

|                     |                              |               | Output falling 80%                          |     |      |      |       |

|                     |                              |               | to 20% of final                             |     |      |      |       |

|                     |                              |               | value, V <sub>LOAD</sub> =                  |     |      |      |       |

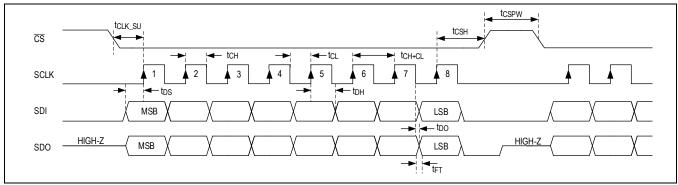

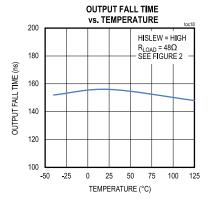

|                     |                              | HISLEW = low  | 24V, R <sub>L</sub> = 48Ω, C <sub>L</sub> = |     | 1030 | 1900 |       |

|                     |                              |               | 100pF                                       |     |      |      |       |

|                     |                              |               | (see <u>Figure 2</u> )                      |     |      |      |       |

| Output Fall-Time    | t <sub>F</sub>               |               | Output falling 80%                          |     |      |      | ns    |

|                     |                              |               | to 20% of final                             |     |      |      |       |

|                     |                              |               | value, V <sub>LOAD</sub> =                  |     |      |      |       |

|                     |                              | HISLEW = high | 24V, $R_L$ = 48Ω, $C_L$ =                   |     | 125  | 250  |       |

|                     |                              | _             |                                             |     |      |      |       |

|                     |                              |               | 100pF                                       |     |      |      |       |

|                     | 1                            |               | (see <u>Figure 2</u> )                      |     |      |      | 1     |

| $(V_{DD} = +7V \text{ to } +65V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } +5.5V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C,  unless otherwise noted. Typical value of the second sec$ | es are at |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| $T_A = +25^{\circ}C, V_{DD} = +24V, V_L = V_5) (Note 1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

| PARAMETER                                           | SYMBOL              | COND                                                                      | ITIONS                                                                                                                               | MIN                   | TYP  | MAX                  | UNITS |

|-----------------------------------------------------|---------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|----------------------|-------|

|                                                     |                     | HISLEW = low                                                              | Output rising 20%<br>to 80% of final<br>value, $V_{LOAD}$ =<br>24V, $R_L$ = 48 $\Omega$ , $C_L$ =<br>100pF<br>(see <i>Figure 2</i> ) |                       | 110  |                      |       |

| Output Rise-Time                                    | <sup>t</sup> R      | HISLEW = high                                                             | Output rising 20%<br>to 80% of final<br>value, $V_{LOAD}$ =<br>24V, $R_L$ = 48 $\Omega$ , $C_L$ =<br>100pF<br>(see <u>Figure 2</u> ) |                       | 110  |                      | ns    |

| REVERSE CURRENT DE                                  | TECTION (REV        | )                                                                         | · · ·                                                                                                                                |                       |      |                      |       |

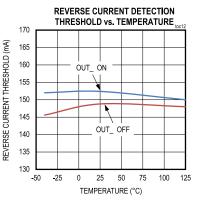

| Reverse Current                                     | ITH_OUT_RV_<br>OFF  | V <sub>5</sub> > V <sub>5_UVLO</sub> ,<br>current flow out of<br>any OUT_ | OUT_ switch is off                                                                                                                   | -185                  | -135 | -95                  | ٣٨    |

| Detection Threshold                                 | ITH_OUT_RV_<br>ON   | V <sub>5</sub> > V <sub>5_UVLO</sub> ,<br>current flow out of<br>any OUT_ | OUT_ switch is on                                                                                                                    | -190                  | -150 | -115                 | mA    |

| REV Pullup Current<br>(Not in Reverse<br>Condition) | IREV_PU             | $V_5 > V_5_{UVLO}, I_{OUT}$ $V_{REV} = V_5 - 0.4V$                        | $V_5 > V_5 \cup V_{100}, I_{00T} \ge I_{TH} \cup T_{RV} X,$                                                                          |                       | 45   |                      | μA    |

| REV Pulldown<br>Resistance<br>(Reverse Condition)   | R <sub>REV_PD</sub> | $V_5 > V_5_{UVLO}$ , I <sub>OUT</sub>                                     | _ < I <sub>TH_OUT_RV_X</sub>                                                                                                         |                       | 8    | 16                   | Ω     |

| Auto-Retry Delay                                    | <sup>t</sup> REV_AR | Delay until REV out                                                       | out is turned back on<br>on turn-off                                                                                                 |                       | 2    |                      | S     |

| LOGIC INPUTS (INRUSH                                |                     | IN_, LATCHEN, SDI,                                                        | SCLK, CS)                                                                                                                            | 1                     |      |                      |       |

| Input Voltage High                                  | VIH                 |                                                                           |                                                                                                                                      | 0.8 x V <sub>L</sub>  |      |                      | V     |

| Input Voltage Low                                   | VIL                 |                                                                           |                                                                                                                                      |                       |      | $0.2 	ext{ x V}_{L}$ | V     |

| Input Threshold<br>Hysteresis                       | VI_TH               |                                                                           |                                                                                                                                      |                       | 0.1  |                      | V     |

| Input Pulldown Resistor                             | R <sub>PD</sub>     | All logic input pins, e                                                   | except CS                                                                                                                            |                       | 100  |                      | kΩ    |

| Input Pullup Resistor                               | R <sub>PU</sub>     | CS input                                                                  |                                                                                                                                      |                       | 100  |                      | kΩ    |

| LOGIC OUTPUT (FAULT                                 | , SPIFLT, SDO)      |                                                                           |                                                                                                                                      | 1                     |      |                      |       |

| Output Logic Low                                    | V <sub>OL</sub>     | FAULT, SPIFLT, I <sub>LC</sub>                                            |                                                                                                                                      |                       |      | 0.33                 | V     |

| Output Logic High                                   | V <sub>OH</sub>     | SDO, I <sub>LOAD</sub> = -5mA                                             |                                                                                                                                      | V <sub>L</sub> - 0.33 |      |                      | V     |

| Three-State Leakage                                 | I <sub>LEAK</sub>   | Open-drain output F<br>V <sub>PULLUP</sub> = 5V ( <u>Note</u>             |                                                                                                                                      | -1                    |      | +1                   | μA    |

| SDO Pulldown Resistor                               | R <sub>PD</sub>     | CS is high                                                                |                                                                                                                                      |                       | 100  |                      | kΩ    |

| TIMING CHARACTERIST                                 | rics                |                                                                           |                                                                                                                                      |                       |      |                      |       |

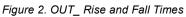

| SPI (MAX14918) (see <u>Fig</u>                      | <u>qure 3)</u>      |                                                                           |                                                                                                                                      |                       |      |                      |       |

| SCLK Clock Period                                   | t <sub>CH+CL</sub>  |                                                                           |                                                                                                                                      | 100                   |      |                      | ns    |

| SCLK Pulse Width High                               | t <sub>CH</sub>     |                                                                           |                                                                                                                                      | 35                    |      |                      | ns    |

| SCLK Pulse Width Low                                | t <sub>CL</sub>     |                                                                           |                                                                                                                                      | 45                    |      |                      | ns    |

| CS Falling to SCLK<br>Rising Time                   | <sup>t</sup> CLK_SU |                                                                           |                                                                                                                                      | 50                    |      |                      | ns    |

| $(V_{DD} = +7V \text{ to } +65V, V_5 = +4.5V \text{ to } +5.5V, V_L = +1.62V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted}.$ Typical values | ues are at |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| $T_A = +25^{\circ}C, V_{DD} = +24V, V_L = V_5) (Note 1)$                                                                                                                                                    |            |

| PARAMETER                                     | SYMBOL                 | CONDITIONS                                                              | MIN | TYP  | MAX | UNITS |

|-----------------------------------------------|------------------------|-------------------------------------------------------------------------|-----|------|-----|-------|

| SDI Hold Time                                 | t <sub>DH</sub>        |                                                                         | 10  |      |     | ns    |

| SDI Setup Time                                | t <sub>DS</sub>        |                                                                         | 10  |      |     | ns    |

| SDO Propagation Delay                         | t <sub>DO</sub>        | C <sub>LOAD</sub> = 10pF at SDO pin, SCLK falling<br>edge to SDO stable |     |      | 35  | ns    |

| SDO Rise and Fall<br>Times                    | t <sub>FT</sub>        |                                                                         |     | 1    |     | ns    |

| SCLK Rising to $\overline{CS}$<br>Rising Time | t <sub>CSH</sub>       |                                                                         | 100 |      |     | ns    |

| CS Pulse Width High                           | t <sub>CSPW</sub>      |                                                                         | 50  |      |     | ns    |

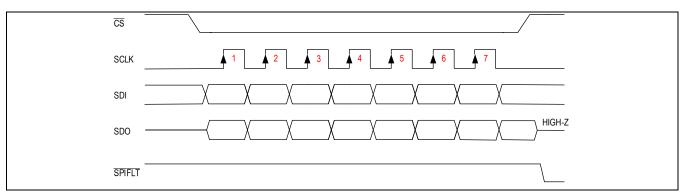

| MAX14918A (see Figure                         | <u>4)</u>              |                                                                         |     |      |     |       |

| IN_ to LATCHEN Setup<br>Time                  | <sup>t</sup> LATCHSU   | MAX14918A only, see <u>Figure 4</u>                                     | 10  |      |     | ns    |

| THERMAL PROTECTION                            | 1                      |                                                                         |     |      |     |       |

| Per-Channel Thermal<br>Shutdown Temperature   | T <sub>JSHDN</sub>     | Junction temperature rising per-channel                                 |     | 160  |     | °C    |

| Per-Channel Thermal<br>Shutdown Hysteresis    | T <sub>JSHDN_HYS</sub> |                                                                         |     | 15   |     | °C    |

| Chip Thermal Shutdown                         | T <sub>CSHDN</sub>     | Temperature rising                                                      |     | 150  |     | °C    |

| Chip Thermal-Shutdown<br>Hysteresis           | T <sub>CSHDN_HYS</sub> |                                                                         |     | 10   |     | °C    |

| LDO Shutdown<br>Temperature                   | T <sub>DSHDN</sub>     | Temperature rising                                                      |     | 160  |     | °C    |

| ELECTROMAGNETIC CO                            | OMPATIBILITY           |                                                                         |     |      |     |       |

| Surge Tolerance                               | V <sub>SURGE</sub>     | OUT_ to COM, IEC 61000-4-5<br>1.2μs/50μs waveform (42Ω/0.5μF)           |     | ±1.2 |     | kV    |

| ESD Contact<br>Discharge                      | V <sub>ESD_C</sub>     | OUT_ to COM, IEC 61000-4-2                                              |     | ±8   |     | kV    |

| ESD Air-Gap Discharge                         | V <sub>ESD_A</sub>     | OUT_ to COM, IEC 61000-4-2                                              |     | ±25  |     | kV    |

| ESD HBM                                       |                        | All pins                                                                |     | ±2   |     | kV    |

**Note 1:** All units are production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

**Note 2:** Current into the device is positive and current out of the device is negative.

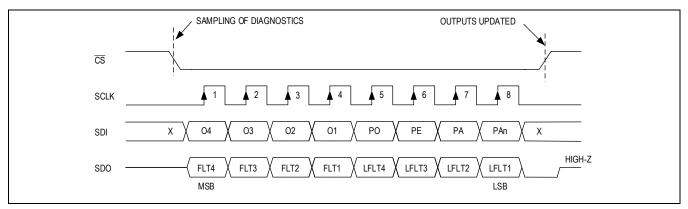

## **Timing Diagrams**

Figure 3. SPI Timing Diagram

Figure 4. IN\_ to LATCHEN Setup Time

# SPI / Parallel Controlled Quad Low-Side Switches with Reverse Current Detection

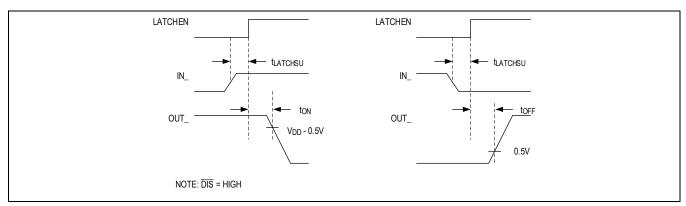

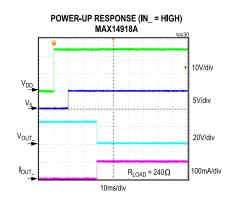

### **Typical Operating Characteristics**

( $V_{DD}$  = +24V,  $V_L$  =  $V_5$ , INRUSH = 0V, HISLEW =  $V_L$ ,  $T_A$  = +25°C, unless otherwise noted)

## SPI / Parallel Controlled Quad Low-Side Switches with Reverse Current Detection

#### ( $V_{DD}$ = +24V, $V_L$ = $V_5$ , INRUSH = 0V, HISLEW = $V_L$ , $T_A$ = +25°C, unless otherwise noted)

www.analog.com

# MAX14918, MAX14918A

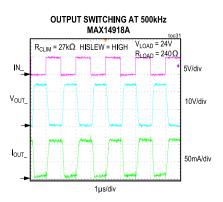

# **Pin Configuration**

### **Pin Descriptions**

| PIN        |            |                 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   | REF    | <b>T</b> |

|------------|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|

| MAX14918   | MAX14918A  | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   | SUPPLY | Туре     |

| 22         | 22         | V <sub>DD</sub> | Linear Regulator Supply Input. Connect to 24V supply if<br>powering V <sub>5</sub> with the internal 5V regulator. If the MAX14918 or<br>MAX14918A is powered by an external 5V supply at the V <sub>5</sub><br>input, V <sub>DD</sub> input must either be connected to GND or left<br>unconnected. Bypass V <sub>DD</sub> to GND using a 1 $\mu$ F ceramic<br>capacitor. |        | Power    |

| 21         | 21         | V <sub>5</sub>  | 5V Supply Input or 5V Linear Regulator Output. Bypass V <sub>5</sub> to GND using a 1µF ceramic capacitor. V5 is the primary device supply and is required for normal operations.                                                                                                                                                                                          |        | Power    |

| 9          | 9          | VL              | Logic Supply Input. Connect a voltage supply between 1.62V and 5.5V. Bypass VL to GND using a 0.1 $\mu$ F ceramic capacitor.                                                                                                                                                                                                                                               |        | Power    |

| 1, 2, 6, 7 | 1, 2, 6, 7 | PGND            | Power Ground. Connect PGND to GND and Exposed Pad (EP).                                                                                                                                                                                                                                                                                                                    |        | Ground   |

| 15         | 15         | GND             | Common ground for all power supplies, logic pins, and input signals. Connect to Exposed Pad.                                                                                                                                                                                                                                                                               |        | Ground   |

| 24         | 24         | OUT1            | Low-Side Switch Output 1                                                                                                                                                                                                                                                                                                                                                   |        | Output   |

| 3          | 3          | OUT2            | Low-Side Switch Output 2                                                                                                                                                                                                                                                                                                                                                   |        | Output   |

| 5          | 5          | OUT3            | Low-Side Switch Output 3                                                                                                                                                                                                                                                                                                                                                   |        | Output   |

| 8          | 8          | OUT4            | Low-Side Switch Output 4                                                                                                                                                                                                                                                                                                                                                   |        | Output   |

# MAX14918, MAX14918A

| 4  | 4  | NC      | No Connection                                                                                                                                                                                                                                               |    |                                   |

|----|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------|

| 18 |    | CS      | Chip Select Input. Assert low to latch the input states and enable the SPI interface. Has a weak internal pullup.                                                                                                                                           | VL | Logic Input                       |

| 17 |    | SCLK    | Serial Clock Input. Has a weak internal pulldown.                                                                                                                                                                                                           | VL | Logic Input                       |

| 16 |    | SDI     | Serial Data Input. Data is clocked into SDI on the rising edge of SCLK. Has a weak internal pulldown.                                                                                                                                                       | VL | Logic Input                       |

| 14 |    | SDO     | Serial Data Output. Data on SDO is updated on the falling edge of SCLK. SDO is three-stated with internal $100k\Omega$ pulldown resistor when $\overline{CS}$ is high.                                                                                      | VL | Logic<br>Output<br>Push-Pull      |

| 13 |    | SPIFLT  | SPI Fault. $\overline{\text{SPIFLT}}$ transitions low when a fault is detected on the SPI interface. Connect a pullup resistor to VL.                                                                                                                       | VL | Logic<br>Output<br>Open-<br>Drain |

|    | 18 | IN1     | Control Logic Input for OUT1. Has a weak internal pulldown.<br>IN1-to-OUT1 control is transparent when LATCHEN is low.                                                                                                                                      | VL | Logic Input                       |

|    | 17 | IN2     | Control Logic Input for OUT2. Has a weak internal pulldown.<br>IN2-to-OUT2 control is transparent when LATCHEN is low.                                                                                                                                      | VL | Logic Input                       |

|    | 16 | IN3     | Control Logic Input for OUT3. Has a weak internal pulldown.<br>IN3-to-OUT3 control is transparent when LATCHEN is low.                                                                                                                                      | VL | Logic Input                       |

|    | 14 | IN4     | Control Logic Input for OUT4. Has a weak internal pulldown.<br>IN4-to-OUT4 control is transparent when LATCHEN is low.                                                                                                                                      | VL | Logic Input                       |

|    | 13 | LATCHEN | Set LATCHEN low for transparent INto-OUT_ operation. Set<br>LATCHEN high to latch the logic at the IN_ inputs. When<br>LATCHEN is high, the OUT_ switches are not affected by the<br>logic state change at the IN_ inputs. Has a weak internal<br>pulldown. | VL | Logic Input                       |

| 10 | 10 | RCLIM   | Global Current Limit Setting Resistor for OUT1 to OUT4. Place a resistor between RCLIM and GND to define maximum load current through the switches. See <u>Current Limiting</u> section for details.                                                        | V5 | Analog<br>Input                   |

| 19 | 19 | HISLEW  | Slew Rate Setting Input. Drive HISLEW high to enable high slew rate on all outputs. Set HISLEW low for low slew rate. Has a weak internal pulldown.                                                                                                         | VL | Logic Input                       |

| 23 | 23 | INRUSH  | Inrush Current Enable Input. Drive INRUSH high to enable 2x current limiting for 10ms (min) after any switch is turned on. Drive INRUSH low to disable inrush current. Has a weak internal pulldown.                                                        | VL | Logic Input                       |

| 20 | 20 | DIS     | Drive DIS low to turn off all OUT_ switches, independent of the IN_ status (MAX14918A) or SPI setting (MAX14918). Has a weak internal pulldown.                                                                                                             | VL | Logic Input                       |

| 12 | 12 | FAULT   | Global Open-Drain Fault Output. The FAULT output is low when<br>the device detects a fault condition. See <u>Fault Signaling</u> section<br>for all the conditions that assert the FAULT pin. Connect a pullup<br>resistor to $V_L$ .                       | VL | Logic<br>Output<br>Open-<br>Drain |

| 11 | 11 | REV     | Reverse Current Gate Driver. REV is low when a reverse current<br>is detected on any output. Connect REV to the gate of an<br>external nMOS transistor for supply-load reverse-polarity<br>protection.                                                      | V5 | Logic<br>Output<br>Open-<br>Drain |

| EP | EP | EP      | Exposed Pad. Connect EP to GND.                                                                                                                                                                                                                             |    |                                   |

MAX14918, MAX14918A

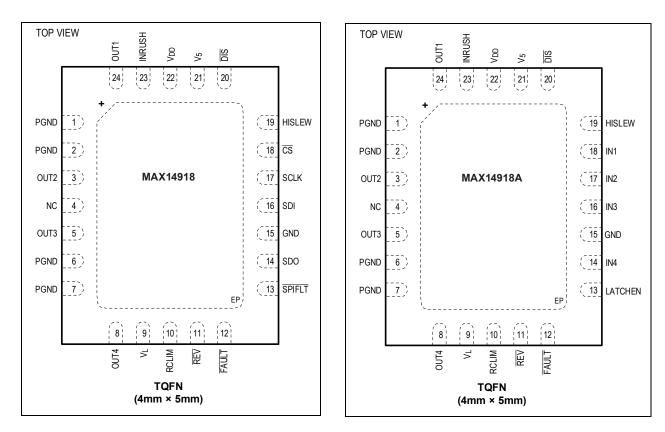

## Functional Diagrams MAX14918

### MAX14918A

### **Detailed Description**

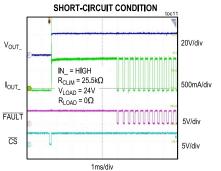

The MAX14918 and MAX14918A are quad 700mA low-side switches for industrial applications, featuring  $140m\Omega$  (typ) low on-resistance with integrated surge protection. The maximum load current through the switches are actively limited. The current limit can be set to meet different system needs and is resistor-settable between 100mA (typ) and 900mA (typ). The switch outputs are protected against short circuit to voltages in the range of 0V to 49V and are protected against thermal overload. Integrated line-to-GND surge protection of up to  $\pm 1.2$ kV/42 $\Omega$  makes external TVS protection unnecessary.

The internal active clamps limit the OUT\_ voltages to +55V (typ), enabling fast turn-off of inductive loads. The devices offer additional control for protection and diagnostics, including thermal overload, reverse-current detection, V<sub>5</sub> supply undervoltage detection, and faults on the RCLIM current-limit setting pin. For load that draws high inrush current, the MAX14918 and MAX14918A have the inrush mode, which provides double the current after switch turn-on for 10ms (min). The devices feature reverse-current detection which can be used to prevent damage caused by high reverse current resulting from field load and supply miswiring.

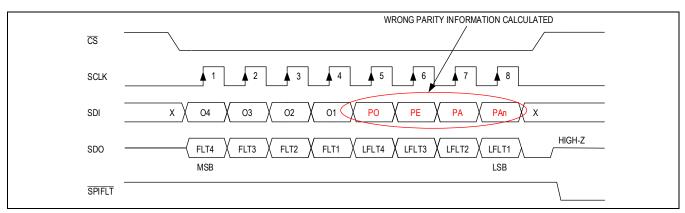

The MAX14918 has an SPI allowing control of multiple MAX14918 devices through a common daisy-chained SPI for high channel-count applications minimizing galvanic isolation requirements. Per-channel diagnostics are returned in the SPI readback. Data corruption on the SDI data is automatically detected and signaled on the SPIFLT output. See <u>Serial</u> <u>Peripheral Interface (MAX14918 Only)</u> section for information on configuring and reading diagnostics with single or daisy-chained devices.

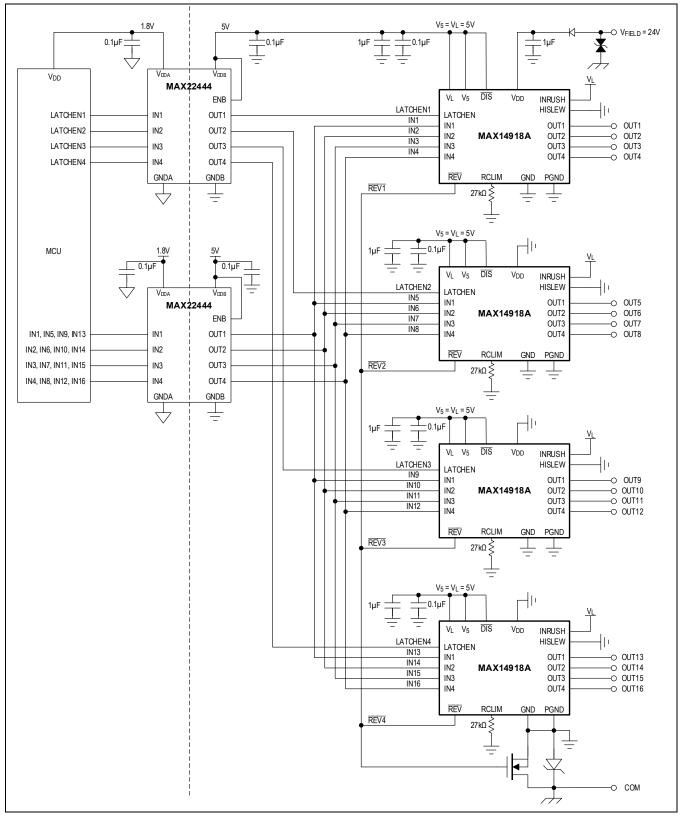

The MAX14918A offers pin-based switch control with a latch option (LATCHEN), which reduces number of isolation channels through multiplexing of shared IN1 to IN4 control inputs while using LATCHEN signals as chip select inputs among multiple MAX14918A devices.

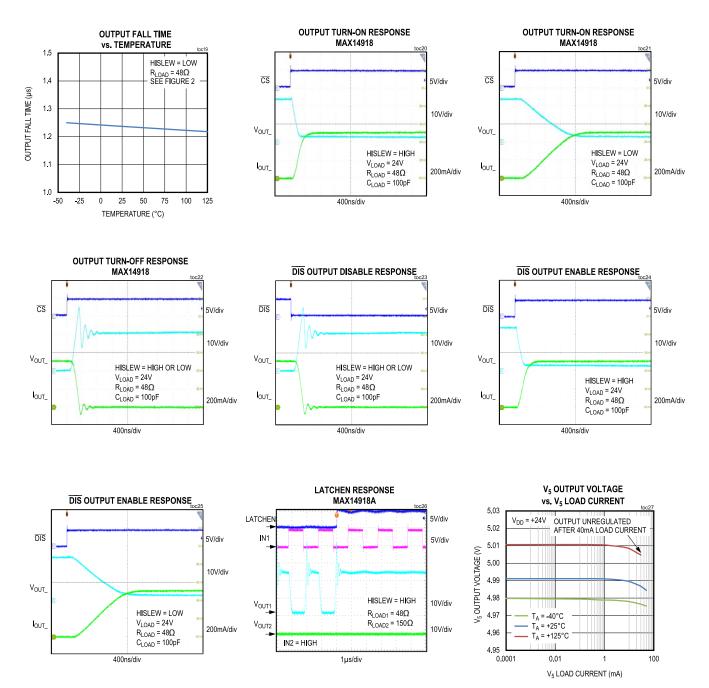

Output slew rate control (HISLEW) provides controlled turn-on edges to reduce LC oscillation due to long cables. A global DIS control signal allows quick turn-off of all OUT\_ switches.

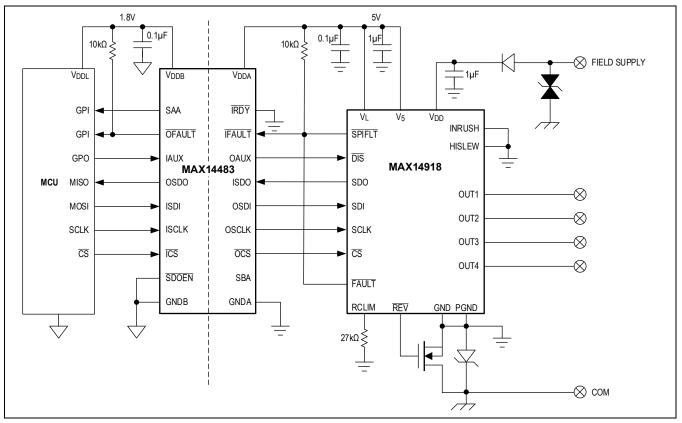

### Power Supply Options with V<sub>DD</sub> and V<sub>5</sub>

The MAX14918 and MAX14918A offer flexible powering options. It can either be powered by  $V_{DD}$  or  $V_5$ . The  $V_{DD}$  supply supports a wide input range from +7V to +65V with a typical case of +24V field supply. The internal LDO regulator handles the wide input to provide a stable +5V output. Applications with limited power rails or unregulated supplies can power the MAX14918 and MAX14918A without the need of external power converters.

In the presence of a stable +5V external supply, the internal LDO can be bypassed, and the MAX14918 and MAX14918A are only powered by external +5V at the V<sub>5</sub> pin. When using the V<sub>5</sub> pin as the supply input, V<sub>DD</sub> is grounded or left unconnected.

### **5V Linear Regulator**

The integrated 5V linear regulator ( $V_5$ ) can supply up to 35mA load current. Note that the linear regulator has high power dissipation when high load current is drawn while powered from high supply voltage. Calculate the power dissipation in the regulator as:

$$P_{DIS} = (V_{DD} - V_5) \times I_5$$

The power dissipation might be excessive with high  $V_5$  load current in combination with high  $V_{DD}$  supply voltage, resulting in self-heating of the device. Care must be taken that the MAX14918 and MAX14918A maximum thermal ratings are not exceeded at the highest operating temperature. When the device enters thermal shutdown, the  $V_5$  linear regulator is automatically turned off at junction temperature of 160°C (typ). The regulator turns on automatically when the junction temperature drops by 10°C (typ).

### Logic Supply $V_L$

The logic supply V<sub>L</sub> supports a wide voltage range of +1.62V to +5.5V. V<sub>L</sub> can either be powered by V<sub>5</sub> or by external +1.8V or +3.3V supply to enable interfacing with microcontrollers, FPGAs, or digital isolators. The logic supply powers the digital interface and logic blocks of the MAX14918 and MAX14918A.

### Undervoltage Lockout

When the  $V_{DD}$ ,  $V_5$ , or  $V_L$  supply voltage is under their respective UVLO threshold, all OUT\_ switches are off.

### **Current Limiting**

The MAX14918 and MAX14918A feature resistor-settable active current limiting, common to all output switches (OUT1 to OUT4). When the current across the switch exceeds the current limit, the load current is limited by the low-side switch. The current limit can be set between 100mA (typ) and 900mA (typ) by  $R_{CLIM}$  resistor between RCLIM pin and GND. The equation to determine  $R_{CLIM}$  for a required  $I_{LIM}$  is:

$$R_{CLIM}(k\Omega) = \frac{V_{CLIM} \times K_1}{(I_{LIM} - K_2)(mA)}$$

where

V<sub>CLIM</sub> = 1.165V (min), 1.2V (typ), 1.235V (max)

K<sub>1</sub> = 17260 (min), 18000 (typ), 19418 (max)

$K_2$  (mA) = -67.1 (min), 0 (typ), 36.98 (max)

The recommended R<sub>CLIM</sub> is between 24k $\Omega$  and 100k $\Omega$ . Use the minimum value of V<sub>CLIM</sub>, K<sub>1</sub> and K<sub>2</sub> to calculate the R<sub>CLIM</sub> value associated with the minimum I<sub>LIM</sub>. If no resistor is connected to the RCLIM pin or R<sub>CLIM</sub> is more than 650k $\Omega$  (typ), I<sub>LIM</sub> is internally set to 650mA (min). If the R<sub>CLIM</sub> resistor is less than 6.5k $\Omega$  (typ), all OUT\_ switches are turned off. The RCLIM pin is short-circuit protected.

For example, assuming the maximum operating load current of a system is less than 600mA, to ensure that the current limit is always higher than 600mA, the R<sub>CLIM</sub> resistor is:

$$R_{CLIM}(k\Omega) = \frac{V_{CLIM} \times K_1}{(I_{LIM} - K_2)(mA)} = \frac{1.165 \times 17260}{(600 + 67.1)(mA)} = 30.14k\Omega$$

### **Fault Signaling**

The FAULT pin is a global fault indication. It is an open-drain logic output that transitions low when the MAX14918 or MAX14918A detects a fault condition. When the device exits fault status and all switches are in normal operation, the FAULT pin transitions passive high. FAULT is asserted for any of the following conditions:

- Chip thermal shutdown

- Any of the OUT\_ switches that are turned on are in thermal overload

- Reverse current detected at OUT\_

- V<sub>5</sub> UVLO

- Short-circuit detected on the RCLIM pin

During power-up,  $\overline{FAULT}$  is asserted until V<sub>5</sub> goes above its UVLO condition (V<sub>5\_UVLO</sub>).  $\overline{FAULT}$  is asserted if any of the switches in ON state are in thermal overload or reverse current condition.

In addition to the open-drain FAULT pin, the MAX14918 also provides fault signaling through the SPI. See <u>MAX14918</u> <u>Thermal Faults (FLT\_ and LFLT\_) on SDO</u> section on how real-time and latched faults are transmitted in each SPI transaction.

### **Chip Thermal Protection**

The device temperature is constantly monitored when the MAX14918 and MAX14918A are powered up (V<sub>5</sub> > V<sub>5\_UVLO</sub>). When the device die temperature rises above 150°C (T<sub>CSHDN</sub>, typ), the device enters thermal shutdown, the global FAULT is asserted low, and all OUT\_ switches are turned off until the chip temperature drops below 140°C (T<sub>CSHDN</sub> - T<sub>CSHDN</sub> HYS).

If the temperature of an output channel rises above  $160^{\circ}C$  (T<sub>JSHDN</sub>), that output is turned off. When the per-channel temperature falls by the hysteresis amount of  $15^{\circ}C$  (T<sub>JSHDN</sub> <sub>HYS</sub>), the output is restored to normal operation.

The integrated LDO features a separate temperature sensor that monitors the temperature resulted from the LDO power dissipation. If the LDO temperature rises above 160°C ( $T_{DSHDN}$ ), the LDO is turned off. It wakes up after cooling down by 10°C ( $T_{CSHDN}_{HYS}$ ).

During normal operation, if any of the above temperature thresholds are triggered, the FAULT output transitions low.

### **INRUSH Mode**

The MAX14918 and MAX14918A offer the inrush mode which supports loads that draw higher current during turn-on. In the inrush mode, each switch provides at least double the current set by the  $R_{CLIM}$  resistor for the inrush duration of 10ms (min) or 12.5ms (typ). After the inrush period, the switch current limit reverts to the value set by  $R_{CLIM}$

### Global Disable (DIS)

The MAX14918 and MAX14918A feature a global DIS input that turns off output switches (OUT1 to OUT4) regardless of its input state. When DIS transitions low, the outputs are in high-impedance within 100ns.

When DIS transitions high, all outputs are switched according to their associated input state. The disable and enable response times for the MAX14918 and MAX14918A are similar to the output turn-on and turn-off propagation delay times.

The disable output option is useful when the microcontroller or the FPGA has to intervene and quickly force all outputs off in the event of a fault.

### Latch Enable (LATCHEN) (MAX14918A Only)

The latch enable input (LATCHEN) allows the MAX14918A to be used in transparent or hold mode. When the latch enable is high, the output is not affected by its associated input (IN\_). When the latch enable is low, the input (IN\_) to output (OUT\_) control is transparent. The MAX14918A LATCHEN-to-OUT\_ delay is the same as IN\_-to-OUT\_ delay specified in the <u>Electrical Characteristics</u>.

The LATCHEN input reduces number of isolation channels through multiplexing of shared IN1 to IN4 control inputs while using LATCHEN signals as chip select inputs among multiple MAX14918A devices. See *Figure 11* for details.

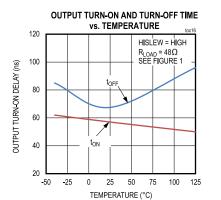

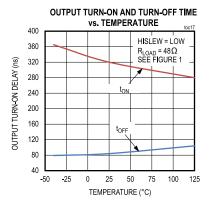

### **Output Slew Rate Control**

The HISLEW pin controls the output turn-on edges. When the HISLEW input is low, output transitions are slower, and the MAX14918 and MAX14918A operate up to 50kHz switching frequency. The slow slew rate mode (HISLEW = low) is useful in applications where the load is capacitive and is connected through a long cable. The cable inductance and possible load capacitance generate LC oscillation during turn-on transitions. If the current during oscillation exceeds the reverse current detection threshold, it is detected as a reverse condition. The MAX14918 and MAX14918A force the REV pin low for 2 seconds, which is the auto-retry time ( $t_{REV}_{AR}$ ). See <u>Reverse Current Detection</u> section for details. The slow slew rate during the output turn-on reduces the magnitude of LC oscillation and EMI.

When the HISLEW input is high, the output transitions are much faster, and the MAX14918 and MAX14918A can operate up to 500kHz switching frequency. This mode is useful in applications where the devices drive resistive loads.

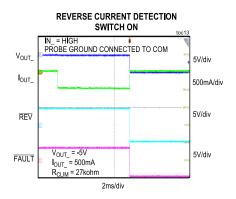

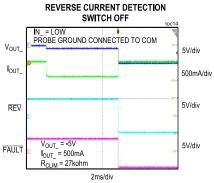

#### **Reverse Current Detection**

The MAX14918 and MAX14918A feature reverse current detection, which is signaled by the REV logic output. A reverse current on any output (OUT\_) can happen when the field supply is miswired with a reverse polarity. The device also protects against a direct reverse connection of the field supply between OUT\_ and COM.

Reverse currents are drawn out of outputs (OUT\_) when a negative voltage is applied across any OUT\_ and COM with the OUT\_ switch either in on or off state. If the reverse current flowing out of any output exceeds 150mA (typ), the REV output transitions low to signal a reverse current condition.

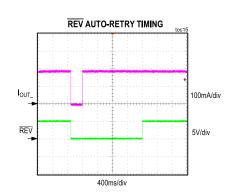

The MAX14918 and MAX14918A drive  $\overline{\text{REV}}$  low and automatically turns off all four OUT\_ switches when it detects a reverse current condition. The  $\overline{\text{REV}}$  output is held low and all four output switches remain off for the auto-retry duration  $(t_{\text{REV}}A_R)$  of 2 seconds (typ) to protect against all possible reverse load miswiring combinations. After the auto-retry delay, the outputs are turned back to the state defined by the IN\_ inputs (MAX14918A) or O\_ bits (MAX14918), and  $\overline{\text{REV}}$  is pulled high. If the cause for reverse current is still present and a reverse current is again detected, the auto-retry scheme turns  $\overline{\text{REV}}$  low again, forcing all outputs off for 2s ( $t_{\text{REV}}A_R$ ).

The  $\overline{\text{REV}}$  output can drive the gate of an external nMOS which opens the PCB field ground to the field COM connection, thereby stopping the reverse current flow. The on-resistance of the external nMOS should be chosen such that it does not contribute significantly to a channel R<sub>ON</sub> since all four output currents flow through the reverse-protecting nMOS. Its R<sub>ON</sub> should be significantly less than one-fourth of the R<sub>ON</sub> of the internal switch, which is less than 35m $\Omega$  (typ).

## MAX14918, MAX14918A

### **Transient Energy Protection**