# **Engineer-to-Engineer Note**

ANALOG Technical notes on using Analog Devices products and development tools Visit our Web resources http://www.analog.com/ee-notes and <u>http://www.analog.com/processors</u> or e-mail processor.support@analog.com or processor.tools.support@analog.com for technical support.

## ADSP-SC596/SC598 Processor Thermal Guidelines

Contributed by Prasanth Rajagopal, Deepak Huchaiah and Vikram Venkatadri

Rev 1 – October 12, 2023

The ADSP-SC596/SC598 processor is a dual-SHARC+® core DSP that doubles the audio performance of a single SHARC+ core and adds an integrated Arm Cortex-A55 core that runs up to 1.2 GHz. This high performance comes with an anticipated cost of increased power consumption and heat dissipation from the processor die. Issues related to heat dissipation and its mitigation is not new to any industry, but, could be considered as relatively newer to SHARC+ based applications. It is important to understand how to manage thermal analysis before designing a system and throughout the life cycle of the product.

This application note provides guidelines for evaluating thermal designs on systems using the ADSP-SC596/SC598 family of processors. This document assumes that the reader is familiar with typical thermal design and management. The details shared in this document needs to be thoroughly evaluated and verified when applying to the actual system design. There are various standard, passive and active thermal management techniques such as heat sinks, fans, etc., that can be applied considering overall cost and mechanical requirements. Additionally, it is important to take into consideration the heat flow contributed by other components as well as any other system-level conditions.

## **Power Consumption**

The power consumed by the chip is dissipated as thermal energy. If this heat is not dissipated fast enough, the chip temperature increases, and the junction temperature can cross beyond the maximum specification limit (125°C). Furthermore, this heat can also spread to other components on the board, if not evaluated and designed properly. In such cases, hot spots can occur in various regions of the board, and the temperature of other components can increase significantly.

The power consumption of the chip when running application software varies according to an increase in junction temperature. ADI provides a power calculator for ADSP-SC596/SC598 processors<sup>[3]</sup>. <u>Table 1</u> is extracted from the power calculator. For average power calculations, three typical application scenarios (activity levels) are considered; each scenario has different Activity Scaling Factor (ASF).

- Activity 1 In this use case, all the accelerators (two FIR, four IIR) are assumed to be used 30% of time. All the cores are assumed to execute tight MAC operations 50% of time and IDLE operation 50% of time, on average.

- Activity 2 In this use case, all the accelerators (two FIR, four IIR) are assumed to be used 50% of time. Both of the SHARC cores are assumed to execute tight MAC operations 70% of time and IDLE operation 30% of time, on average. The Arm core is assumed to execute 75% of time for tight math operations and 25% of time for IDLE operation, on average.

Copyright 2023, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Engineer-to-Engineer Notes.

Peak Activity - In this use case, all the accelerators are assumed to be used 70% of time. All of the cores are assumed to execute tight operations.

The following junction temperatures are considered:

- 85°C Maximum junction temperature; typically used for consumer application.

- □ 100°C High junction temperature used in automotive application.

- □ 125°C Maximum junction temperature for the chip as well as for automotive applications

| Activity Level | Junction<br>Temperature for<br>static power<br>estimation (°C) | VDD_INT Dynamic<br>Power<br>(mW) | VDD_INT<br>Static Power<br>(mW) | Total VDD_INT<br>Power<br>(mW) |

|----------------|----------------------------------------------------------------|----------------------------------|---------------------------------|--------------------------------|

| Activity 1     | 85                                                             | 2999                             | 1147                            | 4146                           |

| Activity 1     | 125                                                            | 2999                             | 3523                            | 6522                           |

| Activity 2     | 100                                                            | 3417                             | 1746                            | 5163                           |

| Activity 2     | 125                                                            | 3417                             | 3523                            | 6940                           |

| Peak Activity  | 100                                                            | 3965                             | 1746                            | 5711                           |

| Peak Activity  | 125                                                            | 3965                             | 3523                            | 7488                           |

Table 1: Power Calculations

Notes on Table 1:

- The power consumption of the activity levels are taken from the ADSP-SC59x power calculator <sup>[3]</sup>. Various clock frequencies are assumed to be the default values in the power calculator. Core clock is assumed to be 1GHz for SHARC and 1.2 GHz for A55

- □ Only power from VDD\_INT at 1V is considered in thermal analysis. Power from other power supplies in the chip (VDD\_EXT, VDD\_REF, VDD\_ANA, VDD\_PLL, VDD\_DMC) are not significant from a thermal perspective and, hence, are not considered.

- □ The ASF for each core and accelerators are mentioned, which contribute to the total power.

- □ The peak activity case is a worst-case software for the chip that is given only for reference. It will not be realistic in a customer use case.

The data in <u>Table 1</u> illustrates how the VDD\_INT power levels could vary with respect to the junction temperature of the processor die. For instance, there is an increase of 2.3W of static power, when the junction temperature rises from 85°C to 125°C. Similarly, when we compare between activity 1 and peak activity, there is an increase of 1W when higher activity levels are executed at same temperature.

## **Phases of Thermal Analysis**

The phases of thermal evaluation include thermal simulation of the system and the actual measurement on the board.

- During simulation, most of the inputs, including boundary conditions and the power consumption of the components, are derived out of estimations and overall system assumptions. Hence, the simulation results are highly dependent on the accuracy of these estimations.

- During the measurement phase, the total power, and temperature are measured physically to verify whether they are within limits by running end application software.

If the temperature dissipated by the processor and all other components in the system are well within their data sheet specification, then the thermal design may be taken forward. Otherwise, the assumptions taken during simulation may not have been accurate enough, and, hence, various board tests can be done to fine-tune simulation.

#### **Thermal Simulation**

Thermal simulation of a board uses 3D Computational Fluid Dynamics (CFD) software (FLOW-3D®). Flotherm® from Mentor Graphics (Siemens) and Icepack® from Ansys are popular tools in the market. There are many other vendors as well.

#### The ECXML Model

Electronics Cooling eXtensible Markup Language (ECXML) is a neutral file format intended to facilitate the provision of thermal models from suppliers to end users for use in 3D CFD thermal simulation tools. A de-facto standard for several years, ECXML is now published by JEDEC as the JEP181 guideline. Forcing a supplier to provide multiple proprietary formats that support these multiple tools is an onerous undertaking and one that, to date, has limited the availability of such simulation models. ECXML now published as JEDEC JEP181.

ADI provides an ECXML format package model for processors on the ADI website, its zip file<sup>[4]</sup> provides usage instructions. The instructions can be used with CFD thermal software that supports importing ECXML-based model.

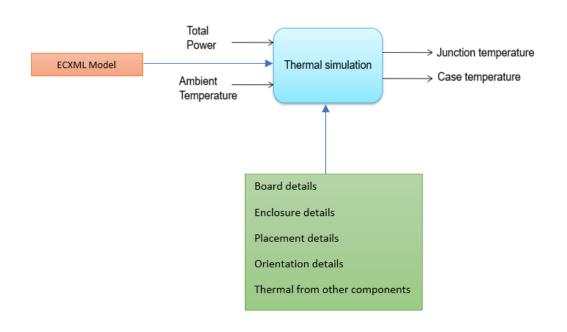

There are several input parameters in a typical thermal simulation, as shown in <u>Figure 1</u>. ADI provides an estimation of the total power via the power calculator and provides the ECXML model of the package. The customer decides the ambient temperature. The details in the green box are also specific to the customer board and system. The important output of the simulation is the final junction temperature of the chip.

#### Figure 1: ECXML Inputs

The ECXML model is a package model with all material information including:

- 1. Thermal characteristics of the device

- 2. Dimensions of the package

Customers can use this model for their system-level thermal simulation.

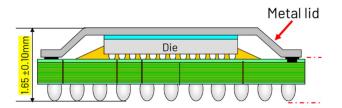

Figure 2 is a pictural representation of the processor package (used only for reference). In the figure, the package size is  $17\text{mm} \times 17\text{mm}$ ; the die size is  $6.48\text{mm} \times 5.86\text{mm} \times 0.355\text{um}$ . All finer dimensions in the figure are available from the ECXML model.

Figure 2: Reference Package

As mentioned in the processor data sheet, the application system thermal simulation is required for accurate temperature analysis. The thermal simulation must account for all specific 3D system design features, including, but not limited to other heat sources, use of heat sinks, use of thermal interface materials, and the system enclosure details. Thermal models of the package are available from Analog Devices product web page (under the Tools and Simulations tab). The thermal models are compatible with all major thermal simulation tools.

The use of JEDEC  $\theta$ JA,  $\theta$ JC, or  $\Psi$ JT thermal parameters for application system thermal estimates is not recommended as indicated in the JEDEC51 specification<sup>[6]</sup>: "*This methodology is not meant to and will not predict the performance of a package in an application-specific environment*." Therefore, these parameters are no longer provided in the device data sheet.

#### Non-uniform power distribution

Legacy SHARC processor families such as ADSP-214xx as well as SHARC+ processor families such as ADSP-SC58x/ADSP-SC57x/ADSP-2156x products consume lower power (~2W to ~4W). The latest generation of products such as the ADSP-SC59x family consume higher power (>5W) owing to a greater number of high-performance cores and accelerators.

The higher power and larger silicon area results in non-uniform power distribution and subsequent hotspots. The ECXML model of the ADSP-SC596/SC598 processor family considers uniform power distribution because it simplifies the thermal simulation. However, to account for these hotspots in simulation phase, an offset value must be added to the junction temperature obtained from simulations.

Different offset values across activity/power levels are provided in Table 2.

| Activity Level | Dynamic Power<br>at 1V (mW) | Static Power at<br>125°C and 1V<br>(mW) | Total Power at<br>1V<br>(mW) | Offset<br>(°C) |

|----------------|-----------------------------|-----------------------------------------|------------------------------|----------------|

| Peak Activity  | 3965                        | 3523                                    | 7488                         | 6              |

| Activity 2     | 3417                        | 3523                                    | 6940                         | 5              |

| Activity 1     | 2999                        | 3523                                    | 6522                         | 4              |

Table 2: Offset Values

The offset values are provided for three different power-levels: peak activity, activity 2 and activity 1. The total power level should be mapped to one of the activity levels shown in the table. For power numbers which fall between two activity levels, choose the next higher activity. For example, if the simulation result from the ECXML mode is 110°C (Tj) and the total power is around 5200mW, then an offset of 6°C (from activity 2 level) must be added to 110°C. The final value from the simulation then becomes 116°C.

| Junction<br>Temperature (°C) | Static Power (mW) |

|------------------------------|-------------------|

| 25                           | 191.00            |

| 40                           | 306.00            |

| 55                           | 481.00            |

| 70                           | 747.00            |

| 85                           | 1147.00           |

| 100                          | 1746.00           |

| 105                          | 2015.00           |

| 115                          | 2660.00           |

| 125                          | 3523.00           |

Static power influence on higher temperature – Simulation phase Table 3 is a snapshot of the static current consumption from the power calculator.

Table 3:Static Current Consumption

<u>Table 3</u> shows that higher static current consumption is observed at higher junction temperatures. However, as discussed earlier, the thermal simulation can only consider ambient temperature and the total chip power consumption as input. The total chip power consumption (an input) depends on the junction temperature (an output). The following method can be used to account for this static power dependency on output junction temperature, during simulation.

- Method 1: Static power at maximum junction temperature (125°C) can be used as input (3523 mW). This covers worst case conditions, safely.

- Method 2: The thermal software must consider the input power as a function of output temperature; the final junction temperature is recorded after the simulation attains a steady saturated state. We expect customers to discuss the temperature influence on static current, with CFD software vendors. There may be various techniques in the software to ensure that rise in power with temperature is considered during simulation.

Since dynamic power does not increase significantly with temperature, it can be derived directly from power calculator and added to total power number.

#### **Measuring Junction Temperature**

The ADSP-SC596/SC598 processors include a Thermal Monitoring Unit (TMU) module. The TMU is integrated into the processor die and digital infrastructure using an MMR-based system access to measure the die temperature variations in real-time. The TMU is a thermal sensor system that consists of temperature-sensors, a calibrated reference current source, and a current comparator. These sensors are placed strategically closer to various hot spots in the chip to allow software to read the maximum junction temperature recorded among multiple sensors.

The most important use case of the TMU is to let application know about whether the processor die temperature has crossed certain limits during run-time. These limits are configured as ALERT and FAULT limits during TMU initialization. The FAULT interrupt can be used to inform the external world that the chip temperature needs critical attention by various mechanism such as internal triggers or toggling a GPIO. For more information on the software programming of the TMU, refer to the hardware reference manual <sup>[2]</sup>. For information on the accuracy of the sensors in the TMU, refer to the device data sheet <sup>[1]</sup>.

## **Recommendations for Thermal Relief**

Since every system and hardware requirements are different, it is not possible to recommend specific reliefs. From the limited tests done on an evaluation board, the following observations were made:

- Thermal paste gives better results than thermal pads.

- Heat sinks may help in two situations: lower ambient temperature and/or lower current from the chip.

- Additional relief mechanisms such as controlled air-flow techniques (fan, coolant, etc.) may be required at higher temperatures, especially when there are several high-power components on the board.

### Conclusion

Compared to older generation SHARC/SHARC+ processors, the ADSP-SC596/SC598 processors can dissipate much more heat when running high performance audio applications. Specially at higher temperatures, it becomes challenging to control the heat dissipation without external measures such as heat sink or air flow. Early thermal analysis and design becomes important when operating the chip at higher temperature.

## References

- [1] ADSP-SC596/SC598 SHARC+ Dual Core DSP with Arm Cortex-A55 Data Sheet. Rev. 0, July 2023. Analog Devices, Inc.

- [2] ADSP-SC595 /SC596/SC598 SHARC+ Processor Hardware Reference. Rev 0.2, August 2022. Analog Devices, Inc.

- [3] EE-440: Estimating Power for ADSP-SC596/SC598 SHARC+ Processors. Rev. 2, July 2022. Analog Devices, Inc.

- [4] Analog Devices, Inc. *Thermal Models*. <u>https://www.analog.com/en/products/ADSP-SC598.html#product-tools</u>

- [5] Bornoff, R. (2020, September 18). *What STEP was for CAD, ECXML is for electronics thermal simulation*. https://blogs.sw.siemens.com/simcenter/ecxml-jedec-jep181-thermal/

- [6] JEDEC. 2023. ECXML Guidelines for Electronic Thermal System Level Models XML Requirements. https://www.jedec.org/standards-documents/docs/jep181

- [7] EE-449: ADSP-21593/21594/ADSP-SC592/SC594 Processor Thermal Guidelines. Rev. 1, September 2023. Analog Devices, Inc.

## **Document History**

| Revision                                                                                 | Description      |

|------------------------------------------------------------------------------------------|------------------|

| Rev I – October, 2023<br>by Prasanth Rajagopal,<br>Deepak Huchaiah, Vikram<br>Venkatadri | Initial Release. |