# **Engineer-to-Engineer Note**

ANALOG Technical notes on using Analog Devices products and development tools Visit our Web resources http://www.analog.com/ee-notes and <u>http://www.analog.com/processors</u> or e-mail processor.support@analog.com or processor.tools.support@analog.com for technical support.

# ADSP-SC595/SC596/SC598 Programming Guidelines for Dynamic Memory Controller

Contributed by Deepak SH

Rev 1 – September 19, 2022

# Introduction

The ADSP-SC595/SC596/SC598 SHARC+® processor incorporates a Dynamic Memory Controller (DMC), which provides a glueless interface between off-chip DDR3 memory devices and the rest of the processor infrastructure. For further technical details on the DMC module, refer to the *ADSP* - *SC595/SC596/SC598 SHARC+ Processor Data Sheet*<sup>[1]</sup> and the *ADSP-SC595/SC596/SC598 SHARC+ Processor Hardware Reference*<sup>[2]</sup>. This EE-note describes some of the important programming guidelines that must be followed when interfacing the ADSP-SC595/SC596/SC598 SHARC+ processor with a DDR memory device. The associated *zip file*<sup>[3]</sup> includes code examples that can be used for basic DMC initialization, DMC initialization using the DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx spreadsheet, and DMC re-initialization. The code examples include a subroutine that can be used to validate the DMC interface for different types of accesses (for example, core, DMA, 8-/16-/32-/64-bit) and data patterns (for example, all 0x0, all 0xF, all 0x5, all 0xA, incremental, random, and all bits toggling).

# Software Considerations – DMC Programming Model

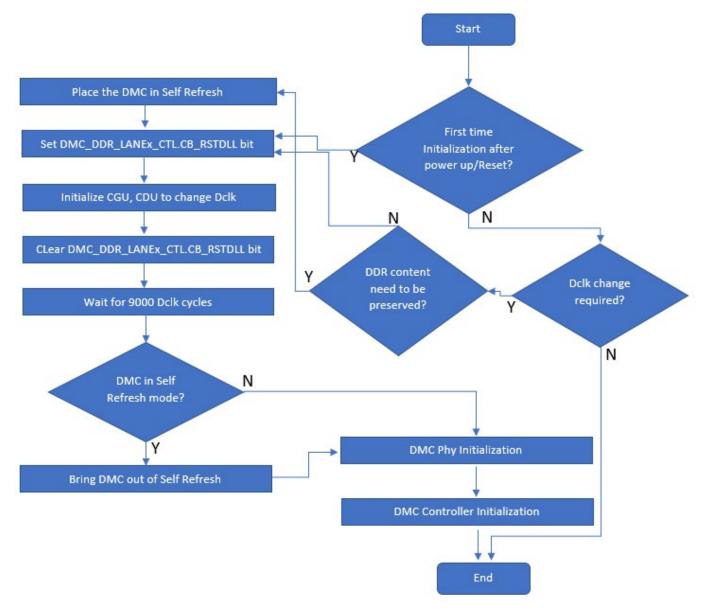

Figure 1 shows the DMC programming flow. DMC initialization consists of:

- Clock Generation Unit (CGU) Initialization

- DMC PHY Initialization

- DMC Controller Initialization

Figure 1: DMC Programming Model Flow Chart

## **CGU Initialization**

Verify that the DDR clock (DCLK) is configured to the required frequency. DCLK can come from either CGU0 (default) or CGU1 by programming the CDU. Route DCLK from CGU1 for cases where the required DCLK frequency is asynchronous to the CCLK and SYSCLK frequencies. For example, assume a case where the required CCLK frequency is 1000 MHz, the SYSCLK frequency is 500 MHz, and the DCLK frequency is 800 MHz. Achieving this frequency combination may not be possible with a single CGU. To realize this configuration, generate CCLK and SYSCLK using CGU0 and DCLK using CGU1. For details on how to program the CGU and Clock Distribution Unit (CDU), refer to the *ADSP-SC595/SC596/SC598 SHARC+ Processor Hardware Reference*<sup>[2]</sup>.

Once the DMC is initialized, ensure that the DCLK frequency has not changed.

## **DMC** Initialization

After reset, configure the DCLK generated from CGU0 to the default frequency. The CGU must be reinitialized to configure the DCLK to the required new frequency. As shown in <u>Figure 1</u>, complete the following steps to initializing the CGU for the first time after reset:

- 1. Set (=1) the DMC\_DDR\_LANE0\_CTL0.CB\_RSTDLL and DMC\_DDR\_LANE1\_CTL0.CB\_RSTDLL bits.

- 2. Change the DMC clock frequency.

- 3. Clear (=0) the DMC\_DDR\_LANE0\_CTL0.CB\_RSTDLL and DMC\_DDR\_LANE1\_CTL0.CB\_RSTDLL bits.

- 4. Wait 9000 DCLK cycles for the DLL to lock.

Typically, the CGU is first initialized in either *preload code* (when the application is loaded through the emulator) or by *init code* (when the application is loaded by the boot process, in the init block) The code may need to be modified to meet system requirements. Refer to the Modifying Default Preload and Initialization Code for Customized CGU/DMC Settings section for details.

#### **On-the-Fly DMC Re-initialization**

If the DCLK frequency is not being changed as part of the re-initialization process, no CGU reinitialization is necessary.

If the DCLK frequency is being changed as part of the re-initialization process, but the DDR content does not need to be preserved, use the same steps as described in DMC Initialization to re-initialize the CGU.

However, if the DCLK frequency is being changed, and code or data already resident in DDR memory must be preserved, follow these steps to re-initialize the CGU:

- 1. Ensure that the DMC is in the idle state by waiting for the DMC\_STAT.IDLE bit to be set (=1).

- 2. Place the DMC into self-refresh mode by setting (=1) the DMC\_CTL.SRREQ bit.

- 3. Poll the DMC\_STAT.SRREQ bit to set (=1); wait for the self-refresh mode transition to complete.

- 4. Set (=1) the DMC\_DDR\_LANE0\_CTL0.CB\_RSTDL and DMC\_DDR\_LANE1\_CTL0.CB\_RSTDLL bits.

- 5. Initialize the CGU and CDU to change the DCLK frequency.

- 6. Clear (=0) the DMC\_DDR\_LANE0\_CTL0.CB\_RSTDLL and DMC\_DDR\_LANE1\_CTL0.CB\_RSTDLL bits.

- 7. Wait 9000 DCLK cycles for the DLL to lock.

- 8. Bring the DMC out of self-refresh mode by clearing (=0) the DMC\_CTL.SRREQ bit.

- 9. Poll the DMC\_STAT.SRREQ bit to clear (=0); wait for the self-refresh exit to complete.

When re-initializing the DMC, the CGU/DMC initialization code should **not** be executed from the DDR memory. Refer to the SC598\_DMC\_Re\_initialization\_A55\_Core0 project in the associated *zip file*<sup>[3]</sup>.

1. Use \_\_attribute\_\_((section(".12\_cached\_code"))) to place the functions in internal memory

for the A55 core. Use  $Pragma("section(\"seg_int_code\")")$  to place the functions in internal memory for the SHARC core

- 2. Use \_\_attribute\_\_((section(".l2\_cached\_data"))) to place the data in internal memory for the A55 core. Use \_\_Pragma("section(\"seg\_int\_data\")") to place the data in internal memory for SHARC core

- 3. Change the PWR service files as follows:

- a. Place adi\_pwr\_ClockInit, adi\_pwr\_Init and adi\_pwr\_SelectCduClockSource functions in internal memory.

- b. Remove adi\_osal\_ExitCriticalRegion and adi\_osal\_EnterCriticalRegion function calls in the adi pwr WriteDIVCTLLocal function

The first 16 bytes of DDR memory are overwritten by the controller during initialization.

## **DMC PHY Initialization**

Refer to Performing ZQ Calibration and Programming Duty Cycles sections in the *ADSP-SC595/SC596/SC598 SHARC+ Processor Hardware Reference*<sup>[2]</sup>. Ensure that the workaround to anomaly 20000117 from the *Silicon Anomaly List*<sup>[4]</sup> is applied.

#### **DMC Controller Initialization**

<u>Table 1</u> through <u>Table 4</u> show the bit fields used to program the DMC. Refer to the Programming the DMC Controller and Programming DQ Delay Trim sections in the *ADSP-SC595/SC596/SC598 SHARC+ Processor Hardware Reference* <sup>[2]</sup>. The controller has a set of registers with bit fields that control:

- Hard-Wired Settings

- Mandatory Settings

- Optional Settings

#### Hard-Wired Settings

There are some bits which are hard-coded in the DDR controller that software cannot adjust. These are shaded in ORANGE in the DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx spreadsheet.

#### Mandatory Settings

Many bits in the configuration, timing, and mode registers must be programmed based on the system to ensure proper DMC operation in the application. These are shaded in **GREEN** in the DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx spreadsheet. For details on how to program these bit fields, refer to the *ADSP-SC595/SC596/SC598 SHARC+ Processor Hardware Reference*<sup>[2]</sup>.

#### **Optional Settings**

There are some bit fields which are not required to be modified for standard DMC operation; however, deeper knowledge of these bits saves power and improves throughput in certain application configurations. For example, the DMC\_CTL.SREQ bit can be used to operate the DMC in a low-power (self-refresh) mode. The DMC\_CTL.PREC bit enables automatic precharge after each access. The DMC\_CTL.ADDRMODE bit improves throughput by switching between page and bank interleaving addressing modes. Users are expected to understand the functionality of these bits clearly by going

through the *ADSP-SC595/SC596/SC598 SHARC+ Processor Hardware Reference*<sup>[2]</sup> and the corresponding memory device data sheet (especially for mode registers). These bits are shaded in <u>YELLOW</u> in the DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx spreadsheet.

| Register | Bit Field |                                                     | Bit Field (C=Controller, V<br>M=JEDEC) |                                                        | Comment                                                                |

|----------|-----------|-----------------------------------------------------|----------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------|

|          | DDR3EN    | DDR3 mode enable                                    | 0-C                                    |                                                        | Always program to 1 for standard DMC operation.                        |

|          | INIT      | Initialize DRAM<br>Start                            | 2-C                                    | Mandatory                                              | Always program to 1 for standard DMC operation.                        |

|          | SRREQ     | Self-Refresh Request                                | 3-C                                    |                                                        | Program <b>0</b> for standard DMC operation                            |

|          | PDREQ     | Power Down<br>Request                               | 4-C                                    |                                                        | Program <b>0</b> for standard DMC operation.                           |

|          | PREC      | Precharge                                           | 6-C                                    | Optional                                               | Program <b>0</b> for standard DMC operation.                           |

|          | RESET     | Reset SDRAM                                         | 7-C                                    |                                                        | Program <b>0</b> for standard DMC operation                            |

|          | ADDRMODE  | Addressing<br>(Page/Bank) Mode                      | 8-C                                    |                                                        | Program <b>0</b> for standard DMC operation. s.                        |

|          | RDTOWR    | RDTOWR Read-to-Write Cycle. 11:9-C Manda            | Mandatory                              | Always program to <b>5</b> for standard DMC operation. |                                                                        |

| DMC_CTL  | PPREF     | Postpone Refresh                                    | 12-C                                   |                                                        | Program <b>0</b> for standard DMC operation                            |

|          | DLLCAL    | DLL Calibration<br>Start                            | 13-C                                   |                                                        | Program <b>0</b> for standard DMC operation                            |

|          | RDECMDDAT | Enhanced Read<br>Command and Data<br>Buffer Enable. | 14-C                                   |                                                        | Always program to 1 for standard DMC operation.                        |

|          | Reserved  | Reserved                                            | 23:15 <b>-</b> C                       |                                                        | Always write these bits with <b>zero</b> .                             |

|          | ZQCS      | ZQ Calibration Short                                | 24-C                                   |                                                        | Program <b>0</b> for standard DMC operation                            |

|          | ZQCL      | ZQ Calibration Long                                 | 25-C                                   | Ontional                                               | Program <b>0</b> for standard DMC operation                            |

|          | RL_DQS    | Read leveling during<br>DQS Gating<br>Training.     | 26-C                                   | Optional                                               | Program <b>0</b> for standard DMC operation                            |

|          | AL_EN     | Additive Latency<br>Enable                          | 27-C                                   | Mandatory                                              | Program 1 for Dclk frequency above 667 MHz                             |

|          | DDR_2133  | DDR3_2133 speed bin operation                       | 28-C                                   | Mandatory                                              | Program 1 for Dclk frequency above 933 MHz. This also enabled tras[5]. |

|          | Reserved  | Reserved                                            | 31:29                                  | Mandatory                                              | Always write these bits with <b>zero</b> .                             |

Table 1: DMC Control Register Bit Fields

| Register | Bit Field |                 | Bit field<br>(C=Controller,<br>M=JEDEC) | Value     | Comment                                                             |

|----------|-----------|-----------------|-----------------------------------------|-----------|---------------------------------------------------------------------|

|          | IFWID     | Interface Width | 3:0-C                                   |           | Always program to <b>2</b> (16-bit). All other values are reserved. |

|          | SDRWID    | SDRAM Width     | 7:4-C                                   |           | Always program to <b>2</b> (16-bit). All other values are reserved. |

| DMC_CFG  | SDRSIZE   | SDRAM Size      | 11:8 <b>-</b> C                         | Mandatory | Obtain from memory device data sheet.                               |

|          | EXTBANK   | External Banks  | 15:12-C                                 |           | Always program to zero (16-bit). All other values are reserved.     |

|          | Reserved  | Reserved        | 31:16 <b>-</b> C                        |           | Always write these bits with <b>zero</b> .                          |

Table 2: DMC Configuration Register Bit Fields

| Register | Bit Field |                                        | Bit field<br>(C=Controller,<br>M=JEDEC) | Value     | Comment                                                                                              |

|----------|-----------|----------------------------------------|-----------------------------------------|-----------|------------------------------------------------------------------------------------------------------|

|          | TRCD      | RAS# to CAS#<br>delay time             | 3:0-C                                   |           |                                                                                                      |

|          | TWTR      | Write-to-Read<br>delay                 | 7:4-C                                   |           |                                                                                                      |

|          | TRP       | Precharge-to-<br>Active time           | 11:8-C                                  |           | Obtain from memory device data sheet.                                                                |

| DMC_TR0  | TRAS      | Active-to-<br>Precharge time           | 17:12-C                                 |           |                                                                                                      |

|          | Reserved  | Reserved                               | 19:18-C                                 |           | Always write these bits with zero.                                                                   |

|          | TRC       | Active-to-Active<br>time               | 25:20-С                                 |           | Obtain from memory device data sheet.                                                                |

|          | Reserved  | Reserved                               | 27:26-C                                 |           | Always write these bits with zero.                                                                   |

|          | TMRD      | Mode register<br>set- to-active        | 31:28-C                                 |           | Obtain from memory device data sheet.                                                                |

|          | TREF      | Refresh Interval                       | 13:0-С                                  |           |                                                                                                      |

|          | Reserved  | Reserved                               | 15:14-C                                 |           | Always write these bits with zero.                                                                   |

| DMC_TR1  | TRFC      | Refresh-to-<br>Active<br>command delay | 24:16-C                                 |           | Obtain from memory device data sheet.                                                                |

| 2        | Reserved  | Reserved                               | 27-25-С                                 |           | Always write these bits with zero.                                                                   |

|          | TRRD      | Active-to-Active<br>time               | 30-28-C                                 | Mandatory | Obtain from memory device data sheet.                                                                |

|          | Reserved  | Reserved                               | 31                                      |           | Always write this bit with zero.                                                                     |

|          | TFAW      | Four Activate<br>Window                | 4:0-C                                   |           | Obtain from memory device data sheet. tFAW is not applicable for LPDDR mode and should be kept zero. |

|         | TFAW5               | Extended<br>Timing Four-<br>Active Window<br>bit 5 | 5-C     |                                                                                                      |

|---------|---------------------|----------------------------------------------------|---------|------------------------------------------------------------------------------------------------------|

|         | Reserved            | Reserved                                           | 7:6-C   | Always write these bits with zero.                                                                   |

| DMC_TR2 | TRTP                | Internal Read to<br>Precharge time                 | 11:8-C  | Obtain from memory device data sheet. tRTP is not applicable for LPDDR mode and should be kept zero. |

|         | TWR<br>(LPDDR only) | Write recovery<br>time                             | 15:12-C |                                                                                                      |

|         | ТХР                 | Exit power down<br>to next valid<br>command        | 19:16-C | Obtain from memory device data sheet.                                                                |

|         | tCKE                | CKE min pulse<br>width                             | 23:20-С |                                                                                                      |

|         | Reserved            | Reserved                                           | 31:24-C | Always write these bits with zero.                                                                   |

Table 3: DMC Timing Register Bit Fields

| Register | Bit Field           |                                   | Bit field<br>(C=Controller,<br>M=JEDEC) | Value         | Comment                                                                                              |

|----------|---------------------|-----------------------------------|-----------------------------------------|---------------|------------------------------------------------------------------------------------------------------|

|          | BL                  | Burst Length                      | 1:0-C, A1:A0-M                          |               | Only BL=8 is supported for DDR3. Always<br>program these bits with<br>zero.                          |

|          | CL                  | CAS Latency                       | 6:4,2-C, A6:A4,<br>A2- M                |               | Program these bits with the required CAS latency.                                                    |

|          | Reserved            | Reserved                          | 3-C, A3-M                               |               | Always write this bit with zero.                                                                     |

| DMC_MR0  | Reserved            | Reserved                          | 7 <b>-</b> C, A7-M                      | Mandatory     | Always write this bit with zero.                                                                     |

|          | DLLRST              | DLL Reset                         | 8-C, A8-M                               | Optional      | Set this bit for DDR3 mode.                                                                          |

|          | WRRECOV             | Write recovery                    | 11:9-C, A11:A9-<br>M                    |               | Program these bits with tWR value from the memory device data sheet.                                 |

|          | PD                  | Active Power Down<br>Mode         | 12-C, A12-M                             |               | Can be left unchanged for standard DMC operation.                                                    |

|          | Reserved            | Reserved                          | 15:13-C,<br>A15:A13-M                   | Hard<br>Wired | These bits are hard-wired to zero.                                                                   |

|          | Reserved            | Reserved                          | 31:16-C                                 |               |                                                                                                      |

|          | DLLEN               | DLL Enable                        | 0-C, A0-M                               |               | Keep this bit set to zero.                                                                           |

|          | DIC0, DIC1          | Output Driver<br>ImpedanceControl | 5,1-C, A5,A1-M                          |               | Select the driver impedance using these bits from the memory side.                                   |

|          | RTT0, RTT1,<br>RTT2 | On Die Termination<br>(ODT)       | 9,6,2-C,<br>A9,A6,A2-M                  |               | Select ODT value using these bits from the memory side.                                              |

|          | AL                  | Additive Latency                  | 4,3-C, A4,A3-M                          |               | Can be cleared for basic DMC initialization. Refer to the memory device data sheet for more details. |

| DMC_MR1 | WL       | Write Leveling                    | 7 <b>-</b> C, A7-M     |               | This bit shall be written with one                                   |

|---------|----------|-----------------------------------|------------------------|---------------|----------------------------------------------------------------------|

|         | Reserved |                                   | 8, 10-C, A8,<br>A10 –M |               | These bits are reserved for future use (must be programmed to zero). |

|         | TDQS     | Termination Data<br>Strobe        | 11-C, A11-M            |               | Should be zero, as it is not applicable for 16-bit devices.          |

|         | QOFF     | Output Buffer<br>Enable           | 12-C, A12-M            |               | Should be zero.                                                      |

|         | Reserved | Reserved                          | 15:13-C,<br>A15:A13-M  | Hard<br>Wired | These bits are hard-wired to zero.                                   |

|         | Reserved | Reserved                          | 31:16-C                |               |                                                                      |

|         | PASR     | Partial Array Self<br>Refresh     | 2:0-C, A2:A0-M         | -             | This bit is unchanged for standard DMC operation.                    |

|         | CWL      | CAS Write Latency                 | 5:3-C, A5:A3-M         | Mandatory     | Obtain from memory device data sheet.                                |

|         | ASR      | Auto Self Refresh                 | 6-C, A6-M              |               | These bits are unchanged for standard DMC                            |

| DMC_MR2 | SRT      | Self-Refresh<br>Temperature Range | 7-C, A7-M              |               | operation.                                                           |

|         | Reserved | Reserved                          | 31-8-C                 | Hard<br>Wired | These bits is hard-wired to zero.                                    |

Table 4: DMC DDR3 Mode Register Bit Fields

## **DMC Initialization Code**

The *zip file*<sup>[3]</sup> associated with this EE-note provides code examples that can be used to initialize the CGU and DMC controller for any custom settings.

#### CGU Initialization

For custom clock settings, change the structures ADI\_PWR\_CGU\_PARAM\_LIST and ADI\_PWR\_CDU\_PARAM\_LIST in the adi\_pwr\_SC59x\_config.c file accordingly. Also, change the cclkdclk\_ratio ratio accordingly. For example, when CCLK = 1000 MHz and Dclk = 800 MHz, the ratio is 1000/800 = 1.25.

#### DMC Initialization

The adi\_dmc.c and adi\_dmc.h files can be used to initialize the DMC to the required settings. For example, the main.c file in the ADSP-SC598\_DMCconfigGenerator\_Core1 project in the associated *zip file*<sup>[3]</sup> illustrates two ways to initialize the DMC for a DDR3 memory with DCLK frequency of 800 MHz as per the JESD79-3F JEDEC specification<sup>[5]</sup>.

Initialize\_DMC\_Basic – Enable this macro in the main.h file to initialize the DMC by configuring the ADI\_DMC\_PARAM\_LIST structure. Figure 2 shows a snapshot from the main.c file of the ADI\_DMC\_PARAM\_LIST structure of code used to initialize the DMC with the Initialize\_DMC\_Basic macro. All of the DDR parameters required to initialize DMC/DDR memory are computed based on the JESD79-3F JEDEC specification<sup>[5]</sup>. The Initialize\_DMC\_Basic approach can be used to quickly test DDR across different frequencies, DriveStrength, and ODT settings. The complete list

of DDR parameters used in this method can be printed on a console using the adi\_printDMCconfig() API (enable the Print\_DMC\_Config macro). The DDR parameters printed are in the format used in the adi\_dmc\_SC59x\_family\_x\_config.h file of the preload/Init code.

```

ADI_DMC_PARAM_LIST Dmc_config;

```

```

Dmc config.DDRSpeedBin = ADI DDR3 MEM 1600;

/* Choose the Speedbin based on the DDR clock frequency */

Dmc config.DDRClockTimePeriod = 1.25f;

/* Time period or tck of DDR clock */

Dmc config.CoreClockTimePeriod = 1.00f;

/* Time period of Core clock */

Dmc config.ProAddCmdDrv = 100;

/* Processor's DriveStrength of Address and command */

/* Processor's DriveStrength of DQ, DQS, DM and clock */

Dmc config.ProClkDqsDrv = 90;

Dmc config.ProOdt = 75;

/* Processor's ODT of DQ, DQS, DM */

Dmc config.MemSize = ADI DDR3 MEM 8Gb;

/* size of DDR memory */

Dmc config.MemTemp = ADI DDR3 MEM NOMINAL TEMP; /* Operating temperature range of DDR memory */

Dmc config.MemDrv = ADI DDR3 DRV 40;

/* DDR memory's DriveStength */

/* DDR memory's ODT */

Dmc config.MemOdt = ADI DDR3 ODT 120;

```

cclkdclk\_ratio = (Dmc\_config.DDRClockTimePeriod/ Dmc\_config.CoreClockTimePeriod);

#### Figure 2: ADI\_DMC\_PARAM\_LIST Snapshot

Based on the JESD79-3F JEDEC specifications<sup>[5]</sup> given for a particular speed bin, the DDR parameters printed or used for configuring the DMC with the Initialize\_DMC\_Basic method should work from a functional perspective. However, check the parameter values with the specific memory device data sheet using the DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx spreadsheet

**Initialize DMC Advanced** - Enable this macro in main.h file to initialize the DMC by configuring the ADI DMC CONFIG structure. This structure is the same as the one used in the adi dmc SC59x family x config.h file of the preload/Init code. For custom DMC settings, the ADI DMC CONFIG structure must be updated according to the system requirements as shown in Figure configured using Figure 4. The ADI DMC CONFIG structure can be 3 and the DMC Registers List SC595 SC596 SC598.xlsx spreadsheet in the associated zip file<sup>[3]</sup> by entering various DMC-specific and DDR memory-specific parameters (from the device data sheet). See Figure 5. Use the generated hex values for the ADI DMC CONFIG structure from the DMC Registers List SC595 SC596 SC598.xlsx spreadsheet as shown in Figure 6 to configure the macros in main.h file as shown in Figure 3. This method of DMC initialization can be used to customize the DDR initialization routine in the preload/initcode as per the DDR memory data sheet; to gives the flexibility to fine tune any of the required DDR parameters.

```

#define CFG0_REG_DDR_DLLCTLCFG 0x0cf00622ul

#define CFG0_REG_DMC_MR2MR3 0x00180004ul

#define CFG0_REG_DMC_CTL_VALUE 0x08000a05ul

#define CFG0_REG_DMC_TR0_VALUE 0x047000c0ul

#define CFG0_REG_DMC_TR1_VALUE 0x61181860ul

#define CFG0_REG_DMC_TR2_VALUE 0x0450620ul

#define CFG0_REG_DMC_ZQCTL_0 0x00785A64ul

#define CFG0_REG_DMC_ZQCTL_1 0x000000ul

#define CFG0_REG_DMC_ZQCTL_2 0x7000000ul

```

Figure 3: main.h file Snapshot

```

96

cclkdclk_ratio = 1.25;

97

98

/* Set DMC Lane Reset */

adi_dmc_lane_reset(true);

99

100

101

/* Initialize CGU and CDU */

if((uint32_t)adi_pwr_cfg0_init() != 0)

102

103

{

104

return ADI_DMC_FAILURE;

105

}

106

/* Clear DMC Lane Reset */

107

adi_dmc_lane_reset(false);

108

109

// add macros here in a header file and that can be used here

110

static ADI_DMC_CONFIG config =

111

/* ulDDR_DLLCTLCFG */

/* ulDDR_EMR2EMR3 */

/* ulDDR_CTL */

/* ulDDR_MREMR1 */

/* ulDDR_TR0 */

/* ulDDR_TR1 */

/* ulDDR_TR1 */

/* ulDDR_T2 */

/* ulDDR_ZQCTL0 */

/* ulDDR_ZOCTL1 */

112

{

CFG0_REG_DDR_DLLCTLCFG,

113

CFG0_REG_DDR_DLLCTLCFG,

CFG0_REG_DMC_MR2MR3,

CFG0_REG_DMC_CTL_VALUE,

114

CFG0_REG_DMC_MR2MR3,

115

CFG0_REG_DMC_MRMR1,

116

CFG0_REG_DMC_TR0_VALUE,

117

CFG0_REG_DMC_TR1_VALUE,

CFG0_REG_DMC_TR2_VALUE,

118

119

CFG0_REG_DMC_ZQCTL_0,

120

CFG0_REG_DMC_ZQCTL_1,

/* ulDDR_ZQCTL1 */

/* ulDDR_ZQCTL2 */

121

122

CFG0_REG_DMC_ZQCTL_2

123

};

124

/* Initialize DMC PHY registers */

125

126

adi_dmc_phy_calibration(&config);

127

/* Initialize DMC Controller */

128

129

if(adi_dmc_ctrl_init(&config) != ADI_DMC_SUCCESS)

130

{

return ADI_DMC_FAILURE;

131

132

}

```

Figure 4: main.c file Snapshot

| Parameter                      | Value       | Unit |

|--------------------------------|-------------|------|

| DCLK                           | 800         | MHz  |

| SDRAM Size                     | 8192        | MB   |

| tRCD                           | 13.75       | ns   |

| tWTR                           | 6           | tCK  |

| tRP                            | 13.75       | ns   |

| tRAS                           | 35          | ns   |

| tRC                            | 48.75       | ns   |

| tMRD                           | 4           | tCK  |

| tREFI                          | 7.8         | us   |

| tRFC                           | 350         | ns   |

| tRRD                           | 6           | tCK  |

| tFAW                           | 40          | ns   |

| tRTP                           | 6           | tCK  |

| tWR                            | 15          | ns   |

| tXP                            | 5           | tCK  |

| tCKE                           | 4           | tCK  |

| CAS Read Latency (CL)          | 11          | tCK  |

| Burst Length                   | 8           | tCK  |

| Driver Impedance (Memory)      | RZQ/6(40)   | Ohms |

| On Die Termination (Memory)    | RZQ/2(120)  | Ohms |

| Driver Impedance (Processor-   | 100         | Ohms |

| Driver Impedance (Processor-   | 90          | Ohms |

| On Die Termination (Processor) | 75          | Ohms |

| Additive Latency (AL)          | AL Disabled | tCK  |

| CAS Write Latency (CWL)        | 8           | tCK  |

Figure 5: DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx Snapshot

| ADI_DMC_CONFIG Structure | 32 bit Hex value |

|--------------------------|------------------|

| ulDDR_DLLCTLCFG          | CF00722          |

| ulDDR_EMR2EMR3           | 180004           |

| ulDDR_CTL                | 8000A05          |

| ulDDR_MREMR1             | D7000C0          |

| ulddr_tro                | 4271CB6B         |

| ulDDR_TR1                | 61181860         |

| ulDDR_TR2                | 450620           |

| ulDDR_ZQCTL0             | 785A64           |

| ulDDR_ZQCTL1             | 0                |

| ulDDR_ZQCTL2             | 7000000          |

Figure 6: DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx Snapshot

#### Validating the DMC Interface

Once the DMC is initialized, it is important to validate it.

- All DMC registers must be initialized to the correct values

- Resolve any basic issues with the DMC hardware interface

- The DMC must be correctly initialized by the software. The register values from the register browser can be compared with the register values in the DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx spreadsheet.

The Memory\_Sweep\_Test() function can be used to check whether all the cores and DMA (MDMA0) accesses to the DMC are working for different data word sizes (8-/16-/32-/64-bit and 32-byte DMA) and for different data patterns (0x0, 0xF, 0x5, 0xA, incremental, random, and all bits toggling). The main.c file in the ADSP-SC598\_DMCconfigGenerator\_core1 project uses these functions to validate the DMC interface. The memory sweep size used in this code is 0x800000 (8 MB); it can be changed to validate the full DMC memory range (for example, 2 Gb = 256 MB).

#### Creating Preload and Initialization Code with Customized CGU and DMC Settings

Preload and initialization code are two concepts that are related to configuring the CGU and DMC prior to the application code running. For a stand-alone application, while performing an active debug via the emulator preload code is used and for controlling the boot stream initialization code is used.

#### Preload Code

When performing active debug on a target platform, an emulator is used. To make working with the board as transparent as possible for the user, the CrossCore<sup>®</sup> Embedded Studio (CCES) tools automate initialization of the CGU/DMC hardware. Applications can be built and loaded to off-chip memory for use in a debug session on the targeted board. Debugging uses *Preload Code*. The preload code projects can be found at *Analog Devices*\*CrossCore Embedded Studio* 2.11.0\SHARC\ldr\init\_code\SC59x\_Init' in the CCES installation directory.

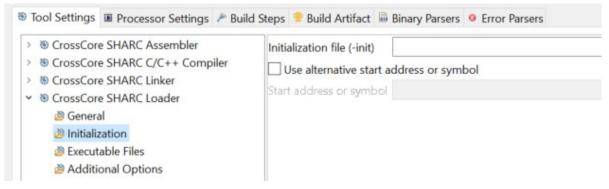

CCES uses the pre-built executable file (See <u>Figure 7</u>) to initialize the CGU and DMC before loading the actual application using the emulator.

| ✓ Ø Device 0 [Core 1] □ C) Apples Devices Core Core Finished ded Studie 2.11 0/SUARCY del pri//SC6500/W probable core1 due | Program                                                                                    | Options               | Silicon revision |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|------------------|

| 🗖 CAAnalaa Davierak Casa-Casa Fashaddad Studio 2.11.0 SUARCAIde askit SC50004 analaad asaa1.duu 🖉 Baata Bura Ataa laad     | ✓ Ø Device 0 [Core 1]                                                                      |                       |                  |

| C:\Analog Devices\CrossCore Embedded Studio 2.11.0\SHARC\Idf\E2KItSC596w_preload_core1.axe Reset, Run after load any       | C:\Analog Devices\CrossCore Embedded Studio 2.11.0\SHARC\ldr\ezkitSC598W_preload_core1.dxe | Reset, Run after load | any              |

Figure 7: Preload Code for EV-SC598-SOM

#### Initialization Code

Unlike preload code, initialization code is actually a part of the application. It is separate from the application. The DXE output is pre-pended to the DXE file of application when CCES assembles the loader stream (LDR) that the processor parses during the boot process. This separate DXE is called the *Initialization Block* in the LDR file. The DXE is booted first into on-chip memory, and subsequently executed before any attempts are made to resolve anything to the external DDR space. It is the ideal place for configuring the CGU and DMC in advance of trying to boot to DDR memory. The Init code projects can be found at *Analog Devices\CrossCore Embedded Studio 2.11.0\SHARC\ldr\init\_code\SC59x\_Init* in the CCES installation directory. The DXE output corresponding to the Init code project can be used as the default initialization code when generating an LDR file by pointing to the DXE in the Loader Options page of the Project Properties. See Figure 8.

Figure 8: Initialization Code Selection in the Loader Options

Typically, for applications requiring a one-time CGU and DMC initialization after reset, the preload (whenloading the application via emulator) or initialization code (when booting the application standalone) is sufficient. However, it is important to understand how to use and modify the default preload and initialization code for customized CGU/DMC settings.

#### Modifying Default Preload and Initialization Code for Customized CGU/DMC Settings

The CGU and DMC settings in the default preload and initialization source code can be modified for the following conditions:

- When using non-default CGU settings

- When using a custom board with a different memory device than the one available on the evaluation board

For example, use the following steps to modify the default preload code sc5948\_preload\_Core0 project for the ADSP-SC598 processor.

- 1. Edit the adi\_pwr\_SC598\_family\_1GHz\_config.h file to change the CGU and CDU configurations.

- 2. Edit the adi\_pwr\_SC59x\_config.h file to configure the cclkdclk\_ratio value.

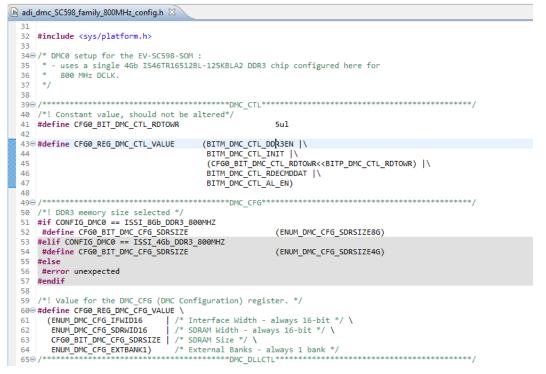

3. Edit the adi\_dmc\_SC598\_family\_800MHz\_config.h file as shown in Figure 10 using the output printed on console (shown in Figure 9) and the adi\_printDMCconfig() API present in the ADSP-SC598\_DMCconfigGenerator\_core1 project. Or, initialize the ADI\_DMC\_CONFIG structure in the adi\_dmc\_SC59x\_config.c file (shown in Figure 11) using the

DMC\_Registers\_List\_SC595\_SC596\_SC598.xlsx (shown in Figure 3 and Figure 6) spreadsheet. See the the associated  $zip file^{[3]}$  for the spreadsheet, and code examples. Refer to the DMC Initialization section for details.

| 🗐 Console 🛛 🔝 Problems 🚺 Executa | ables                                                                                                                                                                                                                                                      |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output                           |                                                                                                                                                                                                                                                            |

| CFG0_BIT_DMC_CTL_DDR3EN          | 101                                                                                                                                                                                                                                                        |

| CFG0_BIT_DMC_CTL_RDTOWR          | 5u1                                                                                                                                                                                                                                                        |

| CFG0_REG_DMC_CTL_VALUE           | ((CFG0_BIT_DMC_CTL_DDR3EN< <bitp_dmc_ctl_ddr3en) bitm_dmc_ctl_init (cfg0_bit_dmc_ctl_rdtowr<<bitp_dmc_ctl_rdtowr) bitm_dmc_ctl_al_en)< td=""></bitp_dmc_ctl_ddr3en) bitm_dmc_ctl_init (cfg0_bit_dmc_ctl_rdtowr<<bitp_dmc_ctl_rdtowr) bitm_dmc_ctl_al_en)<> |

| #define CFG0_BIT_DMC_CFG_SDRSIZE | (ENUM_DMC_CFG_SDRSIZE8G)                                                                                                                                                                                                                                   |

| #define CFG0 REG DMC CFG VALUE \ |                                                                                                                                                                                                                                                            |

| (ENUM_DMC_CFG_IFWID16 /* I       | nterface Width - always 16-bit */ \                                                                                                                                                                                                                        |

| ENUM_DMC_CFG_SDRWID16 /* SI      | DRAM Width - always 16-bit */ \                                                                                                                                                                                                                            |

|                                  | DRAM Size */ \                                                                                                                                                                                                                                             |

| ENUM_DMC_CFG_EXTBANK1) /* E:     | xternal Banks - always 1 bank */                                                                                                                                                                                                                           |

| ADI_DMC_PARAM_DLLCOUNT           | 240ul                                                                                                                                                                                                                                                      |

| CFG0_REG_DMC_DATACYC             | 12ul                                                                                                                                                                                                                                                       |

Figure 9: adi\_printDMCconfig() API Snapshot

Figure 10: adi\_dmc\_SC598\_family\_800MHz\_config.h Snapshot

```

adi_dmc_SC59x_config.c 🖾

44⊖ uint32_t adi_dmc_cfg0_init(void)

45 {

46

uint32_t status = 0u;

47

48

static ADI_DMC_CONFIG config =

49

{

50

CFG0_REG_DDR_DLLCTLCFG,

51

CFG0_REG_DMC_MR2MR3,

52

CFG0_REG_DMC_CTL_VALUE,

CFG0_REG_DMC_TR0_VALUE,

CFG0_REG_DMC_TR0_VALUE,

CFG0_REG_DMC_TR1_VALUE,

CFG0_REG_DMC_TR1_VALUE,

CFG0_REG_DMC_TR2_VALUE,

0x00785A64ul, /* 0x78 (Data/DQS_ODT)

53

54

55

56

57⊝

58

0x5a (90ohms Data/DQS/DM/CLK Drive Strength)

59

0x64 (100ohms Address/Command Drive Strength) */

60

Øul,

0x70000000ul

61

62

};

63

/* Initialize DMC PHY registers */

64

adi_dmc_phy_calibration(&config);

65

66

/* Initialize DMC Controller */

67

if(adi_dmc_ctrl_init(&config) != ADI_DMC_SUCCESS)

68

69

{

70

/* Assign error status return value */

71

status = 1u;

72

}

73

74

return status;

75 }

76

77 /*@}*/

```

Figure 11: adi\_dmc\_SC59x\_config.c Initializing ADI\_DMC\_CONFIG Structure Snapshot

# References

- [1] ADSP-SC595/SC596/SC598: SHARC+ Dual-Core DSP with Arm Cortex-A55 Preliminary Data Sheet (Rev. PrE). Analog Devices, Inc.

- [2] ADSP-SC595/SC596/SC598 SHARC+ Processor Hardware Reference. May 2022, Analog Devices, Inc.

- [3] Associated ZIP File (EE-443V01.zip) forADSP-SC595/SC596/SC598 Programming Guidelines for Dynamic Memory Controller (EE-443). September 2022. Analog Devices, Inc.

- [4] Silicon Anomaly List of the SHARC+®ADSP-SC595/SC596/SC598 product(s), August 2022, Analog Devices, Inc.

- [5] JESD79-3F, July 2012. JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

# **Document History**

| Revision               | Description      |

|------------------------|------------------|

| Rev 1 –September, 2022 | Initial Release. |

| by Deepak SH           |                  |