# **Engineer-to-Engineer Note**

Technical notes on using Analog Devices DSPs, processors and development tools Contact our technical support at dsp.support@analog.com and at dsptools.support@analog.com Or visit our on-line resources http://www.analog.com/ee-notes and http://www.analog.com/processors

# SHARC® DSPs to TigerSHARC® Processors Code Porting Guide

Contributed by Andrew Caldwell and Maikel Kokaly-Bannourah

Rev 1 – July 14, 2004

# **1** Introduction

The following Engineer-to-Engineer note discusses the differences between Analog Devices Inc. (ADI) first and second generation ADSP-2106x and ADSP-2116x SHARC® DSPs and ADSP-TS101 and ADSP-TS20x TigerSHARC® processors.

Over the years, the SHARC DSP architecture has become the world leader for high-end multiprocessor applications. The introduction of the ultra-high performance TigerSHARC architecture makes it the ideal upgrade device for existing SHARC systems looking for a performance boost and a system cost reduction.

This document is a step-by-step, how-to guide for porting SHARC code to its TigerSHARC equivalent. Architectural differences are discussed, and multiple code examples are provided to help you upgrade existing SHARC source code to the next generation of floating-point processors, the TigerSHARC processor family.

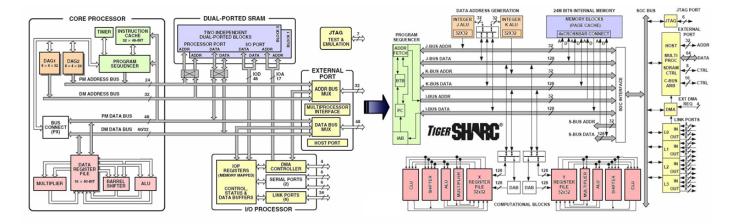

Figure 1. SHARC DSP and TigerSHARC Processor Block Diagrams

Copyright 2004, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices' Engineer-to-Engineer Notes.

# **2** Table of Contents

| 1 Introduction                                                          |   |

|-------------------------------------------------------------------------|---|

| 2 Table of Contents                                                     | 2 |

| 2.1 Code Listing                                                        |   |

| 2.2 Table Listing                                                       | 4 |

| 3 Architecture Overview                                                 | 5 |

| 4 SHARC-to-TigerSHARC Conversion Guidelines                             |   |

| 4.1 Register File                                                       |   |

| 4.2 Data Addressing                                                     |   |

| 4.2.1 Circular Buffers                                                  |   |

| 4.2.2 Addressing in SISD and SIMD                                       |   |

| 4.3 Program Sequencer                                                   |   |

| 4.3.1 Instruction Pipeline                                              |   |

| 4.3.2 Instruction Cache and BTB                                         |   |

| 4.3.3 Program Flow Variations                                           |   |

| 4.3.4 Interrupts                                                        |   |

| 4.4 DMA                                                                 |   |

| 5 SHARC-to-TigerSHARC Conversion Examples                               |   |

| 5.1 Register File                                                       |   |

| 5.2 Data Addressing                                                     |   |

| 5.2.1 Post-Modify and Pre-Modify                                        |   |

| 5.2.2 Circular Buffers                                                  |   |

| 5.2.3 Addressing in SISD and SIMD                                       |   |

| 5.3 Program Sequencer                                                   |   |

| 5.3.1 Pipeline<br>5.3.2 Loops                                           |   |

| 5.3.3 Interrupts                                                        |   |

| 5.4 DMAs                                                                |   |

| 5.4.1 Internal Memory - External Memory                                 |   |

| 5.4.2 Internal Memory - Internal Memory of other DSPs (Multiprocessing) |   |

| 5.4.3 Internal Memory - Link Port I/O                                   |   |

| 6 C Run-Time Environment                                                |   |

| 6.1 Memory .SECTION and SECTION { } Names                               |   |

| 6.2 Register Classification                                             |   |

| 6.2.1 Callee Preserved Registers ("Preserved")                          |   |

| 6.2.2 Caller Save Registers ("Scratch")                                 |   |

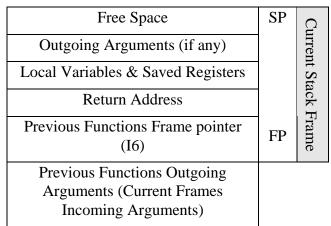

| 6.3 Stack Frame Overview and Differences                                |   |

| 6.3.1 Stack Pointer and Frame Pointer                                   |   |

| 6.3.2 Run-Time Stack                                                    |   |

| 6.4 Code Conversion from SHARC DSPs to TigerSHARC Processors            |   |

| 6.4.1 Procedure Call                                                    |   |

| 6.4.2 Function Prologue                                                 |   |

| 6.4.3 Pushing Additional Data to the Stack                              |   |

| 6.4.5 Popping Data from the Stack                                       |   |

| 6.4.6 Return Values                                                     |   |

| 6.4.7 Function Epilogue                                                 |   |

| 6.4.8 Using Mixed C/C++ and Assembly Naming Conventions                 |   |

| 6.5 Heaps                                                               |   |

| 6.6 Summary                                                             |   |

| 7 Algorithm Code Examples                                               |   |

| 7.1 DFT                                                                 |   |

| 7.1.1 MEMORY Sections                                                   |   |

| 7.1.2 Reset Interrupt Vector                                            |   |

| 7.1.3 Call DB                                                           |   |

| 7.1.4 Data Addressing           | 57 |

|---------------------------------|----|

| 7.2 FIR                         |    |

| 7.2.1 FIR One-to-One Conversion | 57 |

| 7.2.2 Optimized FIR             |    |

| 8 Conclusion                    | 63 |

| 9 References                    |    |

| 10 Document History             | 64 |

# 2.1 Code Listing

| Code 1. JALU and KALU Parallel Instructions                         | 11 |

|---------------------------------------------------------------------|----|

| Code 2. Predicted and Non-predicted Branch                          | 13 |

| Code 3. SHARC DSP Loop                                              | 14 |

| Code 4. TigerSHARC Processor Loop                                   | 14 |

| Code 5. SHARC vs. TigerSHARC Register File Sets                     | 22 |

| Code 6. Post-modify and Pre-modify Data Addressing Operations       | 23 |

| Code 7. Circular Buffers                                            | 23 |

| Code 8. SISD, SIMD and Broadcast Loads                              | 23 |

| Code 9. Delayed Branch                                              | 24 |

| Code 10. Single Loop                                                | 25 |

| Code 11. Nested Loops                                               | 25 |

| Code 12. Standard Timer Interrupt                                   | 27 |

| Code 13. Nested IRQ Interrupt                                       | 28 |

| Code 14. Re-usable IRQ Interrupt                                    | 29 |

| Code 15. User Software Exception                                    | 31 |

| Code 16. SHARC and TigerSHARC to External Memory Device DMA Example | 32 |

| Code 17. SHARC and TigerSHARC Multiprocessor DMA Example            | 34 |

| Code 18. SHARC and TigerSHARC Multiprocessor DMA Example            | 35 |

| Code 19. ADSP-2106x/2116x Procedure Call                            | 40 |

| Code 20. ADSP-21020 Procedure Call                                  | 40 |

| Code 21. TigerSHARC Procedure Call                                  | 40 |

| Code 22. SHARC Function Call Macro                                  | 41 |

| Code 23. TigerSHARC Function Call Macro                             | 41 |

| Code 24. TigerSHARC Function Prologue Macros                        | 41 |

| Code 25. Post-Modify Store to the J Stack                           | 42 |

| Code 26. SHARC "puts" Macro                                         | 42 |

| Code 27. TigerSHARC "puts" Macros                                   | 42 |

| Code 28. Example Showing "puts" Macro Usage                         | 43 |

| Code 29. SHARC and TigerSHARC "save_reg" Macros                     |    |

| Code 30. SHARC "reads(x)" Macro                                     |    |

| Code 31. TigerSHARC "reads(x)" Macro                                | 45 |

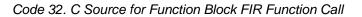

| Code 32. C Source for Function Block FIR Function Call              | 45 |

| Code 33. Example for Retrieval or Arguments Passed to Block FIR     | 46 |

| Code 34. SHARC "gets(x)" Macro                                      | 46 |

| Code 35. TigerSHARC "gets(x)" Macro                                 | 46 |

| Code 36. SHARC "alter(x)" Macro                                     | 46 |

| Code 37. TigerSHARC "alter(x)" Macro                                | 46 |

| Code 38. "restore_reg" Macro on SHARC DSPs                          | 47 |

| Code 39. "restore_reg" Macro on TigerSHARC Processors               | 47 |

| Code 40. Pushing and Popping the Stack Example                                   | 48 |

|----------------------------------------------------------------------------------|----|

| Code 41. ADSP-21020 and ADSP-21160 Function Epilogue Macros                      | 48 |

| Code 42 SHARC Function Epilogue Macros                                           | 49 |

| Code 43. TigerSHARC Function Epilogue Macros                                     | 49 |

| Code 44. SHARC Heap Declaration in "seg_init.asm"                                | 51 |

| Code 45. SHARC Heap MEMORY Section Placement within the .LDF                     | 51 |

| Code 46. TigerSHARC Heap Declaration in "ts_hdr.asm"                             | 51 |

| Code 47. TigerSHARC Heap Memory Section Placement within the .LDF                | 51 |

| Code 48. SHARC Multiple Heap Declaration in "seg_init.asm"                       | 52 |

| Code 49. SHARC Multiple Heap Memory Section Placement within the .LDF            | 53 |

| Code 50. TigerSHARC Multiple Heap Declaration in "ts_hdr.asm"                    | 53 |

| Code 51. TigerSHARC Processors Multiple Heap Memory Section Placement within LDF | 53 |

| Code 52. SHARC and TigerSHARC DFT Example                                        | 56 |

| Code 53. Floating Point Block FIR One-to-One Conversion                          | 60 |

| Code 54. Optimized Floating Point Block FIR                                      | 62 |

|                                                                                  |    |

# 2.2 Table Listing

| Fable 1. SHARC and TigerSHARC Features Overview                      | 6    |

|----------------------------------------------------------------------|------|

| Cable 2. SHARC DSP and TigerSHARC Processor Registers Mapping Scheme |      |

| Fable 3. Sequencer Instructions                                      | . 20 |

| Fable 4. Condition and Loop Termination Codes                        |      |

| Table 5. SHARC and TigerSHARC Default Memory Sections                |      |

| Fable 6. Frame & Stack Pointer Registers                             | . 38 |

| Fable 7. Registers used for Passing Arguments                        | .44  |

| Fable 8. Parameter Return Registers                                  | . 48 |

| Table 9. Accessing C from Assembly                                   |      |

| Fable 10. Accessing Assembly from C                                  | . 49 |

| Fable 11. Accessing C++ from Assembly                                | . 50 |

| Fable 12. Accessing Assembly from C++                                | . 50 |

| Fable 13. SHARC and TigerSHARC Heap Management Functions             | . 54 |

# **3 Architecture Overview**

The first and second generation SHARC - Super Harvard Architecture Computer – DSPs, ADSP-2106x and ADSP-2116x, build on the ADSP-21000 DSP core family to form a complete system-on-chip, adding dual-ported on-chip SRAM, and integrated I/O peripherals.

The SHARC architecture combines a highperformance floating-point DSP core with integrated on-chip features including a host processor interface, DMA controller, serial ports, link ports, and shared bus connectivity for glueless multiprocessing for up to six SHARC processors.

This architecture balances a high-performance DSP core with high-performance buses, yielding an ideal solution for audio, military, communications, test equipment, motor control, imaging and many other applications.

The ADSP-TSxxx TigerSHARC processor family sets a new standard of performance for digital signal processors, combining multiple computation units for floating-point and fixedpoint processing, as well as very large word widths. This new architecture maintains a system-on-achip, scalable computing design philosophy, including up to 24 Mbits of on-chip memory, integrated I/O peripherals, a host processor interface, DMA controllers, link ports, and shared bus connectivity for glueless multiprocessing of up to eight TigerSHARC processors.

The TigerSHARC processor's extremely highperformance core and increased feature set makes it the ideal upgrade device for existing SHARC systems looking for a performance boost and a system cost reduction.

Due to the architectural changes (added units, modified pipeline, increased memory structure, internal bus architecture improvement, etc.) introduced when moving from SHARC DSPs to TigerSHARC processors, the source code requires modification to overcome code incompatibility.

This document first examines the main differences between the two architectures and then shows you how to convert SHARC source code to its TigerSHARC equivalent.

Table 1 summarizes these two architectures mainfeatures.

|                                    | ADSP-2106x                | ADSP-2116x             | ADSP-TS101                    | ADSP-TS20x                    |

|------------------------------------|---------------------------|------------------------|-------------------------------|-------------------------------|

| Electrical and Mechanical Features |                           |                        |                               |                               |

| Production Process                 | 0.35-0.5 microns          | 0.18-0.25 microns      | 0.13 microns                  | 0.13 microns                  |

| Core Clock Rate                    | 40-66 MHz                 | 80-100 MHz             | 250-300 MHz                   | 500-600 MHz                   |

| Temperature Range                  | -40° to 85°C              | -40° to 85°C           | -40° to 85°C                  | -40° to 85°C                  |

| Core Supply Voltage                | 5 V / 3.3 V               | 2.5 V / 1.9 V          | 1.2 V                         | 1.0 V / 1.2 V                 |

| I/O Supply Voltage                 | 5 V / 3.3 V               | 3.3 V                  | 3.3 V                         | 2.5 V                         |

| Package Size                       | 23x23 mm                  | 27x27 mm               | 19x19 / 27x27 mm              | 25x25 mm                      |

|                                    |                           | Core Features          |                               |                               |

| Core                               | SISD                      | SIMD                   | MIMD                          | MIMD                          |

| Processing Elements                | Х                         | X and Y                | X and Y                       | X and Y                       |

| Register File                      | 32x40 bits                | 64x40 bits             | 64x32 bits                    | 64x32 bits                    |

| Fixed-point data                   | 32-bit                    | 32-bit                 | 8-, 16-, 32-, 64-bit          | 8-, 16-, 32-, 64-bit          |

| Floating-point data                | 32-, 40-bit               | 32-, 40-bit            | 32-, 40-bit                   | 32-, 40-bit                   |

| Pipeline Depth                     | 3 stages                  | 3 stages               | 8 stages                      | 10 stages                     |

| Branch Prediction                  | N/A                       | N/A                    | Branch Target Buffer<br>(BTB) | Branch Target Buffer<br>(BTB) |

| Memory                             | 0.5-4 Mbit                | 1-4 Mbit               | 6 Mbit                        | 4-24 Mbit                     |

| Internal Data Bus Width            | 1x40-bit and 1x48-<br>bit | 2x64–bit               | 3x128-bit                     | 4x128-bit                     |

| Data Addressing                    | DAGs                      | DAGs                   | IALUs                         | IALUs                         |

| Timers                             | 1 / 2                     | 1                      | 2                             | 2                             |

|                                    |                           | External Interfaces    |                               |                               |

| External Memories                  | SRAM, SDRAM               | SRAM, SBSRAM,<br>SDRAM | SRAM, SBSRAM,<br>SDRAM        | SRAM,SBSRAM,<br>SDRAM         |

| External Bus Width                 | 48 bits                   | 32/64 bits             | 32/64 bits                    | 32/64 bits                    |

| DMA Channels                       | 10                        | 14                     | 14                            | 14                            |

| I/O Throughput                     | 300M bytes/sec            | 800M bytes/sec         | 1.8G bytes/sec                | 4G bytes/sec                  |

| Multiprocessor                     | 6 + Host                  | 6 + Host               | 8 + Host                      | 8 + Host                      |

| Link Ports                         | 6 x 4-bits                | 6 x 4/8 bits           | 4 x 8-bits                    | 2-4 x 8-bits (LVDS)           |

| Link Ports Compatibility           | ADSP-2116x                | ADSP-2106x             | N/C                           | N/C                           |

| Serial Ports                       | 2                         | 2-4                    | N/A                           | N/A                           |

| IRQ Lines                          | 3                         | 3                      | 4                             | 4                             |

| G-P I/O Pins                       | 4                         | 4                      | 4                             | 4                             |

N/A: Not Applicable, N/C: Not Compatible

# Table 1. SHARC and TigerSHARC Features Overview

# 4 SHARC-to-TigerSHARC Conversion Guidelines

Table 2 shows the ADSP-2106x and ADSP-2116x SHARC DSPs registers, along with their TigerSHARC processor (ADSP-TS101 and ADSP-TS20x) equivalent.

The main differences between the two architectures, and how they can be mapped to each other, are discussed.

The SHARC-to-TigerSHARC register map shown throughout this EE-Note is not fixed. It is simply an example of how this can be done.

The given mapping scheme has been selected to provide code translation in the simplest way, with the SHARC DSP family features in mind.

This does not necessarily mean that it will produce the most efficient TigerSHARC code. It will, however, help you to translate source code to run on TigerSHARC platforms.

| Register Type                 | ADSP-2106x     | ADSP-2116x      | ADSP-TS101       | ADSP-TS201       |

|-------------------------------|----------------|-----------------|------------------|------------------|

|                               | Register File  |                 |                  |                  |

| Processing Element X<br>(P/R) | R15-0, F15-0   | R15-0, F15-0    | xR15:0, xFR15-0  | xR15:0, xFR15-0  |

| Processing Element X<br>(S/R) | R'15-0, F'15-0 | R'15-0, F'15-0  | xR31:16,xFR31-16 | xR31:16,xFR31-16 |

| Processing Element Y<br>(P/R) | N/A            | S15:0, SF15-0   | yR15-0, yFR15-0  | yR15-0, yFR15-0  |

| Processing Element Y<br>(S/R) | N/A            | S'15:0, SF15-0  | yR31-16,yFR31-16 | yR31-16,yFR16-0  |

|                               |                | Data Addressing |                  |                  |

| Index (P/R)                   | I7-0(DAG1),    | I7-0(DAG1),     | J11-4(JALU),     | J11-4(JALU),     |

|                               | I15-8(DAG2)    | I15-8(DAG2)     | K11-4(KALU)      | K11-4(KALU)      |

| Index (S/R)                   | I'7-0(DAG1),   | I'7-0(DAG1),    | J27-20(JALU),    | J27-20(JALU),    |

|                               | I'15-8(DAG2)   | I'15-8(DAG2)    | K27-20(KALU)     | K27-20(KALU)     |

| Modify (P/R)                  | M7-0(DAG1),    | M7-0(DAG1),     | J19-12(JALU),    | J19-12(JALU),    |

|                               | M15-8(DAG2)    | M15-8(DAG2)     | K19-12(KALU)     | K19-12(KALU)     |

| Modify (S/R)                  | M'7-0(DAG1),   | M'7-0(DAG1),    | J30-28(JALU),    | J30-28(JALU),    |

|                               | M'15-8(DAG2)   | M'15-8(DAG2)    | K30-28(KALU)     | K30-28(KALU)     |

| Circular Buffers              | I7-0(DAG1),    | I7-0(DAG1),     | J3-0(JALU),      | J3-0(JALU),      |

|                               | I15-8(DAG2)    | I15-8(DAG2)     | K3-0(KALU)       | K3-0(KALU)       |

| Length                        | L7-0(DAG1),    | L7-0(DAG1),     | JL3-0(JALU),     | JL3-0(JALU),     |

|                               | L15-8(DAG2)    | L15-8(DAG2)     | KL3-0(KALU)      | KL3-0(KALU)      |

| Base                          | B7-0(DAG1),    | B7-0(DAG1),     | JB3-0(JALU),     | JB3-0(JALU),     |

|                               | B15-8(DAG2)    | B15-8(DAG2)     | KB3-0(KALU)      | KB3-0(KALU)      |

| Register Type                    | ADSP-2106x                                                                                | ADSP-2116x                                                                                           | ADSP-TS101                       | ADSP-TS201                       |

|----------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|

|                                  |                                                                                           | Program Sequencer                                                                                    |                                  |                                  |

| Program Counter                  | PC                                                                                        | PC                                                                                                   | PC                               | PC                               |

| Program Counter<br>Stack         | PCSTK                                                                                     | PCSTK                                                                                                | N/A                              | N/A                              |

| Program Counter<br>Stack Pointer | PCSTKP                                                                                    | PCSTKP                                                                                               | N/A                              | N/A                              |

| Loop Counter                     | LCNTR                                                                                     | LCNTR                                                                                                | LC1-0                            | LC1-0                            |

| Loop Termination<br>Address      | LADDR                                                                                     | LADDR                                                                                                | N/A                              | N/A                              |

| Current Loop Counter             | CURLCNTR                                                                                  | CURLCNTR                                                                                             | N/A                              | N/A                              |

|                                  |                                                                                           | Bus Exchange                                                                                         |                                  |                                  |

|                                  | PX, PX1 & PX2                                                                             | PX, PX1 & PX2                                                                                        | N/A                              | N/A                              |

|                                  |                                                                                           | Timer                                                                                                |                                  |                                  |

| Period Register                  | TPERIOD                                                                                   | TPERIOD                                                                                              | TMRIN1-0H/L                      | TMRIN1-0H/L                      |

| Count Register                   | TCOUNT                                                                                    | TCOUNT                                                                                               | TIMER1-0H/L                      | TIMER1-0H/L                      |

|                                  |                                                                                           | System Registers                                                                                     |                                  |                                  |

| Control                          | MODE2-1                                                                                   | MODE2-1                                                                                              | SQCTL                            | SQCTL,<br>INTCTL                 |

| Interrupts                       | IRPTL, IMASK,<br>IMASKP                                                                   | IRPTL, IMASK,<br>IMASKP, MMASK                                                                       | ILATH/L, IMASH/L,<br>PMASKH/L    | ILATH/L, IMASH/L,<br>PMASKH/L    |

| Flags                            | MODE2                                                                                     | FLAGS                                                                                                | SQCTL                            | FLAGS                            |

| Status                           | ASTAT, STKY,<br>USTAT2-1                                                                  | ASTATx/y, STKYx/y,<br>USTAT4-1                                                                       | ASTATx/y,<br>JSTATx/y, KSTATx/y  | ASTATx/y,<br>JSTATx/y, KSTATx/y  |

|                                  |                                                                                           | System Control                                                                                       |                                  |                                  |

| Configuration                    | SYSCON, SYSTAT,<br>WAIT, VIRPT                                                            | SYSCON, SYSTAT,<br>WAIT, VIRPT                                                                       | SYSCON, SYSTAT,<br>SDRCON        | SYSCON, SYSTAT,<br>SDRCON        |

| IOP Registers                    | MSGR7-0                                                                                   | MSGR7-0                                                                                              | N/A                              | N/A                              |

| Bus                              | MODE2, BMAX,<br>BCNT                                                                      | MODE2, BMAX,<br>BCNT                                                                                 | BUSLK, BMAX,<br>BMAXC            | BUSLK, BMAX,<br>BMAXC            |

| DMA                              |                                                                                           |                                                                                                      |                                  |                                  |

| External Port                    | EPB3-0, DMAC9-6,<br>II9-6, EI9-6, IM9-6,<br>EM9-6, C9-6, EC9-6,<br>CP9-6, GP9-6           | EPB3-0, DMAC13-10,<br>II13-10, EI13-10,<br>IM13-10, EM13-10,<br>C13-10, EC13-10,<br>CP13-10, GP13-10 | DCS3-0, DCD3-0,<br>DC13-12, DCNT | DCS3-0, DCD3-0,<br>DC13-12, DCNT |

| Link Port                        | II5-3, II1, IM5-3, IM1,<br>C5-3, C1, CP5-3, CP1,<br>GP5-3, GP1, DB5-3,<br>DB1, DA5-3, DA1 | II9-4, IM9-4, C9-4,<br>CP9-4, GP9-4, DB9-4,<br>DA9-4                                                 | DC11-4, DCNT                     | DC11-4, DCNT                     |

| <b>Register Type</b> | ADSP-2106x                                           | ADSP-2116x                                           | ADSP-TS101                          | ADSP-TS201                                        |

|----------------------|------------------------------------------------------|------------------------------------------------------|-------------------------------------|---------------------------------------------------|

| Serial Port          | II3-0, IM3-0, C3-0,<br>CP3-0, GP3-0, DB3-0,<br>DA3-0 | II3-0, IM3-0, C3-0,<br>CP3-0, GP3-0, DB3-0,<br>DA3-0 | N/A                                 | N/A                                               |

| Status               | DMASTAT                                              | DMASTAT                                              | DSTAT                               | DSTAT                                             |

|                      |                                                      | Link Port Control                                    |                                     |                                                   |

| Buffer & Control     | LBUF5-0, LCTL                                        | LBUF5-0, LCTL1-0,<br>LIRPTL                          | LCTL3-0,<br>LBUFTX3-0,<br>LBUFRX3-0 | LRCTL3-0,<br>LTCTL3-0,<br>LBUFTX3-0,<br>LBUFRX3-0 |

| Common               | LCOM                                                 | LCOM                                                 | LSTAT3-0                            | LSTAT3-0                                          |

| Assignment           | LAR                                                  | LAR                                                  | N/A                                 | N/A                                               |

| Service Request      | LSRQ                                                 | LSRQ                                                 | LSTAT3-0                            | LSTAT3-0                                          |

| Serial Port Control  |                                                      |                                                      |                                     |                                                   |

| Buffer & Control     | TX1-0, RX1-0,<br>STCTL1-0,<br>SRCTL1-0               | TX1-0, RX1-0,<br>STCTL1-0,<br>SRCTL1-0               | N/A                                 | N/A                                               |

| Multiplier Registers |                                                      |                                                      |                                     |                                                   |

|                      | MR, MR2-0, MRF,<br>MRF2-0, MRB,<br>MRB2-0            | MR, MR2-0, MRF,<br>MRF2-0, MRB,<br>MRB2-0            | MR3-0, MR4                          | MR3-0, MR4                                        |

P/R: Primary Registers, S/R: Secondary Registers, N/A: Not Applicable

Table 2. SHARC DSP and TigerSHARC Processor Registers Mapping Scheme

Table 2 lists TigerSHARC processorregisters that are relevant to the SHARCDSPs registers. It does not list allTigerSHARC registers.

For details on all TigerSHARC registers, refer to the *ADSP-TS101 TigerSHARC Processor Hardware Reference* [5] and the *ADSP-TS201 TigerSHARC Processor Hardware Reference* [7].

## 4.1 Register File

The register file of first-generation ADSP-2106x processors features two sets (primary and secondary) of 16 40-bit-wide registers (R0-R15) for fast context switching.

The same applies to the ADSP-2116x SHARC DSP register file, with the addition of a second register file set (S0-S15) for SIMD operations (Single-Instruction Multiple-Data). The two register files and the included arithmetic units are referred to as Processing Element X (PEx) and Processing Element Y (PEy).

ADSP-2106x DSPs are SISD machines (Single-Instruction Single-Data) and therefore do not have a PEy unit.

The TigerSHARC processor's Compute Block X (CBx) register file set has 32 32-bit registers (XR0-XR31), but has no extra set for fast context switching. However, since the register file has twice the number of registers, direct register mapping can be accomplished.

TigerSHARC processors also have a second processing unit, Compute Block Y (CBy), with a set of 32 32-bit registers (YR0-YR31). These registers can be mapped directly to the PEy register set of the ADSP-2116x SHARC DSPs when performing SIMD operations.

The register file mapping used throughout this document is as follows:

$R15-0 \Rightarrow xR15-0$  (SISD operations)

$R'15-0 \Rightarrow xR31-16$  (SISD operations)

$s15-0 \Rightarrow yR15-0$  (SIMD operations)

$s'15-0 \Rightarrow yR31-16$  (SIMD operations)

Single quotes (') are used to denote the alternate or secondary register set.

Refer to section 5.1 Register File for SHARC DSP programming examples and their TigerSHARC processor equivalent.

# 4.2 Data Addressing

As shown in Table 2, the SHARC DSP Data Address Generators (DAGs) are replaced by the TigerSHARC Integer Arithmetic Logic Units (IALUs).

Generally, the IALUs (JALU and KALU) have the same functionality as the DAGs (DAG1 and DAG2). Additionally, IALUs can also perform arithmetic and logical operations (add and subtract, arithmetic and logic shift, logical operations, as well as some mathematical functions – ABS, MIN, MAX, etc.), resulting in extra capacity for computationally demanding applications.

Unlike DAGs, both IALUs are connected to all internal memory blocks, enabling each IALU to

address any memory block (i.e., there are no DM/PM limitations).

Also, each IALU contains a register file (32 32bit registers) with dedicated registers for circular buffer addressing.

Because of their flexible register set and ability to address any memory block, each IALU register can be mapped to any DAG register. Throughout this EE-Note, the following SHARC-to-TigerSHARC data addressing register map is used:

*I7-0 ⇒ J11-4, I15-8 ⇒ K11-4*

*M*7-0 *⇒ J*19-12, *M*15-8 *⇒ K*19-12

*I'7-0 ⇒ J27-20, I'15-8 ⇒ K27-20*

$M'7-0 \Rightarrow J30-28, M'15-8 \Rightarrow K30-28$

Similar to the Processing Element register files, each DAG has a secondary register set on the SHARC architecture. Since TigerSHARC processors do not have these extra sets and have only 32 IALU registers per unit (J and K), the number of alternate modifier registers is limited to 3 instead of 8. This, however, should not impact most (if not all) applications, because not all other available modifier registers (J/K19-12, J/K30-28) will be in use at the very same time.

Unlike the other IALU registers, J31 and K31 cannot be used as general-purpose registers.

For more details, refer to the *ADSP*-*TS101 TigerSHARC Processor Programming Reference* [6] and the *ADSP-TS201 TigerSHARC Processor Programming Reference* [8].

DAGs support loading/storing of data using the PM and DM buses in the same instruction (e.g., dm(i0,m0)=r0, f8=pm(i8,m8);).

IALUs support the use of the JALU and KALU in parallel. However, due to the register mapping scheme used throughout this EE-Note, dedicating CBx registers to Pex (CBy to Pey), JALU and

KALU cannot be used in the same instruction for storing data from CBx:

```

// Parallel LOAD from memory-ALLOWED

xr0 = [j4+j12]; xr1 = [k4+=k12];;

//Parallel STORE to memory-NOT ALLOWED

[j4+=j12] = xr2; [k4+=k12] = xr3;;

// Parallel STORE to memory-ALLOWED

[j4+=j12] = xr2; [k4+=k12] = yr3;;

```

## Code 1. JALU and KALU Parallel Instructions

The second instruction in Code 1 results in a resource violation since the number of required CBx output ports (2) exceeds the allowed maximum (1). As shown in the third instruction, using the CBy register for one of the stores to memory is allowed, resulting in the correct use of J and K in the same instruction.

To keep things as simple as possible and to comply with the register map selected for this EE-Note, parallel DM and PM stores will be translated as two individual instructions (e.g., [j4+=j12] = xr2;; [k4+=k12] = xr3;;).

# (j)

For SHARC DSPs, parallel instructions are separated by a comma "," and the end of an instruction line is denoted by a single semicolon ";".

For TigerSHARC processors, a semicolon ";" separates parallel instructions, and a double semicolon "; ;" terminates an instruction line.

Refer to section 5.2.1 Post-Modify and Pre-Modify for SHARC DSP programming examples and their TigerSHARC Processor equivalent.

# 4.2.1 Circular Buffers

Although TigerSHARC processors have 32 J and 32 K IALU registers, only eight circular buffers can be used at a time (via J0–J3 and K0–K3, and their respective JL/KL and JB/KB registers).

For this reason, 17-10 and 115-18 have been mapped to J11-J4 and K11-K4, allowing J3-J0and K3-K0 to be dedicated for circular buffers.  $I7-0 \Rightarrow J3-0, I15-8 \Rightarrow K3-0$  $L7-0 \Rightarrow JL3-0, L15-8 \Rightarrow KL3-0$  $B7-0 \Rightarrow JB3-0, B15-8 \Rightarrow KB3-0$

Refer to section 5.2.2 Circular Buffers for SHARC DSP programming examples and their TigerSHARC processor equivalent.

## 4.2.2 Addressing in SISD and SIMD

The following section applies only to ADSP-2116x SHARC DSPs. It does not apply to first-generation ADSP-2106x SHARC DSPs.

SIMD mode does not change the addressing operations in the DAGs; it changes the amount of data that moves during each access. The DAGs put the same addresses on the buses in SIMD and SISD modes. In SIMD mode, the DSP's memory and processing elements get data from the locations named (explicit) in the instruction syntax and the complementary (implicit) locations.

This differs in TigerSHARC processors. In this case, SIMD is no longer a processor mode. TigerSHARC SIMD operation are controlled at instruction level. Specifying "x" as part of the instruction performs an operation using the CBx. Specifying "y" as part of the instruction performs an operation in CBy. Using "xy" or "yx" results in an operation in both compute blocks, CBx and CBy.

The order in which "x" and "y" are specified influences the way data is moved between memory and the compute blocks. Specifying "xy" (e.g., xyR0) moves the lower portion of the data to/from CBy and the higher portion to/from CBx.

On the other hand, specifying "yx" (e.g., yxR0) moves the lower portion of the data into or from CBx and the higher portion into or from CBy.

Additionally, when neither "x" nor "y" precedes the register file name (e.g., R0), the data move will be performed in one of the following two ways: in the same manner as for "xy" (i.e., the lower portion to/from CBy and the higher

to/from CBx) or the same data to/from both CBx and CBy. This depends on the number of registers specified as the source or destination of the transaction, as well as the length of the data being transferred.

Moving the same data from/to both compute blocks is equivalent to Broadcast mode of the ADSP-2116x SHARC DSPs. In this mode, identical data is moved to/from each processing element.

Refer to section 5.2.3 Addressing in SISD and SIMD for SHARC DSP programming examples and their TigerSHARC processor equivalent.

## 4.3 Program Sequencer

This section details some of the fundamental differences in the program sequencer between SHARC DSPs and TigerSHARC processors. This is not an in-depth comparison of the two program sequencers; only specific parts deemed important for the successful conversion of source code from the SHARC DSP to the TigerSHARC processor are covered. For detailed information on SHARC DSP and TigerSHARC processor program sequencers, refer to the hardware documentation listed in section 9 References.

The following subjects will be covered briefly, focusing on the main differences with regards to programming between the SHARC DSPs and the TigerSHARC processor.

- Instruction pipeline

- Instruction cache and BTB

- Program flow variations

- Interrupts

# 4.3.1 Instruction Pipeline

As shown in Table 1, SHARC DSPs have an instruction pipeline depth of three thus processing instructions in three clock cycles. TigerSHARC processors have a much larger, fully interlocked pipeline. For ADSP-TS101 processors, the pipeline depth is 8; for ADSP-TS20x processors, the depth is 10. For sequential

accesses, pipeline depth does not pose a problem when converting SHARC DSP code to the TigerSHARC processor. The pipeline comes into effect for non-sequential accesses such as jumps, subroutine calls and returns, interrupts, and loops. Due to the fully interlocked pipeline of the TigerSHARC processors, you do not need to be aware of the order of execution of instructions and when data will be available with regard to functionality. However. correct from performance perspective, this is an important area and is covered in great detail in the ADSP-TS101 TigerSHARC Processor Programming Reference [6] and the ADSP-TS201 TigerSHARC Processor Programming Reference [8].

## 4.3.2 Instruction Cache and BTB

Engineers familiar with the SHARC DSP family should be aware of the instruction cache that is located within the program sequencer. The instruction cache allows for simultaneous fetching of an instruction and a program memory data access. TigerSHARC processors do not require an instruction cache in the program sequencer due to the number of memory blocks. There are a sufficient number of memory blocks and internal buses so that an instruction fetch and two data accesses can take place without an instruction cache. This, however, is largely dependent upon how data and program memory is structured within the Linker Description File (.LDF).

The TigerSHARC program sequencer does have a form of cache known as a branch target buffer (BTB). The BTB is a 32 entry 4-way set associative cache that has been implemented to help reduce the number of stalls incurred with non-sequential accesses on these deeply pipelined processors. The destination address of a branch instruction can be stored to the BTB, acting as an early indication for the sequencer on the next iteration where to continue fetching code. The BTB becomes especially important in loop execution in which incorrect usage can result in significant loss of performance.

To use the BTB, the BTB must be enabled and the sequencer must predict the instruction flow. Predicted instruction flow is the default method of a branch instruction. However, you can specify that a branch is not predicted to occur. This is especially useful for conditional branch instructions in which the condition is more likely to be false than true. Non-predicted branches do not update the BTB.

Examples of writing predicted and non predicted branch instructions are shown below. Refer to section 5.3.2 Loops for a complete loop example.

```

/* conditional branch based on the

result of an X compute block

computation being equal to zero */

If xaeq, jump label;;

```

- /\* conditional branch with prediction

based on the result of an X compute

block computation being equal to

zero \*/

- If xaeq, jump label (P);;

- /\* conditional branch with no

prediction based on the result of

an X compute block computation

being equal to zero \*/

If xaeq, jump label (NP);;

# Code 2. Predicted and Non-predicted Branch

In the first example above, no option has been placed at the end of the instruction. By default, this will be predicted but can be forced to be predicted or non-predicted through the tools with the use of an assembler switch. Refer to the *VisualDSP++ 3.5 Assembler and Preprocessor Manual for TigerSHARC Processors* [13] for further details.

For a detailed description of the BTB and its operation, Refer to the *ADSP-TS101 TigerSHARC Processor Programming Reference* [6] and the *ADSP-TS201 TigerSHARC Processor Programming Reference* [8].

# 4.3.3 Program Flow Variations

The program flow of SHARC DSPs and TigerSHARC processors is mostly linear. This

linear flow varies, however, when the program uses non-sequential program structures such as:

- Jumps

- Loops

- Subroutines

- Interrupts

- Idle

For a list of typical sequencer instructions on the SHARC DSPs and their TigerSHARC processor equivalent, refer to Table 3 at the end of this section.

There is a difference in the way that a CALL instruction is handled by the program sequencers on SHARC DSPs and TigerSHARC processors. Because TigerSHARC processors have no PC stack, the return address from the CALL is instead saved to the CJMP register. Therefore, before performing another CALL, the CJMP register must be saved to memory, otherwise the return location for the preceding CALL will be lost. A return from a CALL on TigerSHARC processors is performed using the CJMP instruction. Thus, the CJMP instruction on TigerSHARC processors maps directly to the RTS instruction on SHARC DSPs.

One fundamental difference between branching on the SHARC DSPs and TigerSHARC processors is that the TigerSHARC program sequencer does not support the delayed branch feature. Thus, when converting unconditional delayed branches (i.e., call label (db);), move the two instructions immediately following the delayed branch to before the branch. However, when converting conditional delayed branches (e.g., IF EQ JUMP(PC, label) (db);), copy the two instructions immediately following the delayed branch (without deleting them from their original location) to the beginning of the target branch. Refer to section 5.3.1 Pipeline for a delayed branch example.

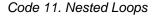

Both SHARC DSPs and TigerSHARC processors support zero-overhead looping execution. SHARC DSPs support up to six

nested loops using the program sequencer's loop support registers.

The setup of a loop requires a loop counter register, an instruction to decrement the counter, and a conditional instruction to terminate the loop at the required time. The main difference between setting up a loop on the SHARC DSPs and the TigerSHARC processors is that the SHARC DSPs require the use of a DO/UNTIL instruction as the conditional instruction. The instruction immediately following the DO/UNTIL is the first instruction of the loop, and the last instruction of the loop is indicated by a label.

```

LCNTR = count, DO label UNTIL LCE;

/* first instruction */

Instruction;

.....

/* last instruction in loop */

label: Instruction;

```

Code 3. SHARC DSP Loop

When executing the DO/UNTIL instruction, the program sequencer pushes the address of the loop's last instruction and the loop's termination condition onto the loop address stack. The sequencer also pushes the address of the instruction following the DO/UNTIL instruction onto the PC stack.

The TigerSHARC sequencers do not work in this manner. They do not have a loop address stack or a PC stack from which the required instructions can be read. Instead, they have two dedicated loop counter registers (LCO and LC1) and special loop counter conditions (IF NLCOE, IF NLC1E, IF LCOE, and IF LCIE) for setting up zerooverhead loops. If more than two nested loops are required, set up the additional loops using the IALU registers. The effect of these differences between the sequencers means that the loop has a different structure from that of the SHARC DSPs. TigerSHARC On processors, the beginning of the loop is indicated by a label, and a conditional jump instruction is required at the end of the loop to jump back to this label. If the test on the conditional jump is true, the instruction immediately following the conditional instruction is then fetched.

```

LCx = count;;

/*first instruction of loop */

label: Instruction;;....

.....

/* last instruction of loop */

IF NLCxE, jump label; instruction;;

```

# Code 4. TigerSHARC Processor Loop

Refer to section 5.3.2 Loops for examples of setting up and performing loops on SHARC DSPs and how this same operation is translated for operation on TigerSHARC processors.

# 4.3.4 Interrupts

There are significant differences between the way that interrupts are set up on the SHARC DSPs and the TigerSHARC processors. The first point to note is that the interrupt vector addresses on TigerSHARC are not in internal or external program memory as they are on the SHARC DSPs. TigerSHARC processors have dedicated registers within the interrupt controller in which the vector addresses are stored. This register set, known as the Interrupt Vector Table (IVT), contains 30 registers. On SHARC DSPs, there are effectively five steps to process an interrupt, assuming the interrupt is enabled:

- 1. Output the interrupt vector address.

- 2. Push the current PC value onto PC stack.

- 3. Depending on the interrupt that occurred, push the ASTAT and MODE1 registers onto status stack.

- 4. Set the appropriate bit in IRPTL.

- 5. Alter IMASKP to reflect the current interrupt nesting state.

TigerSHARC processors react to interrupts in a different manner; this depends on whether the interrupt is a hardware interrupt or a software exception. For hardware interrupts, assuming the interrupt is enabled:

- 1. Set the appropriate bit in ILATL/ILATH.

- 2. Output the interrupt vector address from IVT.

- 3. Store the current PC to RETI.

- 4. Upon entry to the interrupt service routine (ISR), set the appropriate PMASKL/PMASKH bit and set PMASKH bit 29 to block all hardware interrupts on ADSP-TS101. For ADSP-TS20x processors, instead of setting PMASKH bit 29, set SQSTAT bit 21 to block all hardware interrupts.

For software exceptions, assuming they are enabled:

- 1. For ADSP-TS101 processors, set the appropriate bit in ILATH. For ADSP-TS20x processors, set appropriate bit in SQSTAT.

- 2. Output the interrupt vector address.

- 3. Store the current PC to RETS.

Because of differences in the way that SHARC DSPs and TigerSHARC processors handle interrupts, one question immediately comes to mind: how do you nest interrupts on the TigerSHARC processors?

This is one of the significant differences between two families. Because the TigerSHARC processors have no PC stack and do not save registers (there is no status stack), the nesting of interrupts must be performed in the ISR itself. There is no nesting enable bit in a control register. For this reason, all interrupts are disabled upon entry to the ISR, this allows you to save registers to memory (or the C run-time stack). This includes the saving of the RETI register. Failure to save the contents of the RETI register to memory before enabling the nesting or re-using of interrupts will result in the loss of the return address. Interrupts on TigerSHARC processors are nested or re-used by execution of special instructions. For nested interrupts, you must save the RETIB register to memory. Saving the RETIB register to memory results in the following two actions being performed:

- 1. Saves the contents of RETI to memory. The current contents of RETI are the return address from the interrupt.

- 2. On ADSP-TS101 processor, bit 29 of the PMASKH register is cleared, allowing for higher priority interrupts to now occur. On ADSP-TS20x processors, bit 21 of the SQSTAT register is cleared, allowing for higher priority interrupts to occur.

If the interrupt service routine is not nested, restore registers that were saved to a stack at the beginning of the ISR before executing the RTI instruction, which returns to normal program flow. If the interrupt was nested, however, before restoring any registers, disable the interrupts again so as not to clobber any data and risk losing the correct return address. This is performed by restoring the RETIB register from the location from which it was stored in memory. Once this register has been restored, no further interrupts may occur. This allows for safe restoration of any registers. The ISR is then exited using the RTI instruction.

Re-usable interrupts are enabled on TigerSHARC processors by using the reduce to subroutine instruction (RDS). RDS is not equivalent to the RTS instruction on SHARC DSPs. The RDS instruction on TigerSHARC processors has an equivalent effect, clearing the interrupt status option (CI), which is appended to a JUMP instruction within the interrupt vector table on SHARC DSPs. Similar to nested interrupts, save the status and any required registers to the stack, including the RETI register, before executing the RDS instruction. To safely restore all registers at the end of the ISR that has been reduced to a subroutine (including the correct return address), all interrupts must be disabled. This can be achieved by using a similar method to that of nested interrupts, by restoring the return address to the RETIB register. The processor status registers and any registers saved to the stack can then be safely restored from the stack before returning from the ISR.

To return from an ISR that has been reduced to subroutine level, execute the RETI instruction. This instruction returns from the interrupt without modifying any of the mask pointer (PMASK) register bits. However, since interrupts are still disabled, execute this instruction in parallel with a dummy save of the RETIB register. This results in the interrupts being enabled again after return from the ISR.

This method of returning from a subroutine is assuming provides a safe method of effectively nesting not only higher priority interrupts, but also the same interrupt and lower priority interrupts.

Since there is no PC stack on TigerSHARC processors, the only limit to the number of interrupts that may be nested correctly is the size of the stack defined in memory. For details on complying with the C run-time environment stack within assembly routines, refer to section 6 C Run-Time Environment. Examples of setting up interrupts, nested interrupts, and re-usable interrupts on SHARC DSPs and TigerSHARC processors are provided in section 5.3.3 **TigerSHARC** Interrupts. The processor's program sequencer has a different method for handling software exceptions. On SHARC DSPs, software exceptions can result from:

- Fixed-point overflow

- Floating-point overflow

- Floating-point underflow

- Floating-point invalid operation

- User software interrupt 0-3

TigerSHARC processors have extended functionality to the above software exceptions. The exceptions are enabled and handled in a different manner from the SHARC DSPs. On SHARC DSPs, the exceptions previously introduced are enabled from within the IMASK register, where each exception has its own interrupt vector. On TigerSHARC processors, there is only one interrupt handler for all software exceptions. This interrupt handler must read all required registers to determine the cause of the exception. The cause of the exception is determined by reading the EXCAUSE field of the SQSTAT register. The cause of the exception may be any of the following:

- TRAP instruction

- Watchpoint match

- Floating-point exception

- Illegal instruction line

- Non-aligned access

- Protected register access

- Performance monitor counter wrap

- Illegal IALU access

- Emulation disabled exception

Assuming software exceptions are enabled in the IMASK register for ADSP-TS101 processors or the SQCTL register for ADSP-TS20x processors, for any invalid floating-point operation to generate software exceptions the Invalid enable bit (IVEN) of the XSTAT/YSTAT register must be set. For an underflow or overflow operations to generate a software exception, the underflow enable bit (UEN) or overflow enable bit (OEN) must be set in the XSTAT/YSTAT register.

The four user software exceptions on SHARC DSPs can be implemented on TigerSHARC processors by using the TRAP instruction. On SHARC DSPs, you would force the setting of the corresponding software exception bit in the IRPTL register; instead, replace this instruction with TRAP. TigerSHARC processors can support up to 32 TRAP instructions, effectively allowing for 32 user software exceptions. The TRAP instruction is appended with a 5-bit value. When the instruction is executed, this 5-bit value is stored in the SQSTAT register. The software exception ISR would determine that a TRAP instruction has occurred by reading the value obtained from the EXCAUSE field. The specific action to be taken for the TRAP instruction is

determined by reading the 5-bit value from the SPVCMD field of the SQSTAT register.

Similar to SHARC DSPs, software exceptions on the TigerSHARC processors have a higher priority than hardware interrupts. Upon entry to the software exception ISR, the return address is stored to the RETS register. However to exit the ISR, the RTI instruction is executed. As described earlier, the execution of the RTI instruction results in the modification of the mask pointer bits as well as the return of program flow to the address stored in RETI. For this reason, a special procedure is required to return from a software exception. This involves saving the current value in RETI to memory, so as not to corrupt the return address if a hardware interrupt is being served. Next, load the value stored in RETS into RETI; this sets up the correct return address from the software ISR. Lastly, execute the RTI instruction in parallel with the restoring the RETI register from the place it was saved to in memory.

Refer to section 5.3.3 Interrupts for an example of setting up a user software exception. Table 7 lists program flow control instructions for SHARC DSPs and TigerSHARC processor equivalents.

| SHARC DSP                                                    | TigerSHARC Processor                                         |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------|--|--|

| Direct/PC relative jump                                      |                                                              |  |  |

| JUMP <addr24>;</addr24>                                      | JUMP <addr16 addr32=""  =""> (ABS);;</addr16>                |  |  |

| JUMP (PC, <reladdr24>);</reladdr24>                          | JUMP <reladdr16 reladdr32=""  ="">;;</reladdr16>             |  |  |

| JUMP label;                                                  | JUMP label;;                                                 |  |  |

| Direct/PC                                                    | relative call                                                |  |  |

| CALL <addr24>;</addr24>                                      | CALL <addr16 addr32=""  =""> (ABS);;</addr16>                |  |  |

| CALL (PC, <reladdr24>);</reladdr24>                          | CALL <reladdr16 reladdr32=""  ="">;;</reladdr16>             |  |  |

| CALL label;                                                  | CALL label;;                                                 |  |  |

| Conditional direct/PC relative jump                          |                                                              |  |  |

| IF condition JUMP <addr24>;</addr24>                         | IF condition, JUMP < addr16   addr32> (ABS);;                |  |  |

| IF condition JUMP (PC, <reladdr24>);</reladdr24>             | IF condition, JUMP < reladdr16   reladdr32>;;                |  |  |

| IF condition JUMP label;                                     | IF condition, JUMP label;;                                   |  |  |

| Conditional direct/PC relative call                          |                                                              |  |  |

| IF condition CALL <addr24>;</addr24>                         | IF condition, CALL < addr16   addr32> (ABS);;                |  |  |

| IF condition CALL (PC, <reladdr24>);</reladdr24>             | IF condition, CALL < reladdr16   reladdr32>;;                |  |  |

| IF condition CALL label;                                     | IF condition, CALL label;;                                   |  |  |

| Conditional indirect/PC relative jump/compute                |                                                              |  |  |

| IF condition JUMP (Md, Ic), compute;                         | no equivalent                                                |  |  |

| IF condition JUMP (Md, Ic), ELSE compute;                    | no equivalent                                                |  |  |

| IF condition JUMP (PC, <reladdr6>), compute;</reladdr6>      | IF condition, JUMP < reladdr16   reladdr32>; compute;;       |  |  |

| IF condition JUMP (PC, <reladdr6>), ELSE compute;</reladdr6> | IF condition, JUMP < reladdr16   reladdr32>; ELSE, compute;; |  |  |

| IF condition JUMP label, compute;                                                  | IF condition, JUMP label; compute;;                                                              |  |  |  |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| IF condition JUMP label, ELSE compute;                                             | IF condition, JUMP label; ELSE, compute;;                                                        |  |  |  |

| Conditional indirect/PC relative call/compute                                      |                                                                                                  |  |  |  |

| IF condition CALL (Md, Ic), compute;                                               | no equivalent                                                                                    |  |  |  |

| IF condition CALL (Md, Ic), ELSE compute;                                          | no equivalent                                                                                    |  |  |  |

| IF condition CALL (PC, <reladdr6>), compute;</reladdr6>                            | IF condition, CALL < reladdr16   reladdr32>; compute;;                                           |  |  |  |

| IF condition CALL (PC, <reladdr6>), ELSE compute;</reladdr6>                       | IF condition, CALL < reladdr16   reladdr32>; ELSE, compute;;                                     |  |  |  |

| IF condition CALL label, compute;                                                  | IF condition, CALL label; compute;;                                                              |  |  |  |

| IF condition CALL label, ELSE compute;                                             | IF condition, CALL label; ELSE, compute;;                                                        |  |  |  |

| Conditional indirect/PC re-                                                        | lative jump or dreg $\leftarrow \rightarrow$ DM                                                  |  |  |  |

| IF condition JUMP (Md, Ic), ELSE DM(Ia,Mb) = dreg;                                 | no equivalent                                                                                    |  |  |  |

| IF condition JUMP (Md, Ic), ELSE dreg = DM(Ia,Mb);                                 | no equivalent                                                                                    |  |  |  |

| IF condition JUMP (PC, <reladdr6>), ELSE DM(Ia,Mb) = dreg;</reladdr6>              | IF condition, JUMP < reladdr16   reladdr32>; ELSE [Ja + Jb]<br>= ureg;;                          |  |  |  |

| IF <i>condition</i> JUMP (PC, <reladdr6>), ELSE dreg = DM(Ia,Mb);</reladdr6>       | IF <i>condition</i> , JUMP < reladdr16   reladdr32>; ELSE ureg = [Ja + Jb] ;;                    |  |  |  |

| IF condition JUMP label, ELSE DM(Ia,Mb) = dreg;                                    | IF condition, JUMP label; ELSE [Ja + Jb] = ureg;;                                                |  |  |  |

| IF condition JUMP label, ELSE dreg = DM(Ia,Mb);                                    | IF condition, JUMP label; ELSE ureg = [Ja + Jb] ;;                                               |  |  |  |

| Conditional indirect/PC relative call or dreg ←→DM                                 |                                                                                                  |  |  |  |

| IF condition CALL (Md, Ic), ELSE DM(Ia,Mb) = dreg;                                 | no equivalent                                                                                    |  |  |  |

| IF condition CALL (Md, Ic), ELSE dreg = DM(Ia,Mb);                                 | no equivalent                                                                                    |  |  |  |

| IF condition CALL (PC, <reladdr6>), ELSE DM(Ia,Mb) = dreg;</reladdr6>              | IF condition, CALL < reladdr16   reladdr32>; ELSE [Ja + Jb] = ureg;;                             |  |  |  |

| IF <i>condition</i> CALL (PC, <reladdr6>), ELSE dreg = DM(Ia,Mb);</reladdr6>       | IF <i>condition</i> , CALL < reladdr16   reladdr32>; ELSE ureg = [Ja + Jb] ;;                    |  |  |  |

| IF condition CALL label, ELSE DM(Ia,Mb) = dreg;                                    | IF <i>condition</i> , CALL <i>label</i> ; ELSE [Ja + Jb] = ureg;;                                |  |  |  |

| IF condition CALL label, ELSE dreg = DM(Ia,Mb);                                    | IF condition, CALL label; ELSE ureg = [Ja + Jb] ;;                                               |  |  |  |

| Conditional indirect/PC relative jump or compute/dreg $\leftarrow \rightarrow$ DM  |                                                                                                  |  |  |  |

| IF condition JUMP (Md, Ic), ELSE compute, DM(Ia,Mb) = dreg;                        | no equivalent                                                                                    |  |  |  |

| IF condition JUMP (Md, Ic), ELSE compute, dreg = DM(Ia,Mb);                        | no equivalent                                                                                    |  |  |  |

| IF condition JUMP (PC, <reladdr6>), ELSE compute,<br/>DM(Ia,Mb) = dreg;</reladdr6> | IF condition, JUMP < reladdr16   reladdr32>; ELSE<br>compute; [Ja + Jb] = ureg;;                 |  |  |  |

| IF condition JUMP (PC, <reladdr6>), ELSE compute, dreg = DM(Ia,Mb);</reladdr6>     | IF <i>condition</i> , JUMP < reladdr16   reladdr32>; ELSE <i>compute</i> ;<br>ureg = [Ja + Jb];; |  |  |  |

|                                                                                    | 1                                                                                                |  |  |  |

| IF condition JUMP label, ELSE compute, DM(Ia,Mb) = dreg;                                     | IF condition, JUMP label; ELSE compute; [Ja + Jb] = ureg;;                                       |  |  |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| IF condition JUMP label, ELSE compute, dreg = DM(Ia,Mb);                                     | IF <i>condition</i> , JUMP <i>label</i> ; ELSE <i>compute</i> ; ureg = [Ja + Jb];;               |  |  |

| Conditional indirect/PC relativ                                                              | we call or compute/dreg $\leftarrow \rightarrow$ DM                                              |  |  |

| IF condition CALL (Md, Ic), ELSE compute, DM(Ia,Mb) = dreg;                                  | no equivalent                                                                                    |  |  |

| IF condition CALL (Md, Ic), ELSE compute, dreg = DM(Ia,Mb);                                  | no equivalent                                                                                    |  |  |

| IF condition CALL (PC, <reladdr6>), ELSE compute,<br/>DM(Ia,Mb) = dreg;</reladdr6>           | IF condition, CALL < reladdr16   reladdr32>; ELSE<br>compute; [Ja + Jb] = ureg;;                 |  |  |

| IF <i>condition</i> CALL (PC, <reladdr6>), ELSE <i>compute</i>, dreg = DM(Ia,Mb);</reladdr6> | IF <i>condition</i> , CALL < reladdr16   reladdr32>; ELSE <i>compute</i> ;<br>ureg = [Ja + Jb];; |  |  |

| IF condition CALL label, ELSE compute, DM(Ia,Mb) = dreg;                                     | IF condition, CALL label; ELSE compute; [Ja + Jb] = ureg;;                                       |  |  |

| IF condition CALL label, ELSE compute, dreg = DM(Ia,Mb);                                     | IF <i>condition</i> , CALL <i>label</i> ; ELSE <i>compute</i> ; ureg = [Ja + Jb];;               |  |  |

| Return from sub                                                                              | routine or interrupt                                                                             |  |  |

| RTS;                                                                                         | CJMP(ABS);;                                                                                      |  |  |

| К13,                                                                                         | RETI;;                                                                                           |  |  |

| RTI;                                                                                         | RTI(ABS);;                                                                                       |  |  |

| Conditional return from sub                                                                  | proutine or interrupt / compute                                                                  |  |  |

| IF condition RTS;                                                                            | IF condition, CJMP(ABS);;                                                                        |  |  |

| IF condition K1S,                                                                            | IF condition, RETI(ABS);;                                                                        |  |  |

| IF condition RTI;                                                                            | IF condition RTI(ABS);;                                                                          |  |  |

|                                                                                              | IF condition, CJMP(ABS); compute;;                                                               |  |  |

| IF condition RTS, compute;                                                                   | IF condition, RETI(ABS); compute;;                                                               |  |  |

| IF condition RTI, compute;                                                                   | IF condition RTI(ABS); compute;;                                                                 |  |  |

| Conditional return from sub                                                                  | routine or interrupt or compute                                                                  |  |  |

|                                                                                              | IF condition, CJMP(ABS); ELSE compute;;                                                          |  |  |

| IF condition RTS, ELSE compute;                                                              | IF condition, RETI(ABS); ELSE compute;;                                                          |  |  |

| IF condition RTI, ELSE compute;                                                              | IF condition RTI(ABS); ELSE compute;;                                                            |  |  |

| Do until counter expired                                                                     |                                                                                                  |  |  |

| LCNTR = <data16>, Do <addr24> UNTIL LCE;</addr24></data16>                                   | LCx = <data32>;;</data32>                                                                        |  |  |

| LCNTR = ureg, Do <addr24> UNTIL LCE;</addr24>                                                | label:                                                                                           |  |  |

| LCNTR = <data16>, Do (PC, <reladdr24>) UNTIL LCE;</reladdr24></data16>                       |                                                                                                  |  |  |

| LCNTR = ureg, Do (PC, <reladdr24>) UNTIL LCE;</reladdr24>                                    | IF NLCxE, JUMP <i>label</i> ;;                                                                   |  |  |

| Do until                                                                                     |                                                                                                  |  |  |

|                                                                                              |                                                                                                  |  |  |

| DO <addr24> UNTIL <i>termination</i>;</addr24>      | label:                          |

|-----------------------------------------------------|---------------------------------|

| DO (PC, <reladdr24>) UNTIL termination;</reladdr24> | IF not termination JUMP label;; |

## Table 3. Sequencer Instructions

Notice that all RTS commands on SHARC DSPs have two equivalent instructions on TigerSHARC processors. This depends on whether the RTS instruction is used from a simple call or it is used to reduce an interrupt to subroutine level as described earlier.

Table 4 maps the SHARC DSP conditions to those available on TigerSHARC processors. Some of the conditions cannot be mapped directly to the TigerSHARC. To perform the required action for some of these conditions, the STATUS flag on the TigerSHARC can be masked, and the unmasked bit copied to the static flag register (SF0, SF1); then the condition may be based on SF0, SF1, NSF0, or NSF1. For details on static flag registers, refer to the *ADSP-TS101 TigerSHARC Processor Programming Reference* [6] and the *ADSP-TS201 TigerSHARC Processor Programming Reference* [8]. Note that some additional condition codes on TigerSHARC processors are not available on SHARC DSPs.

| Condition                                           | SHARC DSPs           | TigerSHARC Processors          |

|-----------------------------------------------------|----------------------|--------------------------------|

|                                                     | ALU Conditions       |                                |

| ALU equal zero                                      | EQ                   | ${X   Y   XY}AEQ$              |

| ALU less than zero                                  | LT                   | ${X   Y   XY}ALT$              |

| ALU less than or equal to zero                      | LE                   | $\{X \mid Y \mid XY\}ALE$      |